TPS61280D

ZHCSHC3A - JANUARY 2018-REVISED AUGUST 2018

# 适用于单节锂离子、富镍、硅阳极电池应用的 TPS6128xD 低 IQ、宽电压电池前端直流/直流 转换器

### 1 特性

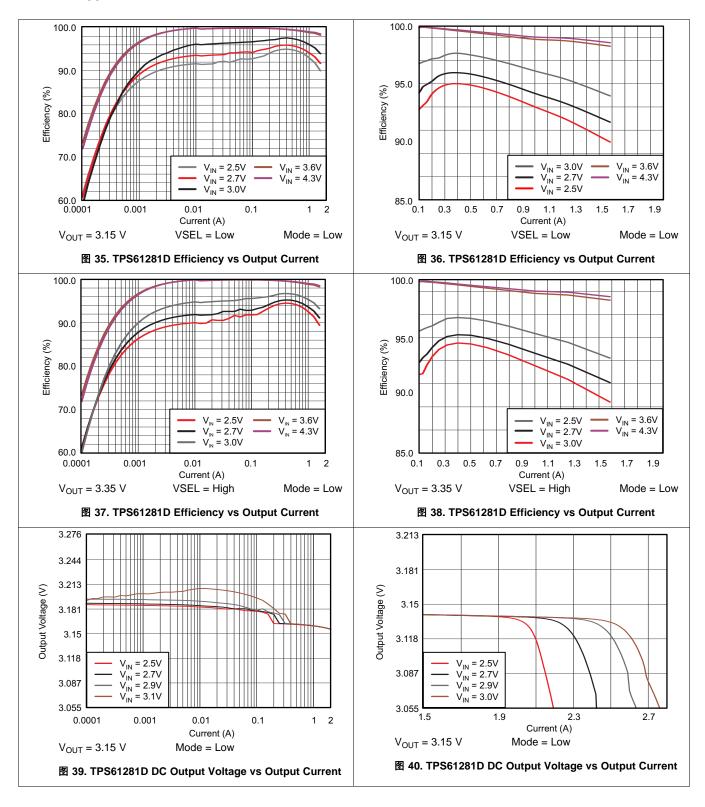

- 频率为 2.3MHz 时,工作效率达 95%

- 低 Io 直通模式下具有 3µA 静态电流

- 2.3V 至 4.8V 的宽 V<sub>IN</sub> 范围

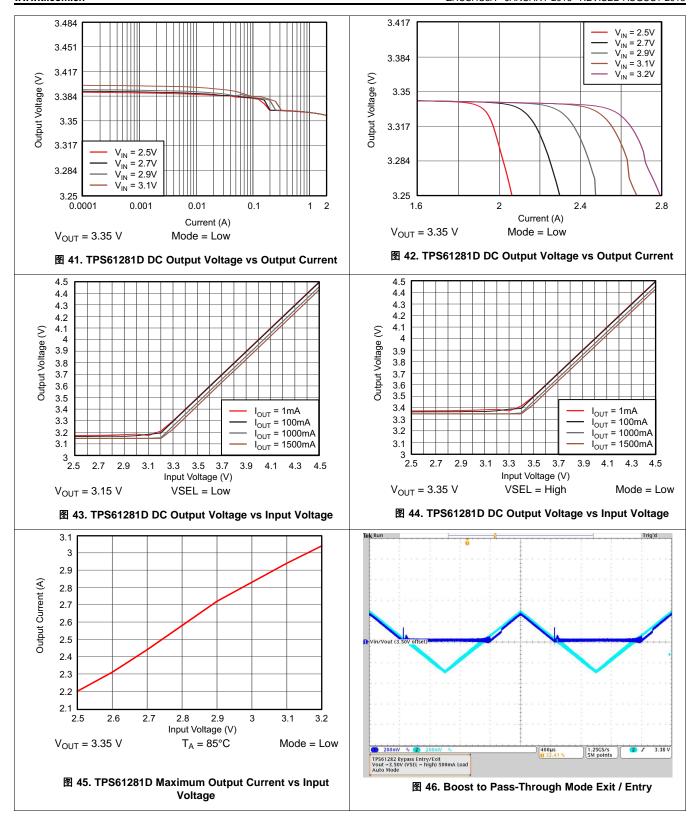

- V<sub>OUT</sub> = 3.35V、V<sub>IN</sub> ≥ 2.65V 时,I<sub>OUT</sub> ≥ 4A(峰值)

- 集成直通模式 (35mΩ)

- 可编程谷值电感器电流限值和输出电压

- 关断期间真正的直通模式

- 同类产品中最佳的 线路和负载瞬态

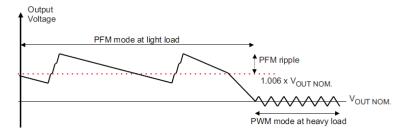

- 低纹波轻负载脉冲频率调制 (PFM) 模式

- 具有片上 E<sup>2</sup>PROM (写保护) 的原样定制

- 两个接口选项:

- 与 I<sup>2</sup>C 兼容的 I/F: 最高 3.4 Mbps (TPS61280D)

- 简单 I/O 逻辑控制接口

- 热关断和过载保护

- 总体解决方案尺寸 < 20mm², 高度低于 1mm

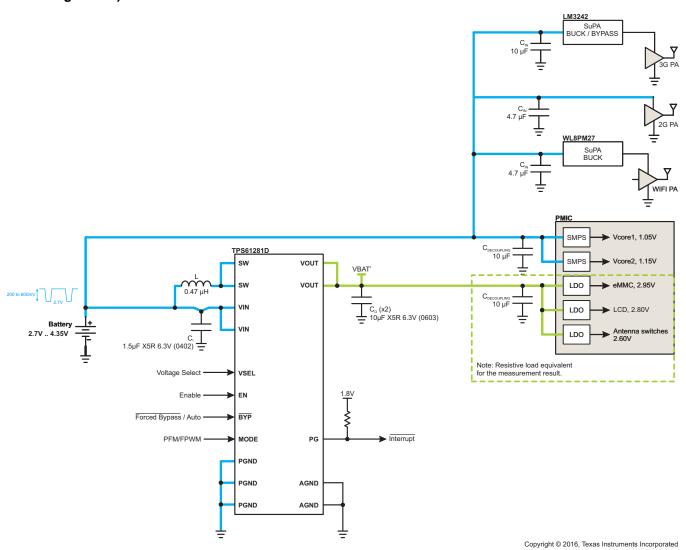

### 2 应用

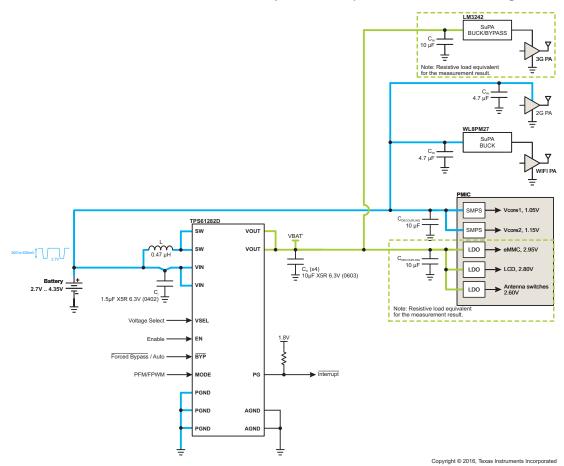

- 单节富镍、硅阳极、锂离子、磷酸铁锂 (LiFePO4) 智能手机或平板电脑

- 2.5G、3G、4G 小型模块数据卡

- 负载峰值功率较高 的 电流受限应用

### 3 说明

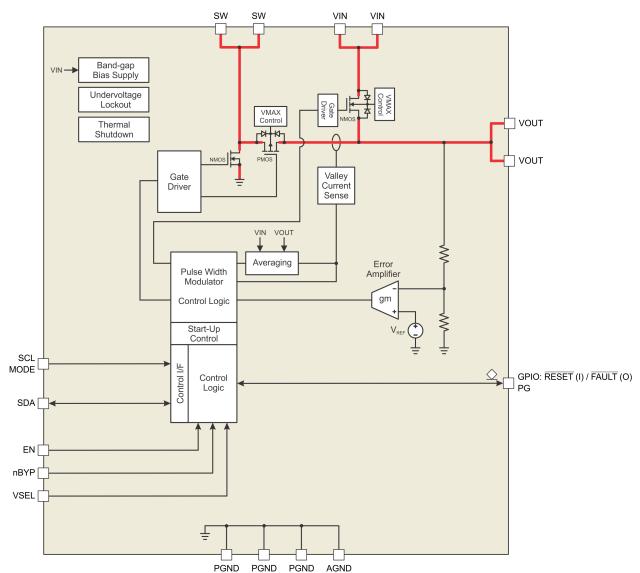

TPS6128xD 器件可以为由锂离子、富镍、硅阳极或磷酸铁锂电池供电的产品提供电源解决方案。电压范围针对诸如智能手机或平板电脑内的单节电池便携式应用进行了优化。

TPS6128xD 可用作高功率预稳压器,延长电池运行时间并克服受电系统的输入电流和电压限制。

在关断情况下,TPS6128xD 运行在真正的直通模式下,静态耗电仅为 3µA,从而可充分延长电池寿命。

运行期间,当电池处于良好的充电状态中时,一个低欧姆、高效集成直通路径将电池连接至受电系统。

如果电池进入较低的充电状态,并且其电压变为低于所需的最小系统电压时,此器件无缝转换至升压模式以利用整个电池容量。

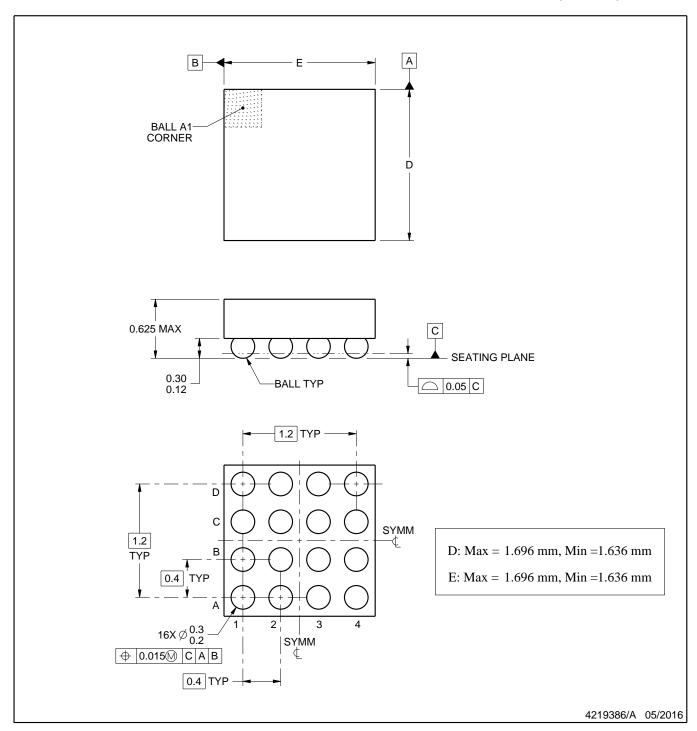

# 器件信息<sup>(1)</sup>

|           | BB 11 1B 10 |                 |

|-----------|-------------|-----------------|

| 器件型号      | 封装          | 封装尺寸 (标称值)      |

| TPS61280D |             |                 |

| TPS61281D | DSBGA (16)  | 1.66mm x 1.66mm |

| TPS61282D |             |                 |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

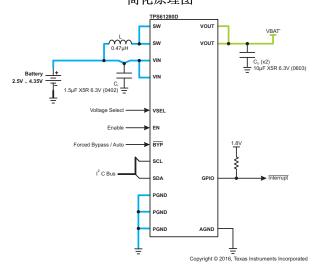

# 简化原理图

| 1       特性       1       9.4 Device Functional Modes         2       应用       1       9.5 Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 22<br>25 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 25       |

| 3 说明 1 9.6 Register Maps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ion 33   |

| 5 说明(续)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |

| 7 Pin Configuration and Functions 4 11 Power Supply Recommendation 12 Layout 12 Layout 12 Layout 13 Layout 14 Layout 15 Layout 15 Layout 16 Layout 17 Layout 17 Layout 18 Layout |          |

| 8.1 Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 46       |

| 8.3 Recommended Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 48       |

| 8.5 Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 48       |

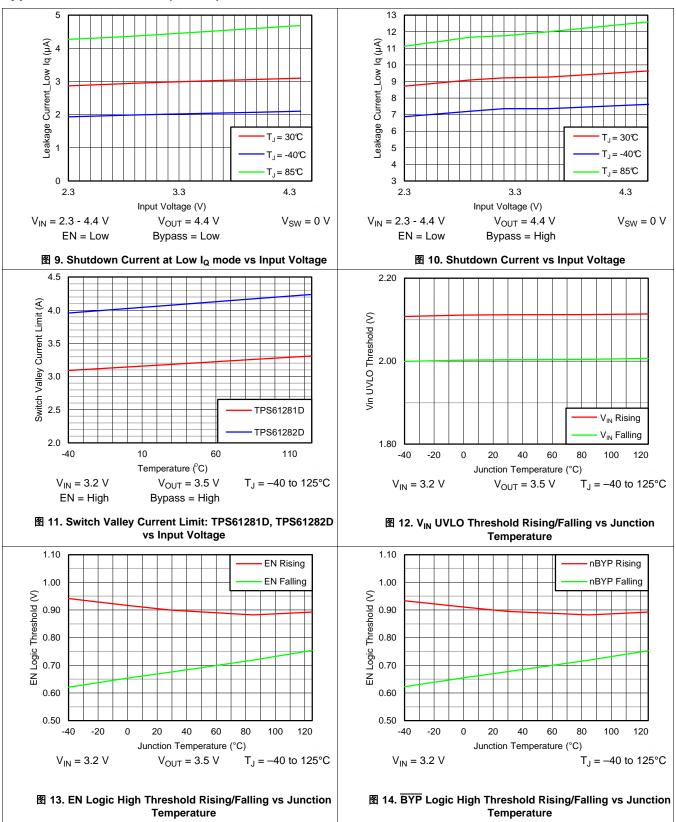

| 8.8 Typical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

| 9.1 Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

# 4 修订历史记录

| CI | Changes from Original (January 2018) to Revision A |   |  |  |

|----|----------------------------------------------------|---|--|--|

| •  | 将器件 TPS61281D 和 TPS61282D 从产品预览 更改为生产 数据           | 1 |  |  |

| •  | Changed the TPS61280D pin configuration            | 4 |  |  |

| •  | Changed the TPS6128xD pin configuration            | 5 |  |  |

# 5 说明 (续)

TPS6128xD 器件支持超过 4A 的脉冲负载电流,即使是深度放电的电池亦可。在这种运行模式下,TPS6128xD 可充分使用全部电池容量:克服了高最小输入电压的受电组件的电池切断电压过高的问题;新的电池化学物质可完全放电;该器件可对强制系统关断的高电流脉冲进行缓冲,从而实现在升压和绕过模式之间的无缝相互转换。

这会对电池导通时间产生很大影响,从而在相同的电池容量前提下提供更长的使用时间和更佳的用户体验,或者在相同的使用时间前提下降低电池成本。

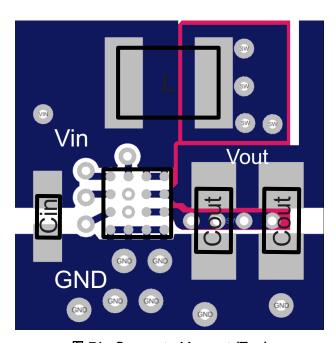

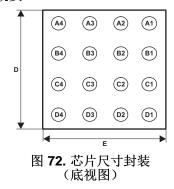

TPS6128xD 采用 16 引脚芯片级封装 (CSP),最大限度地减少了外部组件的数量,因此拥有非常小巧的解决方案尺寸 (< 20mm²),支持使用小型电感器和输入电容器。

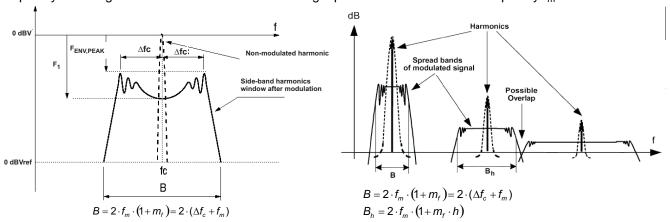

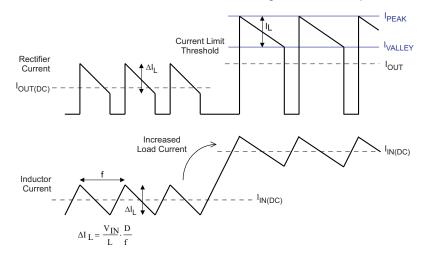

TPS6128xD 在 2.3MHz 的同步升压模式下运行,在轻负载电流情况下会进入省电模式运行 (PFM),以便在整个负载电流范围内保持高效率。

# 6 Device Comparison Table

| PART NUMBER |                                                                            | DEVICE<br>SPECIFIC FEATURES                        |

|-------------|----------------------------------------------------------------------------|----------------------------------------------------|

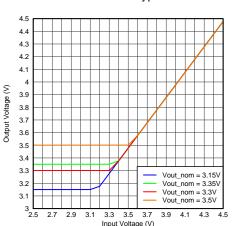

|             | 22 2                                                                       | DC/DC boost / bypass threshold = 3.15 V (VSEL = L) |

| TPS61280D   | I <sup>2</sup> C Control Interface User Prog. E <sup>2</sup> PROM Settings | DC/DC boost / bypass threshold = 3.35 V (VSEL = H) |

|             |                                                                            | Valley inductor current limit = 3 A                |

|             | Simple Logic Control Interface                                             | DC/DC boost / bypass threshold = 3.15 V (VSEL = L) |

| TPS61281D   |                                                                            | DC/DC boost / bypass threshold = 3.35 V (VSEL = H) |

|             |                                                                            | Valley inductor current limit = 3 A                |

|             | Simple Logic Control Interface                                             | DC/DC boost / bypass threshold = 3.3 V (VSEL = L)  |

| TPS61282D   |                                                                            | DC/DC boost / bypass threshold = 3.5 V (VSEL = H)  |

|             |                                                                            | Valley inductor current limit = 4 A                |

# 7 Pin Configuration and Functions

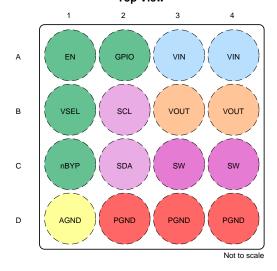

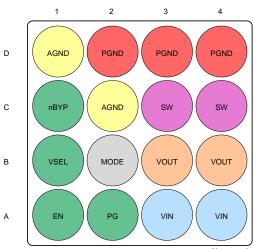

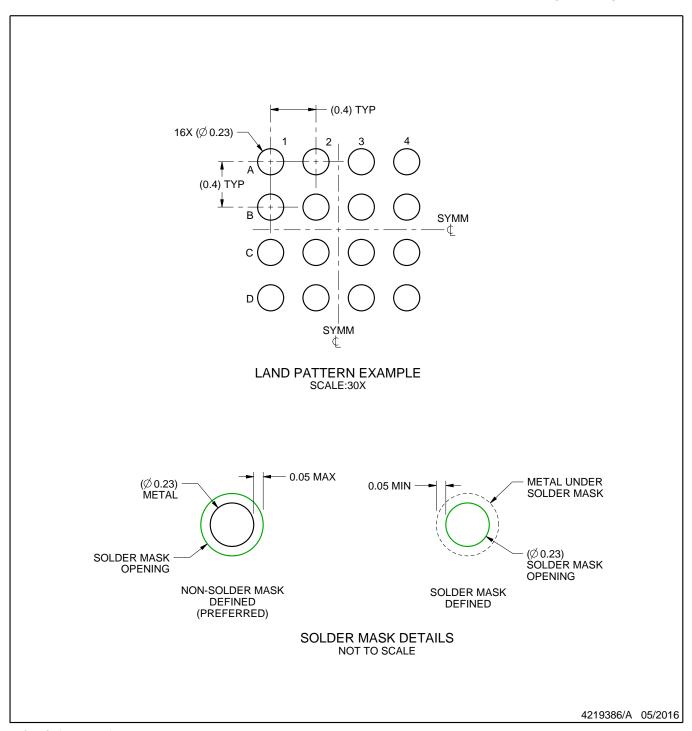

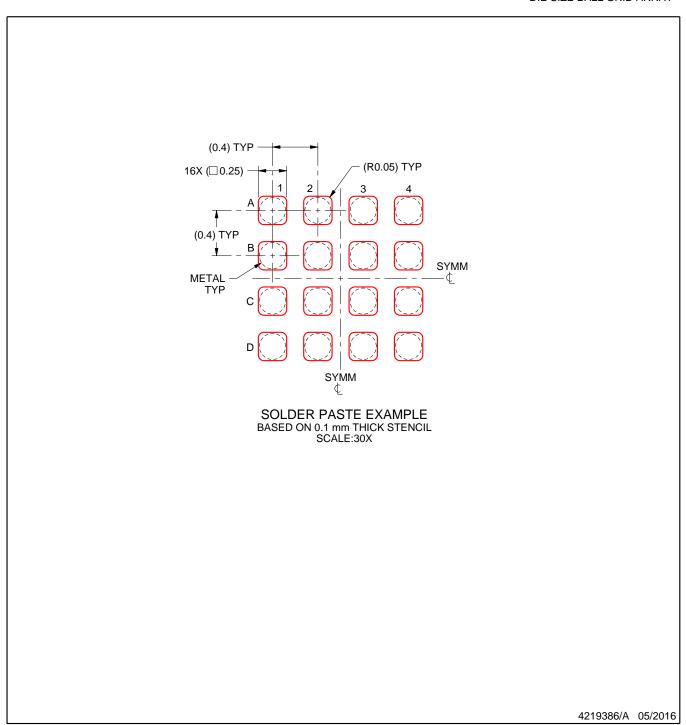

# TPS61280D YFF Package 16-Bump DSBGA Top View

#### TPS61280D YFF Package 16-Bump DSBGA Bottom View

#### Not to scale

# Pin Functions, TPS61280D

| F               | PIN    | 1/0 | PERCENTION                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-----------------|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME            | NO.    | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VIN             | A3, A4 | I   | Power supply input.                                                                                                                                                                                                                                                                                                                                                                                                            |

| VOUT            | B3, B4 | 0   | Boost converter output.                                                                                                                                                                                                                                                                                                                                                                                                        |

|                 |        |     | This is the enable pin of the device. On the rising edge of the enable pin, all the registers are reset with their default values. This input must not be left floating and must be terminated.                                                                                                                                                                                                                                |

| EN              | A1     | ı   | EN = Low: The device is forced into shutdown mode and the I2C control interface is disabled. Depending on the logic level applied to the nBYP input, the converter can either be forced in pass-through mode or it's output can be regulated to a minimum level so as to limit the input-to-output voltage difference to less than 3.6V (typ). The current consumption is reduced to a few μA. For more details, refer to 表 2. |

|                 |        |     | EN = High: The device is operating normally featuring automatic dc/dc boost, pass-through mode transition. For more details, refer to 表 2.                                                                                                                                                                                                                                                                                     |

|                 |        |     | This pin can either be configured as a input (mode selection) or as dual role input/open-drain output RST/FAULT) pin. Per default, the pin is configured as RST/FAULT input/output. The input must not be left floating and must be terminated.                                                                                                                                                                                |

|                 |        |     | Manual Reset Input: Drive RST/FAULT low to initiate a reset of the converter's output. nRST/nFAULT controls a falling edge-triggered sequence consisting of a discharge phase of the capacitance located at the converter's output followed by a start-up phase.                                                                                                                                                               |

| GPIO            | A2     | I/O | Fault Output (open-drain interrupt signal to host): Indicates that a fault has occurred (e.g. thermal shutdown, output voltage out of limits, current limit triggered, and so on). To signal such an event, the device generates a falling edgetriggered interrupt by driving a negative pulse onto the GPIO line and then releases the line to its inactive state.                                                            |

|                 |        |     | Mode selection input = Low: The device is operating in regulated frequency pulse width modulation mode (PWM) at high-load currents and in pulse frequency modulation mode (PFM) at light load currents.                                                                                                                                                                                                                        |

|                 |        |     | Mode selection input = High: Low-noise mode enabled, regulated frequency PWM operation forced.                                                                                                                                                                                                                                                                                                                                 |

| VSEL            | B1     | I   | VSEL signal is primarily used to set the output voltage dc/dc boost, pass-through threshold. This pin must not be left floating and must be terminated.                                                                                                                                                                                                                                                                        |

| nBYP            | C1     | I   | A logic low level on the BYP input forces the device in pass-through mode. This pin must not be left floating and must be terminated.                                                                                                                                                                                                                                                                                          |

| SCL             | B2     | ı   | Serial interface clock line. This pin must not be left floating and must be terminated.                                                                                                                                                                                                                                                                                                                                        |

| SDA             | C2     | I/O | Serial interface address/data line. This pin must not be left floating and must be terminated.                                                                                                                                                                                                                                                                                                                                 |

| SW              | C3, C4 | I/O | Inductor connection. Drain of the internal power MOSFET. Connect to the switched side of the inductor.                                                                                                                                                                                                                                                                                                                         |

| PGND D2, D3, D4 |        |     | Power ground pin.                                                                                                                                                                                                                                                                                                                                                                                                              |

| AGND            | D1     |     | Analog ground pin. This is the signal ground reference for the IC.                                                                                                                                                                                                                                                                                                                                                             |

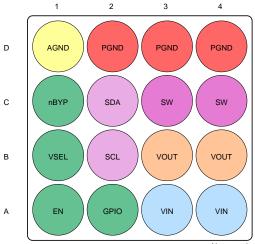

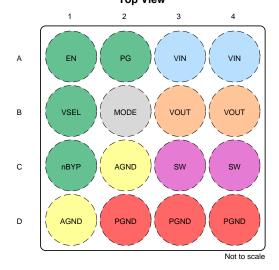

#### TPS6128xD YFF Package 16-Bump DSBGA Top View

#### TPS6128xD YFF Package 16-Bump DSBGA Bottom View

Not to scale

### Pin Functions, TPS6128xD

|                     | PIN        |          | ·                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

|---------------------|------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME NO. VIN A3, A4 |            | I/O      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| VIN                 | A3, A4     | - 1      | Power supply input.                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| VOUT                | B3, B4     | 0        | Boost converter output.                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|                     |            |          | This is the enable pin of the device. On the rising edge of the enable pin, all the registers are reset with their default values. This input must not be left floating and must be terminated.                                                                                                                                                                                             |  |  |  |  |

| EN                  | A1         | 1        | EN = Low: The device is forced into shutdown mode. Depending on the logic level applied to the nBYP input, the converter can either be forced in pass-through mode or it's output can be regulated to a minimum level so as to limit the input-to-output voltage difference to less than 3.6V (typ). The current consumption is reduced to a few μA. For more details, refer to 表 2.        |  |  |  |  |

|                     |            |          | EN = High: The device is operating normally featuring automatic dc/dc boost, pass-through mode transition. For more details, refer to 表 2.                                                                                                                                                                                                                                                  |  |  |  |  |

| PG A2               |            | 0        | Power-Good Output (open-drain output to host): A logic high on the PG output indicates that the converter's output voltage is within its regulation limits. A logic low indicates a fault has occurred (e.g. thermal shutdown, output volta out of limits, current limit triggered, and so on). The PG signal is de-asserted automatically once the IC resumes proper operation.            |  |  |  |  |

| VSEL B1             |            | I        | VSEL signal is primarily used to set the output voltage dc/dc boost, pass-through threshold. This pin must not be left floating and must be terminated.                                                                                                                                                                                                                                     |  |  |  |  |

| nBYP C1             |            | I        | A logic low level on the BYP input forces the device in pass-through mode. For more details, refer to 表 2. This pin must not be left floating and must be terminated.                                                                                                                                                                                                                       |  |  |  |  |

|                     |            |          | This is the mode selection pin of the device. This pin must not be left floating, must be terminated and can be connected to AGND. During start-up this pin must be held low. Once the output voltage settled and PG pin indicates that the converter's output voltage is within its regulation limits the device can be forced in PWM mode operation by applying a high level on this pin. |  |  |  |  |

| MODE                | B2         | <b> </b> | MODE = Low: The device is operating in regulated frequency pulse width modulation mode (PWM) at high-load currents and in pulse frequency modulation mode (PFM) at light load currents. This pin must be held low during device start-up.                                                                                                                                                   |  |  |  |  |

|                     |            |          | MODE = High: Low-noise mode enabled, regulated frequency PWM operation forced.                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| SW C3, C4 I/O       |            | I/O      | Inductor connection. Drain of the internal power MOSFET. Connect to the switched side of the inductor.                                                                                                                                                                                                                                                                                      |  |  |  |  |

| PGND                | D2, D3, D4 |          | Power ground pin.                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| AGND                | C2, D1     |          | Analog ground pin. This is the signal ground reference for the IC.                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

# 8 Specifications

### 8.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                   |                                                                                                                                        |                             | MIN  | MAX | UNIT |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------|-----|------|

|                   | Voltage at VOUT <sup>(2)</sup>                                                                                                         | DC                          | -0.3 | 4.7 | V    |

|                   | Voltage at VIN <sup>(2)</sup> , EN <sup>(2)</sup> , VSEL <sup>(2)</sup> , BYP <sup>(2)</sup> , PG <sup>(2)</sup> , GPIO <sup>(2)</sup> | DC                          | -0.3 | 5.2 | V    |

| Innut valtage     | Voltage at SCL <sup>(2)</sup> , SDA <sup>(2)</sup> MODE <sup>(2)</sup>                                                                 | DC                          | -0.3 | 3.6 | V    |

| input voitage     |                                                                                                                                        | DC                          | -0.3 | 4.7 | V    |

|                   | Voltage at SW <sup>(2)</sup>                                                                                                           | Transient: 2 ns, 2.3<br>MHz | -0.3 | 5.5 | V    |

|                   | Differential voltage between VIN and VOUT                                                                                              | -0.3                        | 4    | V   |      |

| Innut ourrent     | Continuous average current into SW (3)                                                                                                 |                             | 1.8  | Α   |      |

| Temperature range | Peak current into SW <sup>(4)</sup>                                                                                                    |                             | 5.5  | Α   |      |

| Power dissipation |                                                                                                                                        | Internally limited          |      |     |      |

| T                 | Operating temperature range, T <sub>A</sub> <sup>(5)</sup>                                                                             |                             | -40  | 85  | °C   |

| remperature range | Operating virtual junction, T <sub>J</sub>                                                                                             | -40                         | 150  | °C  |      |

| T <sub>stg</sub>  | Storage temperature range                                                                                                              |                             | -65  | 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods my affect device reliability.

2) All voltages are with respect to network ground terminal.

# 8.2 ESD Ratings

|                  |  |                                                                               | VALUE | UNIT |

|------------------|--|-------------------------------------------------------------------------------|-------|------|

|                  |  | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins <sup>(1)</sup>   | ±2000 | V    |

| V <sub>ESD</sub> |  | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2) | ±1000 | V    |

|                  |  | Machine Model - (MM)                                                          | ±200  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

### 8.3 Recommended Operating Conditions

|                                                               |                                                                                      | MIN  | NOM | MAX  | UNIT     |

|---------------------------------------------------------------|--------------------------------------------------------------------------------------|------|-----|------|----------|

| V <sub>I</sub> L C <sub>O</sub> I <sub>L</sub> T <sub>A</sub> | Input voltage range                                                                  | 2.30 |     | 4.85 | <b>V</b> |

| VI                                                            | Input voltage range for in-situ customization by E <sup>2</sup> PROM write operation | 3.4  | 3.5 | 3.6  | <b>V</b> |

| L                                                             | Inductance                                                                           | 200  | 470 | 800  | nΗ       |

| Co                                                            | Output capacitance                                                                   | 9    | 13  | 100  | μF       |

| IL                                                            | Maximum load current during start-up                                                 | 250  |     |      | mA       |

| T <sub>A</sub>                                                | Ambient temperature                                                                  | -40  |     | 85   | ů        |

| $T_{J}$                                                       | Operating junction temperature                                                       | -40  |     | 125  | ô        |

<sup>3)</sup> Limit the junction temperature to 105°C for continuous operation at maximum output power.

<sup>(4)</sup> Limit the junction temperature to 105°C for 15% duty cycle operation.

<sup>(5)</sup> In applications where high power dissipation and/or poor package thermal resistance is present, the maximum ambient temperature may have to be derated. Maximum ambient temperature (T<sub>A(max)</sub>) is dependent on the maximum operating junction temperature (T<sub>J(max)</sub>), the maximum power dissipation of the device in the application (P<sub>D(max)</sub>), and the junction-to-ambient thermal resistance of the part/package in the application (θ<sub>JA</sub>), as given by the following equation: T<sub>A(max)</sub> = T<sub>J(max)</sub> - (θ<sub>JA</sub> X P<sub>D(max)</sub>). To achieve optimum performance, it is recommended to operate the device with a maximum junction temperature of 105°C.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 8.4 Thermal Information

|                    |                                              | TPS6128xD   |      |

|--------------------|----------------------------------------------|-------------|------|

|                    | THERMAL METRIC <sup>(1)</sup>                | YFF (DSBGA) | UNIT |

|                    |                                              | 16 PINS     |      |

| $R_{\theta JA}$    | Junction-to-ambient thermal resistance       | 78          | °C/W |

| $R_{\theta JCtop}$ | Junction-to-case (top) thermal resistance    | 0.6         | °C/W |

| $R_{\theta JB}$    | Junction-to-board thermal resistance         | 13          | °C/W |

| ΨЈТ                | Junction-to-top characterization parameter   | 2.4         | °C/W |

| ΨЈВ                | Junction-to-board characterization parameter | 13          | °C/W |

| $R_{\theta JCbot}$ | Junction-to-case (bottom) thermal resistance | n/a         | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

### 8.5 Electrical Characteristics

Minimum and maximum values are at  $V_{IN} = 2.3 \text{ V}$  to 4.85 V,  $V_{OUT} = 3.4 \text{ V}$  (or  $V_{IN}$ , whichever is higher), EN = 1.8 V, VSEL = 1.8 V, nBYP = 1.8 V,  $-40^{\circ}\text{C} \le \text{T}_{J} \le 125^{\circ}\text{C}$ ; Circuit of Parameter Measurement Information section (unless otherwise noted). Typical values are at  $V_{IN} = 3.2 \text{ V}$ ,  $V_{OUT} = 3.4 \text{ V}$ , EN = 1.8 V,  $T_{J} = 25^{\circ}\text{C}$  (unless otherwise noted).

|                      | PARAMETER                                         |           | TEST CONDITIONS                                                                                                                                                                                    |                               | MIN TYP                 | MAX  | UNIT |

|----------------------|---------------------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------------|------|------|

| SUPPLY               | CURRENT                                           |           |                                                                                                                                                                                                    |                               |                         |      |      |

|                      |                                                   |           | DC/DC boost mode. Device not switching I <sub>OUT</sub> = 0 mA, V <sub>IN</sub> = 3.2 V, V <sub>OUT</sub> = 3.4 V                                                                                  |                               | 47.4                    | 65.6 | μΑ   |

| lα                   | Operating quiescent current into V <sub>IN</sub>  | TPS6128xD | Pass-through mode (auto)<br>EN = 1.8 V, BYP = 1.8 V, V <sub>IN</sub> = 3.6 V                                                                                                                       |                               | 27.4                    | 42.6 | μΑ   |

| 'Q                   |                                                   | 1F30120xD | Pass-through mode (forced)<br>EN = 1.8 V, BYP = AGND, V <sub>OUT</sub> = 3.6 V                                                                                                                     | -40°C ≤ T <sub>J</sub> ≤ 85°C | 15.4                    | 25.6 | μΑ   |

|                      | Operating quiescent current into V <sub>OUT</sub> |           | DC/DC boost mode. Device not switching $I_{OUT} = 0$ mA, $V_{IN} = 3.2$ V, $V_{OUT} = 3.4$ V                                                                                                       |                               | 8.9                     | 19.6 | μΑ   |

|                      | Chuthaum aurrant                                  | TD06420vD | $EN = 0 \text{ V}, \overline{BYP} = 0 \text{ V}, V_{IN} = 3.6 \text{ V}$                                                                                                                           |                               | 3                       | 6.6  | μΑ   |

| I <sub>SD</sub>      | Shutdown current                                  | TPS6128xD | EN = 0 V, <del>BYP</del> = 1.8 V, V <sub>IN</sub> = 3.6 V                                                                                                                                          |                               | 8.9                     | 20.6 | μΑ   |

|                      | 11-4                                              | TD00400D  | Falling                                                                                                                                                                                            |                               | 2                       | 2.1  | V    |

| V <sub>UVLO</sub>    | Under-voltage lockout threshold                   | TPS6128xD | Hysteresis                                                                                                                                                                                         |                               | 0.1                     |      | V    |

| EN, VSE              | L, nBYP, MODE, SDA, SCL, GPIO,                    | PG        |                                                                                                                                                                                                    |                               |                         |      |      |

| V <sub>IL</sub>      | Low-level input voltage                           | TD00400 D |                                                                                                                                                                                                    |                               |                         | 0.4  | V    |

| V <sub>IH</sub>      | High-level input voltage                          | TPS6128xD |                                                                                                                                                                                                    |                               | 1.2                     |      | V    |

| V <sub>OL</sub>      | Low-level output voltage (SDA)                    | TD004000D | I <sub>OL</sub> = 8 mA                                                                                                                                                                             |                               |                         | 0.3  | V    |

|                      | Low-level output voltage (GPIO)                   | TPS61280D | I <sub>OL</sub> = 8 mA, GPIOCFG = 0                                                                                                                                                                |                               |                         | 0.3  | V    |

|                      | Low-level output voltage (PG)                     | TPS6128xD | I <sub>OL</sub> = 8 mA                                                                                                                                                                             |                               |                         | 0.3  | V    |

| R <sub>PD</sub>      | EN, VSEL, BYP, pull-down resistance               | TPS6128xD | Input ≤ 0.4 V                                                                                                                                                                                      |                               | 300                     |      | kΩ   |

| 0                    | EN, VSEL, BYP, MODE, PG input capacitance         | TPS6128xD | Input connected to ACAID or V                                                                                                                                                                      |                               | 9                       |      | pF   |

| C <sub>IN</sub>      | SDA, SCL, GPIO input capacitance                  | TPS61280D | Input connected to AGND or V <sub>IN</sub>                                                                                                                                                         |                               | 9                       |      | pF   |

| .,                   | Dower good throubold                              | TD06400vD | Rising V <sub>OUT</sub>                                                                                                                                                                            |                               | 0.95 x V <sub>OUT</sub> |      |      |

| $V_{THPG}$           | Power good threshold                              | TPS6128xD | Falling V <sub>OUT</sub>                                                                                                                                                                           |                               | 0.9 x V <sub>OUT</sub>  |      |      |

| I <sub>lkg</sub>     | land lands a summer                               | TD00400D  | Input connected to AGND                                                                                                                                                                            | -40°C ≤ T <sub>J</sub> ≤      | 0                       |      | μA   |

|                      | Input leakage current                             | TPS6128xD | Input connected V <sub>IN</sub>                                                                                                                                                                    | 85°C                          |                         | 0.5  | μA   |

| OUTPUT               | T                                                 |           |                                                                                                                                                                                                    |                               |                         |      | -    |

| V <sub>OUT(TH)</sub> | Threshold DC voltage accuracy                     | TPS6128xD | No load. Open loop                                                                                                                                                                                 |                               | -1.5%                   | 1.5% |      |

| V                    | Regulated DC voltage accuracy                     | TPS6128xD | $ \begin{array}{l} 2.65 \text{ V} \leq \text{V}_{\text{IN}} \leq \text{V}_{\text{OUT\_TH}} \text{ - } 150 \text{ mV} \\ \text{I}_{\text{OUT}} = 0 \text{mA} \\ \text{PWM operation}. \end{array} $ |                               | -2%                     | 2%   |      |

| V <sub>OUT</sub>     | Regulated DC voltage accuracy                     | 1F30120XD | 2.65 V $\leq$ V <sub>IN</sub> $\leq$ V <sub>OUT_TH</sub> - 150 mV I <sub>OUT</sub> = 0 mA PFM/PWM operation                                                                                        |                               | -2%                     | 4%   |      |

# **Electrical Characteristics (continued)**

Minimum and maximum values are at  $V_{IN} = 2.3 \text{ V}$  to 4.85 V,  $V_{OUT} = 3.4 \text{ V}$  (or  $V_{IN}$ , whichever is higher), EN = 1.8 V, VSEL = 1.8 V, nBYP = 1.8 V,  $-40 ^{\circ}\text{C} \leq \text{T}_{J} \leq 125 ^{\circ}\text{C}$ ; Circuit of Parameter Measurement Information section (unless otherwise noted). Typical values are at  $V_{IN} = 3.2 \text{ V}$ ,  $V_{OUT} = 3.4 \text{ V}$ , EN = 1.8 V,  $T_{J} = 25 ^{\circ}\text{C}$  (unless otherwise noted).

|                     | PARAMETER                                            |                        | TEST CONDITIONS                                                                                                                                                                                                 | MIN  | TYP  | MAX  | UNIT |

|---------------------|------------------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| $\Delta V_{OUT}$    | Power-save mode output ripple voltage                | TPS6128xD              | PFM operation, I <sub>OUT</sub> = 1 mA                                                                                                                                                                          |      | 30   |      | mVpk |

|                     | PWM mode output ripple voltage                       |                        | PWM operation, I <sub>OUT</sub> = 500 mA                                                                                                                                                                        |      | 15   |      | mVpk |

| POWER               | SWITCH                                               |                        |                                                                                                                                                                                                                 |      |      |      |      |

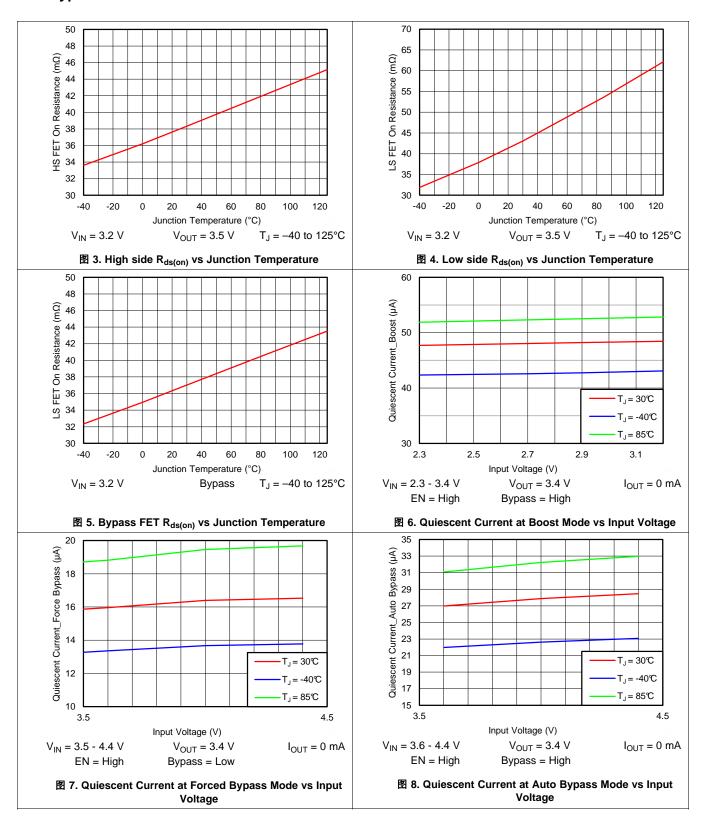

|                     | Low-side switch MOSFET on resistance                 |                        | V <sub>IN</sub> = 3.2 V, V <sub>OUT</sub> = 3.5 V                                                                                                                                                               |      | 45   | 80   | mΩ   |

| r <sub>DS(on)</sub> | High-side rectifier MOSFET on resistance             | TPS6128xD              | V <sub>IN</sub> = 3.2 V, V <sub>OUT</sub> = 3.5 V                                                                                                                                                               |      | 40   | 70   | mΩ   |

|                     | High-side pass-through MOSFET on resistance          |                        | V <sub>IN</sub> = 3.2 V                                                                                                                                                                                         |      | 35   | 60   | mΩ   |

|                     | Reverse leakage current into SW                      |                        | $\begin{aligned} &EN = AGND,  V_{IN} = V_{OUT} = SW = 3.5 \; V \\ &-40^{\circ}C \leq T_J \leq 85^{\circ}C \end{aligned}$                                                                                        |      | 0.1  | 2    | μΑ   |

| l <sub>lkg</sub>    | Reverse leakage current into VOUT                    | TPS6128xD              | $\begin{array}{l} EN = \overline{BYP} = V_{IN}, \ V_{IN} = 2.9 \ V, \ V_{OUT} = 4.4 \ V, \ V_{SW} = 0 \ V \\ \text{device not switching} \\ -40^{\circ}\text{C} \leq T_{J} \leq 85^{\circ}\text{C} \end{array}$ |      | 0.11 | 2    | μΑ   |

| I <sub>SINK</sub>   | VOUT sink capability                                 | TPS6128xD              | EN = AGND, $V_{OUT} \le 3.6 \text{ V}$ , $I_{OUT} = -10 \text{ mA}$                                                                                                                                             |      |      | 0.3  | V    |

|                     | Valley inductor current limit                        | TPS61280D<br>TPS61281D | $V_{\rm IN}$ = 2.9 V, $V_{\rm OUT}$ = 3.5 V, $-40^{\circ}{\rm C}$ $\leq$ T <sub>J</sub> $\leq$ 125 $^{\circ}{\rm C}$ , auto PFM/PWM                                                                             | 2475 | 3000 | 3525 | mA   |

|                     | Valley inductor current limit                        | TPS61282D              | $V_{\rm IN}$ = 2.9 V, $V_{\rm OUT}$ = 3.5 V, $-40^{\circ}{\rm C}$ $\leq$ T <sub>J</sub> $\leq$ 125 $^{\circ}{\rm C}$ , auto PFM/PWM                                                                             | 3300 | 4000 | 4700 | mA   |

|                     | Dear the second second limit                         | TD00400:-D             | $EN = \overline{BYP} = GND, V_{IN} = 3.2 \text{ V}$                                                                                                                                                             |      | 5000 |      | mA   |

|                     | Pass through mode current limit                      | TPS6128xD              | $EN = V_{IN}$ , $\overline{BYP} = don't care , V_{IN} = 3.2 \text{ V}$                                                                                                                                          | 5600 | 7400 | 9100 | mA   |

|                     | Pre-charge mode current limit (linear mode, phase 1) | TPS6128xD              | $V_{IN}$ - $V_{OLIT}$ >= 300 mV                                                                                                                                                                                 | 500  | 650  |      | mA   |

|                     | Pre-charge mode current limit (linear mode, phase 2) | 1P30120XD              | V <sub>IN</sub> - V <sub>OUT</sub> >= 300 mV                                                                                                                                                                    |      | 2000 |      | mA   |

| OSCILL              | ATOR                                                 |                        |                                                                                                                                                                                                                 |      |      |      |      |

| fosc                | Oscillator frequency                                 | TPS6128xD              | V <sub>IN</sub> = 2.7 V, V <sub>OUT</sub> = 3.5 V                                                                                                                                                               |      | 2.3  |      | MHz  |

| THERM               | AL SHUTDOWN, HOT DIE DETECTO                         | R                      |                                                                                                                                                                                                                 |      |      | •    |      |

|                     | Thermal shutdown <sup>(1)</sup>                      | TPS6128xD              |                                                                                                                                                                                                                 | 140  | 160  |      | °C   |

|                     | Hot die detector accuracy <sup>(1)</sup>             | TPS61280D              |                                                                                                                                                                                                                 | -10  | 105  | 10   | °C   |

| TIMING              |                                                      |                        |                                                                                                                                                                                                                 |      |      |      |      |

|                     | Start-up time                                        | TPS6128xD              | $V_{\text{IN}}$ = 3.2 V, VOUT_TH = 01011 (3.4 V), $R_{\text{LOAD}}$ = 50 $\Omega$ Time from active $V_{\text{IN}}$ to $V_{\text{OUT}}$ settled                                                                  |      | 500  |      | μs   |

|                     | GPIO rise time <sup>(1)</sup>                        | TPS61280D              |                                                                                                                                                                                                                 |      |      | 200  | ns   |

<sup>(1)</sup> Specified by characterization. Not tested in production.

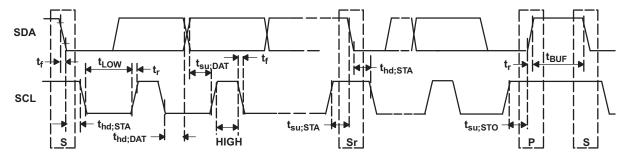

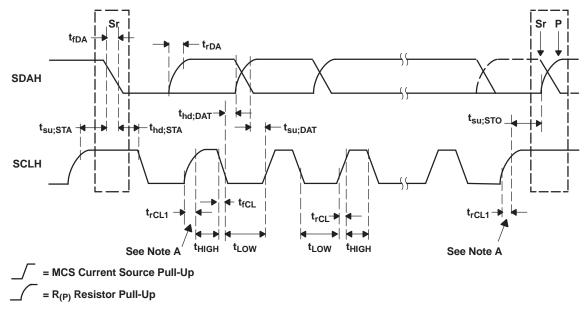

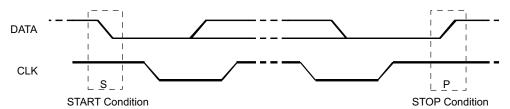

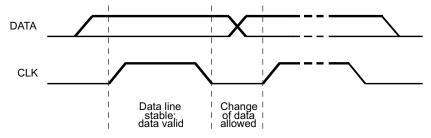

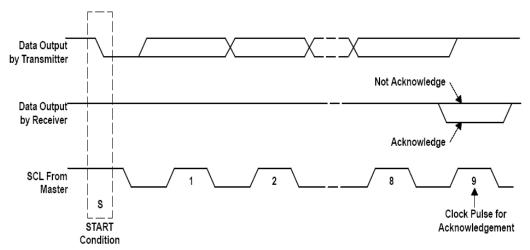

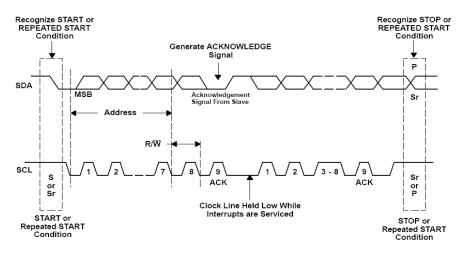

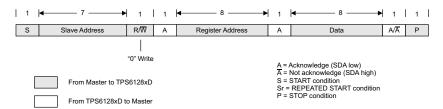

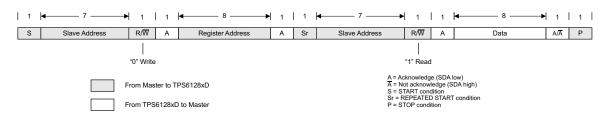

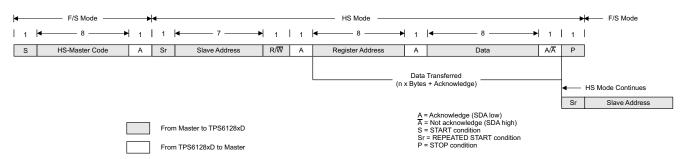

# 8.6 I<sup>2</sup>C Interface Timing Characteristics<sup>(1)</sup>

|                                    | PARAMETER                                        | TEST CONDITIONS                                               | MIN                     | MAX  | UNIT |

|------------------------------------|--------------------------------------------------|---------------------------------------------------------------|-------------------------|------|------|

|                                    |                                                  | Standard mode                                                 |                         | 100  | kHz  |

|                                    |                                                  | Fast mode                                                     |                         | 400  | kHz  |

| f <sub>(SCL)</sub>                 |                                                  | Fast mode plus                                                |                         | 1    | MHz  |

|                                    | SCL Clock Frequency                              | High-speed mode (write operation), $C_B - 100 \text{ pF}$ max |                         | 3.4  | MHz  |

|                                    |                                                  | High-speed mode (read operation), $C_B - 100 \ pF \ max$      |                         | 3.4  | MHz  |

|                                    |                                                  | High-speed mode (write operation), $C_{\rm B}$ – 400 pF max   |                         | 1.7  | MHz  |

|                                    |                                                  | High-speed mode (read operation), $C_{\text{B}}$ – 400 pF max |                         | 1.7  | MHz  |

|                                    | D                                                | Standard mode                                                 | 4.7                     |      | μS   |

| t <sub>BUF</sub>                   | Bus Free Time Between a STOP and START Condition | Fast mode                                                     | 1.3                     |      | μS   |

|                                    |                                                  | Fast mode plus                                                | 0.5                     |      | μS   |

|                                    |                                                  | Standard mode                                                 | 4                       |      | μS   |

| t <sub>HD</sub> , t <sub>STA</sub> | Hold Time (Repeated) START                       | Fast mode                                                     | 600                     |      | ns   |

| THD, ISTA                          | Condition                                        | Fast mode plus                                                | 260                     |      | ns   |

|                                    |                                                  | High-speed mode                                               | 160                     |      | ns   |

|                                    |                                                  | Standard mode                                                 | 4.7                     |      | μS   |

|                                    |                                                  | Fast mode                                                     | 1.3                     |      | μS   |

| $t_{LOW}$                          | LOW Period of the SCL Clock                      | Fast mode plus                                                | 0.5                     |      | μS   |

|                                    |                                                  | High-speed mode, C <sub>B</sub> – 100 pF max                  | 160                     |      | ns   |

|                                    |                                                  | High-speed mode, C <sub>B</sub> – 400 pF max                  | 320                     |      | ns   |

|                                    |                                                  | Standard mode                                                 | 4                       |      | μS   |

|                                    |                                                  | Fast mode                                                     | 600                     |      | ns   |

| t <sub>HIGH</sub>                  | HIGH Period of the SCL Clock                     | Fast mode plus                                                | 260                     |      | ns   |

|                                    |                                                  | High-speed mode, C <sub>B</sub> – 100 pF max                  | 60                      |      | ns   |

|                                    |                                                  | High-speed mode, C <sub>B</sub> – 400 pF max                  | 120                     |      | ns   |

|                                    |                                                  | Standard mode                                                 | 4.7                     |      | μS   |

| t <sub>SU</sub> , t <sub>STA</sub> | Setup Time for a Repeated START                  | Fast mode                                                     | 600                     |      | ns   |

| 'SU, 'STA                          | Condition                                        | Fast mode plus                                                | 260                     |      | ns   |

|                                    |                                                  | High-speed mode                                               | 160                     |      | ns   |

|                                    |                                                  | Standard mode                                                 | 250                     |      | ns   |

| t <sub>SU</sub> , t <sub>DAT</sub> | Data Setup Time                                  | Fast mode                                                     | 100                     |      | ns   |

| 'SU, 'DAI                          | Pata cotap rimo                                  | Fast mode plus                                                | 50                      |      | ns   |

|                                    |                                                  | High-speed mode                                               | 10                      |      | ns   |

|                                    |                                                  | Standard mode                                                 | 0                       | 3.45 | μS   |

|                                    |                                                  | Fast mode                                                     | 0                       | 0.9  | μS   |

| $t_{\text{HD}},t_{\text{DAT}}$     | Data Hold Time                                   | Fast mode plus                                                | 0                       |      | μS   |

|                                    |                                                  | High-speed mode, C <sub>B</sub> – 100 pF max                  | 0                       | 70   | ns   |

|                                    |                                                  | High-speed mode, C <sub>B</sub> – 400 pF max                  | 0                       | 150  | ns   |

|                                    |                                                  | Standard mode                                                 |                         | 1000 | ns   |

|                                    |                                                  | Fast mode                                                     | 20 + 0.1 C <sub>B</sub> | 300  | ns   |

| t <sub>RCL</sub>                   | Rise Time of SCL Signal                          | Fast mode plus                                                |                         | 120  | ns   |

|                                    |                                                  | High-speed mode, C <sub>B</sub> – 100 pF max                  | 10                      | 40   | ns   |

|                                    |                                                  | High-speed mode, C <sub>B</sub> – 400 pF max                  | 20                      | 80   | ns   |

|                                    |                                                  | Standard mode                                                 | 20 + 0.1 C <sub>B</sub> | 1000 | ns   |

|                                    | Rise Time of SCL Signal After a Repeated         | Fast mode                                                     | 20 + 0.1 C <sub>B</sub> | 300  | ns   |

| t <sub>RCL1</sub>                  | START Condition and After an                     | Fast mode plus                                                |                         | 120  | ns   |