ZHCSDD5B - MARCH 2014 - REVISED JANUARY 2015

# TPA6166A2 3.5mm 插孔检测和耳机接口 IC

#### 特性 1

- 超低功耗、高性能 DirectPath™ G 类耳机放大器

- 中央接地输出免除了对隔直电容的需求

- 1% 点谐波失真+噪声 (THD+N) 时,每通道 30mW (32Ω/通道)

- -42dB 至 +6dB 音量控制

- -42dB 增益下的输出噪声为 2.0µV

- 91dB 电源抑制比 (PSRR)

- 接地环路抑制电路,用于减少串扰

- 全差分麦克风前置放大器,具有可变增益和 3.4µV 低噪声

- 集成了交流耦合电容

- 接地环路抑制电路,用于减少耳机与麦克风间的 串扰

- 两种麦克风偏置电压可供选择: 2.0V 和 2.6V

- 92dB 电源抑制比 (PSRR)

- 集成了可编程的麦克风偏置电阻

- 高级的附件插入、移除和型号检测功能

- 采用 10 位逐次逼近寄存器 (SAR) 模数转换器 • (ADC) 提供无源多按钮支持

- 实现了专有方案,可减少耳机接地返回路径上存 在有限电阻时音频播放信号所导致的错误

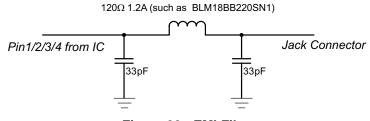

- 在(EVM 上的)插孔连接引脚上集成了 4 级 IEC 静电放电 (ESD) 保护

- 超低功耗芯片关断模式

- I<sup>2</sup>C 接口

- 短路保护功能

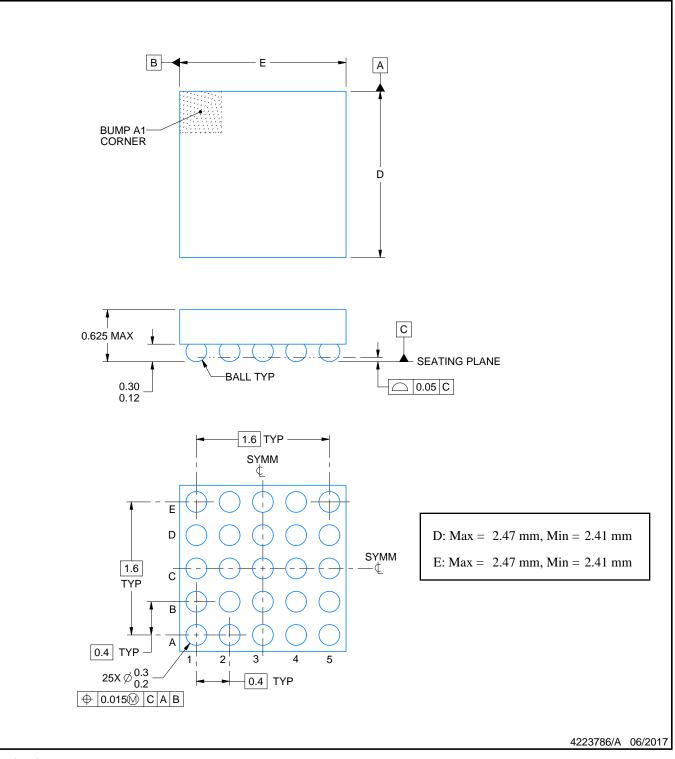

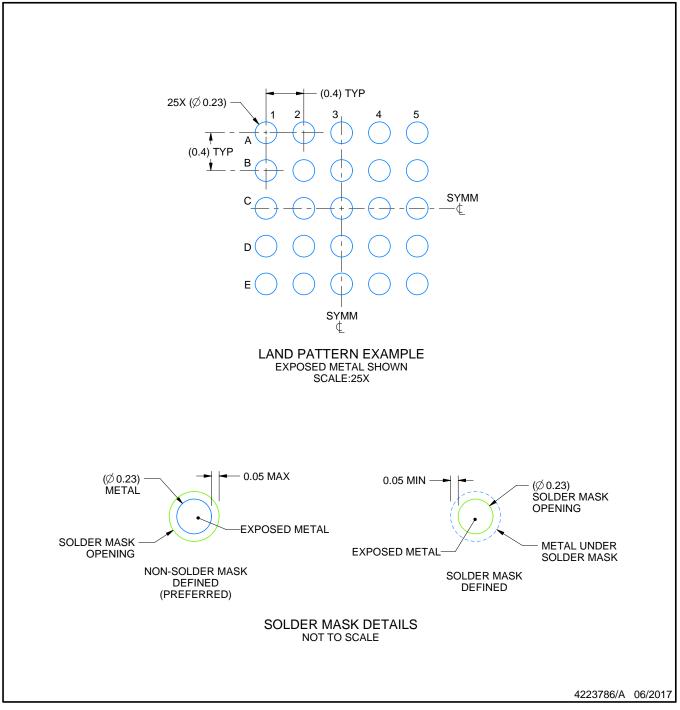

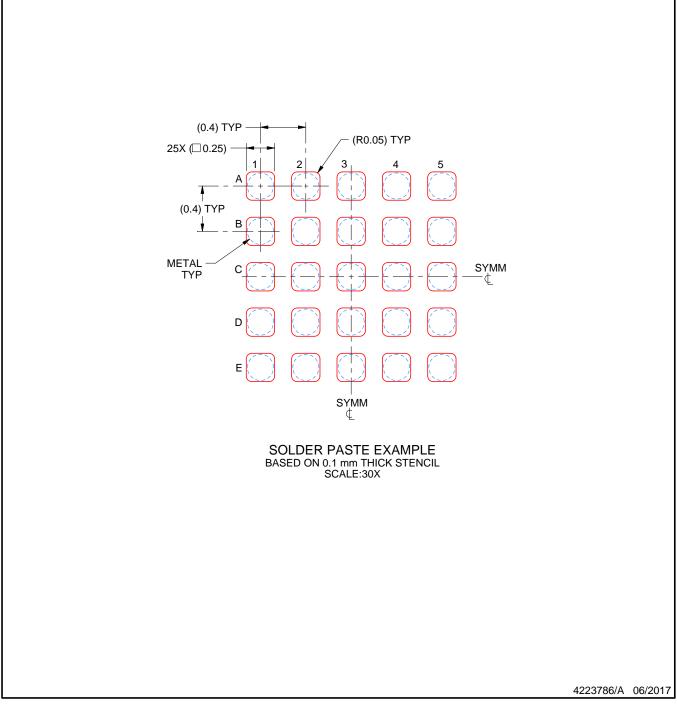

- 0.4mm 间距 25 焊球晶圆级芯片封装 (WCSP)

# 2 应用

- 智能手机和无线耳机 •

- 便携式平板电脑

- 笔记本电脑和扩展坞

# 3 说明

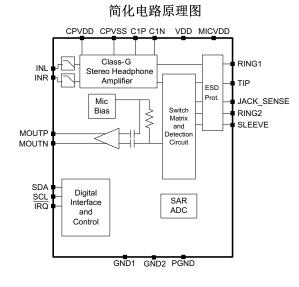

TPA6166A2这款单芯片耳机接口 IC 可轻松检测最终用 户插入到耳机插孔的设备型号,同时提供出色的音质。 此器件将高性能的低功耗 DirectPath 可变衰减 G 类立 体声耳机放大器、具有偏置电路的可变增益麦克风前置 放大器以及高级附件检测电路全部集成在一个微型 5mm × 5mm 引脚、0.4mm 间距 WCSP 封装上,因此 有助于减小最终产品的尺寸。

G 类耳机放大器可根据音频信号电平调整耳机放大器 的供电电压,从而以最大程度延长电池使用寿命。 凭 借 8µV 输出噪声(0dB 时) 和 91dB 的 PSRR,该耳 机放大器可提供出色的音频性能。 DirectPath 免除了 对隔直电容的需求。耳机前置放大器具有两种可编程 增益(12dB和 24dB),以及 3.4µV 输入参考噪声。

耳机偏置电压有两种可编程设置: 2V 和 2.6V。偏置输 出最高可驱动 1.2mA 的电流,并且兼具 2µV 的低输出 噪声和 92dB PSRR,可为无线耳机提供出色的电源噪 声抑制效果。

高级附件检测算法可自动对 6 种支持的附件进行检 测,并且能够使能或禁止内部元件。

#### 器件信息(1)

| 器件型号      | 封装        | 封装尺寸(标称值)       |

|-----------|-----------|-----------------|

| TPA6166A2 | WSCP (25) | 2.50mm x 2.50mm |

|           |           |                 |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

# 目录

| 1 | 特性   |                                                         |

|---|------|---------------------------------------------------------|

| 2 | 应用   | 1                                                       |

| 3 | 说明   | 1                                                       |

| 4 | 修订   | 历史记录 2                                                  |

| 5 | Pin  | Configuration and Functions 3                           |

| 6 | Spe  | cifications 4                                           |

|   | 6.1  | Absolute Maximum Ratings 4                              |

|   | 6.2  | ESD Ratings 4                                           |

|   | 6.3  | Recommended Operating Conditions 4                      |

|   | 6.4  | Thermal Information 4                                   |

|   | 6.5  | Electrical Characteristics 5                            |

|   | 6.6  | Electrical Characteristics, Audio Amplifiers            |

|   | 6.7  | Electrical Characteristics, Mic Preamplifier and Bias 7 |

|   | 6.8  | Timing Requirements 8                                   |

|   | 6.9  | Typical Characteristics 9                               |

| 7 | Deta | ailed Description 13                                    |

|   | 7.1  | Overview 13                                             |

|   | 7.2  | Functional Block Diagram 13                             |

|    | 7.3  | Feature Description         | 13 |

|----|------|-----------------------------|----|

|    | 7.4  | Device Functional Modes     |    |

|    | 7.5  | Register Maps               |    |

| 8  | App  | lication and Implementation |    |

|    | 8.1  | Application Information     |    |

|    | 8.2  | Typical Application         |    |

| 9  | Pow  | er Supply Recommendations   | 40 |

|    | 9.1  | Decoupling Capacitors       | 40 |

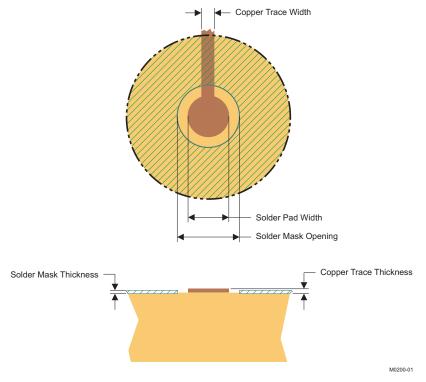

| 10 | Lay  | out                         | 41 |

|    | 10.1 |                             | 41 |

|    | 10.2 | Layout Example              |    |

| 11 |      | 和文档支持                       |    |

|    | 11.1 |                             |    |

|    | 11.2 | 商标                          | 43 |

|    | 11.3 | 静电放电警告                      | 43 |

|    | 11.4 | 术语表                         | 43 |

| 12 | 机械   | 封装和可订购信息                    | 43 |

|    |      |                             |    |

# 4 修订历史记录

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

### Changes from Revision A (June 2014) to Revision B

| • | 已添加引脚配置和功能部分, | ESD 额定值表, | 特性描述部分, | 器件功能模式, | 应用和实施部分, | 电源相关建议部分, |   |

|---|---------------|-----------|---------|---------|----------|-----------|---|

|   | 布局部分,器件和文档支持部 | 分以及机械、封   | 装和可订购信息 | 部分      |          |           | 1 |

#### Changes from Original (January 2014) to Revision A

| • | 已更改 至最新数据表格式 | 1 |

|---|--------------|---|

| • | 已添加 规范和应用信息  | 1 |

| • | 己更改 状态至量产数据  | 1 |

www.ti.com.cn

Page

Page

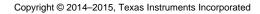

# 5 Pin Configuration and Functions

All NC pins should be left floating. Do not connect them to GND.

#### **Pin Functions**

| PIN           |        |            | DECODIDEION                                                                                                                                 |  |  |

|---------------|--------|------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME          | NO.    | I/O / TYPE | DESCRIPTION                                                                                                                                 |  |  |

| GND1          | A1     | Р          | Analog / digital ground 1                                                                                                                   |  |  |

| INR           | A2     | I          | Headphone right channel input                                                                                                               |  |  |

| INL           | A3     | I          | Headphone left channel input                                                                                                                |  |  |

| CPVDD         | A4     | I          | Headphone charge-pump positive supply (internally generated). Connect a $1\mbox{-}\mu\mbox{F}$ capacitor to ground.                         |  |  |

| JACK_SENSE    | A5     | I/O        | Connect to headset jack terminal 5 (for mechanical switch). If mechanical switch is not available, then this terminal can be kept floating. |  |  |

| NC (Floating) | B1     | 0          | Leave floating (no connection)                                                                                                              |  |  |

| GND2          | B2     | I          | Ground 2 - Connect to ground 1 on board.                                                                                                    |  |  |

| IRQ           | B3     | 0          | Active low interrupt output                                                                                                                 |  |  |

| MOUTN         | B4     | 0          | Microphone preamplifier negative output                                                                                                     |  |  |

| TIP           | B5     | 0          | Left headphone / line output. Connect to headset jack TIP (terminal 1).                                                                     |  |  |

| CPVSS         | C1     | I          | Headphone charge-pump negative supply (internally generated). Connect a 1-µF capacitor to ground.                                           |  |  |

| SCL           | C2     | I          | I <sup>2</sup> C clock line                                                                                                                 |  |  |

| GND           | C3     | I          | Connect to ground                                                                                                                           |  |  |

| MOUTP         | C4     | 0          | Microphone preamplifier positive output                                                                                                     |  |  |

| RING1         | C5     | 0          | Right headphone / line output. Connect to headset jack RING1 (terminal 2).                                                                  |  |  |

| C1N           | D1     | Р          | Charge pump flying capacitor positive terminal                                                                                              |  |  |

| SDA           | D2     | I/O        | I <sup>2</sup> C data line                                                                                                                  |  |  |

| PGND          | D3, E2 | Р          | Power ground                                                                                                                                |  |  |

| NC (Floating) | D4     | 0          | Leave floating (no connection)                                                                                                              |  |  |

| MICVDD        | D5     | Р          | Analog supply                                                                                                                               |  |  |

| C1P           | E1     | Р          | Charge pump flying capacitor negative terminal                                                                                              |  |  |

| VDD           | E3     | Р          | Analog / digital supply                                                                                                                     |  |  |

| RING2         | E4     | I/O        | Connect to headset jack RING2 (terminal 3)                                                                                                  |  |  |

| SLEEVE        | E5     | I/O        | Connect to headset jack SLEEVE (terminal 4)                                                                                                 |  |  |

# 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating temperature range,  $T_A = 25^{\circ}C$  (unless otherwise noted) <sup>(1)</sup>

|                                           |   | MIN                     | MAX | UNIT |

|-------------------------------------------|---|-------------------------|-----|------|

| Supply voltage, VDD                       |   | -0.3                    | 2   | V    |

| Microphone supply voltage, MICVDD         |   | -0.3                    | 3.9 | V    |

| Output continuous total power dissipation | S | See Thermal Information |     |      |

| Storage temperature, T <sub>stg</sub>     |   | -65                     | 85  | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|   |                    |                         |                                                                          | VALUE | UNIT |

|---|--------------------|-------------------------|--------------------------------------------------------------------------|-------|------|

|   |                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>        | ±2000 |      |

| ١ | V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22- $C101^{(2)}$ | ±500  | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

|                    |                          |                                                                                                              | MIN | MAX | UNIT |

|--------------------|--------------------------|--------------------------------------------------------------------------------------------------------------|-----|-----|------|

| VDD                | Supply voltage           |                                                                                                              | 1.7 | 1.9 | V    |

| MICVDD             | Microphone supply        | voltage                                                                                                      | 2.4 | 3.6 | V    |

| T <sub>A</sub>     | Operating temperate      | perating temperature                                                                                         |     | 85  | °C   |

|                    |                          | Line Driver Application, $R_L = 10 \text{ k}\Omega$ , $A_V \ge 0 \text{ dB}$ , specified by design           |     | 470 | pF   |

| C <sub>L,Max</sub> | Maximum load capacitance | Line Driver Application, R <sub>L</sub> = 10 kΩ, A <sub>V</sub> ≤ 0 dB, LO_EXT_STAB = 1, specified by design |     | 470 |      |

|                    |                          | Headphone Application, $R_L = 32 \Omega$ , specified by design                                               |     | 200 |      |

| TJ                 | Operating junction to    | emperature                                                                                                   | -25 | 150 | °C   |

## 6.4 Thermal Information

|                       |                                              | TPA6166A2  |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | YFF (WSCP) | UNIT |

|                       |                                              | 25 PINS    |      |

| $R_{	extsf{	heta}JA}$ | Junction-to-ambient thermal resistance       | 67         |      |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 18         |      |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 38         | °C/W |

| $\psi_{JT}$           | Junction-to-top characterization parameter   | 0.1        |      |

| $\psi_{JB}$           | Junction-to-board characterization parameter | 36         |      |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

## 6.5 Electrical Characteristics

$VDD = 00 \ 1.8 \ V, \ MICVDD = 3.0 \ V, \ A_V = 0 \ dB, \ C_{IN} = 0.47 \ \mu F, \ C_{FLY} = 1.0 \ \mu F, \ C_{CPVDD} = C_{CPVSS} = 1.0 \ \mu F, \ R_{HP} = 32 \ \Omega, \ outputs \ in phase, \ T_A = 25^{\circ}C \ (unless otherwise noted).$

| PARAMETER       |                                      | TEST CONDITIONS                                            |                                       | MIN | TYP   | MAX   | UNIT |

|-----------------|--------------------------------------|------------------------------------------------------------|---------------------------------------|-----|-------|-------|------|

| V <sub>IH</sub> | Input logic high                     | SDA, SCL                                                   |                                       | 1.4 |       |       |      |

| V <sub>IL</sub> | Input logic low                      | SDA, SCL                                                   |                                       |     |       | 0.4   | V    |

| V <sub>OL</sub> | Output logic low                     | ĪRQ                                                        | I <sub>OL</sub> = 3 mA pullup current |     | 0.    | 2×VDD |      |

| I <sub>IH</sub> | Logic high input<br>leakage current  | SDA, SCL                                                   |                                       |     |       | 1     |      |

| I <sub>IL</sub> | Logic low input<br>leakage current   | SDA, SCL                                                   |                                       |     |       | 1     | μΑ   |

| I <sub>ОН</sub> | Logic high output<br>leakage current | ĪRQ                                                        | V <sub>IRQ</sub> = 3.3 V              |     |       | 1     |      |

|                 |                                      |                                                            | I <sub>VDD</sub>                      |     | 2.38  |       | mA   |

|                 |                                      | Audio playback (both channels), no signal into 32 $\Omega$ | IMICVDD                               |     | 0.21  |       | mA   |

|                 |                                      |                                                            | P <sub>CONS</sub> <sup>(1)</sup>      |     | 4.91  |       | mW   |

|                 |                                      | Audio playback (both                                       | I <sub>VDD</sub>                      |     | 3.74  |       | mA   |

|                 |                                      | channels), 100- $\mu$ W output into 32 $\Omega$            |                                       |     | 0.21  |       | mA   |

|                 |                                      |                                                            | P <sub>CONS</sub> <sup>(1)</sup>      |     | 7.35  |       | mW   |

|                 |                                      | 2-way call, no signal into 32 $\Omega$                     | I <sub>VDD</sub>                      |     | 2.36  |       | mA   |

|                 |                                      |                                                            |                                       |     | 0.96  |       | mA   |

|                 |                                      |                                                            | P <sub>CONS</sub> <sup>(1)</sup>      |     | 6.35  |       | mW   |

|                 |                                      |                                                            | I <sub>VDD</sub>                      |     | 3.68  |       | mA   |

| Power of        | consumption                          | 2-way call, 100-μW output into 32 Ω                        |                                       |     | 0.96  |       | mA   |

|                 |                                      | 02 11                                                      | P <sub>CONS</sub> <sup>(1)</sup>      |     | 8.74  |       | mW   |

|                 |                                      |                                                            | I <sub>VDD</sub>                      |     | 10.84 |       | μA   |

|                 |                                      | Accessory not inserted                                     |                                       |     | 1.05  |       | μA   |

|                 |                                      |                                                            | P <sub>CONS</sub> <sup>(1)</sup>      |     | 22.7  |       | μW   |

|                 |                                      | Accessory not inserted,                                    | I <sub>VDD</sub>                      |     | 150.9 |       | μA   |

| me              |                                      | mechanical switch is open                                  | IMICVDD                               |     | 1.05  |       | μA   |

|                 |                                      | (JACK_SENSE=1)                                             | P <sub>CONS</sub> <sup>(1)</sup>      |     | 278.3 |       | μW   |

|                 |                                      |                                                            | I <sub>VDD</sub>                      |     | 108.1 |       | μA   |

|                 |                                      | Accessory inserted and in sleep mode                       | IMICVDD                               |     | 1.06  |       | μA   |

|                 |                                      | mode                                                       | P <sub>CONS</sub> <sup>(1)</sup>      |     | 197.8 |       | μW   |

(1) Total power consumption from VDD and MICVDD.

EXAS STRUMENTS

#### **TPA6166A2**

ZHCSDD5B-MARCH 2014-REVISED JANUARY 2015

www.ti.com.cn

# 6.6 Electrical Characteristics, Audio Amplifiers

$VDD = 1.8 \text{ V}, \text{ MICVDD} = 3.0 \text{ V}, \text{ } \text{A}_{\text{V}} = 0 \text{ } \text{dB}, \text{ } \text{C}_{\text{IN}} = 0.47 \text{ } \mu\text{F}, \text{ } \text{C}_{\text{FLY}} = 1.0 \text{ } \mu\text{F}, \text{ } \text{C}_{\text{CPVDD}} = \text{C}_{\text{CPVSS}} = 1.0 \text{ } \mu\text{F}, \text{ } \text{R}_{\text{L}} = 32 \text{ } \Omega \text{, outputs in phase, } \text{T}_{\text{A}} = 25^{\circ}\text{C} \text{ (unless otherwise noted)}.$

|                      | PARAMETER                                                  | TEST CONDITION                                                                                                                                               | IS                            | MIN    | TYP    | MAX               | UNIT             |  |

|----------------------|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------|--------|-------------------|------------------|--|

| HEADPH               | ONE AND LINE-OUT AMPLIFIERS                                |                                                                                                                                                              | i                             |        |        |                   |                  |  |

|                      | Programmable gain range                                    |                                                                                                                                                              |                               | -42    |        | 6                 | dB               |  |

| A <sub>V,Max</sub>   |                                                            | $A_V = 6 \text{ dB}$                                                                                                                                         |                               | 5.0    | 6.0    | 7.0               | dB               |  |

| A <sub>V,Min</sub>   |                                                            | $A_V = -42 \text{ dB}$                                                                                                                                       |                               | -43    | -42    | -41               | dB               |  |

|                      | Gain step size                                             | -42 dB $\leq A_V \leq 6$ dB                                                                                                                                  |                               |        | 1      |                   | dB               |  |

| ΔA <sub>V</sub>      | Gain matching                                              | Between left and right channels                                                                                                                              |                               | -0.5   |        | 0.5               | dB               |  |

|                      | Mute attenuation                                           |                                                                                                                                                              |                               |        | 103.7  |                   | dB               |  |

|                      |                                                            | THD+N = 1%, f = 1 kHz, $R_L = 32$ channel on                                                                                                                 | Ω, single                     |        | 29.1   |                   |                  |  |

|                      |                                                            | THD+N = 1%, f = 1 kHz, $R_L$ = 32<br>C both channels on                                                                                                      | Ω,                            |        | 23.2   |                   |                  |  |

| Po                   | Output power                                               | THD+N = 1%, f = 1 kHz, $R_L = 16$ channel on                                                                                                                 | Ω, single                     |        | 43.0   |                   | mW               |  |

|                      |                                                            | THD+N = 1%, f = 1 kHz, $R_L$ = 16<br>processing of Request 596221 wa<br>10:19 on 28 Jan 2015. Click here<br>data Click here to access the HTM<br>channels on | as completed at to access the |        | 30.2   |                   |                  |  |

|                      | Total harmonic distortion plus noise                       | $R_{L} = 16 \Omega, P_{O} = 10 \text{ mW}, \text{ f} = 1 \text{ kHz}$                                                                                        | Z                             |        | 0.021% |                   |                  |  |

| THD+N                |                                                            | $R_{L} = 16 \Omega, P_{O} = 0.1 \text{ mW}, f = 1 \text{ kH}$                                                                                                |                               | 0.057% |        |                   |                  |  |

|                      |                                                            | $R_L = 10 \text{ k}\Omega, V_{OUT} = 1 \text{ V}_{RMS}, f = 1$                                                                                               | kHz                           |        | 0.014% |                   |                  |  |

|                      | Power supply rejection ratio                               | $f = dc, VDD = 1.7 V to 1.9 V, A_V =$                                                                                                                        |                               | 70     | 91     |                   |                  |  |

| PSRR                 |                                                            | f = 217 Hz, 100 mV <sub>P-P</sub> ripple on V                                                                                                                | 'DD                           |        | 88     |                   | dB               |  |

|                      |                                                            | f = 10  kHz, 100 mV <sub>P-P</sub> ripple on VDD                                                                                                             |                               |        | 71     |                   |                  |  |

|                      |                                                            | $A_V = 0 dB$                                                                                                                                                 |                               | 8.0    |        | μV <sub>RMS</sub> |                  |  |

| E <sub>N</sub>       | Output noise <sup>(1)</sup>                                | A <sub>V</sub> = -30 dB                                                                                                                                      |                               |        | 2.0    |                   |                  |  |

|                      |                                                            | $A_V = -42 \text{ dB}$                                                                                                                                       |                               |        | 2.0    |                   |                  |  |

|                      | Crosstalk between left and right                           | $R_L = 16 \Omega$ , f = 1 kHz, $P_O = 5 mW$                                                                                                                  |                               |        | -56    |                   | dD               |  |

|                      | channels                                                   | $R_{L} = 32 \Omega, f = 1 \text{ kHz}, P_{O} = 25 \text{ mV}$                                                                                                | V                             |        | -62    |                   | dB               |  |

| R <sub>IN</sub>      | Amplifier input resistance                                 |                                                                                                                                                              |                               |        | 20     |                   | kΩ               |  |

| V <sub>OOS</sub>     | Output offset voltage                                      | $A_V = 0 dB$                                                                                                                                                 |                               | -0.5   |        | 0.5               | mV               |  |

| V <sub>OUT,Max</sub> | Max line output voltage                                    | $R_L = 10 \ k\Omega$                                                                                                                                         |                               |        | 1      |                   | V <sub>RMS</sub> |  |

| f <sub>C,LPF</sub>   | Input low-pass filter 3-dB cutoff frequency <sup>(2)</sup> | $A_V = 0 \text{ dB}$                                                                                                                                         |                               |        | 45.1   |                   | kHz              |  |

|                      | Low-pass filter passband gain <sup>(2)</sup>               | f = 10 Hz to 15 kHz, dc-coupled in $V_{CM} = 0 V$                                                                                                            | nputs with                    |        | -0.4   |                   | dB               |  |

|                      | Low-pass filter stopband gain <sup>(2)</sup>               | f = 145 kHz                                                                                                                                                  |                               |        | -16    |                   | dB               |  |

| f <sub>CP</sub>      | Charge pump frequency                                      |                                                                                                                                                              |                               |        | 1.3    |                   | MHz              |  |

|                      |                                                            | $A_V = 0$ dB, Volume Slewing                                                                                                                                 | Into shutdown                 |        | -83    |                   |                  |  |

|                      | Click and pop <sup>(1)</sup>                               | Enabled, $R_L = 32 \Omega$ , peak voltage, 32 samples / second                                                                                               | Out of shutdown               |        | -69    |                   | dBV              |  |

|                      |                                                            | $P_{O} = 0.5 \text{ mW}, R_{L} = 32 \Omega$                                                                                                                  |                               |        | 6.2    |                   |                  |  |

|                      | Power consumption <sup>(3)</sup>                           | $P_{O} = 5 \text{ mW}, R_{L} = 32 \Omega, \text{THRH} = 2$                                                                                                   | 1                             |        | 13.3   |                   | mW               |  |

|                      |                                                            | $P_{O} = 30 \text{ mW}, R_{L} = 32 \Omega, THRH = 0$                                                                                                         |                               |        | 56.9   |                   | I                |  |

| RL                   | Minimum headphone load                                     |                                                                                                                                                              |                               |        | 32     | 7.8               | Ω                |  |

(1) A-weighted(2) Measured with respect to gain at 997 Hz

(3) Per output channel

# 6.7 Electrical Characteristics, Mic Preamplifier and Bias

VDD = 1.8 V, MICVDD = 3.0 V,  $T_A = 25^{\circ}C$  (unless otherwise noted).

|                   | PARAMETER                                         | TEST CONDIT                                                                                                                                    | MIN                                                           | TYP   | MAX        | UNIT  |                   |

|-------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-------|------------|-------|-------------------|

| MICROP            | HONE BIAS                                         |                                                                                                                                                |                                                               |       |            |       |                   |

|                   |                                                   | Programmed for high value, MICVDD ≥ 2.8 V                                                                                                      |                                                               |       | 2.6        | 2.75  | V                 |

| V <sub>BIAS</sub> | Microphone bias voltage                           | Programmed for low value                                                                                                                       | 1.88                                                          | 2.0   | 2.12       | v     |                   |

| I <sub>OUT</sub>  | Max bias output current                           | Internal bias resistor bypassed (M                                                                                                             | ICR = 011)                                                    |       | 1.2        |       | mA                |

|                   |                                                   | MICR = 000                                                                                                                                     |                                                               | 2.09  | 2.2        | 2.31  |                   |

| P                 |                                                   | MICR = 001                                                                                                                                     |                                                               | 2.47  | 2.6        | 2.73  | kΩ                |

| R <sub>BIAS</sub> | Bias output resistance                            | MICR = 010                                                                                                                                     |                                                               | 2.85  | 3.0        | 3.15  | К12               |

|                   |                                                   | MICR = 011                                                                                                                                     |                                                               |       | 0.13       |       |                   |

| E <sub>N</sub>    | Bias output noise <sup>(1)</sup>                  | Between SLEEVE and RING2, BV 2.2 k $\Omega$ load between SLEEVE and V_{BIAS} = 2.0 V                                                           |                                                               |       | 2.0        |       | μV <sub>RMS</sub> |

| PSRR              |                                                   |                                                                                                                                                | f = dc,<br>MICVDD = 2.8 V to<br>3.6 V                         |       | 92         |       | dB                |

|                   | Power supply rejection ratio                      | Measured between SLEEVE and RING2, 2.2 k $\Omega$ load between SLEEVE and RING2, MICR = 000, V <sub>BIAS</sub> = 2.6 V                         | f = 2 kHz, 100 mV <sub>P-P</sub><br>ripple,<br>MICVDD = 3.0 V |       | 73         |       |                   |

|                   |                                                   | MORC = 000, VBIAS = 2.0 V                                                                                                                      | f = 2 kHz, 100 mV <sub>P-P</sub><br>ripple,<br>MICVDD = 2.8 V |       | 73         |       |                   |

| MicZ              | Microphone Capsule Impedance                      | Measured between Mic and GND before insertion                                                                                                  |                                                               | 1500  |            | 20000 | Ω                 |

| MICROP            | HONE PREAMPLIFIER                                 |                                                                                                                                                |                                                               |       |            |       |                   |

|                   |                                                   | Programmed for high value, f = 997 Hz                                                                                                          |                                                               | 23    | 24         | 25    | ٦Ŀ                |

| A <sub>V</sub>    | Preamplifier gain                                 | Programmed for low value, f = 997 Hz                                                                                                           |                                                               |       | 12         | 13    | dB                |

| E <sub>N</sub>    | Input referred noise <sup>(1)</sup>               | f = 100 Hz to 7 kHz, $A_V$ = 24 dB, N<br>load between SLEEVE and RING2<br>V <sub>BIAS</sub> = 2.0 V                                            |                                                               |       | 3.4        |       | μV <sub>RMS</sub> |

| THD+N             | Total harmonic distortion plus noise              | V <sub>OUT</sub> = 1 V <sub>RMS</sub>                                                                                                          |                                                               |       | 0.095<br>% |       |                   |

|                   |                                                   | Measured between MOUTP-MOUTN, 6.04 k $\Omega$ between SLEEVE and RING2, MICR = 010, V <sub>BIAS</sub> = 2.0 V, f = dc, MICVDD = 2.4 V to 3.6 V |                                                               | 74    |            |       |                   |

| PSRR              | Power supply rejection ratio                      | Measured between MOUTP-<br>MOUTN, 2.2 k $\Omega$ between<br>SLEEVE and RING2,                                                                  | f = dc,<br>MICVDD = 2.8 V to<br>3.6 V                         | 109.5 |            | dB    |                   |

|                   |                                                   | MICR = 000, V <sub>BIAS</sub> = 2.6 V                                                                                                          | f = 2 kHz, 100 mV <sub>P-P</sub><br>ripple on MICVDD          |       | 78         |       |                   |

| V <sub>CMO</sub>  | Output Common Mode                                | MICVDD = 2.4 V - 3.6V                                                                                                                          |                                                               |       | 0.4×MICVDD |       |                   |

| f <sub>C,LO</sub> | Lower -3 dB frequency of HPF <sup>(2)</sup>       |                                                                                                                                                |                                                               | 20    |            |       | Hz                |

| f <sub>C,HI</sub> | Upper -3 dB frequency of amplifier <sup>(2)</sup> |                                                                                                                                                |                                                               |       | 260        |       | kHz               |

(1) A-weighted(2) Measured with respect to gain at 997 Hz

TEXAS INSTRUMENTS

www.ti.com.cn

#### TPA6166A2

ZHCSDD5B-MARCH 2014-REVISED JANUARY 2015

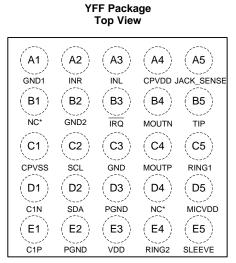

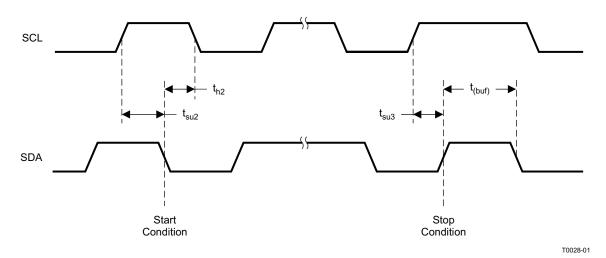

## 6.8 Timing Requirements

For I<sup>2</sup>C interface signals and voltage power-up sequence, over recommended operating conditions (unless otherwise noted). Timing is specified by design.

|                    |                           |                                                | MIN | MAX | UNIT |

|--------------------|---------------------------|------------------------------------------------|-----|-----|------|

| f <sub>SCL</sub>   | Frequency, SCL            | No wait states                                 |     | 400 | kHz  |

| t <sub>w(H)</sub>  | Pulse duration, SCL hig   | h                                              | 0.6 |     | μs   |

| t <sub>w(L)</sub>  | Pulse duration, SCL low   | ,                                              | 1.3 |     | μs   |

| t <sub>su1</sub>   | Setup time, SDA to SCI    |                                                | 100 |     | ns   |

| t <sub>h1</sub>    | Hold time, SCL to SDA     | Hold time, SCL to SDA                          |     |     | ns   |

| t <sub>(buf)</sub> | Bus free time between     | Bus free time between stop and start condition |     |     | μs   |

| t <sub>su2</sub>   | Setup time, SCL to star   | condition                                      | 0.6 |     | μs   |

| t <sub>h2</sub>    | Hold time, start conditio | 0.6                                            |     | μs  |      |

| t <sub>su3</sub>   | Setup time, SCL to stop   | Setup time, SCL to stop condition              |     |     |      |

| t <sub>SP</sub>    | Pulse width of surpress   | 0                                              | 50  | ns  |      |

Figure 1. SCL and SDA Timing

Figure 2. Start and Stop Conditions Timing

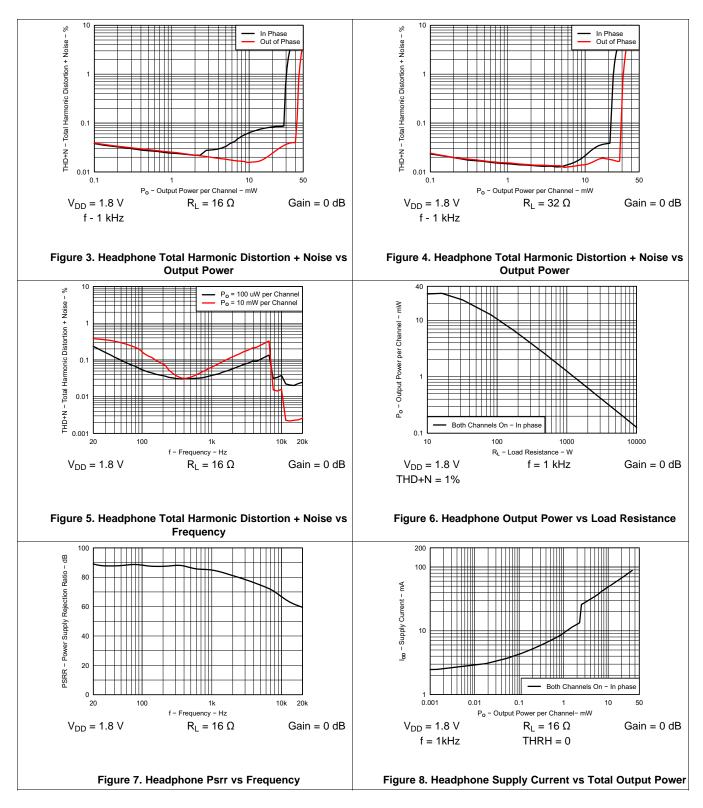

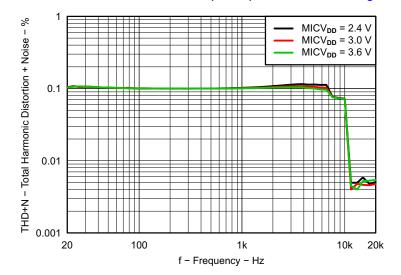

## 6.9 Typical Characteristics

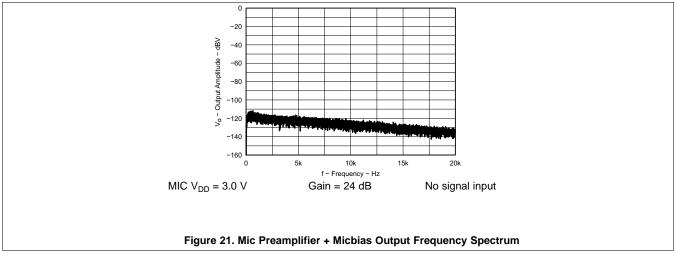

VDD = 1.8 V, MICVDD = 3.0 V,  $A_V = 0$  dB,  $C_{IN} = 0.47 \ \mu\text{F}$ ,  $C_{FLY} = 1.0 \ \mu\text{F}$ ,  $C_{CPVDD} = C_{CPVSS} = 1.0 \ \mu\text{F}$ ,  $R_{HP} = 32 \ \Omega$ , outputs in phase,  $T_A = 25^{\circ}\text{C}$  (unless otherwise noted).

ZHCSDD5B-MARCH 2014-REVISED JANUARY 2015

EXAS

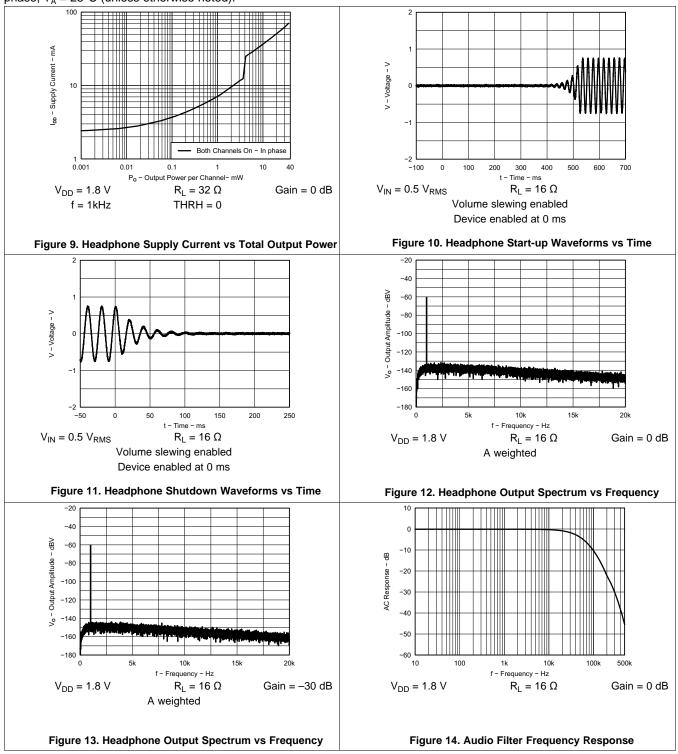

## **Typical Characteristics (continued)**

VDD = 1.8 V, MICVDD = 3.0 V,  $A_V = 0$  dB,  $C_{IN} = 0.47 \ \mu\text{F}$ ,  $C_{FLY} = 1.0 \ \mu\text{F}$ ,  $C_{CPVDD} = C_{CPVSS} = 1.0 \ \mu\text{F}$ ,  $R_{HP} = 32 \ \Omega$ , outputs in phase,  $T_A = 25^{\circ}\text{C}$  (unless otherwise noted).

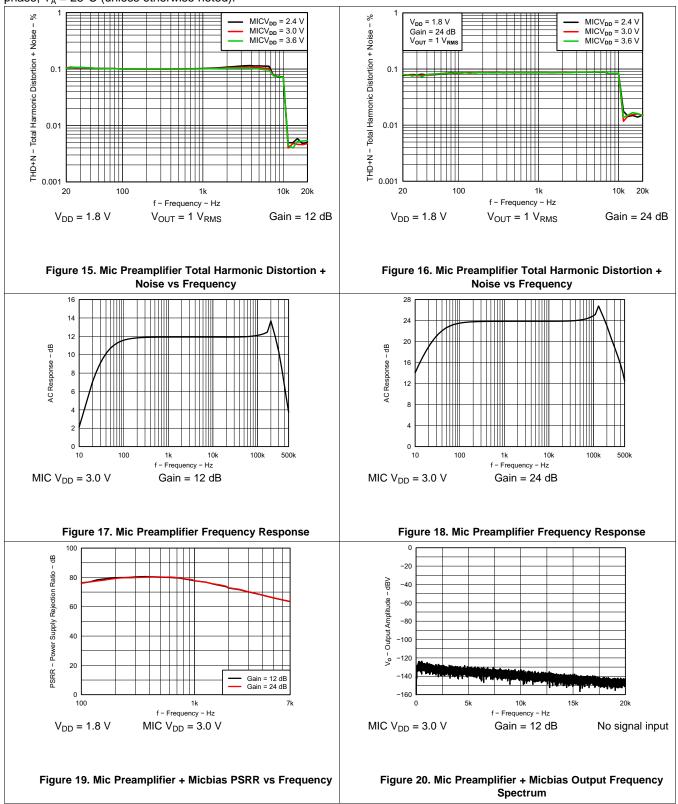

## **Typical Characteristics (continued)**

VDD = 1.8 V, MICVDD = 3.0 V,  $A_V = 0$  dB,  $C_{IN} = 0.47 \ \mu\text{F}$ ,  $C_{FLY} = 1.0 \ \mu\text{F}$ ,  $C_{CPVDD} = C_{CPVSS} = 1.0 \ \mu\text{F}$ ,  $R_{HP} = 32 \ \Omega$ , outputs in phase,  $T_A = 25^{\circ}\text{C}$  (unless otherwise noted).

ZHCSDD5B-MARCH 2014-REVISED JANUARY 2015

www.ti.com.cn

## **Typical Characteristics (continued)**

$VDD = 1.8 \text{ V}, \text{ MICVDD} = 3.0 \text{ V}, \text{ A}_{\text{V}} = 0 \text{ dB}, \text{ C}_{\text{IN}} = 0.47 \text{ }\mu\text{F}, \text{ C}_{\text{FLY}} = 1.0 \text{ }\mu\text{F}, \text{ C}_{\text{CPVDD}} = \text{C}_{\text{CPVSS}} = 1.0 \text{ }\mu\text{F}, \text{ R}_{\text{HP}} = 32 \text{ }\Omega\text{, outputs in phase, } \text{T}_{\text{A}} = 25^{\circ}\text{C} \text{ (unless otherwise noted).}$

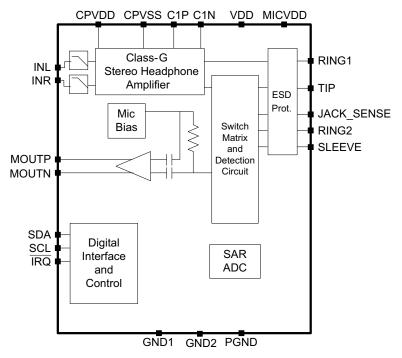

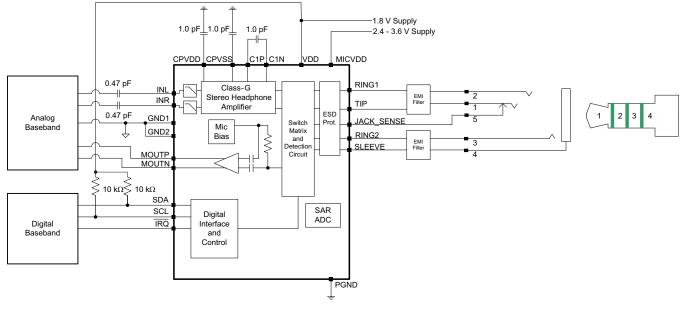

## 7 Detailed Description

## 7.1 Overview

The TPA6166A2 is a small device that serves a large number of complex functions in a portable audio device. It identifies an accessory plugged into the jack, and configures the internal subsystems to take full advantage of its capabilities.

- Headphone-jack accessory detection and identification

- Switch matrix

- · Class-G ground-centered stereo headphone amplifier

- Mic preamplifier and bias

- SAR ADC for various analog sense functions

- ESD protection

- Convenient I<sup>2</sup>C host interface

## 7.2 Functional Block Diagram

## 7.3 Feature Description

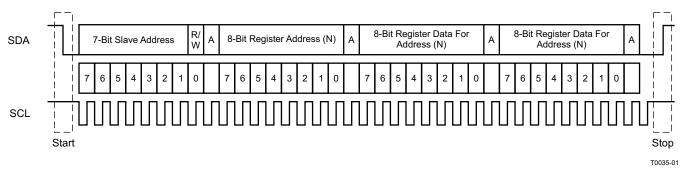

## 7.3.1 I<sup>2</sup>C Interface

The TPA6166A2 I<sup>2</sup>C address is 0x40 (7-bit).

The I<sup>2</sup>C bus employs two signals, SDA (data) and SCL (clock), to communicate between integrated circuits in a system. The bus transfers data serially, one bit at a time. The most significant bit (MSB) is transferred first for the 8-bit address and data bytes. In addition, each byte transferred on the bus is acknowledged by the receiving device with an acknowledge bit. Each transfer operation begins with the master device driving a start condition on the bus and ends with the master device driving a stop condition on the bus. The bus uses transitions on the data terminal (SDA) while the clock is at logic high to indicate start and stop conditions. A high-to-low transition on SDA indicates a start and a low-to-high transition indicates a stop. Normal data-bit transitions must occur within the low time of the clock period.

#### TPA6166A2 ZHCSDD5B – MARCH 2014 – REVISED JANUARY 2015

## **Feature Description (continued)**

Figure 22 shows a typical sequence. The master generates the 7-bit slave address and the read/write (R/W) bit to open communication with another device, and then waits for an acknowledge condition. The TPA6166A2 holds SDA low during the acknowledge clock period to indicate acknowledgment. When acknowledgment occurs, the master transmits the next byte of the sequence. Each device is addressed by a unique 7-bit slave address plus R/W bit (1 byte). All compatible devices share the same signals via a bidirectional bus using a wired-AND connection.

An external pullup resistor must be used for the SDA and SCL signals to set the logic high level for the bus. When the bus level is 3.3 V, use pullup resistors between 1 k $\Omega$  and 2 k $\Omega$ .

There is no limit on the number of bytes that can be transmitted between start and stop conditions. When the last word transfers, the master generates a stop condition to release the bus. A generic data transfer sequence is shown in Figure 22.

#### 7.3.1.1 Single and Multiple Byte Transfers

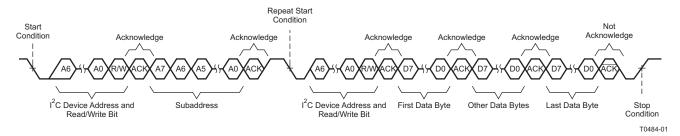

The serial control interface supports both single-byte and multiple byte read/write operations for all registers. During multiple-byte read operations, the TPA6166A2 responds with data, 1 byte at a time, starting at the register assigned, as long as the master device continues to respond with acknowledgments.

The TPA6166A2 supports sequential  $I^2C$  addressing. For write transactions, if a register is issued followed by data for that register and all the remaining registers that follow, a sequential  $I^2C$  write transaction has occurred. For  $I^2C$  sequential write transactions, the register issued then serves as the starting point, and the amount of data subsequently transmitted, before a stop or start is transmitted, determines the number of registers written.

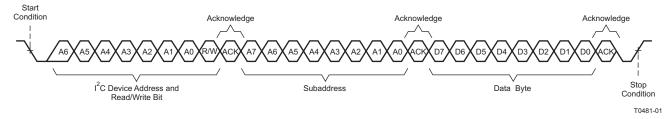

#### 7.3.1.2 Single-Byte Write

As Figure 23 shows, a single-byte data write transfer begins with the master device transmitting a start condition followed by the I2C device address and the read/write bit. The read/write bit determines the direction of the data transfer. For a write data transfer, the read/write bit must be set to 0. After receiving the correct I<sup>2</sup>C device address and the read/write bit, the TPA6166A2 responds with an acknowledge bit. Next, the master transmits the register byte corresponding to the TPA6166A2 internal memory address being accessed. After receiving the register byte, the TPA6166A2 again responds with an acknowledge bit. Next, the master device transmits the data byte to be written to the memory address being accessed. After receiving the register byte, the TPA6166A2 again responds with an acknowledge bit. Next, the master device transmits the data byte to be written to the memory address being accessed. After receiving the register byte, the TPA6166A2 again responds being accessed. After receiving the register byte, the TPA6166A2 again responds being accessed. After receiving the register byte, the TPA6166A2 again responds being accessed. After receiving the register byte, the TPA6166A2 again responds being accessed. After receiving the register byte, the TPA6166A2 again responds being accessed. After receiving the register byte, the TPA6166A2 again responds being accessed. After receiving the register byte, the TPA6166A2 again responds being accessed.

#### Feature Description (continued)

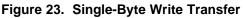

#### 7.3.1.3 Multiple-Byte Write and Incremental Multiple-Byte Write

A multiple-byte data write transfer is identical to a single-byte data write transfer except that multiple data bytes are transmitted by the master device to the TPA6166A2 as shown in Figure 24. After receiving each data byte, the TPA6166A2 responds with an acknowledge bit.

Figure 24. Multiple-Byte Write Transfer

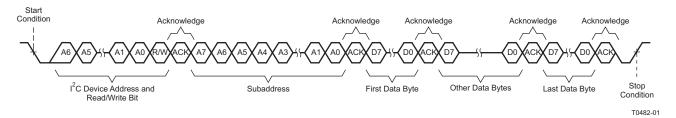

#### 7.3.1.4 Single-Byte Read

As Figure 25 shows, a single-byte data read transfer begins with the master device transmitting a start condition followed by the I<sup>2</sup>C device address and the read/write bit. For the data read transfer, both a write followed by a read are actually executed. Initially, a write is executed to transfer the address byte of the internal memory address to be read. As a result, the read/write bit is set to a 0.

After receiving the TPA6166A2 address and the read/write bit, the TPA6166A2 responds with an acknowledge bit. The master then sends the internal memory address byte, after which the TPA6166A2 issues an acknowledge bit. The master device transmits another start condition followed by the TPA6166A2 address and the read/write bit again. This time the read/write bit is set to 1, indicating a read transfer. Next, the TPA6166A2 transmits the data byte from the memory address being read. After receiving the data byte, the master device transmits a not-acknowledge followed by a stop condition to complete the single-byte data read transfer.

Figure 25. Single-Byte Read Transfer

#### 7.3.1.5 Multiple-Byte Read

A multiple-byte data read transfer is identical to a single-byte data read transfer except that multiple data bytes are transmitted by the TPA6166A2 to the master device as shown in Figure 26. With the exception of the last data byte, the master device responds with an acknowledge bit after receiving each data byte.

TPA6166A2 ZHCSDD5B – MARCH 2014 – REVISED JANUARY 2015

## Feature Description (continued)

## 7.3.2 Accessory Detection

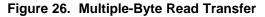

The TPA6166A2 has an advanced accessory jack detection circuitry which determines insertion, removal, as well as type detection of accessories with a 3.5-mm headset jack. The jack and its internal connections are shown in Figure 27.

#### Figure 27. Connecting to a 3.5-mm Headset Jack

When the insertion of a jack is detected, the accessory type detection algorithm runs until two consecutive type detections produce the same result. In general, the type detection algorithm is not run again after this point of time. Hence, on-the-fly change of accessory type is not detected. The following accessories can be detected. Table 6 has specific detection details.

- Stereo Headset (HP with mic)

- Line Out Audio Cable

- Mono Headset

- Stereo Headphone

- Line Out Audio Cable

The limits of detection are shown in Table 1.

#### Table 1. Limits of Detection

| PARAMETER                  | SYMBOL | MIN           | MAX          | UNIT |

|----------------------------|--------|---------------|--------------|------|

| Cable Shield Capacitance   | CCABLE | 150           | 500          | pF   |

| Headphone Load Resistance  | RHP    | 8             | 700/1500*    | Ω    |

| Audio Line Load Resistance | RLINE  | 10            | 50           | kΩ   |

| Microphone Load Resistance | RMIC   | 1.5           | 20           | kΩ   |

| Open/Float                 |        | 200K    70 pF | 10 G    5 pF | kΩ   |

As a result of accessory detection, appropriate blocks are automatically turned on ensuring lower possible power consumption. When accessory is removed, all blocks are turned off ensuring ultra low power. The TPA6166A2 achieves 22.7  $\mu$ W when no accessory is inserted.

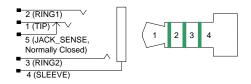

#### 7.3.3 Audio Playback Channel

The TPA6166A2 includes stereo audio channel with integrated low pass filter and class-G headphone amplifier. Figure 28 shows the block diagram for the Audio Channel. The channel includes volume control block. The volume level can be varied from +6 dB to -42 dB in 1-dB steps, in addition to a mute bit, independently for each channel. The volume level of both channels can also be changed simultaneously by the master volume control, which can be achieved by setting Register 0x07, Bit 7 (L=R) to 1. Gain changes are implemented with a soft-stepping algorithm, which only changes the actual volume by one step in every 3.25 ms, either up or down, until the desired volume is reached.

Figure 28. Audio Playback Channel

Because of soft-stepping, the system does not know when the audio channel has been actually muted. This may be important if the system wishes to mute the channel before making a significant change. To help with this situation, the device provides a flag back to the system through a read-only register bit that alerts the system when the part has completed the soft-stepping and the actual volume has reached the desired volume level. Soft-stepping feature can be disabled by setting Register 0x1E, Bit 5 (VSEN) to 1.

The TPA6166A2 integrates switches on RING2 (terminal 3) and SLEEVE (terminal 4) to ground. Based on accessory detection result, either RING2 or SLEEVE is selected as accessory ground, and appropriate switch is turned on. As switches have finite resistance, it can give rise to crosstalk between left and right channel. The TPA6166A2 integrates ground loop rejection circuitry, which reduces crosstalk to a great extent.

The left channel audio output can be routed to TIP. For right channel, audio output is routed to RING1.

ZHCSDD5B-MARCH 2014-REVISED JANUARY 2015

#### 7.3.3.1 Class-G Headphone Amplifier

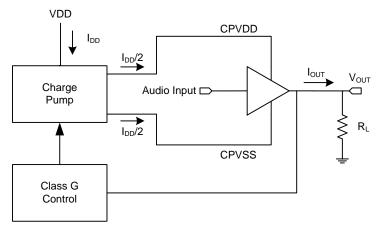

Class-G is a linear amplifier using a modulating supply voltage. A high-efficiency step-down converter regulates the headphone amplifier supply voltage. The headphone amplifier supply voltage increases as the audio output voltage increases. This prevents signal clipping and distortion. The headphone amplifier supply voltage decreases during softer audio periods, reducing battery current and improving overall efficiency. The class-G amplifier has more than twice the efficiency of an equivalent class-AB amplifier. This increases battery life during audio playback.

Figure 29 shows the block diagram for the class-G headphone amplifier. The class-G control examines the amplifier output voltage and determines the optimum headphone supply voltage. CPVDD and CPVSS voltages increase fast enough to avoid any output clipping or distortion. The class-G control operates automatically and does not require programming.

Figure 29. Class-G Headphone Block Diagram

#### 7.3.3.1.1 Headphone Charge Pump

The TPA6166A2 includes a high-efficiency step-down charge pump and an inverting charge pump to generate power supplies for the headphone amplifier. These charge pumps use a common flying capacitor, thus minimizing components. The step-down charge pump regulates CPVDD; the inverting charge pump regulates CPVSS. These are designed to only drive the TPA6166A2 headphone amplifier. Do not use CPVDD or CPVSS as a voltage supply to drive an external device.

## 7.3.3.2 Out-of-Band and Input RF Noise Rejection

When using amplifiers with CODECs and DACs, sometimes there is an increase in the output noise floor from the audio amplifier. This occurs when the output out-of-band noise of the CODEC/DAC folds back into the audio frequency due to the limited gain bandwidth product of the audio amplifier. Single-ended RF noise can also fold back into the audio band thus degrading the audio signal even further.

The TPA6166A2 has a built-in low-pass filter to reduce CODEC/DAC out-of-band noise and RF noise, that could fold back into the audio frequency.

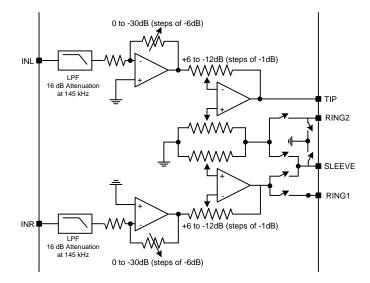

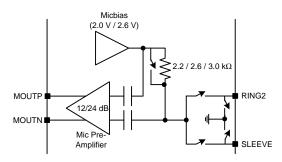

### 7.3.4 Mic Channel

The TPA6166A2 includes microphone preamplifier with selectable gain of 12 dB and 24 dB. The device uses architecture, which removes requirement of external AC coupling capacitor by integrating it inside. The TPA6166A2 also includes Mic-bias with integrated bias resistor. A mic bias voltage can be programmed to 2.0 V or 2.6 V. Mic-bias resistor can be programmed to 2.2 k $\Omega$ , 2.6 k $\Omega$ , 3.0 k $\Omega$  or bypass. Based on accessory detection result, either RING2 (terminal 3 of jack) or SLEEVE (terminal 4 of jack) is selected as Mic input, and appropriate switch is turned on. Figure 30 shows the block diagram for the Mic Channel. Note that Bias resistor bypass mode, accessory detection, removal detection, and mic amp will not function.

Figure 30. Mic Channel

### 7.3.5 Button Press Detection

The TPA6166A2 supports button press detection of different types:

- Single button press/release: When pressed, this typically creates an equivalent resistance of 1  $\Omega$  between RING2 and SLEEVE.

- Passive button press/release: When pressed, this creates an equivalent resistance between RING2 and SLEEVE. The TPA6166A2 reports press and release event along with resistance value (KEYDATA\_DIV and KEYDATA in Register 0x17).

The impedance seen by the ADC is calculated using the following data

- Bias voltage

- Bias resistor

- Parallel impedance of the switch pressed and the microphone capsule impedance

The button press detection is done in a two-stage process. The device remains in a low power mode until a comparator is tripped. The comparator threshold is set to <1500 $\Omega$ . Upon detection, the ADC is started to calculate the impedance pressed.

### NOTE

The ADC will support impedances up to 375  $\Omega$ . Higher values are supported, but are much more susceptible to capacitance in the mic capsule, and could potentially provide erronious readings. At 375  $\Omega$ , Mic Capsule capacitances supported can be up to 50 nF.

For more details on configuring the device for Button Press Detection, see *Button Detection*.

## 7.4 Device Functional Modes

## 7.4.1 I<sup>2</sup>C Options

The TPA6166A2 I<sup>2</sup>C address is 0x40 (7-bit).

- Single-Byte Write

- Multiple-Byte Write

- Incremental Multiple-Byte Write

- Single-Byte Read

- Multiple-Byte Read

## **Device Functional Modes (continued)**

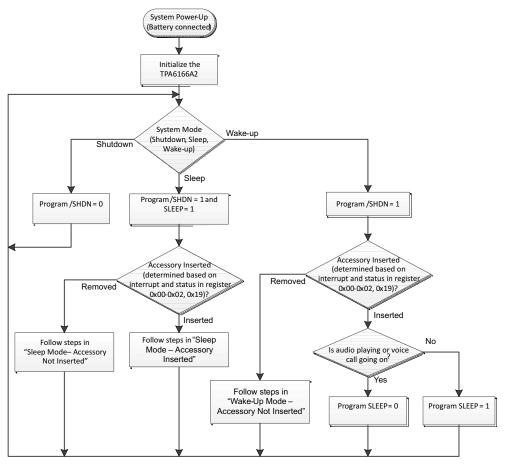

### 7.4.2 System in Shutdown Mode

Shutdown mode enables lowest power consumption from device. During this mode, accessory insertion, removal and type detection are not supported, but as soon as system comes out of shutdown, detection will work fine.

This mode can be programmed by programming /SHDN, register 0x1D (bit-7) to 0 For coming out of shutdown, /SHDN bit should be set to 1.

This will also rerun accessory detection algorithm.

## 7.4.3 System in Sleep Mode

This mode is enabled by programming SLEEP, register 0x1D (bit-6) to 1. During this mode, accessory insertion, removal, type and single-button press/release detection are supported.

### 7.4.3.1 Accessory Not Inserted

When the device is in AUTO mode (register 0x1E, bit 1-0 = 01), the device automatically configures itself in lowest possible power mode.

If accessory was previously inserted and is then removed, interrupt gets generated. Upon interrupt following sequence can be used to determine accessory removal and take appropriate action:

- Read control registers 0x00 to 0x02

- If JKIN, register 0x00, bit-7 = 0, then infer that accessory has been removed. Program SLEEP, register 0x1D, bit-6 = 1.

#### 7.4.3.2 Accessory Inserted

When the device is in AUTO (register 0x1E, bit 1-0 = 01) and SLEEP (register 0x1D, bit-6 = 1) mode, the device automatically configures itself to minimize power consumption. For example: the mic preamplifier and headphone amplifiers are turned off, but removal and button-press detection continue to operate.

If the accessory was previously not inserted and is then inserted, interrupt gets generated. Upon interrupt following sequence can be used to determine accessory insertion and take appropriate action:

- Read control registers 0x00 to 0x02

- If JKIN, register 0x00, bit 7 = 1, then infer that accessory has been inserted.

- Read control register 0x19 to determine type of accessory

When the system wakes up and programs the device out of SLEEP mode, appropriate blocks will automatically turn on based on the type of accessory. System can also use accessory type to configure different routings (example: mix left and right channel for mono headset) and signal swing (depending on whether it is headphone or line-out load).

If the system was previously not in sleep mode and enters sleep mode, the following sequence should be followed to avoid pop noise on the headphone output:

- Enable interrupt due to volume slewing. This can be done by programming register 0x04, bit-5 (IVOL) = 1.

- If register 0x07, bit-7 (L=R) is 1, then program register 0x1E, bits 7-6 (left and right headphone control) = 00 and bits 1-0 (AUTO) = 00. Wait for interrupt due to volume slewing complete (VOL, register 0x00, bit-5).

- If register 0x07, bit-7 (L=R) is 0, then execute following steps:

- If register 0x1E, bit-7=1, then program register 0x1E, bit-7 = 0 and bits 1-0 = 00. Wait for interrupt due to volume slewing complete (VOL, register 0x00, bit-5)

- If register 0x1E, bit-6=1, then program register 0x1E, bit-6 = 0 and bits 1-0 = 00. Wait for interrupt due to volume slewing complete (VOL, register 0x00, bit-5).

- Program device in sleep mode (register 0x1D, bit-6, SLEEP = 1).

- Program device back in Auto mode (register 0x1E, bits 1-0, AUTO = 01.

#### **Device Functional Modes (continued)**

#### 7.4.3.3 Button Detection During Sleep Mode

During Sleep mode, single-button press/release detection is supported. Remaining buttons of passive multibutton headset (resistance of button higher than 0  $\Omega$ ) are also detected as single button (resistance  $\approx 0 \Omega$ ). For a button press, the system can use this event to wake up the system, and then program the device (details in *Button Detection*) to detect the second button press correctly.

Upon interrupt, the following sequence needs to be followed for button detection:

- Read control registers 0x00 to 0x02

- If MCSW, register 0x00, bit 1 = 1, then infer that button has been pressed/released. As long as button is

pressed, MCSW continues to remain set.

#### 7.4.4 System in Wake-Up Mode

This mode is enabled by programming SLEEP, register 0x1D (bit-6) to 0. During this mode, accessory insertion, removal, type, single button press/release and passive multi-button detection are supported.

#### 7.4.4.1 Accessory Not Inserted

When the device is in AUTO mode (register 0x1E, bit 1-0 = 01), the device automatically configures itself in lowest possible power mode.

If accessory was previously inserted and is then removed, interrupt gets generated. Upon interrupt following sequence can be used to determine accessory removal and take appropriate action:

- Read control registers 0x00 to 0x02

- If JKIN, register 0x00, bit 7 = 0, then infer that accessory has been removed. Program SLEEP, register 0x1D, bit-6 = 1.

If a voice call is in progress, the system can use removal information to change from headset to handset mode. If audio is playing, the system can use the removal information to route audio to the speaker amplifier.

#### 7.4.4.2 Accessory Inserted

When the device is in AUTO mode (register 0x1E, bit 1-0 = 01), the device automatically configures itself to turn on appropriate blocks. For example: for mono, only left headphone amp is turned on, whereas for stereo both left and right headphone amps are turned on).

If accessory was previously not inserted and is then inserted, an interrupt is generated. Upon an interrupt, the following sequence can be used to determine that an accessory insertion has occurred and take appropriate action:

- Read control registers 0x00 to 0x02

- If JKIN, register 0x00, bit-7 = 1, then infer that accessory has been inserted.

- Read control register 0x19 (bit 6-0, STATE) to determine type of accessory. Program SLEEP, register 0x1D, bit-6 = 0 (if audio is playing or in voice call).

If a voice call is in progress, the system can use the insertion information to change from handset to headset mode. If audio is playing on speaker, the system can use the insertion information to route audio to headset (accessory).

Accessory type detection can be used to configure different routings (example: for mono headset, mix left and right channel and route it on INL of the TPA6166A2) and signal swing (depending on headphone or line-out load).

#### 7.4.4.3 Audio Not Playing or Not in Voice Call

During this mode, lowest power option is to program the device in SLEEP mode (register 0x1D, bit 6 = 1). This will power down mic preamplifier and headphone amplifiers. If audio starts playing or a voice call starts, SLEEP can be programmed to 0. To minimize pop and clock, headphone amplifiers go through power up sequencing where it first powers up in MUTE and then soft step volume to set gain with slew rate of 3.25 ms/dB. Volume slewing can be disabled by programming register 0x1E, bit-5 to 1.

Copyright © 2014–2015, Texas Instruments Incorporated

## **Device Functional Modes (continued)**

### 7.4.4.4 High Impedance Line Out Load

The TPA6166A2 detects 50-k $\Omega$  max impedance as a line-level output. A value above 50 k $\Omega$  is treated as float and the corresponding amplifier is kept powered down. If higher value line-out load must be supported, the following sequence can be used, when accessory insertion is detected:

- Register 0x19 (bit 6-0, STATE) value is already available immediately after insertion detection (to determine type of accessory). Check if STATE have one of following values

- 0x1B

- 0x1C

- 0x1F

- If value matches one of the above, the following register writes should be done

- Register 0x19 (bits 7-0) = 0x1A

- Register 0x19 (bits 7-0) = 0x9A

The preceding sequence will power up both left and right headphone amplifiers. After this step, the device will again go into automatic mode, where blocks will be powered up and down based on detection result.

### 7.4.4.5 Button Detection

If only single-button detection is required, following sequence can be used when interrupt is generated:

- Read control registers 0x00 to 0x02

- If MCSW, register 0x00, bit 1 = 1, then infer that button has been pressed (PRESS, register 0x01, bit-1 = 1) or released (PRESS, register 0x01, bit-1 = 0)

If both single-button and passive multi-button detection are required, the following sequence can be used:

- As soon as the device is in wake-up mode (SLEEP = 0), following register writes should be done

- Register 0x1C (bit-7) = 1

- Register 0x66 (bits 7-0) = 0xF1

- Register 0x6F (bits 7-0) = 0x01

- Register 0x66 (bits 7-0) = 0x00

- Upon interrupt, following sequence can be used:

- Read control registers 0x00 to 0x02

- If MCSW (register 0x00, bit-1) = 1, then infer that single-button has been pressed (PRESS, register 0x01, bit-1 = 1) or released (PRESS, register 0x01, bit-1 = 0).

- If MCSW = 0 and KEY (register 0x01, bit-2) = 1, then infer that passive multi-button has been pressed (PRESS, register 0x01, bit-1 = 1) or released (PRESS, register 0x01, bit-1 = 0).

- If passive multi-button press is detected, value of button resistance can be known by reading register 0x17 (KEYDATA\_DIV and KEYDATA). Equation for resistance calculation is shown in description of control register 0x17

- When device needs to be taken to Sleep or Shutdown mode or accessory removal gets detected, the following additional registers should be programmed to minimize power consumption

- Register 0x1C (bit-7) = 0

- Register 0x66 (bits 7-0) = 0xF1

- Register 0x6F (bits 7-0) = 0x00

- Register 0x66 (bits 7-0) = 0x00

### 7.5 Register Maps

## 7.5.1 Register Functional Overview

The TPA6166A2 when configured in fully automated mode (bits 1-0, register 0x1E set to 01) automatically enables and disables relevant blocks (headphone, mic preamplifier, mic bias, and so forth) based on result of accessory detection.

| Registers                                                | Read/Write | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00, 0x01,<br>0x02                                      | R          | Configuration and device status registers. These registers are used to report the makeup of the inserted jack as well as report when a microphone switch has been pressed or the jack has been removed. The TPA6166A2 uses the status registers and IRQ to report the status of various device functions. The status registers bits are set when their respective event occurs and cleared upon reading the register. Device status can be determined either by polling the registers or configuring the IRQ to go low when specific events occur and then reading these registers on IRQ. |

| 0x04, 0x05                                               | R/W        | Interrupt mask registers. These registers determine which bits in the status registers $(0x00 - 0x02)$ will trigger IRQ to go low. Once IRQ goes low, it becomes high when status register responsible for IRQ generation gets read.                                                                                                                                                                                                                                                                                                                                                       |

| 0x07, 0x08                                               | R/W        | Headphone volume setting registers. These registers independently control and report the gain of the left and right headphone amplifiers. There is an option to have right channel gain track left channel gain setting. This can be done by setting bit 7 in control register 0x07.                                                                                                                                                                                                                                                                                                       |

| 0x09                                                     | R/W        | Microphone bias and preamplifier setting register. This register is used to program different settings related to microphone preamplifier and microphone bias.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0x0B                                                     | R          | Revision ID register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0x15, 0x16                                               | R/W        | Passive multi-button debounce and delay settings. Debounce helps in filtering any unwanted noise/glitches in system which can cause wrong button detection. The delay register sets the time-out that the mic button press is masked from the system. At the end of the delay time, the TPA6166A2 checks to see if accessory is still present. If accessory is not present, then it does not generate interrupt corresponding to button press. This prevents accessory removal from being detected as a button press (due to RING2 and SLEEVE getting shorted during removal).             |

| 0x17                                                     | R          | Passive multi-button data register. For resistance calculations, refer to control register description in data sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0x19                                                     | R/W        | State Register. Indicates type of accessory (headset with/without mic, headphone, line-out, no accessory inserted, and so forth). If AUTO mode (default) is turned on, relevant blocks are automatically turned on/off based on type of accessory.                                                                                                                                                                                                                                                                                                                                         |

| 0x18, 0x1A                                               | R/W        | Accessory detection test hardware settings. Provides fine-tuning for accessory detection algorithm.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |