**TAS5722L**

ZHCSFV9A -MAY 2016-REVISED DECEMBER 2016

# TAS5722L 15W 数字输入单声道 D 类音频放大器

## 特性

- 单声道 D 类放大器

- 0.02% THD 时为 4Ω/ 17V 持续提供 15W 功率

- >90%的高效 D 类运行,省去了散热器

- 音频性能(PVDD = 16.5V,RSPK =  $4\Omega$ )

- 空闲声道噪声 = 45μVRMS (A-Wtd)

- 总谐波失真 + 噪声 (THD+N) = 0.04% (1W/1kHz)

- 信噪比 (SNR) = 106dB A-Wtd (参考 THD+N = 1%)

- I<sup>2</sup>S 输入: 32kHz 至 96kHz

- 时分复用 (TDM) 音频输入

- 多达 8 条声道(32 位, 96kHz)

- $I^2C$  控制,通过 8 个可选  $I^2C$  地址实现

- 电源

- 功率放大器: 4.5V 至 17V

- 数字 I/O 电压: 1.8V

- 稳定性 特性

- 时钟误差检测器、直流偏移和短路保护

- 过压、欠压和过热保护

### 2 应用

- 低音炮、音箱、条形音响、楼宇自动化

- 有源扬声器,个人计算机

- 环绕立体声系统, 单声道音频系统

### 3 说明

TAS5722L器件是一款高效单声道 D 类音频功率放大 器,其中包含集成的数字输出削波器、多个增益选项和 广泛的电源电压范围。该器件的标称电源电压范围为 4.5V 至 17 VDC。

TAS5722L 已针对高瞬态功率能力进行优化,能够利 用小型扬声器的动态功率余量。可持续为 4Ω 的扬声器 提供超过 15W 的功率。

数字时分复用 (TDM) 接口支持多达 8 个器件共用同一 条总线。

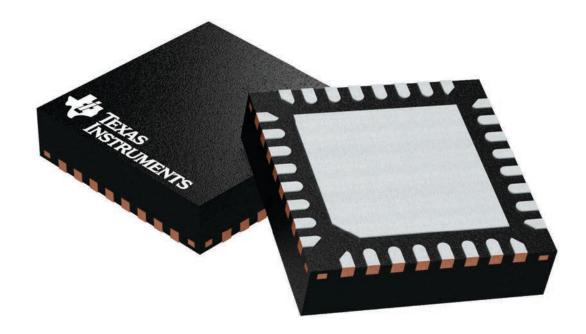

TAS5722L器件采用 4mm x 4mm 32 引脚四方扁平无 引线 (QFN) 封装。

#### 器件信息(1)

| 器件名称     | 封装       | 封装尺寸      |

|----------|----------|-----------|

| TAS5722L | QFN (32) | 4mm x 4mm |

(1) 要了解所有可用封装,请见文档末尾的可订购产品附录。

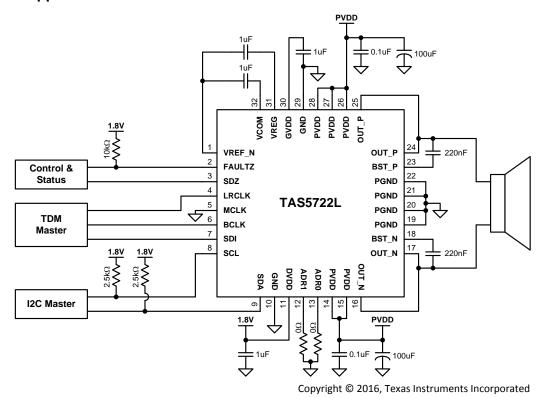

#### 简化电路原理图

Copyright © 2016, Texas Instruments Incorporated

|   | 目                                    | 录  |                                 |                |

|---|--------------------------------------|----|---------------------------------|----------------|

| 1 | 特性 1                                 |    | 7.3 Feature Description         | 1              |

| 2 | 应用 1                                 |    | 7.4 Device Functional Modes     | 2              |

| 3 | 说明 1                                 |    | 7.5 Register Maps               | 3              |

| 4 | 修订历史记录                               | 8  | Applications and Implementation | 39             |

| 5 | Pin Configuration and Functions      |    | 8.1 Application Information     | 39             |

| 6 | Specifications 5                     |    | 8.2 Typical Application         | 3!             |

| ٠ | 6.1 Absolute Maximum Ratings 5       | 9  | Power Supply Recommendations    | 4              |

|   | 6.2 ESD Ratings                      | 10 | Layout                          | 4 <sup>,</sup> |

|   | 6.3 Recommended Operating Conditions |    | 10.1 Layout Guidelines          | 4              |

|   | 6.4 Thermal Information              |    | 10.2 Layout Example             | 42             |

|   | 6.5 Electrical Characteristics       | 11 | 器件和文档支持                         | 4              |

|   | 6.6 Timing Requirements              |    | 11.1 商标                         | 4              |

|   | 6.7 Typical Characteristics          |    | 11.2 静电放电警告                     | 4              |

| 7 | Detailed Description 17              |    | 11.3 Glossary                   |                |

|   | 7.1 Overview                         | 12 | ! 机械封装和可订购信息                    | 4              |

|   | 7.2 Functional Block Diagram         |    | 12.1 Package Option Addendum    | 4              |

# 4 修订历史记录

注: 之前版本的页码可能与当前版本有所不同。

| CI | hanges from Original (May 2016) to Revision A | Pag | јe |

|----|-----------------------------------------------|-----|----|

| •  | 己将产品更改为量产数据。                                  |     | 1  |

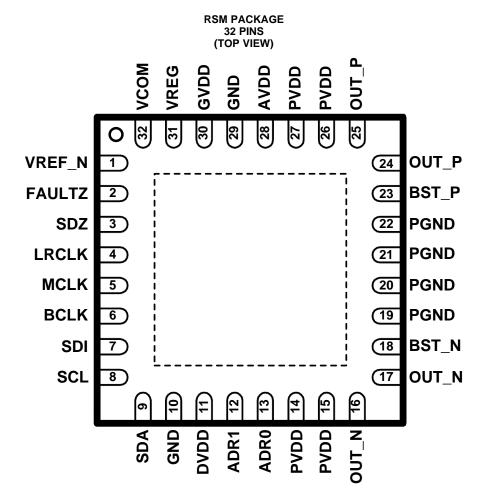

# 5 Pin Configuration and Functions

Pin Functions<sup>(1)</sup>

| PIN I/O/P <sup>(2)</sup>                 |                                                                                             |                                 | DESCRIPTION                                                                                                            |

|------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------|------------------------------------------------------------------------------------------------------------------------|

| NAME                                     | NO.                                                                                         | I/O/F · /                       | DESCRIPTION                                                                                                            |

| ADR1                                     | 12                                                                                          | I                               | $ ho_{2}^{2}$ C address inputs. Each pin can detect a short to DVDD, a short to GND, a 22-k $\Omega$ connection to GND |

| ADR0                                     | 13 I                                                                                        |                                 | and a 22-k $\Omega$ connection to DVDD.                                                                                |

| AVDD                                     | 28                                                                                          | Р                               | Analog power supply input. Connect directly to PVDD.                                                                   |

| BCLK 6 I TDM Interface serial bit clock. |                                                                                             | TDM Interface serial bit clock. |                                                                                                                        |

| BST_N                                    | T_N 18 P Class-D Amplifier negative bootstrap. Connect a capacitor between BST_N and OUT_N. |                                 | Class-D Amplifier negative bootstrap. Connect a capacitor between BST_N and OUT_N.                                     |

| BST_P                                    | 23                                                                                          | Р                               | Class-D Amplifier positive bootstrap. Connect a capacitor between BST_P and OUT_P.                                     |

| DVDD                                     | 11                                                                                          | Р                               | Digital power supply. Connect to 1.8-V supply with external decoupling capacitor.                                      |

| FAULTZ                                   | 2                                                                                           | 0                               | Open drain active low fault flag. Pull up on PCB with resistor to DVDD.                                                |

| GND                                      | 10                                                                                          | P                               | Ground. Connect to PCB ground plane.                                                                                   |

| GND                                      | 29                                                                                          | Г                               | Ground. Connect to PCB ground plane.                                                                                   |

| GVDD                                     | 30                                                                                          | 0                               | Class-D amplifier gate drive regulator output. Connect decoupling cap to PCB ground plane.                             |

| LRCLK                                    | 4                                                                                           | I                               | TDM interface left/right clock.                                                                                        |

| MCLK                                     | 5                                                                                           | I                               | Device master clock.                                                                                                   |

- (1) Connect exposed thermal pad to PCB ground plane

- (2) I = input, O = output, P = power, I/O = bi-directional

# Pin Functions<sup>(1)</sup> (continued)

| PII    | N        | (0)                                                                                  |                                                                                       |  |  |

|--------|----------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|

| NAME   | NO.      | I/O/P <sup>(2)</sup>                                                                 | DESCRIPTION                                                                           |  |  |

|        | 19       |                                                                                      |                                                                                       |  |  |

| DOND   | 20       |                                                                                      | Development Occupation DOD assess designed                                            |  |  |

| PGND   | 21       | Р                                                                                    | Power ground. Connect to PCB ground plane.                                            |  |  |

|        | 22       |                                                                                      |                                                                                       |  |  |

|        | 14       |                                                                                      |                                                                                       |  |  |

| PVDD   | 15<br>26 | Class D amplifier never sumply input. Connect to DVDD sumply and describe externally |                                                                                       |  |  |

| PVDD   |          | P                                                                                    | Class-D amplifier power supply input. Connect to PVDD supply and decouple externally. |  |  |

|        | 27       |                                                                                      |                                                                                       |  |  |

| OUT N  | 16       | 0                                                                                    | Class D amplifier pagetive systems                                                    |  |  |

| OUT_N  | 17       | U                                                                                    | Class-D amplifier negative output.                                                    |  |  |

| OUT_P  | 24       | 0                                                                                    | Class-D amplifier positive output.                                                    |  |  |

| 001_P  | 25       | U                                                                                    | Class-D amplifier positive output.                                                    |  |  |

| SCL    | 8        | I                                                                                    | $I^2$ C clock Input. Pull up on PCB with a 2.4-k $\Omega$ resistor.                   |  |  |

| SDA    | 9        | I/O                                                                                  | l <sup>2</sup> C bi-directional data. Pull up on PCB with a 2.4-kΩ resistor.          |  |  |

| SDI    | 7        | I                                                                                    | TDM interface data input.                                                             |  |  |

| SDZ    | 3        | I                                                                                    | Active low shutdown signal. Assert low to hold device inactive.                       |  |  |

| VCOM   | 32       | 0                                                                                    | Common mode reference output. Connect decoupling capacitor to the VREF_N pin.         |  |  |

| VREF_N | 1        | Р                                                                                    | Negative reference for analog. Connect to VCOM and VREG capacitor negative pins.      |  |  |

| VREG   | 31       | 0                                                                                    | Analog regulator output. Connect decoupling capacitor to the VREF_N pin.              |  |  |

## 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                  |                               |                                          | MIN  | MAX                     | UNIT |

|------------------|-------------------------------|------------------------------------------|------|-------------------------|------|

| V                | Supply voltage (2)            | PVDD, AVDD                               | -0.3 | 20                      | V    |

| V <sub>CC</sub>  |                               | DVDD                                     | -0.3 | 2.25                    |      |

|                  | Digital input voltage         | Digital inputs referenced to DVDD supply | -0.5 | V <sub>DVDD</sub> + 0.5 | V    |

| $T_A$            | Ambient operating temperature |                                          | -25  | 85                      | °C   |

| T <sub>stg</sub> | Storage temperature range     | torage temperature range                 |      | 125                     | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods my affect device reliability.

## 6.2 ESD Ratings

|                    |                         |                                                                               | VALUE | UNIT |

|--------------------|-------------------------|-------------------------------------------------------------------------------|-------|------|

|                    |                         | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins (1)              | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all pins (2) | ±750  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                  |                                  | MIN  | TYP        | MAX | UNIT |

|------------------|----------------------------------|------|------------|-----|------|

| PVDD<br>AVDD     | Power supply voltage             | 4.5  |            | 17  | V    |

| DVDD             | Power supply voltage             | 1.65 | 1.8        | 2   | V    |

| $V_{IH(DR)}$     | High-level digital input voltage |      | $V_{DVDD}$ |     | ٧    |

| $V_{IL(DR)}$     | Low-level digital input voltage  |      | 0          |     | V    |

| R <sub>SPK</sub> | Minimum speaker load             | 3.2  |            |     | Ω    |

| T <sub>A</sub>   | Operating free-air temperature   | -25  |            | 85  | °C   |

| $T_{J}$          | Operating junction temperature   | -25  |            | 150 | ů    |

<sup>(2)</sup> All voltages are with respect to network ground pin.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

#### 6.4 Thermal Information

|                    |                                                           | TAS5722L  |      |

|--------------------|-----------------------------------------------------------|-----------|------|

|                    | THERMAL METRIC <sup>(1)</sup>                             | RSM (QFN) | UNIT |

|                    |                                                           | 32 PINS   |      |

| $R_{\theta JA}$    | Junction-to-ambient thermal resistance (2)                | 37.3      |      |

| $R_{\theta JCtop}$ | Junction-to-case (top) thermal resistance (3)             | 30.4      |      |

| $R_{\theta JB}$    | Junction-to-board thermal resistance (4)                  | 7.9       | °C/M |

| ΨЈТ                | Junction-to-top characterization parameter <sup>(5)</sup> | 0.4       | °C/W |

| ΨЈВ                | Junction-to-board characterization parameter (6)          | 7.7       |      |

| $R_{\theta JCbot}$ | Junction-to-case (bottom) thermal resistance (7)          | 2.5       |      |

- (1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application

- The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

- The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDECstandard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

- The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

- The junction-to-top characterization parameter,  $\psi_{IT}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $R_{\theta JA}$ , using a procedure described in JESD51-2a (sections 6 and 7). The junction-to-board characterization parameter,  $\psi_{JB}$ , estimates the junction temperature of a device in a real system and is extracted

- from the simulation data for obtaining  $R_{\theta JA}$ , using a procedure described in JESD51-2a (sections 6 and 7). The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

## 6.5 Electrical Characteristics

$V_{PVDD}$  = 16.5 V,  $V_{DVDD}$  = 1.8 V,  $R_L$  = 4  $\Omega$  + 33  $\mu$ H,  $f_{PWM}$  = 576 kHz, 22-Hz to 20- kHz Bandwidth, AP AUX-0025 + AES17 Filter (unless otherwise noted)

|                         | PARAMETER                                                 | CONDITIONS                                        | MIN  | TYP | MAX            | UNIT |

|-------------------------|-----------------------------------------------------------|---------------------------------------------------|------|-----|----------------|------|

| DIGITAL INP             | UT AND OUTPUT                                             |                                                   |      |     |                |      |

| V <sub>IH</sub>         | High-level digital input logic voltage threshold          | All digital pins                                  | 70%  |     |                |      |

| V <sub>IL</sub>         | Low-level digital input logic voltage threshold           | All digital pins                                  |      |     | 30%            |      |

| I <sub>IH</sub>         | Input logic "high" leakage for digital inputs             | All digital pins, excluding SDZ                   |      |     | 15             | μΑ   |

| I <sub>IL</sub>         | Input logic "low" leakage for digital inputs              | All digital pins, excluding SDZ                   |      |     | -15            | μΑ   |

| I <sub>IH(SDZ)</sub>    | Input logic "high" leakage for SDZ inputs                 | SDZ                                               |      |     | 1              | μΑ   |

| I <sub>IL(SDZ)</sub>    | Input logic "low" leakage for SDZ inputs                  | SDZ                                               |      |     | -1             | μΑ   |

| V <sub>OL</sub>         | Output logic "low" for FAULTZ open drain Output           | I <sub>OL</sub> = −2 mA                           |      |     | $V_{\rm DVDD}$ |      |

| C <sub>IN</sub>         | Input capacitance for digital inputs                      | All digital pins                                  |      | 5   |                | pF   |

| MASTER CL               | оск                                                       |                                                   |      |     |                |      |

| D <sub>MCLK</sub>       | Allowable MCLK duty cycle                                 |                                                   | 45%  | 50% | 55%            |      |

|                         | MCLK input frequency                                      |                                                   |      |     | 25             | MHz  |

| f <sub>MCLK</sub>       | Supported single-speed MCLK frequencies                   | values: 64, 128, 256 and 512                      | 2.8  |     | 24.6           | MHz  |

|                         | Supported double-speed MCLK frequencies                   | values: 64, 128 and 256                           | 5.6  |     | 24.6           | MHz  |

| SERIAL AUD              | DIO PORT                                                  |                                                   |      |     |                |      |

| D <sub>BCLK</sub>       | Allowable BCLK duty cycle                                 |                                                   | 45%  | 50% | 55%            |      |

|                         | BCLK input frequency                                      |                                                   |      |     | 25             | MHz  |

| f <sub>BCLK</sub>       | Supported single-speed BCLK frequencies                   | values: 64, 96, 128, 192 and 256                  | 2.8  |     | 12.3           | MHz  |

|                         | Supported double-speed BCLK frequencies                   | values: 64, 96, 128, 192 and 256                  | 5.6  |     | 24.6           | MHz  |

| f_                      | Supported single-speed input sample rates                 | values: 44.1 and 48                               | 44.1 |     | 48             | kHz  |

| f <sub>S</sub>          | Supported double-speed input sample rates                 | values: 88.2 and 96                               | 88.2 |     | 96             | kHz  |

| I <sup>2</sup> C CONTRO | L PORT                                                    |                                                   |      |     |                |      |

| C <sub>L(I2C)</sub>     | Allowable load capacitance for each I <sup>2</sup> C Line |                                                   |      |     | 400            | pF   |

| f <sub>SCL</sub>        | SCL frequency                                             | No wait states                                    |      |     | 400            | kHz  |

| PROTECTIO               | N                                                         |                                                   |      |     |                |      |

| OTE <sub>THRESH</sub>   | Over-temperature error (OTE) threshold                    |                                                   |      | 150 |                | °C   |

| OTE <sub>HYST</sub>     | Over-temperature error (OTE) hysteresis                   |                                                   |      | 15  |                | °C   |

| OCE <sub>THRESH</sub>   | overcurrent error (OCE) threshold                         | V <sub>PVDD</sub> = 16.5 V, T <sub>A</sub> = 25°C |      | 5   |                | Α    |

| DCE <sub>THRESH</sub>   | DC error (DCE) threshold                                  | V <sub>PVDD</sub> = 16.5V, TA = 25°C              |      | 2.6 |                | V    |

# Electrical Characteristics (接下页)

$V_{PVDD}$  = 16.5 V,  $V_{DVDD}$  = 1.8 V,  $R_L$  = 4  $\Omega$  + 33  $\mu$ H,  $f_{PWM}$  = 576 kHz, 22-Hz to 20- kHz Bandwidth, AP AUX-0025 + AES17 Filter (unless otherwise noted)

|                                     | PARAMETER                      | CONDITIONS                                                                                                                                                                        | MIN TYP             | MAX   | UNIT  |

|-------------------------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-------|-------|

| AMPLIFIER                           | PERFORMANCE                    |                                                                                                                                                                                   |                     |       |       |

|                                     |                                | $R_L$ = 8 $\Omega$ +33 $\mu$ H, 1% THD+N, $V_{PVDD}$ = 12 V, $f_{IN}$ = 1 kHz                                                                                                     | 8.2                 |       |       |

| D                                   | Continuous average power       | $R_L$ = 8 $\Omega + 33~\mu H,~1\%$ THD+N, $V_{PVDD}$ = 16.5 V, $f_{IN}$ = 1 kHz                                                                                                   | 15.25               |       | W     |

| P <sub>OUT</sub>                    | Commuous average power         | $R_{L} = 4~\Omega + 33~\mu H,~1\%~THD + N,~V_{PVDD} = 12~V, \\ f_{IN} = 1~kHz$                                                                                                    | 14.25               |       | VV    |

|                                     |                                | $\begin{aligned} R_L &= 4~\Omega + 33~\mu H,~1\%~THD + N,~V_{PVDD} = 16.5~V,\\ f_{IN} &= 1~kHz \end{aligned}$                                                                     | 16                  |       |       |

|                                     |                                | $R_L$ = 8 $\Omega$ +33 $\mu$ H, $V_{PVDD}$ = 12 V, $P_{OUT}$ = 4.25 W, 20 Hz $\leq$ $f_{IN}$ $\leq$ 20 kHz                                                                        | 0.05%               |       |       |

| THD+N                               | Total harmonic distortion plus | $R_L$ = 8 Ω+33 μH, $V_{PVDD}$ = 16.5 V, $P_{OUT}$ = 4.25 W, 20 Hz ≤ $f_{IN}$ ≤ 20 kHz                                                                                             | 0.05%               |       |       |

| I UD+N                              | noise                          | $R_L$ = 4 Ω+33 μH, $V_{PVDD}$ = 12 V, $P_{OUT}$ = 8.25 W, 20 Hz ≤ $f_{IN}$ ≤ 20 kHz                                                                                               | 0.05%               |       |       |

| P <sub>EFF</sub>                    |                                | $R_L$ = 4 Ω+33 μH, $V_{PVDD}$ = 16.5 V, $P_{OUT}$ = 8.25 W, 20 Hz ≤ $f_{IN}$ ≤ 20 kHz                                                                                             | 0.06%               |       |       |

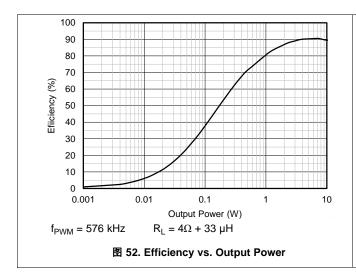

| P <sub>EFF</sub> V <sub>N</sub> KCP | Power officiency               | $R_L$ = 8 Ω+33 μH, $V_{PVDD}$ = 16.5 V, $P_{OUT}$ = 10 W                                                                                                                          | 90%                 |       |       |

| PEFF                                | Power efficiency               | $R_L$ = 4 Ω+33 μH, $V_{PVDD}$ = 16.5 V, $P_{OUT}$ = 14 W                                                                                                                          | 87%                 |       |       |

| V <sub>N</sub>                      | Integrated noise floor voltage | A-Weighted, Gain = 20.7dBV, $R_L$ = 8 $\Omega$ +33 $\mu H$                                                                                                                        | 50                  |       | μVrms |

| KCP                                 | Click-pop performance          | Into and out of HW reset, into and out of SW shutdown, when SAIF clocks are applied or removed and during power rail cycling.  Measured using Maxim click-pop measurement method. | -60                 |       | dB    |

| Ф сс                                | Channel-to-channel phase shift | Output phase shift between multiple devices from 20 Hz to 20 kHz. Across all sample frequencies and SAIF operating modes.                                                         | 0.2                 |       | deg   |

|                                     |                                | AC, 5.5 V ≤ V <sub>PVDD</sub> ≤ 16.5 V, DVDD = 1.8<br>V+200 mV <sub>P-P</sub> , f <sub>RIPPLE</sub> from 20 Hz to 20 kHz                                                          | 69                  |       |       |

| PSRR                                | Power supply rejection ratio   | AC, $V_{PVDD}$ = 16.5 V+200 mV <sub>P-P</sub> , $f_{RIPPLE}$ from 20 Hz to 5 kHz                                                                                                  | 64                  |       | dB    |

|                                     | <u> </u>                       | AC, $V_{PVDD}$ = 16.5 V+100 mV <sub>P-P</sub> , $f_{RIPPLE}$ from 5 kHz to 20 kHz                                                                                                 | 60                  |       |       |

| $AV_{00}$                           |                                | ANALOG_GAIN[1:0] register bits set to "00"                                                                                                                                        | 19.2                |       | dBV   |

| $AV_{01}$                           | Amplifier analog gain (1)      | ANALOG_GAIN[1:0] register bits set to "01"                                                                                                                                        | 20.7                |       | dBV   |

| $AV_{10}$                           | Amplifier arraing gain.        | ANALOG_GAIN[1:0] register bits set to "10"                                                                                                                                        | 23.5                |       | dBV   |

| AV <sub>11</sub>                    |                                | ANALOG_GAIN[1:0] register bits set to "11"                                                                                                                                        | 26.3                |       | dBV   |

| AV <sub>ERROR</sub>                 | Amplifier analog gain error    |                                                                                                                                                                                   |                     | ±0.15 | dB    |

| Vos                                 | DC output offset voltage       | Measured between OUTP and OUTN                                                                                                                                                    | 1.5                 |       | mV    |

| A <sub>RIPPLE</sub>                 | Frequency response             | Maximum deviation above or below passband gain.                                                                                                                                   | ±0.15               |       | dB    |

| f <sub>LP</sub>                     | -3 dB Output Cutoff Frequency  |                                                                                                                                                                                   | 0.47×f <sub>S</sub> |       | Hz    |

| R <sub>DS(on)FET</sub>              | Power stage FET on-resistance  | T <sub>A</sub> = 25°C                                                                                                                                                             | 120                 |       | mΩ    |

<sup>(1)</sup> When PVDD is less than 5.5 V, the voltage regulator that operates the analog circuitry does not have enough headroom to maintain the nominal 5.4-V internal voltage. The lack of headroom causes a direct reduction in gain (approximately –0.8 dB at 5 V and –1.74 dB at 4.5 V), but the device functions properly down to V<sub>PVDD</sub> = 4.5 V. For operation below 5.5V, the VREG\_LVL bit (register 0x14, bit 2) can be set high, which reduces the internal voltage regulator output voltage to prevent variation in gain. When the bit is set high, all gain settings are reduced by 3dB.

# Electrical Characteristics (接下页)

$V_{PVDD}$  = 16.5 V,  $V_{DVDD}$  = 1.8 V,  $R_L$  = 4  $\Omega$  + 33  $\mu$ H,  $f_{PWM}$  = 576 kHz, 22-Hz to 20- kHz Bandwidth, AP AUX-0025 + AES17 Filter (unless otherwise noted)

| PARAMETER              |                                                    | CONDITIONS                              | MIN | TYP | MAX | UNIT |

|------------------------|----------------------------------------------------|-----------------------------------------|-----|-----|-----|------|

| R <sub>DS(on)TOT</sub> | Power stage total on-resistance (FET+bond+package) | T <sub>A</sub> = 25°C                   |     | 150 |     | mΩ   |

| I <sub>P-P</sub>       | Peak output current                                | T <sub>A</sub> = 25°C                   |     | 5   |     | Α    |

| f <sub>PWM</sub>       | PWM switching frequency                            | values: 6, 8, 10, 12, 14, 16, 20 and 24 | 6   |     | 24  | MHz  |

# 6.6 Timing Requirements

|                     |                         |                                                                                                                    | MIN | NOM                  | MAX | UNIT |

|---------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------|-----|----------------------|-----|------|

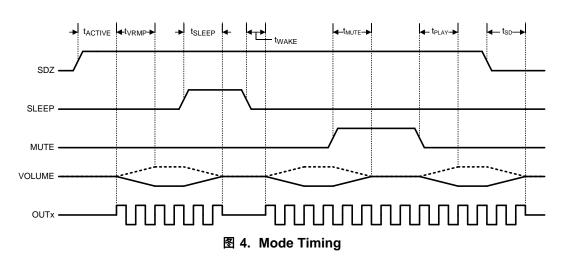

| t <sub>ACTIVE</sub> | Shutdown to Active Time | From deassertion of SDZ (both pin and I <sup>2</sup> C register bit) until the Class-D amplifier begins switching. |     | 25                   |     | ms   |

| t <sub>WAKE</sub>   | Wake Time               | From the deassertion of SLEEP until the Class-D amplifier starts switching.                                        |     | 1                    |     | ms   |

| t <sub>SLEEP</sub>  | Sleep Time              | From the assertion of SLEEP until the Class-D amplifier stops switching.                                           |     | t <sub>vrmp</sub> +1 |     | ms   |

| t <sub>MUTE</sub>   | Play to Mute Time       | From the assertion of MUTE until the volume has ramped to the minimum.                                             |     | $t_{\text{vrmp}}$    |     | ms   |

| t <sub>PLAY</sub>   | Un-Mute to Play Time    | From the deassertion of MUTE until the volume has returned to its current setting.                                 |     | $t_{\text{vrmp}}$    |     | ms   |

| t <sub>SD</sub>     | Active to Shutdown Time | From the assertion of SDZ (pin or I <sup>2</sup> C register bit) until the Class-D amplifier stops switching.      |     | t <sub>vrmp</sub> +1 |     | ms   |

# Timing Requirements (接下页)

|                                    |                                                     |                                                                | MIN | NOM | MAX | UNIT |

|------------------------------------|-----------------------------------------------------|----------------------------------------------------------------|-----|-----|-----|------|

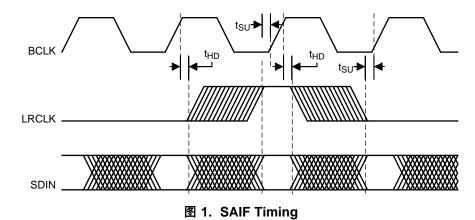

| SERIAL AU                          | DIO PORT                                            |                                                                |     |     |     |      |

| t <sub>H_L</sub>                   | Time High/Low, BCLK, LRCLK, SDI inputs              |                                                                | 10  |     |     | ns   |

|                                    |                                                     | Input t <sub>RISE</sub> ≤ 1 ns, input t <sub>FALL</sub> ≤ 1 ns | 5   |     |     |      |

| t <sub>SU</sub> / t <sub>HLD</sub> | Setup and hold time. LRCLK, SDI input to BCLK edge. | Input t <sub>RISE</sub> ≤ 4 ns, input t <sub>FALL</sub> ≤ 4ns  | 8   |     |     | ns   |

|                                    | input to DoLit dago.                                | Input t <sub>RISE</sub> ≤ 8 ns, input t <sub>FALL</sub> ≤ 8ns  | 12  |     |     |      |

| t <sub>RISE</sub>                  | Rise-time BCLK, LRCLK, SDI inputs                   |                                                                |     |     | 8   | ns   |

| t <sub>FALL</sub>                  | Fall-time BCLK, LRCLK, SDI inputs                   |                                                                |     |     | 8   | ns   |

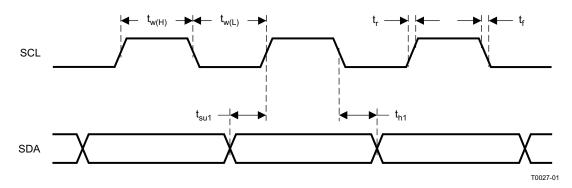

| I <sup>2</sup> C CONTRO            | OL PORT                                             |                                                                | *   |     | *   |      |

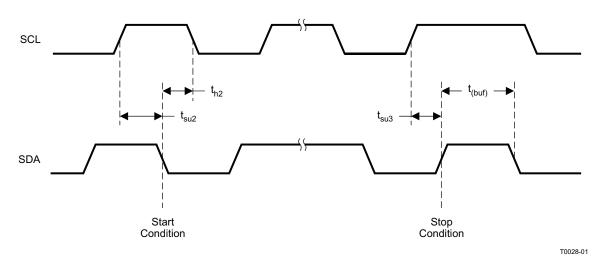

| t <sub>BUF</sub>                   | Bus free time between start and stop conditions     |                                                                | 1.3 |     |     | μs   |

| t <sub>H1(I2C)</sub>               | Hold Time, SCL to SDA                               |                                                                | 0   |     |     | ns   |

| t <sub>H2(I2C)</sub>               | Hold Time, start condition to SCL                   |                                                                | 0.6 |     |     | μs   |

| t <sub>START(I2C)</sub>            | I2C Startup Time after DVDD Power On Reset          |                                                                |     |     | 12  | ms   |

| t <sub>R(I2C)</sub>                | Rise Time, SCL and SDA                              |                                                                |     |     | 300 | ns   |

| t <sub>F(I2C)</sub>                | Fall Time, SCL and SDA                              |                                                                |     |     | 300 | ns   |

| t <sub>SU1(I2C)</sub>              | Setup, SDA to SCL                                   |                                                                | 100 |     |     | ns   |

| t <sub>SU2(I2C)</sub>              | Setup, SCL to start condition                       |                                                                | 0.6 |     |     | μs   |

| t <sub>SU3(I2C)</sub>              | Setup, SCL to stop condition                        |                                                                | 0.6 |     |     | μs   |

| $t_{W(H)}$                         | Required pulse duration, SCL "HIGH"                 |                                                                | 0.6 |     |     | μs   |

| $t_{W(L)}$                         | Required pulse duration, SCL "LOW"                  |                                                                | 1.3 |     |     | μs   |

| PROTECTIO                          | ON                                                  |                                                                |     |     |     |      |

|                                    | American for the time of the most of                | DC detect error                                                |     | 650 |     | ms   |

| t <sub>FAULTZ</sub>                | Amplifier fault time-out period                     | OTE or OCE fault                                               |     | 1.3 |     | S    |

图 2. SCL and SDA Timing

图 3. Start and Stop Conditions Timing

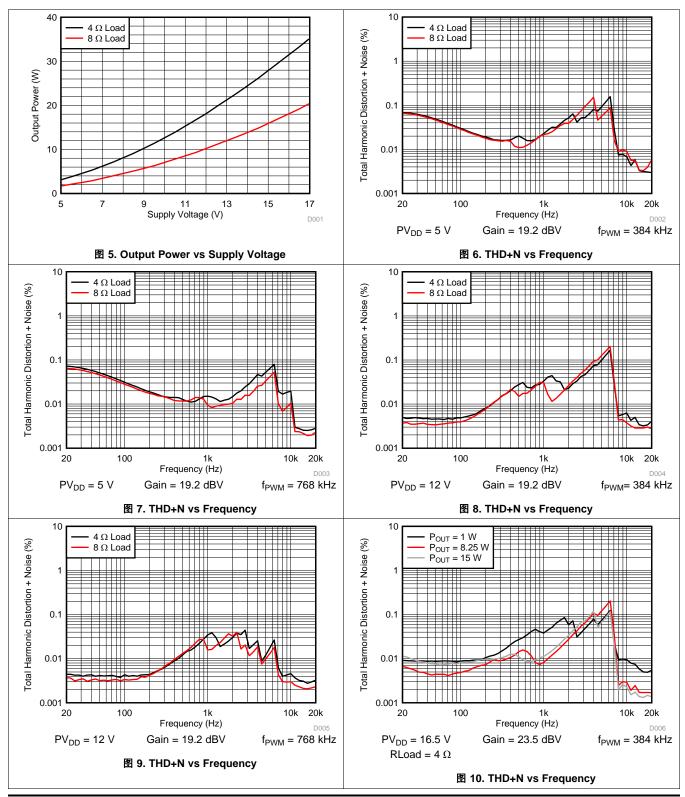

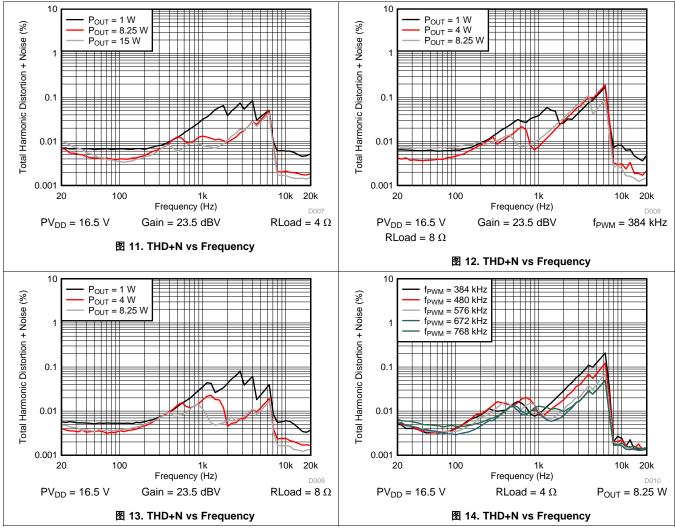

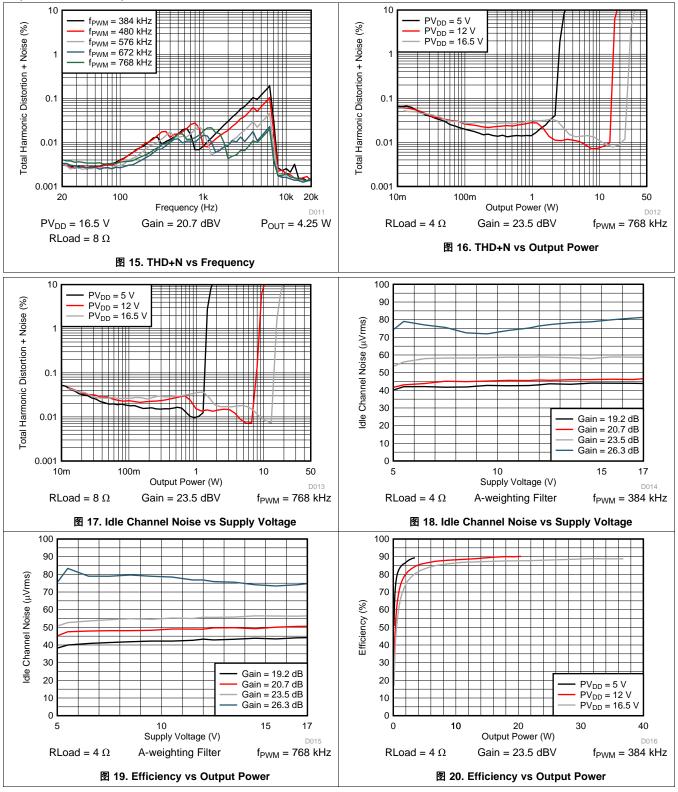

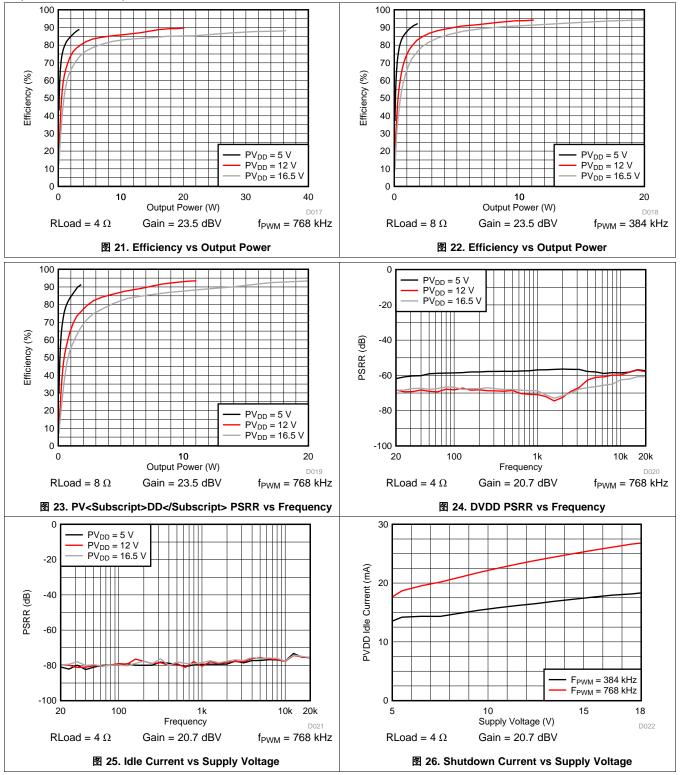

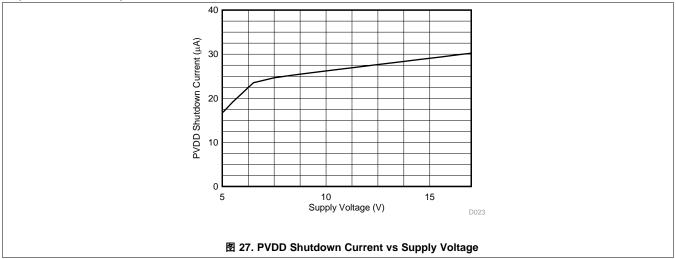

#### 6.7 Typical Characteristics

## 7 Detailed Description

#### 7.1 Overview

The TAS5722L device is a high-efficiency mono Class-D audio power amplifier optimized for high-transient power capability to utilize the dynamic power headroom of small loudspeakers. The TAS5722L device is capable of delivering more than 14 W continuously into a  $4-\Omega$  speaker.

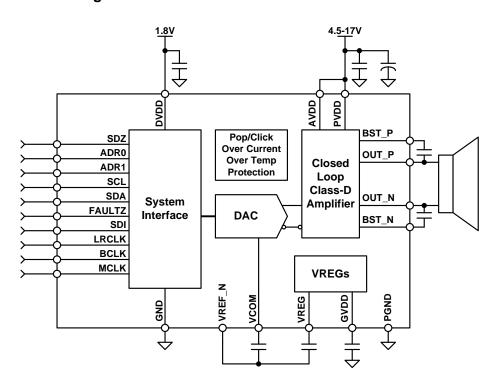

#### 7.2 Functional Block Diagram

### 7.3 Feature Description

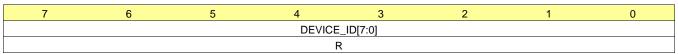

# 7.3.1 Adjustable I<sup>2</sup>C Address

The TAS5722L device has two address pins, which allow up to 8  $I^2C$  addressable devices to share a common TDM bus.  $\frac{1}{8}$  1 lists each  $I^2C$  Device ID setting.

注

The I<sup>2</sup>C Device ID is the 7 most significant bits of the 8-bit address transaction on the bus (with the read/write bit being the least significant bit). For example, a Device ID of 0x6C would be read as 0xD8 when the read/write bit is 0.

| 表 1. I <sup>*</sup> C | Device | Identifier | (ID) | Generation |

|-----------------------|--------|------------|------|------------|

|-----------------------|--------|------------|------|------------|

| ADR1         | ADR0                 | I2C_DEV_ID | DEFAULT TDM<br>SLOT |

|--------------|----------------------|------------|---------------------|

|              | Short to GND         | 0x6C       | 0                   |

| Short to GND | 22-k $\Omega$ to GND | 0x6D       | 1                   |

|              | 22-kΩ to DVDD        | 0x6E       | 2                   |

|              | Short to DVDD        | 0x6F       | 3                   |

| 表 1. | I <sup>2</sup> C Device Identifier | (ID) | Generation | (接下页) |

|------|------------------------------------|------|------------|-------|

|      |                                    |      |            |       |

| ADR1         | ADR0                  | I2C_DEV_ID | DEFAULT TDM<br>SLOT |

|--------------|-----------------------|------------|---------------------|

|              | Short to GND          | 0x70       | 4                   |

| 22-kΩ to GND | 22-k $\Omega$ to GND  | 0x71       | 5                   |

|              | 22-k $\Omega$ to DVDD | 0x72       | 6                   |

|              | Short to DVDD         | 0x73       | 7                   |

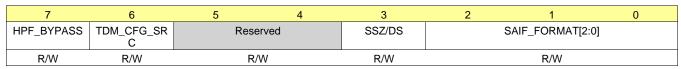

Use a 22-k $\Omega$  resistor with a 5% (or better) tolerance as a pull-up or pull-down resistor. By default, the device uses the TDM time slot equal to its offset from the base I<sup>2</sup>C Device ID (see  $\frac{1}{8}$  1). The TDM slot can also be manually configured by setting the TDM\_CFG\_SRC bit high (bit 6, reg 0x02) and programming the TDM\_SLOT\_SELECT[3:0] bits to the desired slot (bits 0-3, reg 0x03).

For 2-channel, I<sup>2</sup>S operation, TDM slot 0 and 1 correspond to the right and left channels respectively. For left and right justified formats, TDM slot 0 and 1 correspond to left and right channels respectively.

#### 7.3.2 I<sup>2</sup>C Interface

The TAS5722L device has a bidirectional I<sup>2</sup>C interface that is compatible with the Inter-Integrated Circuit (I<sup>2</sup>C) bus protocol and supports both 100 kHz and 400 kHz data transfer rates. The slave-only device does not support a multi-master bus environment or wait-state insertion. The control interface is used to program the registers of the device and to read device status.

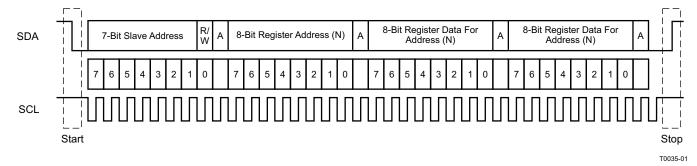

The I²C bus employs two signals, SDA (data) and SCL (clock), to communicate between integrated circuits in a system. Data is transferred on the bus serially, one bit at a time. The address and data can be transferred in byte (8-bit) format, with the most-significant bit (MSB) transferred first. In addition, each byte transferred on the bus is acknowledged by the receiving device with an acknowledge bit. Each transfer operation begins with the master device driving a start condition on the bus and ends with the master device driving a stop condition on the bus. The bus uses transitions on the data pin (SDA) while the clock (SCL) is "HIGH" to indicate start and stop conditions. A high-to-low transition on SDA indicates a start and a low-to-high transition indicates a stop. Normal data-bit transitions must occur within the low time of the clock period. These conditions are shown in ₹ 28. The master generates the 7-bit slave address and the read/write (R/W) bit to open communication with another device and then waits for an acknowledge condition. The TAS5722L device holds SDA "LOW" during the acknowledge clock period to indicate an acknowledgment. When the hold occurs, the master transmits the next byte of the sequence. All compatible devices share the same signals via a bidirectional bus using a wired-AND connection. An external pull-up resistor must be used for the SDA and SCL signals to set the "HIGH" level for the bus.

图 28. Typical I<sup>2</sup>C Timing Sequence

The number of bytes that can be transmitted between start and stop conditions is unlimited. When the last word transfers, the master generates a stop condition to release the bus. A generic data transfer sequence is shown in 图 28.

## 7.3.2.1 Writing to the $l^2$ C Interface

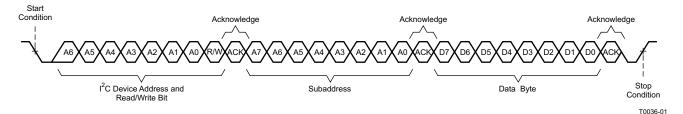

As shown 29, a single-byte data-write transfer begins with the master device transmitting a start condition followed by the I<sup>2</sup>C bit and the read/write bit. The read/write bit determines the direction of the data transfer. For a data-write transfer, the read/write bit is a 0. After receiving the correct I<sup>2</sup>C bit and the read/write bit, the TAS5722L device responds with an acknowledge bit. Next, the master transmits the address byte corresponding to the TAS5722L device register being accessed. After receiving the address byte, the TAS5722L device again responds with an acknowledge bit. Next, the master device transmits the data byte to be written to the memory address being accessed. After receiving the data byte, the TAS5722L device again responds with an acknowledge bit. Finally, the master device transmits a stop condition to complete the single-byte data-write transfer.

图 29. Single Byte Write Transfer Timing

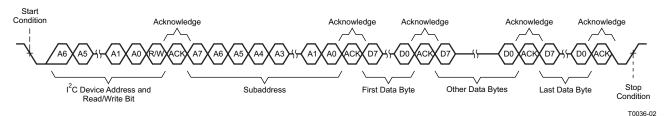

A multi-byte data write transfer is identical to a single-byte data write transfer except that multiple data bytes are transmitted as shown in 30. After receiving each data byte, the TAS5722L device responds with an acknowledge bit. Sequential data bytes are written to sequential addresses.

图 30. Multi-Byte Write Transfer Timing

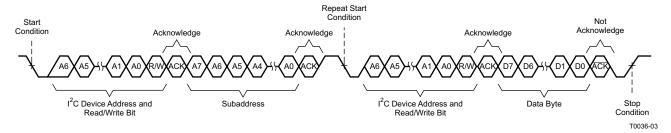

#### 7.3.2.2 Reading from the $^{\rho}$ C Interface

As shown in 30, a data-read transfer begins with the master device transmitting a start condition, followed by the I² device address and the read/write bit. For the data read transfer, both a write followed by a read are actually done. Initially, a write is done to transfer the address byte of the internal register to be read. As a result, the read/write bit becomes a 0. After receiving the TAS5722L device address and the read/write bit, TAS5722L device responds with an acknowledge bit. In addition, after sending the internal memory address byte or bytes, the master device transmits another start condition followed by the TAS5722L device address and the read/write bit again. Then the read/write bit becomes a 1, indicating a read transfer. After receiving the address and the read/write bit, the TAS5722L device again responds with an acknowledge bit. Next, the TAS5722L device transmits the data byte from the register being read. After receiving the data byte, the master device transmits a not-acknowledge followed by a stop condition to complete the data-read transfer.

图 31. Single Byte Read Transfer Timing

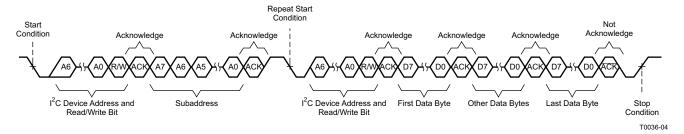

A multiple-byte data read transfer is identical to a single-byte data read transfer except that multiple data bytes are transmitted by the TAS5722L to the master device as shown 32. Except for the last data byte, the master device responds with an acknowledge bit after receiving each data byte.

图 32. Multi-Byte Read Transfer Timing

#### 7.3.3 Serial Audio Interface (SAIF)

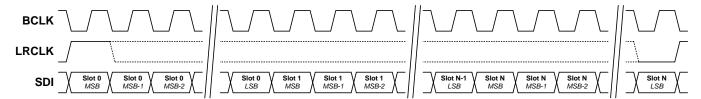

The TAS5722L device SAIF supports a variety of standard stereo serial audio formats including I<sup>2</sup>S, Left Justified and Right Justified. It also supports a time division multiplexed (TDM) format that is capable of transporting up to 8 channels of audio data on a single bus. LRCLK and SDIN are sampled on the rising edge of BCLK.

For the stereo formats (I<sup>2</sup>S, Left Justified and Right Justified), the TAS5722L device supports BCLK to LRCLK ratios of 32, 48 and 64. If the BCLK to LRCLK ratio is 64, MCLK can be derived from BCLK internally. The MCLK\_PIN\_CFG bit (register 0x13, bit 1) controls the source of MCLK and by default derives MCLK from an internal version of BCLK. In this case connect the MCLK pin to a valid logic low value.

If the BCLK to LRCLK ratio is 32 or 48, MCLK must be externally driven. The valid MCLK to LRCLK ratios are 64, 128, 256 and 512 as long as the frequency of MCLK is 37 MHz or less. If the BCLK to LRCLK ratio is 64, it is also acceptable to connect BCLK to MCLK and set the MCLK\_PIN\_CFG bit high.

For TDM operation, the TAS5722L device supports 4 and 8 times slots at both single speed (44.1 kHz or 48 kHz) and double speed (88.2/96 kHz) sample rates. 表 2 lists the supported TDM frame configurations. For 16 and 32-bits per TDM slot, MCLK can be connected to BCLK internally by leaving the MCLK\_PIN\_CFG bit (register 0x13, bit 1) to its default value of 0. For 24-bit time slot operation, MCLK must be externally driven with a valid ratio of 64, 128, 256 or 512 as long as MCLK is less than 37 MHz.

|                         |              |                            |           | 3           |              |

|-------------------------|--------------|----------------------------|-----------|-------------|--------------|

| SAMPLE<br>RATE<br>(kHz) | TDM<br>SLOTS | BITS<br>PER<br>TDM<br>SLOT | SUPPORTED | MCLK = BCLK | TDM_SLOT_16B |

|                         |              | 16                         | Yes       | Yes         | 1            |

|                         | 4            | 24                         | Yes       | No          | 0            |

| 44.4/40                 |              | 32                         | Yes       | Yes         | 0            |

| 44.1/48                 | 8            | 16                         | Yes       | Yes         | 1            |

|                         |              | 24                         | Yes       | No          | 0            |

|                         |              | 32                         | Yes       | Yes         | 0            |

|                         |              | 16                         | Yes       | Yes         | 1            |

|                         | 4            | 24                         | Yes       | No          | 0            |

| 88.2/96                 |              | 32                         | Yes       | Yes         | 0            |

|                         |              | 16                         | Yes       | Yes         | 1            |

|                         | 8            | 24                         | Yes       | No          | 0            |

|                         |              | 32                         | Yes       | Yes         | 0            |

表 2. TDM Frame Configurations

If 16-bit time slots are utilized, set the TDM\_SLOT\_16B register bit (register 0x13, bit 2) to a 1. The SAIF auto detects 24-bit vs. 32-bit time slot widths if TDM\_SLOT\_16B is set to a 0.

The TAS5722L device selects the channel for playback based on either its  $I^2C$  base address offset or based on a dedicated time slot selection register. See the *Adjustable I^2C Address* section for more information.

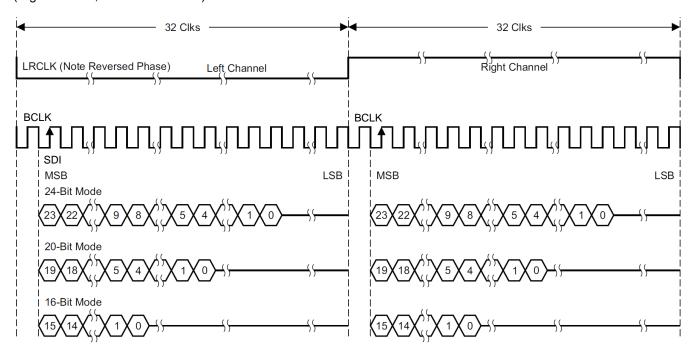

#### 7.3.3.1 Stereo PS Format Timing

illustrates the timing of the stereo I<sup>2</sup>S format with 64 BCLK per LRCLK. Two's complement data is transmitted MSB to LSB with the left channel word beginning one BCLK after the falling edge of LRCLK and the right channel beginning one BCLK after the rising edge of LRCLK. Since data is MSB aligned to the beginning of word transmission, data precision does not need to be configured. Set the SAIF\_FORMAT[2:0] register bits to I<sup>2</sup>S (register 0x02, bits 2:0 = 3'b100).

A. Data presented in two's-complement form with most significant bit (MSB) first.

图 33. I<sup>2</sup>S 64-f<sub>S</sub> Format

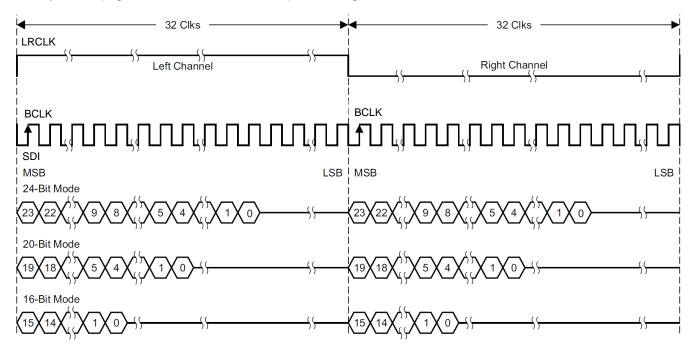

#### 7.3.3.2 Stereo Left-Justified Format Timing

The stereo left justified format is very similar to the  $I^2S$  format timing, except the data word begins transmission at the same cycle that LRCLK toggles (when it is shifted by one bit from  $I^2S$ ). The phase of LRCLK is also opposite of  $I^2S$ . The left channel begins transmission when LRCLK transitions from low to high and the right channel begins transmission when LRCLK transitions from high-to-low. Set the SAIF\_FORMAT[2:0] register bits to left-justified (register 0x02, bits 2:0 = 3'b101). The timing is illustrated in .

A. Data presented in two's-complement form with most significant bit (MSB) first.

图 34. Left-Justified 64-fs Format

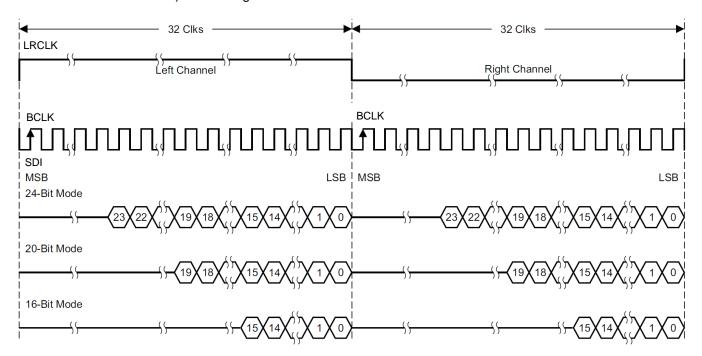

#### 7.3.3.3 Stereo Right-Justified Format Timing

The stereo right justified format aligns the LSB of left channel data to the high to low transition of LRCLK and the LSB of the right channel data to the low to high transition of LRCLK. To insure data is received correctly, the SAIF must be configured for the proper data precision. The TAS5722L supports 16, 18, 20 and 24-bit data precision in right justified format. Set the SAIF\_FORMAT[2:0] register bits (register 0x02, bits 2:0) to the appropriate right-justified setting based on bit precision (value = 3'b000 for 24-bit, 3'b001 for 20-bit, 3'b010 for 18-bit and 3'b011 for 16-bit). The timing is illustrated in .

图 35. Right-Justified 64-f<sub>S</sub> Format

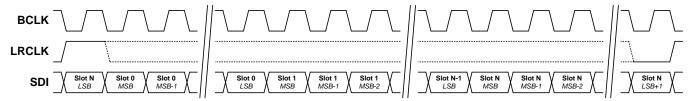

#### 7.3.3.4 TDM Format Timing

A TDM frame begins with the low to high transition of LRCLK. As long as LRCLK is high for at least one BCLK period and low for one BCLK period, duty cycle is irrelevant. The SAIF automatically detects the number of time slots as long as valid BCLK to LRCLK ratios are utilized (see SAIF introduction above).

For  $I^2S$  aligned TDM operation (when time slot 0 begins, one clock cycle after the low to high transition of LRCLK), set SAIF\_FORMAT[2:0] register bits to  $I^2S$  (register 0x02, bits 2:0 = 3'b100). Data is MSB aligned within the 32-bit time slots, so data precision does not need to be configured. The TDM format timing is illustrated in .

图 36. TDM I<sup>2</sup>S Format

For left-justified TDM operation (when time slot 0 begins the cycle LRCLK transitions from low to high), set  $SAIF\_FORMAT[2:0]$  register bits to left-justified(register 0x02, bits 2:0 = 3'b101). As with  $I^2S$ , data is MSB aligned. The timing is illustrated in .

图 37. TDM Left- and Right-Justified Format

For right-justified TDM operation (when time slot 0 begins the cycle LRCLK transitions from low to high), data is LSB aligned to the 32-bit time slot. As with stereo right-justified formats, the TAS5722L must have the data precision configured. Set the SAIF\_FORMAT[2:0] register bits (register 0x02, bits 2:0) to the appropriate right-justified setting based on bit precision (value = 3'b000 for 24-bit, 3'b001 for 20-bit, 3'b010 for 18-bit and 3'b011 for 16-bit). The timing shown in is the same as left-justified TDM, with the data LSB aligned.

#### 7.3.4 Audio Signal Path

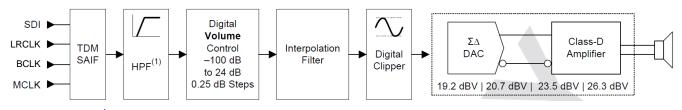

illustrates the audio signal flow from the TDM SAIF to the speaker.

(1) See 表 3 for frequency options.

图 38. Audio Signal Path

## 7.3.4.1 High-Pass Filter (HPF)

Excessive DC in audio content can damage loudspeakers, so the amplifier employs a DC detect circuit that shuts down the power stage and issues a latching fault if this condition occurs. A high-pass filter is provided in the TAS5722L device to remove DC from incoming audio data to prevent this from occurring. 表 3 shows the high-pass, -3 dB corner frequencies for each sample rate. The filter can be bypassed by writing a 1 into bit 7 of register 0x02. The high pass corner frequency can be adjusted by setting the HPF\_CORNER bits in the Digital Control 3 register (B[5:7], register 0x13).

表 3. High-Pass Filter -3 dB Corner Frequencies by Sample Rate

| SAMPLE RATE | -3dB CC | RNER FR | EQUENCY | (Hz) vs. H | IPF_CORN | ER [2:0] |       |       |

|-------------|---------|---------|---------|------------|----------|----------|-------|-------|

| (kHz)       | 000     | 001     | 010     | 011        | 100      | 101      | 110   | 111   |

| 44.1        | 3.675   | 7.35    | 14.7    | 29.4       | 58.8     | 117.6    | 235.2 | 470.4 |

| 48          | 4       | 8       | 16      | 32         | 64       | 128      | 256   | 512   |

| 88.2        | 7.35    | 14.7    | 29.4    | 58.8       | 117.6    | 235.2    | 470.4 | 940.8 |

| 96          | 8       | 16      | 32      | 64         | 128      | 256      | 512   | 1024  |

### 7.3.4.2 Amplifier Analog Gain and Digital Volume Control

The gain from TDM SAIF to speaker is controlled by setting the amplifier's analog gain and digital volume control. Amplifier analog gain settings are presented as the output level in dBV (dB relative to 1 Vrms) with a full scale serial audio input (0 dBFS) and the digital volume control set to 0 dB. It should be noted that these levels may not be achievable because of analog clipping in the amplifier, so they should be used to convey gain only.

表 4 outlines each gain setting expressed in dBV and  $V_{PK}$ .

表 4. Amplifier Gain Settings

| ANALOG_GAIN [1:0] | FULL SCAI | LE OUTPUT             |

|-------------------|-----------|-----------------------|

| SETTING           | dBV       | V <sub>PEAK</sub> (V) |

| 00                | 19.2      | 12.9                  |

| 01                | 20.7      | 15.3                  |

| 10                | 23.5      | 21.2                  |

| 11                | 26.3      | 29.2                  |

公式 1 calculates the amplifiers output voltage.

$$V_{AMP} = Input + A_{dvc} + A_{AMP} dBV$$

where

- V<sub>AMP</sub> is the amplifier output voltage in dBV

- Input is the digital input amplitude in dB with respect to 0 dBFS

- A<sub>dvc</sub> is the digital volume control setting, -100 dB to 24dB in 0.25-dB steps

- A<sub>AMP</sub> is the amplifier analog gain setting (19.2, 20.7, 23.5, or 26.3) in dBV

(1)

Clipping in the digital domain occurs if the input level (in dB relative to 0 dBFS) plus the digital volume control setting (in dB) are greater than 0 dB. The signal path has approximately 0.5 dB of headroom, but TI does not recommend utilizing it.

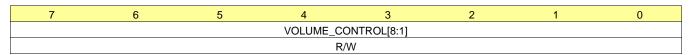

The digital volume control (DVC) can be adjusted from -100 dB to 24 dB in 0.25-dB steps. 公式 2 illustrates how to set the 9-bit volume control bits. The top 8 MSBs of the DVCvalue are stored in Volume Control register (register 0x04) and the LSB is stored in the Digital Control 3 register (register 0x13, bit 0).

$$DVC_{value} = 0x19E + \frac{A_{dvc}}{0.25}$$

(2)

For example, digital volume settings of 0 dB, 24 dB and -100 dB map to 0x19E, 0x1FE and 0x0E respectively. Values below 0x0E are equivalent to mute (the amplifier continues to switch with no audio). When a change in digital volume control occurs, the device ramps the volume to the new setting in 0.25 dB steps either every LRCLK or every 8 LRCLK depending on the value of the VOL\_RAMP\_RATE bit (bit 6, reg 0x03).

The Class-D amplifier uses a closed-loop architecture, so the gain does not depend on the supply input ( $V_{PVDD}$ ). The approximate threshold for the onset of analog clipping is calculated in 公式 3.

$$V_{PK\left(max,preclip\right)} = V_{PVDD} \times \left(\frac{R_L}{2 \times R_{DS\left(on\right)} + R_{int\,erconnect} + R_L}\right) V$$

#### where

- ullet  $V_{PK(max,preclip)}$  is the maximum peak unclipped output voltage in V

- V<sub>PVDD</sub> is the power supply voltage

- $R_L$  is the speaker load in  $\Omega$

- $R_{interconnect}$  is the additional resistance in the PCB (such as cabling and filters) in  $\Omega$

- $R_{DS(on)}$  is the power stage total on resistance (FET+bonding+packaging) in  $\Omega$

The effective on-resistance for the device (including FETs, bonding and packaging leads) is approximately 150 m $\Omega$  at room temperature and increases by approximately 1.6 times over +100°C rise in temperature.  $\frac{1}{2}$ 5 shows approximate maximum unclipped peak output voltages at room temperature (excluding interconnect resistances).

表 5. Approximate Maximum Unclipped Peak Output Voltage at Room Temperature

| SUPPLY VOLTAGE V <sub>PVDD</sub> (V) | PEAK V           | UNCLIPPED<br>OLTAGE<br>(V) |

|--------------------------------------|------------------|----------------------------|

|                                      | $R_L = 4 \Omega$ | $R_L = 8 \Omega$           |

| 12                                   | 11.16            | 11.57                      |

| 17                                   | 15.81            | 16.39                      |

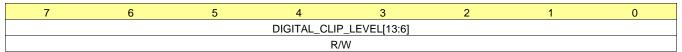

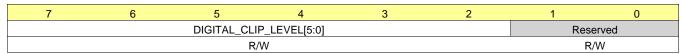

#### 7.3.4.3 Digital Clipper

The digital clipper hard limits the maximum DAC sample value, which provides a simple hardware mechanism to control the largest signal applied to the speaker. Because the block resides in the digital domain, the actual maximum output voltage also depends on the amplifier gain setting and the supply voltage (V<sub>PVDD</sub>) limited amplifier voltage swing (For example, analog clipping may occur before digital clipping).

The maximum amplifier output voltage (excluding limitation due to swing) is calculated in 公式 4.

$$V_{AMP\left(max,dc\right)} = 20 \times log_{10} \left( \frac{DC_{level}}{0xFFFF} \right) + 0.5 + A_{AMP}$$

#### where

- V<sub>AMP(max,dc)</sub> is the amplifier maximum output voltage in dBV

- DC<sub>level</sub> is the digital clipper level

- A<sub>AMP</sub> is the amplifier analog gain setting (19.2, 20.7, 23.5, or 26.3) in dBV

Configure the digital clipper by writing the 20-bit  $DC_{level}$  to registers 0x01, 0x10 and 0x11. Set the  $DC_{level}$  to 0xFFFFF effectively bypasses the digital clipper.

(4)

(3)

### 7.3.4.4 Class-D Amplifier Settings

The PWM switching rate of the Class-D amplifier is a phase locked multiple of the input audio sample rate. 表 6 lists the PWM switching rate settings as programmed in bit 4 through bit 6 in register 0x06. The double-speed sample rates (for example 88.2 kHz, 96 kHz) have the same PWM switching frequencies as their equivalent single-speed sample rates.

表 6. PWM Switching Rates

| PWM_RATE [2:0] | SINGLE-SPEED<br>PWM RATE (× f <sub>LRCLK</sub> ) | DOUBLE-SPEED<br>PWM RATE × f <sub>LRCLK</sub> ) | 44.1 kHz, 88.2 kHz<br>f <sub>PWM</sub> (kHz) | 48 kHz, 96 kHz<br>f <sub>PWM</sub> (kHz) |

|----------------|--------------------------------------------------|-------------------------------------------------|----------------------------------------------|------------------------------------------|

| 000            | 6                                                | 3                                               | 264.6                                        | 288                                      |

| 001            | 8                                                | 4                                               | 352.8                                        | 384                                      |

| 010            | 10                                               | 5                                               | 441                                          | 480                                      |

| 011            | 12                                               | 6                                               | 529.2                                        | 576                                      |

| 100            | 14                                               | 7                                               | 617.4                                        | 672                                      |

| 101            | 16                                               | 8                                               | 705.6                                        | 768                                      |

| 110            | 20                                               | 10                                              | 882                                          | 960                                      |

| 111            | 24                                               | 12                                              | 1058.4                                       | 1152                                     |

The Class-D power stage overcurrent detector issues a latching fault if the load current exceeds the safe limit for the device. This threshold can be proportionately adjusted if desired by programming bits 4-5 of register 0x08. 表 7 shows the relative setting for each overcurrent setting.

表 7. Overcurrent Threshold Settings

| OC_THRESH<br>[1:0] | OVERCURRENT<br>THRESHOLD (%) |

|--------------------|------------------------------|

| 00                 | 100                          |

| 01                 | 75                           |

| 10                 | 50                           |

| 11                 | 25                           |

#### 7.4 Device Functional Modes

This section describes the modes of operation for the TAS5722L device.

表 8. Typical Current Consumption<sup>(1)</sup>

| INPUT<br>VOLTAGE<br>V <sub>PVDD</sub> (V) | MODE          | PWM<br>FREQUENCY<br>f <sub>PWM</sub> (kHz) | I <sub>PVDD</sub> +I <sub>AVDD</sub><br>(mA) | INPUT<br>CURRENT<br>I <sub>DVDD</sub> (mA) |

|-------------------------------------------|---------------|--------------------------------------------|----------------------------------------------|--------------------------------------------|

|                                           |               | 384                                        | 11.45                                        |                                            |

|                                           |               | 480                                        | 12.21                                        |                                            |

|                                           | Idle and Mute | 576                                        | 12.94                                        | 1.30                                       |

| 5                                         |               | 672                                        | 13.70                                        |                                            |

|                                           |               | 768                                        | 14.41                                        |                                            |

|                                           | Sleep         | _                                          | 8.48                                         | 0.32                                       |

|                                           | Shutdown      | _                                          | 0.021                                        | 0.046                                      |

|                                           |               | 384                                        | 13.06                                        |                                            |

|                                           | Idle and Mute | 480                                        | 14.46                                        |                                            |

|                                           |               | 576                                        | 15.79                                        | 1.30                                       |

| 12.5                                      |               | 672                                        | 17.18                                        |                                            |

|                                           |               | 768                                        | 18.49                                        |                                            |

|                                           | Sleep         | _                                          | 7.49                                         | 0.32                                       |

|                                           | Shutdown      | _                                          | 0.042                                        | 0.046                                      |

|                                           |               | 384                                        | 14.00                                        |                                            |

|                                           |               | 480                                        | 15.60                                        |                                            |

|                                           | Idle and Mute | 576                                        | 17.10                                        | 1.30                                       |

| 16.5                                      |               | 672                                        | 18.66                                        |                                            |

|                                           |               | 768                                        | 20.15                                        |                                            |

|                                           | Sleep         | _                                          | 7.61                                         | 0.32                                       |

|                                           | Shutdown      | _                                          | 0.045                                        | 0.046                                      |

<sup>(1)</sup> T<sub>A</sub> = 25°C, PVDD pin tied to AVDD pin, V<sub>DVDD</sub> = 1.8 V, R<sub>LOAD</sub> =  $4\Omega$  + 33  $\mu$ H, f<sub>IN</sub> = Idle, f<sub>S</sub> = 48 kHz, Gain = 20.7 dBV, PWR\_TUNE bit = 1

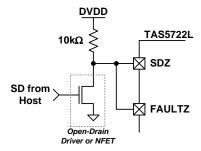

#### 7.4.1 Shutdown Mode (SDZ)

The device enters shutdown mode if either the SDZ pin is asserted low or the I<sup>2</sup>C SDZ register bit is set low (bit 0, reg 0x01). In shutdown mode, the device consumes the minimum quiescent current with most analog and digital blocks powered down. The Class-D amplifier power stage powers down and the output pins are in a Hi-Z state. I<sup>2</sup>C communication remains possible in shutdown mode and register bits states are retained.

If a latching fault condition has occurred (Over Temperature, Over Current or DC detect), the SDZ pin or I<sup>2</sup>C bit must toggle low before the fault register can be cleared. For more information on faults and recovery, see the *Faults and Status* section.

When the device exits shutdown mode (either by releasing the SDZ pin high or setting the  $I^2C$  SDZ register bit high), the device powers up the internal analog and digital blocks required for operation. If the  $I^2C$  SLEEP bit is set low (bit 1, reg 0x01), the device powers up the Class-D amplifier and begins the switching of the power stage. If the  $I^2C$  MUTE bit is set low (bit 4, reg 0x03), the device ramps up the volume to the current setting and begins playing audio.

If shutdown mode is asserted while audio is playing, the device ramps down the volume on the audio, stops the Class-D switching, puts the Class-D power stage output pins in a Hi-Z state and powers down the analog and digital blocks.

## 7.4.2 Sleep Mode

Sleep mode is similar to shutdown mode, except analog and digital blocks required to begin playing audio quickly remain powered up. Sleep mode operates as a *hard mute* where the Class-D amplifier stops switching, but the device does not power down completely. Entering sleep mode does not clear latching faults.

#### 7.4.3 Mode Timing

The time to enter or exit sleep or mute and the time to enter shudown are dominated by  $t_{VRMP}$ . 表 9 lists the timing parameters based on  $t_{VRMP}$ .

|            | 71 1                                                       |                   |  |  |  |  |  |

|------------|------------------------------------------------------------|-------------------|--|--|--|--|--|

| SAMPLE     | RAMP TIMES (t <sub>VRAMP</sub> ) FROM -100 dB to 0 dB (ms) |                   |  |  |  |  |  |

| RATE (kHz) | VOL_RAMP_RATE = 0                                          | VOL_RAMP_RATE = 1 |  |  |  |  |  |

| 44.1       | 72.6                                                       | 9.1               |  |  |  |  |  |

| 48         | 66.7                                                       | 8.3               |  |  |  |  |  |

| 88.2       | 36.3                                                       | 4.5               |  |  |  |  |  |

| 96         | 33.3                                                       | 4.2               |  |  |  |  |  |

表 9. Typical DVC Ramp Times

#### 7.4.4 Auto Sleep Mode

Auto sleep mode is an optional feature that automatically moves the amplifier from active mode to sleep mode when the device presents an idle audio input (i.e. zero value) to the SAIF for a prescribed number of samples. The device automatically returns to active mode when the device presents a non-idle audio input sample to the SAIF. Auto sleep mode takes advantage of the TAS5722L device's ability to rapidly enter and exit sleep mode from active mode. Because the device applies idle audio samples to the SAIF before entering sleep mode, a volume ramp can be avoided. When exiting sleep mode, the amplifier can resume switching before input sample has propagated through the signal path, which avoids any audible artifacts when resuming playback. AUTO\_SLEEP[1:0] (bits 4:3 in register 0x13) configures the number of idle samples required to enter auto sleep.

#### 7.4.5 Active Mode

If shutdown mode and sleep mode are not asserted, the device is in active mode. During active mode, audio playback is enabled.

#### 7.4.6 Mute Mode

When the  $I^2C_MUTE$  bit is set high (bit 4, reg 0x03) and the device is in active mode, the volume is ramped down and the Class-D amplifier continues to operate with an idle audio input.

#### 7.4.7 Faults and Status

During the power-up sequence, the power-on-reset circuit (POR) monitoring the DVDD pin domain releases all registers from reset (including the I<sup>2</sup>C registers) once DVDD is valid. The device does not exit shutdown mode until the PVDD pin has a valid voltage between the undervoltage lockout (UVLO) and overvoltage lockout (OVLO) thresholds. If DVDD drops below the POR threshold the device transitions into shutdown mode with all registers held in reset. If UVLO or OVLO thresholds are violated by PVDD, the device transitions into sleep mode, but registers are not forced into reset. Both of these conditions are non-latching and the device operates normally once supply voltages are valid again. The device can be reset only by reducing DVDD below the POR threshold.

The device transitions into sleep mode if it detects any faults with the SAIF clocks such as

- Invalid MCLK to LRCLK and BCLK to LRCLK ratios

- Invalid MCLK and LRCLK frequencies

- Halting of MCLK, BCLK or LRCLK clocks

Upon detection of a SAIF clock error, the device transitions into sleep mode as quickly as possible to limit the possibility of audio artifacts. Once all SAIF clock errors are resolved, the device volume ramps back to its previous playback state. During an SAIF clock error, the FAULTZ pin asserts low and the CLKE bit asserts high (register 0x08, bit 3).

While operating in shutdown mode, the SAIF clock error detect circuitry powers down and the CLKE bit reads high. This reading is not an indication of a SAIF clock error. If the device has not entered active mode after a power-up sequence or after transitioning out of shutdown mode, the FAULTZ pin pulses low for only approximately 10 µs every 350 µs. This action prevents a possible locking condition if the FAULTZ is connected to the SDZ pin to accomplish automatic recovery. Once the device has entered active mode one time (after power up or deassertion of shutdown mode), the SAIF clock errors pull the FAULTZ pin low continuously until the fault has cleared.

The device also monitors die temperature, power stage load current and amplifier output DC content and issues latching faults if any of these conditions occur. A die temperature of approximately 150°C causes the device to enter sleep mode and issue an over-temperature error (OTE) readable via I<sup>2</sup>C (bit 0, reg 0x08).

Sustained excessive DC content at the output of the Class-D amplifier can damage loudspeakers via voice coil heating. The amplifier has an internal circuit to detect significant DC content that forces the device into sleep mode. The device issues a DC detect error (DCE) readable via I<sup>2</sup>C (bit 1, reg 0x08).

If the Class-D amplifier load current exceeds the threshold set by the OC\_THRESH register bits (bits 5-4, reg 0x08), the device enters sleep mode and issues an overcurrent error (OCE) that is readable via I<sup>2</sup>C (bit 2, reg 0x08).