UCC29950

ZHCSDI3A - SEPTEMBER 2014-REVISED MARCH 2015

# UCC29950 CCM PFC 和 LLC 组合控制器

# 特性

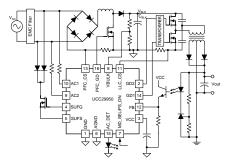

- 高效功率因数校正 (PFC) 和半桥谐振逻辑链路控制 (LLC) 组合控制器

- 连续导通模式 (CCM) 升压功率因数校正

- 支持自偏置或辅助(外部)偏置工作模式

- 完全内部补偿的 PFC 环路

- 3 步轻松设计 PFC 级 (设计电压反馈、电流反馈和功率级)

- 100kHz 固定 PFC 频率,具有抖动特性,可确保符 合 EMI 标准

- 真正的输入功率限制,独立于线路电压

- 固定 LLC 频率工作范围为 70kHz 至 350kHz

- 死区变化范围为 LLC 半桥功率级的整个负载范围, 可扩展零电压开关 (ZVS) 范围

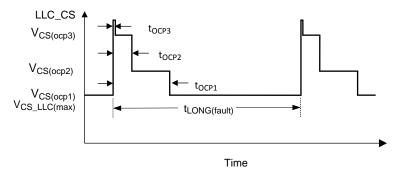

- 三级 LLC 过流保护

- Hiccup 工作模式,可提供连续过载和短路保护

- 低待机功耗, 由高压启动金属氧化物半导体场效应 晶体管 (MOSFET) 和 X-Cap 放电功能共同实现

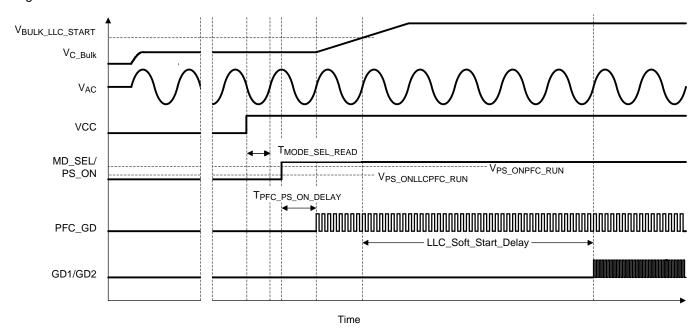

- 内置软启动和转换器排序功能, 可简化设计

- 交流线路欠压保护,具有故障指示器

- PFC 总线过压和欠压保护

- 过温保护

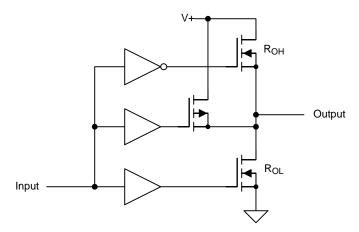

- 用于扩展功率级的外部栅极驱动器

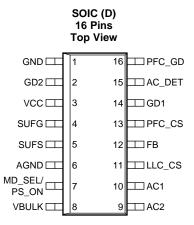

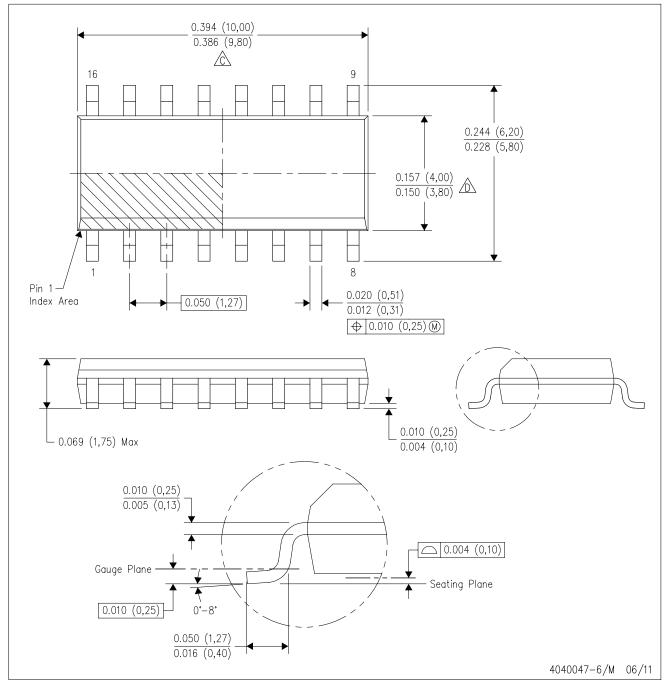

- 小外形尺寸集成电路 (SOIC)-16 封装

# 2 应用

- 离线交流-直流服务器电源(通过 80 PLUS® 铜牌/ 银牌/金牌认证)

- 工业 DIN 导轨和开放式电源

- 游戏机和打印机电源

- 高密度适配器

- 照明驱动器

## 3 说明

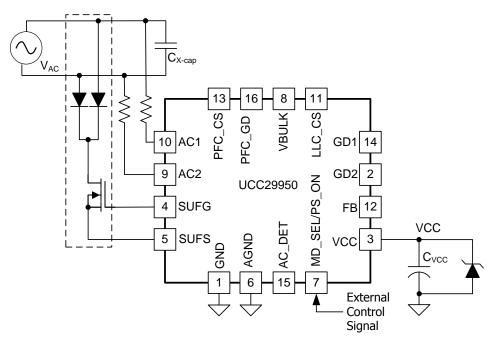

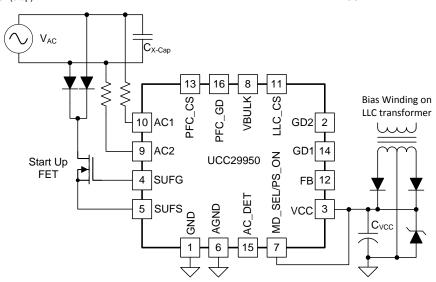

UCC29950 可为交流-直流转换器提供 LLC 转换器级 和 CCM 升压功率因数校正 (PFC) 级,从而实现全部 控制功能。 这款转换器经过了优化,非常便于使用。

凭借专有 CCM PFC 算法,系统能够获得高效率、更 小的转换器尺寸以及高功率因数等诸多优势。 集成的 LLC 控制器可实现高效直流-直流转换级,利用软开关 来降低电磁干扰 (EMI) 噪声。 这款组合控制器兼具 PFC 控制和 LLC 控制,使得控制算法能够充分利用来 自两级的信息。

该控制器包含一个启动控制电路, 此电路采用耗尽型 MOSFET 且内置器件电源管理功能,可最大程度降低 外部元件需求,并且有助于降低系统实现成本。

为进一步降低待机功耗,该控制器还集成了 X-Cap 放 电电路。 UCC29950 实现了一整套系统保护功能,其 中包括交流线路欠压保护、PFC 总线欠压 PFC 和 LLC、过流保护和热关断保护。

## 器件信息(1)

| 器件型号     | 封装             | 封装尺寸 (标称值)      |

|----------|----------------|-----------------|

| UCC29950 | SOIC 16 引脚 (D) | 9.90mm x 6.00mm |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

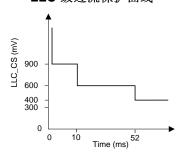

## LLC 级过流保护曲线

简化电路原理图

|             |                                                                                                                                                                                                                                                                                                                                                                   | į.            |                                                                               |         |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------------------------------------------------------------------------------|---------|

| 1<br>2      | 特性                                                                                                                                                                                                                                                                                                                                                                |               | <ul><li>7.3 Feature Description</li><li>7.4 Device Functional Modes</li></ul> |         |

| 3<br>4<br>5 | 说明                                                                                                                                                                                                                                                                                                                                                                |               | Application and Implementation  8.1 Application Information                   | 30<br>5 |

| 6           | Specifications         6           6.1 Absolute Maximum Ratings         6           6.2 Storage Conditions         6           6.3 ESD Ratings         6           6.4 Recommended Operating Conditions         7           6.5 Thermal Information         7           6.6 Electrical Characteristics         8           6.7 Typical Characteristics         11 | 9<br>10<br>11 | Power Supply Recommendations                                                  | 59<br>  |

| 7           | Detailed Description         13           7.1 Overview         13           7.2 Functional Block Diagram         14                                                                                                                                                                                                                                               | 12            | 11.4 术语表                                                                      |         |

# 4 修订历史记录

| Changes from Original (September 2014) to Revision A | Page |

|------------------------------------------------------|------|

| • 已更改 销售状态从产品定制到产品目录。                                | 1    |

# 5 Pin Configuration and Functions

## **Pin Functions**

| PI               | IN  | 1/0 | DESCRIPTION                                                                                                                                                                                                                             |  |  |  |

|------------------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME             | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                             |  |  |  |

| GND              | 1   | =   | Power ground. Connect all the gate driver pulsating current returns to this pin.                                                                                                                                                        |  |  |  |

| GD2              | 2   | 0   | Gate drive output for LLC stage MOSFET. The typical peak current is 1-A source, 1.6-A sink $(C_{LOAD} = 1 \text{ nF})$                                                                                                                  |  |  |  |

| VCC              | 3   | -   | Bias supply input.                                                                                                                                                                                                                      |  |  |  |

| SUFG             | 4   | 0   | Start-up MOSFET gate drive output. Leave open circuit if not used.                                                                                                                                                                      |  |  |  |

| SUFS             | 5   | I   | Start-up MOSFET Source. Connect to VCC if not used.                                                                                                                                                                                     |  |  |  |

| AGND             | 6   | =   | Signal ground. Connect all device control signal returns to this ground.                                                                                                                                                                |  |  |  |

| MD_SEL/PS_<br>ON | 7   | ı   | <ol> <li>Dual function pin:</li> <li>Mode Select Function (MD_SEL): Select self bias or Aux bias mode of operation.</li> <li>Power Supply On Function (PS_ON): Stop/start control of PFC and LLC stages, Aux Bias mode only.</li> </ol> |  |  |  |

| VBULK            | 8   | 1   | Voltage sense input for PFC stage output.                                                                                                                                                                                               |  |  |  |

| AC2              | 9   | ı   | AC line voltage detection. Connect 9.3 MΩ between AC line and this pin.                                                                                                                                                                 |  |  |  |

| AC1              | 10  | ı   | AC line voltage detection. Connect 9.3 MΩ between AC line and this pin.                                                                                                                                                                 |  |  |  |

| LLC_CS           | 11  | ı   | Current sense input for the LLC stage.                                                                                                                                                                                                  |  |  |  |

| FB               | 12  | I   | Feedback signal input for LLC stage.                                                                                                                                                                                                    |  |  |  |

| PFC_CS           | 13  | 1   | Current sense input for the PFC stage.                                                                                                                                                                                                  |  |  |  |

| GD1              | 14  | 0   | Gate drive output for LLC stage MOSFET. The typical peak current is 1-A source, 1.6-A sink $(C_{LOAD} = 1 \text{ nF})$ .                                                                                                                |  |  |  |

| AC_DET           | 15  | 0   | AC line voltage fail signal output, for system use.                                                                                                                                                                                     |  |  |  |

| PFC_GD           | 16  | 0   | The typical peak current is 0.6-A source, 1.3-A sink (C <sub>LOAD</sub> = 1 nF).                                                                                                                                                        |  |  |  |

## 5.1 Detailed Pin Descriptions

### 5.1.1 VCC

The VCC pin is the power supply input terminal to the device. This pin should be decoupled with a 10-µF ceramic bypass capacitor in both Aux Bias and Self Bias Modes. An additional hold-up capacitor is needed at this pin if operating in Self Bias Mode.

## 5.1.2 MD SEL/PS ON

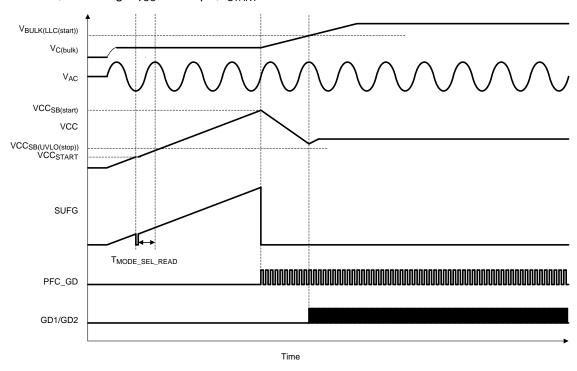

MD\_SEL/PS\_ON pin. This pin can be used to make the UCC29950 operate in Self Bias or Auxiliary Bias Mode. If MD\_SEL/PS\_ON pin is high during start up the controller enters Self Bias Mode. In this mode, the capacitor on the device's VCC rail is charged by an external depletion mode MOSFET connected at the SUFS and SUFG pins. Once the VCC rail reaches an appropriate operating voltage, the FET is turned off and the VCC rail is then supplied from an auxiliary winding on the LLC transformer. This avoids the standing or static losses incurred if a drop resistor from rectified AC line were used to charge the VCC rail during startup.

If the MD\_SEL/PS\_ON pin is held low for at least 10 ms during start up the UCC29950 enters Aux Bias Mode. Once this time has passed this pin may be used to turn on the PFC stage on its own or both the PFC and LLC stages according to the values given in the MD\_SEL/PS\_ON part of the Electrical Characteristics.

## 5.1.3 SUFG, SUFS

The SUFG and SUFS are the control pins for an external start-up depletion mode FET. The use of a switched device here eliminates the static power dissipation in a conventional resistive start-up approach where a drop resistor from the rectified AC line to VCC is typically used. As a result standby power consumption is reduced.

Connect the FET gate to SUFG and its source to SUFS. The drain of the FET is connected to the rectified AC voltage. SUFG and SUFS control the initial charging of the capacitor on the VCC rail during start-up in the Self-Bias mode of operation. In this mode SUFG tracks SUFS as  $C_{VCC}$  is charged and VCC rises. When VCC reaches VCC<sub>SB(start)</sub> (typically 16.2 V) SUFG goes low. This turns the start-up FET off and the PFC and LLC gate outputs start running. SUFG remains low unless VCC falls below VCC<sub>SB\_UVLO(stop)</sub> (typically 7.9 V) or an X-Cap discharge is required. If VCC falls below VCC<sub>SB\_UVLO(stop)</sub> then SUFG goes high to turn the start-up FET on and recharge  $C_{VCC}$  back up to VCC<sub>SB\_START</sub>.

SUFG and SUFS also provide an X-Cap discharge function in both Aux Bias and Self Bias Modes. This function is described fully in Active X-Cap Discharge.

If the UCC29950 is used in Aux Bias Mode then VCC is supplied by an external source and the external depletion mode FET is used only to provide the X-Cap discharge function. SUFG is at 0 V after a time  $T_{\text{MODE\_SEL\_READ}}$  has elapsed during power up after  $C_{\text{VCC}}$  exceeds VCC<sub>START</sub>. SUFG goes high whenever an X-Cap discharge is required. If the start up FET is not used and X-Cap discharge is not desired then SUFS should be connected to VCC and SUFG should be left open circuit.

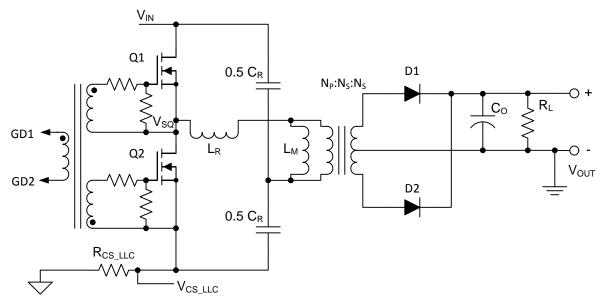

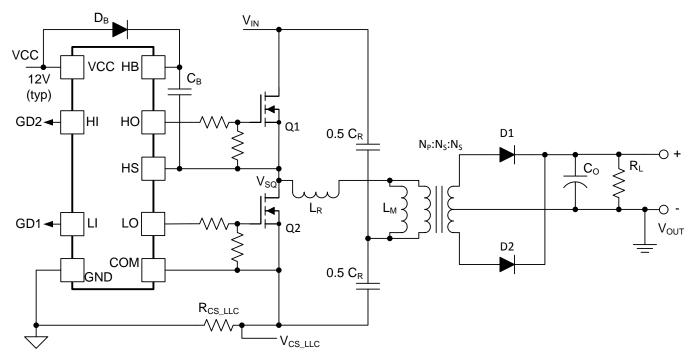

## 5.1.4 GD1, GD2

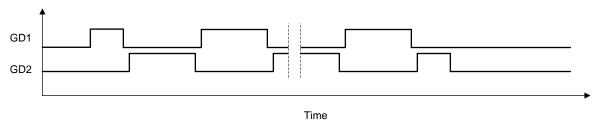

GD1 and GD2 are the LLC gate drive outputs for the LLC half-bridge power MOSFETs. A gate drive transformer or other suitable device is required to generate a floating drive for the high-side MOSFET. The first and last LLC gate drive pulses are normally half width and appear on GD1 and GD2 respectively. If the LLC\_OCP3 level is exceeded then the final pulse is of normal width. The typical peak current is 1-A source, 1.6-A sink (1-nF load).

## **Detailed Pin Descriptions (continued)**

#### 5.1.5 GND

GND is the power ground for the device. Connect all the gate-driver pulsating current returns to this pin.

#### 5.1.6 AGND

AGND is the signal ground for device control signals. Connect all control signal returns to this pin.

## 5.1.7 LLC\_CS

LLC\_CS is the LLC stage current sense input. LLC\_CS is used for LLC stage over-load protection. The load current is reflected to the primary side of the transformer where it is sensed using a resistor. The UCC29950 senses the LLC stage input current level and enters the over-current protection Shut-Down Mode when the current-sense signal exceeds the current and time thresholds described in LLC Three Level Over-Current Protection . The controller tries to resume operation at 1-s intervals.

#### 5.1.8 FB

FB is the LLC stage control-loop feedback input. Connect the opto-coupler emitter to this pin. The FB pin is the input to the internal VCO. The VCO generates the switching frequency of the LLC converter. GD1 and GD2 stop switching if this pin is driven above  $V_{FB\_LLC(off)}$  (typically 3.75 V) and resume operation when it falls below  $V_{FB(max)}$  (typically 3.0 V). If this pin is held below  $V_{FB(min)}$  (typically 200 mV) the GD1 and GD2 outputs runs at their minimum frequency.

### 5.1.9 PFC GD

PFC\_GD is the gate-driver output for a PFC MOSFET. Connect the PFC MOSFET gate through a resistor to control its switching speed. Because of the limited driving capability an external gate driver might be needed to support certain power MOSFET input capacitance conditions. The typical peak current is 0.6-A source, 1.3-A sink ( $C_{LOAD} = 1 \text{ nF}$ ).

### 5.1.10 PFC CS

PFC\_CS is the current sense input for the PFC stage. It is recommended to add a current-limiting resistor between the current-sense resistor and current-sense pin, to prevent damage during inrush conditions. A  $1-k\Omega$  resistor normally suffices. The UCC29950 implements a new hybrid average current-control method which controls the average current but uses the peak PFC\_CS signal to terminate each switching cycle (see Hybrid PFC Control Loop). Correct PCB layout is important to ensure that the signal at this pin is an accurate representation of the current being controlled.

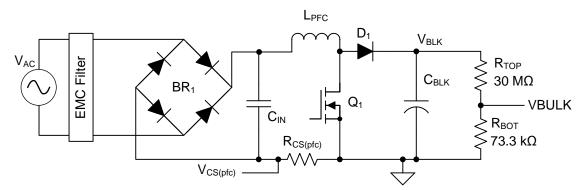

## 5.1.11 VBULK

The VBULK pin is used for PFC output-voltage sensing. Connect the sensing resistors to this pin. The upper resistor in the potential divider must be 30 M $\Omega$  and the lower resistor must be 73.3 k $\Omega$ . The high impedance reduces the static power dissipation.

#### 5.1.12 AC1, AC2

AC1 and AC2 are the AC line voltage sensing inputs. The UCC29950 uses differential sensing for more accurate measurement of line voltage. These pins must be connected to the two line inputs via  $9.3-M\Omega$  resistors.

## 5.1.13 AC DET

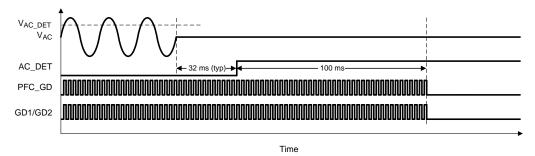

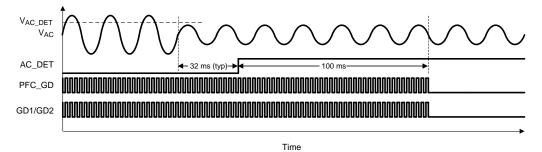

The AC\_DET is a system-level signal which may be used for indication and system control. AC\_DET goes high if the instantaneous AC voltage remains below the brownout level for longer than 32 ms. An opto-coupler can be used to send a signal to a system supervisor device so that appropriate action can be taken. In order to provide hold-up time to the system, the power stages continue to operate for 100 ms after AC\_DET goes high. This behavior is shown in Figure 10, Figure 11 and Figure 12.

# 6 Specifications

## 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                                   |                                                | MIN  | MAX      | UNIT |

|-----------------------------------|------------------------------------------------|------|----------|------|

| Supply Voltage                    | VCC                                            | -0.3 | 20       | V    |

| Continuous Input<br>Voltage Range | LLC_CS                                         | -0.3 | 4.5      | V    |

|                                   | FB, AC1, AC2, VBULK, MD_SEL/PS_ON              | -0.3 | VCC+0.3  | V    |

|                                   | AC_DET                                         | 0    | 4.5      | V    |

|                                   | SUFS                                           | -0.3 | 20       | V    |

|                                   | SUFG                                           | -0.3 | SUFS+0.3 | V    |

|                                   | GD1, GD2, PFC_GD                               | -0.5 | VCC+0.5  | V    |

|                                   | PFC_CS                                         | -1.3 | 4.5      | V    |

| Continuous Input<br>Current Range | PFC_CS                                         |      | ±15      | mA   |

| T <sub>SOL</sub>                  | Lead temperature (10 s)                        |      | 260      | °C   |

| Operational Junction              | erational Junction Temperature, T <sub>J</sub> |      | 125      | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 Storage Conditions

|                  |                           | MIN | MAX | UNIT |

|------------------|---------------------------|-----|-----|------|

| T <sub>stg</sub> | Storage temperature range | -40 | 150 | °C   |

## 6.3 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 500-V HBM is possible with the necessary precautions.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. Manufacturing with less than 250-V CDM is possible with the necessary precautions.

# 6.4 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                           |                                | MIN | NOM MAX | UNIT |

|---------------------------|--------------------------------|-----|---------|------|

| VCC                       | Supply voltage range           | 11  | 18      | V    |

| $V_{FB}$                  | FB pin voltage range           | 0   | VCC     | V    |

| V <sub>MD_SEL/PS_ON</sub> | MD_SEL/PS_ON pin voltage range | 0   | VCC     | V    |

| RL1/RL2                   | Line sensing resistors         |     | 9.3     | ΜΩ   |

## 6.5 Thermal Information

|                      |                                              | UCC29950 |      |

|----------------------|----------------------------------------------|----------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | SOIC (D) | UNIT |

|                      |                                              | 16 PINS  |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 78.9     |      |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 40.3     |      |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 36.3     | °C/W |

| ΨЈТ                  | Junction-to-top characterization parameter   | 8.9      |      |

| ΨЈВ                  | Junction-to-board characterization parameter | 36.0     |      |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

## 6.6 Electrical Characteristics

-40°C < T<sub>J</sub> < 125°C<sup>(1)</sup>, VCC = 12 V, all voltages are with respect to AGND (unless otherwise noted)

|                                  | PARAMETER                                                                                                                                                                                                         | TEST CONDITIONS                                                                                                | MIN  | TYP  | MAX  | UNIT |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|------|------|------|------|

| VCC Bias Suppl                   | y (Self Bias Mode)                                                                                                                                                                                                |                                                                                                                |      |      |      |      |

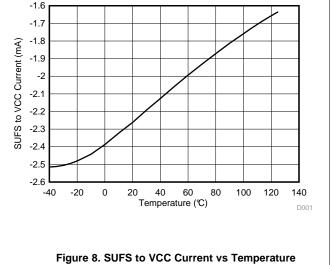

| I <sub>SUFS</sub>                | Charging current into V <sub>CC</sub>                                                                                                                                                                             | SUFS = 7.5 V, VCC = 4 V                                                                                        | -1   | -2   | -4   | mA   |

| VCC <sub>SB(start)</sub>         | In Self Bias mode, the controller will not start PFC and LLC gate drive outputs until the start up FET has charged the capacitance on the VCC pin above this level                                                | MD_SEL/PS_ON = VCC at power-up (self bias mode)                                                                | 15.0 | 16.2 | 17.4 | V    |

| VCC <sub>SB_UVLO(stop)</sub>     | In Self Bias mode, VCC must be greater than this level to allow the controller to continue to output the PFC and LLC gate drives.                                                                                 | VCC falling Self Bias Mode                                                                                     | 7.3  | 7.9  | 8.5  |      |

| VCC Bias Supply                  | y (Aux Bias Mode)                                                                                                                                                                                                 |                                                                                                                |      |      |      |      |

| VCC <sub>START</sub> (2)         | Controller logic starts at this VCC voltage                                                                                                                                                                       | VCC rising                                                                                                     | 4.4  | 6    | 7.0  |      |

| VCC <sub>STOP</sub> (2)          | Controller logic stops at this VCC voltage                                                                                                                                                                        | VCC falling                                                                                                    | 3.7  | 5.0  | 5.8  |      |

| VCC <sub>AB_UVLO(start</sub> )   | In Aux Bias Mode, VCC must be greater than this level to allow the controller to start the PFC and LLC gate drive outputs.                                                                                        | VCC rising MD_SEL/PS_ON<br>= 0 V at power-up (Aux Bias<br>Mode)                                                | 10.0 | 10.5 | 10.9 | V    |

| VCC <sub>AB_UVLO(stop)</sub>     | In Aux Bias Mode, VCC must be greater than this level to allow the controller to continue to output the PFC and LLC gate drives.                                                                                  | VCC falling Aux Bias Mode                                                                                      | 9.1  | 9.6  | 10.0 |      |

| VCC Supply Cur                   | rent                                                                                                                                                                                                              |                                                                                                                |      |      |      |      |

| ICC <sub>ENABLE</sub>            | Device is Enabled and providing PFC & LLC gate drive outputs                                                                                                                                                      | GD1, GD2 at LLC <sub>FMAX</sub> . PFC_GD at f <sub>PFC</sub> (100 kHz nom). GD1, GD2 and PFC_GD pins unloaded. | 7.5  | 8.0  | 18.3 | mA   |

| MD_SEL/PS_ON                     | , Mode Select Function at Power Up                                                                                                                                                                                | •                                                                                                              |      |      |      |      |

| V <sub>MODE_SELSB</sub>          | Minimum voltage on the MD_SEL/PS_ON pin that will select Self Bias mode on power up (see Device Functional Modes).                                                                                                |                                                                                                                | 1.1  | 1.6  | 2.1  | V    |

| T <sub>MODE_SEL_READ</sub>       | After VCC pin exceeds VCC <sub>START</sub> . This is the minimum time that the MD_SEL/PS_ON pin must remain below V <sub>MODE_SELSB</sub> to ensure that Aux Bias Mode is selected (see Device Functional Modes). |                                                                                                                | 10   |      |      | ms   |

| MD_SEL/PS_ON                     | , Power Supply On Function, Aux Bias Mode On                                                                                                                                                                      | ly                                                                                                             |      |      |      |      |

| V <sub>PS_ONPFC_RUN</sub>        | Minimum voltage on the MD_SEL/PS_ON pin that causes PFC stage to run <sup>(3)</sup>                                                                                                                               |                                                                                                                | 20   | 25   | 33   | %VCC |

| V <sub>PS_ONLLCPFC_R</sub><br>UN | Minimum voltage on the MD_SEL/PS_ON pin that causes PFC and LLC stages to run (3)                                                                                                                                 |                                                                                                                | 66   | 75   | 85   | %VCC |

| AC_DET                           |                                                                                                                                                                                                                   |                                                                                                                |      |      |      |      |

| V <sub>OH_TP_LZ</sub>            | AC_DET output high                                                                                                                                                                                                | $I_{(AC\_DET)} = -1 \text{ mA}$                                                                                | 2.5  | 3.1  | 4.1  | V    |

| V <sub>OL</sub>                  | AC_DET output low                                                                                                                                                                                                 | I <sub>(AC_DET)</sub> = 1 mA                                                                                   | 19   | 35   | 80   | mV   |

| I <sub>O(max_source)</sub>       | AC_DET source current                                                                                                                                                                                             | V <sub>OUT</sub> > 2.4 V                                                                                       |      |      | -1.6 | mA   |

| I <sub>O(max_sink)</sub>         | AC_DET sink current                                                                                                                                                                                               | V <sub>OUT</sub> < 0.5 V                                                                                       |      |      | 6.0  | mA   |

The device has been characterized over the entire temperature range during development. Individual devices may enter temperature shutdown ( $T_{SD}$ ) at  $T_J$  lower than 125°C. (1)

<sup>(2)</sup> VCC<sub>START</sub>is always greater than VCC<sub>STOP</sub>.

(3) Threshold voltage will track VCC and is therefore specified as a percentage of VCC.

# **Electrical Characteristics (continued)**

-40°C <  $T_J$  < 125°C<sup>(1)</sup>, VCC = 12 V, all voltages are with respect to AGND (unless otherwise noted)

|                                      | PARAMETER                                                                                                                                                                                                                      | TEST CONDITIONS                                                 | MIN   | TYP   | MAX   | UNIT              |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-------|-------|-------|-------------------|

| VBULK, PFC OU                        | TPUT VOLTAGE                                                                                                                                                                                                                   |                                                                 |       |       |       |                   |

| V <sub>BULK(ovp)</sub>               | PFC output overvoltage protection (auto recovery)                                                                                                                                                                              |                                                                 | 1.06  | 1.10  | 1.14  | V                 |

| V <sub>BULK(reg)</sub>               | V <sub>BULK</sub> regulation set-point                                                                                                                                                                                         |                                                                 | 0.907 | 0.940 | 0.973 | V                 |

| V <sub>BULK(Ilc_start)</sub>         | LLC operation start threshold                                                                                                                                                                                                  |                                                                 | 0.70  | 0.73  | 0.77  | V                 |

| V <sub>BULK(IIc_stop)</sub>          | LLC operation stop threshold                                                                                                                                                                                                   |                                                                 | 0.45  | 0.49  | 0.53  | V                 |

|                                      | INE SENSING FOR PFC                                                                                                                                                                                                            | ,                                                               |       |       | '     |                   |

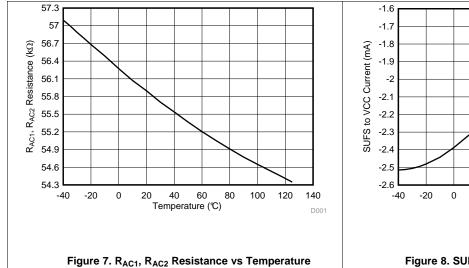

| R <sub>AC1</sub>                     | AC1 pin resistance to AGND                                                                                                                                                                                                     | AC1 pin                                                         | 45    | 60    | 71    |                   |

| R <sub>AC2</sub>                     | AC2 pin resistance to AGND                                                                                                                                                                                                     | AC2 pin                                                         | 45    | 60    | 71    | kΩ                |

| I <sub>AC(det)</sub> (4) (5)         | AC_DET is active HIGH when I <sub>AC</sub> is below this level                                                                                                                                                                 | Force current into AC1 or AC2 pins. Unused pin input at 0 V.    | 7.03  | 7.48  | 7.93  |                   |

| I <sub>AC(low_falling)</sub> (4) (5) | PFC stage stops 100 ms after I <sub>AC</sub> is at or below this level                                                                                                                                                         | Force current into AC1 or AC2 pins. Unused pin input at 0 V.    | 7.03  | 7.48  | 7.93  |                   |

| I <sub>AC(low_rising)</sub> (4) (5)  | PFC stage is allowed to start when I <sub>AC</sub> is at or above this level                                                                                                                                                   | Force current into AC1 or AC2 pins. Unused pin input at 0 V.    | 8.04  | 8.55  | 9.1   |                   |

| AC(high_falling) (4) (5              | PFC stage restarts if $I_{\mbox{\scriptsize AC}}$ falls below this level. No soft-start                                                                                                                                        | Force current into AC1 or AC2 pins. Unused pin input at 0 V.    | 30.7  | 32.0  | 33.3  | μA <sub>RMS</sub> |

| I <sub>AC(high_rising)</sub> (4) (5) | PFC stage stops if I <sub>AC</sub> is at or above this level                                                                                                                                                                   | Force current into AC1 or AC2 pins. Unused pin input at 0 V.    | 31.8  | 33.1  | 34.4  |                   |

| I <sub>AC(halt)</sub> (4) (5)        | PFC and LLC stages stop if $\ensuremath{I_{AC}}$ is at or above this level                                                                                                                                                     | Force current into AC1 or AC2 pins. Unused pin input at 0 V.    | 32.8  | 34.2  | 35.6  |                   |

| PFC_CS, PFC C                        | URRENT SENSE                                                                                                                                                                                                                   |                                                                 |       |       |       |                   |

| V <sub>PFCCS(cav_max)</sub>          | Maximum voltage at PFC_CS pin, (ignoring signal ripple due to inductor ripple current) that determines maximum power delivered. Used to determine R <sub>CS_PFC</sub> . (see PFC Stage Current Sensing Figure 13 and Figure 6) |                                                                 | -200  | -225  | -250  | mV                |

| V <sub>PFCCS(max)</sub>              | Maximum voltage at PFC_CS pin                                                                                                                                                                                                  | VBULK pin = 800 mV,<br>$ V_{AC1} - V_{AC2}  = V_{AC\_PEAK}$ (6) | -570  | -800  | -950  |                   |

| PFC_GD, PFC G                        | ATE DRIVER                                                                                                                                                                                                                     |                                                                 |       |       |       |                   |

| V <sub>HI(pfc_2mA)</sub>             | PFC_GD high level                                                                                                                                                                                                              | $I_{O(PFC\_GD)} = -2 \text{ mA}$                                | 11.5  | 11.8  | 12.0  | V                 |

| V <sub>HI(pfc_75mA)</sub>            | PFC_GD high level                                                                                                                                                                                                              | $I_{O(PFC\_GD)} = -75 \text{ mA}$                               | 8.5   | 9.5   | 10.5  | V                 |

| $R_{PFC(gd\_hi)}$                    | PFC_GD pull-up resistance                                                                                                                                                                                                      | $I_{O(PFC\_GD)} = -50 \text{ mA}$                               |       | 14    | 25    | Ω                 |

| $R_{PFC(gd\_lo)}$                    | PFC_GD pull-down resistance                                                                                                                                                                                                    | $I_{O(PFC\_GD)} = 75 \text{ mA}$                                |       | 4.4   | 10    | 7.2               |

| t <sub>R(pfc)</sub>                  | PFC_GD rise time                                                                                                                                                                                                               | Capacitive load of 1.0 nF on PFC_GD pin, 20% to 80%             |       | 30    | 45    | ne                |

| t <sub>F(pfc)</sub>                  | PFC_GD fall time                                                                                                                                                                                                               | Capacitive load of 1.0 nF on PFC_GD pin, 20% to 80%             |       | 10    | 25    | ns                |

| f <sub>PFC</sub>                     | Switching frequency                                                                                                                                                                                                            | Includes dithering of ±2 kHz at nominal 333-Hz rate.            | 87    | 98    | 109   | kHz               |

<sup>(4)</sup> These are specified at 25°C. The relative levels for these specifications track each other. The equivalent line voltages are given in Table 3, assuming a source impedance of 9.3 M $\Omega$ .

<sup>(5)</sup> This is the current into the AC1 or AC2 pins.

(6) Tested at peak of line voltage or 90° from zero crossing.

# **Electrical Characteristics (continued)**

-40°C <  $T_J$  < 125°C<sup>(1)</sup>, VCC = 12 V, all voltages are with respect to AGND (unless otherwise noted)

|                                         | PARAMETER                                                                           | TEST CONDITIONS                                                                                                                     | MIN  | TYP  | MAX  | UNIT  |

|-----------------------------------------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| FB, LLC Contr                           | ol Loop Feedback                                                                    |                                                                                                                                     |      |      |      |       |

| V <sub>FB(min)</sub> <sup>(7)</sup>     | Minimum voltage on FB pin where LLC frequency is modulated                          | Below V <sub>FB_MIN</sub> , LLC frequency is LLC <sub>Fmin</sub>                                                                    | 0.17 | 0.2  | 0.23 |       |

| V <sub>FB(max)</sub> <sup>(7)</sup>     | Maximum voltage on FB pin where LLC frequency is modulated                          | Between V <sub>FB_MAX</sub> , and V <sub>FB_LLC_OFF</sub> LLC frequency is LLC <sub>Fmax</sub>                                      | 2.90 | 3    | 3.10 | V     |

| V <sub>FB(IIc_off)</sub> <sup>(7)</sup> | Voltage on FB pin above which LLC gate drive terminated                             | Once V <sub>FB</sub> exceeds V <sub>FB_LLC_OFF</sub> , V <sub>FB</sub> must fall below V <sub>FB_MAX</sub> to resume switching      | 3.62 | 3.75 | 3.88 |       |

| LLC <sub>FMIN</sub> <sup>(7)</sup>      | Minimum LLC switching frequency                                                     |                                                                                                                                     | 63.7 | 70   | 74.8 | 1.11- |

| LLC <sub>FMAX</sub> <sup>(7)</sup>      | Maximum LLC switching frequency                                                     |                                                                                                                                     | 321  | 350  | 378  | kHz   |

| LLC <sub>T(dead)</sub> (8)              | Time for which GD1 and GD2 are both low during LLC operation at LLC <sub>FMIN</sub> | LLC dead-time at minimum switching frequency.                                                                                       | 224  | 300  | 388  | ns    |

| R <sub>FB</sub>                         | Internal resistance from FB pin to AGND                                             |                                                                                                                                     | 45   | 60   | 71   | kΩ    |

| LLC_CS, LLC                             | Current Sense                                                                       | •                                                                                                                                   |      |      |      |       |

| V <sub>CS(ocp3)</sub> <sup>(9)</sup>    | LLC Overcurrent threshold level three                                               | If this level is exceeded the PFC and LLC stages will stop for t <sub>LONG(fault)</sub> . Restart with a normal soft-start sequence | 0.87 | 0.9  | 0.94 | ٧     |

| V <sub>CS(IIc_max)</sub>                | Voltage at LLC_CS pin at 100% of full load                                          |                                                                                                                                     | 0.27 | 0.30 | 0.33 |       |

| FAULT Section                           | n                                                                                   |                                                                                                                                     |      |      | 1.   |       |

| t <sub>LONG(fault)</sub>                | Recovery time after long fault                                                      |                                                                                                                                     | 0.9  | 1.0  | 1.5  | S     |

| t <sub>SHORT(fault)</sub>               | Recovery time after short fault                                                     |                                                                                                                                     | 90   | 100  | 150  | ms    |

| GD1, GD2, LL0                           | C GATE Drive Output                                                                 |                                                                                                                                     |      |      | 1    |       |

| V <sub>GD(hi_2mA)</sub>                 | GD1, GD2 output high level                                                          | $I_{O(GDx)} = -2 \text{ mA}$                                                                                                        | 11.5 | 11.8 | 12   | .,    |

| V <sub>GD(hi_75mA)</sub>                | GD1, GD2 output high level                                                          | $I_{O(GDx)} = -75 \text{ mA}$                                                                                                       | 9.3  | 10.1 | 10.9 | V     |

| R <sub>GD(hi)</sub>                     | GD1, GD2 gate driver pull-up resistance                                             | $I_{O(GDx)} = -50 \text{ mA}$                                                                                                       |      | 5.8  | 10.5 | _     |

| R <sub>GD(lo)</sub>                     | GD1, GD2 gate driver pull-down resistance                                           | $I_{O(GDx)} = 75 \text{ mA}$                                                                                                        |      | 1.6  | 5    | Ω     |

| t <sub>r(Ilcgd)</sub>                   | LLC gate driver rise time                                                           | Capacitive load of 1 nF on GD1, GD2 pins                                                                                            |      | 12   | 30   |       |

| t <sub>f(Ilcgd)</sub>                   | LLC gate driver fall time                                                           | capacitive load of 1 nF on GD1, GD2 pins (20% to 80%)                                                                               |      | 11   | 25   | ns    |

| Thermal Shuto                           | down                                                                                |                                                                                                                                     |      |      |      |       |

| T <sub>SD</sub>                         | Thermal shutdown temperature                                                        |                                                                                                                                     |      |      | 125  | 00    |

| T <sub>ST</sub>                         | Start / restart temperature                                                         |                                                                                                                                     |      | 113  |      | °C    |

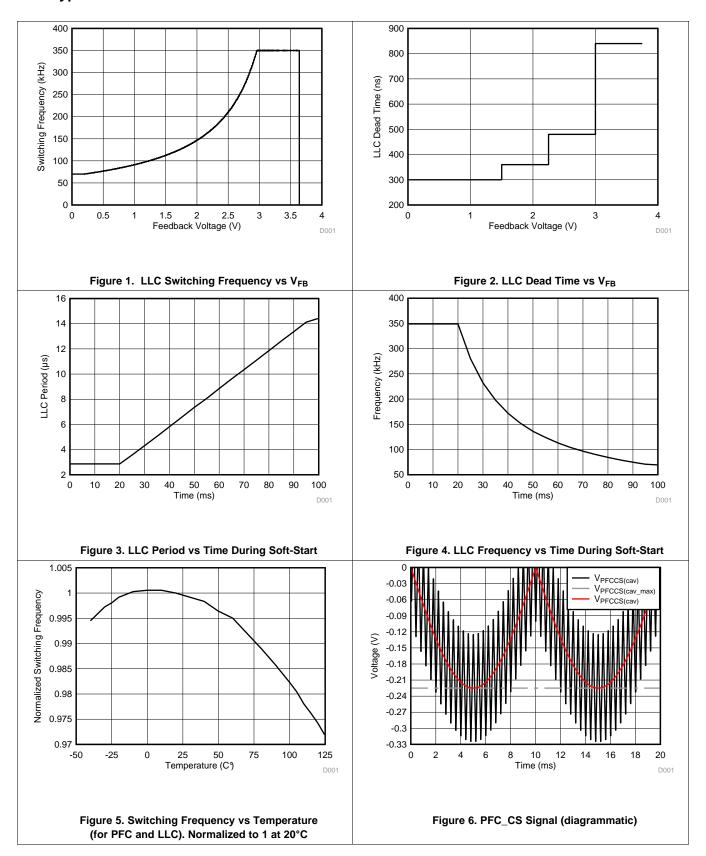

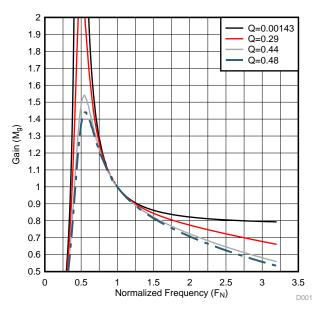

<sup>(7)</sup> Refer to Figure 1.

<sup>(8)</sup> Refer to Figure 2.

(9) Refer to Table 4 for other LLC Stage Over-Current Protection Levels.

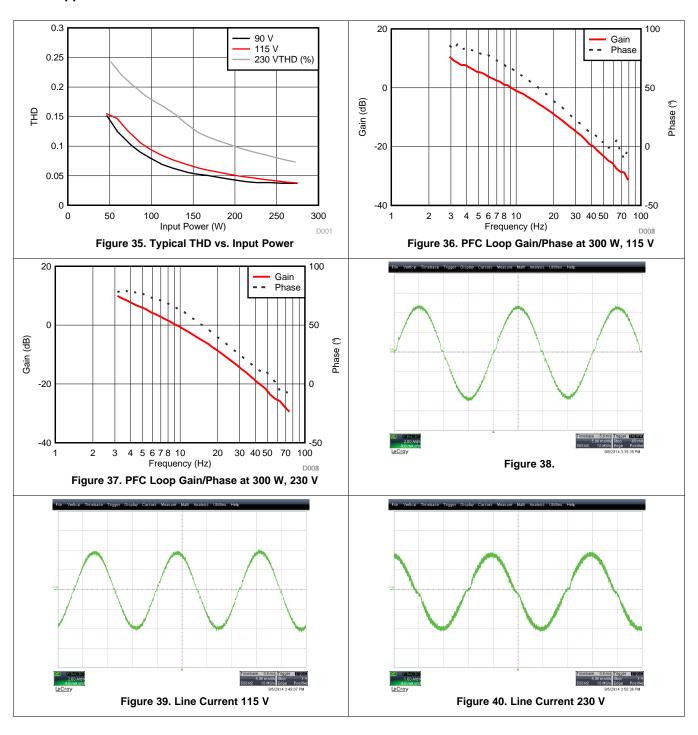

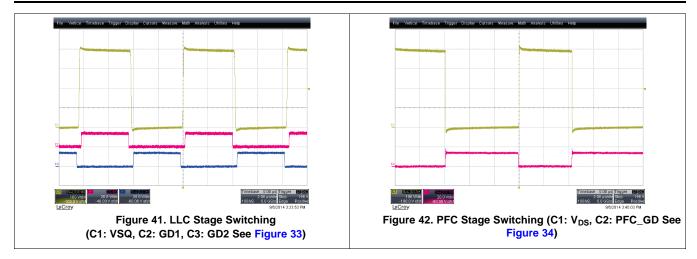

## 6.7 Typical Characteristics

# **Typical Characteristics (continued)**

# 7 Detailed Description

#### 7.1 Overview

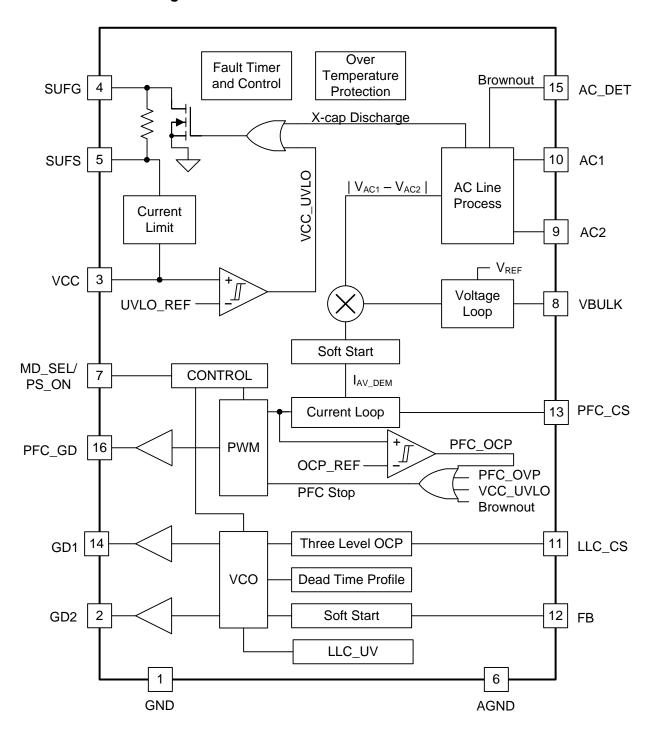

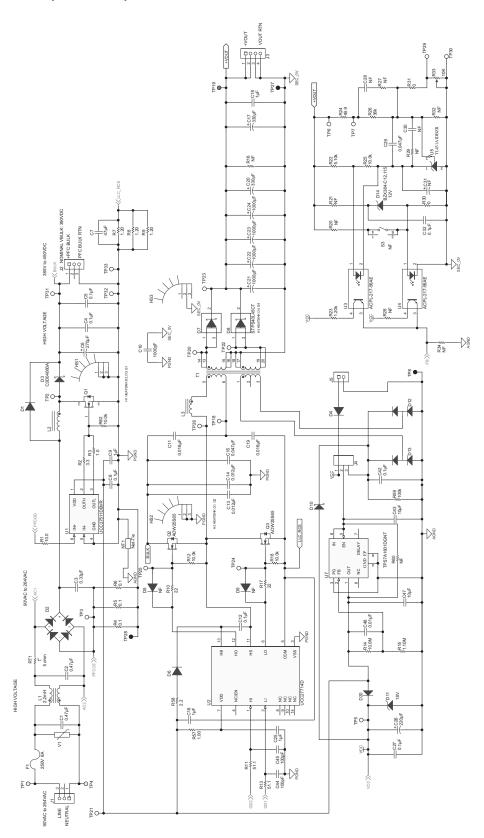

The UCC29950 combines all the functions necessary to control a Boost PFC and LLC power system. It is packaged in an SOIC-16 package. The SUFG and SUFS pins allow the system designer to use an external depletion mode MOSFET to provide start up power instead of using a dissipative resistor. The use of high-impedance voltage sensing networks further reduces standby power. The combo device uses information from both PFC and LLC stages to optimize the system efficiency, transient response and standby power. The controller can be operated with bias current supplied from a small external PSU (Aux Bias) or from a winding on the LLC transformer (Self Bias). In Aux Bias Mode, the MD\_SEL/PS\_ON pin allows the user to turn on the PFC stage alone or both PFC and LLC stages.

The UCC29950 has many protection features, these include:

- · Bias Rail Under-Voltage Lockout

- Active X-Cap Discharge

- Line Under-Voltage Detection

- · Line Over-Voltage Detection

- Line Brownout Detection

- Three Level Output Overcurrent Profile on LLC Stage

- PFC Stage Constant Input Power Limit

- PFC Stage Input Current Limit

- PFC Stage Second Current Limit

- PFC Stage Output Overvoltage Protection

- V<sub>BLK</sub> Sensing Network Fault Detection

- V<sub>BLK</sub> Over-Voltage Protection

- PFC and LLC Stage Soft-Start

- PFC Stage Frequency Dithering

- Thermal Shutdown

The UCC29950 implements an advanced control algorithm to control the PFC stage input current. This proprietary hybrid method combines both average and peak-mode control methods.

- Accurate control of the average current drawn from the line gives good THD.

- Peak inductor current information is used to terminate each PFC switching cycle.

- The algorithm is insensitive to variations in the peak-to-average current ratio.

The input current is accurately controlled so that it follows the correct sinusoidal shape and also gives inherent cycle-by-cycle protection against excess MOSFET current. A further advantage is that the control loop is insensitive to PFC inductor and bulk capacitor variations. The UCC29950 takes full advantage of this fact to implement internal compensation of the PFC stage. This simplifies the system designer's task and reduces the external component count. A sophisticated soft-start algorithm is used to achieve a constant soft-start ramp time over a wide range of bulk capacitor values and initial conditions.

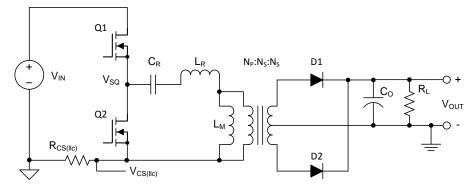

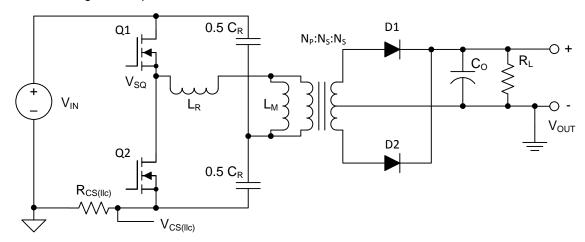

An LLC stage is typically used to convert the PFC stage output to an isolated final voltage for system use. The UCC29950 provides all the primary-side functions needed to control such a second stage. The input to the FB pin is an isolated control signal from the output. This signal is fed into a voltage-to-frequency converter (VCO). The VCO inserts an appropriate dead time and the resulting signals are routed through some on-chip drivers connected to the GD1 and GD2 outputs. The dead time is shortest at low LLC frequencies and is increased automatically as frequency is increased. A three level Over-Current Protection (OCP) function stops the GD1 and GD2 signals if the current signal at the LLC CS pin goes outside of a defined current vs time profile.

# 7.2 Functional Block Diagram

# 7.3 Feature Description

# Table 1. UCC29950 Features and Benefits

| Feature                                                                                                                                       | Benefit                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Self-Bias Mode allowing off-line operation                                                                                                    | Eliminate cost of Auxiliary Flyback Bias supply in system                                                                                                                |

| Control output for external high-voltage, depletion mode start-up MOSFET                                                                      | Eliminates drop resistor from rectified AC line, reduces stand-by power                                                                                                  |

| Integrated X-Cap discharge function using external start-up MOSFET                                                                            | Eliminates bleed resistor across differential EMI filter capacitor, reduces stand-by power                                                                               |

| PFC stage design in 3 easy steps - (i) design voltage feedback network, (ii) choose current sense feedback resistor, (iii) design power stage | Greatly simplifies design effort                                                                                                                                         |

| Advanced control algorithm for PFC Stage                                                                                                      | Good iTHD and insensitivity to inductor and bulk capacitor variations, Cycle by cycle PFC overcurrent protection                                                         |

| Internal compensation of PFC Stage Voltage and Current feedback loops                                                                         | Reduces Component count, eliminates 2 design steps (voltage and current loop compensation)                                                                               |

| Differential AC Line sensing with fixed 9.3M-ohm resistors                                                                                    | Accurate measurement of line conditions under no-load or start-up conditions for improved performance and protection - Eliminates 1 design step (AC line sensing)        |

| PFC frequency dithering                                                                                                                       | Simplifies EMI filtering and eases EMI compliance                                                                                                                        |

| True input power limit, independent of line voltage                                                                                           | Limit set by choice of R <sub>CS(pfc)</sub> allowing designer greater flexibility compared to fixed limits that depending on AC line voltage                             |

| Zero Voltage Switching (ZVS) over a wide range of operating conditions                                                                        | Reduced switching losses in the LLC converter power devices                                                                                                              |

| Three Level over current protection for LLC and Hiccup mode of operation                                                                      | Allows the power stage to ride through a short-term transient overload but reacts quickly to protect the power stage from heavy overload or output short-circuit events. |

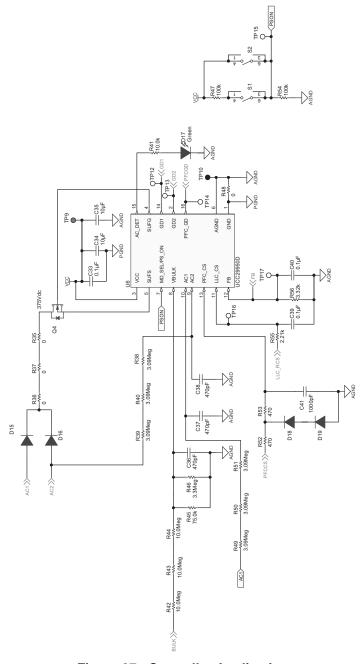

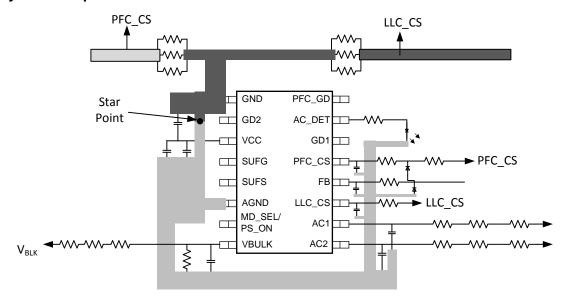

#### 7.3.1 Sense Networks

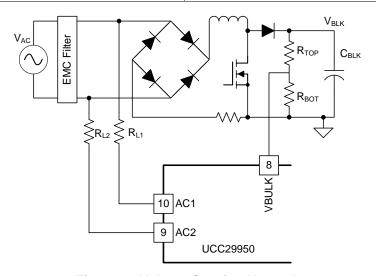

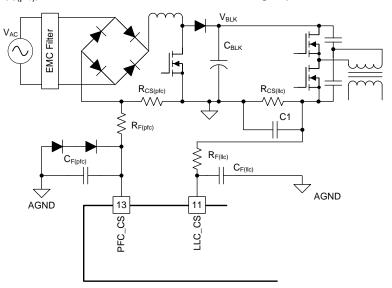

The UCC29950 uses fixed scaling factors to measure the signals at its pins. The circuit position of the voltage sensing resistors is shown in Figure 9. The current sensing resistors are shown in Figure 13.

The resistors in the  $V_{BLK}$  sensing network,  $R_{TOP}$  and  $R_{BOT}$  in Figure 9 have been chosen to minimize the power dissipation and ensure correct operation over the expected tolerance bands. The impedance in this network may be reduced by choosing lower value resistors provided that the potential division ratio is unchanged or kept within the limits given below.

The nominal ratio is  $30~\text{M}\Omega/73.33~\text{k}\Omega=409.28$ . This has been chosen to give a nominal V<sub>BULK</sub> regulation setpoint of 385 V. This voltage is the ideal operating point for the PFC. It prevents direct conduction into the bulk capacitor at high line and prevents false OVP tripping due to load transients - especially under high load conditions where the voltage ripple on the bulk capacitor is maximum. It is possible to change the nominal setpoint within the limits below.

If the ratio is increased above the nominal value then there is a risk of triggering a sense network fault condition at startup - as described in the next section. The maximum ratio is not an absolutely fixed value but is likely to be about 425 with a corresponding  $V_{BULK}$  regulation setpoint of 400 V. The minimum ratio is governed by the desire to avoid direct conduction into the bulk capacitor when operating at high line.  $V_{BULK}$  must be greater than 374 V to avoid this condition on a 264 VRMS line. The corresponding minimum ratio is about 395.

| RESISTOR                            | DESCRIPTION                                                                                                                                  | MIN   | TYP   | MAX   | UNIT  |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| R <sub>L1</sub> and R <sub>L2</sub> | 1% tolerance parts are recommended. To meet voltage ratings, it may be necessary to split the resistance across more than one part.          | 9.21  | 9.30  | 9.40  | ΜΩ    |

| R <sub>TOP</sub>                    | 1% tolerance parts are recommended. To meet voltage ratings, it may be necessary to split the resistance across more than one part.          | 29.7  | 30.0  | 30.3  | IVILI |

| R <sub>BOT</sub>                    | 1% tolerance parts are recommended. A parallel combination of a 75-k $\Omega$ and a 3.3-M $\Omega$ resistor gives a nominal 73.33 k $\Omega$ | 72.50 | 73.33 | 74.07 | kΩ    |

| R <sub>CS(pfc)</sub>                | Value depends on system power level and is given by Equation 59                                                                              |       | 33    |       | mΩ    |

| R <sub>CS(IIc)</sub>                | Value depends on system power level and is given by Equation 36                                                                              | 400   |       | 11122 |       |

**Table 2. Sensing Resistor Values**

Figure 9. Voltage Sensing Network

## 7.3.2 Sense Network Fault Detection

In a boost converter, there is a direct conduction path from AC line to the bulk capacitor which ensures that it will be charged to peak of line even if the PFC stage controller is inactive. At start-up the UCC29950 measures AC line voltage and the voltage on the PFC bulk energy storage capacitor. If the UCC29950 measures  $V_{BLK}$  to be lower than  $V_{AC}$  it enters a latched fault condition. This feature prevents the PFC stage from running if the upper resistor in the voltage sensing network has gone open circuit. If the lower resistor has gone open circuit, then the UCC29950 detects this as an over-voltage event on the output and PFC switching will not start.

## 7.3.3 PFC Stage Soft-Start

The UCC29950 soft-start will typically charge the PFC boost capacitor within 50 ms to 100 ms of starting.

## 7.3.4 AC Line Voltage Sensing

The UCC29950 uses differential AC line sensing through its AC1 and AC2 pins. Differential sensing provides more accurate measurements than single ended sensing, especially at startup and under light load conditions. It also allows faster detection of AC line disconnection or failure.

Normal single ended sensing assumes that the diodes connected to the negative going AC line are forward biased and that a single measurement of the positive going AC line is a true representation of the input voltage. This is normally true but if there is no current being drawn, as is the case under no-load or start up conditions, then it is possible that all the diodes in the bridge are reverse biased. If this happens then a single ended measurement will overestimate the true AC line voltage. The differential AC line sensing used in the UCC29950 avoids these errors.

The external resistor value impedance for AC1 and AC2 is required to be 9.3 M $\Omega$ . This reduces the static power dissipation and provides the correct divider ratio in conjunction with the GAIN and OFFSET factors of the device, (see Equation 1).

These factors are set at the time the UCC29950 is tested. They are used to compensate for device to device variations in  $R_{AC1}$  and  $R_{AC2}$ .

$$VAC = |AC1 - AC2 - OFFSET| \times GAIN \tag{1}$$

AC1 and AC2 must be connected to the AC line side of the bridge rectifier through  $9.3\text{-}M\Omega$  resistors. The high impedance sensing network is effectively a current source which is why the levels in the electrical characteristics table are given in terms of currents rather than voltages. The equivalent voltages are given in Table 3.

The  $9.3-M\Omega$  resistors must be able to support the full voltage at peak of AC line and are conveniently made from three  $3.09-M\Omega$  resistors in series. It is recommended to minimize the length of track between the ACx pins and the lowest resistor in the chain.

| Table 3   | DEC AC | l ina | Voltage | Action | Levels <sup>(1)</sup> |

|-----------|--------|-------|---------|--------|-----------------------|

| i abie 3. | PFC AC | LIIIE | vollage | ACLION | revers.               |

|                               | VOLTAGE                                                          | PARAMETER                     | MIN  | TYP | MAX  | UNIT      |

|-------------------------------|------------------------------------------------------------------|-------------------------------|------|-----|------|-----------|

| V <sub>AC(det)</sub>          | AC_DET will be active HIGH when VAC is below this level          | I <sub>AC(det)</sub>          | 65.5 | 70  | 74.5 | $V_{RMS}$ |

| V <sub>AC(low_falling)</sub>  | PFC stage stops 100 ms after VAC is at or below this level       | I <sub>AC(low_falling)</sub>  | 65.5 | 70  | 74.5 |           |

| V <sub>AC(low_rising)</sub>   | PFC stage is allowed to start when VAC is at or above this level | I <sub>AC(low_rising)</sub>   | 75   | 80  | 85.2 |           |

| V <sub>AC(high_falling)</sub> | PFC stage restarts if VAC falls below this level                 | I <sub>AC(high_falling)</sub> | 287  | 300 | 313  |           |

| V <sub>AC(high_rising)</sub>  | PFC stage stops if VAC is at or above this level                 | I <sub>AC(high_rising)</sub>  | 297  | 310 | 323  |           |

| V <sub>AC(halt)</sub>         | PFC and LLC stages stop if VAC is at or above this level         | I <sub>AC(halt)</sub>         | 306  | 320 | 333  |           |

<sup>(1)</sup> Based on parameter values in Electrical Characteristics table and calculated assuming 9.3 MΩ resistors in AC1 and AC2 lines. The relative levels of these action levels track each other.

## 7.3.5 V<sub>BLK</sub> Sensing

$V_{BLK}$  is sensed through a potential divider with a resistance of 30 M $\Omega$  between the VBULK pin and  $V_{BLK}$ . The bottom resistor in the potential divider is 73.3 k $\Omega$ . The 30 M $\Omega$  resistor has to support the full  $V_{BLK}$  voltage and it is normal to split this resistance into three separate parts of 10 M $\Omega$  each. As noted in Sense Network Fault Detection the UCC29950 will not start the power stages if it detects that  $V_{BLK}$  is less than peak of VAC. Because of the high impedance nature of the sensing network it is recommended to minimize the length of track between the VBULK pin and the lowest resistor in the sensing chain.

## 7.3.6 AC Input UVLO and Brownout Protection

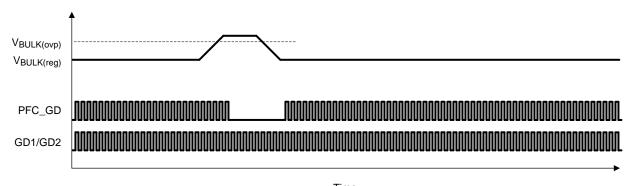

The UCC29950 provides full brownout protection and will not react to single-cycle AC line dropouts. While the PFC stage is running the controller checks each AC line half-cycle. A valid AC line input is detected if the peak voltage during an AC line half-cycle is greater than the brownout level (equivalent to  $70~V_{RMS}$ ). The AC\_DET output goes high if no valid AC line input is detected for a period greater than 32 ms and both the PFC and LLC stages stop operating 100 ms later.

NOTE

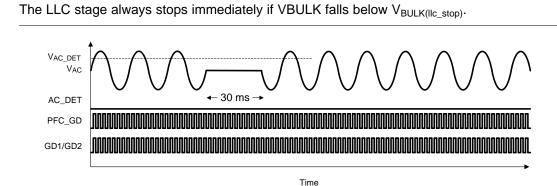

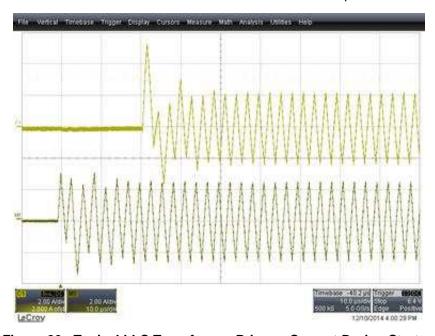

Figure 10. AC Line Dropout

Figure 11. AC Line Disconnect

Figure 12. AC Line Brownout

#### 7.3.7 Dither

The PFC stage switching frequency is stepped between three discrete frequencies at a rate of 333 Hz. The frequencies are spaced at nominal 2-kHz intervals. The dither rate is selected to avoid harmonics of the major AC line frequencies. Dither is effective in reducing the average EMI level and also reduces the quasi-peak levels but to a lesser extent.

## 7.3.8 Active X-Cap Discharge

If the Active X-Cap discharge function is to be used, the drain of the start-up FET must be connected to the AC side of the bridge rectifier, as shown in Figure 20. The X-Cap is discharged by bringing SUFG low to turn the start-up FET on. The discharge path is then through the startup FET, via the SUFS pin and into  $C_{VCC}$ .

### **NOTE**

A Zener diode should be used to clamp VCC and prevent multiple X-Cap discharge events from over charging the capacitor. This Zener diode should be 18V rated device in Self-bias applications. A lower voltage Zener could be used in Aux bias applications, providing that the Zener voltage is greater than the normal operating VCC rail voltage.

When the AC line is removed the UCC29950 detects that the zero voltage crossings on  $V_{AC}$  have ceased. If the PFC stage is running at that time then the X-Cap is discharged through the switching action of the PFC stage and no further action is needed. If the PFC stage is not running at the time of disconnection, perhaps because MD\_SEL/PS\_ON is held low or VBULK is  $> V_{BULK(reg)}$ , then SUFG is set high if  $VC_{X-Cap}$  (the voltage on the X-Cap) is greater than 42 V and the X-Cap is discharged. If  $VC_{X-Cap}$  is < 42 V then it is regarded as being at a safe level, discharge is not needed and SUFG is not set high. The X-Cap is always discharged within the 1 s allowed by the safety standards but there may be up to 300 ms delay or latency in SUFG operation if the controller is operating in burst mode, for example at light loads. The UCC29950 makes the decision to set SUFG high based on the voltage on the X-Cap at the end of this latency period.

## 7.3.9 LLC Stage Soft Start

The LLC stage soft-start ramps the LLC gate drive frequency from min period  $(1/LLC_{F(max)})$  to max period  $(1/LLC_{F(min)})$  over a 100-ms interval. The ramp is terminated when the voltage at the FB pin is such that it would command a higher frequency than the ramp. The first pulse from the GD1 output is half width.

## 7.3.10 PFC Stage Current Sensing

The UCC29950 controls the average current in the PFC inductor. This means that the current sense signal at the PFC\_CS pin must represent the inductor current during the full PFC switching cycle. That is when the MOSFET is ON and also when the MOSFET is OFF. This is achieved by putting the current sensing resistor,  $R_{CS(pfc)}$ , in the position shown in Figure 13 and Figure 34.

#### NOTE

The current sense signal,  $V_{\text{CS\_PFC}}$ , is negative going, so the signal goes more negative as the inductor current increases.

The current sensing resistor is on the input current return path and inrush currents flow through it. These may generate large voltage drops on the current sense resistor. These voltages may be higher than the negative voltage rating on the PFC\_CS pin. A resistor, recommended value = 1 k $\Omega$ , between the current sensing resistor and the PFC\_CS pin is used to avoid over stressing the device. Signal diodes may be necessary to provide additional clamping. A small filter capacitor may be useful to further reduce the noise level at this pin but be careful that this part does not significantly attenuate the ripple component of the current sense signal. These components are shown in Figure 13.

The current drawn from the AC line is limited so that the peak voltage on the PFC\_CS pin, ignoring PFC stage switching ripple, does not exceed –225 mV, V<sub>TH(PFCCS(cav max)</sub>), as shown in Figure 6.

There is a second current limit point at  $V_{PFCCS(max)}$  and the peak voltage at the PFC\_CS pin should not be allowed to exceed this limit (-570 mV). The operation of this second current limit is explained later. The PFC current sense resistor ( $R_{CS(pfc)}$ ) value needed can be calculated using Equation 59.

Figure 13. Current Sensing Connections

## 7.3.11 Input Power Limit

The UCC29950 has a true input power limit which limits the PFC stage power at a level which is independent of the AC line voltage. This is more useful than a simple fixed input current limit where the power would be limited at different levels depending on the AC line voltage. The power limit is set by the choice of R<sub>CS(pfc)</sub> according to Equation 59.

## 7.3.12 PFC Stage Soft Start

When the power system is first connected, the bulk capacitor charges to the peak value of the AC line voltage. The PFC stage soft-start process first calculates the current needed to charge the bulk capacitor from this initial stage to the regulation setpoint (VBULK at  $V_{BULK(reg)}$ ) in a nominal 50 ms. This is an approximate calculation based on a bulk capacitance of 0.8- $\mu$ F per watt and varies if a larger or smaller capacitor is used. The PFC stage is then started using this current limit value.

## 7.3.13 Hybrid PFC Control Loop

The UCC29950 controls a continuous-conduction mode PFC stage by using a novel method combining average current-mode control with peak-current sensing. Among other advantages, this method eliminates the peak-mode line current distortions due to a varying peak-to-average current ratio. The average current is used to control the average value of the PFC inductor current and the peak current is used to terminate each PWM cycle and provide high bandwidth, cycle-by-cycle current control or limiting. Good power factor is achieved by forcing the average input current to follow a demand signal that is derived from the AC line voltage.

Traditional current-mode control systems require resistor and capacitor compensation components to shape the system response. It is difficult to integrate these components into a semiconductor chip and external parts must be used. The UCC29950 avoids the need for external compensation networks by implementing the average portion of the control loop digitally. The entire outer-voltage control loop is digital and the required slow response is easily achieved without the need for external parts. This mixed signal approach uses digital methods for low-frequency compensation and analog op-amps and comparators for the actual PWM duty-cycle generation.

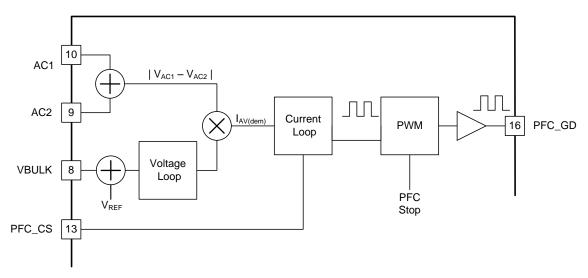

The input AC line voltage is sensed differentially through the AC1 and AC2 pins, as shown in Figure 14. Differential sensing allows more accurate measurement of the AC line voltage over the entire input power range, including no load, than single ended sensing. The output of the voltage loop is multiplied by the instantaneous line voltage,  $|V_{AC1} - V_{AC2}|$ , to give an average current demand signal,  $I_{AV(dem)}$ , for the current loop. The  $I_{AV(dem)}$ , the voltage loop and  $|V_{AC1} - V_{AC2}|$  signals are all implemented digitally. The voltage loop provides correct compensation over the expected range of bulk capacitor values, based on a capacitance to power ratio between 0.5  $\mu$ F W<sup>-1</sup> and 2.4  $\mu$ F W<sup>-1</sup>. This eliminates the need for external compensation components and simplifies the design task.

The current-demand signal normally has a rectified sinusoidal shape. The current-loop output is used to program a duty cycle which is then sent to the PFC\_GD pin through a driver. The minimum duty cycle is 0% at which point the PFG\_GD output is kept low for the entire switching cycle. The maximum duty cycle for the PFC\_GD output is at least 92%.

#### NOTE

The maximum duty cycle is imposed by the PWM block independently of the input from the current loop and does not depend on inputs from the current loop or elsewhere.

Figure 14. PFC Control Loop

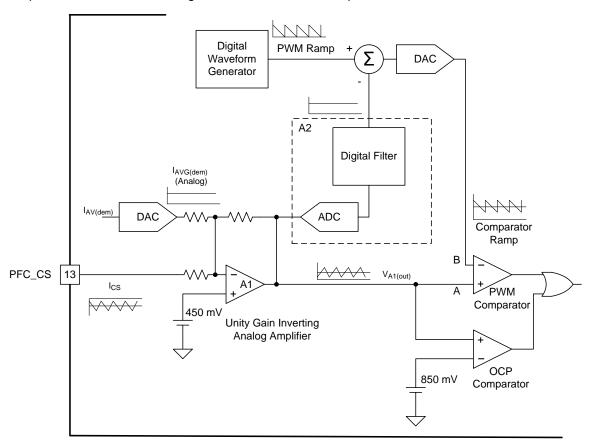

The inner current loop uses a hybrid mixed signal control method as shown in Figure 15. The  $I_{AV(dem)}$  signal (digital average current demand) is converted to an analog form and summed with the sensed current signal  $I_{CS}$  by the unity gain inverting amplifier, A1. The current sensed is the total inductor current which means that the sensing resistor must be placed in the negative return as shown in Figure 13. The  $I_{AV(dem)}$  signal is positive going, greater  $I_{AV(dem)}$  values commands larger currents. The signal at the PFC\_CS pin is negative going so that larger currents give a more negative signal level. The action of the control loop is to keep the inverting and non-inverting inputs to A1 at the same level (450 mV). The output of the A1 amplifier contains both average and peak-inductor current information. The average level at the A1 amplifier output is extracted by the ADC and digital filter shown in the block called A2 in Figure 15. This average level is then subtracted from the fixed PWM ramp coming from the waveform generator. The result is converted into an analog signal by the DAC and sent to the inverting input of the fast analog PWM Comparator. The comparator ramp has an offset which is a function of the digital-filter output. This offset value moves up and down in response to changes at the A1 output. The comparator ramp at the inverting input is negative going and that at the non-inverting input is positive going. This increases the noise immunity of the comparator making an incorrect, early termination of the cycle is less likely.

If the  $I_{AV(dem)}$  signal increases, for example in response to an AC line voltage or load change then the average output of the A1 amplifier initially decreases by the same amount. The PWM duty cycle, and inductor current, will then increase because as  $V_{A1(out)}$  moves negative, it takes longer for the two signals at the comparator inputs to intersect and terminate the cycle. The digital-filter output also increases in response to the change in  $V_{A1(out)}$  according to its frequency response characteristic and the average value of the comparator ramp moves negative. This tends to reduce the PWM duty cycle. Eventually, as the PFC inductor current increases the  $V_{A1(out)}$  signal returns to its equilibrium point at 450 mV. The digital filter dynamically adjusts its output up or down so as to keep the average value of the comparator ramp at the level where  $V_{A1(out)}$  is kept at 450 mV. The overall effect is that a unipolar sinusoidal demand signal is translated into a unipolar sinusoidal PFC inductor current.

Figure 15. UCC29950 Hybrid Current-Mode Control

## 7.3.14 PFC Stage Second Current Limit

An individual PFC switching cycle is normally terminated by the PWM Comparator. If for some reason the PWM Comparator fails or has stopped operating then there is a second comparator monitoring the output of the A1 amplifier (OCP Comparator in Figure 15). The OCP comparator turns the PFC MOSFET off and provides an additional protection function for the devices in the power train.

If the output of A1 reaches 850 mV then the OCP comparator trips. Two actions follow:

- 1. The existing PWM cycle is terminated immediately.

- 2. Both the PFC and LLC stages shut down for 1 s followed by a re-start.

#### 7.3.15 PFC Inductor and Bulk Capacitor Recommendations