bq24745

SLUS761D - DECEMBER 2007 - REVISED OCTOBER 201

www.ti.com

# SMBus-Controlled Multi-Chemistry Battery Charger With Input Current Detect Comparator and Charge Enable Pin

Check for Samples: bq24745

# **FEATURES**

- NMOS-NMOS Synchronous Buck Converter with 300-kHz Frequency and >95% Efficiency

- 30-ns Minimum Driver Dead-Time and 99.5%

Maximum Effective Duty Cycle

- High-Accuracy Voltage and Current Regulation

- ±0.5% Charge Voltage Accuracy

- ±3% Charge Current Accuracy

- ±3% Adapter Current Accuracy

- ±2% Input Current Sense Amp Accuracy

- Integration

- Input Current Comparator, With Adjustable Threshold and Hysteresis

- Internal Soft-Start

- Safety

- Dynamic Power Management (DPM)

- Up to 19.2-V Battery Voltage

- 7-V–24-V AC/DC-Adapter Operating Range

- Simplified SMBus Control Interface

- Charge Voltage DAC (1.024 V–19.2 V)

- Charge Current DAC (128 mA–8.064 A)

- Adapter Current Limit DPM DAC (256 mA-11.008 A)

- Status and Monitoring Outputs

- AC/DC Adapter Present With Adjustable Voltage Threshold

- Input Current Comparator With Adjustable Threshold and Hysteresis

- Current Sense Amplifier for Current Drawn From Input Source

- Charge Any Battery Chemistry: Li+, NiCd, NiMH, Lead Acid, Etc.

- Charge Enable Pin

- < 10-µA Battery Current With Adapter Removed

- < 1-mA Input DCIN Current With Adapter Present and Charge Disabled

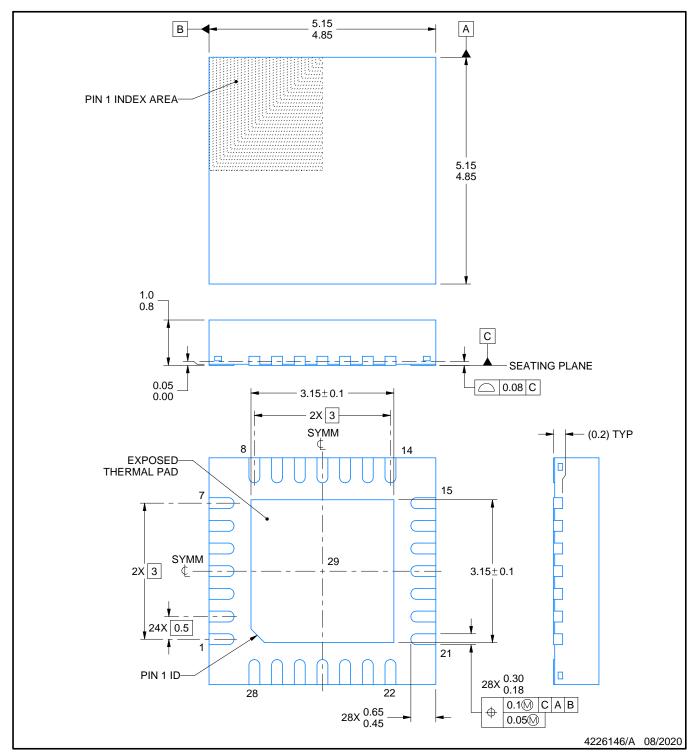

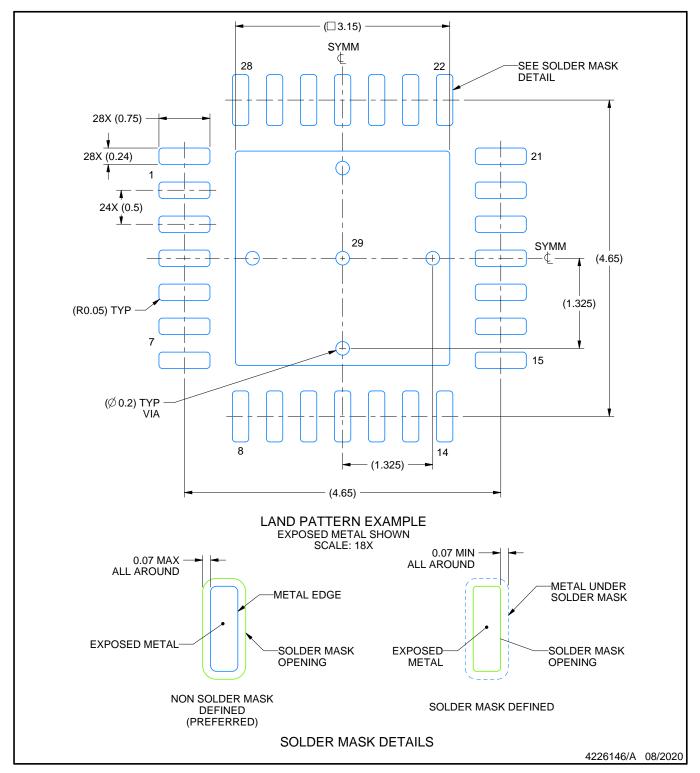

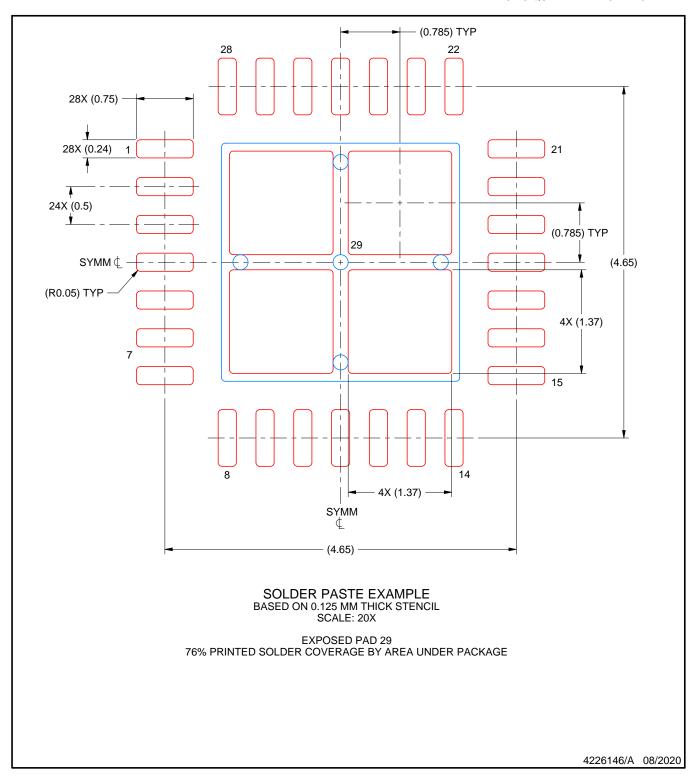

- 28-Pin, 5-mm × 5-mm QFN Package

# **APPLICATIONS**

- · Notebook and Ultra-Mobile Computers

- Portable Data-Capture Terminals

- Portable Printers

- Medical Diagnostics Equipment

- Battery Bay Chargers

- Battery Backup Systems

# **DESCRIPTION**

The bq24745 is a high-efficiency, synchronous battery charger with an integrated input-current comparator, offering low component count for space-constrained, multi-chemistry battery-charging applications. The input-current, charge-current, and charge-voltage DACs allow very high regulation accuracies that can be easily programmed by the system power-management microcontroller using the SMBus interface. The bq24745 charges two, three, or four series Li+ cells, and is available in a 28-pin, 5-mm × 5 mm QFN package.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# **DESCRIPTION (CONTINUED)**

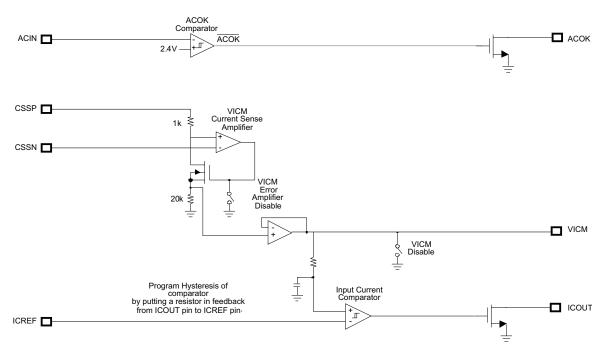

The bq24745 features dynamic power management (DPM) and input power limiting. These features reduce battery-charge current when the input power limit is reached to avoid overloading the ac adaptor when supplying the load and the battery charger simultaneously. A highly accurate current-sense amplifier enables precise measurement of input current from the ac adapter, allowing monitoring the overall system power. If the adapter current is above the programmed low-power threshold, a signal is sent to host so that the system optimizes its performance to the power available from the adapter. An integrated comparator monitors the input current through the current-sense amplifier, and indicates when the input current exceeds a programmable threshold limit.

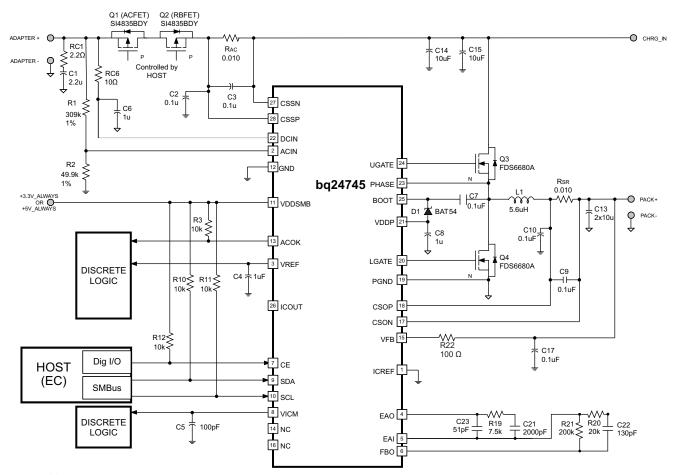

# TYPICAL APPLICATIONS

$V_{IN} = 20 \text{ V}, V_{BAT} = 4\text{-cell Li-Ion}, I_{CHARGE} = 4.5 \text{ A}$

(1) Pullup rail could be either VREF or other system rail.

Figure 1. Typical System Schematic Using External Input-Current Comparator (Discrete Logic) Instead of Internal Comparator

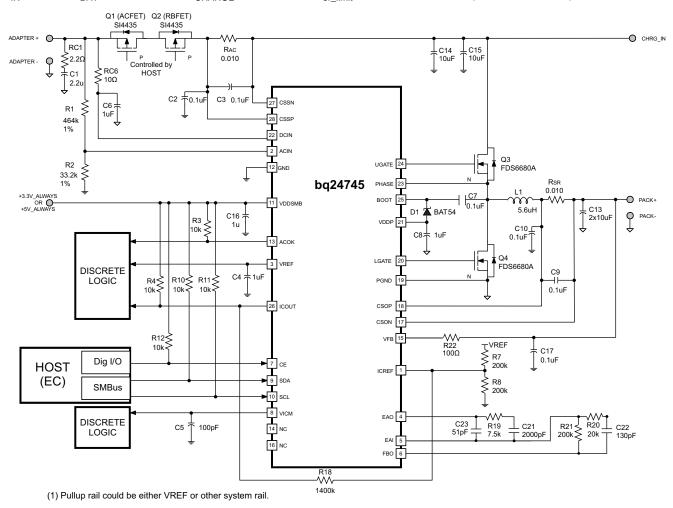

$V_{IN} = 20 \text{ V}$ ,  $V_{BAT} = 4$ -cell Li-Ion,  $I_{CHARGE} = 4.5 \text{ A}$ ,  $VICM_{er\ limit} = 6 \text{ A}$ , for ICOUT Input Current comparator.

Figure 2. Typical System Schematic Using Internal Input-Current Comparator

# **ORDERING INFORMATION**

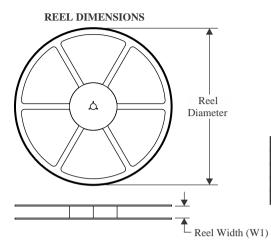

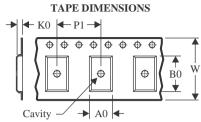

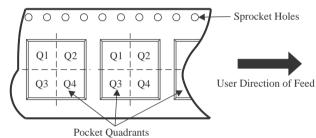

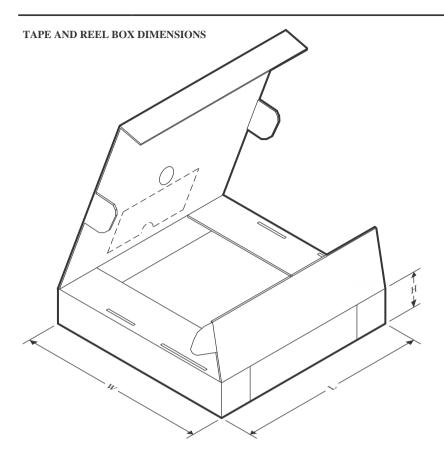

| PART NUMBER | PACKAGE                | ORDERING NUMBER<br>(Tape and Reel) | QUANTITY |

|-------------|------------------------|------------------------------------|----------|

| bc24745     | 00 min 5 mm v 5 mm OFN | bq24745RHDR                        | 3000     |

| bq24745     | 28-pin 5-mm × 5-mm QFN | bq24745RHDT                        | 250      |

# **PACKAGE THERMAL DATA**

| PACKAGE                  | θ <sub>JA</sub> | T <sub>A</sub> = 40°C<br>POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C |

|--------------------------|-----------------|---------------------------------------|------------------------------------------------|

| QFN – RHD <sup>(1)</sup> | 36°C/W          | 2.36 W                                | 0.028 W/°C                                     |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI Web site at www.ti.com.

Copyright © 2007–2011, Texas Instruments Incorporated

www.ti.com

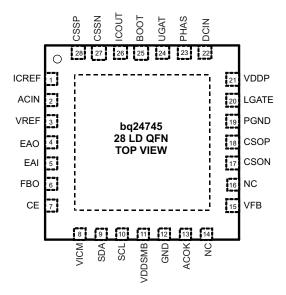

# Table 1. PIN FUNCTIONS - 28-PIN QFN

|     | PIN    | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                           |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                           |

| 1   | ICREF  | Input-current comparator voltage reference input. Connect a resistor divider from VREF to ICREF and from ICREF to GND to program the reference for the ICOUT comparator. The ICREF pin voltage is compared to the VICM pin voltage and the logic output is given on the ICOUT open-drain pin. Connecting a positive feedback resistor from the ICREF pin to the ICOUT pin programs the hysteresis. |

| 2   | ACIN   | Adapter-detected voltage-set input. Program the adapter-detect threshold by connecting a resistor divider from the adapter input to ACIN pin to GND. Adapter voltage is detected if the ACIN-pin voltage is greater than 2.4 V. The VICM current-sense amplifier, ICOUT comparator, and ACOK output are active when the ACIN pin voltage is greater than 0.6 V.                                    |

| 3   | VREF   | 3.3-V regulated voltage output. Place a 1-µF ceramic capacitor from VREF to the GND pin close to the IC. This voltage could be used for ratiometric programming of voltage and current regulation and for programming the ICREF threshold.                                                                                                                                                         |

| 4   | EAO    | Error amplifier output for compensation. Connect the feedback-compensation components from EAO to EAI. Typically, a capacitor in parallel with a series resistor and capacitor. This node is internally compared to the PWM sawtooth oscillator signal.                                                                                                                                            |

| 5   | EAI    | Error amplifier input for compensation. Connect the feedback compensation components from EAI to EAO. Connect the input compensation from FBO to EAI.                                                                                                                                                                                                                                              |

| 6   | FBO    | Feedback output for compensation. Connect the input compensation from FBO to EAI. Typically, a resistor in parallel with a series resistor and capacitor.                                                                                                                                                                                                                                          |

| 7   | CE     | Charge enable active-high logic input. HI enables charge. LO disables charge.                                                                                                                                                                                                                                                                                                                      |

| 8   | VICM   | Adapter current-sense-amplifier output. The VICM voltage is 20 times the differential voltage across CSSP-CSSN. Place a 100-pF (max) or less ceramic decoupling capacitor from VICM to GND.                                                                                                                                                                                                        |

| 9   | SDA    | SMBus data input. Connect to the SMBus data line from the host controller. A $10$ -k $\Omega$ pullup resistor to the host controller power rail is needed.                                                                                                                                                                                                                                         |

| 10  | SCL    | SMBus clock input. Connect to the SMBus clock line from the host controller. A 10-k $\Omega$ pullup resistor to the host controller power rail is needed.                                                                                                                                                                                                                                          |

| 11  | VDDSMB | Input voltage for SMBus logic. Connect a 3.3-V supply rail or 5-V rail to the VDDSMB pin. Connect a 0.1-µF ceramic capacitor from VDDSMB to GND for decoupling.                                                                                                                                                                                                                                    |

| 12  | GND    | Analog ground. On PCB layout, connect to the analog ground plane, and only connect to PGND through the thermal pad underneath the IC.                                                                                                                                                                                                                                                              |

| 13  | ACOK   | Valid adapter active-high detect logic open-drain output. Pulled HI when Input voltage is above the ACIN programmed threshold. Connect a $10$ -k $\Omega$ pullup resistor from the ACOK pin to pull up the supply rail.                                                                                                                                                                            |

| 14  | NC     | No connect. Pin floating internally.                                                                                                                                                                                                                                                                                                                                                               |

| 15  | VFB    | Battery-voltage remote sense. Directly connect a Kelvin sense trace from the battery-pack positive terminal to the VFB pin to sense the battery pack voltage accurately. Place a 0.1-µF capacitor from VFB to GND close to the IC to filter high-frequency noise.                                                                                                                                  |

| 16  | NC     | No Connect. Pin floating internally.                                                                                                                                                                                                                                                                                                                                                               |

| 17  | CSON   | Charge-current sense resistor, negative input. An optional 0.1-µF ceramic capacitor is placed from the CSON pin to GND for common-mode filtering. A 0.1-µF ceramic capacitor is placed from CSON to CSOP to provide differential-mode filtering.                                                                                                                                                   |

| 18  | CSOP   | Charge-current sense resistor, positive input. A 0.1-µF ceramic capacitor is placed from CSOP pin to GND for common-mode filtering. A 0.1-µF ceramic capacitor is placed from CSON to CSOP to provide differential-mode filtering.                                                                                                                                                                 |

| 19  | PGND   | Power ground. On PCB layout, connect directly to the source of the low-side power MOSFET, and to the to ground connection of the input and output capacitors of the charger. Only connect to GND through the thermal pad underneath the IC.                                                                                                                                                        |

| 20  | LGATE  | PWM low-side driver output. Connect to the gate of the low-side power MOSFET with a short trace.                                                                                                                                                                                                                                                                                                   |

| 21  | VDDP   | PWM low-side driver positive 6-V supply output. Connect a 1-µF ceramic capacitor from VDDP to the PGND pin, close to the IC. Use for high-side driver bootstrap voltage by connecting a small signal Schottky diode from VDDP to BOOT.                                                                                                                                                             |

| 22  | DCIN   | IC-power positive supply. Connect to the common-source (diode-OR) point: source of high-side P-channel MOSFET and source of reverse blocking power P-channel MOSFET. Place a 1- $\mu$ F ceramic capacitor from DCIN to the GND pin close to the IC. Place a 10- $\Omega$ resistor from the adapter input to the DCIN pin to limit inrush current.                                                  |

| 23  | PHASE  | PWM high-side driver negative supply. Connect to the phase-switching node (junction of the low-side power MOSFET drain, high-side power MOSFET source, and output inductor). Connect the 0.1-µF bootstrap capacitor from PHASE to BOOT.                                                                                                                                                            |

| 24  | UGATE  | PWM high-side driver output. Connect to the gate of the high-side power MOSFET with a short trace.                                                                                                                                                                                                                                                                                                 |

# Table 1. PIN FUNCTIONS – 28-PIN QFN (continued)

|     | PIN   | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                             |

| 25  | BOOT  | PWM high-side driver positive supply. Connect a 0.1-µF bootstrap ceramic capacitor from BOOT to PHASE. Connect a small bootstrap Schottky diode from VDDP to BOOT.                                                                                                                                                                                                                                                   |

| 26  | ICOUT | Input-current comparator active-high open-drain logic output. Place a $10\text{-k}\Omega$ pullup resistor from the ICOUT pin to the pullup voltage rail. Place a positive-feedback resistor from the ICOUT pin to the ICREF pin for programming hysteresis. The output is HI when the VICM pin voltage is lower than the ICREF pin voltage. The output is LO when VICM pin voltage is higher than ICREF pin voltage. |

| 27  | CSSN  | Adapter current-sense resistor, negative input. An optional 0.1-µF ceramic capacitor is placed from the CSSN pin to GND for common-mode filtering. A 0.1-µF ceramic capacitor is placed from CSSN to CSSP to provide differential-mode filtering.                                                                                                                                                                    |

| 28  | CSSP  | Adapter current-sense resistor, positive input. A 0.1-µF ceramic capacitor is placed from the CSSP pin to GND for common-mode filtering. A 0.1-µF ceramic capacitor is placed from CSSN to CSSP to provide differential-mode filtering.                                                                                                                                                                              |

# **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted) (1) (2)

|                |                                                          | VALUE       | UNIT |  |

|----------------|----------------------------------------------------------|-------------|------|--|

|                | DCIN, CSOP, CSON, CSSP, CSSN, VFB, ACOK                  | -0.3 to 30  |      |  |

| Voltage range  | PHASE                                                    | –1 to 30    |      |  |

|                | EAI, EAO, FBO, VDDP, LGATE, ACIN, VICM, ICOUT, ICREF, CE | -0.3 to 7   |      |  |

|                | VDDSMB, SDA, SCL                                         | -0.3 to 6   | V    |  |

|                | VREF                                                     | -0.3 to 3.6 |      |  |

|                | BOOT, UGATE with respect to GND and PGND                 | -0.3 to 36  |      |  |

| Maximum differ | ence voltage: CSOP-CSON, CSSP-CSSN                       | -0.5 to 0.5 |      |  |

| Junction tempe | rature range                                             | -40 to 155  | °C   |  |

| Storage temper | ature range                                              | -55 to 155  | °C   |  |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# RECOMMENDED OPERATING CONDITIONS

over operating free-air temperature range (unless otherwise noted)

|                                                  |                                             | MIN  | NOM MAX | UNIT |

|--------------------------------------------------|---------------------------------------------|------|---------|------|

|                                                  | PHASE                                       | -0.7 | 24      |      |

|                                                  | DCIN, CSOP, CSON, CSSP, CSSN, VFB, ACOK     | 0    | 24      |      |

|                                                  | VDDP, LGATE                                 | 0    | 6.5     |      |

| Voltage range                                    | VREF                                        |      | 3.3     | .,   |

|                                                  | EAI, EAO, FBO, ACIN, VICM, ICOUT, ICREF, CE | 0    | 5.5     | V    |

|                                                  | BOOT, UGATE with respect to GND and PGND    | 0    | 30      |      |

|                                                  | VDDSMB, SDA, SCL                            | 0    | 5.5     |      |

| Maximum difference voltage: CSOP-CSON, CSSP-CSSN |                                             | -0.3 | 0.3     |      |

| Junction tempera                                 | unction temperature range -40 125           |      | °C      |      |

| Storage tempera                                  | torage temperature range –55 150            |      | 150     | °C   |

Copyright © 2007–2011, Texas Instruments Incorporated

<sup>(2)</sup> All voltages are with respect to GND if not specified. Currents are positive into, and negative out of the specified terminal. Consult Packaging Section of the data book for thermal limitations and considerations of packages.

www.ti.com

# **ELECTRICAL CHARACTERISTICS**

7 V  $\leq$  V<sub>DCIN</sub>  $\leq$  24 V, 0°C < T<sub>J</sub> < 125°C, typical values are at T<sub>A</sub> = 25°C, with respect to AGND (unless otherwise noted)

|                           | PARAMETER                                             | TEST CONDITIONS                                                                            | MIN       | TYP    | MAX        | UNIT |

|---------------------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------|-----------|--------|------------|------|

| OPERATING C               | ONDITIONS                                             | ,                                                                                          |           |        |            |      |

| V <sub>DCIN_OP</sub>      | DCIN input-voltage operating range                    |                                                                                            | 7         |        | 24         | ٧    |

| CHARGE VOLT               | FAGE REGULATION                                       |                                                                                            |           |        |            |      |

| V <sub>VFB_OP</sub>       | VFB input-voltage range                               |                                                                                            | 0         |        | DCIN       | V    |

|                           |                                                       | ChargeVoltage() = 0x41A0                                                                   | 16.716    | 16.8   | 16.884     | V    |

|                           |                                                       |                                                                                            | -0.5%     |        | 0.5%       |      |

|                           |                                                       |                                                                                            | 12.529    | 12.592 | 12.655     | V    |

| .,                        | VFB charge-voltage regulation accuracy                | ChargeVoltage() = 0x3130                                                                   | -0.5%     |        | 0.5%       |      |

| V <sub>VFB_REG</sub> _ACC |                                                       |                                                                                            | 8.350     | 8.4    | 8.450      | V    |

|                           |                                                       | ChargeVoltage() = 0x20D0                                                                   | -0.6%     |        | 0.6%       |      |

|                           |                                                       |                                                                                            | 4.154     | 4.192  | 4.230      | V    |

|                           |                                                       | ChargeVoltage() = 0x1060                                                                   | -0.9%     |        | 0.9%       |      |

| V <sub>VFB_REG_</sub> RNG | Charge-voltage regulation range                       | T <sub>J</sub> = 0 to 125°C, 1.024 V–19.2 V, Max DAC value is 19.2 V                       | 1.024     |        | 19.2       | V    |

| CHARGE CURF               | RENT REGULATION                                       | · ·                                                                                        |           |        |            |      |

| V <sub>IREG_CHG_RNG</sub> | Charge-current regulation differential-voltage range  | $V_{IREG\_CHG} = V_{CSOP} - V_{CSON}$ , max. DAC value is 80.64 mV                         | 0         |        | 80.64      | mV   |

|                           |                                                       | Ob ()                                                                                      |           | 3968   |            | mA   |

|                           |                                                       | ChargeCurrent() = 0x0F80                                                                   | -3%       |        | 3%         |      |

|                           |                                                       | Ob                                                                                         |           | 2048   |            | mA   |

|                           | Charge-current regulation accuracy                    | ChargeCurrent() = 0x0800                                                                   | -5%       |        | 5%         |      |

| CHRG_REG_ACC              |                                                       | ChargeCurrent() = 0x0200                                                                   |           | 512    |            | mA   |

|                           |                                                       |                                                                                            | -25%      |        | 25%        |      |

|                           |                                                       | ChargeCurrent() = 0x0080                                                                   |           | 128    |            | mA   |

|                           |                                                       |                                                                                            | -33%      |        | 33%        |      |

| INPUT CURREI              | NT REGULATION                                         |                                                                                            |           |        |            |      |

| V <sub>IREG_DPM_RNG</sub> | Adapter-current regulation differential-voltage range | $V_{IREG\_DPM} = V_{CSSP} - V_{CSSN}$ , max. DAC value is 110.084 mV                       | 0         |        | 110.1      | mV   |

|                           |                                                       | InputCurrent() ≥ 0x0800                                                                    |           | 4096   |            | mA   |

|                           |                                                       |                                                                                            | -3%       |        | 3%         |      |

|                           |                                                       | I                                                                                          |           | 2048   |            | mA   |

|                           |                                                       | InputCurrent() = 0x0400                                                                    | -5%       |        | 5%         |      |

| INPUT_REG_ACC             | Input-current regulation accuracy                     | 1 10 10 0 0100                                                                             |           | 512    |            | mA   |

|                           |                                                       | InputCurrent() = 0x0100                                                                    | -25%      |        | 25%        |      |

|                           |                                                       | 1, 10, 10, 0,000                                                                           |           | 256    |            | mA   |

|                           |                                                       | InputCurrent() = 0x0080                                                                    | -33%      |        | 33%        |      |

| VREF REGULA               | TOR                                                   | 1                                                                                          |           |        |            |      |

| V <sub>VREF REG</sub>     | VREF regulator voltage                                | V <sub>ACIN</sub> > 0.6 V, 0 – 30 mA                                                       | 3.267     | 3.3    | 3.333      | V    |

| I <sub>VREF_LIM</sub>     | VREF current limit                                    | V <sub>VREF</sub> = 0 V, V <sub>ACIN</sub> > 0.6 V                                         | 35        |        | 80         | mA   |

|                           |                                                       |                                                                                            |           |        |            |      |

|                           | \TOR                                                  |                                                                                            |           |        |            |      |

| VDDP REGULA               |                                                       | V <sub>ACIN</sub> > 0.6 V, 0 – 50 mA                                                       | 5.7       | 6      | 6.3        | V    |

|                           | ATOR  VDDP regulator voltage                          | V <sub>ACIN</sub> > 0.6 V, 0 – 50 mA<br>V <sub>VDDP</sub> = 0 V, V <sub>ACIN</sub> > 0.6 V | 5.7<br>90 | 6      | 6.3<br>135 | V    |

$7 \text{ V} \le \text{V}_{DCIN} \le 24 \text{ V}, 0^{\circ}\text{C} < \text{T}_{J} < 125^{\circ}\text{C}$ , typical values are at  $\text{T}_{A} = 25^{\circ}\text{C}$ , with respect to AGND (unless otherwise noted)

| V <sub>CSSP/N_OP</sub>     | RENT SENSE AMPLIFIER                                    |                                                                                           | -     |      |       |     |

|----------------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------|-------|------|-------|-----|

| V <sub>VICM</sub>          | 1                                                       |                                                                                           |       |      |       |     |

| V <sub>VICM</sub>          | Input common-mode range                                 | Voltage on CSSP/CSSN                                                                      | 0     |      | 24    | V   |

| 1                          | VICM output-voltage range                               |                                                                                           | 0     |      | 2.25  | V   |

| I <sub>VICM</sub>          | VICM output current                                     |                                                                                           | 0     |      | 1     | mA  |

| A <sub>VICM</sub>          | Current-sense amplifier voltage gain                    | A <sub>VICM</sub> = V <sub>VICM</sub> / V <sub>IREG DPM</sub>                             |       | 20   |       | V/V |

|                            |                                                         | V <sub>IREG_DPM</sub> = V(CSSP–CSSN) ≥ 40 mV                                              | -2%   |      | 2%    |     |

|                            |                                                         | V <sub>IREG_DPM</sub> = V(CSSP-CSSN) = 20 mV                                              | -3%   |      | 3%    |     |

|                            | Adapter-current sense accuracy                          | V <sub>IREG_DPM</sub> = V(CSSP-CSSN) = 5 mV                                               | -25%  |      | 25%   |     |

|                            |                                                         | V <sub>IREG DPM</sub> = V(CSSP-CSSN) = 1.5 mV                                             | -33%  |      | 33%   |     |

| I <sub>VICM LIM</sub>      | Output-current limit                                    | V <sub>VICM</sub> = 0 V                                                                   | 1     |      |       | mA  |

| C <sub>VICM MAX</sub>      | Maximum output load capacitance                         | For stability with 0-mA to 1-mA load                                                      |       |      | 100   | pF  |

|                            | ATOR INPUT UNDERVOLTAGE)                                |                                                                                           |       |      |       |     |

| V <sub>DCIN_VFB_OP</sub>   | Differential voltage from DCIN to VFB                   |                                                                                           | -20   |      | 24    | V   |

| V <sub>ACIN_CHG</sub>      | ACIN rising threshold                                   | Min. voltage to enable charging, V <sub>ACIN</sub> rising                                 | 2.376 | 2.4  | 2.424 | V   |

| V <sub>ACIN_CHG_HYS</sub>  | ACIN falling hysteresis                                 | V <sub>ACIN</sub> falling                                                                 |       | 40   |       | mV  |

|                            | ACIN rising deglitch <sup>(1)</sup>                     | V <sub>ACIN</sub> rising                                                                  | 50    | 100  | 150   | μs  |

|                            | ACIN falling deglitch                                   | V <sub>ACIN</sub> falling                                                                 |       | 1    |       | µs  |

| V <sub>ACIN_BIAS</sub>     | Adapter present rising threshold                        | Min voltage to enable all bias, V <sub>ACIN</sub> rising                                  | 0.56  | 0.62 | 0.68  | V   |

| V <sub>ACIN_BIAS_HYS</sub> | Adapter present falling hysteresis                      | V <sub>ACIN</sub> falling                                                                 |       | 20   |       | mV  |

| ACIN_DIAG_IIIG             | ACIN rising deglitch (1)                                | V <sub>ACIN</sub> rising                                                                  |       | 200  |       |     |

|                            | ACIN falling deglitch                                   | V <sub>ACIN</sub> falling                                                                 |       | 1    |       | μs  |

| DCIN / VFB COI             | MPARATOR (REVERSE DISCHARGING PROT                      |                                                                                           |       |      |       |     |

| V <sub>DCIN-VFB</sub> FALL | DCIN to VFB falling threshold                           | V <sub>DCIN</sub> – V <sub>VFB</sub> to turn off ACFET                                    | 140   | 185  | 240   | mV  |

| V <sub>DCIN-VFB_HYS</sub>  | DCIN to VFB hysteresis                                  | DOIN VI B                                                                                 |       | 50   | -     | mV  |

| DOIN VI B_IIIO             | DCIN to VFB rising deglitch                             | V <sub>DCIN</sub> - V <sub>VFB</sub> > V <sub>DCIN-VFB</sub> RISE                         |       | 1    |       | ms  |

|                            | DCIN to VFB falling deglitch                            | V <sub>DCIN</sub> - V <sub>VFB</sub> < V <sub>DCIN-VFB</sub> FALL                         |       | 3.3  |       | μs  |

| VFB OVERVOL                | TAGE COMPARATOR                                         | DOIN VI B DOIN VI B_I YEE                                                                 |       |      |       |     |

| V <sub>OV_RISE</sub>       | Overvoltage rising threshold                            | As percentage of V <sub>VFB REG</sub>                                                     |       | 104  |       |     |

| V <sub>OV_FALL</sub>       | Overvoltage falling threshold                           | As percentage of V <sub>VFB REG</sub>                                                     |       | 102  |       | %   |

|                            | NDERVOLTAGE and TRICKLE CHARGE) COM                     | _                                                                                         |       |      |       |     |

| •                          | VFB short rising threshold                              |                                                                                           | 2.6   | 2.7  | 2.9   | V   |

| V <sub>VFB</sub> SHORT HYS | VFB short falling hysteresis                            |                                                                                           |       | 215  | -     | mV  |

| - VFB_3HOK1_H13            | VFB short rising deglitch                               | V <sub>VFB</sub> > V <sub>VFB_SHORT</sub> + V <sub>VFB_SHORT_HYS</sub><br>Detection delay |       | 1.5  |       | μs  |

|                            | VFB short falling deglitch                              | V <sub>VFB</sub> < V <sub>VFB_SHORT</sub>                                                 |       | 3.3  |       | μs  |

| I <sub>TRKL_REG_ACC</sub>  | Trickle-charge current-regulation accuracy in BATSHORT  | V <sub>VFB</sub> = V <sub>VFB_SHORT</sub>                                                 | 60    | 200  | 300   | mA  |

| I <sub>LOW_MAX_REG</sub>   | Maximum charge current regulation at low voltage (<4 V) | V <sub>VFB_SHORT</sub> < V <sub>VFB</sub> < 4                                             |       | 3    |       | Α   |

| CHARGE OVER                | CURRENT COMPARATOR                                      | <u> </u>                                                                                  |       |      |       |     |

| V <sub>oc</sub>            | Charge overcurrent falling threshold                    | As percentage of I <sub>REG CHG</sub>                                                     |       | 145% |       |     |

| -                          | Minimum current limit (CSOP–CSON)                       |                                                                                           |       | 50   |       | mV  |

|                            | Internal filter pole frequency                          |                                                                                           |       | 160  |       | kHz |

| INPUT UNDERV               | OLTAGE LOCK-OUT COMPARATOR (UVLO)                       |                                                                                           |       |      |       |     |

| UVLO                       | AC undervoltage rising threshold                        | Measure on DCIN pin                                                                       | 3.5   | 4    | 4.5   | V   |

| V <sub>UVLO_HYS</sub>      | AC undervoltage hysteresis, falling                     |                                                                                           |       | 260  |       | mV  |

|                            | NT COMPARATOR                                           | 1                                                                                         |       |      | -     |     |

|                            |                                                         |                                                                                           | -6.8  | 0.12 | 6.8   | mV  |

<sup>(1)</sup> Verified by design.

SLUS761D - DECEMBER 2007-REVISED OCTOBER 2011

www.ti.com

# **ELECTRICAL CHARACTERISTICS (continued)**

7 V  $\leq$  V<sub>DCIN</sub>  $\leq$  24 V, 0°C < T<sub>J</sub> < 125°C, typical values are at T<sub>A</sub> = 25°C, with respect to AGND (unless otherwise noted)

|                           | PARAMETER                                                                    | TEST CONDITIONS                                                                                                                  | MIN | TYP  | MAX | UNIT  |

|---------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|-------|

| THERMAL SHU               | TDOWN COMPARATOR                                                             |                                                                                                                                  |     |      |     |       |

| T <sub>SHUT</sub>         | Thermal shutdown rising temperature                                          | Temperature Increasing                                                                                                           |     | 155  |     | 0.0   |

| T <sub>SHUT_HYS</sub>     | Thermal shutdown hysteresis, falling                                         |                                                                                                                                  |     | 20   |     | °C    |

|                           | E DRIVER (UGATE)                                                             |                                                                                                                                  |     |      |     |       |

| R <sub>DS_HI_ON</sub>     | High-side driver (HSD) turnon resistance                                     | V <sub>BOOT</sub> - V <sub>PHASE</sub> = 5.5 V                                                                                   |     |      | 6   | Ω     |

| R <sub>DS HI OFF</sub>    | High-side driver turnoff resistance                                          | $V_{BOOT} - V_{PHASE} = 5.5 \text{ V}$                                                                                           |     |      | 1   | Ω     |

| V <sub>BOOT_REFRESH</sub> | Bootstrap refresh comparator threshold voltage                               | V <sub>BOOT</sub> – V <sub>PHASE</sub> when low-side refresh pulse is requested                                                  | 4   |      |     | V     |

| Inort LEAK                | BOOT leakage current when charge enabled                                     | High side is on; charge enabled                                                                                                  |     |      | 200 | μA    |

| IBOOT_LEAK                | E DRIVER (LGATE)                                                             | Tight dide to on, onarge onabled                                                                                                 |     |      | 200 | μ, τ  |

|                           | Low-side driver (LSD) turnon resistance                                      |                                                                                                                                  |     |      | 6   | Ω     |

| R <sub>DS_LO_ON</sub>     |                                                                              |                                                                                                                                  |     |      |     |       |

| R <sub>DS_LO_OFF</sub>    | Low-side driver turnoff resistance                                           |                                                                                                                                  |     |      | 1   | Ω     |

| PWM DRIVERS               | TIMING                                                                       | T                                                                                                                                |     |      |     |       |

|                           | Driver dead time                                                             | Dead time when switching between LGATE and UGATE, no load at LGATE and UGATE                                                     | 30  |      |     | ns    |

| PWM OSCILLA               | TOR                                                                          |                                                                                                                                  |     |      |     |       |

| F <sub>SW</sub>           | PWM switching frequency                                                      |                                                                                                                                  | 240 |      | 360 | kHz   |

| V <sub>RAMP_HEIGHT</sub>  | PWM ramp height                                                              | As percentage of DCIN                                                                                                            |     | 6.67 |     | %DCIN |

| QUIESCENT CL              | JRRENT                                                                       |                                                                                                                                  |     |      | '   |       |

| I <sub>OFF_STATE</sub>    | Total off-state battery current from CSOP, CSON, VFB, DCIN, BOOT, PHASE, etc | $V_{VFB} = 16.8 \text{ V}, V_{ACIN} < 0.6 \text{ V}, V_{DCIN} > 5 \text{ V}, 0^{\circ}\text{C} \le T_{J} \le 85^{\circ}\text{C}$ |     | 7    | 10  | μA    |

| I <sub>BAT_ON</sub>       | Battery on-state quiescent current                                           | V <sub>VFB</sub> = 16.8 V, 0.6V < V <sub>ACIN</sub> < 2.4 V,<br>V <sub>DCIN</sub> > 5 V                                          |     | 0.7  | 1   | mA    |

| I <sub>BAT_LOAD_CD</sub>  | Internal battery load current, charge disabled                               | Charge is disabled: V <sub>VFB</sub> = 16.8 V,<br>V <sub>ACIN</sub> > 2.4 V, V <sub>DCIN</sub> > 5 V                             |     | 0.7  | 1   | mA    |

| I <sub>BAT_LOAD_CE</sub>  | Internal battery load current, charge enabled                                | Charge is enabled: V <sub>VFB</sub> = 16.8 V,<br>V <sub>ACIN</sub> > 2.4 V, V <sub>DCIN</sub> > 5 V                              | 6   | 10   | 12  | mA    |

| I <sub>AC</sub>           | Adapter quiescent current                                                    | Charge disabled, V <sub>DCIN</sub> = 20 V                                                                                        |     | 0.7  | 1   | mA    |

| I <sub>AC_SWITCH</sub>    | Adapter switching quiescent current                                          | Charge enabled, V <sub>DCIN</sub> = 20 V, converter running                                                                      |     | 25   |     | mA    |

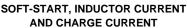

| INTERNAL SOF              | T START (8 Steps to Regulation Current ICHG                                  | 6)                                                                                                                               |     |      |     |       |

|                           | Soft-start steps                                                             |                                                                                                                                  |     | 8    |     | step  |

|                           | Soft-start step time                                                         |                                                                                                                                  |     | 1.5  |     | ms    |

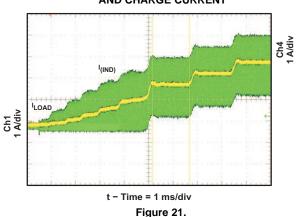

| CHARGER SEC               | CTION POWER-UP SEQUENCING                                                    | <u> </u>                                                                                                                         |     |      |     |       |

| OHAROER GEO               | Charge-enable delay after power up                                           | Delay from when adapter is detected to when the charger is allowed to turn on                                                    |     | 1.5  |     | ms    |

| CHARGE LINDS              | EDCLIDDENT COMPARATOR (CVC) E-RV-CVC)                                        | LE SYNCHRONOUS TO NON-SYNCHRONOUS)                                                                                               |     |      |     |       |

| V <sub>UCP</sub>          | Cycle-by-cycle synchronous to non-synchronous transition threshold           | Cycle-by-cycle, (CSOP-CSON) voltage, falling, LGATE turns off and latches off until next cycle                                   | 5   | 10   | 15  | mV    |

|                           | Blankout time after LGATE turns on                                           | Blankout comparator after LGATE turns on                                                                                         |     | 100  |     | ns    |

| I OGIC INDUT F            | PIN CHARACTERISTICS (CE) <sup>(2)</sup> Pull-up CE with                      | ' .                                                                                                                              |     | 100  |     | 113   |

|                           | · · · · · · · · · · · · · · · · · · ·                                        | 1 -2.2 N2/ 16515(0) Of directly to VREF.                                                                                         |     |      | 0.0 | 17    |

| V <sub>IN_LO</sub>        | Input low-threshold voltage                                                  |                                                                                                                                  | 2 . |      | 8.0 | V     |

| V <sub>IN_HI</sub>        | Input high-threshold voltage                                                 |                                                                                                                                  | 2.1 |      |     |       |

| V <sub>BIAS</sub>         | Input bias current                                                           | $V = 0 \text{ TO } V_{VDDP}$                                                                                                     |     |      | 1   | μA    |

|                           | OGIC OUTPUT PIN CHARACTERISTICS (ACO                                         |                                                                                                                                  |     |      |     |       |

| V <sub>OUT_LO</sub>       | Output low saturation voltage                                                | Sink current = 5 mA                                                                                                              |     |      | 0.5 | V     |

| VDDSMB INPU               | T SUPPLY FOR SMBus                                                           | ,                                                                                                                                |     |      |     |       |

| V <sub>VDDSMB_RANGE</sub> | VDDSMB input voltage range                                                   |                                                                                                                                  | 2.7 | -    | 5.5 | V     |

| V <sub>VDDSMB_UVLO_</sub> | VDDSMB undervoltage lockout threshold                                        | V <sub>VDDSMB</sub> rising                                                                                                       | 2.4 | 2.5  | 2.6 | V     |

| Threshold_Rising          | voltage, rising                                                              | 1550115                                                                                                                          |     |      |     |       |

(2) Pull up CE with ≥ 2-kΩ resistor, or connect directly to VREF.

www.ti.com

SLUS761D - DECEMBER 2007 - REVISED OCTOBER 2011

# **ELECTRICAL CHARACTERISTICS (continued)**

$7 \text{ V} \le \text{V}_{\text{DCIN}} \le 24 \text{ V}, 0^{\circ}\text{C} < \text{T}_{\text{J}} < 125^{\circ}\text{C}, \text{ typical values are at T}_{\text{A}} = 25^{\circ}\text{C}, \text{ with respect to AGND (unless otherwise noted)}$

| PARAMETER                           | TEST CONDITIONS                                                                                        | MIN | TYP | MAX | UNIT |

|-------------------------------------|--------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| IVDDSMB_lq VDDSMB quiescent current | $V_{VDDSMB} = SCL = SDA = 5.5 \text{ V},  0^{\circ}\text{C} \leq \text{T}_{J} \leq 85^{\circ}\text{C}$ |     | 20  | 27  | μΑ   |

# **ELECTRICAL CHARACTERISTICS**

7 Vdc  $\leq$  V<sub>(VCC)</sub>  $\leq$  24 Vdc,  $-20^{\circ}$ C<T<sub>1</sub> <125 $^{\circ}$ C, ref = AGND (unless otherwise noted)<sup>(1)</sup>

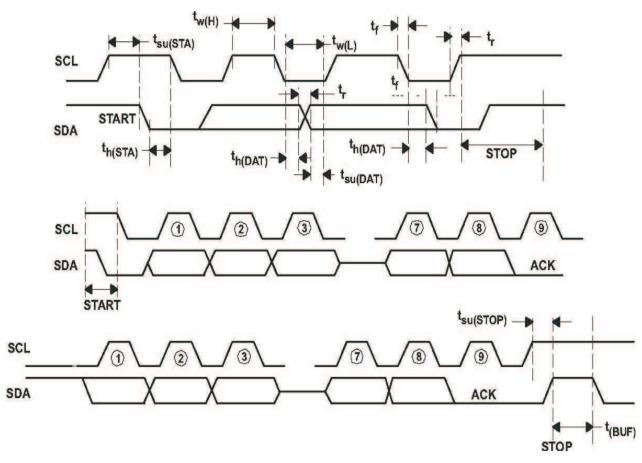

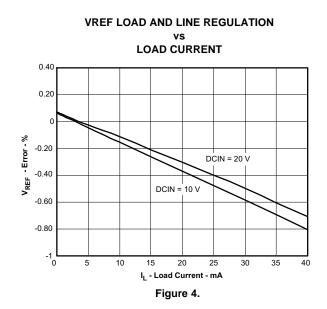

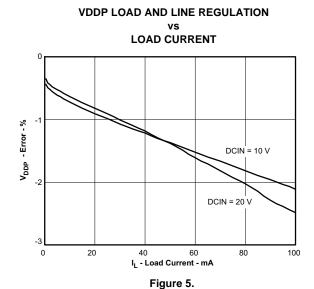

| PARAMET               | ER<br>ING SPECIFICATION (VDD = 2.7 V to 5.5 V) (see Figures 4 and 5)] | MIN         | TYP | MAX | UNIT |

|-----------------------|-----------------------------------------------------------------------|-------------|-----|-----|------|

| SMBus TI              | MING CHARACTERISTICS                                                  |             |     | •   |      |

| t <sub>R</sub>        | SCLK/SDATA rise time                                                  |             |     | 1   | μs   |

| t <sub>F</sub>        | SCLK/SDATA fall time                                                  |             |     | 300 | ns   |

| $t_{W(H)}$            | SCLK pulse duration high                                              | 4           |     | 50  | μs   |

| $t_{W(L)}$            | SCLK pulse duration low                                               | 4.7         |     |     | μs   |

| t <sub>SU(STA)</sub>  | Setup time for START condition                                        | 4.7         |     |     | μs   |

| t <sub>H(STA)</sub>   | START condition hold time after which first clock pulse is generated  | 4           |     |     | μs   |

| t <sub>SU(DAT)</sub>  | Data setup time                                                       | 250         |     |     | ns   |

| $t_{H(DAT)}$          | Data hold time                                                        | 300         |     |     | ns   |

| t <sub>SU(STOP)</sub> | Setup time for STOP condition                                         | 4           |     |     | μs   |

| $t_{(BUF)}$           | Bus free time between START and STOP condition                        | 4.7         |     |     | μs   |

| F <sub>S(CL)</sub>    | Clock frequency                                                       | 10          |     | 100 | kHz  |

| HOST CO               | MMUNICATION FAILURE                                                   |             |     |     |      |

| t <sub>timeout</sub>  | SMBus bus release timeout                                             | 22          | 25  | 35  | ms   |

| $t_{\text{WDI}}$      | Watchdog timeout period                                               | 140         | 170 | 210 | S    |

| OUTPUT I              | BUFFER CHARACTERISTICS                                                | <del></del> |     | ·   |      |

| V <sub>(SDAL)</sub>   | Output LO voltage at SDA, I <sub>(SDA)</sub> = 3 mA                   |             |     | 0.4 | V    |

<sup>(1)</sup> Devices participating in a transfer time out when any clock low exceeds the 2- ms minimum time-out period. Devices that have detected a time-out condition must reset the communication no later than the 35-ms maximum timeout period. Both a master and a slave must adhere to the maximum value specified, as it incorporates the cumulative stretch limit for both a master (10 ms) and a slave (25 ms).

Product Folder Link(s): bq24745

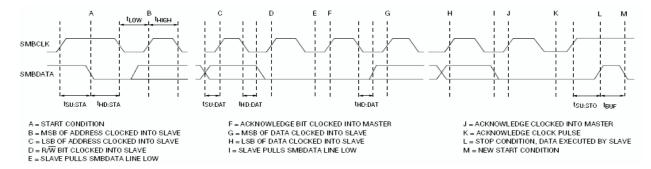

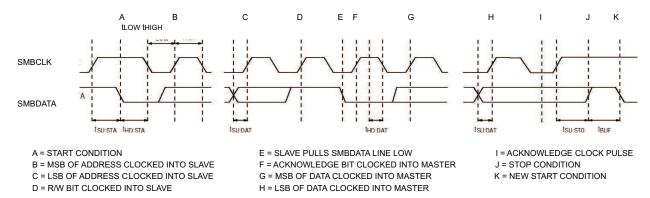

Figure 3. SMBus Communication Timing Waveforms

# TYPICAL CHARACTERISTICS

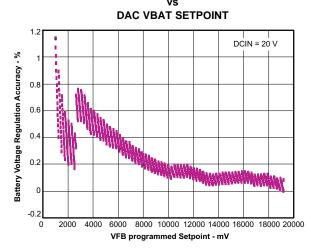

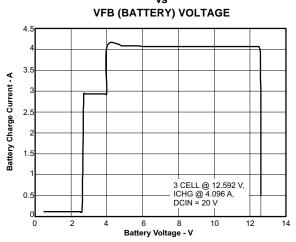

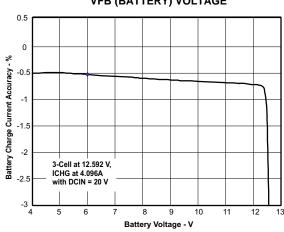

# VFB (BATTERY) VOLTAGE REGULATION ACCURACY

# CHARGE CURRENT 3 CELL @ 12.592 V, ICHG @ 8.064 A, DCIN = 20 V CONTRIBUTION AND ADDITIONS OF THE PROPERTY OF

Figure 6.

# VFB (BATTERY) VOLTAGE REGULATION ACCURACY

Figure 7.

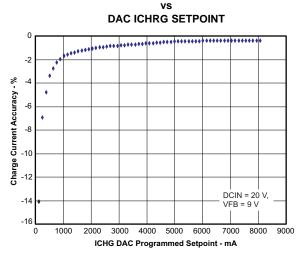

# CHARGE CURRENT REGULATION ACCURACY

Figure 8.

# CHARGE CURRENT REGULATION ACCURACY

Figure 9.

# INPUT CURRENT REGULATION (DPM) ACCURACY

#

Figure 10.

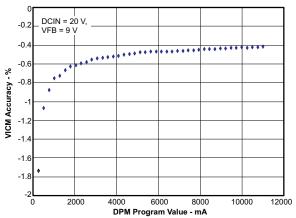

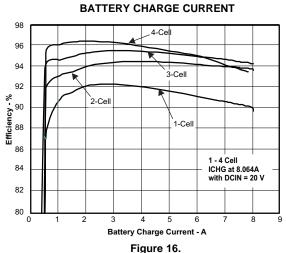

# VICM INPUT CURRENT-SENSE AMPLIFIER ACCURACY INPUT CHARGE CURRENT

Figure 11.

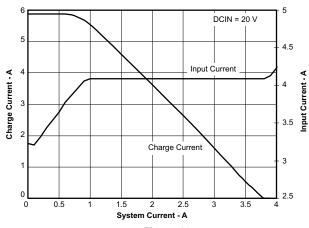

# INPUT CURRENT REGULATION (DPM) AND CHARGE CURRENT

#### vs SYSTEM CURRENT

Figure 12.

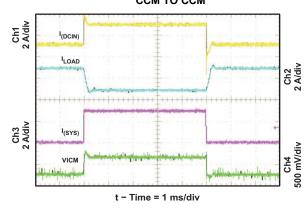

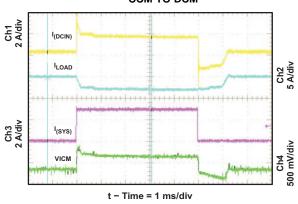

#### INPUT CURRENT REGULATION (DPM) TRANSIENT SYSTEM LOAD RESPONSE CCM TO CCM

Figure 13.

# INPUT CURRENT REGULATION (DPM) TRANSIENT SYSTEM LOAD RESPONSE **CCM TO DCM**

# **CHARGE CURRENT REGULATION ACCURACY VFB (BATTERY) VOLTAGE**

Figure 14.

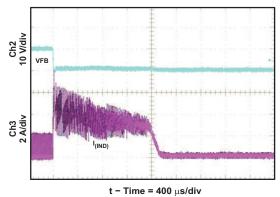

**BATTERY REMOVAL (From Constant-Current Mode)**

Figure 15.

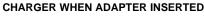

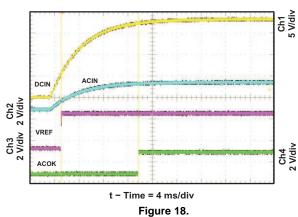

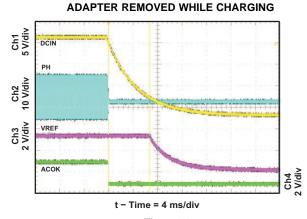

Figure 17.

Figure 19.

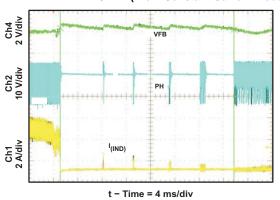

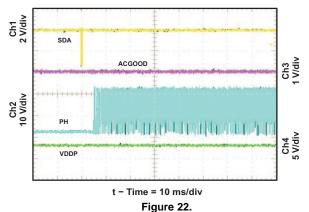

**CHARGE DISABLED BY SMBus**

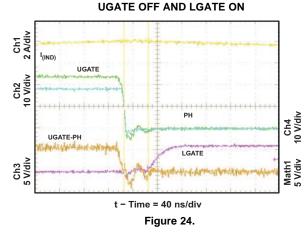

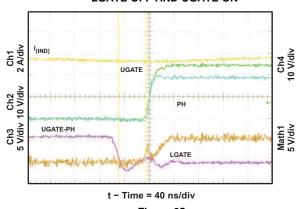

# DEAD-TIME BETWEEN

DEAD-TIME BETWEEN LGATE OFF AND UGATE ON

Figure 25.

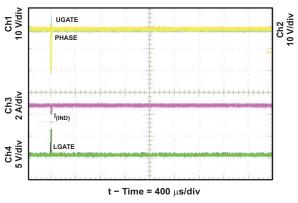

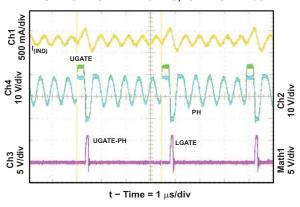

# NEAR 100% DUTY CYCLE BOOTSTRAP RECHARGE PULSE

Figure 26.

# BATTERY SHORTED CHARGER RESPONSE, OVERCURRENT PROTECTION (OCP) AND CHARGE CURRENT REGULATION

Figure 27.

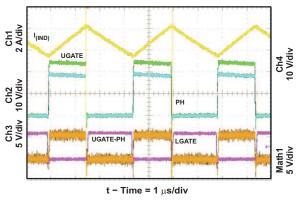

# CONTINUOUS CONDUCTION MODE (CCM) SWITCHING WAVEFORMS, ICHARGE = 3986 mA

Figure 28.

# DISCONTINUOUS CONDUCTION MODE (DCM) SWITCHING WAVEFORMS, ICHARGE = 256 mA

Figure 29.

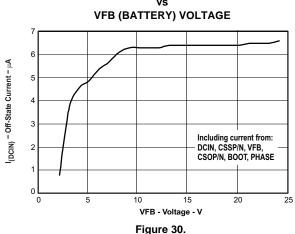

# OFF-STATE BATTERY CURRENT (LOW Iq)

OFF-STATE DCIN CURRENT (LOW Iq)

vs

DCIN INPUT VOLTAGE (With Adapter Connected)

Figure 31.

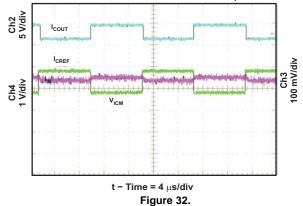

PROGRAMMABLE REFERENCE AND HYSTERESIS INPUT CURRENT COMPARATOR (With Pulsed Current)

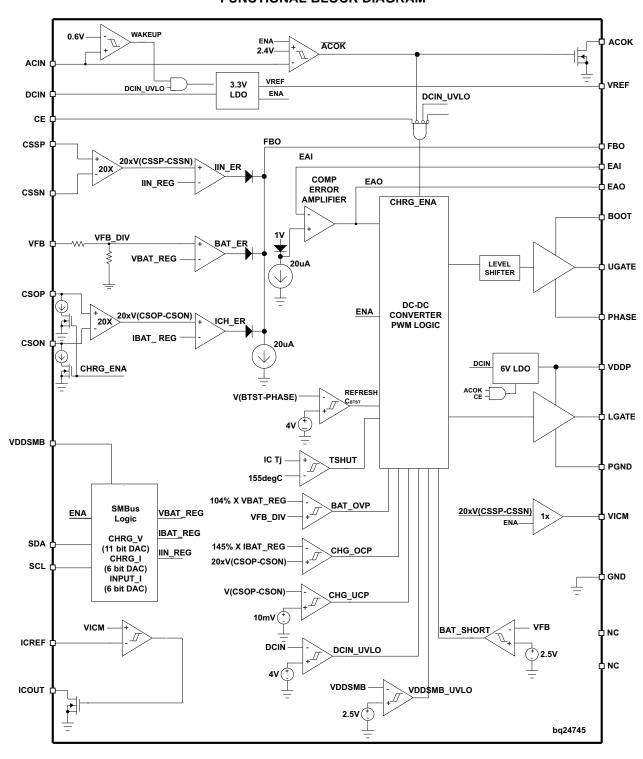

# **FUNCTIONAL BLOCK DIAGRAM**

SLUS761D - DECEMBER 2007 - REVISED OCTOBER 2011

www.ti.com

#### **DETAILED DESCRIPTION**

# **SMBus Interface**

The bq24745 operates as a slave, receiving control inputs from the embedded controller host through the SMBus interface.

# **Battery-Charger Commands**

The bq24745 supports five battery-charger commands that use either Write-Word or Read-Word protocols, as summarized in Table 2. ManufacturerID() and DeviceID() can be used to identify the bq24745. On the bq24745, the ManufacturerID() command always returns 0x0040 and the DeviceID() command always returns 0x0006.

**Table 2. Battery Charger SMBus Registers**

| REGISTER ADDRESS | REGISTER NAME    | READ/WRITE    | DESCRIPTION                   | POR STATE | POR<br>Voltage/Current          |

|------------------|------------------|---------------|-------------------------------|-----------|---------------------------------|

| 0x14             | ChargeCurrent()  | Read or write | 6-bit charge-current setting  | 0x0000    | 0 mV                            |

| 0x15             | ChargeVoltage()  | Read or write | 11-bit charge-voltage setting | 0x0000    | 0 mA                            |

| 0x3F             | InputCurrent()   | Read or write | 6-bit input-current setting   | 0x0080    | 256 mA (10-mΩ R <sub>AC</sub> ) |

| 0xFE             | ManufacturerID() | Read-only     | Manufacturer ID               | 0x0040    | _                               |

| 0xFF             | DeviceID()       | Read-only     | Device ID                     | 0x0006    | _                               |

#### **SMBus**

The bq24745 receives control inputs from the SMBus interface. The bq24745 uses a simplified subset of the commands documented in System Management Bus Specification V1.1, which can be downloaded from www.smbus.org. The bq24745 uses the SMBus Read-Word and Write-Word protocols (Figure 33) to communicate with the smart battery. The bq24745 performs only as an SMBus slave device with address 0b0001 001\_ (0x12) and does not initiate communication on the bus. In addition, the bq24745 has two identification (ID) registers (0xFE): a 16-bit device ID register and a 16-bit manufacturer ID register (0xFF).

The data (SDA) and clock (SCL) pins have Schmitt-trigger inputs that can accommodate slow edges. Choose pullup resistors (10 k $\Omega$ , typ.) for SDA and SCL to achieve rise times according to the SMBus specifications.

Communication starts when the master signals a START condition, which is a high-to-low transition on SDA, while SCL is high. When the master has finished communicating, the master issues a STOP condition, which is a low-to-high transition on SDA, while SCL is high. The bus is then free for another transmission. Figure 34 and Figure 35 show the timing diagram for signals on the SMBus interface. The address byte, command byte, and data bytes are transmitted between the START and STOP conditions. The SDA state changes only while SCL is low, except for the START and STOP conditions. Data is transmitted in 8-bit bytes and is sampled on the rising edge of SCL. Nine clock cycles are required to transfer each byte in or out of the bq24745 because either the master or the slave acknowledges the receipt of the correct byte during the ninth clock cycle.

# a) Write-Word Format

| s   | SLAVE<br>ADDRESS | w    | ACK | COMMAND<br>BYTE | ACK | LOW DATA<br>BYTE | ACK | HIGH DATA<br>BYTE | ACK | Р |

|-----|------------------|------|-----|-----------------|-----|------------------|-----|-------------------|-----|---|

|     | 7 BITS           | 1b   | 1b  | 8 BITS          | 1b  | 8 BITS           | 1b  | 8 BITS            | 1b  |   |

|     | MSB LSB          | 0    | 0   | MSB LSB         | 0   | MSB LSB          | 0   | MSB LSB           | 0   |   |

| Pre | eset to 0b000    | 1001 |     |                 |     | D7 D0            |     | D15 D8            |     |   |

ChargeCurrent() = 0x14ChargeVoltage() = 0x15= 0x3FInputCurrent()

# b) Read-Word Format

| s   | SLAVE<br>ADDRESS             | w  | ACK | COMMAND<br>BYTE | ACK | s         | SLAVE<br>ADDRESS | R  | ACK   | LOW DATA<br>BYTE | ACK    | HIGH DATA<br>BYTE | NACK | Р |

|-----|------------------------------|----|-----|-----------------|-----|-----------|------------------|----|-------|------------------|--------|-------------------|------|---|

|     | 7 BITS                       | 1b | 1b  | 8 BITS          | 1b  |           | 7 BITS           | 1b | 1b    | 8 BITS           | 1b     | 8 BITS            | 1b   |   |

|     | MSB LSB                      | 0  | 0   | MSB LSB         | 0   |           | MSB LSB          | 1  | 0     | MSB LSB          | 0      | MSB LSB           | 1    |   |

| Pre | Preset to 0b0001001 Register |    |     |                 |     | Preset to |                  |    | D7 D0 |                  | D15 D8 |                   |      |   |

0b0001010

Preset to 0b0001001

ChargeMode() = 0x14

ChargeMode() = 0x15

ChargeMode() = 0x3F

#### LEGEND:

S = START CONDITION OR REPEATED START CONDITION ACK = ACKNOWLEDGE (LOGIC-LOW) W = WRITE BIT (LOGIC-LOW)

P = STOP CONDITION NACK = NOT ACKNOWLEDGE (LOGIC-HIGH) R = READ BIT (LOGIC-HIGH)

MASTER TO SLAVE SLAVE TO MASTER

Figure 33. SMBus Write-Word and Read-Word Protocols

Figure 34. SMBus Write Timing

Figure 35. SMBus Read Timing

# **BATTERY VOLTAGE REGULATION**

The bq24745 uses a high-accuracy voltage regulator for charging voltage. The battery voltage regulation setting is programmed by the host microcontroller ( $\mu$ C), through the SMBus interface that sets an 11-bit DAC. The battery termination voltage is a function of the battery chemistry. Consult the battery manufacturer to determine this voltage.

The VFB pin is used to sense the battery voltage for voltage regulation and should be connected as close to the battery as possible, or directly on the output capacitor. A 0.1-µF ceramic capacitor from VFB to GND is recommended to be as close to the VFB pin as possible to decouple high-frequency noise.

To set the output charge-voltage regulation limit, use the SMBus to write a 16-bit ChargeVoltage() command using the data format listed in Table 3. The ChargeVoltage() command uses the Write-Word protocol (see Figure 33). The command code for ChargeVoltage() is 0x15 (0b0001 0101). The bq24745 provides a 1.024-V to 19.200-V charge voltage range, with 16-mV resolution. Setting ChargeVoltage() below 1.024 V or above 19.2 V clears the DAC and terminates charge.

On reset, the ChargeVoltage() and ChargeCurrent() values are cleared (0) and the charger remains off until both the ChargeVoltage() and the ChargeCurrent() commands are sent. During reset, both high-side and low-side FETs remain off until the charger is started.

BIT **BIT NAME** DESCRIPTION 0 Not used Not used 2 Not used 3 Not used 4 Charge voltage, DACV 0 0 = Adds 0 mV of charger voltage 1 = Adds 16 mV of charger voltage<sup>(1)</sup> 5 Charge voltage, DACV 1 0 = Adds 0 mV of charger voltage 1 = Adds 32 mV of charger voltage<sup>(1)</sup> 6 Charge voltage, DACV 2 0 = Adds 0 mV of charger voltage 1 = Adds 64 mV of charger voltage (1) 7 Charge voltage, DACV 3 0 = Adds 0 mV of charger voltage 1 = Adds 128 mV of charger voltage<sup>(1)</sup> 8 Charge voltage, DACV 4 0 = Adds 0 mV of charger voltage 1 = Adds 256 mV of charger voltage<sup>(1)</sup> 9 Charge voltage, DACV 5 0 = Adds 0 mV of charger voltage 1 = Adds 512 mV of charger voltage<sup>(1)</sup> 10 Charge voltage, DACV 6 0 = Adds 0 mV of charger voltage 1 = Adds 1,024 mV of charger voltage

Table 3. Charge Voltage Register (0x15)

(1) Must be used in conjunction with other bits for a minimum output of 1024 mV

# Table 3. Charge Voltage Register (0x15) (continued)

| BIT | BIT NAME                | DESCRIPTION                                                               |

|-----|-------------------------|---------------------------------------------------------------------------|

| 11  | Charge voltage, DACV 7  | 0 = Adds 0 mV of charger voltage<br>1 = Adds 2,048 mV of charger voltage  |

| 12  | Charge voltage, DACV 8  | 0 = Adds 0 mV of charger voltage<br>1 = Adds 4,096 mV of charger voltage  |

| 13  | Charge voltage, DACV 9  | 0 = Adds 0 mV of charger voltage<br>1 = Adds 8,192 mV of charger voltage  |

| 14  | Charge voltage, DACV 10 | 0 = Adds 0 mV of charger voltage<br>1 = Adds 16,384 mV of charger voltage |

| 15  | -                       | Not used                                                                  |

# **CHARGE CURRENT REGULATION**

The ChargeCurrent() SMBus 6-bit DAC register sets the maximum charging current. Battery current is sensed by resistor  $R_{SR}$  connected between the CSOP and CSON pins. The maximum full-scale differential voltage between CSOP and CSON is 80.64 mV. Thus, for a 0.010- $\Omega$  sense resistor, the maximum charging current is 8.064 A.

The CSOP and CSON pins are used to measure the voltage across  $R_{SR}$ , which has a default value of 10 m $\Omega$ . However, resistors of other values can also be used. A larger sense resistor results in a larger sense voltage and higher regulation accuracy, but at the expense of higher conduction loss.

To set the charge current, use the SMBus to write a 16-bit ChargeCurrent() command using the data format listed in Table 4. The ChargeCurrent() command uses the Write-Word protocol (see Figure 33). The command code for ChargeCurrent() is 0x14 (0b0001 0100). When using a  $10-m\Omega$  sense resistor, the bq24745 provides a charge current range of 128 mA to 8.064 A, with 128-mA resolution. Set ChargeCurrent() to 0 to terminate charging. Setting ChargeCurrent() below 128 mA, or above 8.064 A, clears DAC and terminates charge.

The bq24745 includes a foldback current limit when the battery voltage is low. If the battery voltage is less than 3.6 V but above 2.5 V, any charge current limit above 3 A is clamped at 3 A. If the battery voltage is less than 2.5 V, the charge current is set to 220 mA until that voltage rises above 2.7 V. The ChargeCurrent() register is preserved and becomes active again when the battery voltage is higher than 2.7 V. This function effectively provides a fold-back current limit, which protects the charger during short circuit and overload.

On reset, the ChargeVoltage() and ChargeCurrent() values are cleared (0) and the charger remains off until both the ChargeVoltage() and the ChargeCurrent() commands are sent. During reset, both high-side and low-side FETs remain off until the charger is started.

Table 4. Charge Current Register (0x14), Using 10-m $\Omega$  Sense Resistor

| BIT | BIT NAME               | DESCRIPTION                                                              |

|-----|------------------------|--------------------------------------------------------------------------|

| 0   | _                      | Not used                                                                 |

| 1   | _                      | Not used                                                                 |

| 2   | _                      | Not used                                                                 |

| 3   | -                      | Not used                                                                 |

| 4   | -                      | Not used                                                                 |

| 5   | _                      | Not used                                                                 |

| 6   | _                      | Not used                                                                 |

| 7   | Charge current, DACI 0 | 0 = Adds 0 mA of charger current<br>1 = Adds 128 mA of charger current   |

| 8   | Charge current, DACI 1 | 0 = Adds 0 mA of charger current<br>1 = Adds 256 mA of charger current   |

| 9   | Charge current, DACI 2 | 0 = Adds 0 mA of charger current<br>1 = Adds 512 mA of charger current   |

| 10  | Charge current, DACI 3 | 0 = Adds 0 mA of charger current<br>1 = Adds 1,024 mA of charger current |

| 11  | Charge current, DACI 4 | 0 = Adds 0 mA of charger current<br>1 = Adds 2,048 mA of charger current |

Product Folder Link(s): bq24745

www.ti.com

Table 4. Charge Current Register (0x14), Using 10-mΩ Sense Resistor (continued)

| BIT | BIT NAME               | DESCRIPTION                                                              |

|-----|------------------------|--------------------------------------------------------------------------|

| 12  | Charge current, DACI 5 | 0 = Adds 0 mA of charger current<br>1 = Adds 4,096 mA of charger current |

| 13  |                        | Not used                                                                 |

| 14  |                        | Not used                                                                 |

| 15  |                        | Not used                                                                 |

# INPUT ADAPTER CURRENT REGULATION

The total input current from an ac adapter or other dc source is a function of the system supply current and the battery charging current. System current normally fluctuates as portions of the system are powered up or down. Without dynamic power management (DPM), the source must be able to supply the maximum system current and the maximum charger input current simultaneously. By using DPM, the input current regulator reduces the charging current to keep the input current from exceeding the limit set by the Input Current SMBus 6-bit DAC register. With high-accuracy limiting, the current capability of the ac adaptor can be lowered, reducing system cost.

The CSSP and CSSN pins are used to sense  $R_{AC}$  with a default value of 10 m $\Omega$ . However, resistors of other values can also be used. A larger a sense resistor results in a larger sense voltage and a higher regulation accuracy, but at the expense of higher conduction loss.

The total input current, from a wall cube or other dc source, is the sum of the system supply current and the current required by the charger. When the input current exceeds the set input current limit, the bq24745 decreases the charge current to provide priority to system load current. As the system supply rises, the available charge current drops linearly to zero.

$$I_{\text{NPUT}} = I_{\text{SYSTEM}} + \left[ \frac{I_{\text{LOAD}} \times V_{\text{BATTERY}}}{V_{\text{IN}} \times \eta} \right] + I_{\text{BIAS}}$$

(1)

where n is the efficiency of the dc-dc converter (typically 85% to 95%).

To set the input current limit, use the SMBus to write a 16-bit InputCurrent() command using the data format listed in Table 5. The InputCurrent() command uses the Write-Word protocol (see Figure 33). The command code for InputCurrent() is 0x3F (0b0011 1111). When using a 10-mΩ sense resistor, the bq24745 provides an input-current limit range of 256 mA to 11.008 A, with 256-mA resolution. InputCurrent() settings from 1 mA to 256 mA clears DAC and terminates charge. On reset the input current limit is 256 mA.

Table 5. Input Current Register (0x3F), Using 10-m $\Omega$  Sense Resistor.

| BIT | BIT NAME               | DESCRIPTION                                                              |

|-----|------------------------|--------------------------------------------------------------------------|

| 0   | -                      | Not used                                                                 |

| 1   | _                      | Not used                                                                 |

| 2   | _                      | Not used                                                                 |

| 3   | -                      | Not used                                                                 |

| 4   | -                      | Not used                                                                 |

| 5   | -                      | Not used                                                                 |

| 6   | _                      | Not used                                                                 |

| 7   | Charge current, DACS 0 | 0 = Adds 0 mA of charger current<br>1 = Adds 256 mA of charger current   |

| 8   | Charge current, DACS 1 | 0 = Adds 0 mA of charger current<br>1 = Adds 512 mA of charger current   |

| 9   | Charge current, DACS 2 | 0 = Adds 0 mA of charger current<br>1 = Adds 1,024 mA of charger current |

| 10  | Charge current, DACS 3 | 0 = Adds 0 mA of charger current<br>1 = Adds 2,048 mA of charger current |

| 11  | Charge current, DACS 4 | 0 = Adds 0 mA of charger current<br>1 = Adds 4,096 mA of charger current |

# Table 5. Input Current Register (0x3F), Using 10-m $\Omega$ Sense Resistor. (continued)

| BIT | BIT NAME               | DESCRIPTION                                                                             |

|-----|------------------------|-----------------------------------------------------------------------------------------|

| 12  | Charge current, DACS 5 | 0 = Adds 0 mA of charger current<br>1 = Adds 8,192 mA of charger current; 11,008 mA max |

| 13  | _                      | Not used                                                                                |

| 14  | _                      | Not used                                                                                |

| 15  | _                      | Not used                                                                                |