Sample &

🖥 Buy

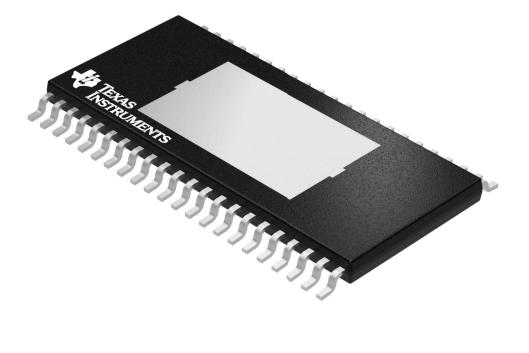

**TAS5614LA**

ZHCS930A - MAY 2012 - REVISED MARCH 2015

TAS5614LA 150W 立体声/300W 单声道 PurePath™ HD 数字输入 D 类功率级

Technical

Documents

#### 特性 1

- PurePath<sup>™</sup> HD 集成反馈提供:

- 1W 功率/4Ω 负载条件下的总谐波失真 (THD) 为 0.03%

- 电源抑制比 (PSRR) > 65dB (无输入信号)

- (A 加权) 信噪比 (SNR) > 105dB

- 用于控制 G 类电源的预钳位输出

- 通过使用 60mΩ 输出金属氧化物半导体场效应晶体 管 (MOSFET) 减小了散热器体积,满输出功率时效 率 > 90%

- 总谐波失真+噪声 (THD+N) 为 10% 时的输出功率

- 150W/4Ω,桥接负载 (BTL) 立体声配置

- 300W/2Ω,并行桥接负载 (PBTL) 单声道配置

- THD+N 为 1% 时的输出功率

- 125W/4Ω,桥接负载 (BTL) 立体声配置

- 65W/8Ω,桥接负载 (BTL) 立体声配置

- 启动时无喀哒声和噼啪声

- 采用具有错误报告功能的自我保护设计,包含欠压 保护 (UVP)、过热保护和短路保护

- 采用推荐的系统设计时,符合电磁干扰 (EMI) 标准

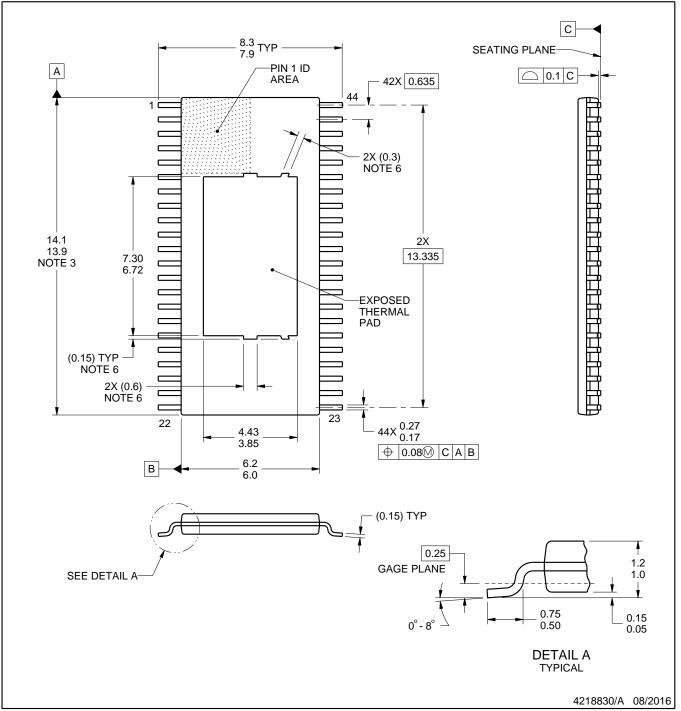

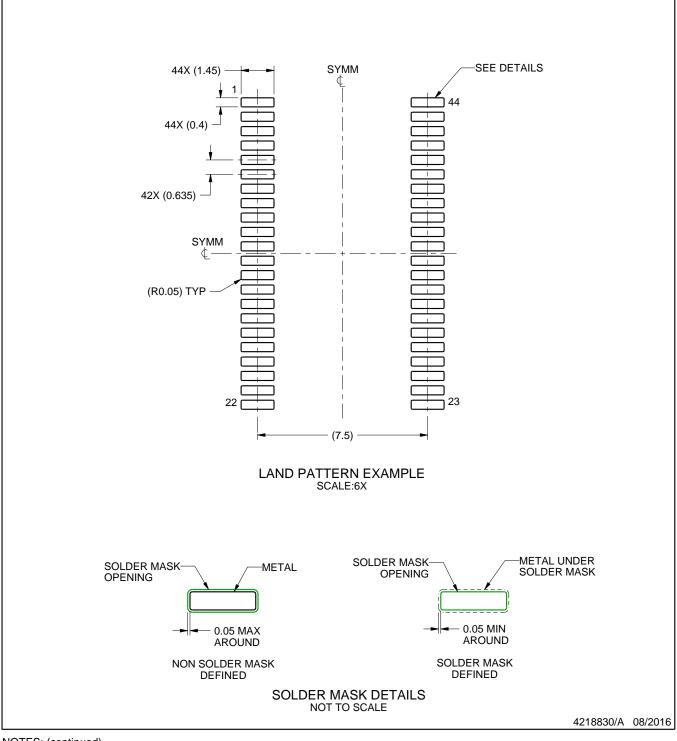

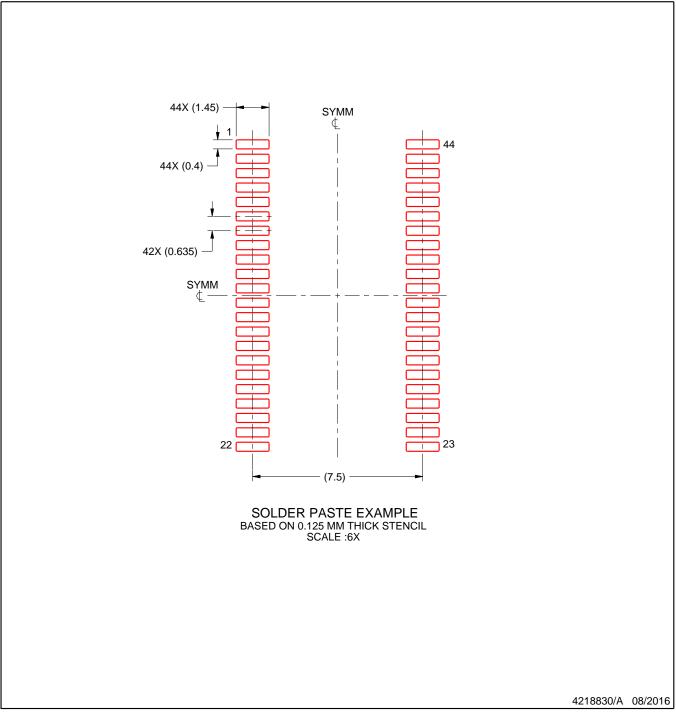

- 采用 44 引脚散热薄型小外形尺寸 (HTSSOP) • (DDV) 封装,减小了电路板尺寸

- 2 应用

- 蓝光碟™ 和 DVD 接收器

- 高功率条形音响

- 有源超低音扬声器和有源扬声器

- 微型 Combo 系统 ٠

### 3 说明

Tools &

Software

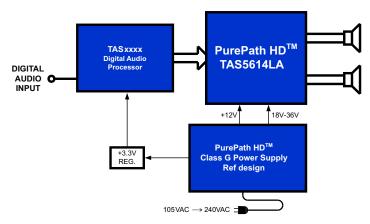

TAS5614LA 器件是一款基于 TAS5614LA 的功能优化 D 类功率放大器。

Support &

Community

2.2

TAS5614LA 使用大型金属氧化物半导体场效应晶体管 (MOSFET) 提升功率效率,并采用新型栅极驱动方案 降低空闲状态下和输出信号较低时的损耗,从而减小散 热器尺寸。

该器件可使用独特的预钳位输出信号来控制 G 类电 源。 这一优势与 TAS5614LA 的低空闲损耗和高功率 效率相结合,可实现行业领先水平的效率,从而确保构 建超级"绿色"系统。

TAS5614LA 使用恒定电压增益。 内部匹配增益电阻器 确保了一个高电源抑制比, 使得输出电压只取决于音频 输入电压并避免了任何电源的人工缺陷。

TAS5614LA 的高集成度使得放大器易于使用: 另外, 使用 TI 的参考原理图和 PCB 布局缩短了设计时间。 TAS5614LA 采用节省空间的表面贴装 44 引脚 HTSSOP 封装。

器件信息(1)

| 器件型号      | 封装          | 封装尺寸(标称值)        |

|-----------|-------------|------------------|

| TAS5614LA | HTSSOP (44) | 14.00mm x 6.10mm |

(1) 要了解所有可用封装,请见数据表末尾的可订购产品附录。

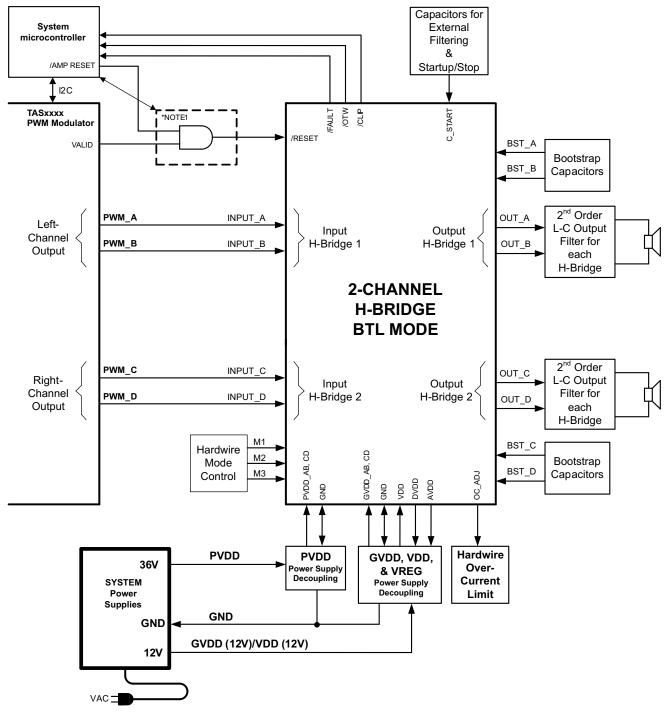

### TAS5614LA 典型应用框图

目录

| 1 | 特性     | . 1 |

|---|--------|-----|

| 2 | 应用     | . 1 |

| 3 | 说明     | . 1 |

| 4 | 修订历史记录 | . 2 |

Pin Configuration and Functions ...... 3

Specifications...... 4

Absolute Maximum Ratings ...... 4 ESD Ratings...... 4

Recommended Operating Conditions ...... 5

Thermal Information ...... 5

6.6 Audio Specification Stereo (BTL)...... 7

| 7 | Deta | ailed Description 12                  |

|---|------|---------------------------------------|

|   | 6.9  | Typical Characteristics               |

|   | 6.8  | Audio Specification Mono (PBTL)8      |

|   | 6.7  | Audio Specification 4 Channels (SE) 7 |

#### 修订历史记录 4

5 6

6.1

6.2

6.3 6.4

6.5

## Changes from Original (May 2012) to Revision A

已添加 引脚配置和功能部分, ESD 额定值表,特性描述部分,器件功能模式,应用和实施部分,电源相关建议部分, 布局部分,器件和文档支持部分以及机械、封装和可订购信息部分.....1

|    | 71   | Our and and                 | 40 |

|----|------|-----------------------------|----|

|    |      | Overview                    |    |

|    | 7.2  | Functional Block Diagrams   | 13 |

|    | 7.3  | Feature Description         | 15 |

|    | 7.4  | Device Functional Modes     | 19 |

| 8  | Арр  | lication and Implementation | 21 |

|    | 8.1  | Application Information     | 21 |

|    | 8.2  | Typical Applications        | 21 |

| 9  | Pow  | ver Supply Recommendations  | 31 |

| 10 | Lay  | out                         | 31 |

|    | 10.1 | Layout Guidelines           | 31 |

|    | 10.2 | Layout Example              | 33 |

| 11 | 器件   | 和文档支持                       | 35 |

|    | 11.1 | 商标                          | 35 |

|    | 11.2 | 静电放电警告                      | 35 |

|    | 11.3 | 术语表                         | 35 |

| 12 | 机械   | 载、封装和可订购信息                  | 35 |

| 12 |      | 、封装和可订购信息                   |    |

EXAS **ISTRUMENTS**

www.ti.com.cn

Page

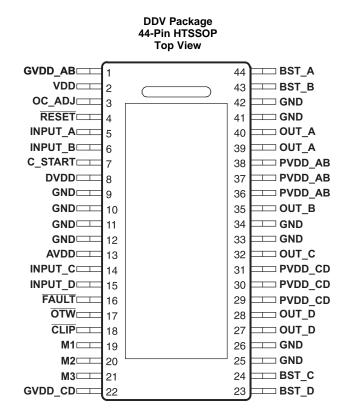

## 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN     |                                          | I/O/P <sup>(1)</sup> | DESCRIPTION                                 |  |  |

|---------|------------------------------------------|----------------------|---------------------------------------------|--|--|

| NAME    | NO.                                      | 1/0/P***             | DESCRIPTION                                 |  |  |

| AVDD    | 13                                       | Р                    | Internal voltage regulator, analog section  |  |  |

| BST_A   | 44                                       | Р                    | Bootstrap pin, A-side                       |  |  |

| BST_B   | 43                                       | Р                    | Bootstrap pin, B-side                       |  |  |

| BST_C   | 24                                       | Р                    | Bootstrap pin, C-side                       |  |  |

| BST_D   | 23                                       | Р                    | Bootstrap pin, D-side                       |  |  |

| CLIP    | 18                                       | 0                    | Clipping warning, open drain, active low    |  |  |

| C_START | 7                                        | 0                    | Start-up ramp                               |  |  |

| DVDD    | 8                                        | Р                    | Internal voltage regulator, digital section |  |  |

| FAULT   | 16                                       | 0                    | Shutdown signal, open drain, active low     |  |  |

| GND     | 9, 10, 11, 12, 25,<br>26, 33, 34, 41, 42 | Р                    | Ground                                      |  |  |

| GVDD_AB | 1                                        | Р                    | Gate-drive voltage supply, AB-side          |  |  |

| GVDD_CD | 22                                       | Р                    | Gate-drive voltage supply, CD-side          |  |  |

| INPUT_A | 5                                        | I                    | PWM input signal for half-bridge A          |  |  |

| INPUT_B | 6                                        | I                    | PWM input signal for half-bridge B          |  |  |

| INPUT_C | 14                                       | I                    | PWM input signal for half-bridge C          |  |  |

| INPUT_D | 15                                       | I                    | PWM input signal for half-bridge D          |  |  |

| M1      | 19                                       | I                    | Mode selection 1 (LSB)                      |  |  |

| M2      | 20                                       | I                    | Mode selection 2                            |  |  |

| M3      | 21                                       | I                    | Mode selection 3 (MSB)                      |  |  |

| OC_ADJ  | 3                                        | 0                    | Overcurrent threshold programming pin       |  |  |

(1) I = Input, O = Output, P = Power

Copyright © 2012-2015, Texas Instruments Incorporated

STRUMENTS

XAS

### Pin Functions (continued)

| PIN       |            | I/O/P <sup>(1)</sup> | DESCRIPTION                                     |

|-----------|------------|----------------------|-------------------------------------------------|

| NAME      | NO.        | 1/0/P*/              | DESCRIPTION                                     |

| OTW       | 17         | 0                    | Overtemperature warning, open drain, active low |

| OUT_A     | 39, 40     | 0                    | Output, half-bridge A                           |

| OUT_B     | 35         | 0                    | Output, half-bridge B                           |

| OUT_C     | 32         | 0                    | Output, half-bridge C                           |

| OUT_D     | 27, 28     | 0                    | Output, half-bridge D                           |

| PVDD_AB   | 36, 37, 38 | Р                    | PVDD supply for half-bridge A and B             |

| PVDD_CD   | 29, 30, 31 | Р                    | PVDD supply for half-bridge C and D             |

| RESET     | 4          | I                    | Device reset input, active low                  |

| VDD       | 2          | Р                    | Input power supply                              |

| PowerPAD™ | _          | Р                    | Ground, connect to grounded heat sink           |

## 6 Specifications

### 6.1 Absolute Maximum Ratings

over operating free-air temperature range unless otherwise noted (1)

|                                                                                                               | MIN  | MAX  | UNIT |

|---------------------------------------------------------------------------------------------------------------|------|------|------|

| VDD to GND, GVDD_X <sup>(2)</sup> to GND                                                                      | -0.3 | 13.2 | V    |

| PVDD_X <sup>(2)</sup> to GND <sup>(3)</sup> , OUT_X to GND <sup>(3)</sup> , BST_X to GVDD_X <sup>(2)(3)</sup> | -0.3 | 50   | V    |

| BST_X to GND <sup>(3)(4)</sup>                                                                                | -0.3 | 62.5 | V    |

| DVDD to GND                                                                                                   | -0.3 | 4.2  | V    |

| AVDD to GND                                                                                                   | -0.3 | 8.5  | V    |

| OC_ADJ, M1, M2, M3, C_START, INPUT_X to GND                                                                   | -0.3 | 4.2  | V    |

| RESET, FAULT, OTW, CLIP, to GND                                                                               | -0.3 | 4.2  | V    |

| Maximum continuous sink current (FAULT, OTW, CLIP)                                                            |      | 9    | mA   |

| Maximum operating junction temperature, T <sub>J</sub>                                                        | 0    | 150  | °C   |

| Lead temperature                                                                                              |      | 260  | °C   |

| Storage temperature, T <sub>stg</sub>                                                                         | -40  | 150  | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) GVDD\_X and PVDD\_X represents a full bridge gate drive or power supply. GVDD\_X is GVDD\_AB or GVDD\_CD, PVDD\_X is PVDD\_AB or PVDD\_CD

(3) These voltages represents the DC voltage + peak AC waveform measured at the pin of the device in all conditions.

(4) Maximum BST\_X to GND voltage is the sum of maximum PVDD to GND and GVDD to GND voltages minus a diode drop.

### 6.2 ESD Ratings

|                    |                         |                                                                                   | VALUE | UNIT |

|--------------------|-------------------------|-----------------------------------------------------------------------------------|-------|------|

| M                  | Electrostatic discharge | Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins $^{\left(1\right)}$  | 2000  | N/   |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged device model (CDM), per JEDEC specification JESD22-C101, all $pins^{(2)}$ | 500   | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

|                         |                                                 |                                  |                                                                                                                              | MIN  | NOM | MAX  | UNIT |

|-------------------------|-------------------------------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------|------|-----|------|------|

| PVDD_X                  | Full-bridge supply                              |                                  | DC supply voltage                                                                                                            | 12   | 36  | 38   | V    |

| GVDD_X                  | Supply for logic regula<br>gate-drive circuitry | ators and                        | DC supply voltage                                                                                                            | 10.8 | 12  | 13.2 | V    |

| VDD                     | Digital regulator suppl                         | y voltage                        | DC supply voltage                                                                                                            | 10.8 | 12  | 13.2 | V    |

|                         |                                                 | BTL                              | Output filter: $L = 10 \mu H$ , 1 $\mu F$ .                                                                                  | 3.0  | 4.0 |      |      |

| RL                      | Load impedance                                  | SE                               | Output AD modulation,                                                                                                        | 1.5  | 3.0 |      | Ω    |

|                         |                                                 | PBTL                             | switching frequency > 350 kHz.                                                                                               | 1.5  | 2.0 |      |      |

| L <sub>OUTPUT</sub>     | Output filter inductance                        |                                  | Minimum inductance at overcurrent<br>limit, including inductor tolerance,<br>temperature and possible inductor<br>saturation | 5    |     |      | μH   |

| F <sub>PWM</sub>        | PWM frame rate                                  |                                  |                                                                                                                              | 352  | 384 | 500  | kHz  |

| C <sub>PVDD</sub>       | PVDD close decoupli                             | PVDD close decoupling capacitors |                                                                                                                              | 0.44 | 1   |      | μF   |

| C START                 | Ctart un roma conceit                           | ~ <b>r</b>                       | BTL and PBTL configuration                                                                                                   |      | 100 |      | nF   |

| C_START                 | Start-up ramp capacit                           | 01                               | SE and 1xBTL+2xSE configuration                                                                                              |      | 1   |      | μF   |

| R <sub>OC</sub>         | Overcurrent programr resistor                   | ning                             | Resistor tolerance = 5%                                                                                                      | 24   |     | 33   | kΩ   |

| R <sub>OC_LATCHED</sub> | Overcurrent programr resistor                   | ning                             | Resistor tolerance = 5%                                                                                                      | 47   | 62  | 68   | kΩ   |

| TJ                      | Junction temperature                            |                                  |                                                                                                                              | 0    |     | 125  | °C   |

### 6.4 Thermal Information

|                       | THERMAL METRIC <sup>(1)</sup>                | DDV (HTSSOP) | UNIT |

|-----------------------|----------------------------------------------|--------------|------|

|                       |                                              | 44 PINS      |      |

| $R_{\theta JH}$       | Junction-to-heat sink thermal resistance     | 2.3          |      |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 0.8          |      |

| $R_{\theta JB}$       | Junction-to-board thermal resistance         | 2.1          | 8CAN |

| $\Psi_{JT}$           | Junction-to-top characterization parameter   | 0.8          | °C/W |

| Ψ <sub>JB</sub>       | Junction-to-board characterization parameter | 2.1          |      |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | n/a          |      |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

#### TAS5614LA

ZHCS930A-MAY 2012-REVISED MARCH 2015

NSTRUMENTS www.ti.com.cn

ÈXAS

### 6.5 Electrical Characteristics

$\underline{PVDD}_X = 36 \text{ V}, \text{ } \text{GVDD}_X = 12 \text{ V}, \text{ } \text{VDD} = 12 \text{ V}, \text{ } \text{T}_{\text{C}} \text{ (Case temperature)} = 75^{\circ}\text{C}, \text{ } \text{f}_{\text{S}} = 384 \text{ kHz}, \text{ } \text{unless otherwise specified}.$

|                                                | PARAMETER                                                                             | TEST CONDITIONS                                                                              | MIN | TYP  | MAX | UNIT   |

|------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-----|------|-----|--------|

| INTERNAL VOLTAGE R                             | REGULATOR AND CURRENT CONSUMP                                                         | TION                                                                                         |     |      |     |        |

| DVDD                                           | Voltage regulator, only used as a reference node                                      | VDD = 12 V                                                                                   | 3.0 | 3.3  | 3.6 | V      |

| AVDD                                           | Voltage regulator, only used as a reference node                                      | VDD = 12 V                                                                                   |     | 7.8  |     | V      |

|                                                |                                                                                       | Operating, 50% duty cycle                                                                    |     | 20   |     |        |

| VDD                                            | VDD supply current                                                                    | Idle, reset mode                                                                             |     | 20   |     | mA     |

|                                                |                                                                                       | 50% duty cycle                                                                               |     | 9    |     |        |

| GVDD_X                                         | Gate-supply current per full-bridge                                                   | Reset mode                                                                                   |     | 2    |     | mA     |

|                                                |                                                                                       | 50% duty cycle without load                                                                  |     | 23   |     |        |

| PVDD_X                                         | Full-bridge idle current                                                              | RESET low                                                                                    |     | 1.9  |     | mA     |

|                                                |                                                                                       | VDD and GVDD_X at 0V                                                                         |     | 0.35 |     |        |

| OUTPUT-STAGE MOSF                              | ETs                                                                                   | · · ·                                                                                        |     |      |     |        |

| R <sub>DS(on)</sub> , LS                       | Drain-to-source resistance, low side (LS)                                             | $T_J = 25^{\circ}C$ , excludes metalization                                                  |     | 60   | 100 | mΩ     |

| R <sub>DS(on), HS</sub>                        | Drain-to-source resistance, high side (HS)                                            | GVDD = 12 V                                                                                  |     | 60   | 100 | mΩ     |

| O PROTECTION                                   |                                                                                       | · I                                                                                          |     |      |     |        |

| V <sub>uvp,GVDD</sub>                          | Undervoltage protection limit,                                                        |                                                                                              |     | 8.5  |     | V      |

| V <sub>uvp,GVDD, hyst</sub> <sup>(1)</sup>     | GVDD_X                                                                                |                                                                                              |     | 0.7  |     | V      |

| V <sub>uvp,VDD</sub>                           |                                                                                       |                                                                                              |     | 8.5  |     | V      |

| vuvp,VDD, hyst <sup>(1)</sup>                  | Undervoltage protection limit, VDD                                                    |                                                                                              |     | 0.7  |     | V      |

| V <sub>uvp,PVDD</sub>                          |                                                                                       |                                                                                              |     | 8.5  |     | V      |

| V <sub>uvp,PVDD,hyst</sub> <sup>(1)</sup>      | Undervoltage protection limit, PVDD_X                                                 |                                                                                              |     | 0.7  |     | V      |

| OTW <sup>(1)</sup>                             | Overtemperature warning                                                               |                                                                                              | 115 | 125  | 135 | °C     |

| OTW <sub>hyst</sub> <sup>(1)</sup>             | Temperature drop needed below OTW temperature for OTW to be inactive after OTW event. |                                                                                              |     | 25   |     | °C     |

| OTE <sup>(1)</sup>                             | Overtemperature error                                                                 |                                                                                              | 145 | 155  | 165 | °C     |

| OTE-OTW <sub>differential</sub> <sup>(1)</sup> | OTE-OTW differential                                                                  |                                                                                              | -   | 30   |     | °C     |

| OTE <sub>HYST</sub> <sup>(1)</sup>             | A device reset is needed to clear<br>FAULT after an OTE event                         |                                                                                              |     | 25   |     | °C     |

| OLPC                                           | Overload protection counter                                                           | f <sub>PWM</sub> = 384 kHz                                                                   |     | 2.6  |     | ms     |

| loc                                            | Overcurrent limit protection                                                          | Resistor – programmable, nominal<br>peak current in 1- $\Omega$ load, ROC = 24<br>k $\Omega$ |     | 15   |     | A      |

|                                                | Overcurrent limit protection, latched                                                 | Resistor – programmable, nominal peak current in 1- $\Omega$ load, ROC = 62 k $\Omega$       |     | 15   |     | A      |

| ост                                            | Overcurrent response time                                                             | Time from application of short condition to Hi-Z of affected half bridge                     |     | 150  |     | ns     |

| PD                                             | Internal pulldown resistor at output of each half bridge                              | Connected when RESET is active to provide bootstrap charge. Not used in SE mode.             |     | 3    |     | mA     |

| STATIC DIGITAL SPEC                            | IFICATIONS                                                                            |                                                                                              |     |      |     |        |

| V <sub>IH</sub>                                | High level input voltage                                                              |                                                                                              | 1.9 |      |     | V      |

| V <sub>IL</sub>                                | Low level input voltage                                                               | INPUT_X, M1, M2, M3, RESET                                                                   |     |      | 0.8 | V      |

| LEAKAGE                                        | Input leakage current                                                                 |                                                                                              |     |      | 100 | μA     |

| OTW / SHUTDOWN (FA                             | .ULT)                                                                                 |                                                                                              |     |      |     |        |

| R <sub>INT_PU</sub>                            | Internal pullup resistance, OTW, CLIP,                                                | FAULT to DVDD                                                                                | 20  | 26   | 33  | kΩ     |

| V <sub>OH</sub>                                | High level output voltage                                                             | Internal pullup resistor                                                                     | 3   | 3.3  | 3.6 | V      |

| V <sub>OL</sub>                                | Low level output voltage                                                              | I <sub>O</sub> = 4 mA                                                                        |     | 200  | 500 | mV     |

| FANOUT                                         | Device fanout OTW, FAULT, CLIP                                                        | No external pullup                                                                           |     | 30   |     | device |

(1) Specified by design.

### 6.6 Audio Specification Stereo (BTL)

Audio performance is recorded as a chipset consisting of a PWM Processor (modulation index limited to 97.7%) and a TAS5614LA power stage with PCB and system configurations in accordance with recommended guidelines. Audio frequency = 1 kHz, PVDD\_X = 36 V, GVDD\_X = 12 V, R<sub>L</sub> = 4  $\Omega$ , f<sub>s</sub> = 384 kHz, R<sub>oc</sub> = 24 k $\Omega$ , T<sub>c</sub> = 75°C, Output Filter: L<sub>DEM</sub> = 10  $\mu$ H, C<sub>DEM</sub> = 1  $\mu$ F, unless otherwise noted.

|                   | PARAMETER                                      | TEST CONDITIONS                                 | MIN TY | P MAX | UNIT |  |

|-------------------|------------------------------------------------|-------------------------------------------------|--------|-------|------|--|

| Р                 | Dower output per channel                       | $R_L = 4 \Omega$ , 10% THD+N                    | 15     | 0     | W    |  |

| Po                | Power output per channel                       | $R_L = 4 \Omega$ , 1% THD+N                     | 12     | 5     | vv   |  |

| THD+N             | Total harmonic distortion + noise              | 1-W, 1-kHz signal                               | 0.03%  | 0     |      |  |

| V <sub>n</sub>    | Output integrated noise                        | A-weighted, AES17 measuring filter              | 18     | )     | μV   |  |

| V <sub>OS</sub>   | Output offset voltage                          | No signal                                       | 10     | 0 20  | mV   |  |

| SNR               | Signal-to-noise ratio <sup>(1)</sup>           | A-weighted, AES17 measuring filter              | 10     | 5     | dB   |  |

| DNR               | Dynamic range                                  | A-weighted, –60 dBFS (rel 1%<br>THD+N)          | 10     | 5     | dB   |  |

| P <sub>idle</sub> | Power dissipation due to Idle losses (IPVDD_X) | $P_{O} = 0$ , channels switching <sup>(2)</sup> | 1.0    | 6     | W    |  |

(1) SNR is calculated relative to 1% THD-N output level.

(2) Actual system idle losses also are affected by core losses of output inductors.

### 6.7 Audio Specification 4 Channels (SE)

Audio performance is recorded as a chipset consisting of a PWM Processor (modulation index limited to 97.7%) and a TAS5614LA power stage with PCB and system configurations in accordance with recommended guidelines. Audio frequency = 1 kHz, PVDD\_X = 36 V, GVDD\_X = 12 V, R<sub>L</sub> = 4  $\Omega$ , f<sub>S</sub> = 384 kHz, R<sub>OC</sub> = 24 k $\Omega$ , T<sub>C</sub> = 75°C, Output Filter: L<sub>DEM</sub> = 10  $\mu$ H, C<sub>DEM</sub> = 1  $\mu$ F, C<sub>DCB</sub> = 470  $\mu$ F, unless otherwise noted.

|                   | PARAMETER                                      | TEST CONDITIONS                                | MIN | ТҮР    | MAX | UNIT |  |

|-------------------|------------------------------------------------|------------------------------------------------|-----|--------|-----|------|--|

| р                 | Power output per channel                       | $R_L = 3 \Omega$ , 10% THD+N                   |     | 50     |     | W    |  |

| Po                | ower output per channel                        | $R_L = 3 \Omega$ , 1% THD+N                    |     | 42     |     |      |  |

| THD+N             | Total harmonic distortion + noise              | 1-W, 1-kHz signal                              | C   | 0.025% |     |      |  |

| V <sub>n</sub>    | Output integrated noise                        | A-weighted, AES17 measuring filter             |     | 180    |     | μV   |  |

| SNR               | Signal-to-noise ratio <sup>(1)</sup>           | A-weighted, AES17 measuring filter             |     | 102    |     | dB   |  |

| DNR               | Dynamic range                                  | A-weighted, –60 dBFS (rel 1%<br>THD+N)         |     | 102    |     | dB   |  |

| P <sub>idle</sub> | Power dissipation due to Idle losses (IPVDD_X) | $P_{O} = 0$ , channel switching <sup>(2)</sup> |     | 1.6    |     | W    |  |

(1) SNR is calculated relative to 1% THD-N output level.

(2) Actual system idle losses also are affected by core losses of output inductors.

TAS5614LA

ZHCS930A - MAY 2012 - REVISED MARCH 2015

www.ti.com.cn

### 6.8 Audio Specification Mono (PBTL)

Audio performance is recorded as a chipset consisting of a PWM Processor (modulation index limited to 97.7%) and a TAS5614LA power stage with PCB and system configurations in accordance with recommended guidelines. Audio frequency = 1 kHz, PVDD\_X = 36 V, GVDD\_X = 12 V, R<sub>L</sub> = 4  $\Omega$ , f<sub>S</sub> = 384 kHz, R<sub>OC</sub> = 24 k $\Omega$ , T<sub>C</sub> = 75°C, Output Filter: L<sub>DEM</sub> = 10  $\mu$ H, C<sub>DEM</sub> = 1  $\mu$ F, unless otherwise noted.

|                        | PARAMETER                                      | TEST CONDITIONS                                     | MIN TYP | MAX | UNIT |

|------------------------|------------------------------------------------|-----------------------------------------------------|---------|-----|------|

|                        |                                                | R <sub>L</sub> = 2 Ω, 10%, THD+N                    | 300     |     |      |

|                        |                                                | $R_L = 3 \Omega$ , 10% THD+N                        | 200     |     |      |

| P <sub>O</sub> Power o |                                                | R <sub>L</sub> = 4 Ω, 10% THD+N                     | 160     |     | W    |

|                        | Power output per channel                       | R <sub>L</sub> = 2 Ω, 1% THD+N                      | 250     |     | VV   |

|                        |                                                | R <sub>L</sub> = 3 Ω, 1% THD+N                      | 160     |     |      |

|                        |                                                | $R_L = 4 \Omega$ , 1% THD+N                         | 130     |     |      |

| THD+N                  | Total harmonic distortion + noise              | 1-W, 1-kHz signal                                   | 0.025%  |     |      |

| Vn                     | Output integrated noise                        | A-weighted, AES17 measuring filter                  | 180     |     | μV   |

| V <sub>OS</sub>        | Output offset voltage                          | No signal                                           | 10      | 20  | mV   |

| SNR                    | Signal to noise ratio <sup>(1)</sup>           | A-weighted, AES17 measuring filter                  | 105     |     | dB   |

| DNR                    | Dynamic range                                  | A-weighted, -60 dBFS (rel 1% THD)                   | 105     |     | dB   |

| P <sub>idle</sub>      | Power dissipation due to idle losses (IPVDD_X) | $P_{O} = 0$ , All channels switching <sup>(2)</sup> | 1.6     |     | W    |

(1) SNR is calculated relative to 1% THD-N output level.

(2) Actual system idle losses are affected by core losses of output inductors.

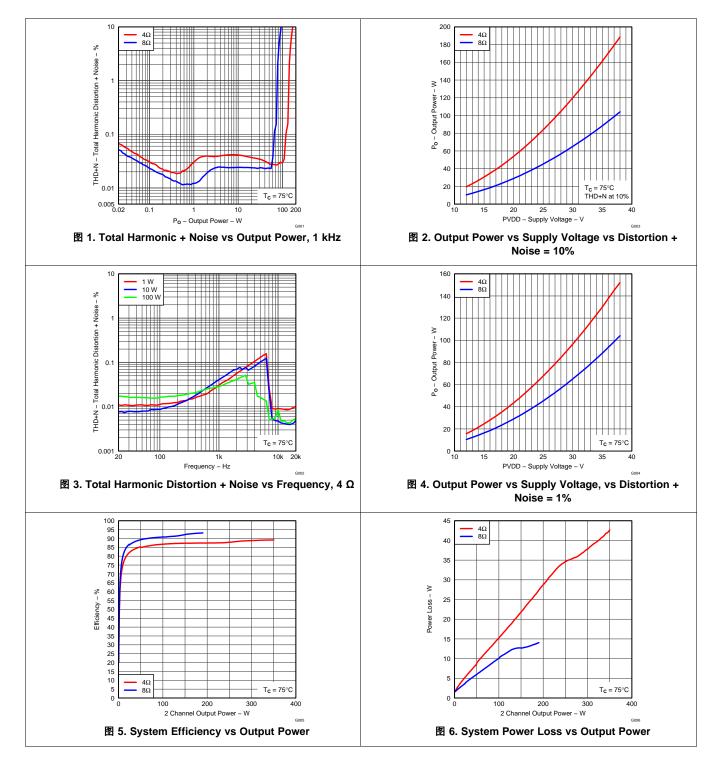

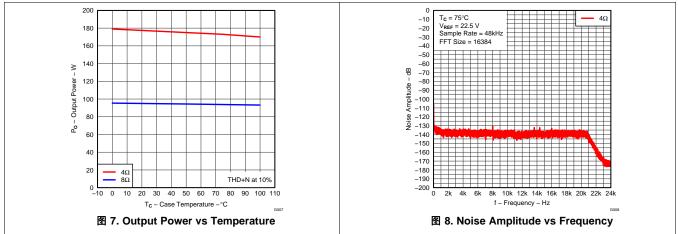

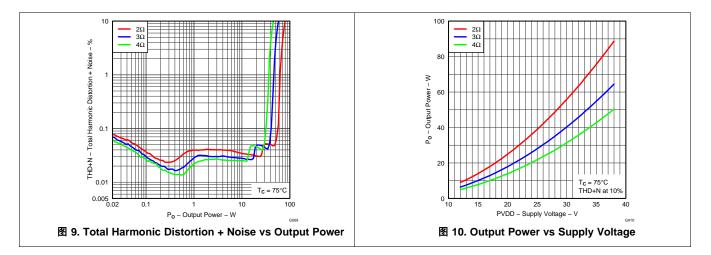

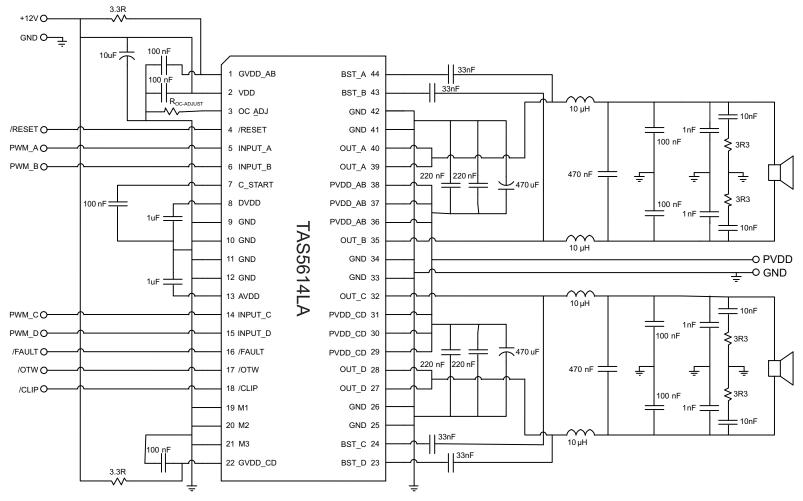

### 6.9 Typical Characteristics

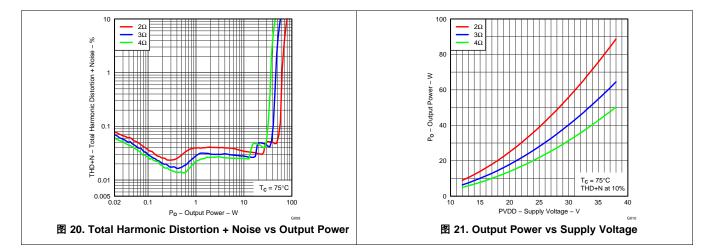

### 6.9.1 BTL Configuration

Measurement conditions are: 1 kHz, PVDD\_X = 36 V, GVDD\_X = 12 V,  $R_L = 4 \Omega$ ,  $f_S = 384$  kHz,  $R_{OC} = 24 k\Omega$ ,  $T_C = 75^{\circ}C$ , Output Filter:  $L_{DEM} = 10 \mu$ H,  $C_{DEM} = 1 \mu$ F, 20-Hz to 20-kHz BW (AES17 low-pass filter), unless otherwise noted.

## BTL Configuration (接下页)

Measurement conditions are: 1 kHz, PVDD\_X = 36 V, GVDD\_X = 12 V, R<sub>L</sub> = 4  $\Omega$ , f<sub>S</sub> = 384 kHz, R<sub>OC</sub> = 24 k $\Omega$ , T<sub>C</sub> = 75°C, Output Filter: L<sub>DEM</sub> = 10  $\mu$ H, C<sub>DEM</sub> = 1  $\mu$ F, 20-Hz to 20-kHz BW (AES17 low-pass filter), unless otherwise noted.

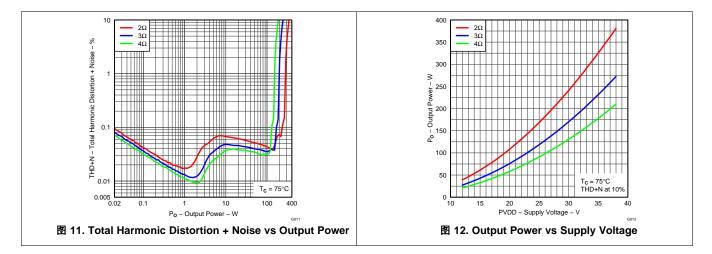

### 6.9.2 SE Configuration

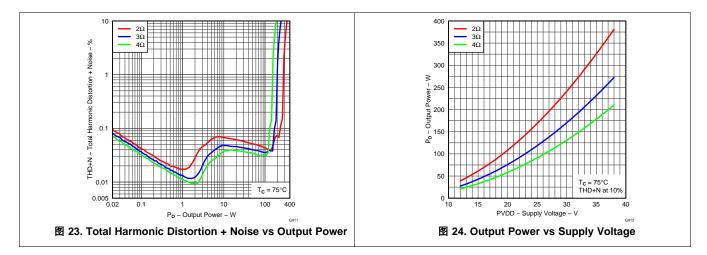

### 6.9.3 PBTL Configuration

## 7 Detailed Description

### 7.1 Overview

TAS5614LA is a PWM input, audio PWM (class-D) amplifier. The output of the TAS5614LA can be configured for single-ended, BTL (Bridge-Tied Load) or parallel BTL (PBTL) output. It requires two rails for power supply, PVDD and 12 V (GVDD and VDD).

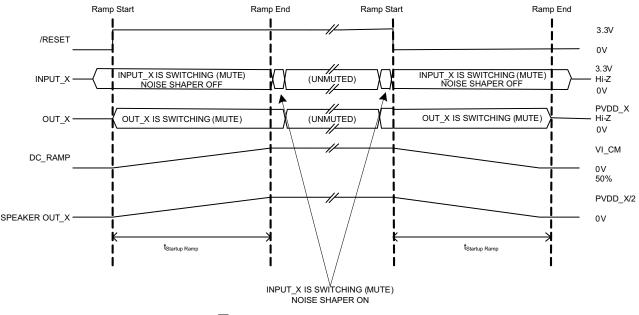

*Functional Block Diagrams* shows typical connections for BTL outputs. Detailed schematic can be viewed in TAS5614LA EVM user's guide (SLAU375).

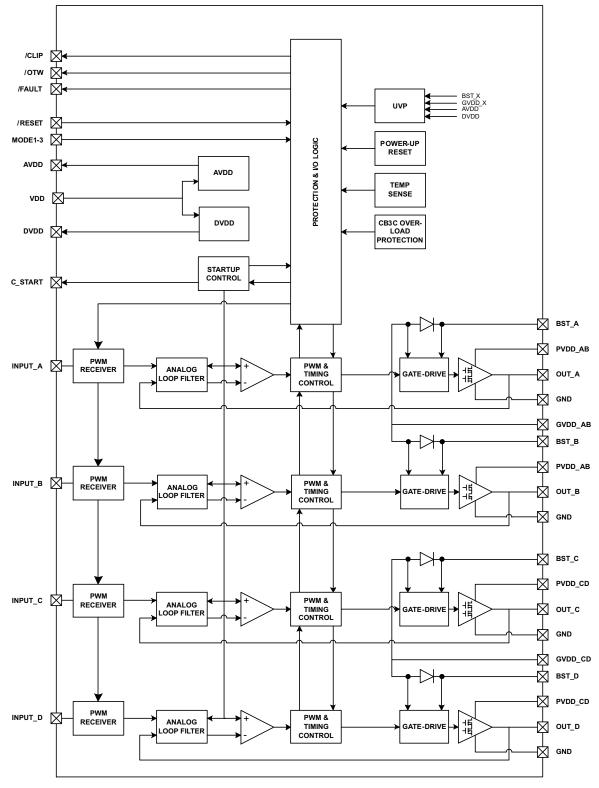

### 7.2 Functional Block Diagrams

(1) Logic AND is inside or outside the microprocessor.

图 13. Typical System Block Diagram

TEXAS INSTRUMENTS

www.ti.com.cn

## Functional Block Diagrams (接下页)

#### 7.3 Feature Description

#### 7.3.1 Power Supplies

To facilitate system design, the TAS5614LA needs only a 12-V supply in addition to the (typical) 36-V powerstage supply. An internal voltage regulator provides suitable voltage levels for the digital and low-voltage analog circuitry. Additionally, all circuitry requiring a floating voltage supply, for example, the high-side gate drive, is accommodated by built-in bootstrap circuitry requiring only an external capacitor for each half-bridge.

To provide outstanding electrical and acoustical characteristics, the PWM signal path including gate drive and output stage is designed as identical, independent half-bridges. For this reason, each half-bridge has separate bootstrap pins (BST\_X) and each full-bridge has separate power stage supply (PVDD\_X) and gate supply (GVDD\_X) pins. Furthermore, an additional pin (VDD) is provided as supply for all common circuits. Although supplied from the same 12-V source, it is highly recommended to separate GVDD\_AB, GVDD\_CD, and VDD on the printed-circuit board (PCB) by RC filters (see application diagram for details). These RC filters provide the recommended high-frequency isolation. Special attention should be paid to placing all decoupling capacitors as close to their associated pins as possible. In general, inductance between the power supply pins and decoupling capacitors must be avoided. (See reference board documentation for additional information.)

Special attention should be paid to the power-stage power supply; this includes component selection, PCB placement, and routing. As indicated, each full-bridge has independent power-stage supply pins (PVDD\_X). For optimal electrical performance, EMI compliance, and system reliability, it is important that each PVDD\_X connection is decoupled with minimum  $2 \times 220$ -nF ceramic capacitors placed as close as possible to each supply pin. TI recommends following the PCB layout of the TAS5614LA reference design. For additional information on recommended power supply and required components, see the application diagrams in this data sheet.

The 12-V supply should be from a low-noise, low-output-impedance voltage regulator. Likewise, the 36-V powerstage supply is assumed to have low output impedance and low noise. The power-supply sequence is not critical as facilitated by the internal power-on-reset circuit. Moreover, the TAS5614LA is fully protected against erroneous power-stage turn on due to parasitic gate charging when power supplies are applied. Thus, voltagesupply ramp rates (dV/dt) are noncritical within the specified range (see *Recommended Operating Conditions*).

#### 7.3.1.1 Boot Strap Supply

For a properly functioning bootstrap circuit, a small ceramic capacitor must be connected from each bootstrap pin (BST\_X) to the power-stage output pin (OUT\_X). When the power-stage output is low, the bootstrap capacitor is charged through an internal diode connected between the gate-drive power-supply pin (GVDD\_X) and the bootstrap pin. When the power-stage output is high, the bootstrap capacitor potential is shifted above the output potential and thus provides a suitable voltage supply for the high-side gate driver. In an application with PWM switching frequencies in the range from 300 kHz to 400 kHz, TI recommends to use 33-nF ceramic capacitors, size 0603 or 0805, for the bootstrap supply. These 33-nF capacitors ensure sufficient energy storage, even during minimal PWM duty cycles, to keep the high-side power stage FET (LDMOS) fully turned on during the remaining part of the PWM cycle.

#### 7.3.2 System Power-Up and Power-Down Sequence

#### 7.3.2.1 Powering Up

The TAS5614LA does not require a power-up sequence. The outputs of the H-bridges remain in a highimpedance state until the gate-drive supply voltage (GVDD\_X) and VDD voltage are above the undervoltage protection (UVP) voltage threshold (see *Electrical Characteristics*). Although not specifically required, TI recommends holding RESET in a low state while powering up the device. This allows an internal circuit to charge the external bootstrap capacitors by enabling a weak pulldown of the half-bridge output.

#### 7.3.2.2 Powering Down

The TAS5614LA does not require a power-down sequence. The device remains fully operational as long as the gate-drive supply (GVDD\_X) voltage and VDD voltage are above the undervoltage protection (UVP) voltage threshold (see *Electrical Characteristics*). Although not specifically required, it is a good practice to hold RESET low during power down, thus preventing audible artifacts including pops or clicks.

### Feature Description (接下页)

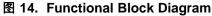

#### 7.3.3 Start-up and Shutdown Ramp Sequence

The integrated start-up and stop sequence ensures a click and pop free startup and shutdown sequence of the amplifier. The start-up sequence uses a voltage ramp with a duration set by the CSTART capacitor. The sequence uses the input PWM signals to generate output PWM signals, hence input idle PWM should be present during both startup and shut down ramping sequences.

VDD, GVDD\_X, and PVDD\_X power supplies must be turned on and with settled outputs before starting the start-up ramp by setting RESET high.

During start-up and shutdown ramp the input PWM signals should be in muted condition with the PWM processor noise shaper activity turned off (50% duty cycle).

The duration of the start-up and shutdown ramp is 100 ms + X ms, where X is the CSTART capacitor value in nF.

TI recommends using 100-nF CSTART in BTL and PBTL mode and 1  $\mu$ F in SE mode configuration. This results in ramp times of 200 ms and 1.1 s, respectively. The longer ramp time in SE configuration allows charge and discharge of the output ac coupling capacitor without audible artifacts.

#### 图 15. Start-up/Shutdown Ramp

#### 7.3.4 Unused Output Channels

If all available output channels are not used, TI recommends disabling switching of unused output nodes to reduce power consumption. Furthermore by disabling unused output channels the cost of unused output LC demodulation filters can be avoided.

Disabling a channel is done by leave the bootstrap capacitor (BST) unstuffed and connecting the respective input to GND. The unused output pin(s) can be left floating. Please note that the PVDD decoupling capacitors still need to be mounted.

| OPERATING<br>MODE | PWM<br>INPUT | OUTPUT<br>CONFIGURATION | UNUSED<br>CHANNEL | INPUT_A     | INPUT_B     | INPUT_C     | INPUT_D     | UNSTUFFED<br>COMPONENT        |

|-------------------|--------------|-------------------------|-------------------|-------------|-------------|-------------|-------------|-------------------------------|

| 000               | 2N + 1       |                         |                   |             |             |             |             | BST_A and BST_B               |

| 001               | 1N + 1       | 2 x BTL                 | AB<br>CD          | GND<br>PWMa | GND<br>PWMb | PWMc<br>GND | PWMd<br>GND | capacitors<br>BST C and BST D |

| 010               | 2N + 1       |                         | CD                | i wivia     |             | GND         | GND         | capacitors                    |

#### 表 1. Unused Output Channels

### Feature Description (接下页)

| OPERATING<br>MODE | PWM<br>INPUT | OUTPUT<br>CONFIGURATION | UNUSED<br>CHANNEL | INPUT_A | INPUT_B | INPUT_C | INPUT_D         | UNSTUFFED<br>COMPONENT |

|-------------------|--------------|-------------------------|-------------------|---------|---------|---------|-----------------|------------------------|

|                   |              | А                       | GND               | PWMb    | PWMc    | PWMd    | BST_A capacitor |                        |

| 101               | 411 - 4      | 4 x SE                  | В                 | PWMa    | GND     | PWMc    | PWMd            | BST_B capacitor        |

| 101               | 1N + 1       |                         | С                 | PWMa    | PWMb    | GND     | PWMd            | BST_C capacitor        |

|                   |              |                         | D                 | PWMa    | PWMb    | PWMc    | GND             | BST_D capacitor        |

### 表 1. Unused Output Channels (接下页)

### 7.3.5 Device Protection System

The TAS5614LA contains advanced protection circuitry carefully designed to facilitate system integration and ease of use, as well as to safeguard the device from permanent failure due to a wide range of fault conditions such as short circuits, overload, overtemperature, and undervoltage. The TAS5614LA responds to a fault by immediately setting the power stage in a high-impedance (Hi-Z) state and asserting the FAULT pin low. In situations other than overload and overtemperature error (OTE), the device automatically recovers when the fault condition has been removed, that is, the supply voltage has increased.

The device will function on errors, as shown in the following table.

| BTL MODE      |           | PBTL MODE     |           | SE MODE       |           |  |

|---------------|-----------|---------------|-----------|---------------|-----------|--|

| CHANNEL FAULT | TURNS OFF | CHANNEL FAULT | TURNS OFF | CHANNEL FAULT | TURNS OFF |  |

| А             | A+B       | А             | A+B+C+D   | А             | A+B       |  |

| В             |           | В             |           | В             |           |  |

| С             | C+D       | С             |           | С             | C+D       |  |

| D             |           | D             | _         | D             |           |  |

表 2. Device Protection

Bootstrap UVP does not shutdown according to the table, it shuts down the respective high-side FET.

### 7.3.6 Pin-to-Pin Short-Circuit Protection (PPSC)

The PPSC detection system protects the device from permanent damage if a power output pin (OUT\_X) is shorted to GND or PVDD\_X. For comparison, the OC protection system detects an overcurrent after the demodulation filter where PPSC detects shorts directly at the pin before the filter. PPSC detection is performed at start-up that is, when VDD is supplied, consequently a short to either GND or PVDD\_X after system start-up will not activate the PPSC detection system. When PPSC detection is activated by a short on the output, all half-bridges are kept in a Hi-Z state until the short is removed, the device then continues the start-up sequence and starts switching. The detection is controlled globally by a two step sequence. The first step ensures that there are no shorts from OUT\_X to GND, the second step tests that there are no shorts from OUT\_X to PVDD\_X. The total duration of this process is roughly proportional to the capacitance of the output LC filter. The typical duration is <15 ms/µF. While the <u>PPSC</u> detection is in progress, FAULT is kept low, and the device will not react to changes applied to the RESET pins. If no shorts are present the PPSC detection passes, and FAULT is released. A device reset will not start a new PPSC detection. PPSC detection is enabled in BTL and PBTL output configurations, the detection is not performed in SE mode. To prevent to tripping the PPSC detection system TI recommends not inserting resistive load to GND or PVDD\_X.

### 7.3.7 Overtemperature Protection

The TAS5614LA has a two-level temperature-protection system that asserts an active-low warning signal (OTW) when the device junction temperature exceeds 125°C (typical). If the device junction temperature exceeds 155°C (typical), the device is put into thermal shutdown, resulting in all half-bridge outputs being set in the high-impedance (Hi-Z) state and FAULT being asserted low. OTE is latched in this case. To clear the OTE latch, RESET must be asserted. Thereafter, the device resumes normal operation.

#### TAS5614LA ZHCS930A – MAY 2012 – REVISED MARCH 2015

TEXAS INSTRUMENTS

www.ti.com.cn

#### 7.3.8 Overtemperature Warning, OTW

The overtemperature warning OTW asserts when the junction temperature has exceeded recommended operating temperature. Operation at junction temperatures above OTW threshold is exceeding recommended operation conditions and is strongly advised to avoid.

If OTW asserts, action should be taken to reduce power dissipation to allow junction temperature to decrease until it gets below the OTW hysteresis threshold. This action can be decreasing audio volume or turning on a system cooling fan.

#### 7.3.9 Undervoltage Protection (UVP) and Power-On Reset (POR)

The UVP and POR circuits of the TAS5614LA fully protect the device in any power-up/down and brownout situation. While powering up, the POR circuit resets the overload circuit (OLP) and ensures that all circuits are fully operational when the GVDD\_X and VDD supply voltages reach stated in *Electrical Characteristics*. Although GVDD\_X and VDD are independently monitored, a supply voltage drop below the UVP threshold on any VDD or <u>GVDD\_X</u> pin results in all half-bridge outputs immediately being set in the high-impedance (Hi-Z) state and FAULT being asserted low. The device automatically resumes operation when all supply voltages have increased above the UVP threshold.

#### 7.3.10 Error Reporting

Note that asserting RESET low forces the FAULT signal high, independent of faults being present. TI recommends monitoring the OTW signal using the system micro controller and responding to an overtemperature warning signal by, for example, turning down the volume to prevent further heating of the device resulting in device shutdown (OTE).

To reduce external component count, an internal pullup resistor to 3.3 V is provided on both FAULT and OTW outputs.

The FAULT, OTW, pins are active-low, open-drain outputs. Their function is for protection-mode signaling to a PWM controller or other system-control device.

Any fault resulting in device shutdown is signaled by the FAULT pin going low. Likewise, OTW goes low when the device junction temperature exceeds 125°C (see the following table).

| FAULT | OTW | DESCRIPTION                                                                       |

|-------|-----|-----------------------------------------------------------------------------------|

| 0     | 0   | Overtemperature (OTE) or overload (OLP) or undervoltage (UVP)                     |

| 0     | 1   | Overload (OLP) or undervoltage (UVP)                                              |

| 1     | 0   | Junction temperature higher than 125°C (overtemperature warning)                  |

| 1     | 1   | Junction temperature lower than 125°C and no OLP or UVP faults (normal operation) |

#### 表 3. Error Reporting

#### 7.3.11 Fault Handling

If a fault situation occurs while in operation, the device will act accordingly to the fault being a global or a channel fault. A global fault is a chip-wide fault situation and will cause all PWM activity of the device to be shut down, and will assert FAULT low. A global fault is a latching fault and clearing FAULT and restart operation requires resetting the device by toggling RESET. Toggling RESET should never be allowed with excessive system temperature, so it is advised to monitor RESET by a system microcontroller and only allow releasing RESET (RESET high) if the OTW signal is cleared (high). A channel fault will result in shutdown of the PWM activity of the affected channel(s). Note that asserting RESET low forces the FAULT signal high, independent of faults being present. TI recommends monitoring the OTW signal using the system micro controller and responding to an over temperature warning signal by, for example, turning down the volume to prevent further heating of the device resulting in device shutdown (OTE).

| FAULT or EVENT                                  | FAULT or EVENT<br>DESCRIPTION | GLOBAL or<br>CHANNEL     | REPORTING<br>METHOD | LATCHED or SELF<br>CLEARING | ACTION NEEDED TO<br>CLEAR                            | OUTPUT FETs                        |

|-------------------------------------------------|-------------------------------|--------------------------|---------------------|-----------------------------|------------------------------------------------------|------------------------------------|

| PVDD_X UVP                                      |                               |                          |                     |                             |                                                      |                                    |

| VDD UVP                                         |                               | Olah al                  | FAULT Pin           |                             | Increase affected supply                             | 11: 7                              |

| GVDD_X UVP                                      | Voltage Fault                 | Global                   | FAULT PIN           | Self Clearing               | voltage                                              | Hi-Z                               |

| AVDD UVP                                        |                               |                          |                     |                             |                                                      |                                    |

| POR (DVDD UVP)                                  | Power On Reset                | Global                   | FAULT Pin           | Self Clearing               | Allow DVDD to rise                                   | H-Z                                |

| BST UVP                                         | Voltage Fault                 | Channel (half<br>bridge) | None                | Self Clearing               | Allow BST cap to recharge<br>(low side on, VDD 12 V) | High Side Off                      |

| OTW                                             | Thermal Warning               | Global                   | OTW Pin             | Self Clearing               | Cool below lower OTW<br>threshold                    | Normal operation                   |

| OTE (OTSD)                                      | Thermal Shutdown              | Global                   | FAULT Pin           | Latched                     | Toggle RESET                                         | Hi-Z                               |

| OLP (CBC >2.6 ms)                               | OC shutdown                   | Channel                  | FAULT Pin           | Latched                     | Toggle RESET                                         | Hi-Z                               |

| Latched OC (ROC > 47k)                          | OC shutdown                   | Channel                  | FAULT Pin           | Latched                     | Toggle RESET                                         | Hi-Z                               |

| CBC (24k < ROC <<br>33k)                        | OC Limiting                   | Channel                  | None                | Self Clearing               | reduce signal level or remove short                  | Flip state, cycle by cycle at fs/2 |

| Stuck at Fault <sup>(1)</sup> (1 to 3 channels) | No PWM                        | Channel                  | None                | Self Clearing               | resume PWM                                           | Hi-Z                               |

| Stuck at Fault <sup>(1)</sup> (All channels)    | No PWM                        | Global                   | None                | Self Clearing               | resume PWM                                           | Hi-Z                               |

| (1) Stuck at Fault of                           | ccurs when input PW           | M drops below            | minimum PW          | M frame rate given ir       | Recommended Operating (                              | Conditions                         |

#### 表 4. Fault Handling

(1) Stuck at Fault occurs when input PWM drops below minimum PWM frame rate given in *Recommended Operating Conditions*.

### 7.3.12 Device Reset

When RESET is asserted low, all power-stage FETs in the four half-bridges are forced into a high-impedance (Hi-Z) state.

In BTL modes, to accommodate bootstrap charging prior to switching start, asserting the reset input low enables weak pulldown of the half-bridge outputs. In the SE mode, the output is forced into a high impedance state when <u>asserting</u> the reset input low. Asserting reset input low removes any fault information to be signaled on the FAULT output, that is, FAULT is forced high. A rising-edge transition on reset input allows the device to resume operation after an overload fault. To ensure thermal reliability, the rising edge of RESET must occur no sooner than 4 ms after the falling edge of FAULT.

### 7.4 Device Functional Modes

There are three main output modes that the user can configure the device as per application requirement. In addition there are two PWM modulation modes, AD and BD.

AD modulation can have single-ended (SE) or differential analog inputs. AD modulation can also be configured to have SE, BTL, BTL+SE, or PBTL outputs. BD modulation requires differential analog inputs.

BD modulation can only be configured in BTL or PTBL mode.

### Device Functional Modes (接下页)

### 7.4.1 Mode Selection Pins

|    | MODE PINS | i  | PWM                   | OUTPUT                | INPUT A | INPUT B | INPUT C | INPUT D | MODE    |

|----|-----------|----|-----------------------|-----------------------|---------|---------|---------|---------|---------|

| M3 | M2        | M1 | INPUT <sup>(1)</sup>  | CONFIGURATION         | INPUTA  |         | INPUTC  | INPUTD  | MODE    |

| 0  | 0         | 0  | 2N + 1                | 2 x BTL               | PWMa    | PWMb    | PWMc    | PWMd    | AD mode |

| 0  | 0         | 1  | 1N + 1 <sup>(2)</sup> | 2 x BTL               | PWMa    | Unused  | PWMc    | Unused  | AD mode |

| 0  | 1         | 0  | 2N + 1                | 2 x BTL               | PWMa    | PWMb    | PWMc    | PWMd    | BD mode |

| 0  | 1         | 1  | 1N + 1 <sup>(2)</sup> | 1 x BTL + 2 x SE      | PWMa    | Unused  | PWMc    | PWMd    | AD mode |

| 1  | 0         | 0  | 2N + 1                | 1 x PBTL              | PWMa    | PWMb    | 0       | 0       | AD mode |

| 1  | 0         | 0  | 1N + 1 <sup>(2)</sup> | 1 x PBTL              | PWMa    | Unused  | 0       | 1       | AD mode |

| 1  | 0         | 0  | 2N + 1                | 1 x PBTL              | PWMa    | PWMb    | 1       | 0       | BD mode |

| 1  | 0         | 1  | 1N + 1                | 4 x SE <sup>(3)</sup> | PWMa    | PWMb    | PWMc    | PWMd    | AD mode |

The 1N and 2N naming convention is used to indicate the number of PWM lines to the power stage per channel in a specific mode.

Using 1N interface in BTL and PBTL mode results in increased DC offset on the output terminals.

The 4xSE mode can be used as 1xBTL + 2xSE configuration by feeding a 2N PWM signal to either INPUT\_AB or INPUT\_CD for improved dc offset accuracy

### 8 Application and Implementation

#### 注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 8.1 Application Information

#### 8.1.1 System Design Consideration

A rising-edge transition on reset input allows the device to execute the startup sequence and starts switching.

Apply audio only according to the timing information for startup and shutdown sequence. That will start and stop the amplifier without audible artifacts in the output transducers.

The CLIP signal indicates that the output is approaching clipping (when output PWM starts skipping pulses due to loop filter saturation). The signal can be used to initiate an audio volume decrease or to adjust the power supply rail.

The device inverts the audio signal from input to output.

The DVDD and AVDD pins are not recommended to be used as a voltage source for external circuitry.

#### 8.2 Typical Applications

The following sections discuss in detail three typical audio PWM (class-D) configurations:

- Differential input, stereo BTL outputs

- Differential input, mono PBTL output

- Single-ended inputs, quad single-ended outputs.

### 8.2.1 Typical BTL Application

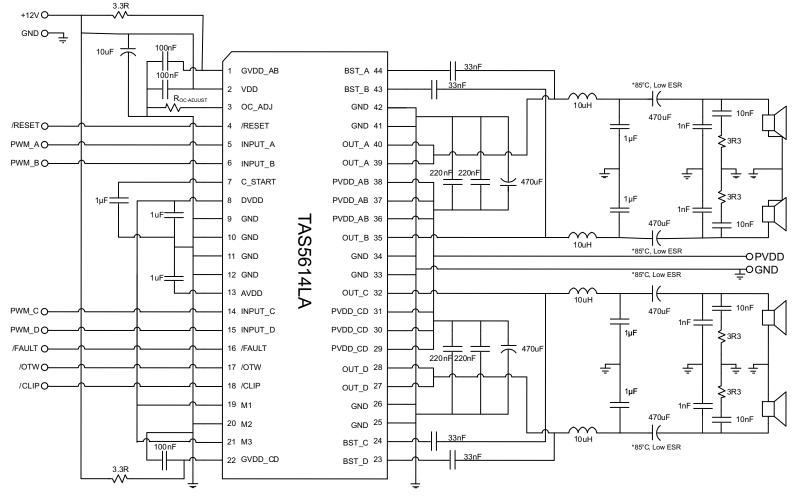

图 16. Typical Differential (2N) BTL Application With AD Modulation Filters

PWM(-).

#### 8.2.1.1 Design Requirements

See 图 16 for application schematic. In this application, differential PWM inputs are used with AD modulation from the PWM modulator (TAS5558). AD modulation scheme is defined as PWM(+) is opposite polarity from

#### 8.2.1.2 Detailed Design Procedure

- Pin 1 GVDD\_AB is the gate drive voltage for half-bridges A and B. This pin needs a 3.3-Ω isolation resistor and a 0.1-uF decoupling capacitor.

- Pin 2 VDD is the supply for internal voltage regulators AVDD and DVDD. This pin needs a 10-uF bulk capacitor and a 0.1-uF decoupling capacitor.

- Pin 3 Roc adjust is the overcurrent programming resistor. Depending on the application, this resistor can be between 24 k $\Omega$  to 68 k $\Omega$ .

- Pin 4 RESET pin when asserted, it keeps outputs Hi-Z and no PWM switching. This pin can be controlled by a microprocessor.

- Pins 5 and 6 These are PWM (+) and PWM (-) pins with signals provided by a PWM modulator such as TAS5558. These are PWM differential pair.

- Pin 7 Start-up ramp capacitor should be 0.1 uF for BTL configuration.

- Pin 8 Digital output supply pin is connected to 1-uF decoupling capacitor.

- Pins 9-12 Ground pins are connected to board ground.

- Pin 13 Analog output supply pin is connected to 1-uF decoupling capacitor.

- Pins 14 and 15 These are PWM (+) and PWM (–) pins with signals provided by a PWM modulator such as TAS5558. These are PWM differential pair.

- Pin 16 Fault pin can be monitored by a micro-controller via GPIO pin. System can decide to assert reset or shutdown.

- Pin 17 Overtemperature warning pin can be monitored by a microcontroller through a GPIO pin. System can decide to turn on fan or lower output power.

- Pin 18 Output clip indicator can be monitored by a microcontroller via a GPIO pin. System can decide to lower the volume.

- Pins 19-21 Mode pins set the input and output configurations. For this configuration M1-M3 are grounded. These mode pins must be hardware configured, such as, not through GPIO pins from a micro-controller.

- Pin 22 GVDD\_CD is the gate drive voltage for half-bridges C and D. This pin needs a 3.3-Ω isolation resistor and a 0.1-uF decoupling capacitor.

- Pins 23, 24, 43, 44 Bootstrap pins for half-bridges A, B, C, and D. Connect 33 nF from this pin to corresponding output pins.

- Pins 25, 26, 33, 34, 41, 42 These ground pins should be used to ground decoupling capacitors from PVDD\_X.

TAS5614LA

ZHCS930A - MAY 2012 - REVISED MARCH 2015

TAS5614LA

ZHCS930A-MAY 2012-REVISED MARCH 2015

www.ti.com.cn

#### 8.2.1.3 Application Curves

### 8.2.2 Typical SE Configuration

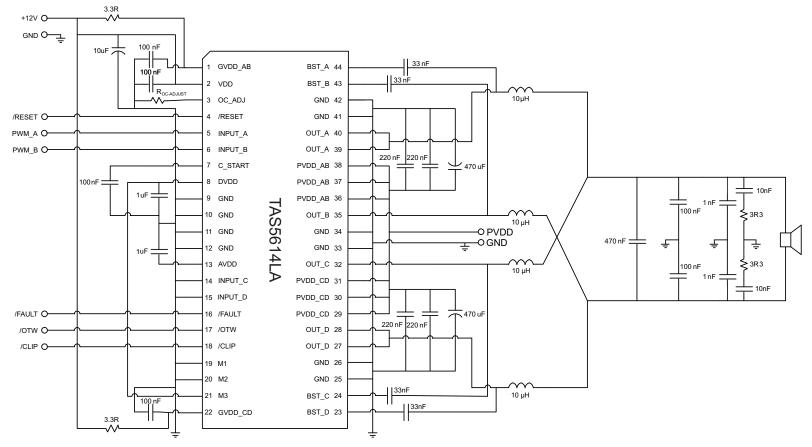

图 19. Typical (1N) SE Application

#### TAS5614LA

ZHCS930A - MAY 2012 - REVISED MARCH 2015

#### 8.2.2.1 Design Requirements

See 19 for application schematic. In this application, four single-ended PWM inputs are used with AD modulation from the PWM modulator such as the TAS5558. AD modulation scheme is defined as PWM(+) is opposite polarity from PWM(-). The single-ended (SE) output configuration is often used to drive 4 independent channels in one TAS5614LA device.

#### 8.2.2.2 Detailed Design Procedure

- Pin 1 GVDD\_AB is the gate drive voltage for half-bridges A and B. It needs a 3.3-Ω isolation resistor and a 0.1-uF decoupling capacitor.

- Pin 2 VDD is the supply for internal voltage regulators AVDD and DVDD. It needs a 10-uF bulk cap and a 0.1-uF decoupling capacitor.

- Pin 3 Roc adjust is the overcurrent programming resistor. Depending on the application, this resistor can be between 24 k $\Omega$  to 68 k $\Omega$ .

- Pin 4 RESET pin when asserted, it keeps outputs Hi-Z and no PWM switching. This pin can be controlled by a microprocessor.

- Pins 5 and 6 These are PWM (+) and PWM (-) pins with signals provided by a PWM modulator such as TAS5558. These are PWM differential pair.

- Pin 7 Start up ramp capacitor should be 1 uF for SE configuration.

- Pin 8 Digital output supply pin is connected to 1-uF decoupling cap.

- Pins 9-12 Ground pins are connected to board ground.

- Pin 13 Analog output supply pin is connected to 1-uF decoupling cap.

- Pins 14 and 15 These are PWM (+) and PWM (-) pins with signals provided by a PWM modulator such as TAS5558. These are PWM differential pair.

- Pin 16 Fault pin can be monitored by a microcontroller through GPIO pin. System can decide to assert reset or shutdown.

- Pin 17 Overtemperature warning pin can be monitored by a microcontroller through a GPIO pin. System can decide to turn on fan or lower output power.

- Pin 18 Output clip indicator can be monitored by a microcontroller through a GPIO pin. System can decide to lower the volume.

- Pins 19-21 Mode pins set the input and output configurations. For this configuration M1-M3 are grounded. These mode pins must be hardware configured, such as, not through GPIO pins from a microcontroller.

- Pin 22 GVDD\_CD is the gate drive voltage for half-bridges C and D. This pin needs a 3.3-Ω isolation resistor and a 0.1-uF decoupling capacitor.

- Pins 23, 24, 43, 44 Bootstrap pins for half-bridges A, B, C, and D. Connect 33 nF from this pin to corresponding output pins.

- Pins 25, 26, 33, 34, 41, 42 These ground pins should be used to ground decoupling capacitors from PVDD\_X.

### 8.2.2.3 Application Curves

### 8.2.3 Typical PBTL Configuration

图 22. Typical Differential (2N) PBTL Application With AD Modulation Filter

#### 8.2.3.1 Design Requirements

See 22 for application schematic. In this application, one differential PWM input is used with AD modulation from the PWM modulator such as the TAS5558. AD modulation scheme is defined as PWM(+) is opposite polarity from PWM(-). The output PBTL configuration is often used to drive lower impedance load such as a subwoofer.

#### 8.2.3.2 Detailed Design Procedure

- Pin 1 GVDD\_AB is the gate drive voltage for half-bridges A and B. This pin needs a 3.3-Ω isolation resistor and a 0.1-uF decoupling capacitor.

- Pin 2 VDD is the supply for internal voltage regulators AVDD and DVDD. This pin needs a 10-uF bulk cap and a 0.1-uF decoupling capacitor.

- Pin 3 Roc adjust is the over-current programming resistor. Depending on the application, this resistor can be between 24 k $\Omega$  to 68 k $\Omega$ .

- Pin 4 RESET pin when asserted, it keeps outputs Hi-Z and no PWM switching. This pin can be controlled by a microprocessor.

- Pins 5 and 6 These are PWM (+) and PWM (-) pins with signals provided by a PWM modulator such as TAS5558. These are PWM differential pair.

- Pin 7 Start up ramp capacitor should be 0.1 uF for PBTL configuration.

- Pin 8 Digital output supply pin is connected to 1-uF decoupling capacitor.

- Pins 9-12 Ground pins are connected to board ground.

- Pin 13 Analog output supply pin is connected to 1-uF decoupling cap.

- Pins 14 and 15 These are PWM (+) and PWM (-) pins with signals provided by a PWM modulator such as TAS5558. These are PWM differential pair.

- Pin 16 Fault pin can be monitored by a microcontroller through GPIO pin. System can decide to assert reset or shutdown.

- Pin 17 Overtemperature warning pin can be monitored by a microcontroller through a GPIO pin. System can decide to turn on fan or lower output power.

- Pin 18 Output clip indicator can be monitored by a microcontroller through a GPIO pin. System can decide to lower the volume.

- Pins 19-21 Mode pins set the input and output configurations. For this configuration M1-M3 are grounded. These mode pins must be hardware configured, such as, not through GPIO pins from a microcontroller.

- Pin 22 GVDD\_CD is the gate drive voltage for half-bridges C and D. It needs a 3.3-Ω isolation resistor and a 0.1-uF decoupling capacitor.

- Pins 23, 24, 43, 44 Bootstrap pins for half-bridges A, B, C, and D. Connect 33 nF from this pin to corresponding output pins.

- Pins 25, 26, 33, 34, 41, 42 These ground pins should be used to ground decoupling capacitors from PVDD\_X.

- Pins 27, 28, 32, 35, 39, 40 Output pins from half-bridges A, B, C, and D. Connect appropriate bootstrap capacitors and differential LC filter as shown in 🛿 22.

TAS5614LA

ZHCS930A-MAY 2012-REVISED MARCH 2015

www.ti.com.cn

#### 8.2.3.3 Application Curves

### 9 Power Supply Recommendations

The most important parameters are the absolute maximum rating on PVDD pins, bootstrap pins, and output pins. Over stress the device with higher that maximum voltage rating may shorten device lifetime operation and even cause device damage. Be sure that the specifications in *Specifications* are observed. For best audio performance, low ESR bulk caps are recommended. Depending on the application 470-µF capacitor or higher should be used. As always, decoupling capacitors must be placed no more than 1 mm from the power supply pins. If PCB space is not allowed for close placement of the decoupling capacitor, the decoupling capacitors can be placed on the back side of the device with vias. However, it still needs to be right below the pins.

### 10 Layout

### 10.1 Layout Guidelines

#### 10.1.1 PCB Material Recommendation

FR-4 Glass Epoxy material with 1 oz. (35 µm) is recommended for use with the TAS5614LA. The use of this material can provide for higher power output, improved thermal performance, and better EMI margin (due to lower PCB trace inductance.

#### 10.1.2 PVDD Capacitor Recommendation

The large capacitors used in conjunction with each full-bridge, are referred to as the PVDD Capacitors. These capacitors should be selected for proper voltage margin and adequate capacitance to support the power requirements. In practice, with a well designed system power supply, 1000  $\mu$ F, 50 V should support most applications. The PVDD capacitors should be low ESR type because they are used in a circuit associated with high-speed switching.

#### **10.1.3 Decoupling Capacitor Recommendation**

To design an amplifier that has robust performance, passes regulatory requirements, and exhibits good audio performance, good quality decoupling capacitors should be used. In practice, X5R or better should be used in this application.

The voltage of the decoupling capacitors should be selected in accordance with good design practices. Temperature, ripple current, and voltage overshoot must be considered. This fact is particularly true in the selection of the close decoupling capacitor that is placed on the power supply to each half-bridge. It must withstand the voltage overshoot of the PWM switching, the heat generated by the amplifier during high power output, and the ripple current created by high power output. A minimum voltage rating of 50V is required for use with a 36-V power supply.

See the TAS5614LADDVEVM user's guide, SLAU375, for more details including layout and bill of materials.

#### 10.1.4 Circuit Component and Printed Circuit Board Recommendation

These requirements must be followed to achieve best performance and reliability and minimum ground bounce at rated output power of TAS5614LA.

#### 10.1.4.1 Circuit Component Requirements

A number of circuit components are critical to performance and reliability. They include LC filter inductors and capacitors, decoupling capacitors and the heatsink. The best detailed reference for these is the TAS5614LA EVM BOM in the user's guide, which includes components that meet all the following requirements.

- High frequency decoupling capacitors: small high frequency decoupling capacitors are placed next to the IC to control switching spikes and keep high frequency currents in a tight loop to achieve best performance and reliability and EMC. They must be high quality ceramic parts with material like X7R or X5R and voltage ratings at least 30% greater than PVDD, to minimize loss of capacitance caused by applied dc voltage. (Capacitors made of materials like Y5V or Z5U should never be used in decoupling circuits or audio circuits because their capacitance falls dramatically with applied dc and ac voltage, often to 20% of rated value or less.)

- Bulk decoupling capacitors: large bulk decoupling capacitors are placed as close as possible to the IC to

### Layout Guidelines (接下页)

stabilize the power supply at lower frequencies. They must be high quality aluminum parts with low ESR and ESL and voltage ratings at least 25% more than PVDD to handle power supply ripple currents and voltages

- LC filter inductors: to maintain high efficiency, short circuit protection and low distortion, LC filter inductors must be linear to at least the OCP limit and must have low DC resistance and core losses. For SCP, minimum working inductance, including all variations of tolerance, temperature and current level, must be 5 µH. Inductance variation of more than 1% over the output current range can cause increased distortion.

- LC filter capacitors: to maintain low distortion and reliable operation, LC filter capacitors must be linear to twice the peak output voltage. For reliability, capacitors must be rated to handle the audio current generated in them by the maximum expected audio output voltage at the highest audio frequency.

- Heatsink: The heatsink must be fabricated with the PowerPAD contact area spaced 1.0 mm ±0.01 mm above mounting areas that contact the PCB surface. It must be supported mechanically at each end of the IC. This mounting ensures the correct pressure to provide good mechanical, thermal and electrical contact with TAS5614LA PowerPAD. The PowerPAD contact area must be bare and must be interfaced to the PowerPAD with a thin layer (about 1 mil) of a thermal compound with high thermal conductivity.

#### 10.1.4.2 Printed Circuit Board Requirements

PCB layout, audio performance, EMC and reliability are linked closely together, and solid grounding improves results in all these areas. The circuit produces high, fast-switching currents, and care must be taken to control current flow and minimize voltage spikes and ground bounce at IC ground pins. Critical components must be placed for best performance and PCB traces must be sized for the high audio currents that the IC circuit produces.

Grounding: ground planes must be used to provide the lowest impedance and inductance for power and audio signal currents between the IC and its decoupling capacitors, LC filters and power supply connection. The area directly under the IC should be treated as central ground area for the device, and all IC grounds must be connected directly to that area. A matrix of vias must be used to connect that area to the ground plane. Ground planes can be interrupted by radial traces (traces pointing away from the IC), but they must never be interrupted by circular traces, which disconnect copper outside the circular trace from copper between it and the IC. Top and bottom areas that do not contain any power or signal traces should be flooded and connected with vias to the ground plane.

Decoupling capacitors: high frequency decoupling capacitors must be located within 2 mm of the IC and connected directly to PVDD and GND pins with solid traces. Vias must not be used to complete these connections, but several vias must be used at each capacitor location to connect top ground directly to the ground plane. Placement of bulk decoupling capacitors is less critical, but they still must be placed as close as possible to the IC with strong ground return paths. Typically the heatsink sets the distance.

LC filters: LC filters must be placed as close as possible to the IC after the decoupling capacitors. The capacitors must have strong ground returns to the IC through top and bottom grounds for effective operation.

PCB copper must be at least 1 ounce thickness. PVDD and output traces must be wide enough to carry expected average currents without excessive temperature rise. PWM input traces must be kept short and close together on the input side of the IC and must be shielded with ground flood to avoid interference from high power switching signals.

The heatsink must be grounded well to the PCB near the IC, and a thin layer of highly conductive thermal compound (about 1 mil) must be used to connect the heatsink to the PowerPAD.

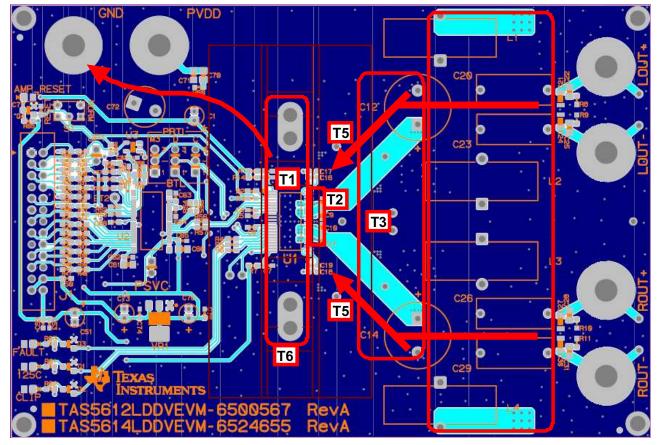

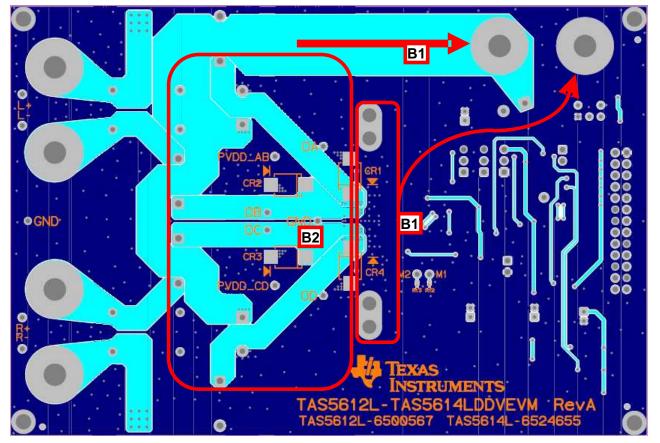

#### 10.2 Layout Example

**Note T1**: Bottom and top layer ground plane areas are used to provide strong ground connections. The area under the IC must be treated as central ground, with IC grounds connected there and a strong via matrix connecting the area to bottom ground plane. The ground path from the IC to the power supply ground through top and bottom layers must be strong to provide very low impedance to high power and audio currents.