www.ti.com.cn

# DS90UA101-Q1 多通道数字音频链路

查询样品: DS90UA101-Q1

#### 特性

- 数字音频串行器

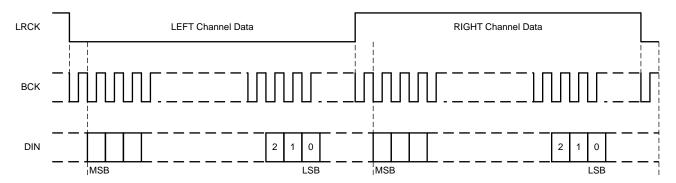

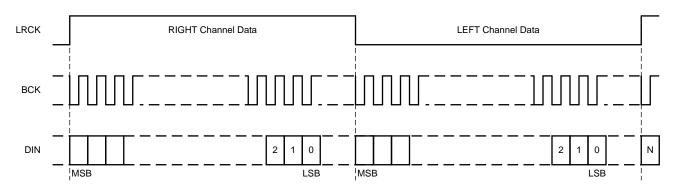

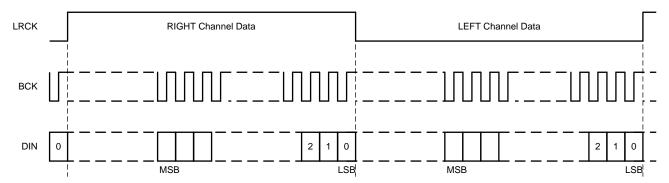

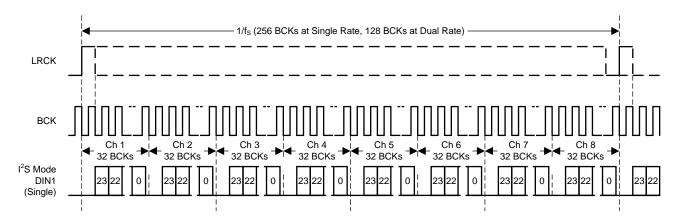

- 灵活的数字音频输入,支持 I<sup>2</sup>S(立体声)或时分复用 (TDM)(多通道)格式

- 同轴或单个差分对互连

- 高速串行输出接口

- 极低延迟 (< 15μs)

- 具有 I<sup>2</sup>C 兼容串行控制总线的双向控制接口通道

- 支持多达 8 个立体声 I<sup>2</sup>S 或 TDM 音频输入

- 支持 10MHz 至 50MHz 的音频系统频率

- 单个 1.8V 电源

- 1.8V 或 3.3V I/O 接口

- 4/4 个专用通用输入/输出

- 具有嵌入式时钟的直流均衡 & 扰频数据

- 汽车应用级产品:符合 AEC-Q100 2 级要求

- 温度范围: -40°C 至 105°C

- 符合 ISO 10605 以及 IEC 61000-4-2 静电放电 (ESD) 标准

# 应用范围

- 汽车信息娱乐系统

- 主动噪声消除系统

- 分布式多通道音频系统

## 说明

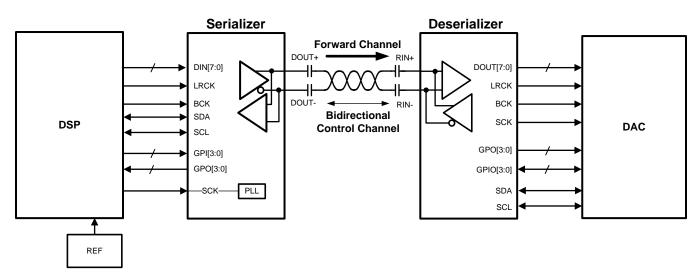

DS90UA101-Q1 串行器,与 DS90UA102-Q1 解串器一同使用,为多通道音频系统中数字音频的分发提供了一个解决方案。它在一个单条屏蔽双绞线或同轴电缆上借助一个嵌入式时钟用高速已串化接口发送数据。这个串行总线系统配置在链路上支持高速数据正向传输和低速双向控制通道。数字音频、通用 IO 和一个单差分对上控制信号的联合使用减少了互连尺寸和重量,同时也减少了与偏斜和系统延迟相关的设计问题。

DS90UA101-Q1 串行器嵌入了时钟,并且将信号电平 位移至高速低压差分信令。 此器件将多达 8 个数字音 频数据输入、字/帧同步、位时钟和系统时钟串化。

四个专用的通用输入引脚和四个通用输出引脚可灵活地实现与远程器件之间的控制和中断信号传输。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

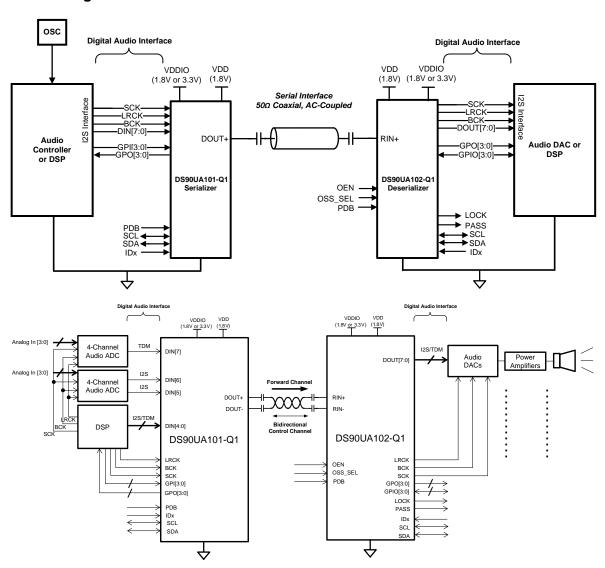

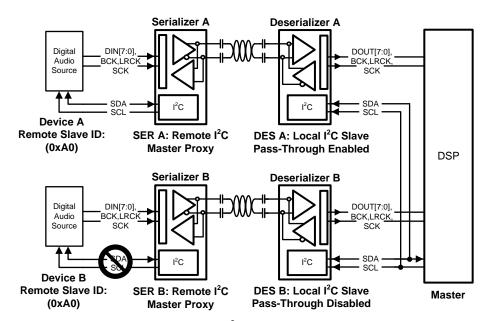

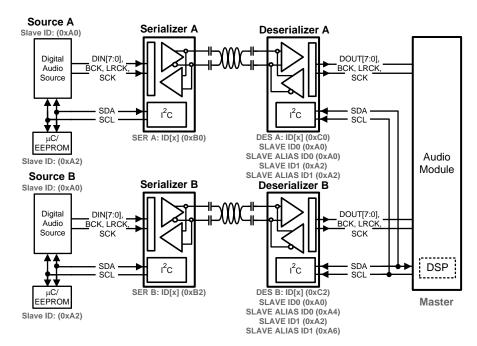

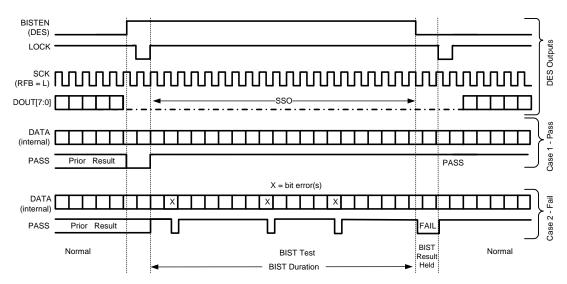

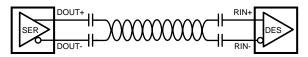

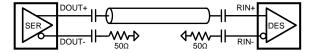

# **Applications Diagrams**

Figure 1. Applications Diagrams

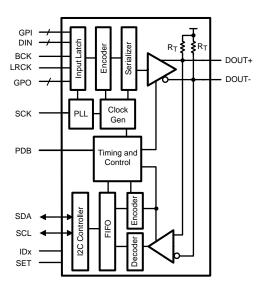

# **Block Diagram**

Figure 2. Block Diagram

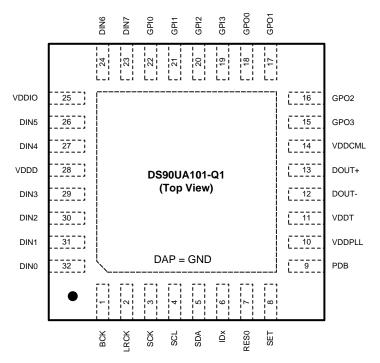

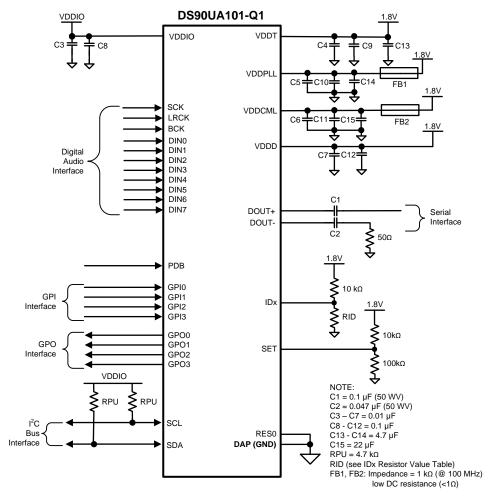

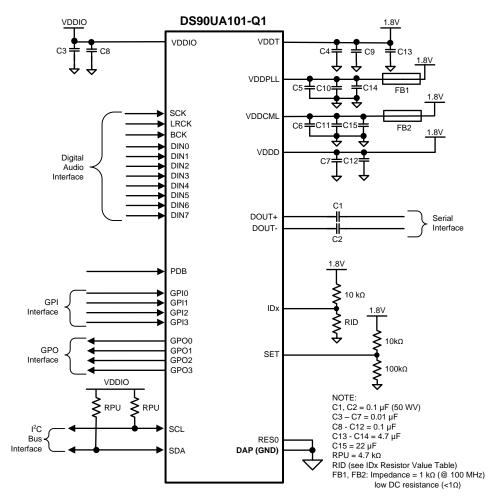

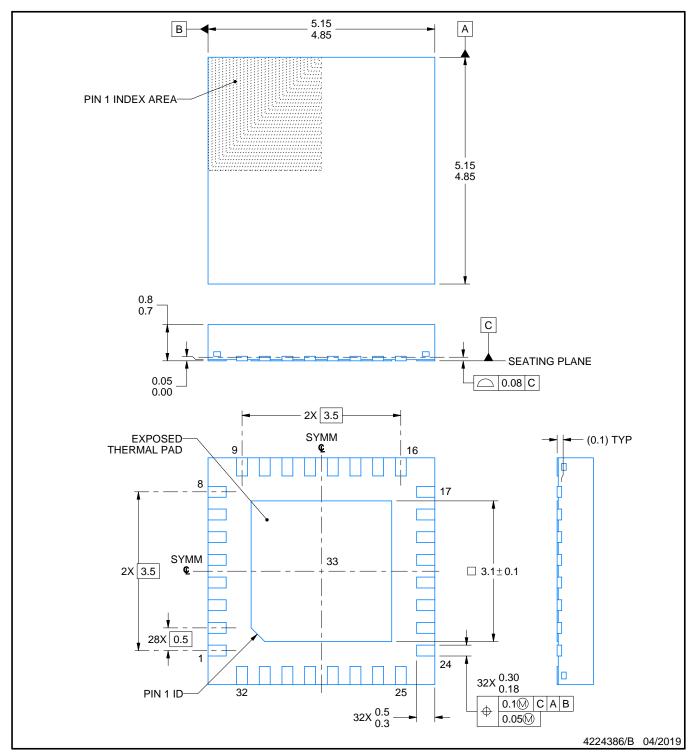

# DS90UA101-Q1 Pin Diagram

Figure 3. DS90UA101-Q1 — Top View

# **Pin Descriptions**

| Pin Name                | Pin #                             | I/O, Type                      | Description                                                                                                                                              |  |  |  |  |  |

|-------------------------|-----------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Digital Audio Interface |                                   |                                |                                                                                                                                                          |  |  |  |  |  |

| SCK                     | 3                                 | Input, LVCMOS w/<br>pull down  | System clock input. Forward channel audio data is clocked from this pin.                                                                                 |  |  |  |  |  |

| LRCK                    | 2                                 | Input, LVCMOS w/<br>pull down  | Word clock input.                                                                                                                                        |  |  |  |  |  |

| BCK                     | 1                                 | Input, LVCMOS w/<br>pull down  | Bit clock input.                                                                                                                                         |  |  |  |  |  |

| DIN[7:0]                | 23, 24, 26, 27,<br>29, 30, 31, 32 | Inputs, LVCMOS<br>w/ pull down | Digital audio data inputs. Each input can be in I <sup>2</sup> S, TDM, LJ, or RJ format.                                                                 |  |  |  |  |  |

| LVCMOS Pa               | rallel Interface                  |                                |                                                                                                                                                          |  |  |  |  |  |

| GPI[3:0]                | 19, 20, 21, 22                    | Inputs, LVCMOS<br>w/ pull down | General purpose inputs.                                                                                                                                  |  |  |  |  |  |

| GPO[3:0]                | 15, 16, 17, 18                    | Outputs, LVCMOS                | General purpose outputs.                                                                                                                                 |  |  |  |  |  |

| Control and             | Configuration                     |                                |                                                                                                                                                          |  |  |  |  |  |

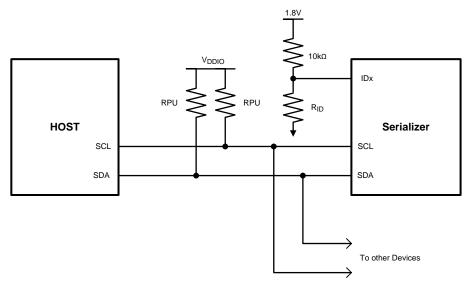

| SCL                     | 4                                 | Input/Output, Open<br>Drain    | $I^2C$ clock line. Must have an external pull-up to $V_{DDIO}.$ DO NOT FLOAT. Recommended pull-up: $4.7\ k\Omega.$                                       |  |  |  |  |  |

| SDA                     | 5                                 | Input/Output, Open<br>Drain    | $I^2C$ data input/output line. Must have an external pull-up to $V_{DDIO}.$ DO NOT FLOAT. Recommended pull-up: 4.7 k $\Omega.$                           |  |  |  |  |  |

| IDx                     | 6                                 | Input, Analog                  | Device I <sup>2</sup> C address select.  The IDx pin on the Serializer is used to assign its I <sup>2</sup> C device address. See Table 2. DC NOT FLOAT. |  |  |  |  |  |

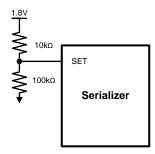

| SET                     | 8                                 | Input, Analog                  | Device SET. Connect to external 10 k $\Omega$ pull-up to 1.8V rail and 100k $\Omega$ pull-down to GND. DO NOT FLOAT.                                     |  |  |  |  |  |

#### www.ti.com.cn

| Pin Name       | Pin # | I/O, Type                     | Description                                                                                                                                                                                                                                                    |  |  |

|----------------|-------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| PDB            | 9     | Input, LVCMOS w/<br>pull down | Power down mode input pin. PDB = H, device is enabled and is ON. PDB = L, device is powered down. When the device is in the powered down state, the transmitter outputs are both HIGH, the PLL is shutdown, and IDD is minimized. Control registers are RESET. |  |  |

| Serial Interfa | ice   |                               |                                                                                                                                                                                                                                                                |  |  |

| DOUT+          | 13    | Input/Output, LVDS            | True serial interface output.  The interconnection must be AC-coupled to this pin with a 0.1 µF capacitor.                                                                                                                                                     |  |  |

| DOUT-          | 12    | Input/Output, LVDS            | Inverting serial interface output.  The interconnection must be AC-coupled to this pin with a 0.1 µF capacitor.                                                                                                                                                |  |  |

| Power and G    | round |                               |                                                                                                                                                                                                                                                                |  |  |

| VDDPLL         | 10    | Power                         | 1.8V (±5%) PLL power.                                                                                                                                                                                                                                          |  |  |

| VDDT           | 11    | Power                         | 1.8V (±5%) analog core power.                                                                                                                                                                                                                                  |  |  |

| VDDCML         | 14    | Power                         | 1.8V (±5%) CML driver power.                                                                                                                                                                                                                                   |  |  |

| VDDIO          | 25    | Power                         | LVCMOS I/O power. 1.8V (±5%) or 3.3V (±10%).                                                                                                                                                                                                                   |  |  |

| VDDD           | 28    | Power                         | 1.8V (±5%) digital power.                                                                                                                                                                                                                                      |  |  |

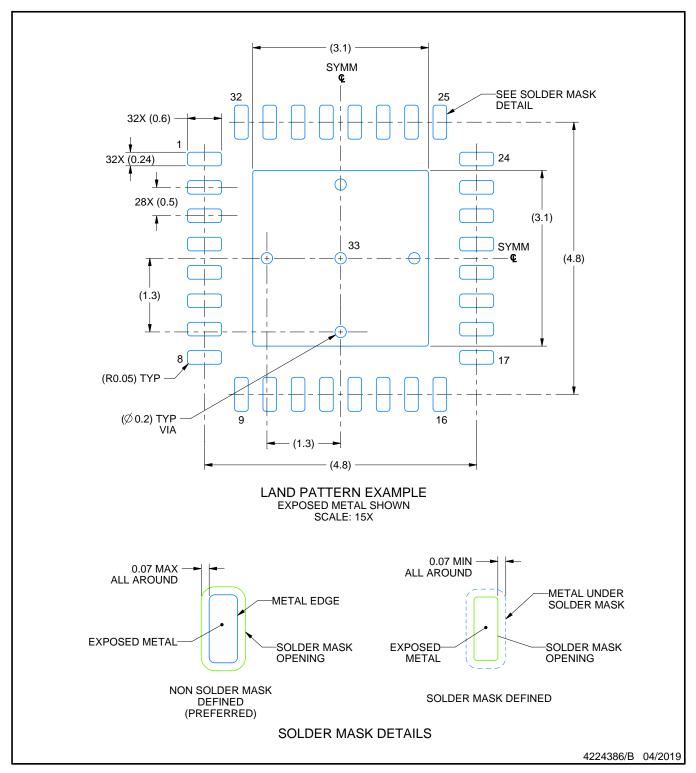

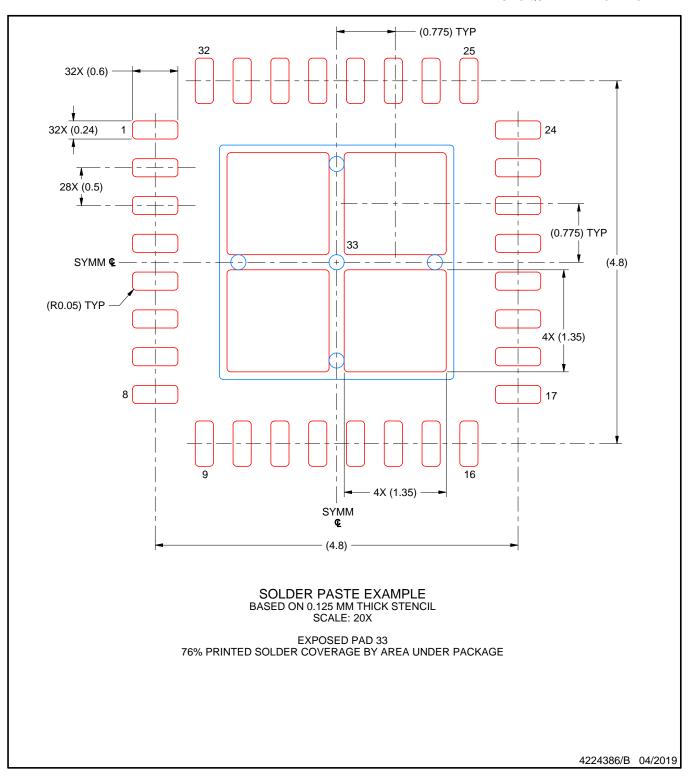

| GND            | DAP   | Ground                        | DAP is the large metal contact located at the bottom center of the LLP package. Connect to the GND plane with at least 9 vias.                                                                                                                                 |  |  |

| Other          |       |                               |                                                                                                                                                                                                                                                                |  |  |

| RES0           | 7     | Reserved                      | Reserved. Connect to GND.                                                                                                                                                                                                                                      |  |  |

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

# ABSOLUTE MAXIMUM RATINGS(1)

| ADOCEOTE MAXIMOM RATINGO                     |                                       |

|----------------------------------------------|---------------------------------------|

| Supply Voltage – V <sub>DDn</sub> (1.8V)     | −0.3V to +2.5V                        |

| Supply Voltage – V <sub>DDIO</sub>           | -0.3V to +4.0V                        |

| LVCMOS I/O Voltage                           | $-0.3V$ to + $(V_{DDIO} + 0.3V)$      |

| CML Driver I/O Voltage (V <sub>DDCML</sub> ) | $-0.3V$ to $+(V_{DDCML} + 0.3V)$      |

| Junction Temperature                         | +150°C                                |

| Storage Temperature                          | −65°C to +150°C                       |

| Maximum Package Power Dissipation Capacity   | 1/θ <sub>JA</sub> °C/W above +25°     |

| Package Derating:<br>DS90UA101-Q1 32L WQFN   |                                       |

| θ <sub>JA</sub> (based on 16 thermal vias)   | 38.4°C/W                              |

| θ <sub>JC</sub> (based on 16 thermal vias)   | 6.9°C/W                               |

| ESD Rating (IEC 61000-4-2)                   | $R_D = 330\Omega, C_S = 150pF$        |

| Air Discharge (DOUT+, DOUT-)                 | ≥±25 kV                               |

| Contact Discharge (DOUT+, DOUT-)             | ≥±7 kV                                |

| ESD Rating (ISO10605)                        | $R_D = 330\Omega$ , $C_S = 150/330pF$ |

| ESD Rating (ISO10605)                        | $R_D = 2K\Omega, C_S = 150/330pF$     |

| Air Discharge (DOUT+, DOUT-)                 | ≥±15 kV                               |

| Contact Discharge (DOUT+, DOUT-)             | ≥±8 kV                                |

| ESD Rating (HBM)                             | ≥±8 kV                                |

| ESD Rating (CDM)                             | ≥±1 kV                                |

| ESD Rating (MM)                              | ≥±250 V                               |

For soldering specifications: see product folder at www.ti.com and www.ti.com/lit/an/snoa549c/snoa549c.pdf

## RECOMMENDED OPERATING CONDITIONS

|                                                  | Min  | Nom | Max  | Units |

|--------------------------------------------------|------|-----|------|-------|

| Supply Voltage (V <sub>DDn</sub> )               | 1.71 | 1.8 | 1.89 | V     |

| LVCMOS Supply Voltage (V <sub>DDIO</sub> )<br>OR | 1.71 | 1.8 | 1.89 | V     |

| LVCMOS Supply Voltage (V <sub>DDIO</sub> )       | 3.0  | 3.3 | 3.6  | V     |

| Supply Noise <sup>(1)</sup>                      |      |     |      |       |

| V <sub>DDn</sub> (1.8V)                          |      |     | 25   | mVp-p |

| V <sub>DDIO</sub> (1.8V)                         |      |     | 25   | mVp-p |

| V <sub>DDIO</sub> (3.3V)                         |      |     | 50   | mVp-p |

| Operating Free Air Temperature (T <sub>A</sub> ) | -40  | +25 | +105 | °C    |

| SCK Clock Frequency (STP Cable)                  | 10   |     | 50   | MHz   |

| SCK Clock Frequency (Coaxial Cable)              | 25   |     | 50   | MHz   |

<sup>(1)</sup> Supply noise testing was done with minimum capacitors (as shown on Figure 32 and Figure 33 on the PCB. A sinusoidal signal is AC coupled to the V<sub>DDn</sub> (1.8V) supply with amplitude = 25 mVp-p measured at the device V<sub>DDn</sub> pins. Bit error rate testing of input to the Ser and output of the Des with 10 meter cable shows no error when the noise frequency on the Ser is less than 1 MHz. The Des on the other hand shows no error when the noise frequency is less than 750 kHz.

<sup>(1) &</sup>quot;Absolute Maximum Ratings" indicate limits beyond which damage to the device may occur, including inoperability and degradation of device reliability and/or performance. Functional operation of the device and/or non-degradation at the Absolute Maximum Ratings or other conditions beyond those indicated in the Recommended Operating Conditions is not implied. The Recommended Operating Conditions indicate conditions at which the device is functional; the device should not be operated beyond such conditions.

#### **ELECTRICAL CHARACTERISTICS**

Over recommended operating supply and temperature ranges unless otherwise specified. (1)(2)(3)

| Symbol          | Parameter                                       | Condition                                                         | Min                       | Тур                         | Max                                    | Units                |    |

|-----------------|-------------------------------------------------|-------------------------------------------------------------------|---------------------------|-----------------------------|----------------------------------------|----------------------|----|

| LVCMOS DC S     | PECIFICATIONS 3.3V I/O (S                       | SER INPUTS, GPI, GPO,                                             | <b>CONTROL INPUTS</b>     | AND OUTP                    | JTS)                                   |                      |    |

| V <sub>IH</sub> | High Level Input<br>Voltage                     | V <sub>IN</sub> = 3.0V to 3.6V                                    |                           | 2.0                         |                                        | V <sub>IN</sub>      | V  |

| $V_{IL}$        | Low Level Input<br>Voltage                      | V <sub>IN</sub> = 3.0V to 3.6V                                    |                           | GND                         |                                        | 0.8                  | V  |

| I <sub>IN</sub> | Input Current                                   | V <sub>IN</sub> = 0V or 3.6V<br>V <sub>IN</sub> = 3.0V to 3.6V    |                           | -20                         | ±1                                     | +20                  | μA |

| V <sub>OH</sub> | High Level Output<br>Voltage                    | $V_{DDIO} = 3.0V$ to 3.6V<br>$I_{OH} = -4$ mA                     |                           | 2.4                         |                                        | V <sub>DDIO</sub>    | V  |

| V <sub>OL</sub> | Low Level Output<br>Voltage                     | $V_{DDIO} = 3.0V$ to 3.6V $I_{OL} = +4$ mA                        |                           | GND                         |                                        | 0.4                  | V  |

| I <sub>OS</sub> | Output Short Circuit<br>Current                 | V <sub>OUT</sub> = 0V                                             | Serializer<br>GPO Outputs |                             | -15                                    |                      | mA |

| I <sub>OZ</sub> | TRI-STATE Output Current                        | $PDB = 0V,$ $V_{OUT} = 0V \text{ or } V_{DD}$                     | LVCMOS Outputs            | -20                         |                                        | +20                  | μΑ |

| LVCMOS DC S     | PECIFICATIONS 1.8V I/O (S                       | SER INPUTS, GPI, GPO,                                             | <b>CONTROL INPUTS</b>     | AND OUTP                    | JTS)                                   |                      |    |

| V <sub>IH</sub> | High Level Input<br>Voltage                     | V <sub>IN</sub> = 1.71V to 1.89V                                  |                           | 0.65 V <sub>IN</sub>        |                                        | V <sub>IN</sub>      | V  |

| V <sub>IL</sub> | Low Level Input<br>Voltage                      | V <sub>IN</sub> = 1.71V to 1.89V                                  |                           | GND                         |                                        | 0.35 V <sub>IN</sub> | V  |

| I <sub>IN</sub> | Input Current                                   | V <sub>IN</sub> = 0V or 1.89V<br>V <sub>IN</sub> = 1.71V to 1.89V |                           | -20                         | ±1                                     | +20                  | μΑ |

| V <sub>OH</sub> | High Level Output<br>Voltage                    | $V_{DDIO} = 1.71V \text{ to } 1.89V$<br>$I_{OH} = -4 \text{ mA}$  |                           | V <sub>DDIO</sub> -<br>0.45 |                                        | V <sub>DDIO</sub>    | V  |

| I <sub>OS</sub> | Output Short Circuit Current                    | V <sub>OUT</sub> = 0V                                             | Serializer<br>GPO Outputs |                             | -11                                    |                      | mA |

| l <sub>oz</sub> | TRI-STATE Output Current                        | $PDB = 0V,$ $V_{OUT} = 0V \text{ or } V_{DD}$                     | LVCMOS Outputs            | -20                         |                                        | +20                  | μΑ |

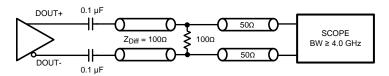

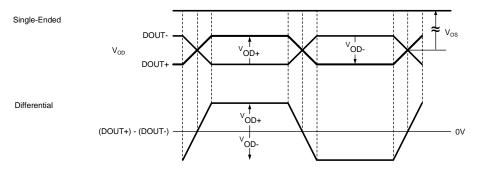

| CML DRIVER D    | OC SPECIFICATIONS (DOU                          | T+, DOUT-)                                                        |                           |                             |                                        |                      |    |

| V <sub>OD</sub> | Output Differential Voltage                     | $R_L = 100\Omega$ (Figure 8)                                      |                           | 268                         | 340                                    | 412                  | mV |

| $\Delta V_{OD}$ | Output Differential Voltage Unbalance           | $R_L = 100\Omega$                                                 |                           |                             | 1                                      | 50                   | mV |

| V <sub>OS</sub> | Output Differential<br>Offset Voltage           | R <sub>L</sub> = 100Ω<br>(Figure 8)                               |                           |                             | V <sub>DD</sub> -<br>V <sub>OD/2</sub> |                      | V  |

| $\Delta V_{OS}$ | Offset Voltage<br>Unbalance                     | R <sub>L</sub> = 100Ω                                             |                           | 1                           | 50                                     | mV                   |    |

| I <sub>OS</sub> | Output Short Circuit<br>Current                 | DOUT± = 0V                                                        |                           |                             | -26                                    |                      | mA |

| R <sub>T</sub>  | Differential Internal<br>Termination Resistance | Differential across DOU                                           | T+ and DOUT-              | 80                          | 100                                    | 120                  | 0  |

|                 | Single-ended<br>Termination Resistance          | DOUT+ or DOUT-                                                    |                           | 40                          | 50                                     | 60                   | Ω  |

<sup>(1)</sup> The Electrical Characteristics tables list verified specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not

Current into device pins is defined as positive. Current out of a device pin is defined as negative. Voltages are referenced to ground except  $V_{OD}$ ,  $\Delta V_{OD}$ ,  $V_{TH}$  and  $V_{TL}$  which are differential voltages. Typical values represent most likely parametric norms at 1.8V or 3.3V,  $T_A = +25^{\circ}$ C, and at the Recommended Operation Conditions at the time of product characterization and are not verified.

# **ELECTRICAL CHARACTERISTICS** (continued)

Over recommended operating supply and temperature ranges unless otherwise specified. (1)(2)(3)

| Symbol              | Parameter                                                                      | Conditions                                                                                                                                                                                                 |                                                                                             | Min | Тур | Max  | Units |

|---------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----|-----|------|-------|

| SUPPLY CURR         | ENT, DIGITAL, PLL, AND                                                         | ANALOG VDD                                                                                                                                                                                                 |                                                                                             |     |     |      |       |

| I <sub>DDIOT</sub>  | Serializer (Tx) V <sub>DDIO</sub><br>Supply Current<br>(includes load current) | $ \begin{array}{l} R_L = 100\Omega \\ \text{WORST CASE Pattern} \\ \text{(Figure 5)} \end{array}  \begin{array}{l} V_{DDIO} = 1.89V \\ \text{f} = 50 \text{ MHz} \\ \text{Default Registers} \end{array} $ |                                                                                             |     | 1.5 | 3    |       |

|                     |                                                                                |                                                                                                                                                                                                            | V <sub>DDIO</sub> = 3.6V<br>f = 50 MHz<br>Default Registers                                 |     | 5   | 8    |       |

|                     |                                                                                | $R_L = 100\Omega$<br>Random Pattern                                                                                                                                                                        | V <sub>DDIO</sub> = 1.8V<br>f = 24.576 MHz<br>Default Registers                             |     | 1.5 |      | ^     |

|                     |                                                                                |                                                                                                                                                                                                            | V <sub>DDIO</sub> 1.8V<br>f = 12.288 MHz<br>Default Registers                               |     | 1.5 |      | mA    |

|                     |                                                                                |                                                                                                                                                                                                            | V <sub>DDIO</sub> = 3.3V<br>f = 24.576 MHz<br>Default Registers                             |     | 5   |      |       |

|                     |                                                                                |                                                                                                                                                                                                            | $V_{\rm DDIO} = 3.3 V$<br>$f = 12.288  {\rm MHz}$<br>Default Registers                      |     | 5   |      |       |

| I <sub>DDT</sub>    | Serializer (Tx) V <sub>DDn</sub><br>Core Supply Current                        | $R_L = 100\Omega$<br>WORST CASE Pattern<br>(Figure 5)                                                                                                                                                      | $V_{DDn} = 1.89V,$<br>$V_{DDIO} = 3.6V$<br>f = 50  MHz<br>Default Registers                 |     | 61  | 80   |       |

|                     |                                                                                | $R_L = 100\Omega$<br>Random Pattern                                                                                                                                                                        | V <sub>DDn</sub> = 1.8V,<br>V <sub>DDIO</sub> = 3.3V<br>f = 24.576 MHz<br>Default Registers |     | 51  |      | mA    |

|                     |                                                                                |                                                                                                                                                                                                            | V <sub>DDn</sub> = 1.8V,<br>V <sub>DDIO</sub> = 3.3V<br>f = 12.288 MHz<br>Default Registers |     | 49  |      |       |

|                     | Serializer (Tx) Supply<br>Current Power-down                                   | PDB = 0V; All other<br>LVCMOS Inputs = 0V                                                                                                                                                                  | V <sub>DDIO</sub> = 1.89V<br>Default Registers                                              |     | 300 | 1000 | μA    |

| I <sub>DDTZ</sub>   |                                                                                |                                                                                                                                                                                                            | V <sub>DDIO</sub> = 3.6V<br>Default Registers                                               |     | 300 | 1000 | μA    |

|                     | Serializer (Tx) V <sub>DDIO</sub><br>Supply Current Power-                     | PDB = 0V; All other<br>LVCMOS Inputs = 0V                                                                                                                                                                  | V <sub>DDIO</sub> = 1.89V<br>Default Registers                                              |     | 15  | 100  | μA    |

| I <sub>DDIOTZ</sub> | down                                                                           |                                                                                                                                                                                                            | V <sub>DDIO</sub> = 3.6V<br>Default Registers                                               |     | 15  | 100  | μA    |

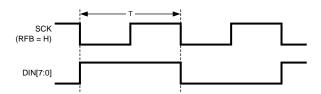

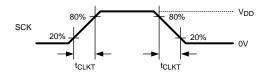

# **ELECTRICAL CHARACTERISTICS:** Recommended Timing for SCK

Over recommended operating supply and temperature ranges unless otherwise specified. (1)(2)(3)(4)

| Symbol                                                                                  | Parameter                            | Conditions F        |     | Min  | Тур  | Max | Units |

|-----------------------------------------------------------------------------------------|--------------------------------------|---------------------|-----|------|------|-----|-------|

| t <sub>TCP</sub>                                                                        | Transmit Clock Period                | STP Cable           | SCK | 20   | Т    | 100 |       |

|                                                                                         |                                      | Coaxial Cable       | SCK | 20   | Т    | 40  | ns    |

| t <sub>TCIH</sub>                                                                       | Transmit Clock Input High Time       | f = 10 MHz - 50 MHz | SCK | 0.4  | 0.5  | 0.6 | Т     |

| t <sub>TCIL</sub>                                                                       | Transmit Clock Input Low Time        | f = 10 MHz - 50 MHz | SCK | 0.4  | 0.5  | 0.6 | Т     |

| t <sub>CLKT</sub>                                                                       | SCK Input Transition Time (Figure 9) | f = 10 MHz - 50 MHz | SCK | 0.05 | 0.25 | 0.3 | Т     |

| t <sub>JIT0</sub> SCK Input Jitter Refer to Jitter freq> $f/40$ , $f = 10$ MHz - 50 MHz |                                      | SCK                 |     | 0.1  |      | Т   |       |

<sup>(1)</sup> The Electrical Characteristics tables list verified specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not verified.

<sup>(2)</sup> Current into device pins is defined as positive. Current out of a device pin is defined as negative. Voltages are referenced to ground except V<sub>OD</sub>, ΔV<sub>OD</sub>, V<sub>TH</sub> and V<sub>TL</sub> which are differential voltages.

<sup>(3)</sup> Typical values represent most likely parametric norms at 1.8V or 3.3V, T<sub>A</sub> = +25°C, and at the Recommended Operation Conditions at the time of product characterization and are not verified.

<sup>(4)</sup> Recommended Input Timing Requirements are input specifications and not tested in production.

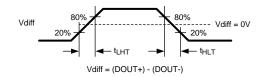

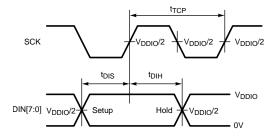

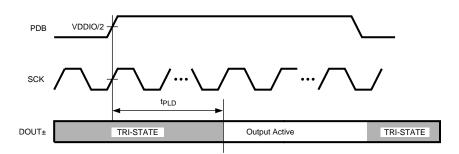

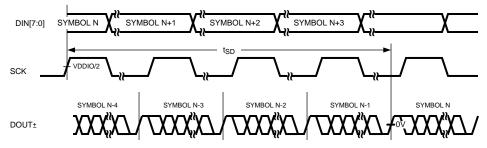

# **ELECTRICAL CHARACTERISTICS: Serializer Switching Characteristics**

Over recommended operating supply and temperature ranges unless otherwise specified. (1)(2)(3)

| Symbol            | Parameter                                                                    | Conditions                                                                                                                                                                      | Min    | Тур   | Max | Units |

|-------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|-----|-------|

| t <sub>LHT</sub>  | CML Low-to-High Transition Time                                              | $R_L = 100\Omega$ (Figure 6)                                                                                                                                                    |        | 150   | 330 | ps    |

| t <sub>HLT</sub>  | CML High-to-Low Transition Time                                              | $R_L = 100\Omega$ (Figure 6)                                                                                                                                                    |        | 150   | 330 | ps    |

| t <sub>DIS</sub>  | Data Input Setup to SCK                                                      | Serializer Data Inputs                                                                                                                                                          | 2      |       |     | ns    |

| t <sub>DIH</sub>  | Data Input Hold from SCK                                                     | (Figure 10)                                                                                                                                                                     | 2      |       |     | ns    |

| t <sub>PLD</sub>  | Serializer PLL Lock Time                                                     | $R_L = 100\Omega^{(4)(5)}$ , (Figure 11)                                                                                                                                        |        | 1     | 2   | ms    |

| t <sub>SD</sub>   | Serializer Delay <sup>(5)</sup>                                              | $R_T = 100\Omega$<br>Register 0x03h b[0] (TRFB = 1)<br>(Figure 12)                                                                                                              | 11.75T | 13T   | 15T | ns    |

| t <sub>JIND</sub> | Serializer Output<br>Deterministic Jitter                                    | Serializer output intrinsic deterministic jitter . Measured (cycle-cycle) with PRBS-7 test pattern (3) (6)                                                                      |        | 0.13  |     | UI    |

| t <sub>JINR</sub> | Serializer Output Random<br>Jitter                                           | Serializer output intrinsic random jitter (cycle-cycle). Alternating-1,0 pattern.                                                                                               |        | 0.04  |     | UI    |

| t <sub>JINT</sub> | Peak-to-peak Serializer<br>Output Jitter                                     | Serializer output peak-to-peak jitter includes deterministic jitter, random jitter, and jitter transfer from Serializer input. Measured (cycle-cycle) with PRBS-7 test pattern. |        | 0.396 |     | UI    |

| $\lambda_{STXBW}$ | Serializer Jitter Transfer<br>Function -3 dB Bandwidth <sup>(7)</sup>        | SCK = 50MHz                                                                                                                                                                     |        | 2.2   |     | MHz   |

| $\delta_{STX}$    | Serializer Jitter Transfer<br>Function (Peaking) <sup>(7)</sup>              | SCK = 50MHz                                                                                                                                                                     |        | 1.16  |     | dB    |

| δ <sub>STXf</sub> | Serializer Jitter Transfer<br>Function (Peaking<br>Frequency) <sup>(7)</sup> | SCK = 50MHz                                                                                                                                                                     |        | 600   |     | kHz   |

- (1) The Electrical Characteristics tables list verified specifications under the listed Recommended Operating Conditions except as otherwise modified or specified by the Electrical Characteristics Conditions and/or Notes. Typical specifications are estimations only and are not verified.

- (2) Current into device pins is defined as positive. Current out of a device pin is defined as negative. Voltages are referenced to ground except  $V_{OD}$ ,  $\Delta V_{OD}$ ,  $V_{TH}$  and  $V_{TL}$  which are differential voltages.

(3) Typical values represent most likely parametric norms at 1.8V or 3.3V,  $T_A = +25$ °C, and at the Recommended Operation Conditions at

- the time of product characterization and are not verified.

- $t_{\text{PLD}}$  and  $t_{\text{DDLT}}$  is the time required by the Serializer and Deserializer to obtain lock when exiting power-down state with an active SCK.

- Specification is verified by design.

- UI Unit Interval is equivalent to one ideal serialized data bit width. The UI scales with SCK frequency. (6)

- (7) Specification is by characterization and is not tested in production.

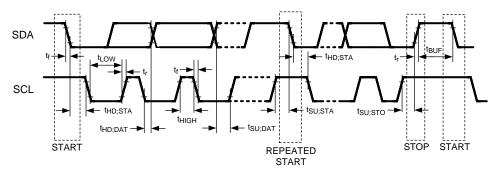

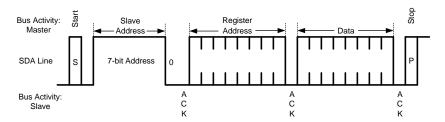

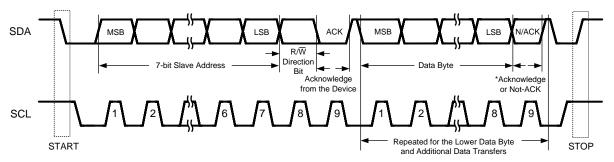

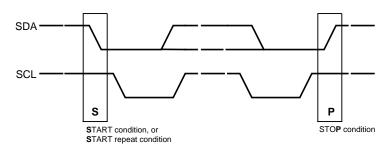

# **BIDIRECTIONAL CONTROL BUS TIMING SPECIFICATIONS**

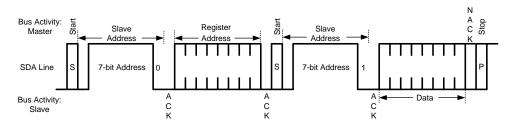

# Bidirectional Control Bus: AC Timing Specifications (SCL, SDA) - I<sup>2</sup>C Compliant

Over recommended supply and temperature ranges unless otherwise specified. (Figure 4)

| Symbol              | Parameter                                 | Conditions    | Min | Тур | Max  | Units |

|---------------------|-------------------------------------------|---------------|-----|-----|------|-------|

| Recomm              | ended Input Timing Requirements           |               |     |     |      |       |

| 4                   | SCI Clark Francisco                       | Standard Mode |     |     | 100  | kHz   |

| f <sub>SCL</sub>    | SCL Clock Frequency                       | Fast Mode     |     |     | 400  | kHz   |

|                     | SCL Low Period                            | Standard Mode | 4.7 |     |      | μs    |

| t <sub>LOW</sub>    | SCL Low Period                            | Fast Mode     | 1.3 |     |      | μs    |

|                     | SCL High Period                           | Standard Mode | 4.0 |     |      | μs    |

| t <sub>HIGH</sub>   | SCL High Fellod                           | Fast Mode     | 0.6 |     |      | μs    |

| +                   | Hold time for a start or a repeated start | Standard Mode | 4.0 |     |      | μs    |

| t <sub>HD:STA</sub> | condition                                 | Fast Mode     | 0.6 |     |      | μs    |

| +                   | Set Up time for a start or a repeated     | Standard Mode | 4.7 |     |      | μs    |

| t <sub>SU:STA</sub> | start condition                           | Fast Mode     | 0.6 |     |      | μs    |

|                     | Data Hold Time                            | Standard Mode | 0   |     | 3.45 | μs    |

| t <sub>HD:DAT</sub> | Data Hold Tillle                          | Fast Mode     | 0   |     | 900  | ns    |

|                     | Data Cat I la Tima                        | Standard Mode | 250 |     |      | ns    |

| t <sub>SU:DAT</sub> | Data Set Up Time                          | Fast Mode     | 100 |     |      | ns    |

|                     | Sat Un Time for STOP Condition            | Standard Mode | 4.0 |     |      | μs    |

| t <sub>SU:STO</sub> | Set Up Time for STOP Condition            | Fast Mode     | 0.6 |     |      | μs    |

| +                   | Bus Free time between Stop and Start      | Standard Mode | 4.7 |     |      | μs    |

| t <sub>BUF</sub>    | Bus Free time between Stop and Start      | Fast Mode     | 1.3 |     |      | μs    |

|                     | SCL & SDA Bigs Time                       | Standard Mode |     |     | 1000 | ns    |

| t <sub>r</sub>      | SCL & SDA Rise Time                       | Fast Mode     |     |     | 300  | ns    |

| +                   | SCL & SDA Fall Time                       | Standard Mode |     |     | 300  | ns    |

| t <sub>f</sub>      | SOL & SDA Fall Time                       | Fast Mode     |     |     | 300  | ns    |

# Bidirectional Control Bus: DC Timing Specifications (SCL, SDA) - I<sup>2</sup>C Compliant<sup>(1)</sup>

Over recommended supply and temperature ranges unless otherwise specified.

| Symbol              | Parameter                       | Min                                                   | Тур                   | Max | Units                 |    |

|---------------------|---------------------------------|-------------------------------------------------------|-----------------------|-----|-----------------------|----|

| Recomme             | ended Input Timing Requirements |                                                       |                       |     |                       |    |

| V <sub>IH</sub>     | Input High Level                | SDA and SCL                                           | 0.7*V <sub>DDIO</sub> |     | $V_{DDIO}$            | V  |

| V <sub>IL</sub>     | Input Low Level                 | SDA and SCL                                           | GND                   |     | 0.3*V <sub>DDIO</sub> | V  |

| V <sub>HY</sub>     | Input Hysteresis                |                                                       |                       | >50 |                       | mV |

| V <sub>OL</sub>     | Output Low Level                | SDA, I <sub>OL</sub> =0.5mA                           | 0                     |     | 0.4                   | V  |

| I <sub>IN</sub>     | Input Current                   | SDA or SCL, V <sub>IN</sub> =V <sub>DDIO</sub> OR GND | -10                   |     | 10                    | μΑ |

| t <sub>R</sub>      | SDA Rise Time-READ              | SDA, RPU = 10kΩ, Cb ≤                                 |                       | 430 |                       | ns |

| t <sub>F</sub>      | SDA Fall Time-READ              | 400pF(Figure 4)                                       |                       | 20  |                       | ns |

| t <sub>SU;DAT</sub> |                                 | (Figure 4)                                            |                       | 560 |                       | ns |

| t <sub>HD;DAT</sub> |                                 | (Figure 4)                                            |                       | 615 |                       | ns |

| t <sub>SP</sub>     |                                 |                                                       |                       | 50  |                       | ns |

| C <sub>IN</sub>     |                                 | SDA or SCL                                            |                       | <5  |                       | pF |

<sup>(1)</sup> Specification is verified by design.

#### **TIMING AND CIRCUIT DIAGRAMS**

Figure 4. Bidirectional Control Bus Timing

Figure 5. "Worst Case" Test Pattern

Figure 6. Serializer CML Output Transition Times

Figure 7. Serializer CML Output Load

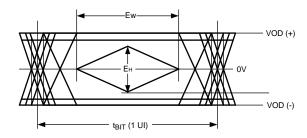

Figure 8. Serializer VOD and Differential Diagram

Figure 9. Serializer Input Clock Transition Times

Figure 10. Serializer Setup/Hold Times

Figure 11. Serializer PLL Lock Time

Figure 12. Serializer Delay

Figure 13. CML Output Driver

#### **DS90UA101-Q1 REGISTER INFORMATION**

The table below contains information on the DS90UA101-Q1 control registers. These registers are accessible locally via the I<sup>2</sup>C control interface, or remotely via the Bidirectional Control Channel. Addresses not listed are reserved. Fields listed as reserved should not be changed from the listed default value.

| Addr<br>(Hex) | Name                       | Bits | Field                     | R/W | Default (Hex) | Description                                                                                                                                                                                                   |

|---------------|----------------------------|------|---------------------------|-----|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x00          | I <sup>2</sup> C Device ID | 7:1  | DEVICE ID                 | RW  | 0xB0          | 7-bit address of Serializer.<br>0x58'h (0101_100X'b) default.                                                                                                                                                 |

|               |                            | 0    | SER ID SEL                | RW  |               | Serializer DEVICE ID is from IDx.     Register I <sup>2</sup> C DEVICE ID overrides IDx.                                                                                                                      |

| 0x01          | Power and Reset            | 7    | RSVD                      |     | 0x30          | Reserved.                                                                                                                                                                                                     |

|               |                            | 6    | RDS                       | RW  |               | Digital output drive strength. 1: High drive strength. 0: Low drive strength.                                                                                                                                 |

|               |                            | 5    | V <sub>DDIO</sub> Control | RW  |               | Auto voltage control. 1: Enable (auto-detect mode). 0: Disable.                                                                                                                                               |

|               |                            | 4    | V <sub>DDIO</sub> Mode    | RW  |               | V <sub>DDIO</sub> voltage set. 1: Sets V <sub>DDIO</sub> mode to 3.3V. 0: Sets V <sub>DDIO</sub> mode to 1.8V.                                                                                                |

|               |                            | 3    | ANAPWDN                   | RW  |               | This register can be set only through local I <sup>2</sup> C access. 1: Analog power-down: Powers down the analog block in the Serializer.  0: Analog power-up: Powers up the analog block in the Serializer. |

|               |                            | 2    | RSVD                      |     |               | Reserved.                                                                                                                                                                                                     |

|               |                            | 1    | Digital Reset 1           | RW  |               | <ol> <li>Resets the digital block except for register values. This bit is self-clearing.</li> <li>Normal operation.</li> </ol>                                                                                |

|               |                            | 0    | Digital Reset 0           | RW  |               | Resets the entire digital block including all register values. This bit is self-clearing.     Normal operation.                                                                                               |

# ZHCSBO6A - JULY 2013-REVISED SEPTEMBER 2013

| Addr<br>(Hex) | Name                     | Bits | Field                                                | R/W | Default<br>(Hex) | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                               |  |

|---------------|--------------------------|------|------------------------------------------------------|-----|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0x03          | General<br>Configuration | 7    | RX CRC Checker<br>Enable                             | RW  | 0xC5             | Back channel CRC Checker enable. 1:Enable. 0:Disable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                               |  |

|               |                          | 6    | TX Parity<br>Generator Enable                        | RW  |                  | Forward channel Parity Generator enable. 1: Enable. 0: Disable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                               |  |

|               |                          | 5    | CRC Error Reset                                      | RW  |                  | Clear CRC error counters. This bit is NOT self-clearing. 1: Clear counters. 0: Normal operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                               |  |

|               |                          | 4    | I <sup>2</sup> C Remote Write<br>Auto<br>Acknowledge | RW  |                  | Automatically acknowledge I <sup>2</sup> C remote writes. This mode should only be used when the system is LOCKED.  1: Enable: When enabled, I <sup>2</sup> C writes to the Deserializer (or any remote I <sup>2</sup> C slave, if I <sup>2</sup> C Pass All is enabled) are immediately acknowledged without waiting for the Deserializer to acknowledge the write. The accesses are then remapped to the address specified in 0x06.  0: Disable.                                                                                                                                                                                                                                                                                                                |                                                                                                                                                               |  |

|               |                          | 3    | I <sup>2</sup> C Pass All                            | RW  |                  | Pass-through all I <sup>2</sup> C transactions. For an explanation of I <sup>2</sup> C pass-through, refer to I <sup>2</sup> C Pass-Through and Multiple Device Addressing.  1: Enable pass-through of all I <sup>2</sup> C accesses to I <sup>2</sup> C IDs that do not match the Serializer I <sup>2</sup> C ID. The I <sup>2</sup> C accesses are then remapped to the address specified in register 0x06.  0: Enable pass-through only of I <sup>2</sup> C accesses to I <sup>2</sup> C IDs matching either the remote Deserializer I <sup>2</sup> C ID or the remote slave I <sup>2</sup> C ID.                                                                                                                                                              |                                                                                                                                                               |  |

|               |                          | 2    | I <sup>2</sup> C Pass-Through                        | RW  |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | I <sup>2</sup> C pass-through mode. 1: Pass-through enabled. Refer to I <sup>2</sup> C Pass-Through and Multiple Device Addressing. 0: Pass-through disabled. |  |

|               |                          | 1    | RSVD                                                 | RW  |                  | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                               |  |

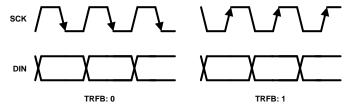

|               |                          | 0    | TRFB                                                 | RW  |                  | SCK clock edge select.  1: Parallel interface data is strobed on the rising clock edge.  0: Parallel interface data is strobed on the falling clock edge.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                               |  |

| 0x06          | DES ID                   | 7:1  | Deserializer<br>Device ID                            | RW  |                  | This field stores the 7-bit l <sup>2</sup> C address of the remote Deserializer. If an l <sup>2</sup> C transaction (originating from the Serializer side) is addressed to DES Alias, the transaction will be remapped to this address before it is passed across the Bidirectional Control Channel to the remote Deserializer.  This field is automatically configured by the Bidirectional Control Channel once RX LOCK has been detected. Software may overwrite this value, but the Freeze Device ID bit should also be asserted to prevent overwriting by the Bidirectional Control Channel.  A value of 0 in this field disables l <sup>2</sup> C access to the remote Deserializer. Refer to l <sup>2</sup> C Pass-Through and Multiple Device Addressing. |                                                                                                                                                               |  |

|               |                          | 0    | Freeze Device ID                                     | RW  |                  | Freeze Deserializer Device ID.  1: Prevents auto-loading of the Deserializer Device ID from the back channel. The ID will be frozen at the value written.  0: Allows auto-loading of the Deserializer Device ID from the back channel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                               |  |

#### www.ti.com.cn

| Addr<br>(Hex) | Name           | Bits | Field                    | R/W | Default<br>(Hex) | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|---------------|----------------|------|--------------------------|-----|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0x07          | DES Alias      | 7:1  | Deserializer Alias<br>ID | RW  | 0x00             | This field stores a 7-bit I <sup>2</sup> C address. Once set, it configures the Serializer to accept any transaction designated for the I <sup>2</sup> C address stored in this field. The transaction will then be remapped to the I <sup>2</sup> C address specified in the DES ID register.  A value of 0 in this field disables I <sup>2</sup> C access to the remote Deserializer. Refer to I <sup>2</sup> C Pass-Through and Multiple Device Addressing. |  |  |  |  |

|               |                | 0    | RSVD                     |     |                  | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 80x0          | Slave ID       | 7:1  | Slave ID                 | RW  | 0x00             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|               |                | 0    | RSVD                     |     |                  | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 0x09          | Slave Alias    | 7:1  | Slave Alias ID           | RW  | 0x00             | This field stores a 7-bit I <sup>2</sup> C address. Once set, it configures the Serializer to accept any transaction designated for the I <sup>2</sup> C address stored in this field. The transaction will then be remapped to the I <sup>2</sup> C address specified in the Slave ID register.  A value of 0 in this field disables I <sup>2</sup> C access to the remote slave. Refer to I <sup>2</sup> C Pass-Through and Multiple Device Addressing.      |  |  |  |  |

|               |                | 0    | RSVD                     |     |                  | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 0x0A          | CRC Errors     | 7:0  | CRC Error Byte 0         | R   | 0x00             | Number of back-channel CRC errors during normal operation. Least significant byte.                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| 0x0B          | CRC Errors     | 7:0  | CRC Error Byte 1         | R   | 0x00             | Number of back-channel CRC errors during normal operation. Most significant byte.                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| 0x0C          | General Status | 7:5  | Rev-ID                   | R   |                  | Revision ID. 0x00: Production.                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|               |                | 4    | RX Lock Detect           | R   |                  | 1: RX LOCKED.<br>0: RX not LOCKED.                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

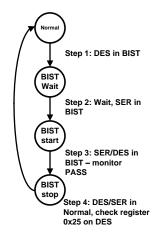

|               |                | 3    | BIST CRC Error<br>Status | R   |                  | 1: CRC errors in BIST mode. 0: No CRC errors in BIST mode.                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|               |                | 2    | SCK Detect               | R   |                  | 1: Valid SCK detected. 0: Valid SCK not detected.                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|               |                | 1    | DES Error                | R   |                  | 1: CRC error is detected during communication with the Deserializer.     This bit is cleared upon loss of link or assertion of CRC Error Reset bit in register 0x03[5].     0: No errors detected.                                                                                                                                                                                                                                                             |  |  |  |  |

|               |                | 0    | Link Detect              | R   |                  | 1: Cable link detected. 0: Cable link not detected. This includes any of the following faults:  — Cable open. — '+' and '-' shorted. — Short to GND. — Short to battery.                                                                                                                                                                                                                                                                                       |  |  |  |  |

# ZHCSBO6A - JULY 2013-REVISED SEPTEMBER 2013

| Addr<br>(Hex) | Name                           | Bits | Field                 | R/W | Default<br>(Hex) | Description                                                                                                                                                                                                                    |

|---------------|--------------------------------|------|-----------------------|-----|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0x0D          | GPO3 and GPO2<br>Configuration | 7    | GPO2 Output<br>Value  | RW  | 0x55             | Local GPO2 Output Value. This value is output on the GPO2 pin when GPO2 is enabled, the local GPO2 direction is set to output, and remote GPO2 control is disabled.                                                            |

|               |                                | 6    | GPO2 Remote<br>Enable | RW  |                  | Remote GPO2 control:  1: Enable GPO2 control from the remote Deserializer.  The GPO2 pin needs to be an output, and the value is received from the remote Deserializer.  0: Disable GPO2 control from the remote Deserializer. |

|               |                                | 5    | GPO2 Direction        | RW  |                  | Local GPO2 direction: 1: Input. 0: Output.                                                                                                                                                                                     |

|               |                                | 4    | GPO2 Enable           | RW  |                  | GPO2 enable: 1: Enable GPO2 operation. 0: TRI-STATE.                                                                                                                                                                           |

|               |                                | 3    | GPO3 Output<br>Value  | RW  |                  | Local GPO3 Output Value. This value is output on the GPO3 pin when GPO3 is enabled, the local GPO3 direction is set to output, and remote GPO3 control is disabled.                                                            |

|               |                                | 2    | GPO3 Remote<br>Enable | RW  |                  | Remote GPO3 control:  1: Enable GPO3 control from the remote Deserializer.  The GPO3 pin needs to be an output, and the value is received from the remote Deserializer.  0: Disable GPO3 control from the remote Deserializer. |

|               |                                | 1    | GPO3 Direction        | RW  |                  | Local GPO3 direction: 1: Input. 0: Output.                                                                                                                                                                                     |

|               |                                | 0    | GPO3 Enable           | RW  |                  | GPO3 enable: 1: Enable GPO3 operation. 0: TRI-STATE.                                                                                                                                                                           |

| 0x0E          | GPO1 and GPO0<br>Configuration | 7    | GPO0 Output<br>Value  | RW  | 0x35             | Local GPO0 Output Value. This value is output on the GPO0 pin when GPO0 is enabled, the local GPO0 direction is set to output, and remote GPO0 control is disabled.                                                            |

|               |                                | 6    | GPO0 Remote<br>Enable | RW  |                  | Remote GPO0 control:  1: Enable GPO0 control from the remote Deserializer.  The GPO0 pin needs to be an output, and the value is received from the remote Deserializer.  0: Disable GPO0 control from the remote Deserializer. |

|               |                                | 5    | GPO0 Direction        | RW  |                  | Local GPO0 direction: 1: Input. 0: Output.                                                                                                                                                                                     |

|               |                                | 4    | GPO0 Enable           | RW  |                  | GPO0 enable: 1: Enable GPO0 operation. 0: TRI-STATE.                                                                                                                                                                           |

|               |                                | 3    | GPO1 Output<br>Value  | RW  |                  | Local GPO1 Output Value. This value is output on the GPO1 pin when GPO1 is enabled, the local GPO1 direction is set to output, and remote GPO1 control is disabled.                                                            |

|               |                                | 2    | GPO1 Remote<br>Enable | RW  |                  | Remote GPO1 control:  1: Enable GPO1 control from the remote Deserializer.  The GPO1 pin needs to be an output, and the value is received from the remote Deserializer.  0: Disable GPO1 control from the remote Deserializer. |

|               |                                | 1    | GPO1 Direction        | RW  |                  | Local GPO1 direction: 1: Input. 0: Output.                                                                                                                                                                                     |

|               |                                | 0    | GPO1 Enable           | RW  |                  | GPO1 enable: 1: Enable GPO1 operation. 0: TRI-STATE.                                                                                                                                                                           |

#### www.ti.com.cn

| No.   PC Master Config   4.3   SDA Output   PRW   Delay   PRW                                                                                                                                                                                                                                                                                                                                                                                                                                               | Addr<br>(Hex) | Name                           | Bits | Field                         | R/W | Default<br>(Hex) | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |