**TPL5100**

ZHCSBB7C -JULY 2013-REVISED DECEMBER 2014

# TPL5100 具有 MOS 驱动器的毫微功耗可编程定时器

# 特性

- 电源电压范围为 1.8V 至 5.0V

- 可选定时器间隔 16s 至 1024s

- 流耗 30nA (2.5V 时的典型值)

#### 应用 2

- 电池供电系统

- 能量收集系统

- 远程数据记录器

- 传感器节点

- 电源选通应用

- 楼宇自动化

- 低功耗无线系统

- 消费类电子产品

# 3 说明

TPL5100 是一个长期定时器集成电路 (IC), 针对低功 耗应用进行了优化。 TPL5100 能够替代一个微型控制 器 (µC) 的内部定时器, 使 µC 能够完全关闭, 而不用 运行一个定时器,从而减少60%至80%的总功 耗。TPL5100 适用于循环供电应用,并且提供 16 秒 至 1024 秒的可选定时间隔。 TPL5100 还可通过一个 电源正常数字输入监视电池管理 IC,并在存在正常电 源电压时仅为微控制器供电。 此器件采用 10 引脚超 薄小外形尺寸 (VSSOP) 封装。

## 器件信息(1)

| 器件型号    | 封装         | 封装尺寸 (标称值)      |

|---------|------------|-----------------|

| TPL5100 | VSSOP (10) | 3.00mm x 3.00mm |

(1) 如需了解所有可用封装,请见数据表末尾的可订购产品附录。

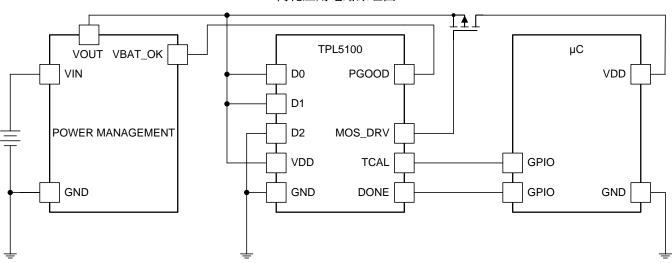

## 简化应用电路原理图

|   | 目園                                           |    | 70 5 " 181 18"                 | ,          |

|---|----------------------------------------------|----|--------------------------------|------------|

| 1 | 特性 1                                         |    | 7.2 Functional Block Diagram   |            |

| 2 | 应用1                                          |    | 7.3 Feature Description        | 8          |

| 3 | 说明 1                                         |    | 7.4 Device Functional Modes    | 10         |

| 4 | 修订历史记录 2                                     | 8  | Application and Implementation |            |

| 5 | Pin Configuration and Functions3             |    | 8.1 Application Information    |            |

| 6 | Specifications4                              |    | 8.2 Typical Application        | <u>1</u> 1 |

| Ü | 6.1 Absolute Maximum Ratings                 | 9  | Power Supply Recommendations   | 13         |

|   | 6.2 ESD Ratings                              | 10 | Layout                         | 13         |

|   | 6.3 Recommended Operating Ratings 4          |    | 10.1 Layout Guidelines         |            |

|   | 6.4 Thermal Information4                     |    | 10.2 Layout Example            | 13         |

|   | 6.5 Electrical Characteristics5              | 11 | 器件和文档支持                        | 14         |

|   | 6.6 Timing Requirements TCAL, MOS_DRV, DONE, |    | 11.1 商标                        | 14         |

|   | PGOOD6                                       |    | 11.2 静电放电警告                    | 14         |

|   | 6.7 Typical Characteristics                  |    | 11.3 术语表                       | 14         |

| 7 | Detailed Description 8                       | 12 | 机械封装和可订购信息                     |            |

|   | 7.1 Overview 8                               |    |                                |            |

# 4 修订历史记录

| Cł | hanges from Revision B (August 2013) to Revision C                                                                                                                                                                                                                                  | Page |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| •  | Added ESD Ratings table, Feature Description section, Device Functional Modes, Application and Implementation section, Power Supply Recommendations section, Layout section, Device and Documentation Support section, and Mechanical, Packaging, and Orderable Information section |      |

| •  | Removed T <sub>A</sub> value.                                                                                                                                                                                                                                                       | 4    |

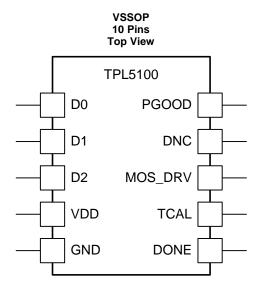

# **5 Pin Configuration and Functions**

# **Pin Functions**

| PIN     |     | 1/0 | DESCRIPTION                                                        | APPLICATION INFORMATION                                       |  |

|---------|-----|-----|--------------------------------------------------------------------|---------------------------------------------------------------|--|

| NAME    | NO. | 1/0 | DESCRIPTION                                                        | APPLICATION INFORMATION                                       |  |

| D0      | 1   | I   | Logic Input to set period delay (t <sub>DP</sub> )                 | Connect to GND (low logic value) or to VDD (high logic value) |  |

| D1      | 2   | I   | Logic Input to set period delay (t <sub>DP</sub> )                 | Connect to GND (low logic value) or to VDD (high logic value) |  |

| D2      | 3   | I   | Logic Input to set period delay (t <sub>DP</sub> )                 | Connect to GND (low logic value) or to VDD (high logic value) |  |

| VDD     | 4   | Р   | Supply voltage                                                     |                                                               |  |

| GND     | 5   | G   | Ground                                                             |                                                               |  |

| DONE    | 6   | I   | Logic input for Watchdog functionality                             |                                                               |  |

| TCAL    | 7   | 0   | Short duration pulse output for estimation of TPL5100 timer delay. |                                                               |  |

| MOS_DRV | 8   | 0   | Drives external MOSFET to power cycle the remaining system.        |                                                               |  |

| DNC     | 9   | -   | Do Not Connect                                                     | Leave this pin floating                                       |  |

| PGOOD   | 10  | I   | Digital power good input                                           |                                                               |  |

# 6 Specifications

# 6.1 Absolute Maximum Ratings<sup>(1)(2)</sup>

|                                                     | MIN  | MAX     | UNIT |

|-----------------------------------------------------|------|---------|------|

| Supply Voltage (VDD-GND)                            | -0.3 | 6       | V    |

| Input voltage                                       | -0.3 | VDD+0.3 | V    |

| Voltage between any two pins (3)                    | -0.3 | VDD+0.3 | V    |

| Input Current on any pin                            | -5   | 5       | mA   |

| Junction Temperature, T <sub>J</sub> <sup>(4)</sup> |      | 150     | °C   |

| Storage temperature, T <sub>stg</sub>               | -65  | 150     | °C   |

- (1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- (2) All voltages referenced to ground unless otherwise noted.

- (3) When the input voltage (VIN) at any pin exceeds the power supply (VDD), the current on that pin must not exceed 5 mA and the voltage must also not exceed 6.0 V.

- (4) The maximum power dissipation is a function of TJ(MAX), ĵ,JA, and the ambient temperature, TA. The maximum allowable power dissipation at any ambient temperature is PDMAX = (TJ(MAX) TA)/ ĵ,JA. All numbers apply for packages soldered directly onto a PC board.

# 6.2 ESD Ratings

|                    |                         |                                                                                | VALUE | UNIT |

|--------------------|-------------------------|--------------------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)                         | ±2000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | V    |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- 2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Ratings

|                          | MIN | MAX | UNIT |

|--------------------------|-----|-----|------|

| Supply Voltage (VDD-GND) | 1.8 | 5.0 | V    |

| Temperature Range        | -40 | 105 | °C   |

### 6.4 Thermal Information

|                 |                                        | TPL5100 |      |

|-----------------|----------------------------------------|---------|------|

|                 | THERMAL METRIC <sup>(1)</sup>          | VSSOP   | UNIT |

|                 |                                        | 10 PINS |      |

| $R_{\theta JA}$ | Junction-to-ambient thermal resistance | 196.8   | °C/W |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

## 6.5 Electrical Characteristics(1)

Specifications are for  $T_A$  = $T_J$  = 25°C, VDD-GND=2.5 V, unless otherwise stated.

|                      | PARAMETER                                                         | TEST CONDITIONS                 | MIN <sup>(2)</sup> | TYP <sup>(3)</sup>                            | MAX <sup>(2)</sup> | UNIT   |

|----------------------|-------------------------------------------------------------------|---------------------------------|--------------------|-----------------------------------------------|--------------------|--------|

| POWER SUP            | PLY                                                               |                                 |                    |                                               |                    |        |

| IVDD                 | Supply current <sup>(4)</sup>                                     | PGOOD=VDD                       |                    | 30                                            | 50                 | nA     |

|                      |                                                                   | PGOOD=GND                       |                    | 12                                            |                    | nA     |

| TIMER                |                                                                   |                                 | 1                  |                                               |                    |        |

| t <sub>DP</sub>      | Timer Delay Period                                                |                                 |                    | 16, 32, 64,<br>100, 128,<br>256, 512,<br>1024 |                    | s      |

|                      | Timer Delay Period drift over life time (5)                       |                                 |                    | 0.06 %                                        |                    |        |

|                      | Timer Delay Period drift over temperature                         |                                 |                    | 400                                           |                    | ppm/°C |

| t <sub>CAL</sub>     | Calibration pulse width                                           |                                 | 14.063             | 15.625                                        | 17.188             | ms     |

|                      | t <sub>DP</sub> to t <sub>CAL</sub> matching error <sup>(6)</sup> | VDD<=3.0 V                      |                    |                                               | 0.1%               |        |

| t <sub>DONE</sub>    | DONE Pulse width (6)                                              |                                 | 100                |                                               |                    | ns     |

| t <sub>MOS_DRV</sub> | MOS_DRV Pulse width                                               |                                 |                    | 31.25                                         |                    | ms     |

| DIGITAL LOG          | GIC LEVELS                                                        |                                 | ·                  |                                               |                    | •      |

| VIH                  | Logic High Threshold                                              | PGOOD, DONE                     | 0.7xVDD            |                                               |                    | V      |

| VIL                  | Logic Low Threshold                                               | PGOOD, DONE                     |                    |                                               | 0.3xVDD            | V      |

| VOL                  | La sia autout Hisb Laval                                          | MOS_DRV, TCAL<br>lout = 100 uA  | VDD-0.3            |                                               |                    | V      |

| VOH                  | Logic output High Level                                           | MOS_DRV, TCAL<br>lout = 1 mA    | VDD-0.7            |                                               |                    | V      |

| VOI                  | Large control Land                                                | MOS_DRV, TCAL<br>lout = -100 uA |                    |                                               | 0.3                | ٧      |

| VOL                  | Logic output Low Level                                            | MOS_DRV, TCAL<br>lout = -1 mA   |                    |                                               | 0.7                | ٧      |

<sup>(1)</sup> Electrical Characteristics table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions

result in very limited self-heating of the device such that  $T_J = T_A$ . Limits are specified by testing, design, or statistical analysis at 25°C. Limits over the operating temperature range are specified through correlations using statistical quality control (SQC) method.

<sup>(3)</sup> Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration. The typical values are not tested and are not ensured on shipped production material.

The supply current doesn't take in account load and pull-up resistor current. Input pins are at GND or VDD.

Operational life time test procedure equivalent to 10 years.

<sup>(6)</sup> Ensured by design.

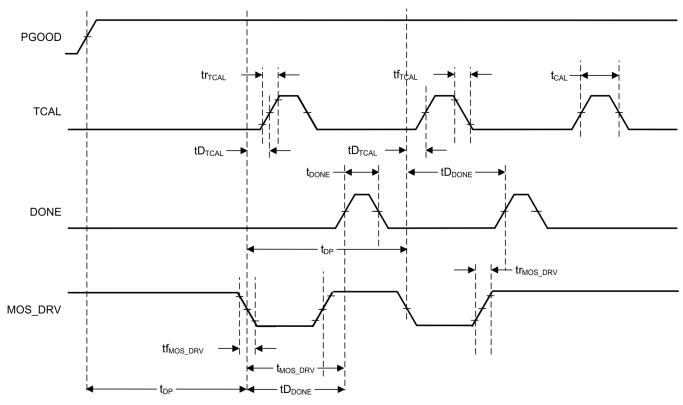

# 6.6 Timing Requirements TCAL, MOS\_DRV, DONE, PGOOD

|                       |                       |                      | MIN NO               | MAX | UNIT |

|-----------------------|-----------------------|----------------------|----------------------|-----|------|

| tr <sub>TCAL</sub>    | Rise Time TCAL        | Capacitve load 15 pF | 5                    | 0   | ns   |

| tf <sub>TCAL</sub>    | Fall Time TCAL        | Capacitve load 15 pF | 5                    | 0   | ns   |

| tr <sub>MOS_DRV</sub> | Rise Time MOS_DRV     | Capacitve load 50 pF |                      | 4   | ns   |

| tf <sub>MOS_DRV</sub> | Fall Time MOS_DRV     | Capacitve load 50 pF | 5                    | 0   | ns   |

|                       |                       | Min delay            | 10                   | 0   | ns   |

| tD <sub>DONE</sub>    | DONE to MOS_DRV delay | Max delay            | t <sub>DP</sub> -5 : |     | ms   |

| tD <sub>TCAL</sub>    | TCAL to MOS_DRV delay |                      | t <sub>CAL</sub> /   | 2   | ms   |

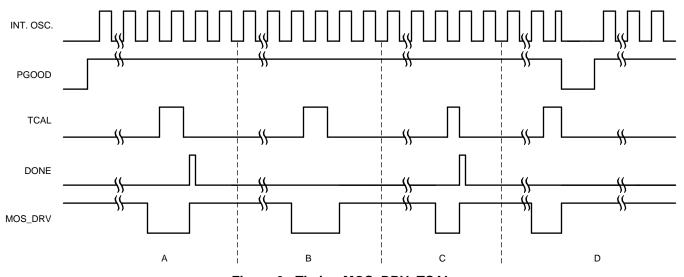

Figure 1. Timing Diagram

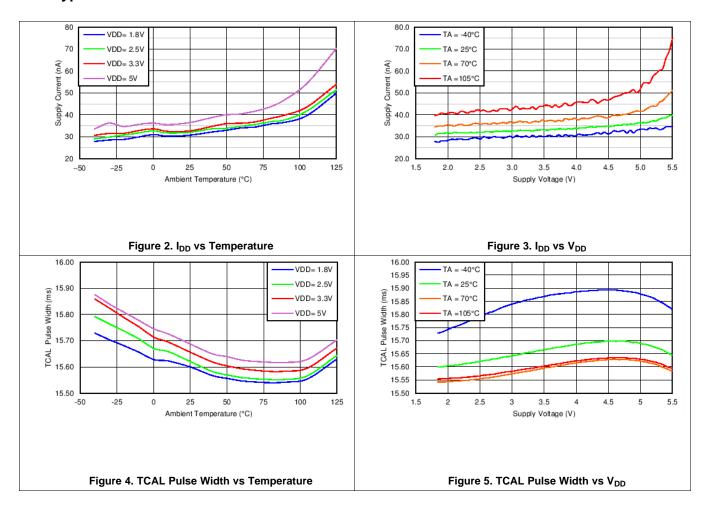

# 6.7 Typical Characteristics

# 7 Detailed Description

#### 7.1 Overview

The TPL5100 is a long-term timer for low-power applications. The TPL5100 is designed for use in power cycled applications and provides selectable timing from 16 s to 1024 s. An additional feature is interfacing which is achieved through the TPL5100 to a power-management IC.

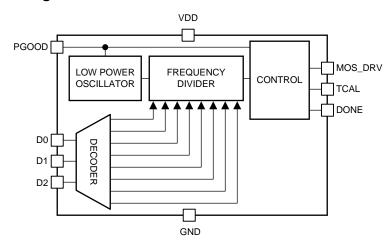

## 7.2 Functional Block Diagram

### 7.3 Feature Description

## 7.3.1 Supervisor Feature

A critical event that can corrupt the memory of a microcontroller is a voltage supply drop (supply lower than minimum operating range), and a reset of the microcontroller is mandatory if this occurs. Since the TPL5100 is the right choice in systems which stay most of the time in deep sleep or completely OFF, due to its ultra-low power consumption, it is fundamental that it takes into account the voltage drop events. The TPL5100 implements the supervisor feature when working with some power-management ICs, which indicate the status of the supply voltage with a power-good or battery-good output. The supervisory functionality is enabled by simply connecting the Battery management power-good output to the TPL5100 PGOOD pin. If this feature is not used connect the PGOOD pin to VDD.

In case the power-management IC detects a voltage drop while the microcontroller is OFF, consequently lowering the PGOOD line, the TPL5100 resets its internal counter and does not allow the micro to turn ON until the PGOOD is high again. This series of events allows the microcontroller to avoid working in an unsafe voltage supply condition. If the PGOOD signal is lowered while the microcontroller is ON, the TPL51000 turns the microcontroller OFF. The micro will be turned ON when PGOOD is high again and the selected delay is elapsed.

### 7.3.2 Calibration Pulse

The TPL5100 is based on an ultra-low power oscillator, which has a relatively low frequency and low accuracy; however, it shows very good cycle-to-cycle repeatability and very low temperature drift. In most of the applications, the accuracy of the oscillator is enough, but if a more accurate measure of the delay period is required, it is possible to measure the base period of the internal oscillator. A single pulse, which has the same duration as the base period of the internal oscillator, is present at the TCAL pin of the TPL5100. This pulse starts after a half period of the internal oscillator, from the falling edge of the MOS\_DRV pulse.

A microcontroller-connected to the TPL5100 can routinely measure the width of the TCAL pulse, using a counter and an external crystal. Once the base period of the TPL5100 is measured, the actual time delay is calculated by multiplying the measured period by a factor, N (see Table 1), dependent upon the nominal selected time delay.

The resolution and the accuracy of the measurement depend upon the external crystal. Since the frequency of the internal oscillator of the TPL5100 is very stable, the measurement of the calibration pulse is suggested only when a high gradient of ambient temperature is observed. The measurement of the TCAL pulse is useful in battery-powered applications that implement a precise battery life counter in the microcontroller.

### **Feature Description (continued)**

### 7.3.2.1 Overview of the Timing Signals MOS\_DRV, TCAL, and DONE

Figure 6 shows the timing of PGOOD, MOS\_DRV, and TCAL with respect to DONE. The frame, A, shows a typical sequence after the PGOOD, low to high, transition. As soon as PGOOD is high, the internal oscillator is powered ON. At the end of the delay period (t<sub>DP</sub>), a MOS enable signal (MOS\_DRV), followed by a calibration pulse, TCAL, is sent out. The calibration pulse starts after a half period of the internal oscillator from the falling edge of the MOS\_DRV signal, and lasts one internal oscillator period. A "DONE" signal is received before the end of the MOS\_DRV pulse. As soon as the TPL5100 receives the DONE signal, the counter resets and MOS\_DRV and TCAL return to default conditions (MOS\_DRV signal high and TCAL signal low).

The frame, B, shows a non-standard sequence. A "DONE" signal has not been received before the end of the MOS\_DRV pulse. The MOS\_DRV signal stays low for 2 internal oscillator periods. The calibration pulse starts after a half period of the internal oscillator from the falling edge of the MOS\_DRV signal, and lasts one internal oscillator period. The external power gating MOS stays ON for 2 internal oscillator periods.

The frame, C, shows a standard sequence, but in this case, the TPL5100 receives the DONE signal when MOS\_DRV is high and TCAL pulse is still high. As soon as the TPL5100 recognizes the DONE signal, the counter resets and MOS\_DRV and TCAL return to default conditions (MOS\_DRV signal high and TCAL signal low). The external power-gating MOS stays ON for the execution time of the program of the connected microcontroller.

The frame, D, shows a typical PGOOD, high to low transition. As soon as PGOOD is low, the internal oscillator is powered OFF and the digital output pins, TCAL and MOS\_DRV, are asynchronously reset by the falling edge of the PGOOD signal, such that TCAL resets at low logical values, while MOS\_DRV resets at a high logical value. The external power gating MOS stays ON less than the execution time of the program of the connected microcontroller.

Figure 6. Timing MOS\_DRV, TCAL

# 7.3.3 Configuration and Interface

The time interval between 2 adjacent pulses is selectable through 3 digital input pins (D0, D1, D2) that can be strapped to either VDD (1) or GND (0). Eight possible time delays can be selected, as shown in Table 1.

**Table 1. Timer Delay Period**

| D2 | D1 | D0 | Time (s) | Factor N           |

|----|----|----|----------|--------------------|

| 0  | 0  | 0  | 16       | 2 <sup>10</sup>    |

| 0  | 0  | 1  | 32       | 2 <sup>11</sup>    |

| 0  | 1  | 0  | 64       | 2 <sup>12</sup>    |

| 0  | 1  | 1  | 100      | 100*2 <sup>6</sup> |

# **Feature Description (continued)**

# **Table 1. Timer Delay Period (continued)**

| D2 | D1 | D0 | Time (s) | Factor N        |

|----|----|----|----------|-----------------|

| 1  | 0  | 0  | 128      | 2 <sup>13</sup> |

| 1  | 0  | 1  | 256      | 2 <sup>14</sup> |

| 1  | 1  | 0  | 512      | 2 <sup>15</sup> |

| 1  | 1  | 1  | 1024     | 2 <sup>16</sup> |

# 7.4 Device Functional Modes

The TPL5100 is a long-term timer with a watchdog feature for low-power applications. The TPL5100 is designed for use in interrupt-driven applications and provides selectable timing from 1 s to 64 s. An additional supervisor feature is achieved through interfacing the TPL5100 to a power-management IC.

# 8 Application and Implementation

#### NOTE

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

### 8.1 Application Information

In battery powered applications the design of the system is driven by low-current consumption. The TPL5100 is suitable in the applications where there is the needs to monitor environment conditions in remote site at long fixed timer interval. Occasionally in these applications the micro is kept on to enable the watchdog and count the elapsed time. Often due to the high frequency clock of the microcontrollers, a special structure must be configured to count for several seconds. The TPL5100 can mimic the same job, by completely turning off the micro and sometimes the entire power channel; this results in burning only tens of nA.

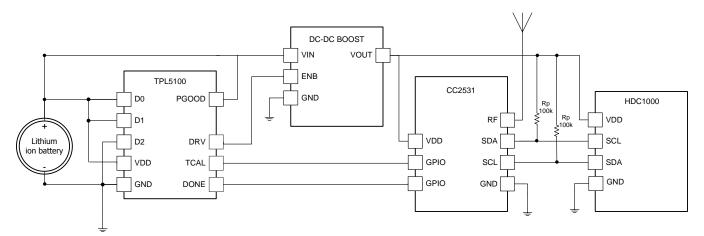

## 8.2 Typical Application

The TPL5100 can be used in environment sensor nodes such as humidity and temperature sensor node. The sensor node has to measure the humidity and the temperature and transmit the data through a low power RF micro such as the CC2530. Since the temperature and the humidity in home application do not change so fast, the measurement and the transmission of the data can be done at very low rate, such as every 30 seconds. The RF micro should spend most of the time in counting the elapsed time, but using the TPL5100 it is possible to complete turn off the RF micro and enlarge the battery life. The TPL5100 will turn on the RF micro when the programmed timer interval elapses.

Figure 7. Sensor Node

### 8.2.1 Design Requirements

The design is driven by the low current consumption constraint. The data are usually acquired at a rate between 30 s to 60 s. The highest necessity is the maximization of the battery life. The TPL5100 helps achieve this goal because it allows turning off the RF micro.

## 8.2.2 Detailed Design Procedure

When the focal constraint is the battery life, the selection of a low-power voltage regulator and low-leakage MOSFET to power gate the microcontroller is mandatory. The first step in the design is the calculation of the power consumption of each device in the different mode of operations. An example is the HDC1000, in measurement mode the RF micro is in normal operation and transmission. The different modes offer the possibility to select the appropriate timer interval which respect the application constraint and maximize the life of the battery.

# **Typical Application (continued)**

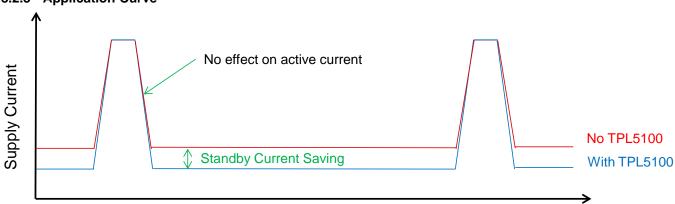

# 8.2.3 Application Curve

Time Figure 8. Effect of TPL5100 on Current Consumption

# 9 Power Supply Recommendations

The TPL5100 requires a voltage supply within 2.7 V and 5.5 V. A multilayer, ceramic-bypass X7R capacitor of 0.1µF between VDD and GND pin is recommended.

# 10 Layout

## 10.1 Layout Guidelines

The more sensitive pins of the TPL5100 are the digital input pins D0, D1, D2 to select the timer interval. It is mandatory to connect them to VDD or GND through short traces avoiding series resistance. Moreover, it is mandatory to keep these pins far from traces of high frequency signals, such as clock or communication bus. Signal integrity of DRV and TCAL signal is achieved reducing parasitic capacitance on the traces between the TPL5100 and the microcontroller.

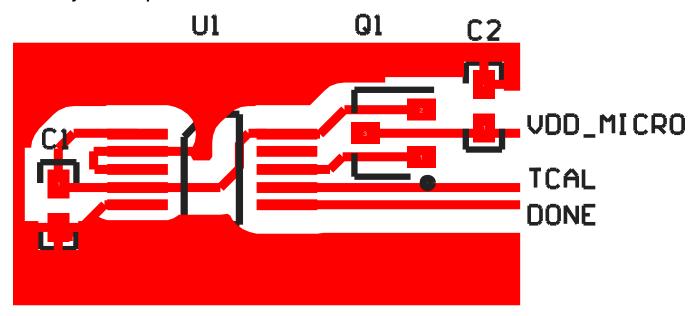

## 10.2 Layout Example

Figure 9. Board Layout

# 11 器件和文档支持

# 11.1 商标

All trademarks are the property of their respective owners.

# 11.2 静电放电警告

这些装置包含有限的内置 ESD 保护。 存储或装卸时,应将导线一起截短或将装置放置于导电泡棉中,以防止 MOS 门极遭受静电损伤。

# 11.3 术语表

SLYZ022 — TI 术语表。

这份术语表列出并解释术语、首字母缩略词和定义。

# 12 机械封装和可订购信息

以下页中包括机械封装和可订购信息。 这些信息是针对指定器件可提供的最新数据。 这些数据会在无通知且不对本文档进行修订的情况下发生改变。 欲获得该数据表的浏览器版本,请查阅左侧的导航栏。

# PACKAGE OPTION ADDENDUM

10-Dec-2020

#### PACKAGING INFORMATION

www.ti.com

| Orderable Device | Status | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp      | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|--------|--------------|--------------------|------|----------------|--------------|-------------------------------|--------------------|--------------|-------------------------|---------|

| TPL5100DGSR      | ACTIVE | VSSOP        | DGS                | 10   | 3500           | RoHS & Green | SN                            | Level-1-260C-UNLIM | -40 to 105   | ASAA                    | Samples |

| TPL5100DGST      | ACTIVE | VSSOP        | DGS                | 10   | 250            | RoHS & Green | SN                            | Level-1-260C-UNLIM | -40 to 105   | ASAA                    | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

10-Dec-2020

# **PACKAGE MATERIALS INFORMATION**

www.ti.com 10-Aug-2022

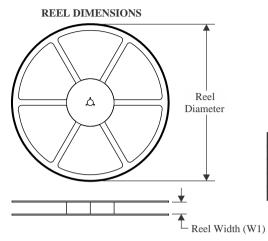

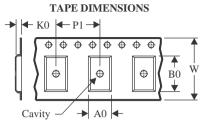

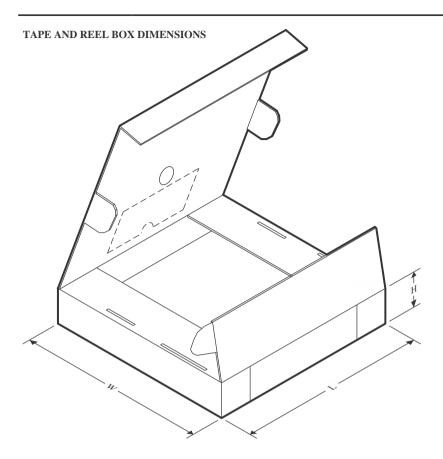

# TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

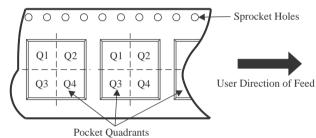

## QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPL5100DGSR | VSSOP           | DGS                | 10 | 3500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| TPL5100DGST | VSSOP           | DGS                | 10 | 250  | 178.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

www.ti.com 10-Aug-2022

## \*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPL5100DGSR | VSSOP        | DGS             | 10   | 3500 | 367.0       | 367.0      | 35.0        |

| TPL5100DGST | VSSOP        | DGS             | 10   | 250  | 208.0       | 191.0      | 35.0        |

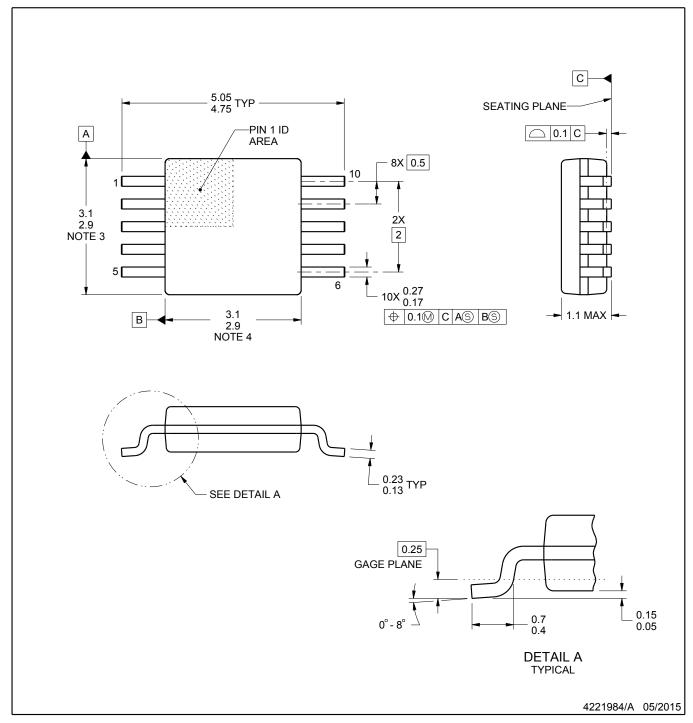

SMALL OUTLINE PACKAGE

### NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.

2. This drawing is subject to change without notice.

3. This dimension does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not

- exceed 0.15 mm per side.

- 4. This dimension does not include interlead flash. Interlead flash shall not exceed 0.25 mm per side.

- 5. Reference JEDEC registration MO-187, variation BA.

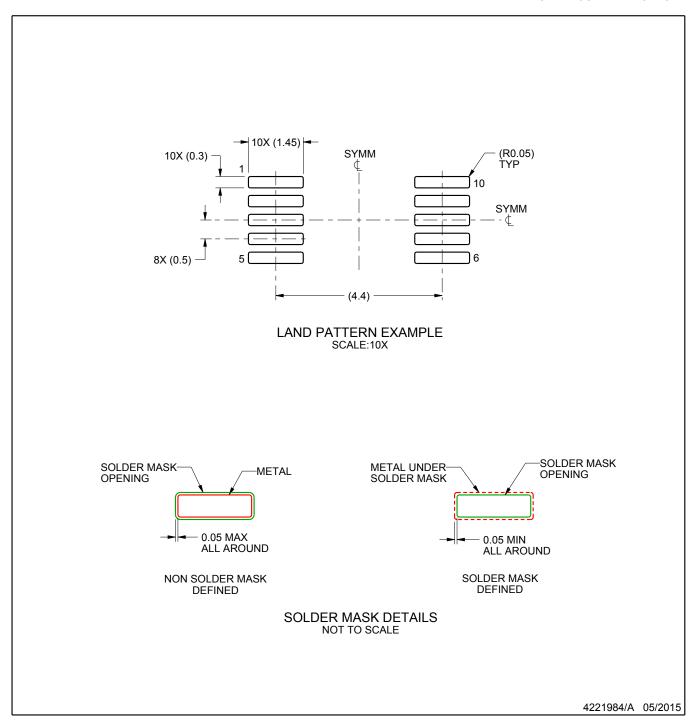

SMALL OUTLINE PACKAGE

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

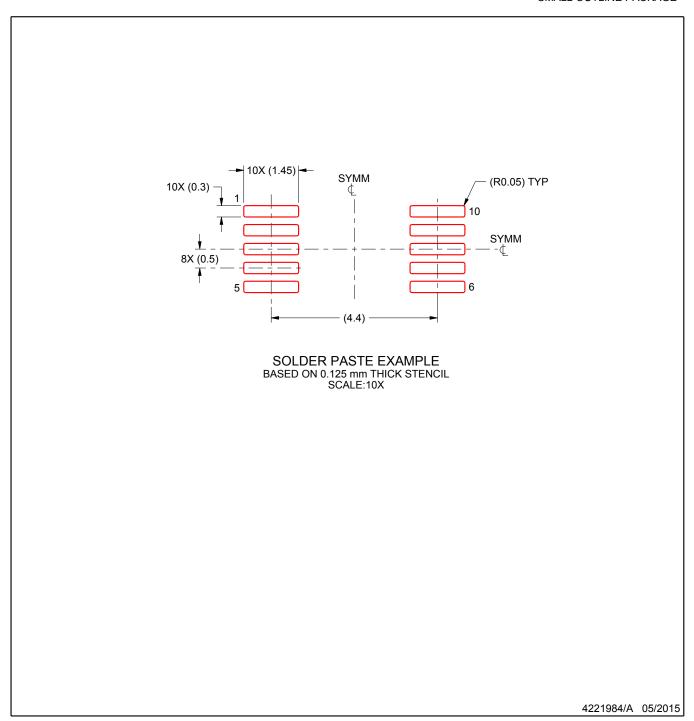

SMALL OUTLINE PACKAGE

NOTES: (continued)

- 8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

- 9. Board assembly site may have different recommendations for stencil design.

# 重要声明和免责声明

TI"按原样"提供技术和可靠性数据(包括数据表)、设计资源(包括参考设计)、应用或其他设计建议、网络工具、安全信息和其他资源,不保证没有瑕疵且不做出任何明示或暗示的担保,包括但不限于对适销性、某特定用途方面的适用性或不侵犯任何第三方知识产权的暗示担保。

这些资源可供使用 TI 产品进行设计的熟练开发人员使用。您将自行承担以下全部责任:(1) 针对您的应用选择合适的 TI 产品,(2) 设计、验证并测试您的应用,(3) 确保您的应用满足相应标准以及任何其他功能安全、信息安全、监管或其他要求。

这些资源如有变更,恕不另行通知。TI 授权您仅可将这些资源用于研发本资源所述的 TI 产品的应用。严禁对这些资源进行其他复制或展示。您无权使用任何其他 TI 知识产权或任何第三方知识产权。您应全额赔偿因在这些资源的使用中对 TI 及其代表造成的任何索赔、损害、成本、损失和债务,TI 对此概不负责。

TI 提供的产品受 TI 的销售条款或 ti.com 上其他适用条款/TI 产品随附的其他适用条款的约束。TI 提供这些资源并不会扩展或以其他方式更改 TI 针对 TI 产品发布的适用的担保或担保免责声明。

TI 反对并拒绝您可能提出的任何其他或不同的条款。

邮寄地址:Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022,德州仪器 (TI) 公司