SN65HVD61

SLLS770D - JANUARY 2007 - REVISED JUNE 2011

# ControlNet<sup>™</sup> TRANSCEIVER

Check for Samples: SN65HVD61

## **FEATURES**

- Compatible With the ControlNet Standard

- I/O Operates From 2.5-V to 5-V Supply

- Receiver thresholds within –120mV to 120mV

- Receiver hysteresis >50mV

- Low Power Standby Mode

- Thermal Shutdown Protection

- Power-Up/Down Glitch-free Bus Inputs and Outputs

- Short-Circuit Protection on Outputs

- RoHS Compliant

- ControlNet Vendor ID 806

## DESCRIPTION

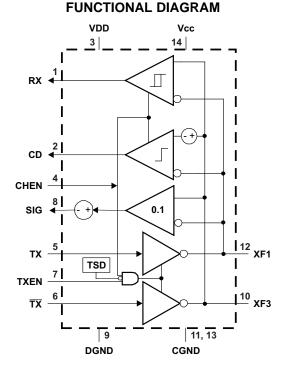

The SN65HVD61 is designed to meet the requirements for the driver and receiver circuitry of the ControlNet coaxial-based physical layer.

These devices are single-channel circuits with one transceiver for single node operation or distributed stand-alone applications.

The pull-or-pull transmitter circuit is designed to sink current from a center-tapped transformer, providing galvanic isolation from the shared bus.

These devices incorporate a differential receiver (RX) with the 120 mV sensitivity needed by ControlNet industrial applications.

A secondary receiver (CD) detects the presence of a valid positive differential signal.

The third signal receiver function (SIG) provides a scaled analog output which is proportional to the differential voltage between XF1 and XF3. This output can be used for diagnostic purposes.

# APPLICATIONS

- Industrial Networks

- Programmable Controllers

- Industrial Drives

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet. ControlNet is a trademark of ODVA.

# SN65HVD61

SLLS770D - JANUARY 2007 - REVISED JUNE 2011

www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### **ORDERING INFORMATION**

| PART NUMBER | PACKAGE <sup>(1)</sup> | MARKED AS |

|-------------|------------------------|-----------|

| SN65HVD61   | D                      |           |

|             | DR <sup>(2)</sup>      | - 65HVD61 |

For the most current package and ordering information, see the Package Option Addendum at the end (1)of this document, or see the TI website at www.ti.com.

(2)R suffix indicates tape and reel

#### ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

|                 |                                   |                                                                            |                     | VALUE | UNIT |  |  |

|-----------------|-----------------------------------|----------------------------------------------------------------------------|---------------------|-------|------|--|--|

| V <sub>CC</sub> | Supply voltage <sup>(2)</sup> (3) |                                                                            |                     |       |      |  |  |

| V <sub>DD</sub> | Supply voltage <sup>(4)</sup>     | Supply voltage <sup>(4)</sup>                                              |                     |       |      |  |  |

|                 | Logic input voltage range (TX,    | Logic input voltage range (TX, TXBAR, TXEN, CHEN)                          |                     |       |      |  |  |

|                 | Bus terminal voltage range (XF    | -22 to +22                                                                 | V                   |       |      |  |  |

|                 | Logic input current, (TX, TXBA    | ogic input current, (TX, TXBAR , TXEN, CHEN)                               |                     |       |      |  |  |

|                 | Bus terminal current (XF1, XF3    | Internally limited                                                         |                     |       |      |  |  |

|                 | Receiver output current (RX, C    | Receiver output current (RX, CD)                                           |                     |       |      |  |  |

|                 |                                   | Liveren Deck, Medel <sup>(4)</sup>                                         | Bus pins (XF1, XF3) | 16    | kV   |  |  |

|                 | Electro de la districtione        | Human Body Model <sup>(4)</sup>                                            | All other pins      | 4     | kV   |  |  |

|                 | Electrostatic discharge           | Charged Device Model <sup>(5)</sup>                                        | Allinian            | 1500  | V    |  |  |

|                 |                                   | Machine Model <sup>(6)</sup>                                               | All pins            | 200   | V    |  |  |

| TJ              | Junction temperature (see (7) t   | Junction temperature (see <sup>(7)</sup> below regarding thermal shutdown) |                     |       |      |  |  |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

DGND and CGND should be connected to a common ground plane external to the device. All voltage values, except differential I/O bus (2) voltages, are with respect to the ground plane

V<sub>CC</sub> and V<sub>DD</sub> lower limits are DC conditions, see application information regarding start-up transients. (3)

Tested in accordance JEDEC Standard 22, Test Method A114-A. (4)

(5)

Tested in accordance JEDEC Standard 22, Test Method C101. Tested in accordance JEDEC Standard 22, Test Method A115-A. (6)

(7)If the internal junction temperature exceeds 170°C, a thermal shutdown function will disable the transmitter.

#### **DISSIPATION RATINGS**

| CIRCUIT BOARD<br>MODEL <sup>(1)</sup> | RD $T_A \le 25^{\circ}C$ DERATING FACTOR <sup>(2)</sup><br>ABOVE $T_A = 25^{\circ}C$ |           | T <sub>A</sub> = 65°C | T <sub>A</sub> = 100°C |

|---------------------------------------|--------------------------------------------------------------------------------------|-----------|-----------------------|------------------------|

| Low-K                                 | 625 mW                                                                               | 5 mW/°C   | 425 mW                | 250 mW                 |

| High-K                                | 1180 mW                                                                              | 9.5 mW/°C | 800 mW                | 475 mW                 |

(1) Tested in accordance with the Low-K or High-K thermal metric definitions of EIA/JESD51-3 for leaded surface mount packages. For additional information about JEDEC thermal models, see Texas Instruments Application Note Thermal Characteristics of Logic and Linear Packages using JEDEC PCB Designs (SZZA017).

This is the inverse of the junction-to-ambient thermal resistance when board-mounted and with no air flow. (2)

## **RECOMMENDED OPERATING CONDITIONS**

|                 |                                            |                                                              | MIN     | NOM | MAX     | UNIT |

|-----------------|--------------------------------------------|--------------------------------------------------------------|---------|-----|---------|------|

| $V_{CC}$        | Analog supply voltage <sup>(1)</sup>       | 4.5                                                          | 5       | 5.5 | V       |      |

| $V_{DD}$        | Input/Output supply voltage <sup>(2)</sup> | Input/Output supply voltage <sup>(2)</sup>                   |         |     |         |      |

| VIH             | High-level logic input voltage             | TY TYPAD TYPAL CUPN                                          | 0.7×VDD |     | VDD     |      |

| V <sub>IL</sub> | Low-level logic input voltage              | TX, TXBAR, TXEN, CHEN                                        | 0       | (   | ).3×VDD | V    |

|                 | Bus pin common-mode voltage                | (VXF1 + VXF3 ) / 2                                           | 4.5     |     | 5.5     | V    |

|                 | Voltage at any bus terminal (XF1,          | XF3)                                                         | -10     |     | 15      | V    |

|                 | Transmitter peak output current (X         |                                                              | 130     | 150 | mA      |      |

| I <sub>OH</sub> | High-level logic output current            |                                                              | -8      |     |         | A    |

| I <sub>OL</sub> | Low-level logic output current             | RX, CD                                                       |         |     | 8       | mA   |

|                 | Output current                             | SIG                                                          | -1      |     | 1       | mA   |

| T <sub>A</sub>  |                                            | $4.75 \text{ V} \le \text{V}_{CC} \le 5.25 \text{ V}$        | -40     |     | 100     |      |

|                 | Operating free-air temperature             | $4.5 \text{ V} \leq \text{V}_{\text{CC}} \leq 5.5 \text{ V}$ | -30     |     | 100     | °C   |

| TJ              | Junction temperature                       |                                                              |         |     | 150     |      |

|                 | Signaling rate                             |                                                              |         | 10  |         | Mbps |

|                 | Relative humidity (non-condensing          |                                                              |         | 95% |         |      |

A power-shutdown feature keeps the device disabled when the voltage at V<sub>CC</sub> is below 2.1 V.

The I/O ring voltage for this device (V<sub>DD</sub>) should be the same as the power supply voltage for the controller with which it interfaces. In the case where the voltages are different, designers must consider the logic threshold compatibility between devices.

SLLS770D – JANUARY 2007 – REVISED JUNE 2011

www.ti.com

ISTRUMENTS

EXAS

## **ELECTRICAL CHARACTERISTICS**

over operating free-air temperature range (unless otherwise noted)

|                     | PARAMETER                                                 | TEST COND                                                             | ITIONS                                                       | MIN                 | TYP <sup>(1)</sup> | MAX                 | UNIT |

|---------------------|-----------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------|---------------------|--------------------|---------------------|------|

| BUS PINS            | S (XF1, XF3)                                              |                                                                       |                                                              |                     |                    |                     |      |

| V <sub>OL(TX)</sub> | Transmitter output low voltage                            | Connect to V <sub>CC</sub> through                                    |                                                              |                     | 0.9                | 1.2                 | V    |

| V <sub>OH(TX)</sub> | Transmitter output high voltage                           | 37.5 Ω, ±1% resistor                                                  | V <sub>CC</sub> -0.05                                        | V <sub>CC</sub>     |                    | v                   |      |

| V <sub>O(OFF)</sub> | Transmitter off noise level,<br> XF3-XF1                  | $R_L$ = 37.5 Ω, 0 to 20 MHz BW inputs idle, CHEN and TXEN             |                                                              |                     |                    | 5                   | mV   |

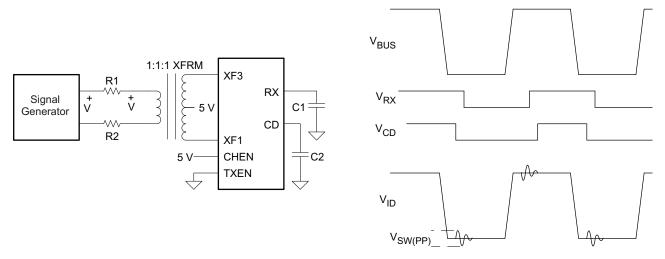

| V <sub>SW(PP)</sub> | Receiver-to-bus reflection, peak-to-peak                  | R1=R2=50 Ω, C1=C2=15pF,                                               | See Figure 3                                                 |                     |                    | 200                 | mV   |

| V <sub>TH+</sub>    | Positive-going differential input threshold voltage       | 4.5V < Vcm < 5.5V                                                     |                                                              |                     | 35                 | 120                 | mV   |

| V <sub>TH-</sub>    | Negative-going differential input threshold voltage       | 4.5V < Vcm < 5.5V                                                     |                                                              | -120                | -35                |                     | mV   |

| V <sub>hys</sub>    | Hysteresis voltage (V <sub>TH+</sub> – V <sub>TH-</sub> ) | 4.5V < Vcm < 5.5V, RX output                                          | t                                                            | 50                  | 70                 |                     | mV   |

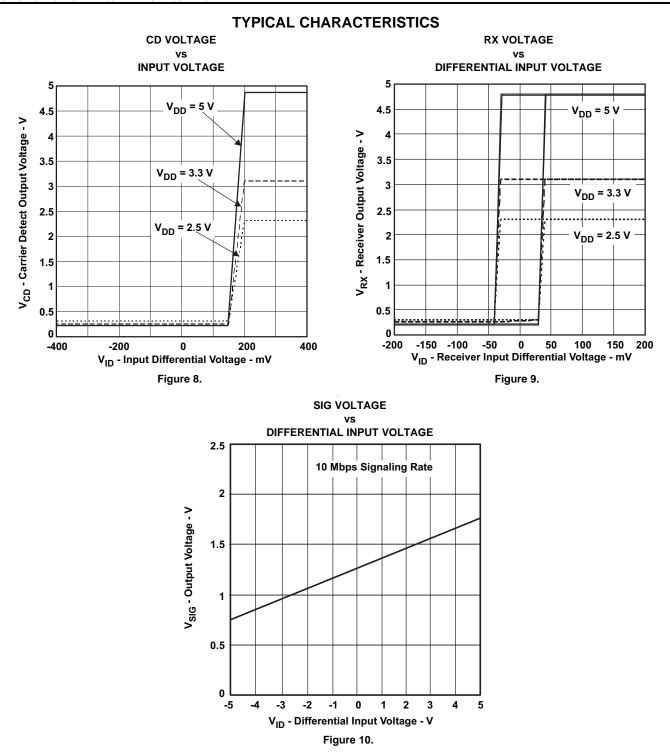

| V <sub>CD</sub>     | Carrier detect threshold voltage, (XF3-XF1)               | 4.5V < Vcm < 5.5V                                                     |                                                              | 23                  | 175                | 255                 | mV   |

|                     | Pus terminal input lookage surrent                        | V <sub>I</sub> = 10V, TXEN at 0V,<br>Other input at –10V to 10V       |                                                              |                     |                    | 1.2                 | mA   |

| I                   | Bus terminal input leakage current                        | $V_I = -10V$ , TXEN at 0V<br>Other input at -10V to 10V               |                                                              | -1.7                |                    |                     | ШA   |

| I <sub>I(off)</sub> | Bus terminal input leakage current                        | $V_{CC}$ < 2V, $V_{I}$ = -10V to 10V<br>Other input at -10 V to 10 V  | -1.7                                                         |                     | 1.2                | mA                  |      |

| l <sub>os</sub>     | Short-circuit output current                              | $0 < V_O < V_{CC}$                                                    | -400                                                         |                     | 400                | mA                  |      |

| R <sub>IN</sub>     | Bus terminal input resistance                             | $V_I = -10V$ to 10V, Other input                                      | at CGND, DC                                                  | 12                  |                    |                     | kΩ   |

| C <sub>IN</sub>     | Differential input capacitance (XF1-to-XF3)               | 10 MHz AC test frequency, 1 HP4194A or equivalent imped $V_{CC} = 0V$ |                                                              | 7                   | 11                 | pF                  |      |

| LOGIC IN            | PUTS (TX, TXBAR, TXEN,CHEN)                               |                                                                       |                                                              |                     |                    |                     |      |

| l <sub>l</sub>      | Logic input current                                       | TX, TXBAR, TXEN, CHEN                                                 |                                                              | -100                |                    | 100                 | μA   |

| I <sub>I(off)</sub> | Logic input power-off current                             | V <sub>DD</sub> at 0 V, TX,TXBAR, TXEN                                | I, CHEN                                                      |                     | -100               | 100                 | μA   |

| LOGIC OL            | UTPUTS (RX, CD)                                           | ·                                                                     |                                                              |                     |                    |                     |      |

| V                   | Logic output voltage, high lovel                          | C <sub>L</sub> = 15 pF                                                |                                                              | $0.8 \times V_{DD}$ |                    |                     | V    |

| V <sub>OH</sub>     | Logic output voltage, high level                          | $I_0 = -4 \text{ mA}, V_{DD} > 3V$                                    | = -4 mA, V <sub>DD</sub> > 3V                                |                     |                    |                     |      |

| V                   |                                                           | C <sub>L</sub> = 15 pF                                                |                                                              |                     |                    | $0.2 \times V_{DD}$ | V    |

| V <sub>OL</sub>     | Logic output voltage, low level                           | I <sub>O</sub> = 4 mA                                                 |                                                              |                     |                    | 0.4                 | v    |

| I <sub>OZ</sub>     | Logic output high-impedance-state current                 | RX, CD, 0 < V <sub>O</sub> < V <sub>DD</sub>                          |                                                              | -20                 |                    | 20                  | μA   |

| I <sub>O(off)</sub> | Logic output power-off current                            | V <sub>DD</sub> at 0 V, 0 < V <sub>O</sub> < 5.5V                     |                                                              | -1                  |                    | 1                   | mA   |

| SIGNAL S            | STRENGTH PIN (SIG)                                        |                                                                       |                                                              |                     |                    |                     |      |

| V <sub>SIG(0)</sub> | SIG output voltage with zero differential input voltage   | $R_L = 5 k\Omega$                                                     |                                                              | 1.125               | 1.25               | 1.375               | V    |

|                     |                                                           | V <sub>ID</sub> switching at 10 Mbps,                                 | $4.75 \text{V} \leq \text{V}_{\text{CC}} \leq 5.25 \text{V}$ |                     |                    | 120                 |      |

| GAIN                | SIG gain ΔV <sub>O</sub> /ΔV <sub>ID</sub>                | V <sub>O</sub> measured with 20 MHz bandwidth, See Figure 10          |                                                              |                     | 140                | mV/V                |      |

| POWER S             | SUPPLY PINS (V <sub>CC</sub> , CGND, VDD, DGND)           |                                                                       |                                                              |                     |                    |                     |      |

|                     | Analog supply current (dynamic)                           | CHEN and TXEN at logic high                                           | n, No load                                                   |                     | 36                 | 65                  |      |

| lcc                 | Analog supply current, chip disabled                      | CHEN at logic low                                                     |                                                              |                     | 1.8                | 3                   | mA   |

|                     | Analog supply current,<br>Lowest power conditions         | CHEN at DGND, TX and TXBAR at $V_{DD}$                                |                                                              |                     | 0.8                | 2                   |      |

|                     | I/O supply current, I/O, dynamic                          | CHEN at logic high, no load                                           |                                                              |                     |                    | 5                   | mA   |

| IDD                 | I/O supply current, I/O, chip disabled                    | CHEN at logic low                                                     |                                                              |                     |                    | 105                 | μA   |

(1) All typical values are at 25°C and with a 5 V supply. For typical values with a 3.3V supply, refer to the TYPICAL CHARACTERISTICS curves.

SN65HVD61

www.ti.com

## SLLS770D – JANUARY 2007 – REVISED JUNE 2011

# SWITCHING CHARACTERISTICS

over operating recommended operating conditions (unless otherwise noted)

|                                   | PARAMETER                                                                   | TEST CO                                                 | MIN                             | TYP | MAX | UNIT |       |

|-----------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------|-----|-----|------|-------|

| TRANS                             | <b>/</b> ITTER                                                              |                                                         |                                 |     |     |      |       |

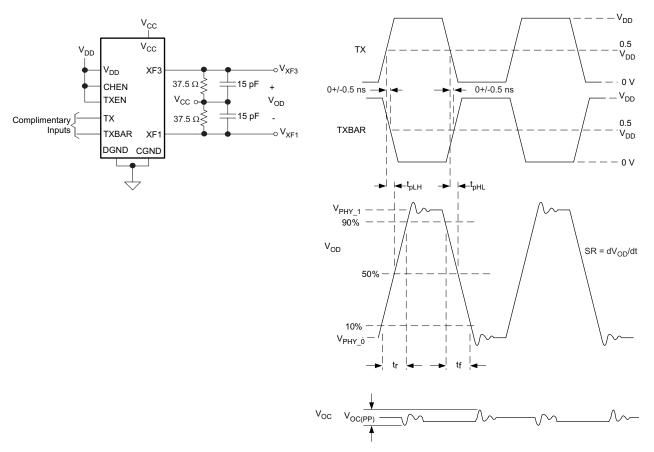

| t <sub>r</sub>                    | Output rise time (10%-to-90%) differential                                  |                                                         |                                 |     | 20  | 30   |       |

| t <sub>f</sub>                    | Output fall time (90%-to-10%) differential                                  |                                                         |                                 | 20  | 30  |      |       |

| t <sub>PLH</sub>                  | Propagation delay time, low-to-high-level differential output               | R <sub>L</sub> = 37.5 Ω, C <sub>L</sub> = 1             |                                 |     | 22  | 50   | ns    |

| t <sub>PHL</sub>                  | Propagation delay time, high-to-low-level differential output               | TXEN at logic high,                                     | See Figure 1 <sup>(1)</sup>     |     | 24  | 50   | 115   |

| t <sub>sk(p)</sub>                | Pulse skew, differential (XF3-XF1)<br>  t <sub>PLH</sub> - t <sub>PHL</sub> |                                                         |                                 | 2   | 5   |      |       |

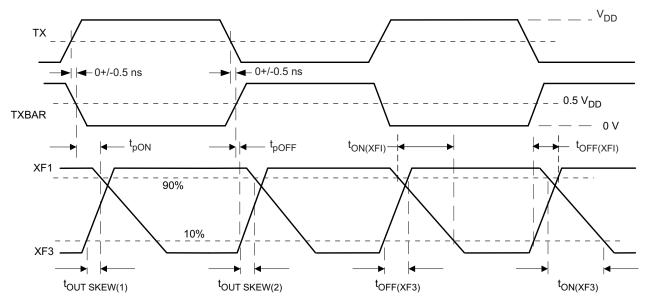

| t <sub>OUT</sub><br>SKEW          | Output delay skew, $t_{\text{pON}} - t_{\text{pOFF}},$ single-ended outputs | R <sub>L</sub> = 37.5 Ω, C <sub>L</sub> = 1             | 0                               | 7   | 12  | ns   |       |

| t <sub>ON</sub> -t <sub>OFF</sub> | Symmetry, turn-on-time-to-turn-off-time, 10%/90%, each single-ended output  | TXEN at logic high, See Figure 2                        |                                 | 0   | 9   | 12   | 115   |

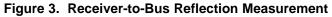

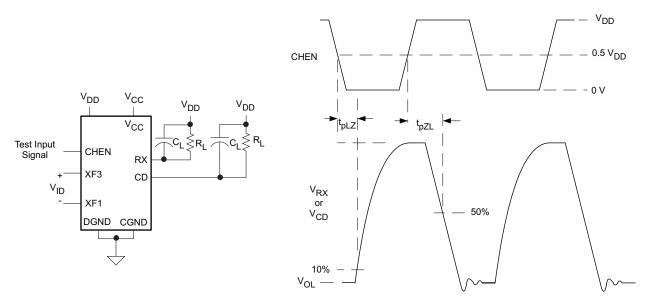

| t <sub>PZL</sub>                  | Propagation delay time, disabled-to-low-level output                        | R <sub>L</sub> = 37.5 Ω,<br>C <sub>L</sub> = 15 pF, See | TXEN changing,                  |     |     | 250  |       |

| t <sub>PLZ</sub>                  | Propagation delay time, low-level-to-disabled-output                        |                                                         | CHEN at VDD                     |     |     | 400  | ns    |

| t <sub>PZL</sub>                  | Propagation delay time, disabled-to-low-level output                        | _ Figure 4                                              | CHEN changing,                  |     |     | 400  | 115   |

| t <sub>PLZ</sub>                  | Propagation delay time, low-level-to-disabled-output                        |                                                         | TXEN at VDD                     |     |     | 400  |       |

| SR                                | Output differential slew rate                                               | See Figure 1                                            | 0°C < T < 85°C                  |     |     | 1    | V/ns  |

|                                   | Transmit jitter, differential                                               | 10 Mbps Mancheste                                       | er-code                         |     | 2.5 |      | ns    |

| RECEIV                            | ERS (RX and CD)                                                             |                                                         |                                 |     |     |      |       |

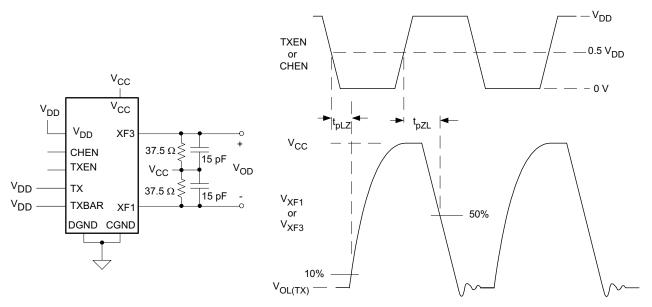

| t <sub>r</sub>                    | Output rise time (10%-to-90%)                                               |                                                         |                                 |     | 2   | 20   |       |

| t <sub>f</sub>                    | Output fall time (90%-to-10%)                                               | ) ( 10 F) (                                             |                                 |     | 2   | 20   |       |

| t <sub>PLH</sub>                  | Propagation delay time, low-to-high-level output                            | $V_{ID} = \pm 2.5V,$<br>$R_{L} = 1 k\Omega,$            |                                 |     | 25  | 40   |       |

| t <sub>PHL</sub>                  | Propagation delay time, high-to-low-level output                            | $C_{L} = 15 \text{ pF},$<br>See Figure 5                |                                 |     | 25  | 40   | ns    |

|                                   |                                                                             | See Figure 5                                            | RX                              |     | 0.2 | 4.5  |       |

| t <sub>sk(p)</sub>                | Pulse skew  t <sub>PLH</sub> – t <sub>PHL</sub>                             |                                                         | CD                              |     |     | 7    |       |

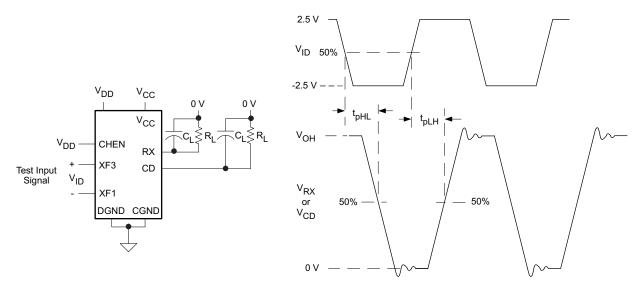

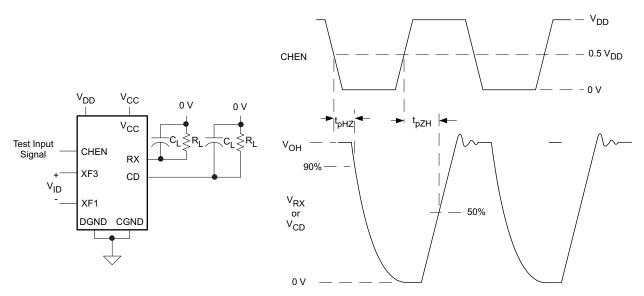

| t <sub>PZL</sub>                  | Propagation delay time, high-impedance-to-low-level output                  | $V_{ID} = -2.5V, R_L = 11$                              | $k\Omega, C_L = 15 \text{ pF},$ |     |     | 1000 |       |

| t <sub>PLZ</sub>                  | Propagation delay time, low-level-to-high-impedance output                  | See Figure 6                                            |                                 |     |     | 55   | ns    |

| t <sub>PZH</sub>                  | Propagation delay time, high-impedance-to-high-level output                 | $V_{ID} = 2.5V, R_L = 1ks$                              | Ω, C <sub>L</sub> = 15 pF,      |     |     | 1000 |       |

| t <sub>PHZ</sub>                  | Propagation delay time, high-level-to-high- impedance output                | See Figure 7                                            |                                 |     |     | 55   | 55 ns |

|                                   | Receive jitter                                                              | 10 Mbps Mancheste                                       | er-code                         |     | 0.5 |      |       |

(1) 30 ns maximum represents the worst-case allowable rise/fall time when connected to a transformer-coupler network.

SN65HVD61 SLLS770D – JANUARY 2007 – REVISED JUNE 2011

www.ti.com

Texas Instruments

#### PARAMETER MEASUREMENT INFORMATION

Figure 1. Transmitter Differential Switching Characteristics

Figure 2. Transmitter Single-Ended Switching Characteristics

PARAMETER MEASUREMENT INFORMATION (continued)

Figure 4. Transmitter Enable/Disable Test Circuits and Characteristics

TEXAS INSTRUMENTS

www.ti.com

Figure 5. Test Circuit and Signal Waveforms, Receiver and Carrier Detect

Figure 6. Test Circuit and Signal Waveforms, Receiver Enable and Disable With Low Bus Input

PARAMETER MEASUREMENT INFORMATION (continued)

Figure 7. Test Circuit and Signal Waveforms, Receiver Enable and Disable With High Bus Input

| TRANSMITTER |                  |                  |                  |                  |                  |  |  |  |  |

|-------------|------------------|------------------|------------------|------------------|------------------|--|--|--|--|

|             | INP              | UTS              |                  | OUTP             | UTS              |  |  |  |  |

| CHEN        | TXEN             | ТХ               | TXBAR            | XF1              | XF3              |  |  |  |  |

| L or OPEN   | Х                | Х                | Х                | Z                | Z                |  |  |  |  |

|             | L or OPEN        | Х                | Х                | Z                | Z                |  |  |  |  |

|             |                  | L or OPEN        | L or OPEN        | Z                | Z                |  |  |  |  |

| Н           | н                | L or OPEN        | Н                | Z                | L                |  |  |  |  |

|             |                  | Н                | L or OPEN        | L                | Z                |  |  |  |  |

|             | H <sup>(1)</sup> | H <sup>(1)</sup> | H <sup>(1)</sup> | L <sup>(1)</sup> | L <sup>(1)</sup> |  |  |  |  |

#### Table 1. FUNCTION TABLES

(1) This combination is not supported and should be avoided in ControlNet applications

| RECEIVER  |                                           |                 |    |  |  |  |  |  |  |

|-----------|-------------------------------------------|-----------------|----|--|--|--|--|--|--|

|           | INPUTS                                    |                 |    |  |  |  |  |  |  |

| CHEN      | XF1, XF3                                  | CONDITION       | RX |  |  |  |  |  |  |

| L or OPEN | X                                         | Chip disabled   | Z  |  |  |  |  |  |  |

|           | $(V_{XF3} - V_{XF1}) < V_{TH-}$           | Negative signal | L  |  |  |  |  |  |  |

| н         | $V_{TH-} < (V_{XF3} - V_{XF1}) < V_{TH+}$ | No signal       | ?  |  |  |  |  |  |  |

|           | $V_{TH+} < (V_{XF3} - V_{XF1})$           | Positive signal | Н  |  |  |  |  |  |  |

| CARRIER DETECT |                                |                      |    |  |  |  |  |  |  |

|----------------|--------------------------------|----------------------|----|--|--|--|--|--|--|

|                | INPUTS                         |                      |    |  |  |  |  |  |  |

| CHEN           | XF1, XF3                       | CONDITION            | CD |  |  |  |  |  |  |

| L or OPEN      | Х                              | Chip disabled        | Z  |  |  |  |  |  |  |

|                | $(V_{XF3} - V_{XF1}) < V_{CD}$ | Carrier not detected | L  |  |  |  |  |  |  |

|                | $V_{CD} < (V_{XF3} - V_{XF1})$ | Carrier detected     | Н  |  |  |  |  |  |  |

www.ti.com

**ISTRUMENTS**

**EXAS**

#### **APPLICATION INFORMATION**

#### THERMAL SHUTDOWN

In most cases, the device's internal junction temperature will not reach the thermal shutdown temperature if operated within the recommended operating conditions. However, during fault conditions, such as driver short-circuit, the junction temperature may reach the thermal shutdown limit. This also depends on the thermal characteristics of the device mounting, the circuit board, and environmental factors. After the device reaches the thermal shutdown temperature, the driver outputs will be disabled, and the device will cool down. If the short-circuit is still present when the drivers are re-enabled, this *thermal shutdown cycle* will repeat until the short-circuit fault is removed.

For long-term reliability, the package power dissipation must not exceed the values in the data sheet POWER DISSIPATION RATINGS for extended periods.

#### **POWER-UP TRANSIENTS**

The absolute maximum ratings for Vcc and Vdd specify the limits for these supplies. During initial power-on, these supply voltages may instantaneously drop below the given lower limit. Designers should consider that diodes in the circuitry will begin to turn on if the voltage becomes too negative, and that damage may occur if these diodes dissipate significant power internal to the device. The actual threshold for possible damage is a function of both undervoltage magnitude and undervoltage transient duration. Further, the allowable undervoltage transient conditions depend on factors such as device junction temperature and power supply source impedance.

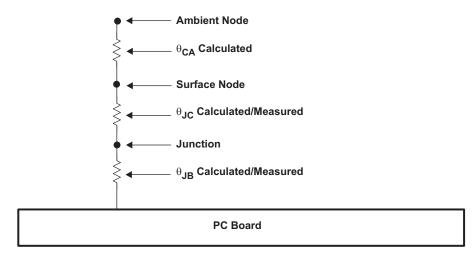

#### THERMAL CHARACTERISTICS OF IC PACKAGES

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ) is defined as the difference in junction temperature to ambient temperature divided by the operating power.  $\theta_{JA}$  is NOT a constant and is a strong function of

- the PCB design (50% variation)

- altitude (20% variation)

- device power (5% variation)

$\theta_{JA}$  can be used to compare the thermal performance of packages if the specific test conditions are defined and used. Standardized testing includes specification of PCB construction, test chamber volume, sensor locations, and the thermal characteristics of holding fixtures.  $\theta_{JA}$  is often misused when it is used to calculate junction temperatures for other installations.

TI uses two test PCBs as defined by JEDEC specifications. The low-k board gives average in-use condition thermal performance and consists of a single trace layer 25 mm long and 2-oz thick copper. The high-k board gives best case in-use condition and consists of 2 1-oz buried power planes with a single trace layer 25 mm long with 2-oz thick copper. A 4% to 50% difference in  $\theta_{JA}$  can be measured between these two test cards

Junction-to-case thermal resistance ( $\theta_{JC}$ ) is defined as difference in junction temperature to case divided by the operating power. It is measured by putting the mounted package up against a copper block cold plate to force heat to flow from die, through the mold compound into the copper block.

$\theta_{JC}$  is a useful thermal characteristic when a heatsink is applied to package. It is NOT a useful characteristic to predict junction temperature as it provides pessimistic numbers if the case temperature is measured in a non-standard system and junction temperatures are backed out. It can be used with  $\theta_{JB}$  in 1-dimensional thermal simulation of a package system.

Junction-to-board thermal resistance ( $\theta_{JB}$ ) is defined to be the difference in the junction temperature and the PCB temperature at the center of the package (closest to the die) when the PCB is clamped in a cold-plate structure.  $\theta_{JB}$  is only defined for the high-k test card.

SN65HVD61

SLLS770D – JANUARY 2007 – REVISED JUNE 2011

www.ti.com

STRUMENTS

XAS

$\theta_{JB}$  provides an overall thermal resistance between the die and the PCB. It includes a bit of the PCB thermal resistance (especially for BGA's with thermal balls) and can be used for simple 1-dimensional network analysis of package system.

|                 | JEDEC High-K Model | JEDEC Low-K Model |

|-----------------|--------------------|-------------------|

| θ <sub>JA</sub> | 105.7°C/W          | 199.5°C/W         |

| θ <sub>JB</sub> | 52.3               | 52.3              |

| θ <sub>JC</sub> | 56.32°C/W          | 56.32°C/W         |

Figure 11. Thermal Resistance

Additional information about thermal metrics for integrated circuits is available in the Texas Instruments Application Note *IC Package Thermal Metrics* (SPRA953).

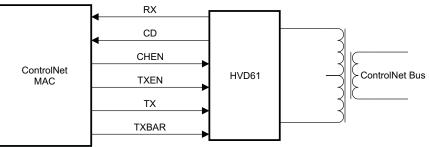

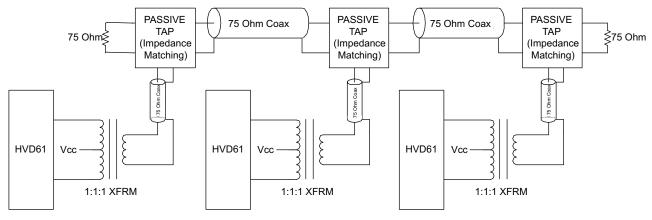

#### ControlNet APPLICATION

In a typical ControlNet application, several nodes will be connected to a common bus, as shown in Figure 12. At any time, only one node should actively drive the bus; all active nodes continually receive the bus state. The node which is actively driving the bus will sink current through either the XF1 or XF3 terminal, causing the voltage on the bus to be either differential high or differential low.

Figure 12. Typical ControlNet Application

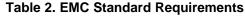

## SYSTEM-LEVEL EMC PROTECTION

The ControlNet network is intended to operate reliably in harsh industrial environments. At a system level, the network is tested according to several international electromagnetic compatibility (EMC) standards. The requirements are summarized in the Table 2 and Figure 13.

| EMC STANDARD  | DESCRIPTION OF TEST METHOD              | LEVEL                        |  |  |  |  |  |

|---------------|-----------------------------------------|------------------------------|--|--|--|--|--|

| IEC 61000-4-2 | Electro Static Discharge (ESD) Immunity | 6 kV Contact<br>8 kV Air-Gap |  |  |  |  |  |

| IEC 61000-4-3 | Radiated Radio Frequency (RF) Immunity  | 10V/m at 80 MHz to 2.7GHz    |  |  |  |  |  |

| IEC 61000-4-4 | Fast Transients / Burst Immunity        | 1 kV                         |  |  |  |  |  |

| IEC 61000-4-5 | Surge Immunity                          | 1 kV                         |  |  |  |  |  |

| IEC 61000-4-6 | Conducted Radio Frequency (RF) Immunity | 10V at 150 kHz to 80 MHz     |  |  |  |  |  |

Figure 13. Simplified Test Set-Up for EMC Standards

#### **DRIVER FUNCTIONS**

The ControlNet standard requires the transmitter to generate a signal with nominal amplitude of 8.2Vpp into a 37.5  $\Omega$  load. This applies to the double-terminated coax bus as shown in Figure 12. Rise and fall times should not exceed 30 nsec, and the signal slew rate should not exceed 1 V/nsec. Transmit signal distortion (ringing, droop, overshoot) should not exceed 10% of the peak-to-peak amplitude.

#### **RECEIVER FUNCTIONS**

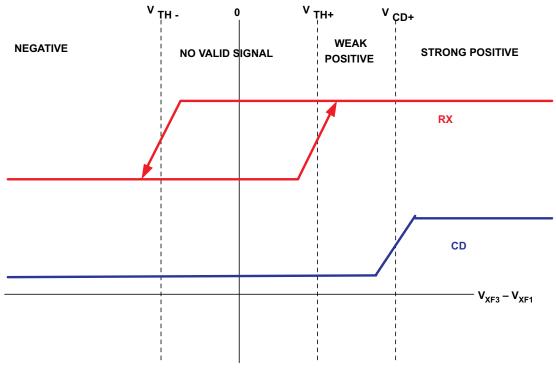

The function of the primary receiver (RX) and the carrier detect (CD) depends on the signals XF1 and XF3. The purpose of RX is to indicate the status of the two ControlNet bus lines, based on the signals XF1 and XF3. If the voltage at XF3 is greater than the voltage at XF1, then the bus state is positive, and RX should output a HIGH voltage. This corresponds to a Phy\_1 symbol. If the voltage at XF3 is less than the voltage at XF1, then the bus state is negative, and RX should output a LOW voltage. This corresponds to a Phy\_0 symbol. See Figure 14. Note that the allowable variation in  $V_{TH-}$ ,  $V_{TH+}$ , and  $V_{CD}$  is specified in the ELECTRICAL CHARACTERISTICS table.

Figure 14. RX and CD Functions

### SIGNAL STRENGTH OUTPUT

Vsig should be sampled at the beginning of a transmission in the preamble portion of the ControlNet Frame. This portion is the same for all nodes with the exception of the amplitude. Sampling Vsig in the preamble will provide the most consistent measurement. Further oversampling coupled with multiple frame sampling may provide further cable diagnostics such as identifying reflections due to cable breaks. By sampling multiple times in the preamble of a packet the distance to the break or short may be calculated.

Page

#### **REVISION HISTORY**

NOTE: Page numbers of current version may differ from previous versions.

# Changes from Revision C (May 2007) to Revision D Changed ControlNet is a trademark of ControlNet International, Ltd to ControlNet is a trademark of ODVA ...... 1 Changed Bus pin common-mode voltage MIN spec. from "4.75V to "4.5V" and MAX spec. from "5.25V to "5.5V" in Added second GAIN spec with conditions of $4.5V \le V_{CC} \le 5.5V$ in the ELEC CHARA TABLE, and added 140 mV/V

10-Dec-2020

# PACKAGING INFORMATION

| Orderable Device | Status<br>(1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan<br>(2) | Lead finish/<br>Ball material<br>(6) | MSL Peak Temp<br>(3) | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|---------------|--------------|--------------------|------|----------------|-----------------|--------------------------------------|----------------------|--------------|-------------------------|---------|

| SN65HVD61D       | ACTIVE        | SOIC         | D                  | 14   | 50             | RoHS & Green    | Call TI   NIPDAU                     | Level-1-260C-UNLIM   | -40 to 100   | 65HVD61                 | Samples |

| SN65HVD61DR      | ACTIVE        | SOIC         | D                  | 14   | 2500           | RoHS & Green    | NIPDAU                               | Level-1-260C-UNLIM   | -40 to 100   | 65HVD61                 | Samples |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

**RoHS Exempt:** TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead finish/Ball material - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# PACKAGE OPTION ADDENDUM

10-Dec-2020

Texas

STRUMENTS

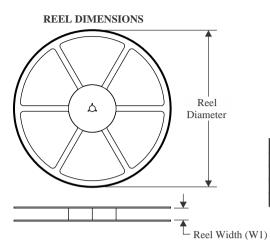

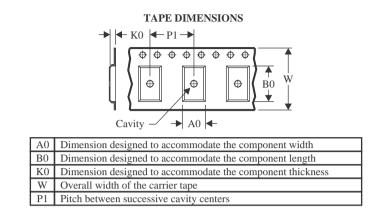

### TAPE AND REEL INFORMATION

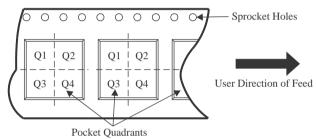

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All | dimensions a | are nominal |

|------|--------------|-------------|

|      |              |             |

| Device      | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| SN65HVD61DR | SOIC            | D                  | 14 | 2500 | 330.0                    | 16.4                     | 6.5        | 9.0        | 2.1        | 8.0        | 16.0      | Q1               |

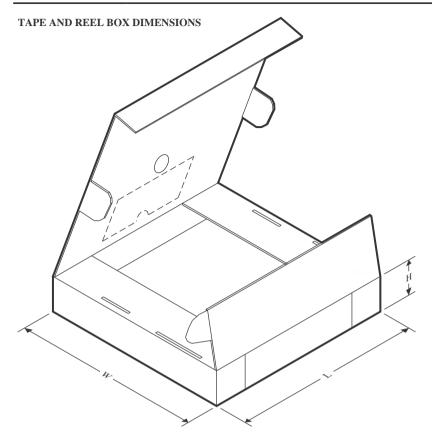

# PACKAGE MATERIALS INFORMATION

3-Jun-2022

\*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| SN65HVD61DR | SOIC         | D               | 14   | 2500 | 356.0       | 356.0      | 35.0        |

## TEXAS INSTRUMENTS

www.ti.com

3-Jun-2022

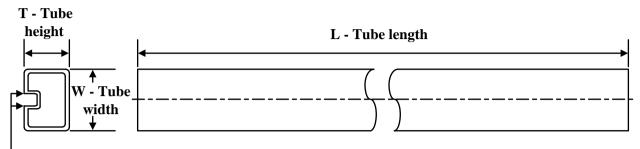

## TUBE

# - B - Alignment groove width

\*All dimensions are nominal

| Device     | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | Τ (μm) | B (mm) |

|------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| SN65HVD61D | D            | SOIC         | 14   | 50  | 506.6  | 8      | 3940   | 4.32   |

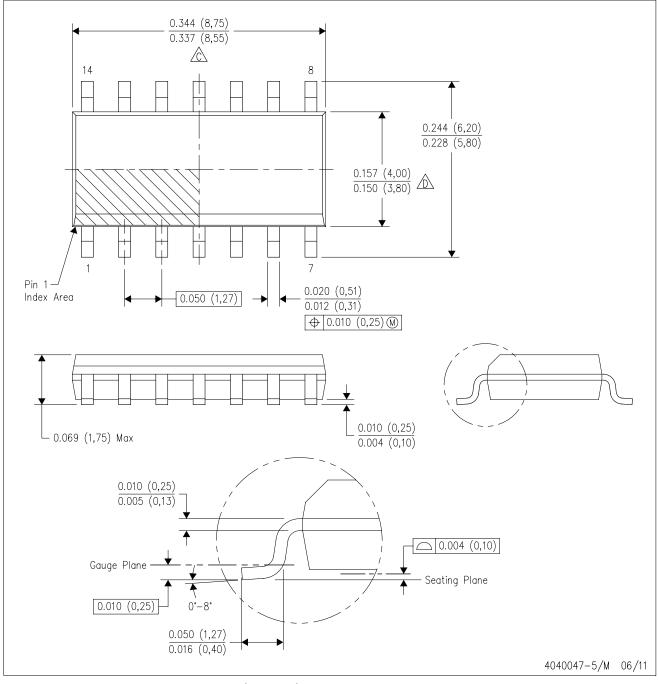

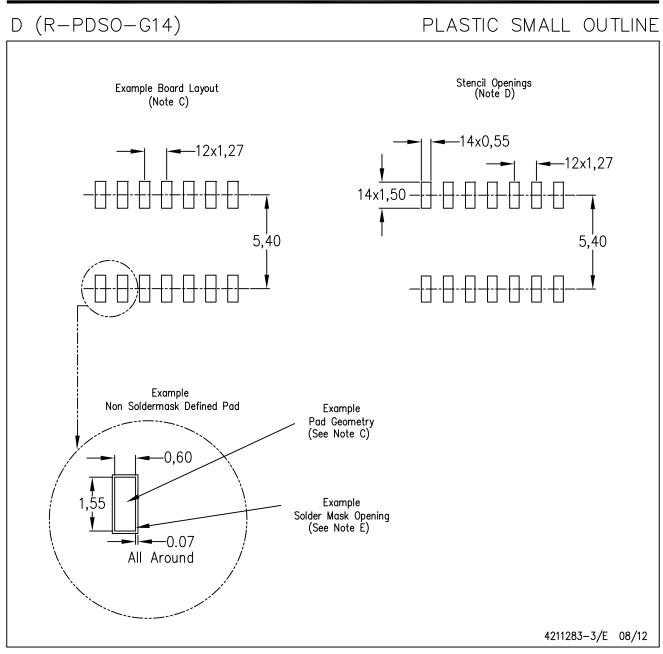

D (R-PDSO-G14)

PLASTIC SMALL OUTLINE

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.006 (0,15) each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.017 (0,43) each side.

- E. Reference JEDEC MS-012 variation AB.

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

## IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2022, Texas Instruments Incorporated