SLTS273E-SEPTEMBER 2006-REVISED JULY 2009

# 3-A, 2.2-V to 5.5-V INPUT, NON-ISOLATED, WIDE-OUTPUT, ADJUSTABLE POWER MODULE WITH *TurboTrans*™

#### **FEATURES**

- Up to 3-A Output Current

- 2.2-V to 5.5-V Input Voltage

- Wide-Output Voltage Adjust (0.69 V to 3.6 V)

- ±1.5% Total Output Voltage Variation

- Efficiencies up to 96%

- Output Overcurrent Protection (Nonlatching, Auto-Reset)

- Operating Temperature: –40°C to 85°C

- Safety Agency Approvals:

- UL60950, CSA 22.2 950, EN60950 VDE

- Prebias Startup

- On/Off Inhibit

- Differential Output Voltage Remote Sense

- Adjustable Undervoltage Lockout

- Auto-Track™ Sequencing

- Ceramic Capacitor Version (PTH04T261W)

- TurboTrans™ Technology

- Designed to meet Ultra-Fast Transient Requirements up to 300 A/μs

- SmartSync Technology

# **APPLICATIONS**

- Complex Multi-Voltage Systems

- Microprocessors

- Bus Drivers

#### **DESCRIPTION**

The PTH04T260/261W is a high-performance, 3-A rated, non-isolated power module. This regulator represents the 2nd generation of the PTH series of power modules which include a reduced footprint and improved features. The PTH04T261W is optimized to be used in applications requiring all ceramic capacitors.

Operating from an input voltage range of 2.2 V to 5.5 V, the PTH04T260/261W requires a single resistor to set the output voltage to any value over the range, 0.69 V to 3.6 V. The wide input voltage range makes the PTH04T260/261W particularly suitable for advanced computing and server applications that use a 2.5-V, 3.3-V or 5-V intermediate bus architecture.

The module incorporates a comprehensive list of features. Output over-current and over-temperature shutdown protects against most load faults. A differential remote sense ensures tight load regulation. An adjustable under-voltage lockout allows the turn-on voltage threshold to be customized. Auto-Track™ sequencing is a popular feature that greatly simplifies the simultaneous power-up and power-down of multiple modules in a power system.

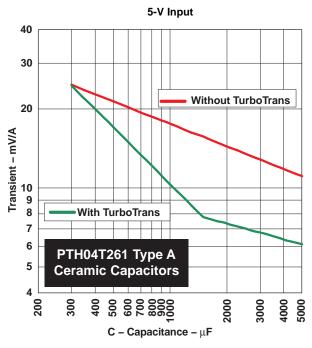

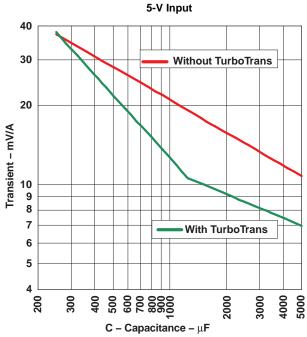

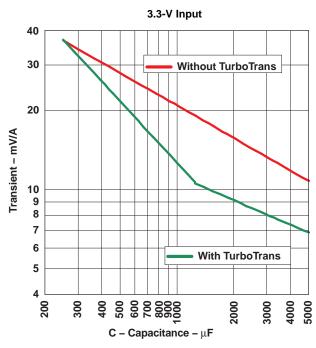

The PTH04T260/261W includes new patent pending technologies, **TurboTrans™** and **SmartSync**. The TurboTrans feature optimizes the transient response of the regulator while simultaneously reducing the quantity of external output capacitors required to meet a target voltage deviation specification. Additionally, for a target output capacitor bank, TurboTrans can be used to significantly improve the regulators transient response by reducing the peak voltage deviation. SmartSync allows for switching frequency synchronization of multiple modules, thus simplifying EMI noise suppression tasks and reduces input capacitor RMS current requirements. Double-sided surface mount construction provides a low profile and compact footprint. Package options include both through-hole and surface mount configurations that are lead (Pb) - free and RoHS compatible.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

TurboTrans, TMS320 are trademarks of Texas Instruments.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

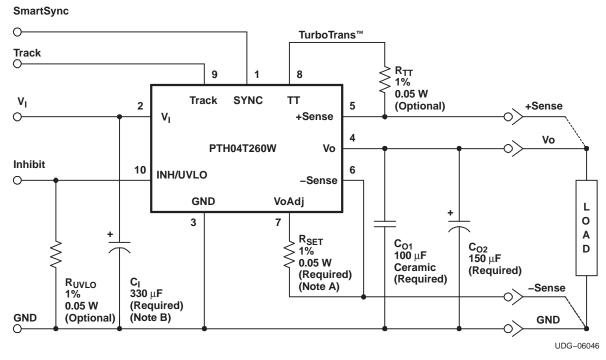

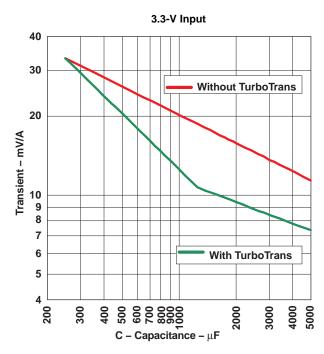

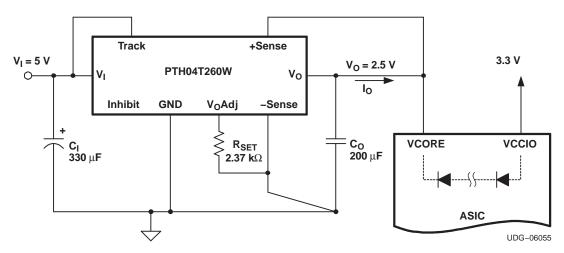

#### PTH04T260W

- A. R<sub>SET</sub> required to set the output voltage to a value higher than 0.69 V. See the *Electrical Characteristics* table.

- B. An additional 22-μF ceramic input capacitor is recommended to reduce RMS ripple current.

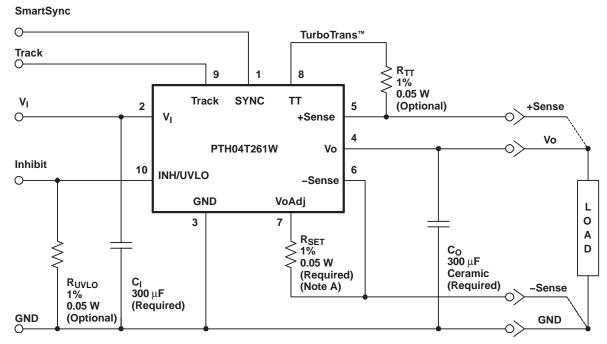

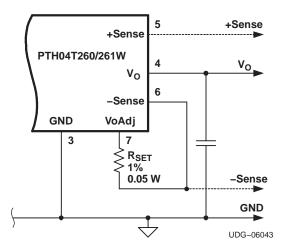

#### PTH04T261W - Ceramic Capacitor Version

- A. R<sub>SET</sub> required to set the output voltage to a value higher than 0.69 V. See the Electrical Characteristics table.

- B. 300 μF of ceramic or 330 μF of electrolytic input capacitance is required for proper operation.

SLTS273E-SEPTEMBER 2006-REVISED JULY 2009

#### ORDERING INFORMATION

For the most current package and ordering information, see the Package Option Addendum at the end of this data sheet, or see the TI website at www.ti.com.

# **DATASHEET TABLE OF CONTENTS**

| DATASHEET SECTION                               | PAGE NUMBER |

|-------------------------------------------------|-------------|

| ENVIRONMENTAL AND ABSOLUTE MAXIMUM RATINGS      | 3           |

| ELECTRICAL CHARACTERISTICS TABLE (PTH04T260W)   | 4           |

| ELECTRICAL CHARACTERISTICS TABLE (PTH04T261W)   | 6           |

| PIN-OUT AND TERMINAL FUNCTIONS                  | 8           |

| TYPICAL CHARACTERISTICS (V <sub>I</sub> = 5V)   | 9           |

| TYPICAL CHARACTERISTICS (V <sub>I</sub> = 3.3V) | 10          |

| ADJUSTING THE OUTPUT VOLTAGE                    | 11          |

| CAPACITOR RECOMMENDATIONS                       | 13          |

| TURBOTRANS™ INFORMATION                         | 17          |

| UNDERVOLTAGE LOCKOUT (UVLO)                     | 22          |

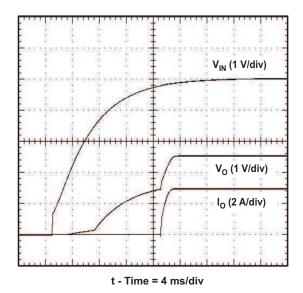

| SOFT-START POWER-UP                             | 23          |

| REMOTE SENSE                                    | 23          |

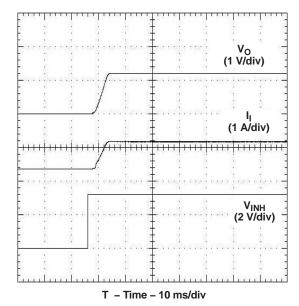

| OUTPUT ON/OFF INHIBIT                           | 24          |

| OVER-CURRENT PROTECTION                         | 24          |

| OVER-TEMPERATURE PROTECTION                     | 25          |

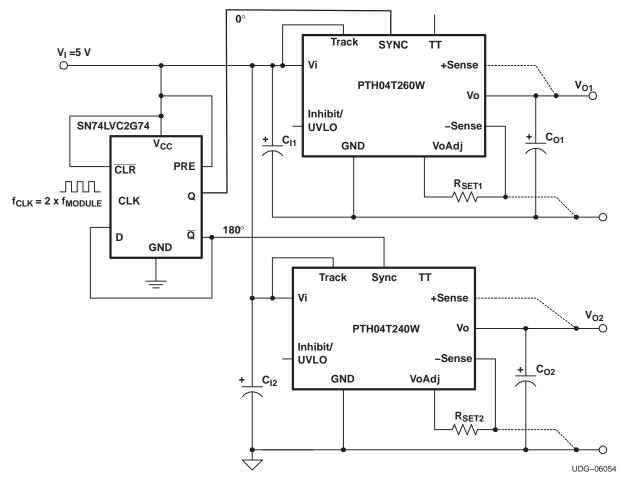

| SYCHRONIZATION (SMARTSYNC)                      | 25          |

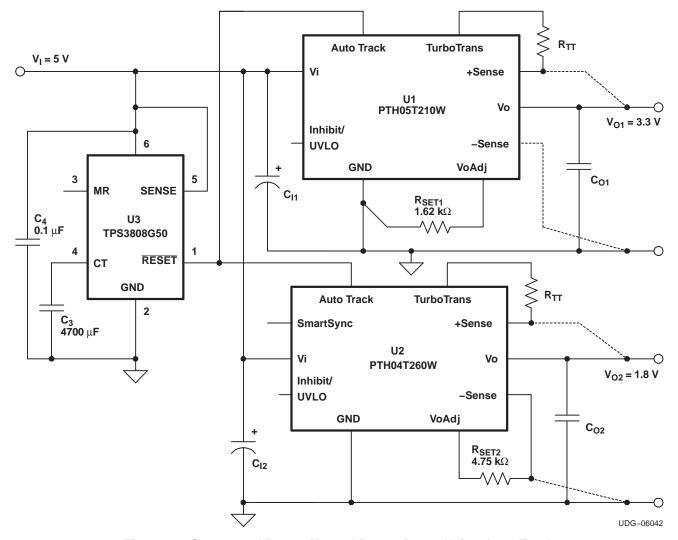

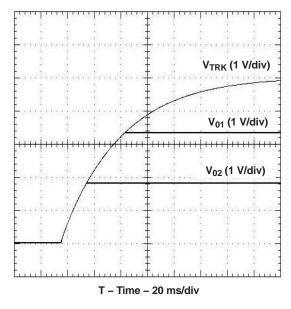

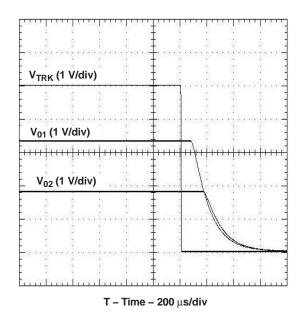

| AUTO-TRACK SEQUENCING                           | 26          |

| PREBIAS START-UP                                | 28          |

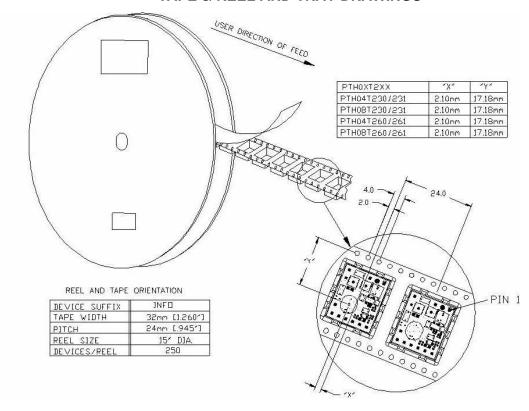

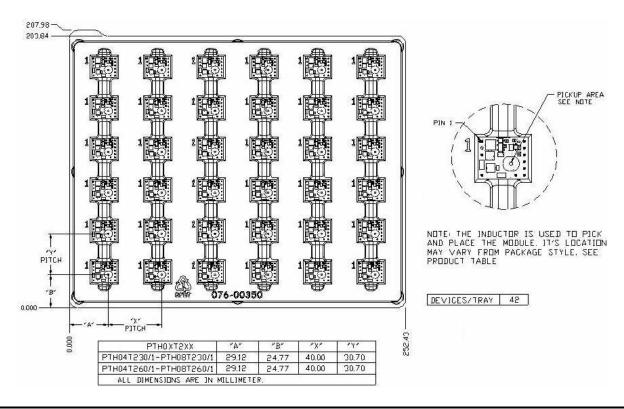

| TAPE & REEL AND TRAY DRAWINGS                   | 30          |

# **ENVIRONMENTAL AND ABSOLUTE MAXIMUM RATINGS**

(Voltages are with respect to GND)

|                     |                               |                                                                       |                  |                       | UNIT  |  |

|---------------------|-------------------------------|-----------------------------------------------------------------------|------------------|-----------------------|-------|--|

| $V_{Track}$         | Track pin voltage             |                                                                       |                  | $-0.3$ to $V_1 + 0.3$ | V     |  |

| T <sub>A</sub>      | Operating temperature range   | Over V <sub>I</sub> range                                             |                  | -40 to 85             |       |  |

| T <sub>wave</sub>   | Wave soldering temperature    | Surface temperature of module body or pins (5 seconds maximum)  AD su |                  | 260                   |       |  |

| _                   | Caldan naflace ta san anatoma | Conference terror entries of mondride body, or mine                   | AS suffix        | 235 <sup>(1)</sup>    | °C    |  |

| T <sub>reflow</sub> | Solder reflow temperature     | Surface temperature of module body or pins                            | AZ suffix        | 260 <sup>(1)</sup>    |       |  |

| T <sub>stg</sub>    | Storage temperature           | Storage temperature of module removed from sh                         | -55 to 125       |                       |       |  |

| T <sub>pkg</sub>    | Packaging temperature         | Shipping Tray or Tape and Reel storage or bake                        | temperature      | 45                    |       |  |

|                     | Machanical shook              | Per Mil-STD-883D, Method 2002.3 1 msec, 1/2                           | Suffix AD        | 500                   |       |  |

|                     | Mechanical shock              | sine, mounted                                                         | Suffix AS and AZ | 250                   | G     |  |

|                     | Machaniaal vibratiaa          | Mil CTD 000D Math at 0007 0 00 0000 H-                                | Suffix AD        | 20                    | G     |  |

|                     | Mechanical vibration          | Mil-STD-883D, Method 2007.2 20-2000 Hz                                | Suffix AS and AZ | 15                    |       |  |

|                     | Weight                        |                                                                       |                  | 2.7                   | grams |  |

|                     | Flammability                  | Meets UL94V-O                                                         |                  |                       |       |  |

<sup>(1)</sup> During reflow of surface mount package version do not elevate peak temperature of the module, pins or internal components above the stated maximum.

# **ELECTRICAL CHARACTERISTICS** PTH04T260W

$T_A$  =25°C,  $V_I$  = 5 V,  $V_O$  = 3.3 V,  $C_I$  = 330  $\mu$ F,  $C_O$ 1 = 100  $\mu$ F ceramic,  $C_O$ 2 = 150  $\mu$ F non-ceramic, and  $I_O$  =  $I_O$  max (unless otherwise stated)

|                         | PARAMETER                                 |                                                                                                                | TEST CONDITIONS                                                                             |                            | PTI                                | H04T260W        | ı                   | UNIT            |

|-------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------|------------------------------------|-----------------|---------------------|-----------------|

|                         |                                           |                                                                                                                |                                                                                             |                            | MIN                                | TYP             | MAX                 |                 |

| Io                      | Output current                            | Over V <sub>O</sub> range                                                                                      | 25°C,                                                                                       | natural convection         | 0                                  |                 | 3                   | Α               |

|                         |                                           | 0 1                                                                                                            | 1                                                                                           | $0.69 \le V_{O} \le 1.7$   | 2.2                                |                 | 5.5                 | .,              |

| VI                      | Input voltage range                       | Over I <sub>O</sub> range                                                                                      |                                                                                             | 1.7 < V <sub>O</sub> ≤ 3.6 | V <sub>O</sub> +0.5 <sup>(1)</sup> |                 | 5.5                 | V               |

|                         | Output adjust range                       | Over I <sub>O</sub> range                                                                                      |                                                                                             |                            | 0.69                               |                 | 3.6                 | V               |

|                         | Set-point voltage tolerance               |                                                                                                                |                                                                                             |                            |                                    | ±0.5            | ±1 <sup>(2)</sup>   | %V <sub>o</sub> |

| .,                      | Temperature variation                     | -40°C < T <sub>A</sub> < 85°C                                                                                  | -40°C < T <sub>A</sub> < 85°C                                                               |                            |                                    | ±0.3            |                     | %V <sub>o</sub> |

| Vo                      | Line regulation                           | Over V <sub>I</sub> range                                                                                      |                                                                                             |                            |                                    | ±2              |                     | mV              |

|                         | Load regulation                           | Over I <sub>O</sub> range                                                                                      |                                                                                             |                            |                                    | ±2              |                     | mV              |

|                         | Total output variation                    | Includes set-point, lin                                                                                        | e, load, –40°C ≤ T <sub>A</sub> ≤ 85°                                                       | С                          |                                    |                 | ±1.5 <sup>(3)</sup> | %Vo             |

|                         |                                           |                                                                                                                | $R_{SET} = 1.21 \text{ k}\Omega, V_{O} = 3.3 \text{ V}$                                     |                            |                                    | 95%             |                     |                 |

|                         |                                           |                                                                                                                | $R_{SET} = 2.38 \text{ k}\Omega, V_O = 2.5$                                                 | 5 V                        |                                    | 93%             |                     |                 |

|                         |                                           |                                                                                                                | $R_{SET} = 4.78 \text{ k}\Omega, V_{O} = 1.8$                                               | 3 V                        |                                    | 91%             |                     |                 |

| η                       | Efficiency                                | I <sub>O</sub> = 3 A                                                                                           | $R_{SET} = 7.09 \text{ k}\Omega, V_{O} = 1.5$                                               |                            | 90%                                |                 |                     |                 |

|                         |                                           |                                                                                                                | $R_{SET} = 12.1 \text{ k}\Omega, V_O = 1.2$                                                 |                            | 88%                                |                 |                     |                 |

|                         |                                           |                                                                                                                | $R_{SET} = 20.8 \text{ k}\Omega, V_{O} = 1.0$                                               | ) V                        |                                    | 87%             |                     |                 |

|                         |                                           |                                                                                                                | $R_{SET} = 689 \text{ k}\Omega, V_O = 0.7 \text{ V}$                                        |                            |                                    | 84%             |                     |                 |

|                         | V <sub>O</sub> Ripple (peak-to-peak)      | 20-MHz bandwidth                                                                                               |                                                                                             | 1                          |                                    | %V <sub>O</sub> |                     |                 |

| I <sub>LIM</sub>        | Overcurrent threshold                     | Reset, followed by au                                                                                          | to-recovery                                                                                 |                            |                                    | 6               |                     | Α               |

|                         |                                           |                                                                                                                | w/o TurboTrans                                                                              |                            |                                    | 100             |                     | μSec            |

|                         |                                           | 2.5 A/ $\mu$ s load step<br>50% to 100% l <sub>O</sub> max<br>V <sub>I</sub> = 3.3 V<br>V <sub>O</sub> = 2.5 V | $C_O 1$ = 100 $\mu$ F, ceramic $C_O 2$ = 150 $\mu$ F, non-ceramic                           | V <sub>O</sub> Overshoot   |                                    | 50              |                     | mV              |

|                         |                                           |                                                                                                                | w/o TurboTrans $^{(4)}$ C <sub>O</sub> 1 = 100 μF ceramic C <sub>O</sub> 2 = 990 μF, Type B | Recovery Time              |                                    | 120             |                     | μSec            |

|                         | Transient response                        |                                                                                                                |                                                                                             | V <sub>O</sub> Overshoot   |                                    | 30              |                     | mV              |

|                         |                                           |                                                                                                                | with TurboTrans                                                                             | Recovery Time              |                                    | 180             |                     | μSec            |

|                         |                                           |                                                                                                                | $C_{O}1 = 100 \ \mu F$ ceramic $C_{O}2 = 990 \ \mu F$ , Type B $R_{TT} = 1.54 \ k\Omega$    | V <sub>O</sub> Overshoot   |                                    | 18              |                     | mV              |

| I <sub>IL</sub>         | Track input current (pin 9)               | Pin to GND                                                                                                     |                                                                                             |                            |                                    |                 | -130 <sup>(5)</sup> | μΑ              |

| dV <sub>track</sub> /dt | Track slew rate capability                | $C_O \le C_O \text{ (max)}$                                                                                    |                                                                                             |                            |                                    |                 | 1                   | V/ms            |

|                         |                                           | V <sub>I</sub> increasing, R <sub>UVLO</sub> =                                                                 | = OPEN                                                                                      |                            |                                    | 1.95            | 2.19                |                 |

| $UVLO_{ADJ}$            | Adjustable Under-voltage lockout (pin 10) | V <sub>I</sub> decreasing, R <sub>UVLO</sub>                                                                   | = OPEN                                                                                      |                            | 1.3                                | 1.5             |                     | V               |

|                         | (F                                        | Hysteresis, R <sub>UVLO</sub> ≤ 52.3 kΩ                                                                        |                                                                                             |                            |                                    | 0.5             |                     |                 |

|                         |                                           | Input high voltage (VI                                                                                         |                                                                                             |                            | Open <sup>(6)</sup>                | V               |                     |                 |

|                         | Inhibit control (pin 10)                  | Input low voltage (V <sub>IL</sub>                                                                             | -0.2                                                                                        |                            | 0.6                                |                 |                     |                 |

|                         |                                           | Input low current (I <sub>IL</sub> ), Pin 10 to GND                                                            |                                                                                             |                            | 125                                |                 | μΑ                  |                 |

| I <sub>in</sub>         | Input standby current                     | Inhibit (pin 10) to GN                                                                                         | D, Track (pin 9) open                                                                       |                            |                                    | 5               |                     | mA              |

| fs                      | Switching frequency                       | Over V <sub>I</sub> and I <sub>O</sub> ranges                                                                  | s, SmartSync (pin 1) to GN                                                                  | ND                         |                                    | 300             |                     | kHz             |

| f <sub>SYNC</sub>       | Synchronization (SYNC) frequency          |                                                                                                                |                                                                                             |                            | 240                                |                 | 400                 | kHz             |

| V <sub>SYNCH</sub>      | SYNC High-Level Input Voltage             |                                                                                                                |                                                                                             |                            | 2                                  | ·               | 5.5                 | V               |

- (1) The minimum input voltage is 2.2 V or ( $V_O$  + 0.5) V, whichever is greater.

- (2) The set-point voltage tolerance is affected by the tolerance and stability of R<sub>SET</sub>. The stated limit is unconditionally met if R<sub>SET</sub> has a

- tolerance of 1% with 100 ppm/C or better temperature stability. The set-point voltage tolerance is affected by the tolerance and stability of  $R_{\text{SET}}$ . The stated limit is unconditionally met if  $R_{\text{SET}}$  has a tolerance of 1% with 200 ppm/C or better temperature stability.

- Without TurboTrans, the minimum ESR limit of 7 m $\Omega$  must not be violated.

- A low-leakage (<100 nA), open-drain device, such as MOSFET or voltage supervisor IC, is recommended to control pin 9. The open-circuit voltage is less than V<sub>I</sub>.

- This control pin has an internal pull-up. Do not place an external pull-up on this pin. If it is left open-circuit, the module operates when input power is applied. A small, low-leakage (<100 nA) MOSFET is recommended for control. The open-circuit voltage is less than 3.5Vdc. For additional information, see the related application information section.

# **ELECTRICAL CHARACTERISTICS (continued)** PTH04T260W

$T_A = 25^{\circ}C$ ,  $V_I = 5$  V,  $V_O = 3.3$  V,  $C_I = 330$   $\mu$ F,  $C_O = 100$   $\mu$ F ceramic,  $C_O = 150$   $\mu$ F non-ceramic, and  $I_O = I_O$  max (unless otherwise stated)

|                    | PARAMETER                    |                                                  | TEST CONDITIONS                           | PTH                                        | UNIT               |                     |       |

|--------------------|------------------------------|--------------------------------------------------|-------------------------------------------|--------------------------------------------|--------------------|---------------------|-------|

|                    |                              |                                                  |                                           |                                            | MIN                | TYP MAX             |       |

| V <sub>SYNCL</sub> | SYNC Low-Level Input Voltage |                                                  |                                           |                                            |                    | 0.8                 | V     |

| t <sub>SYNC</sub>  | SYNC Minimum Pulse Width     |                                                  |                                           |                                            | 200                |                     | ns    |

| Cı                 | External input capacitance   |                                                  |                                           |                                            | 330 (7)            |                     | μF    |

|                    |                              |                                                  | without Capacitance value                 | Nonceramic                                 | 150 <sup>(8)</sup> | 5000 <sup>(9)</sup> | μF    |

|                    |                              | without<br>TurboTrans                            |                                           | Ceramic                                    | 100 (8)            | 500                 |       |

| Co                 | External output capacitance  | raiboriano                                       | Equivalent series resista                 | Equivalent series resistance (non-ceramic) |                    |                     | mΩ    |

|                    | zwoma capat capatiano        | with                                             | Capacitance value                         | see table                                  | 5,000 (11)         | μF                  |       |

|                    |                              | Turbotrans                                       | Turbotrans  Capacitance × ESR product (Co |                                            | 1000               | 10,000              | μF×mΩ |

| MTBF               | Reliability                  | Per Telcordia SR<br>T <sub>A</sub> = 40°C, groun | -332, 50% stress,<br>d benign             | 5.6                                        |                    | 10 <sup>6</sup> Hr  |       |

- (7) A 330 µF input capacitor is required for proper operation. The capacitor must be rated for a minimum of 400 mA rms of ripple current. An additional 22-µF ceramic input capacitor is recommended to reduce rms ripple current.

- 100 µF ceramic and 150 F non-ceramic external output capacitance is required for basic operation. The minimum output capacitance

- requirement increases when *TurboTrans™* (TT) technology is used. See the Application Information for more guidance. This is the calculated maximum disregarding *TurboTrans™* technology. When the *TurboTrans* feature is used, the minimum output capacitance must be increased. See the *TurboTrans* application notes for further guidance.

- (10) When using TurboTrans™ technology, a minimum value of output capacitance is required for proper operation. Additionally, low ESR capacitors are required for proper operation. See the *TurboTrans* application notes for further guidance.

- (11) This is the calaculated maximum when using the TurboTrans feature. Additionally, low ESR capacitors are required for proper operation. See the *TurboTrans* application notes for further guidance.

Submit Documentation Feedback

#### **ELECTRICAL CHARACTERISTICS**

#### PTH04T261W (Ceramic Capacitors)

$T_A = 25$ °C,  $V_I = 5$  V,  $V_O = 3.3$  V,  $C_I = 300$   $\mu F$  ceramic,  $C_O = 300$   $\mu F$  ceramic, and  $I_O = I_O$  max (unless otherwise stated)

|                         | PARAMETER                            |                                             | TEST CONDITIONS                                                                                              |                                    | PTI  | H04T261\ | W                   | UNIT            |

|-------------------------|--------------------------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------|------|----------|---------------------|-----------------|

|                         |                                      |                                             |                                                                                                              | MIN                                | TYP  | MAX      |                     |                 |

| Io                      | Output current                       | Over V <sub>O</sub> range                   | 25°C, natural convection                                                                                     | l                                  | 0    |          | 3                   | Α               |

|                         | land to the management               | 0                                           |                                                                                                              | $0.69 \le V_{O} \le 1.7$           | 2.2  |          | 5.5                 | V               |

| $V_I$                   | Input voltage range                  | Over I <sub>O</sub> range                   |                                                                                                              | V <sub>O</sub> +0.5 <sup>(1)</sup> |      | 5.5      | V                   |                 |

| V <sub>OADJ</sub>       | Output voltage adjust range          | Over I <sub>O</sub> range                   |                                                                                                              | 0.69                               |      | 3.6      | V                   |                 |

|                         | Set-point voltage tolerance          |                                             |                                                                                                              |                                    |      | ±0.5     | ±1 <sup>(2)</sup>   | %V <sub>o</sub> |

|                         | Temperature variation                | $-40$ °C < $T_A$ < $85$ °C                  |                                                                                                              |                                    |      | ±0.3     |                     | %V <sub>o</sub> |

| $V_{O}$                 | Line regulation                      | Over V <sub>I</sub> range                   |                                                                                                              |                                    |      | ±2       |                     | mV              |

|                         | Load regulation                      | Over I <sub>O</sub> range                   |                                                                                                              |                                    |      | ±2       |                     | mV              |

|                         | Total output variation               | Includes set-point,                         | line, load, –40°C ≤ T <sub>A</sub> ≤ 8                                                                       | 5°C                                |      |          | ±1.5 <sup>(2)</sup> | %V <sub>o</sub> |

|                         |                                      |                                             | $R_{SET} = 1.21 \text{ k}\Omega, V_O = 3.3$                                                                  | 3 V                                |      | 95%      |                     |                 |

|                         |                                      |                                             | $R_{SET} = 2.38 \text{ k}\Omega, V_O = 2.5$                                                                  | 5 V                                |      | 93%      |                     |                 |

|                         |                                      |                                             | $R_{SET} = 4.78 \text{ k}\Omega, V_{O} = 1.8$                                                                | 3 V                                |      | 91%      |                     |                 |

| η                       | Efficiency                           | I <sub>O</sub> = 3 A                        | $R_{SET} = 7.09 \text{ k}\Omega, V_O = 1.5$                                                                  | 5 V                                |      | 90%      |                     |                 |

|                         |                                      |                                             | $R_{SET} = 12.1 \text{ k}\Omega, V_O = 1.3$                                                                  | 2 V                                |      | 88%      |                     |                 |

|                         |                                      |                                             | $R_{SET} = 20.8 \text{ k}\Omega, V_O = 1.0$                                                                  |                                    | 87%  |          |                     |                 |

|                         |                                      |                                             | $R_{SET} = 689 \text{ k}\Omega, V_{O} = 0.7 \text{ V}$                                                       |                                    |      | 84%      |                     |                 |

|                         | V <sub>O</sub> Ripple (peak-to-peak) | 20-MHz bandwidth                            |                                                                                                              | 1                                  |      | %Vo      |                     |                 |

| I <sub>LIM</sub>        | Overcurrent threshold                | Reset, followed by                          | auto-recovery                                                                                                |                                    |      | 6        |                     | Α               |

|                         |                                      |                                             | w/o TurboTrans                                                                                               | Recovery time                      |      | 100      |                     | μs              |

|                         |                                      |                                             | $C_O$ = 300 $\mu$ F, TypeA                                                                                   | V <sub>O</sub> over/undershoot     |      | 35       |                     | mV              |

|                         |                                      | 2.5 A/µs load step                          | X C <sub>O</sub> = 800 μF, TypeA<br>R <sub>TT</sub> = open<br>w/ TurboTrans<br>C <sub>O</sub> =800 μF, TypeA | Recovery time                      |      | 100      |                     | μs              |

|                         | Transient response                   | 50 to 100% $I_0$ max $V_1 = 3.3 \text{ V}$  |                                                                                                              | V <sub>O</sub> over/undershoot     |      | 28       |                     | mV              |

|                         |                                      | V <sub>O</sub> = 2.5 V                      |                                                                                                              | Recovery time                      |      | 150      |                     | μs              |

|                         |                                      |                                             |                                                                                                              |                                    |      | 18       |                     | mV              |

| _                       |                                      |                                             | $R_{TT} = 11.3 \text{ k}\Omega$                                                                              | V <sub>O</sub> over/undershoot     |      | 10       | (2)                 |                 |

| I <sub>IL</sub>         | Track input current (pin 9)          | Pin to GND                                  |                                                                                                              |                                    |      |          | -130 <sup>(3)</sup> | μA              |

| dV <sub>track</sub> /dt | Track slew rate capability           | $C_O \le C_O \text{ (max)}$                 |                                                                                                              |                                    |      |          | 1                   | V/ms            |

|                         | Adjustable Under-voltage lockout     | V <sub>I</sub> increasing, R <sub>UVL</sub> |                                                                                                              |                                    |      | 1.95     | 2.19                |                 |

| $UVLO_{ADJ}$            | (pin 10)                             | V <sub>i</sub> decreasing, R <sub>UVL</sub> |                                                                                                              |                                    | 1.3  | 1.5      |                     | V               |

|                         |                                      | Hysteresis, R <sub>UVLO</sub> =             |                                                                                                              |                                    |      | 0.5      | - (4)               |                 |

|                         |                                      | Input high voltage                          |                                                                                                              |                                    |      |          | Open <sup>(4)</sup> | V               |

|                         | Inhibit control (pin 10)             | Input low voltage                           |                                                                                                              |                                    | -0.2 |          | 8.0                 |                 |

|                         |                                      |                                             | (I <sub>IL</sub> ), Pin 10 to GND                                                                            |                                    |      | -235     |                     | μA              |

| I <sub>in</sub>         | Input standby current                |                                             | ND, Track (pin 9) open                                                                                       |                                    |      | 5        |                     | mA              |

| f <sub>s</sub>          | Switching frequency                  | Over V <sub>I</sub> and I <sub>O</sub> rang | es, SmartSync (pin 1) to (                                                                                   | SND                                |      | 300      |                     | kHz             |

| f <sub>SYNC</sub>       | Synchronization (SYNC) frequency     |                                             |                                                                                                              |                                    | 240  |          | 400                 | kHz             |

| V <sub>SYNCH</sub>      | SYNC High-Level Input Voltage        |                                             |                                                                                                              |                                    | 2    |          | 5.5                 | V               |

| $V_{SYNCL}$             | SYNC Low-Level Input Voltage         |                                             |                                                                                                              |                                    |      |          | 8.0                 | V               |

| t <sub>SYNC</sub>       | SYNC Minimum Pulse Width             |                                             |                                                                                                              |                                    | 200  |          |                     | nSec            |

<sup>(1)</sup> The minimum input voltage is 2.2 V or  $(V_O + 0.5)$  V, whichever is greater.

<sup>(2)</sup> The set-point voltage tolerance is affected by the tolerance and stability of R<sub>SET</sub>. The stated limit is unconditionally met if R<sub>SET</sub> has a tolerance of 1% with 100 ppm/C or better temperature stability.

<sup>(3)</sup> A low-leakage (<100 nA), open-drain device, such as MOSFET or voltage supervisor IC, is recommended to control pin 9. The open-circuit voltage is less than V<sub>I</sub>.

<sup>(4)</sup> This control pin has an internal pull-up. Do not place an external pull-up on this pin. If it is left open-circuit, the module operates when input power is applied. A small, low-leakage (<100 nA) MOSFET is recommended for control. The open-circuit voltage is less than 3.5Vdc. For additional information, see the related application note.

# **ELECTRICAL CHARACTERISTICS (continued)**

# PTH04T261W (Ceramic Capacitors)

$T_A = 25$ °C,  $V_I = 5$  V,  $V_O = 3.3$  V,  $C_I = 300$   $\mu F$  ceramic,  $C_O = 300$   $\mu F$  ceramic, and  $I_O = I_O$  max (unless otherwise stated)

|      | PARAMETER                                  |                                                     | TEST CONDITIONS                                  | PTH     | UNIT      |          |                    |

|------|--------------------------------------------|-----------------------------------------------------|--------------------------------------------------|---------|-----------|----------|--------------------|

|      |                                            |                                                     |                                                  |         | MIN       | TYP MAX  |                    |

| Cı   | External input capacitance                 |                                                     |                                                  |         | 300 (5)   |          | μF                 |

|      |                                            | w/o TurboTrans                                      | Capacitance Value                                | Ceramic | 300 (6)   | 5000 (7) | μF                 |

| Co   | C <sub>O</sub> External output capacitance | w/ TurboTrans                                       | w/ TurboTrans  Capacitance Value                 |         | see table | 5000     | μF                 |

|      |                                            |                                                     | Capacitance × ESR product (C <sub>O</sub> × ESR) |         |           |          | μF×mΩ              |

| MTBF | Reliability                                | Per Telcordia SR-3<br>T <sub>A</sub> = 40°C, ground |                                                  |         | 5.6       |          | 10 <sup>6</sup> Hr |

<sup>(5) 300</sup> μF of input capacitance is required for proper operation. 300 μF of ceramic or 330 μF of electrolytic input capacitance can be used. Electrolytic capacitance must be rated for a minimum of 400 mA rms of ripple current. An additional 22-μF ceramic input capacitor is recommended to reduce rms ripple current.

<sup>(6) 300</sup> μF of ceramic output capacitance is required for basic operation. The minimum output capacitance requirement increases when TurboTrans™ (TT) technology is utilized. Additionally, low ESR capacitors are required for proper operation. See related Application Information for more guidance.

<sup>(7)</sup> This is the calculated maximum disregarding *TurboTrans™* technology.

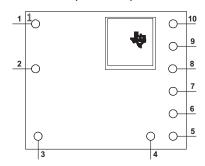

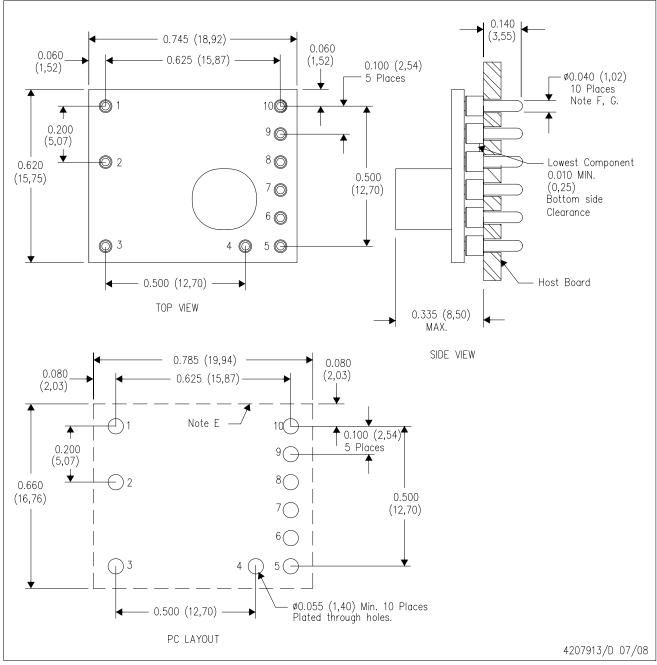

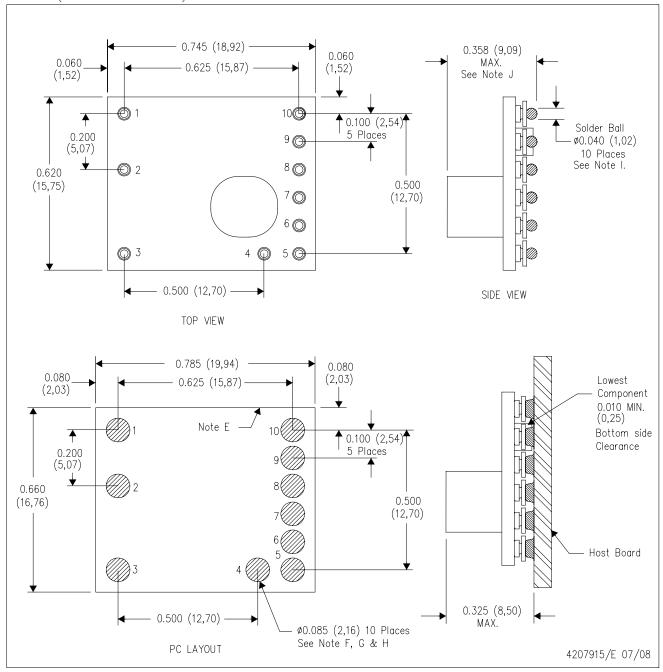

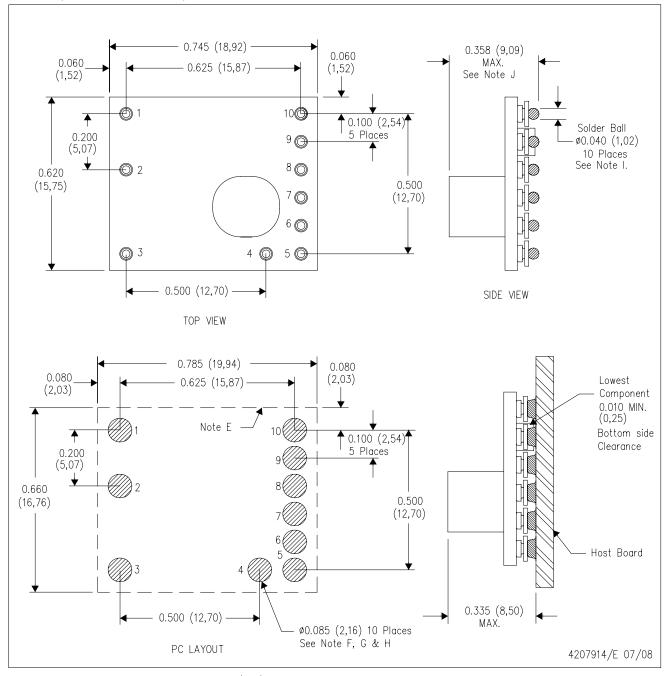

#### PTH04T260/261W (TOP VIEW)

# **TERMINAL FUNCTIONS**

| TERMINA               | <b>AL</b> | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|-----------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| NAME                  | NO.       | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| VI                    | 2         | The positive input voltage power node to the module, which is referenced to common GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| Vo                    | 4         | The regulated positive power output with respect to the GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| GND                   | 3         | This is the common ground connection for the $V_I$ and $V_O$ power connections. It is also the 0 Vdc reference for the control inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

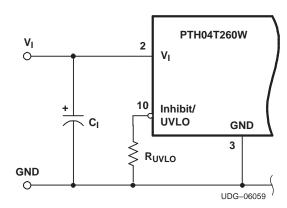

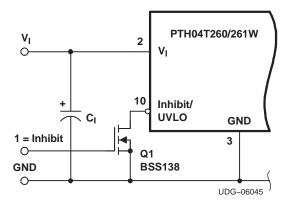

| Inhibit and           | 10        | The Inhibit pin is an open-collector/drain, negative logic input that is referenced to GND. Applying a low level ground signal to this input disables the module's output and turns off the output voltage. When the Inhibit control is active, the input current drawn by the regulator is significantly reduced. If the Inhibit pin is left open-circuit, the module produces an output whenever a valid input source is applied.                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| OVEO                  |           | This pin is also used for input undervoltage lockout (UVLO) programming. Connecting a resistor from this pin to GND (pin 3) allows the ON threshold of the UVLO to be adjusted higher than the default value. For more information, see the Application Information section.                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |  |

| V <sub>O</sub> Adjust | 7         | A 0.05 W 1% resistor must be directly connected between this pin and pin 6 (– Sense), close to the module to set the output voltage to a value higher than 0.69 V. The temperature stability of the resistor should be 100 ppm/°C (or better). The setpoint range for the output voltage is from 0.69 V to 3.6 V. If left open circuit, the output voltage defaults to its lowest value. For further information, on output voltage adjustment see the related application note.                                                                                                                                                                                               |  |  |  |  |  |  |

|                       |           | The specification table gives the preferred resistor values for a number of standard output voltages.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |

| + Sense               | 5         | The sense input allows the regulation circuit to compensate for voltage drop between the module and the load. For optimal voltage accuracy, +Sense must be connected to V <sub>O</sub> , close to the load.                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| - Sense               | 6         | The sense input allows the regulation circuit to compensate for voltage drop between the module and the load. For optimal voltage accuracy, –Sense must be connected to GND (pin 3), very close to the module (within 10 cm).                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

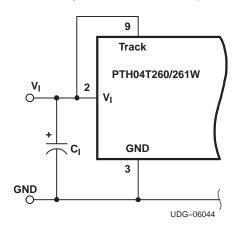

| Track                 | 9         | This is an analog control input that enables the output voltage to follow an external voltage. This pin becomes active typically 20 ms after the input voltage has been applied, and allows direct control of the output voltage from 0 V up to the nominal set-point voltage. Within this range the module's output voltage follows the voltage at the Track pin on a volt-for-volt basis. When the control voltage is raised above this range, the module regulates at its set-point voltage. The feature allows the output voltage to rise simultaneously with other modules powered from the same input bus. If unused, this input should be connected to V <sub>1</sub> . |  |  |  |  |  |  |

|                       |           | NOTE: Due to the undervoltage lockout feature, the output of the module cannot follow its own input voltage during power up. For more information, see the related application note.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| TurboTrans™           | 8         | This input pin adjusts the transient response of the regulator. To activate the TurboTrans feature, a 1%, 0.05 W resistor must be connected between this pin and pin 5 (+Sense) very close to the module. For a given value of output capacitance, a reduction in peak output voltage deviation is achieved by using this feature. If unused, this pin must be left open-circuit. The resistance requirement can be selected from the TurboTrans resistor table in the Application Information section. External capacitance must never be connected to this pin unless the TurboTrans resistor is a short, $0\Omega$ .                                                        |  |  |  |  |  |  |

| SmartSync             | 1         | This input pin sychronizes the switching frequency of the module to an external clock frequency. The SmartSync feature can be used to sychronize the switching fequency of multiple PTH04T260/261W modules, aiding EMI noise suppression efforts. If unused, this pin should be connected to GND (pin 3). For more information, please review the Application Information section.                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |

(1) Denotes negative logic: Open = Normal operation, Ground = Function active

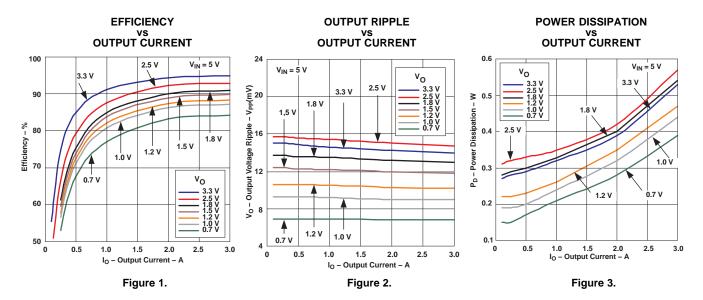

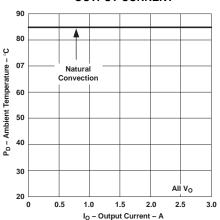

# TYPICAL CHARACTERISTICS(1)(2)

# CHARACTERISTIC DATA $(V_1 = 5 V)$

Figure 4.

- (1) The electrical characteristic data has been developed from actual products tested at 25C. This data is considered typical for the converter. Applies to Figure 1, Figure 2, and Figure 3.

- (2) The temperature derating curves represent the conditions at which internal components are at or below the manufacturer's maximum operating temperatures. Derating limits apply to modules soldered directly to a 100 mm x 100 mm double-sided PCB with 2 oz. copper. Applies to Figure 4.

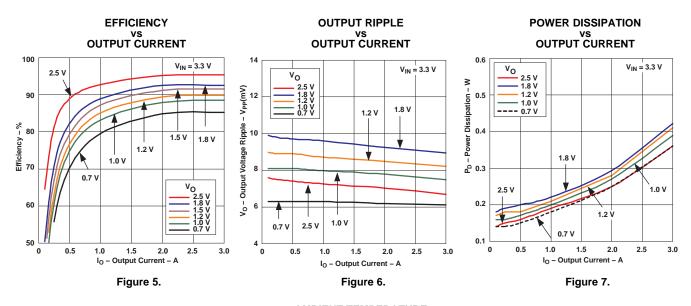

# TYPICAL CHARACTERISTICS(1)(2)

# CHARACTERISTIC DATA (V<sub>I</sub> = 3.3 V)

- Figure 8.

- (1) The electrical characteristic data has been developed from actual products tested at 25C. This data is considered typical for the converter. Applies to Figure 5, Figure 6, and Figure 7.

- (2) The temperature derating curves represent the conditions at which internal components are at or below the manufacturer's maximum operating temperatures. Derating limits apply to modules soldered directly to a 100 mm x 100 mm double-sided PCB with 2 oz. copper. Applies to Figure 8.

#### **APPLICATION INFORMATION**

#### ADJUSTING THE OUTPUT VOLTAGE

The  $V_O$  Adjust control (pin 7) sets the output voltage of the PTH04T260/261W. The adjustment range of the PTH04T260/261W is 0.69V to 3.6V. The adjustment method requires the addition of a single external resistor,  $R_{SET}$ , that must be connected directly between the  $V_O$  Adjust and the –Sense pins. Table 1 gives the standard value of the external resistor for a number of standard voltages, along with the actual output voltage that this resistance value provides.

For other output voltages, the value of the required resistor can either be calculated using the following formula, or simply selected from the range of values given in Table 2. Figure 9 shows the placement of the required resistor.

$$R_{SET} = 10 \text{ k}\Omega \times \frac{0.69}{V_O - 0.69} - 1.43 \text{ k}\Omega$$

(1)

Table 1. Preferred Values of R<sub>SET</sub> for Standard Output Voltages

| V <sub>O</sub> (Standard) (V) | R <sub>SET</sub> (Standard Value) (kΩ) | V <sub>O</sub> (Actual) (V) |

|-------------------------------|----------------------------------------|-----------------------------|

| 3.3 (1)                       | 1.21                                   | 3.304                       |

| 2.5 (1)                       | 2.37                                   | 2.506                       |

| 1.8 (1)                       | 4.75                                   | 1.807                       |

| 1.5 <sup>(1)</sup>            | 6.98                                   | 1.510                       |

| 1.2                           | 12.1                                   | 1.200                       |

| 1.0                           | 20.5                                   | 1.004                       |

| 0.7                           | 681                                    | 0.700                       |

(1) The minimum input voltage is 2.2 V or  $(V_O + 0.5)$  V, whichever is greater.

- (1) R<sub>SET</sub>: Use a 0.05 W resistor with a tolerance of 1% and temperature stability of 100 ppm/°C (or better). Connect the resistor directly between pins 7 and 6, as close to the regulator as possible, using dedicated PCB traces.

- (2) Never connect capacitors from V<sub>O</sub> Adjust to either GND, V<sub>O</sub>, or +Sense. Any capacitance added to the V<sub>O</sub> Adjust pin affects the stability of the regulator.

Figure 9. Vo Adjust Resistor Placement

Table 2. Output Voltage Set-Point Resistor Values (Standard Values)

| V <sub>O</sub> Required (V) | R <sub>SET</sub> (kΩ) | V <sub>O</sub> Required (V) | R <sub>SET</sub> (kΩ) |

|-----------------------------|-----------------------|-----------------------------|-----------------------|

| 0.70                        | 681                   | 1.80                        | 4.75                  |

| 0.75                        | 113                   | 1.85                        | 4.53                  |

| 0.80                        | 61.9                  | 1.90                        | 4.22                  |

| 0.85                        | 41.2                  | 1.95                        | 4.02                  |

| 0.90                        | 31.6                  | 2.00                        | 3.83                  |

| 0.95                        | 24.9                  | 2.10                        | 3.40                  |

| 1.00                        | 20.5                  | 2.20                        | 3.09                  |

| 1.05                        | 17.8                  | 2.30                        | 2.87                  |

| 1.10                        | 15.4                  | 2.40                        | 2.61                  |

| 1.15                        | 13.7                  | 2.50                        | 2.37                  |

| 1.20                        | 12.1                  | 2.60                        | 2.15                  |

| 1.25                        | 10.7                  | 2.70                        | 2.00                  |

| 1.30                        | 9.88                  | 2.80                        | 1.82                  |

| 1.35                        | 9.09                  | 2.90                        | 1.69                  |

| 1.40                        | 8.25                  | 3.00                        | 1.54                  |

| 1.45                        | 7.68                  | 3.10                        | 1.43                  |

| 1.50                        | 6.98                  | 3.20                        | 1.33                  |

| 1.55                        | 6.49                  | 3.30                        | 1.21                  |

| 1.60                        | 6.04                  | 3.40                        | 1.13                  |

| 1.65                        | 5.76                  | 3.50                        | 1.02                  |

| 1.70                        | 5.36                  | 3.60                        | 0.931                 |

| 1.75                        | 5.11                  |                             |                       |

#### CAPACITOR RECOMMENDATIONS FOR THE PTH04T260/261W POWER MODULE

#### **Capacitor Technologies**

# **Electrolytic Capacitors**

When using electrolytic capacitors, high-quality, computer-grade electrolytic capacitors are recommended. Aluminum electrolytic capacitors provide adequate decoupling over the frequency range of 2 kHz to 150 kHz, and are suitable when ambient temperatures are above -20°C. For operation below -20°C, tantalum, ceramic, or OS-CON type capacitors are required.

# **Ceramic Capacitors**

The performance of aluminum electrolytic capacitors is less effective above 150 kHz. Multilayer ceramic capacitors have a low ESR and a resonant frequency higher than the bandwidth of the regulator. They can be used to reduce the reflected ripple current at the input as well as improve the transient response of the output.

# **Tantalum, Polymer-Tantalum Capacitors**

Tantalum type capacitors may only used on the output bus, and are recommended for applications where the ambient operating temperature is less than 0°C. The AVX TPS series and Kemet capacitor series are suggested over many other tantalum types due to their lower ESR, higher rated surge, power dissipation, and ripple current capability. Tantalum capacitors that have no stated ESR or surge current rating are not recommended for power applications.

#### Input Capacitor (Required)

The PTH04T261W requires a minimum input capacitance of 300µF of ceramic type.

The PTH04T260W requires a minimum input capacitance of 330μF of electrolytic type. The ripple current rating of the electrolytic capacitor must be at least 400mArms. An optional 22-μF X5R/X7R ceramic capacitor is recommended to reduce the RMS ripple current.

#### **Input Capacitor Information**

The size and value of the input capacitor is determined by the converter's transient performance capability. This minimum value assumes that the converter is supplied with a responsive, low-inductance input source. This source should have ample capacitive decoupling, and be distributed to the converter via PCB power and ground planes.

Ceramic capacitors should be located as close as possible to the module's input pins, within 0.5 inch (1,3 cm). Adding ceramic capacitance is necessary to reduce the high-frequency ripple voltage at the module's input. This reduces the magnitude of the ripple current through the electroytic capacitor, as well as the amount of ripple current reflected back to the input source. Additional ceramic capacitors can be added to further reduce the RMS ripple current requirement for the electrolytic capacitor.

Increasing the minimum input capacitance to  $680-\mu F$  is recommended for high-performance applications, or wherever the input source performance is degraded.

The main considerations when selecting input capacitors are the RMS ripple current rating, temperature stability, and maintaining less than 100 m $\Omega$  of equivalent series resistance (ESR).

Regular tantalum capacitors are not recommended for the input bus. These capacitors require a recommended minimum voltage rating of  $2 \times (\text{maximum dc voltage} + \text{ac ripple})$ . This is standard practice to ensure reliability. No tantalum capacitors were found to have voltage ratings sufficient to meet this requirement.

When the operating temperature is below 0°C, the ESR of aluminum electrolytic capacitors increases. For these applications, Os-Con, poly-aluminum, and polymer-tantalum types should be considered.

#### **Output Capacitor (Required)**

The PTH04T261W requires a minimum output capacitance of 300μF of ceramic type.

The PTH04T260W requires a minimum 100μF of ceramic and 150 F of non-ceramic output capacitance. Additional non-ceramic, low-ESR capacitance is recommended for improved performance.

The required capacitance above the minimum is determined by actual transient deviation requirements. See the TurboTrans Technology application section within this document for specific capacitance selection.

#### **Output Capacitor Information**

When selecting output capacitors, the main considerations are capacitor type, temperature stability, and ESR. When using the TurboTrans feature, the capacitance X ESR product should also be considered (see the following section).

Ceramic output capacitors added for high-frequency bypassing should be located as close as possible to the load to be effective. Ceramic capacitor values below  $10\mu F$  should not be included when calculating the total output capacitance value.

When the operating temperature is below 0°C, the ESR of aluminum electrolytic capacitors increases. For these applications, Os-Con, poly-aluminum, and polymer-tantalum types should be considered.

# **TurboTrans Output Capacitance**

TurboTrans allows the designer to optimize the output capacitance according to the system transient design requirement. High quality, ultra-low ESR capacitors are required to maximize TurboTrans effectiveness. When using TurboTrans, the capacitor's capacitance ( $\mu$ F) × ESR ( $m\Omega$ ) product determines its capacitor type; Type A, B, or C. These three types are defined as follows:

Type A =  $(100 \le \text{capacitance} \times \text{ESR} \le 1000)$  (e.g. ceramic)

Type B = (1000 < capacitance × ESR ≤ 5000) (e.g. polymer-tantalum)

Type C =  $(5000 < \text{capacitance} \times \text{ESR} \le 10,000)$  (e.g. Os-Con)

When using more than one type of output capacitor, select the capacitor type that makes up the majority of the total output capacitance. When calculating the  $C \times ESR$  product, use the maximum ESR value from the capacitor manufacturer's data sheet.

#### The PTH04T261W should be used when only Type A (ceramic) capacitors are used on the output.

#### Working Examples:

A capacitor with a capacitance of  $330\mu F$  and an ESR of  $5m\Omega$ , has a C×ESR product of  $1650\mu Fxm\Omega$  ( $330\mu F \times 5m\Omega$ ). This is a Type B capacitor.

A capacitor with a capacitance of  $1000\mu F$  and an ESR of  $8m\Omega$ , has a C×ESR product of  $8000\mu F xm\Omega$  ( $1000\mu F xm\Omega$ ). This is a Type C capacitor.

See the TurboTrans Technology application section within this document for specific capacitance selection.

Table 3 includes a preferred list of capacitors by type and vendor. See the Output Bus / TurboTrans column.

# Non-TurboTrans Output Capacitance

If the TurboTrans feature is not used, minimum ESR and maximum capacitor limits must be followed. System stability may be effected and increased output capacitance may be required without TurboTrans.

When using the PTH04T260W without the TurboTrans feature, observe the minimum ESR of the entire output capacitor bank. The minimum ESR limit of the output capacitor bank is  $7m\Omega$ . A list of preferred low-ESR type capacitors, are identified in Table 3.

When using the PTH04T261W without the TurboTrans feature, the maximum amount of capacitance is  $3000\mu F$  of ceramic type. Large amounts of capacitance may reduce system stability.

Using the TurboTrans feature improves system stability, improves transient response, and reduces the amount of output capacitance required to meet system transient design requirements.

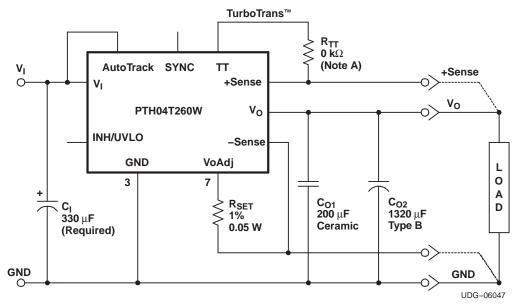

#### **Designing for Fast Load Transients**

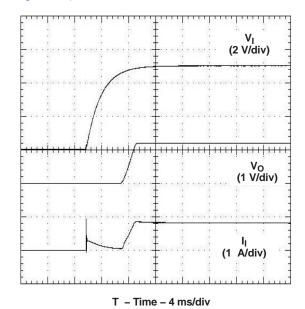

The transient response of the dc/dc converter has been characterized using a load transient with a di/dt of 2.5A/µs. The typical voltage deviation for this load transient is given in the Electrical Characteristics table using the minimum required value of output capacitance. As the di/dt of a transient is increased, the response of a converter's regulation circuit ultimately depends on its output capacitor decoupling network. This is an inherent limitation with any dc/dc converter once the speed of the transient exceeds its bandwidth capability.

If the target application specifies a higher di/dt or lower voltage deviation, the requirement can only be met with additional low ESR ceramic capacitor decoupling. Generally, with load steps greater than  $100A/\mu s$ , adding multiple  $10-\mu F$  ceramic capacitors plus  $10\times 1\mu F$ , and numerous high frequency ceramics ( $\le 0.1\mu F$ ) is all that is required to soften the transient higher frequency edges. The PCB location of these capacitors in relation to the load is critical. DSP, FPGA and ASIC vendors identify types, location and amount of capacitance required for optimum performance. Low impedance buses, unbroken PCB copper planes, and components located as close as possible to the high frequency devices are essential for optimizing transient performance.

Table 3. Input/Output Capacitors<sup>(1)</sup>

|                                             |                           | Сара          | citor Cha                    | racteristic                                    | s                     |              | Quantit               | y                                                   |                                                   |

|---------------------------------------------|---------------------------|---------------|------------------------------|------------------------------------------------|-----------------------|--------------|-----------------------|-----------------------------------------------------|---------------------------------------------------|

|                                             |                           |               | Max                          | Max                                            |                       |              | Outp                  | ut Bus <sup>(2)</sup>                               |                                                   |

| Capacitor Vendor,<br>Type Series (Style)    | Working<br>Voltage<br>(V) | Value<br>(μF) | ESR<br>at 100<br>kHz<br>(mΩ) | Ripple<br>Current<br>at 85°C<br>(Irms)<br>(mA) | Physical<br>Size (mm) | Input<br>Bus | No<br>Turbo-<br>Trans | Turbo-<br>Trans<br>Capacitor<br>Type <sup>(3)</sup> | Vendor Part No.                                   |

| Panasonic                                   |                           |               |                              |                                                |                       |              |                       |                                                     |                                                   |

| SP series (UE)                              | 6.3                       | 220           | 15                           | 3000                                           | 7,3×4,3               | 2            | 1≤ 2                  | B ≥ 1 <sup>(3)</sup>                                | EEFUE0J221R                                       |

| FC (Radial)                                 | 6.3                       | 390           | 117                          | 555                                            | 8 X 11,5              | 1            | ≥ 1                   | N/R (4)                                             | EEUFC0J391                                        |

| FK (SMD)                                    | 6.3                       | 470           | 160                          | 600                                            | 10 X 10,2             | 1            | ≥ 1                   | N/R (4)                                             | EEVFK0J471P                                       |

| United Chemi-Con                            |                           |               |                              |                                                |                       |              |                       |                                                     |                                                   |

| PTB, Poly-Tantalum(SMD)                     | 6.3                       | 330           | 25                           | 2600                                           | 7,3×4,3×2,8           | 1            | 1≤3                   | C ≥ 2 <sup>(3)</sup>                                | 6PTB337MD6TER                                     |

| LXZ, Aluminum (Radial)                      | 6.3                       | 680           | 120                          | 555                                            | 8 X 12                | 1            | 1                     | N/R (4)                                             | LXZ6.3VB681M8X12LL                                |

| PS, Poly-Alum (Radial)                      | 6.3                       | 390           | 12                           | 4770                                           | 8 X 11,5              | 1            | ≤1                    | B ≥ 2 <sup>(3)</sup>                                | 6PS390MH11                                        |

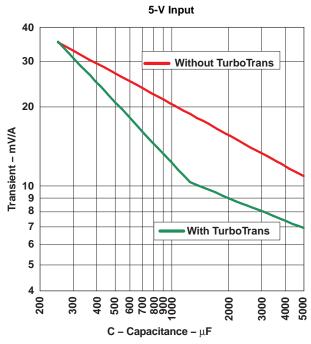

| PT Poly-Tantalum (SMD)                      | 6.3                       | 330           | 40                           | 3000                                           | 7,3×4,3               | 1            | 1                     | N/R (4)                                             | 6PT337MD8TER                                      |