TSC2007-Q1

ZHCS084A - SEPTEMBER 2011 - REVISED DECEMBER 2016

# 具有 I<sup>2</sup>C 接口的 TSC2007-Q1 1.2V 至 3.6V、12 位、 纳瓦级功率、4 线微型触摸屏控制器

## 1 特性

- 符合汽车应用 认证

- 具有符合 AEC-Q100 测试指导的以下结果:

- 器件温度等级 3: 环境工作温度范围为 -40°C 至 85°C

- 器件 HBM ESD 分类等级 3B

- 器件 CDM ESD 分类等级 C6

- 4线触摸屏接口

- 1.2V 至 3.6V 单电源或基准电压

- 比例换算

- 有效吞吐率:

- 高达 20kHz (8 位) 或 10kHz (12 位)

- 通过预处理减少总线活动

- I<sup>2</sup>C 接口支持:

- 标准、快速和高速模式

- 基于命令的简单用户界面:

- 与 TSC2003-Q1 兼容

- 8 位或 12 位分辨率

- 片上温度测量

- 触摸压力测量

- 屏幕触摸内部检测

- 用于笔触式检测或数据可用性中断

- 自动断电控制

- 低功耗:

- 在 1.2V、快速模式和 8.2kHz 均衡率的条件 下,电流为 32.24μA

- 在 1.8V、快速模式和 8.2kHz 均衡率的条件 下,电流为 39.31μA

- 在 2.7V、快速模式和 8.2kHz 均衡率的条件 下,电流为 53.32μA

- 增强型 ESD 保护:

- ±25kV 气隙放电

- ±15kV 接触放电

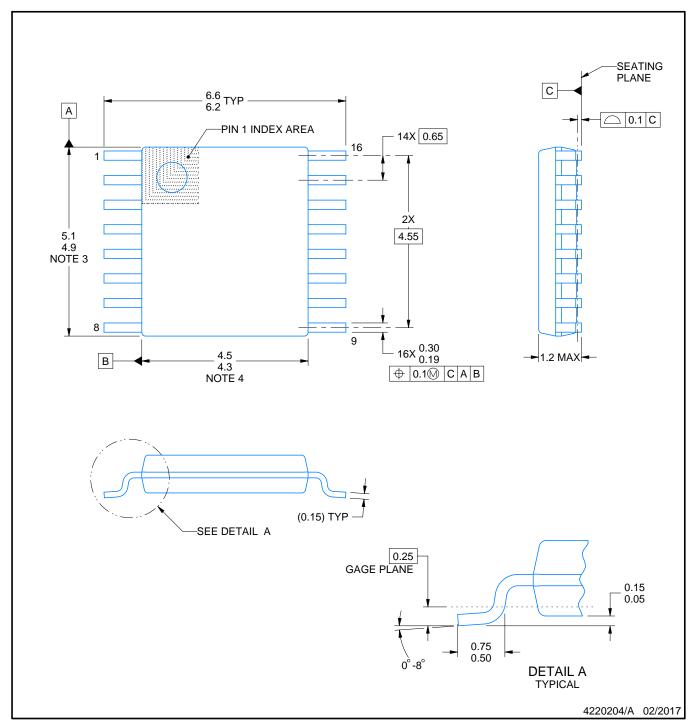

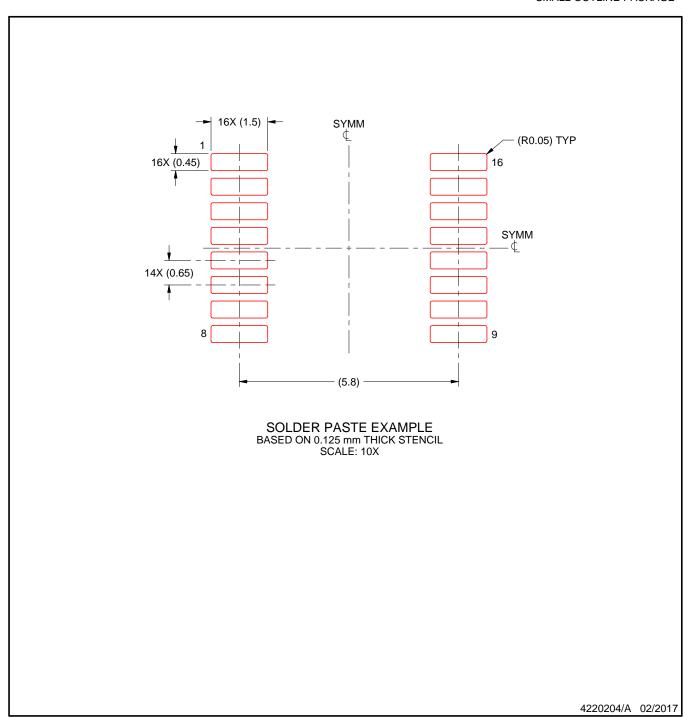

- 5mm x 4.4mm 16 引脚 TSSOP 封装

NOTE: 美国专利号 6246394; 其他专利正在申请中。

## 2 应用

- 车用信息娱乐显示屏

- 汽车导航系统

- 工业用户界面

- 多屏触摸控制系统

# 3 说明

TSC2007-Q1 器件是一款超低功耗触摸屏控制器,旨在与功耗敏感型汽车触摸显示屏结合使用。它具有完整的超低功耗 12 位模数转换 (A-D) 电阻式触摸屏转换器,包括驱动器和用于测量触摸压力的控制逻辑。

除了这些标准 特性外,TSC2007-Q1 还提供触摸屏测量预处理能力以减少总线负载,从而减少主处理器资源的消耗,而将这些资源分配给更关键的功能。

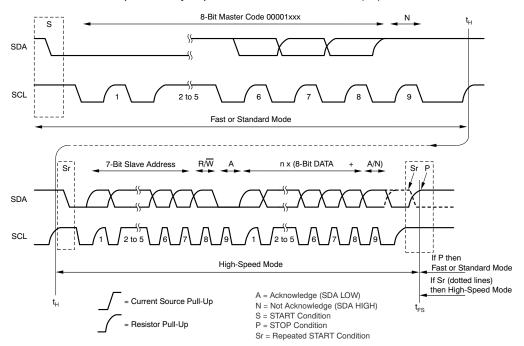

在所有三种定义的模式(标准、快速和高速)下,TSC2007-Q1 均支持 I<sup>2</sup>C 串行总线和数据传输协议。它提供 8 位或 12 位的可编程分辨率,以适应不同的屏幕尺寸和性能需求。

TSC2007-Q1 采用 16 引脚 TSSOP 封装。TSC2007-Q1 的额定工业温度范围为 -40°C 至 85°C。

#### 器件信息(1)

| 器件型号       | 封装         | 封装尺寸 (标称值)      |

|------------|------------|-----------------|

| TSC2007-Q1 | TSSOP (16) | 5.00mm x 4.40mm |

(1) 如需了解所有可用封装,请参阅数据表末尾的可订购产品附录。

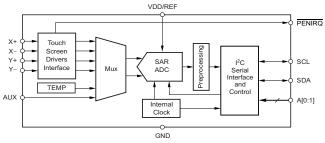

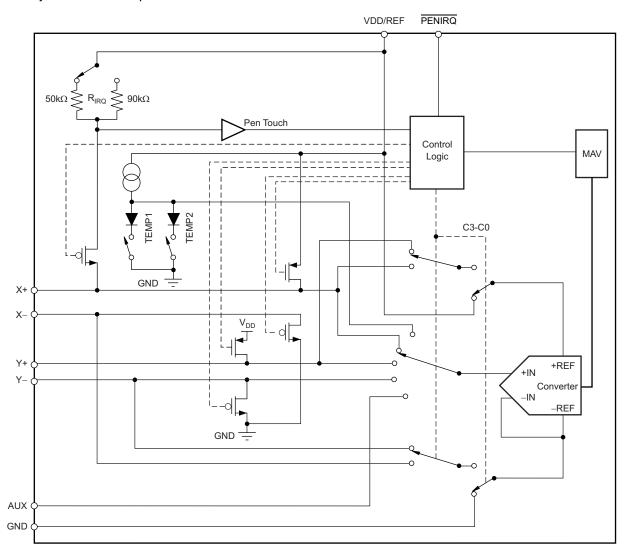

#### 功能框图

Copyright © 2016, Texas Instruments Incorporated

| _ | $\Rightarrow$ |

|---|---------------|

| _ | ملب           |

| _ | w             |

| 1 | 特性1                                                   |    | 7.2 Functional Block Diagram   | 12               |

|---|-------------------------------------------------------|----|--------------------------------|------------------|

| 2 | 应用                                                    |    | 7.3 Feature Description        |                  |

| 3 |                                                       |    | 7.4 Device Functional Modes    |                  |

| 4 | 修订历史2                                                 |    | 7.5 Programming                | 19               |

| 5 | Pin Configuration and Functions                       | 8  | Application and Implementation | 29               |

| 6 | Specifications                                        |    | 8.1 Application Information    | 29               |

| U | 6.1 Absolute Maximum Ratings                          |    | 8.2 Typical Application        | 29               |

|   | 6.2 ESD Ratings                                       | 9  | Power Supply Recommendations   | <mark>3</mark> 3 |

|   | 6.3 Recommended Operating Conditions                  | 10 | Layout                         | 33               |

|   | 6.4 Thermal Information                               |    | 10.1 Layout Guidelines         |                  |

|   | 6.5 Electrical Characteristics                        |    | 10.2 Layout Example            | 34               |

|   | 6.6 Timing Requirements: Standard Mode                | 11 | 器件和文档支持                        |                  |

|   | (SCL = 100 kHz)                                       |    | 11.1 器件支持                      | 35               |

|   | 6.7 Timing Requirements: Fast Mode (SCL = 400 kHz). 7 |    | 11.2 文档支持                      | 35               |

|   | 6.8 Timing Requirements: High-Speed Mode              |    | 11.3 接收文档更新通知                  | 35               |

|   | (SCL = 1.7 MHz)7                                      |    | 11.4 社区资源                      | 35               |

|   | 6.9 Timing Requirements: High-Speed Mode              |    | 11.5 商标                        | 35               |

|   | (SCL = 3.4 MHz)                                       |    | 11.6 静电放电警告                    | 35               |

| _ | 6.10 Typical Characteristics                          |    | 11.7 Glossary                  | 35               |

| 1 | Detailed Description                                  | 12 | 机械、封装和可订购信息                    | 35               |

|   | 7.1 Overview                                          |    |                                |                  |

# 4 修订历史

注: 之前版本的页码可能与当前版本有所不同。

# Changes from Original (September 2011) to Revision A

# Page

| • | 已添加 器件信息表、规格部分、ESD 额定值 表、建议运行条件表、详细 说明部分、应用和实施部分、电源建议部分、布局指南部分、布局示例部分、器件和文档支持部分以及机械、封装和可订购信息部分                | 1  |

|---|---------------------------------------------------------------------------------------------------------------|----|

| • | 已删除 订购信息表;请参阅数据表末尾的"封装选项附录"                                                                                   | 1  |

| • | 已更改 更改了 ESD 额定值信息并将 AEC-Q100 汽车项目符号添加到特性将"汽车信息娱乐显示屏"和"汽车导航系统"项目符号                                             | 1  |

| • | 已添加 添加到 <i>应用</i>                                                                                             | 1  |

| • | 已删除 将"数字缓冲PENIRQ"项目符号从特性中删除                                                                                   |    |

| • | 已删除 将"可编程的片上 PENIRQ 上拉电阻"项目符号从特性中删除                                                                           |    |

| • | 已删除 从绝对最大额定值中删除了引线温度参数                                                                                        | 1  |

| • | 将电源电压参数从电气特性表移到了建议运行条件表                                                                                       | 1  |

| • | Added IEC discharge information                                                                               |    |

| • | Added Thermal Information table                                                                               |    |

| • | Changed R <sub>BJA</sub> values for PW (TSSOP) From: 86 To: 101.7                                             | 4  |

| • | Changed t <sub>OF</sub> to t <sub>F</sub> in Timing Requirements tables                                       | 6  |

| • | Changed text in Reference mode to clarify singled-ended operation                                             |    |

| • | Changed Figure 24 caption text from PINTDAV to PENIRQ                                                         | 18 |

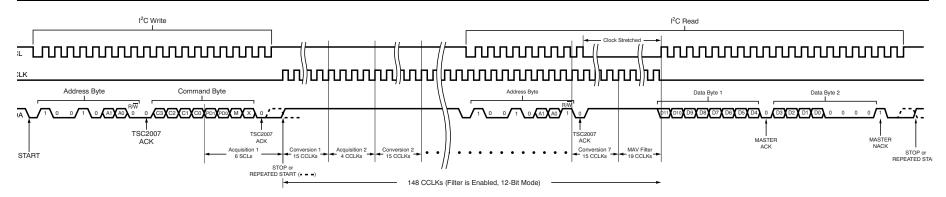

| • | Added subsections to <i>Throughput Rate and I2C Bus Traffic</i> section to clarify 8-bit and 12-bit operation |    |

|   |                                                                                                               |    |

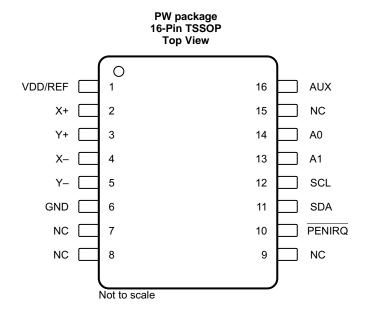

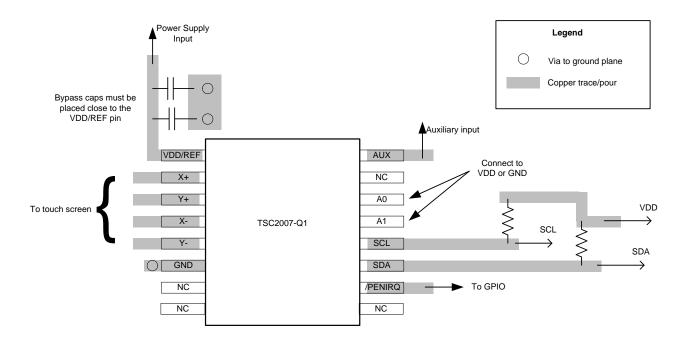

# 5 Pin Configuration and Functions

# **Pin Functions**

| PIN     |             | 1/0                 | A/D     | DESCRIPTION                                                                                                                     |  |  |  |  |

|---------|-------------|---------------------|---------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME    | NO.         | 1/0                 | AID     | DESCRIPTION                                                                                                                     |  |  |  |  |

| A0      | 14          | Input               | Digital | Address input bit 0                                                                                                             |  |  |  |  |

| A1      | 13          | Input               | Digital | Address input bit 1                                                                                                             |  |  |  |  |

| AUX     | 16          | Input               | Analog  | Auxiliary channel input                                                                                                         |  |  |  |  |

| GND     | 6           | _                   | _       | Ground                                                                                                                          |  |  |  |  |

| NC      | 7, 8, 9, 15 | _                   | _       | No connection                                                                                                                   |  |  |  |  |

| PENIRQ  | 10          | Output              | Digital | Data available interrupt output. A delayed (process delay) pen touch detect. Pin polarity with active low.                      |  |  |  |  |

| SCL     | 12          | Input and<br>Output | Digital | Serial clock. This pin is normally an input, but acts as an output when the device stretches the clock to delay a bus transfer. |  |  |  |  |

| SDA     | 11          | Input and<br>Output | Digital | Serial data I/O                                                                                                                 |  |  |  |  |

| VDD/REF | 1           | Input               | _       | Supply voltage and external reference input                                                                                     |  |  |  |  |

| X+      | 2           | Input               | Analog  | X+ channel input                                                                                                                |  |  |  |  |

| X-      | 4           | Input               | Analog  | X- channel input                                                                                                                |  |  |  |  |

| Y+      | 3           | Input               | Analog  | Y+ channel input                                                                                                                |  |  |  |  |

| Y-      | 5           | Input               | Analog  | Y- channel input                                                                                                                |  |  |  |  |

# 6 Specifications

## 6.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted). (1)

|                                                |                                                    | MIN                        | MAX                        | UNIT |

|------------------------------------------------|----------------------------------------------------|----------------------------|----------------------------|------|

| Analog input valtage                           | X+, Y+, AUX to GND                                 | -0.4                       | V <sub>DD</sub> + 0.1      | V    |

| Analog input voltage                           | X-, Y- to GND                                      | -0.4                       | $V_{DD} + 0.1$             | V    |

| Voltage                                        | VDD/REF pin to GND                                 | -0.3                       | 5                          | V    |

| Digital input voltage to GND                   |                                                    | -0.3 V <sub>DD</sub> + 0.3 |                            | V    |

| Digital output voltage to GND                  | Digital output voltage to GND $-0.3$ $V_{DD} + 0.$ |                            | $V_{DD} + 0.3$             | V    |

| Power dissipation                              |                                                    | (T <sub>J(MAX)</sub>       | $-T_A$ ) / $R_{\theta JA}$ |      |

| Operating free-air temperature, T <sub>A</sub> |                                                    | -40 85                     |                            | °C   |

| Junction temperature, T <sub>J</sub>           |                                                    |                            | 150                        | °C   |

| Storage temperature, T <sub>stg</sub>          |                                                    | -65                        | 150                        | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# 6.2 ESD Ratings

|                    |                         |                                                                    |                     | VALUE  | UNIT |  |

|--------------------|-------------------------|--------------------------------------------------------------------|---------------------|--------|------|--|

| V <sub>(ESD)</sub> | Electrostatic discharge | Human-body model (HBM), per AEC Q100-002 <sup>(1)</sup>            |                     | ±8000  |      |  |

|                    |                         | Charged-device model (CDM), per AEC Q100-011                       |                     |        | .,   |  |

|                    |                         | IEC 61000-4-2 contact discharge (2)                                | Pins 2, 3, 4, and 5 | ±15000 | V    |  |

|                    |                         | IEC 61000-4-2 air-gap discharge <sup>(2)</sup> Pins 2, 3, 4, and 5 |                     | ±25000 |      |  |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

## 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|          |                      |     | MIN | MAX | UNIT |

|----------|----------------------|-----|-----|-----|------|

| $V_{DD}$ | Power-supply voltage | VDD | 1.2 | 3.6 | ٧    |

#### 6.4 Thermal Information

|                        |                                              | TSC2007-Q1 |      |

|------------------------|----------------------------------------------|------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | PW (TSSOP) | UNIT |

|                        |                                              | 16 PINS    |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 101.7      | °C/W |

| R <sub>θ</sub> JC(top) | Junction-to-case (top) thermal resistance    | 35.2       | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 47.7       | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 2.4        | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 47         | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

<sup>(2)</sup> Test method based on IEC standard 61000-4-2. Contact Texas Instruments for test details.

#### 6.5 Electrical Characteristics

$T_A = -40$ °C to 85°C.  $V_{PR} = 1.2$  V to 3.6 V (unless otherwise noted).

| PARAMETER                                |                                                                                                                                                                                                             | TE                                                        | ST CONDITIONS           | MIN                                      | TYP                                                                                                                                                                                                     | MAX      | UNIT               |

|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------------|

| AUXILIARY ANALOG INPU                    | Т                                                                                                                                                                                                           |                                                           |                         |                                          |                                                                                                                                                                                                         |          |                    |

| Input voltage range                      |                                                                                                                                                                                                             |                                                           |                         | 0                                        |                                                                                                                                                                                                         | $V_{DD}$ | V                  |

| Input capacitance                        |                                                                                                                                                                                                             |                                                           |                         |                                          | 12                                                                                                                                                                                                      |          | pF                 |

| Input leakage current                    |                                                                                                                                                                                                             |                                                           |                         | -1                                       |                                                                                                                                                                                                         | 1        | μΑ                 |

| A-D CONVERTER                            |                                                                                                                                                                                                             |                                                           |                         |                                          |                                                                                                                                                                                                         | '        |                    |

| Resolution                               |                                                                                                                                                                                                             | Programmable: 8 bits or                                   | 12 bits                 |                                          |                                                                                                                                                                                                         | 12       | Bits               |

| No missing codes                         |                                                                                                                                                                                                             | 12-bit resolution                                         |                         | 11                                       |                                                                                                                                                                                                         |          | Bits               |

| Integral linearity                       |                                                                                                                                                                                                             |                                                           |                         |                                          | ±1.5                                                                                                                                                                                                    |          | LSB <sup>(1)</sup> |

| 0#                                       |                                                                                                                                                                                                             | V <sub>DD</sub> = 1.8 V                                   |                         |                                          | -1.2                                                                                                                                                                                                    |          | LSB                |

| Offset error                             |                                                                                                                                                                                                             | $V_{DD} = 1.8 \text{ V}$ -1.2 $V_{DD} = 3 \text{ V}$ -3.1 |                         |                                          | LSB                                                                                                                                                                                                     |          |                    |

| 0 :                                      |                                                                                                                                                                                                             | V <sub>DD</sub> = 1.8 V                                   |                         |                                          | 0.7                                                                                                                                                                                                     |          | LSB                |

| Gain error                               |                                                                                                                                                                                                             | V <sub>DD</sub> = 3 V                                     |                         |                                          | 0.1                                                                                                                                                                                                     |          | LSB                |

| TOUCH SENSORS                            |                                                                                                                                                                                                             | ·                                                         |                         |                                          |                                                                                                                                                                                                         |          |                    |

| DENIDOIII                                |                                                                                                                                                                                                             | $T_A = 25^{\circ}C, V_{DD} = 1.8 V,$                      | command 1011 set 0000   |                                          | 51                                                                                                                                                                                                      |          | kΩ                 |

| PENIRQ pullup resistor, K <sub>IRO</sub> | )                                                                                                                                                                                                           | $T_A = 25^{\circ}C, V_{DD} = 1.8 V,$                      | command 1011 set 0001   | 90                                       |                                                                                                                                                                                                         |          | kΩ                 |

| 0 11 011 11                              | Y+, X+                                                                                                                                                                                                      |                                                           |                         |                                          | 6                                                                                                                                                                                                       |          | Ω                  |

| Switch ON-resistance                     | Y-, X-                                                                                                                                                                                                      |                                                           |                         |                                          | 5                                                                                                                                                                                                       |          | Ω                  |

| Switch drivers drive current (2          | (3)                                                                                                                                                                                                         | 100-ms duration                                           |                         |                                          |                                                                                                                                                                                                         | 50       | mA                 |

| INTERNAL TEMPERATURE                     | SENSOR                                                                                                                                                                                                      |                                                           |                         |                                          |                                                                                                                                                                                                         |          |                    |

| Temperature range                        |                                                                                                                                                                                                             |                                                           |                         | -40                                      |                                                                                                                                                                                                         | 85       | °C                 |

| emperature range                         | Differential mathed (4)                                                                                                                                                                                     | V <sub>DD</sub> = 3 V                                     |                         | 1.94                                     |                                                                                                                                                                                                         | °C/LSB   |                    |

| Deschation                               |                                                                                                                                                                                                             | Differential method (1)                                   | V <sub>DD</sub> = 1.6 V |                                          | 1.04                                                                                                                                                                                                    |          | °C/LSB             |

| Resolution                               |                                                                                                                                                                                                             | TEMP4 (5)                                                 | V <sub>DD</sub> = 3 V   | 0 —1 —1 —11 ——10 ——40 ——40 ————————————— | 0.35                                                                                                                                                                                                    |          | °C/LSB             |

|                                          |                                                                                                                                                                                                             | TEMPT                                                     | V <sub>DD</sub> = 1.6 V |                                          | 0.19                                                                                                                                                                                                    |          | °C/LSB             |

|                                          |                                                                                                                                                                                                             | Differential mathed (4)                                   | V <sub>DD</sub> = 3 V   |                                          | 112  -1 12  -1 12  11                                                                                                                                                                                   |          | °C/LSB             |

| A                                        |                                                                                                                                                                                                             | Differential method <sup>19</sup>                         | V <sub>DD</sub> = 1.6 V |                                          | ±2                                                                                                                                                                                                      |          | °C/LSB             |

| Accuracy                                 |                                                                                                                                                                                                             | TEMP4 (5)                                                 | V <sub>DD</sub> = 3 V   |                                          | 12<br>±1.5<br>-1.2<br>-3.1<br>0.7<br>0.1<br>51<br>90<br>6<br>5<br>50<br>85<br>1.94<br>1.04<br>0.35<br>0.19<br>±2<br>±2<br>±3<br>±3<br>±3<br>3.19<br>3.66<br>3.78<br>3.82<br>1.6<br>1.83<br>1.88<br>1.91 | °C/LSB   |                    |

|                                          | INIRQ pullup resistor, R <sub>IRQ</sub> TA  TA  TA  Y+, X+  Y-, X-  Itch ON-resistance  Itch drivers drive current (2)(3)  ERNAL TEMPERATURE SENSOR  Inperature range  Diff  TEI  Curacy  TERNAL OSCILLATOR | TEMPT                                                     | V <sub>DD</sub> = 1.6 V |                                          | ±3                                                                                                                                                                                                      |          | °C/LSB             |

| INTERNAL OSCILLATOR                      |                                                                                                                                                                                                             |                                                           |                         |                                          |                                                                                                                                                                                                         |          |                    |

|                                          | 3.19                                                                                                                                                                                                        |                                                           | MHz                     |                                          |                                                                                                                                                                                                         |          |                    |

|                                          |                                                                                                                                                                                                             | 0 D#                                                      | V <sub>DD</sub> = 1.8 V |                                          | 3.66                                                                                                                                                                                                    |          | MHz                |

|                                          |                                                                                                                                                                                                             | g-Bit                                                     | V <sub>DD</sub> = 2.7 V |                                          | 3.78                                                                                                                                                                                                    |          | MHz                |

|                                          |                                                                                                                                                                                                             |                                                           | V <sub>DD</sub> = 3.6 V |                                          | 3.82                                                                                                                                                                                                    |          | MHz                |

|                                          |                                                                                                                                                                                                             |                                                           | V <sub>DD</sub> = 1.2 V |                                          | 1.6                                                                                                                                                                                                     |          | MHz                |

|                                          |                                                                                                                                                                                                             | 40 Dia                                                    | V <sub>DD</sub> = 1.8 V |                                          | 1.83                                                                                                                                                                                                    |          | MHz                |

|                                          |                                                                                                                                                                                                             | 12-Bit                                                    | V <sub>DD</sub> = 2.7 V |                                          | 1.88                                                                                                                                                                                                    |          | MHz                |

|                                          |                                                                                                                                                                                                             |                                                           | V <sub>DD</sub> = 3.6 V |                                          | 1.91                                                                                                                                                                                                    |          | MHz                |

| Frequency drift                          |                                                                                                                                                                                                             | V <sub>DD</sub> = 1.6 V                                   |                         |                                          | 0.0056                                                                                                                                                                                                  |          | %/°C               |

| Freduency drift                          |                                                                                                                                                                                                             | V <sub>DD</sub> = 3 V                                     |                         |                                          |                                                                                                                                                                                                         |          | %/°C               |

<sup>(1)</sup> LSB means Least Significant Bit. With VDD/REF pin = 1.6 V, one LSB is 391  $\mu$ V. (2) Not production tested. Specified by design.

Exceeding 50-mA source current may result in device degradation.

<sup>(4)</sup> Difference between TEMP1 and TEMP2 measurement; no calibration necessary.

(5) Temperature drift is -2.1 mV/°C.

# **Electrical Characteristics (continued)**

$T_A = -40$ °C to 85°C,  $V_{DD} = 1.2$  V to 3.6 V (unless otherwise noted).

| PARAMETER                         |                                 | Т                                                             | TEST CONDITIONS                         |                       |             | MAX                   | UNIT |

|-----------------------------------|---------------------------------|---------------------------------------------------------------|-----------------------------------------|-----------------------|-------------|-----------------------|------|

| DIGITAL INPUT AND                 | ОИТРИТ                          |                                                               |                                         |                       |             |                       |      |

| Logic family                      |                                 |                                                               |                                         |                       | CMOS        |                       |      |

|                                   |                                 | 1.2 V ≤ V <sub>DD</sub> < 1.6 V                               |                                         | 0.7 × V <sub>DD</sub> |             | V <sub>DD</sub> + 0.3 | V    |

|                                   | V <sub>IH</sub>                 | 1.6 V ≤ V <sub>DD</sub> ≤ 3.6 V                               |                                         | 0.7 × V <sub>DD</sub> |             | V <sub>DD</sub> + 0.3 | V    |

| Logic level                       |                                 | $1.2 \text{ V} \le \text{V}_{DD} < 1.6 \text{ V}$             |                                         | -0.3                  |             | $0.2 \times V_{DD}$   | V    |

|                                   | V <sub>IL</sub>                 | 1.6 V ≤ V <sub>DD</sub> ≤ 3.6 V                               |                                         | -0.3                  |             | $0.3 \times V_{DD}$   | V    |

|                                   | I <sub>IL</sub>                 | SCL and SDA pins                                              |                                         | -1                    |             | 1                     | μΑ   |

|                                   | C <sub>IN</sub> <sup>(2)</sup>  | SCL and SDA pins                                              |                                         |                       |             | 10                    | pF   |

|                                   | V <sub>OH</sub>                 | I <sub>OH</sub> = 2 TTL loads                                 |                                         | V <sub>DD</sub> - 0.2 |             | $V_{DD}$              | V    |

|                                   | V <sub>OL</sub>                 | I <sub>OL</sub> = 2 TTL loads                                 |                                         | 0                     |             | 0.2                   | V    |

|                                   | I <sub>LEAK</sub>               | Floating output                                               | Floating output                         |                       |             | 1                     | μΑ   |

|                                   | C <sub>OUT</sub> <sup>(2)</sup> | Floating output                                               | Floating output                         |                       |             | 10                    | pF   |

| Data format                       |                                 |                                                               |                                         | Stra                  | ight binary |                       |      |

| POWER-SUPPLY REG                  | QUIREMENTS                      | ·                                                             |                                         |                       |             |                       |      |

|                                   |                                 |                                                               | V <sub>DD</sub> = 1.2 V, 32.56k eq rate |                       | 128         | 190                   | μA   |

|                                   |                                 |                                                               | V <sub>DD</sub> = 1.2 V, 8.2k eq rate   |                       | 32.24       |                       | μΑ   |

| Quiescent supply curre            | ent                             | 12-bit Fast mode                                              | V <sub>DD</sub> = 1.8 V, 34.42k eq rate |                       | 165         | 240                   | μΑ   |

| (V <sub>DD</sub> with sensor off) |                                 | (clock = 400 kHz)<br>PD[1:0] = 0,0                            | V <sub>DD</sub> = 1.8 V, 8.2k eq rate   |                       | 39.31       |                       | μΑ   |

|                                   |                                 |                                                               | V <sub>DD</sub> = 2.7 V, 34.79k eq rate |                       | 226.2       | 335                   | μΑ   |

|                                   |                                 |                                                               | V <sub>DD</sub> = 2.7 V, 8.2k eq rate   |                       | 53.32       |                       | μΑ   |

| Power down supply cu              | rrent                           | Not addressed, SCL =                                          | Not addressed, SCL = SDA = 1            |                       | 0           | 0.8                   | μΑ   |

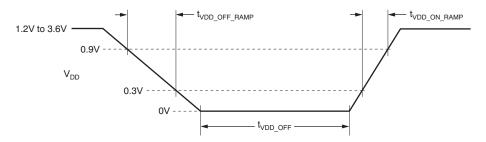

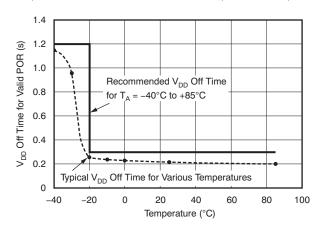

| POWER-ON AND OF                   | SLOPE REQUI                     | REMENTS(2)                                                    |                                         |                       |             | *                     |      |

| V <sub>DD</sub> off ramp          |                                 | $T_A = -40^{\circ}\text{C to } 85^{\circ}\text{C}$            | $T_A = -40$ °C to 85°C                  |                       |             |                       | kV/s |

| V off time                        |                                 | $T_A = -40^{\circ}\text{C to } 85^{\circ}\text{C}, \text{ V}$ | <sub>DD</sub> = 0 V                     | 1.2                   |             |                       | s    |

| V <sub>DD</sub> off time          |                                 | $T_A = -20$ °C to 85°C, V                                     | <sub>DD</sub> = 0 V                     | 0.3                   |             |                       | s    |

| V <sub>DD</sub> on ramp           |                                 | $T_A = -40$ °C to 85°C                                        |                                         | 12                    |             |                       | kV/s |

# 6.6 Timing Requirements: Standard Mode (SCL = 100 kHz)

$T_A = -40$ °C to 85°C,  $V_{DD} = 1.6$  V (unless otherwise noted).

|                      |                                                       |                                             |                                                          | MIN | NOM   | MAX                                                            | UNIT |

|----------------------|-------------------------------------------------------|---------------------------------------------|----------------------------------------------------------|-----|-------|----------------------------------------------------------------|------|

| f <sub>SCL</sub>     | SCL clock frequency                                   |                                             |                                                          | 0   |       | 100                                                            | kHz  |

| t <sub>BUF</sub>     | Bus free time between a STC                           | P and START c                               | ondition                                                 | 4.7 |       |                                                                | μs   |

| t <sub>HD, STA</sub> | Hold time (repeated) START                            | condition                                   |                                                          | 4   |       |                                                                | μs   |

| t <sub>LOW</sub>     | Low period of SCL clock  High period of the SCL clock |                                             |                                                          | 4.7 |       |                                                                | μs   |

| t <sub>HIGH</sub>    | High period of the SCL clock                          |                                             |                                                          | 4   |       |                                                                | μs   |

| t <sub>SU, STA</sub> | Setup time for a repeated ST                          | ART condition                               |                                                          | 4.7 |       |                                                                | μs   |

| t <sub>HD, DAT</sub> | Data hold time                                        |                                             |                                                          | 0   |       | 3.45                                                           | μs   |

| t <sub>SU, DAT</sub> | Data setup time                                       |                                             |                                                          | 250 |       |                                                                | ns   |

| t <sub>R</sub>       | Rise time for both SDA and S (receiving)              | CL signals                                  | C <sub>b</sub> = total bus capacitance                   |     |       | 1000                                                           | ns   |

| 4                    | Fall time for both SDA and                            | Receiving                                   | C <sub>b</sub> = total bus capacitance                   |     |       | 1000<br>300<br>250<br>400<br>434.7<br>570.9<br>2.3 k<br>1.75 k | ns   |

| t <sub>F</sub>       | SCL signals                                           | Transmitting                                | C <sub>b</sub> = total bus capacitance                   |     |       |                                                                | ns   |

| t <sub>SU, STO</sub> | Setup time for STOP conditio                          | n                                           |                                                          | 4   |       |                                                                | μs   |

| C <sub>b</sub>       | Capacitive load for each bus                          | ine                                         | C <sub>b</sub> = total capacitance of one bus line in pF |     |       | 400                                                            | pF   |

|                      | Overla time                                           | 8 bits                                      | 40 SCL + 127 CCLK, V <sub>DD</sub> = 1.8 V               |     | 434.7 |                                                                | μs   |

|                      | Cycle time                                            | 12 bits                                     | 49 SCL + 148 CCLK, V <sub>DD</sub> = 1.8 V               |     | 570.9 |                                                                | μs   |

|                      | Γ#4:4b4                                               | 8 bits                                      | V <sub>DD</sub> = 1.8 V                                  |     | 2.3   |                                                                | kSPS |

|                      | Effective throughput                                  | 12 bits                                     | V <sub>DD</sub> = 1.8 V                                  |     | 1.75  |                                                                | kSPS |

|                      | Equivalent rate = effective                           | fective 8 bits V <sub>DD</sub> = 1.8 V 16.1 |                                                          | kHz |       |                                                                |      |

|                      | throughput × 7                                        | 12 bits                                     | V <sub>DD</sub> = 1.8 V                                  |     | 12.26 |                                                                | kHz  |

# 6.7 Timing Requirements: Fast Mode (SCL = 400 kHz)

All specifications typical at -40°C to 85°C,  $V_{DD}$  = 1.6 V (unless otherwise noted).

|                      |                                                    |               |                                                          | MIN                       | NOM   | MAX | UNIT |

|----------------------|----------------------------------------------------|---------------|----------------------------------------------------------|---------------------------|-------|-----|------|

| f <sub>SCL</sub>     | SCL clock frequency                                |               |                                                          | 0                         |       | 400 | kHz  |

| t <sub>BUF</sub>     | Bus free time between a STC                        | P and START c | ondition                                                 | 1.3                       |       |     | μs   |

| t <sub>HD, STA</sub> | Hold time (repeated) START                         | condition     |                                                          | 0.6                       |       |     | μs   |

| t <sub>LOW</sub>     | Low period of SCL clock                            | 1.3           |                                                          |                           | μs    |     |      |

| t <sub>HIGH</sub>    | High period of the SCL clock                       | 0.6           |                                                          |                           | μs    |     |      |

| t <sub>SU, STA</sub> | Setup time for a repeated ST                       | 0.6           |                                                          |                           | μs    |     |      |

| t <sub>HD, DAT</sub> | Data hold time                                     |               | 0                                                        |                           | 0.9   | μs  |      |

| t <sub>SU, DAT</sub> | Data setup time                                    |               | 100                                                      |                           |       | ns  |      |

| t <sub>R</sub>       | Rise time for both SDA and SCL signals (receiving) |               | C <sub>b</sub> = total bus capacitance                   | 20 + 0.1 × C <sub>b</sub> |       | 300 | ns   |

|                      | Fall time for both SDA and                         | Receiving     | C <sub>b</sub> = total bus capacitance                   | 20 + 0.1 × C <sub>b</sub> |       | 300 | ns   |

| t <sub>F</sub>       | SCL signals                                        | Transmitting  | C <sub>b</sub> = total bus capacitance                   | 20 + 0.1 × C <sub>b</sub> |       | 250 | ns   |

| t <sub>SU, STO</sub> | Setup time for STOP conditio                       | n             |                                                          | 0.6                       |       |     | μs   |

| C <sub>b</sub>       | Capacitive load for each bus                       | line          | C <sub>b</sub> = total capacitance of one bus line in pF |                           |       | 400 | pF   |

|                      | 0 1 6                                              | 8 bits        | 40 SCL + 127 CCLK, V <sub>DD</sub> = 1.8 V               |                           | 134.7 |     | μs   |

|                      | Cycle time                                         | 12 bits       | 49 SCL + 148 CCLK, V <sub>DD</sub> = 1.8 V               |                           | 203.4 |     | μs   |

|                      | F" " 1 1 1 1 1                                     | 8 bits        | V <sub>DD</sub> = 1.8 V                                  |                           | 7.42  |     | kSPS |

| E1                   | Effective throughput                               | 12 bits       | V <sub>DD</sub> = 1.8 V                                  |                           | 4.92  |     | kSPS |

|                      | Equivalent rate = effective                        | 8 bits        | V <sub>DD</sub> = 1.8 V                                  |                           | 51.97 |     | kHz  |

|                      | throughput × 7                                     | 12 bits       | V <sub>DD</sub> = 1.8 V                                  |                           | 34.42 |     | kHz  |

# 6.8 Timing Requirements: High-Speed Mode (SCL = 1.7 MHz)

All specifications typical at  $-40^{\circ}$ C to  $85^{\circ}$ C,  $V_{DD} = 1.6 \text{ V}$  (unless otherwise noted).

|                      |                                             |            |                                                          | MIN | NOM    | MAX | UNIT |

|----------------------|---------------------------------------------|------------|----------------------------------------------------------|-----|--------|-----|------|

| f <sub>SCL</sub>     | SCL clock frequency                         |            |                                                          | 0   |        | 1.7 | MHz  |

| t <sub>HD, STA</sub> | Hold time (repeated) START                  | condition  |                                                          | 160 |        |     | ns   |

| t <sub>LOW</sub>     | Low period of SCL clock                     |            |                                                          | 320 |        |     | ns   |

| t <sub>HIGH</sub>    | High period of the SCL clock                |            |                                                          | 120 |        |     | ns   |

| t <sub>SU, STA</sub> | Setup time for a repeated ST                | 160        |                                                          |     | ns     |     |      |

| t <sub>HD, DAT</sub> | Data hold time                              | 0          |                                                          | 150 | ns     |     |      |

| t <sub>SU, DAT</sub> | Data setup time                             |            | 10                                                       |     |        | ns  |      |

|                      | Rise time for a signal                      | SCL        | C <sub>b</sub> = total bus capacitance                   | 20  |        | 80  | ns   |

| t <sub>R</sub>       | (receiving)                                 | SDA        | C <sub>b</sub> = total bus capacitance                   | 20  |        | 160 | ns   |

|                      | Fall time for a signal                      | SCL        | C <sub>b</sub> = total bus capacitance                   | 20  |        | 80  | ns   |

| t <sub>F</sub>       | (receiving)                                 | SDA        | C <sub>b</sub> = total bus capacitance                   | 20  |        | 160 | ns   |

| t <sub>F</sub>       | Fall time for both SDA and S (transmitting) | CL signals | C <sub>b</sub> = total bus capacitance                   | 20  |        | 160 | ns   |

| t <sub>SU, STO</sub> | Setup time for STOP condition               | n          |                                                          | 160 |        |     | ns   |

| C <sub>b</sub>       | Capacitive load for each bus                | line       | C <sub>b</sub> = total capacitance of one bus line in pF |     |        | 400 | pF   |

|                      | 0 1 "                                       | 8 bits     | 40 SCL + 127 CCLK, V <sub>DD</sub> = 1.8 V               |     | 58.2   |     | μs   |

|                      | Cycle time                                  | 12 bits    | 49 SCL + 148 CCLK, V <sub>DD</sub> = 1.8 V               |     | 109.7  |     | μs   |

|                      | F" ( ) ( )                                  | 8 bits     | V <sub>DD</sub> = 1.8 V                                  |     | 17.17  |     | kSPS |

|                      | Effective throughput                        | 12 bits    | V <sub>DD</sub> = 1.8 V                                  |     | 9.12   |     | kSPS |

|                      | Equivalent rate = effective                 | 8 bits     | V <sub>DD</sub> = 1.8 V                                  |     | 120.22 |     | kHz  |

|                      | throughput × 7                              | 12 bits    | V <sub>DD</sub> = 1.8 V                                  |     | 63.81  |     | kHz  |

# 6.9 Timing Requirements: High-Speed Mode (SCL = 3.4 MHz)

All specifications typical at -40°C to 85°C,  $V_{DD}$  = 1.6 V (unless otherwise noted).

|                                                   |                                  |                                           |                                                          | MIN   | NOM    | MAX | UNIT |

|---------------------------------------------------|----------------------------------|-------------------------------------------|----------------------------------------------------------|-------|--------|-----|------|

| f <sub>SCL</sub>                                  | SCL clock frequency              |                                           |                                                          | 0     |        | 3.4 | MHz  |

| t <sub>HD, STA</sub>                              | Hold time (repeated) START       | condition                                 |                                                          | 160   |        |     | ns   |

| t <sub>LOW</sub>                                  | Low period of SCL clock          |                                           |                                                          | 160   |        |     | ns   |

| t <sub>HIGH</sub>                                 | High period of the SCL clock     |                                           |                                                          | 60    |        |     | ns   |

| t <sub>SU, STA</sub>                              | Setup time for a repeated ST     | Setup time for a repeated START condition |                                                          |       |        |     | ns   |

| t <sub>HD, DAT</sub>                              | Data hold time                   | 0                                         |                                                          | 70    | ns     |     |      |

| t <sub>SU, DAT</sub>                              | Data setup time                  | 10                                        |                                                          |       | ns     |     |      |

| t <sub>R</sub> Rise time for a signal (receiving) | Rise time for a signal           | SCL                                       | C <sub>b</sub> = total bus capacitance                   | 10    |        | 40  | ns   |

|                                                   | (receiving)                      | SDA                                       | C <sub>b</sub> = total bus capacitance                   | 10    |        | 80  | ns   |

|                                                   | Fall time for a signal           | SCL                                       | C <sub>b</sub> = total bus capacitance                   | 10    |        | 40  | ns   |

| t <sub>F</sub>                                    | (receiving)                      | SDA                                       | C <sub>b</sub> = total bus capacitance                   | 10    |        | 80  | ns   |

| t <sub>F</sub>                                    | Fall time for both SDA and South | CL signals                                | C <sub>b</sub> = total bus capacitance                   | 10    |        | 80  | ns   |

| t <sub>SU, STO</sub>                              | Setup time for STOP condition    | n                                         | •                                                        | 160   |        |     | ns   |

| C <sub>b</sub>                                    | Capacitive load for each bus     | line                                      | C <sub>b</sub> = total capacitance of one bus line in pF |       |        | 100 | pF   |

|                                                   | Overlanding                      | 8 bits                                    | 40 SCL + 127 CCLK, V <sub>DD</sub> = 1.8 V               |       | 46.5   |     | μs   |

|                                                   | Cycle time                       | 12 bits                                   | 49 SCL + 148 CCLK, V <sub>DD</sub> = 1.8 V               |       | 95.3   |     | μs   |

|                                                   | F# 6 4 1 1                       | 8 bits                                    | V <sub>DD</sub> = 1.8 V                                  | 21.52 |        |     | kSPS |

| Effective throughput                              |                                  | 12 bits                                   | V <sub>DD</sub> = 1.8 V                                  | 10.49 |        |     | kSPS |

|                                                   | Equivalent rate = effective      | 8 bits                                    | V <sub>DD</sub> = 1.8 V                                  |       | 150.65 |     | kHz  |

|                                                   | throughput × 7                   | 12 bits                                   | V <sub>DD</sub> = 1.8 V                                  |       | 73.46  |     | kHz  |

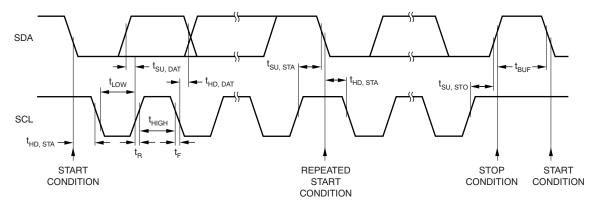

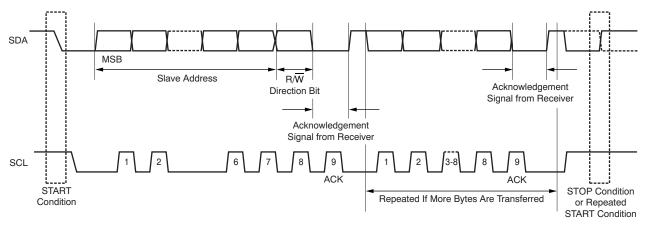

Figure 1. Detailed I/O Timing

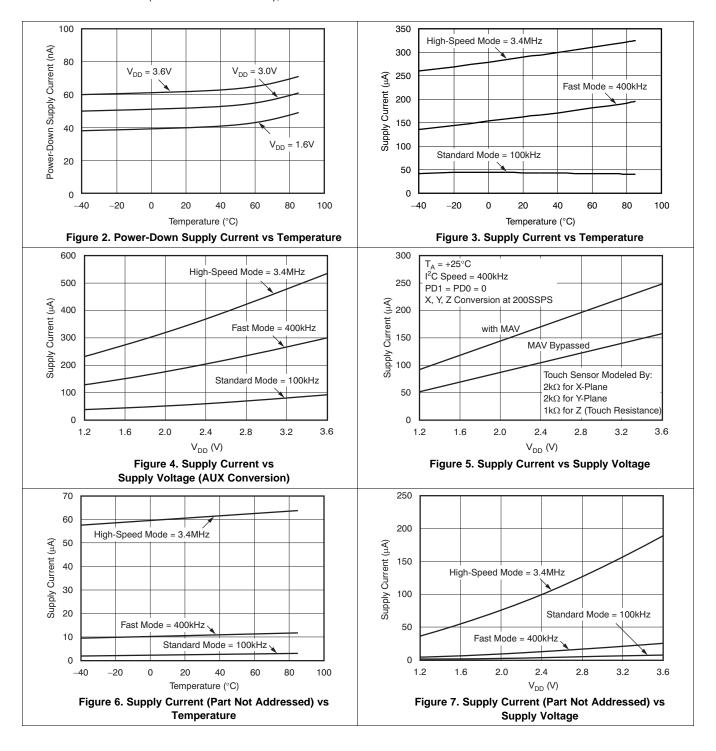

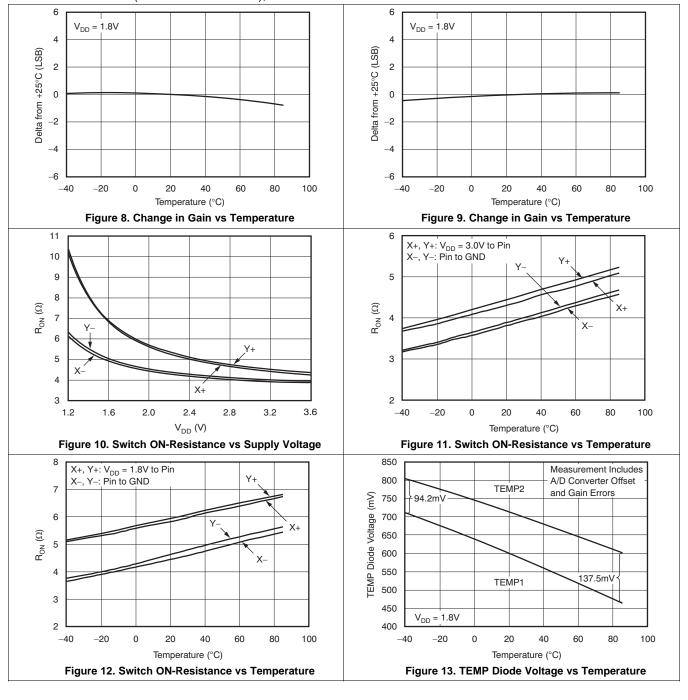

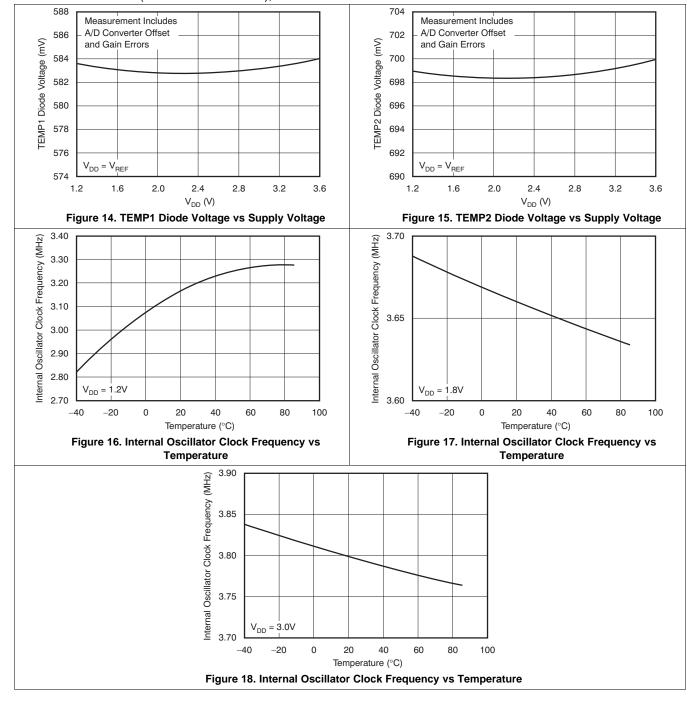

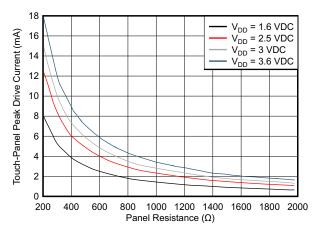

# 6.10 Typical Characteristics

At  $T_A = -40$ °C to 85°C,  $V_{DD} = 1.2$  V to 3.6 V, PD1 = PD0 = 0, Fast mode, 12-bit mode, non-continuous AUX measurement, and MAV filter enabled (see *MAV Filter* section), unless otherwise noted.

# **Typical Characteristics (continued)**

At  $T_A = -40$ °C to 85°C,  $V_{DD} = 1.2$  V to 3.6 V, PD1 = PD0 = 0, Fast mode, 12-bit mode, non-continuous AUX measurement, and MAV filter enabled (see *MAV Filter* section), unless otherwise noted.

# **Typical Characteristics (continued)**

At  $T_A = -40$ °C to 85°C,  $V_{DD} = 1.2$  V to 3.6 V, PD1 = PD0 = 0, Fast mode, 12-bit mode, non-continuous AUX measurement, and MAV filter enabled (see *MAV Filter* section), unless otherwise noted.

## 7 Detailed Description

#### 7.1 Overview

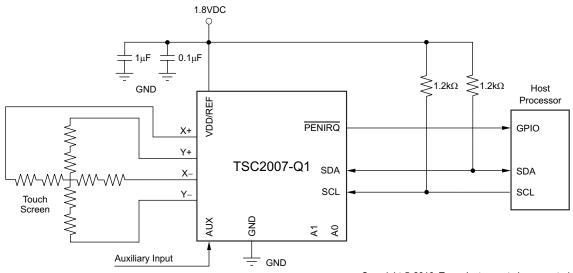

The TSC2007-Q1 is an analog interface circuit for a human interface touch screen devices. All peripheral functions are controlled through the command byte and onboard state machines. The TSC2007-Q1 features include:

- Very low-power touch screen controller

- Very small onboard footprint

- Relieves host from tedious routine tasks by preprocessing, thus saving resources for more critical tasks

- · Ability to work on very low supply voltage

- Minimal connection interface allows easy isolation and reduces the number of dedicated I/O pins required

- Miniature, yet complete; requires no external supporting components

- Enhanced electrostatic discharge (ESD) protection

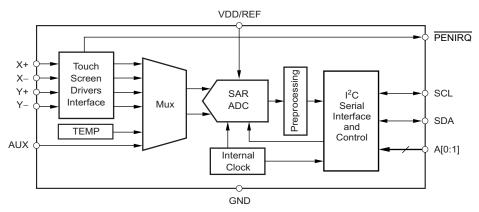

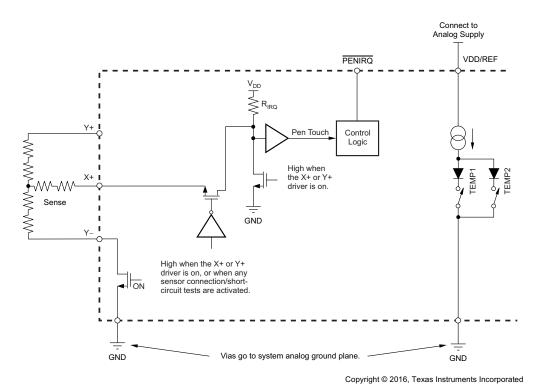

The TSC2007-Q1 consists of the following blocks (see Functional Block Diagram):

- Touch Screen Sensor Interface

- Auxiliary Input (AUX)

- Temperature Sensor

- · Acquisition Activity Preprocessing

- Internal Conversion Clock

- I<sup>2</sup>C Interface

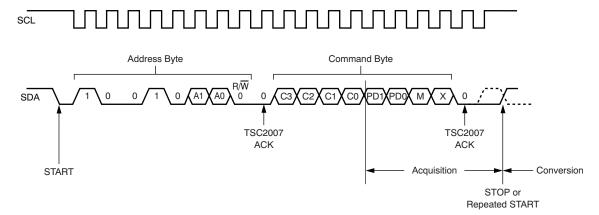

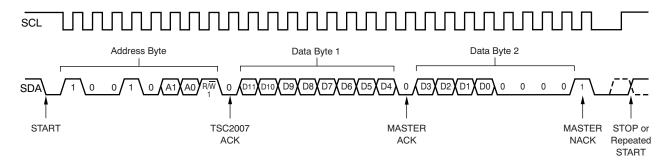

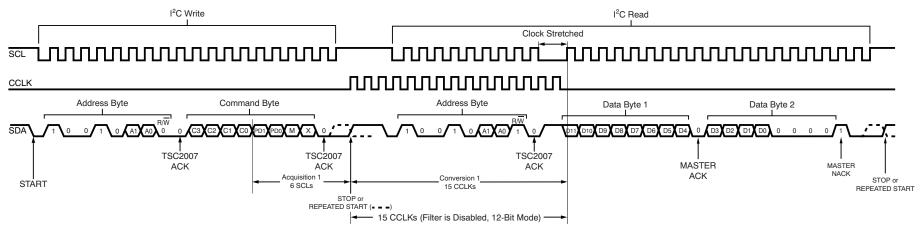

Communication with the TSC2007-Q1 is done through an I<sup>2</sup>C serial interface. The TSC2007-Q1 is an I<sup>2</sup>C slave device; therefore, data are shifted into or out of the TSC2007-Q1 under control of the host microprocessor, which also provides the serial data clock.

Control of the TSC2007-Q1 and its functions is accomplished by writing to the command register of an internal state machine. A simple command protocol compatible with I<sup>2</sup>C is used to address this register.

## 7.2 Functional Block Diagram

Copyright © 2016, Texas Instruments Incorporated

#### 7.3 Feature Description

# 7.3.1 Touch Screen Operation

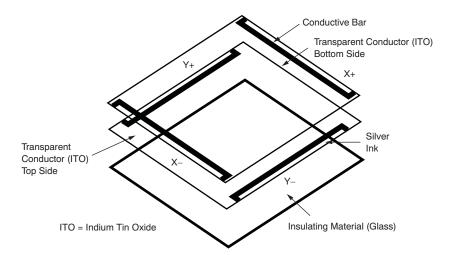

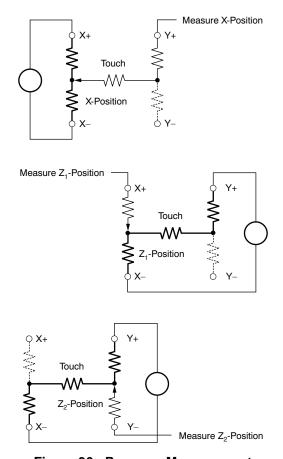

A resistive touch screen operates by applying a voltage across a resistor network and measuring the change in resistance at a given point on the matrix where the screen is touched by an input (stylus, pen, or finger). The change in the resistance ratio marks the location on the touch screen.

The TSC2007-Q1 supports resistive 4-wire configurations, as shown in Figure 35. The circuit determines location in two coordinate pair dimensions, although a third dimension can be added for measuring pressure.

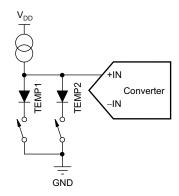

#### 7.3.2 Internal Temperature Sensor

In some applications, such as battery recharging, an ambient temperature measurement is required. The temperature measurement technique used in the TSC2007-Q1 relies on the characteristics of a semiconductor junction operating at a fixed current level. The forward diode voltage ( $V_{BE}$ ) has a well-defined characteristic versus temperature. The ambient temperature can be predicted in applications by knowing the 25°C value of the  $V_{BE}$  voltage and then monitoring the delta of that voltage as the temperature changes.

The TSC2007-Q1 offers two modes of temperature measurement. The first mode requires calibration at a known temperature, but only requires a single reading to predict the ambient temperature. The TEMP1 diode, shown in Figure 19, is used during this measurement cycle. This voltage is typically 580 mV at 25°C with a 10- $\mu$ A current. The absolute value of this diode voltage can vary by a few millivolts; the temperature coefficient ( $T_C$ ) of this voltage is very consistent at -2.1 mV/°C. During the final test of the end product, the diode voltage would be stored at a known room temperature, in system memory, for calibration purposes by the user. The result is an equivalent temperature measurement resolution of 0.35°C/LSB (1 LSB = 732  $\mu$ V with  $V_{REF}$  = 3 V).

Copyright © 2016, Texas Instruments Incorporated

Figure 19. Functional Block Diagram of Temperature Measurement Mode

The second mode does not require a test temperature calibration, but uses a two-measurement (differential) method to eliminate the need for absolute temperature calibration and for achieving 2°C/LSB accuracy. This mode requires a second conversion of the voltage across the TEMP2 diode with a resistance 91 times larger than the TEMP1 diode. The voltage difference between the first (TEMP1) and second (TEMP2) conversion is represented by:

$$\Delta V = \frac{kT}{q} \times ln(N)$$

where

- N = the resistance ratio = 91.

- $k = Boltzmann's constant = 1.3807 \times 10^{-23} J/K (joules per kelvins).$

- q = the electron charge =  $1.6022 \times 10^{-19}$  C (coulombs).

- T = the temperature in kelvins (K).

This method can provide a much improved absolute temperature measurement, but a lower resolution of 1.6°C/LSB. Equation 2 solves for T:

$$T = \frac{q \times \Delta V}{k \times ln(N)}$$

where

•

$$\Delta V = V_{BE} (TEMP2) - V_{BE} (TEMP1) (in mV)$$

(2)

$T = 2.573 \times \Delta V \text{ (in K)}$

or T =

$$2.573 \times \Delta V - 273$$

(in °C)

(1)

Temperature 1 and temperature 2 measurements have the same timing as the other data acquisition cycles shown in Figure 32 and Figure 33.

## 7.3.3 Analog-to-Digital Converter

Figure 20 shows the analog inputs of the TSC2007-Q1. The analog inputs (X, Y, and Z touch panel coordinates, chip temperature and auxiliary inputs) are provided through a multiplexer to the Successive Approximation Register (SAR) A-D converter. The A-D architecture is based on capacitive redistribution architecture, which inherently includes a sample-and-hold function.

Copyright © 2016, Texas Instruments Incorporated

Figure 20. Analog Input Section (Simplified Diagram)

A unique configuration of low ON-resistance switches allows an unselected A-D converter input channel to provide power and an accompanying pin to provide ground for driving the touch panel. By maintaining a differential input to the converter and a differential reference input architecture, it is possible to negate errors caused by the driver switch ON-resistance.

#### 7.3.3.1 Reference

The TSC2007-Q1 uses an external voltage reference that is applied to the VDD/REF pin. The upper reference voltage range is the same as the supply voltage range, which allows for simple, 1.2-V to 3.6-V, single-supply operation of the chip.

#### 7.3.3.2 Reference Mode

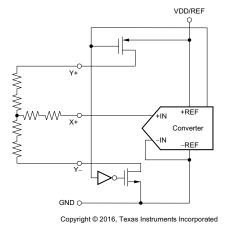

There is a critical item regarding the reference when making measurements while the switch drivers are on. For this discussion, it is useful to consider the basic operation of the TSC2007-Q1 (see Figure 34). The application used in the following example shows the device being used to digitize a resistive touch screen. If the touch screen controller uses a single-ended reference mode, as shown in Figure 21, a measurement of the current Y position of the pointing device is made by connecting the X+ input to the A-D converter, turning on the Y+ and Y-drivers, and digitizing the voltage on X+. For this measurement, the resistance in the X+ lead does not affect the conversion; it does affect the settling time, but the resistance is usually small enough that this timing is not a concern. However, because the resistance between Y+ and Y- is fairly low, the ON-resistance of the Y drivers does make a small difference. Under the situation outlined so far, it would not be possible to achieve a 0-V input or a full-scale input regardless of where the pointing device is on the touch screen because some voltage is lost across the internal switches. In addition, the internal switch resistance is unlikely to track the resistance of the touch screen, providing an additional source of error. Therefore, the TSC2007-Q1 does not support single-ended reference mode.

Figure 21. Simplified Diagram of Single-Ended Reference

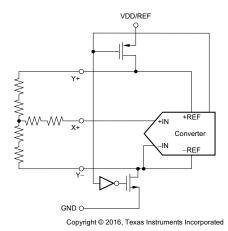

This situation is resolved, as shown in Figure 22, by using the differential mode; the +REF and -REF inputs are connected directly to Y+ and Y-, respectively. This mode makes the A-D converter ratiometric. The result of the conversion is always a percentage of the external reference, regardless of how it changes in relation to the ON-resistance of the internal switches.

Figure 22. Simplified Diagram of Differential Reference (Both Y Switches Enabled, X+ is Analog Input)

## 7.3.3.3 Touch Screen Settling

In some applications, external capacitors may be required across the touch screen to filter noise picked up by the touch screen (noise generated by the LCD panel or back-light circuitry). These capacitors provide a low-pass filter to reduce the noise, but they also cause a settling time requirement when the panel is touched. The settling time typically shows up as a gain error. The problem is that the input or reference has not settled to its final steady-state value before the A-D converter samples the inputs and provides the digital output. Additionally, the reference voltage may continue to change during the measurement cycle.

To resolve these settling-time problems, the TSC2007-Q1 can be commanded to turn on the drivers only without performing a conversion (see Table 4). Time can then be allowed, before the command is issued, to perform a conversion. Generally, the time it takes to communicate the conversion command over the I<sup>2</sup>C bus is adequate for the touch screen to settle.

#### 7.3.3.4 Variable Resolution

The TSC2007-Q1 provides either 8-bit or 12-bit resolution for the A-D converter. Lower resolution is often practical for measuring slow changing signals such as touch pressure. Performing the conversions at lower resolution reduces the amount of time it takes for the A-D converter to complete its conversion process, which also lowers power consumption.

#### 7.3.3.5 8-Bit Conversion

The TSC2007-Q1 provides an 8-bit conversion mode (M = 1) that can be used when faster throughput is required, and the digital result is not as critical (for example, measuring pressure). By switching to the 8-bit mode, a conversion result can be read by transferring only one data byte. The internal clock runs twice as fast at 4 MHz.

The faster clock shortens each conversion by four bits and reduces data transfer time, which results in fewer clock cycles and provides lower power consumption.

#### 7.3.3.6 Conversion Clock and Conversion Time

The TSC2007-Q1 contains an internal clock, which drives the state machines inside the device that perform the many functions of the part. This clock is divided down to provide a clock that runs the A-D converter. The frequency of this clock is 4-MHz clock for 8-bit mode, and a 2-MHz clock for the 12-bit mode.

#### 7.3.3.7 Data Format

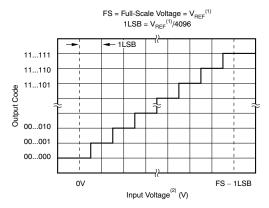

The TSC2007-Q1 output data are in straight binary format as shown in Figure 23. This figure shows the ideal output code for the given input voltage and does not include the effects of offset, gain, or noise.

- (1) Reference voltage at converter: +REF (–REF). See Figure 20.

- (2) Input voltage at converter, after multiplexer: +IN (-IN). See Figure 20.

Figure 23. Ideal Input Voltages and Output Codes

#### 7.3.3.8 Touch Detect