🕳 Order

Now

ZHCSBG1B-JULY 2013-REVISED APRIL 2018

# 采用 QFN 封装且具有 2.95V-6V 输入的 LMZ30606 6A 电源模块

## 1 特性

- 完整的集成式电源解决方案可实现 小尺寸和扁平设计

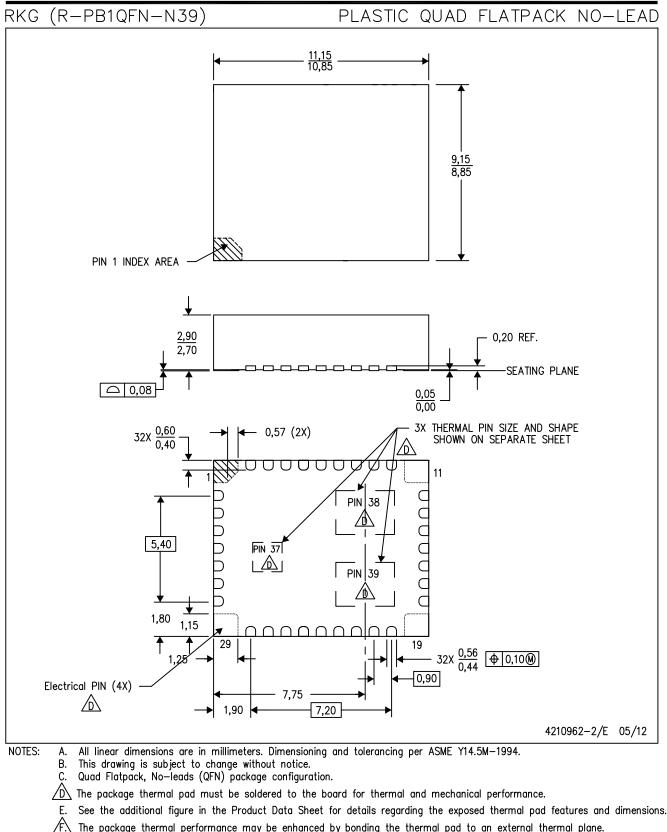

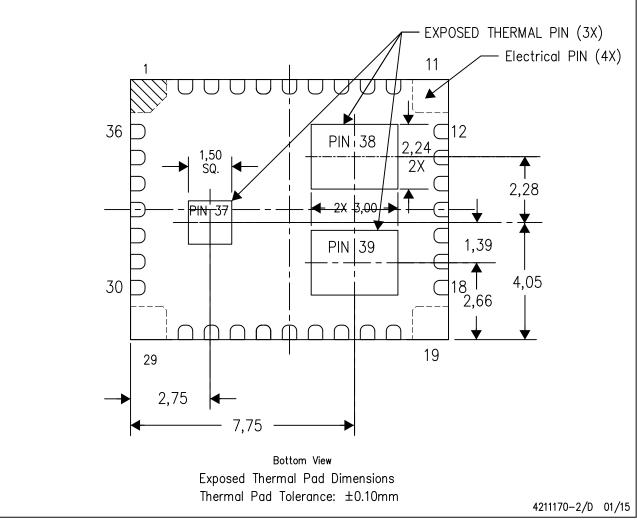

- 9mm x 11mm x 2.8mm 封装

与 LMZ30602 & LMZ30604 引脚兼容

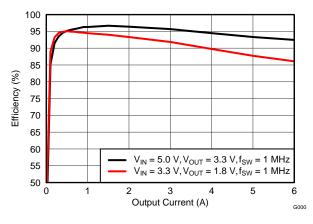

- 效率高达 96%

Texas

INSTRUMENTS

- 宽输出电压调节范围

0.8V 至 3.6V,基准精度为 ±1%

- 可调开关频率 (500kHz 至 2MHz)

- 与外部时钟同步

- 可调慢速启动

- 输出电压排序/跟踪

- 电源正常输出

- 可编程欠压锁定 (UVLO)

- 输出过流保护

- 过热保护

- 运行温度范围: -40℃ 至 85℃

- 增强的散热性能: 12°C/W

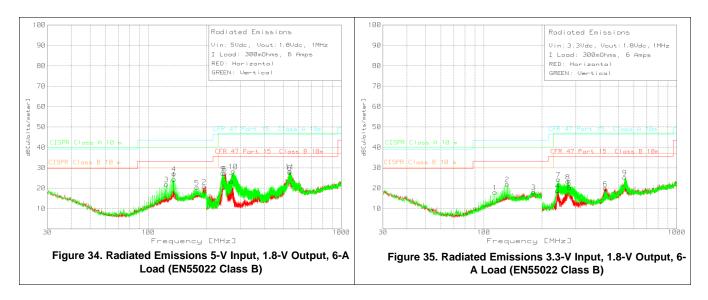

- 符合 EN55022 B 类辐射标准 - 集成屏蔽电感器

- 使用 LMZ30606 并借助 WEBENCH<sup>®</sup> 电源设计器 创建定制设计方案

## 2 应用

- 宽带和通信基础设施

- 自动化测试和医疗设备

- 紧凑型 PCI/PCI 快速接口/PXI 快速接口

- DSP 和 FPGA 负载点 应用

- 高密度分布式电源系统

## 3 说明

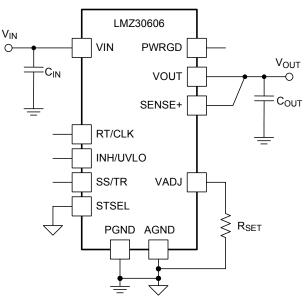

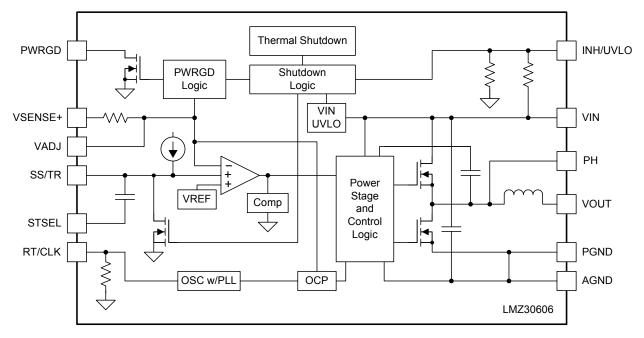

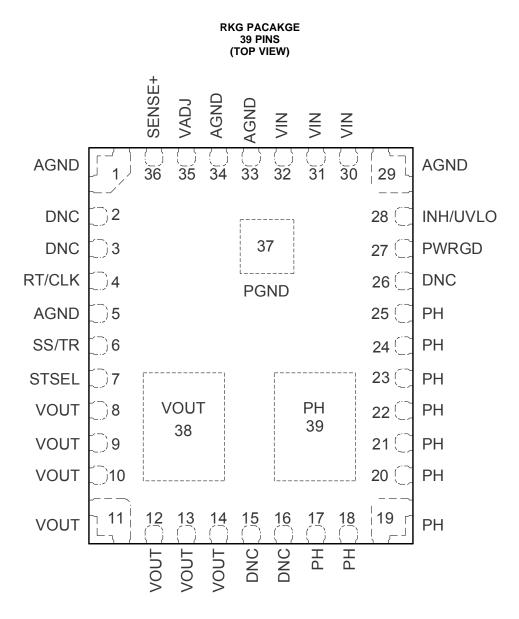

LMZ30606 SIMPLE SWITCHER® 电源模块是一款易 于使用的集成式电源解决方案,此方案在一半高的 QFN 封装内组合了一个带有功率金属氧化物半导体场 效应管 (MOSFET) 的 6A 直流/直流转换器、一个屏蔽 电感器以及无源元件。此整体电源解决方案仅需 3 个 外部组件,并省去了环路补偿和磁性元件选择过程。

9mm × 11mm × 2.8 mm QFN 封装能轻松焊接到印刷 电路板上,并且可实现效率高于 90% 的紧凑型负载点 设计以及结至环境的热阻抗仅为 12°C/W 的出色功率 耗散。在环境温度为 85°C 且无气流的情况下,该器件 可提供 6A 的满额输出电流。

LMZ30606 提供了分离式负载点设计的灵活性和功能 集,非常适合为高性能 DSP 和 FPGA 供电。先进的封 装技术可提供一个与标准 QFN 贴装和测试技术兼容的 耐用且可靠的电源解决方案。

53

简化应用

TEXAS INSTRUMENTS

www.ti.com.cn

## Table 1. Ordering Information

For the most current package and ordering information, see the Package Option Addendum at the end of this datasheet, or see the TI website at www.ti.com.

## 4 Specifications

## 4.1 Absolute Maximum Ratings<sup>(1)</sup>

over operating temperature range (unless otherwise noted)

|                                          |                        |                  |          |                              | Ņ    | VALUE              | UNIT |

|------------------------------------------|------------------------|------------------|----------|------------------------------|------|--------------------|------|

|                                          |                        |                  |          |                              | MIN  | MAX                | UNIT |

|                                          |                        | VIN, PWRGD       |          |                              | -0.3 | 7                  | V    |

| lanut Valtana                            |                        | INH/UVLO, RT/    | /CLK     |                              | -0.3 | 3.3                | V    |

| Input Voltage                            |                        | SS/TR, STSEL,    | , VAD    | J                            | -0.3 | 3                  | V    |

|                                          |                        | SENSE+           | ,        | VADJ rating must also be met | -0.3 | V <sub>OUT</sub>   | V    |

|                                          |                        | PH               |          |                              | -0.6 | 7                  | V    |

| Output Voltage                           |                        | PH 10 ns, trans  | sient    |                              | -2   | 7                  | V    |

|                                          |                        | VOUT             |          |                              | -0.6 | VIN                | V    |

| V <sub>DIFF</sub> (GND to exposed therma | l pad)                 |                  |          |                              | -0.2 | 0.2                | V    |

|                                          |                        | RT/CLK, INH/UVLO |          |                              | ±100 | μA                 |      |

| Source Current                           |                        | PH               |          |                              |      | Current Limit      | А    |

|                                          |                        | PH               |          |                              |      | Current Limit      | А    |

| Sink Current                             |                        | SS/TR            |          |                              |      | ±100               | μA   |

|                                          |                        | PWRGD            |          |                              |      | 10                 | mA   |

| Operating Junction Temperatur            | re                     |                  |          |                              | -40  | 125 <sup>(2)</sup> | °C   |

| Storage Temperature, T <sub>stg</sub>    |                        |                  |          |                              | -65  | 150                | °C   |

| Peak Reflow Case Temperatur              | e <sup>(3)</sup>       |                  |          |                              |      | 250 <sup>(4)</sup> | °C   |

| Maximum Number of Reflows                | Allowed <sup>(3)</sup> |                  |          |                              |      | 3 <sup>(4)</sup>   |      |

| Mechanical Shock                         | Mil-STD-883D           | , Method 2002.3, | 8, 1 mse | ec, 1/2 sine, mounted        |      | 1500               | 0    |

| Mechanical Vibration                     | Mil-STD-883D           | , Method 2007.2, | 2, 20-20 | 000Hz                        |      | 20                 | G    |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) See the temperature derating curves in the Typical Characteristics section for thermal information.

(3) For soldering specifications, refer to the Soldering Requirements for BQFN Packages application note.

(4) Devices with a date code prior to week 14 2018 (1814) have a peak reflow case temperature of 240°C with a maximum of one reflow.

## 4.2 Thermal Information

|               |                                                             | LMZ30606 |      |

|---------------|-------------------------------------------------------------|----------|------|

|               | THERMAL METRIC <sup>(1)</sup>                               | RKG39    | UNIT |

|               |                                                             | 39 PINS  |      |

| $\theta_{JA}$ | Junction-to-ambient thermal resistance <sup>(2)</sup>       | 12       |      |

| ΨJT           | Junction-to-top characterization parameter <sup>(3)</sup>   | 2.2      | °C/W |

| ΨJB           | Junction-to-board characterization parameter <sup>(4)</sup> | 9.7      |      |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics (SPRA953) application report.

(2) The junction-to-ambient thermal resistance,  $\theta_{JA}$ , applies to devices soldered directly to a 100 mm x 100 mm double-sided PCB with 1 oz. copper and natural convection cooling. Additional airflow reduces  $\theta_{JA}$ .

(3) The junction-to-top characterization parameter, ψ<sub>JT</sub>, estimates the junction temperature, T<sub>J</sub>, of a device in a real system, using a procedure described in JESD51-2A (sections 6 and 7). T<sub>J</sub> = ψ<sub>JT</sub> \* Pdis + T<sub>T</sub>; where Pdis is the power dissipated in the device and T<sub>T</sub> is the temperature of the top of the device.

(4) The junction-to-board characterization parameter, ψ<sub>JB</sub>, estimates the junction temperature, T<sub>J</sub>, of a device in a real system, using a procedure described in JESD51-2A (sections 6 and 7). T<sub>J</sub> = ψ<sub>JB</sub> \* Pdis + T<sub>B</sub>; where Pdis is the power dissipated in the device and T<sub>B</sub> is the temperature of the board 1mm from the device.

## 4.3 Electrical Characteristics

Over -40°C to 85°C free-air temperature, VIN = 3.3 V,  $V_{OUT}$  = 1.8 V,  $I_{OUT}$  = 6A,  $C_{IN1}$  = 47 µF ceramic,  $C_{IN2}$  = 220 µF poly-tantalum,  $C_{OUT1}$  = 47 µF ceramic,  $C_{OUT2}$  = 100 µF poly-tantalum (unless otherwise noted)

|                       | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                  | Т                                                                                                                                                                                       | EST CONDITIONS                                        |                                     | MIN                 | TYP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | MAX                        | UNIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I <sub>OUT</sub>      | Output current                                                                                                                                                                                                                                                                                                                                                                             | $T_A = 85^{\circ}C$ , natural convec                                                                                                                                                    | tion                                                  |                                     | 0                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6                          | А                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| V <sub>IN</sub>       | Input voltage range                                                                                                                                                                                                                                                                                                                                                                        | Over I <sub>OUT</sub> range                                                                                                                                                             |                                                       |                                     | 2.95 <sup>(1)</sup> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6                          | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| UVLO                  | VIN Lindenvoltage leekeut                                                                                                                                                                                                                                                                                                                                                                  | VIN = increasing                                                                                                                                                                        |                                                       |                                     |                     | 3.05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3.135                      | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| UVLO                  | vin Ondervollage lockoul                                                                                                                                                                                                                                                                                                                                                                   | VIN = decreasing                                                                                                                                                                        |                                                       |                                     | 2.5                 | 2.75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            | v                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| V <sub>OUT(adj)</sub> | Output voltage adjust range                                                                                                                                                                                                                                                                                                                                                                | Over I <sub>OUT</sub> range                                                                                                                                                             |                                                       |                                     | 0.8                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3.6                        | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                       | Set-point voltage tolerance                                                                                                                                                                                                                                                                                                                                                                | $T_A = 25^{\circ}C$ , $I_{OUT} = 0A$                                                                                                                                                    |                                                       |                                     |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $\pm 1.0\%$ <sup>(2)</sup> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                       | Temperature variation                                                                                                                                                                                                                                                                                                                                                                      | -40°C $\leq$ T <sub>A</sub> $\leq$ +85°C, I <sub>OUT</sub> :                                                                                                                            | = 0A                                                  |                                     |                     | ±0.3%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| V <sub>OUT</sub>      | Line regulation                                                                                                                                                                                                                                                                                                                                                                            | Over VIN range, T <sub>A</sub> = 25°0                                                                                                                                                   | C, I <sub>OUT</sub> = 0A                              |                                     |                     | ±0.1%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                       | Input voltage range ID VIN Undervoltage lockout UIN Undervoltage lockout UIN Undervoltage adjust range Set-point voltage tolerance Temperature variation Line regulation Load regulation Total output voltage variation Efficiency  Output voltage ripple Overcurrent threshold Transient response HHH HL Inhibit Control HHH Ny) Input standby current PWRGD Thresholds PWRGD Low Voltage | Over I <sub>OUT</sub> range, T <sub>A</sub> = 25°                                                                                                                                       | С                                                     |                                     |                     | ±0.1%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                       | Total output voltage variation                                                                                                                                                                                                                                                                                                                                                             | Includes set-point, line, loa                                                                                                                                                           | ad, and temperature va                                | riation                             |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ±1.5% <sup>(2)</sup>       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

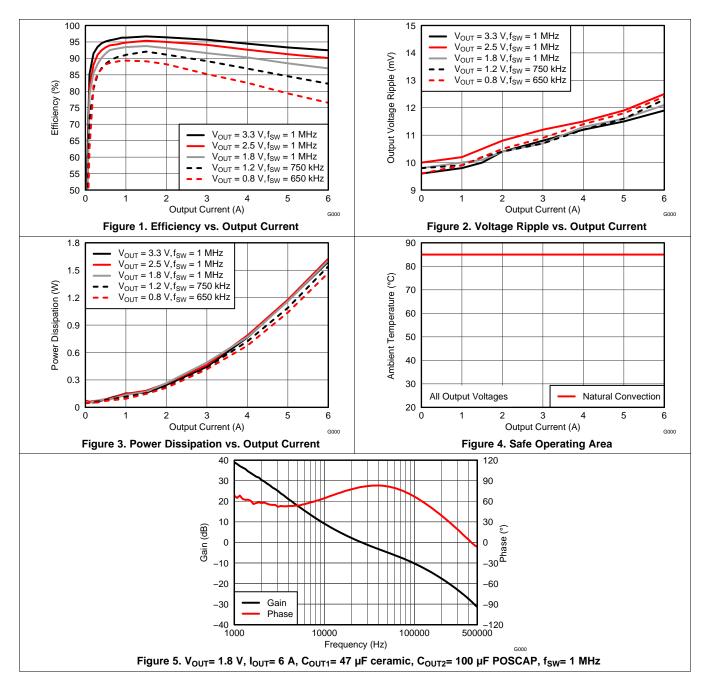

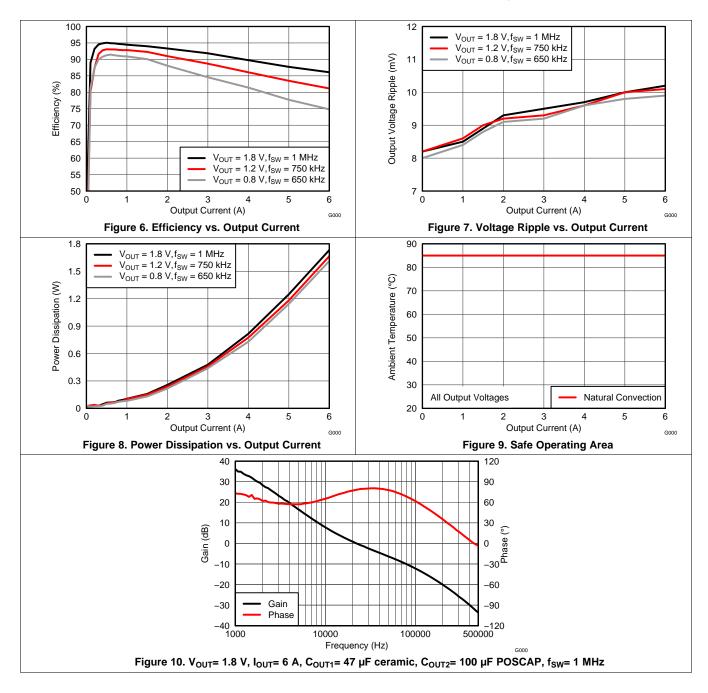

|                       |                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                         | V <sub>OU</sub>                                       | = 3.3V, f <sub>SW</sub> = 1 MHz     |                     | 96%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                       |                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                         | V <sub>OU</sub> .                                     | = 2.5V, f <sub>SW</sub> = 1 MHz     |                     | 94%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                       |                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                         | V <sub>OU</sub> .                                     | = 1.8V, f <sub>SW</sub> = 1 MHz     |                     | 92%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                       |                                                                                                                                                                                                                                                                                                                                                                                            | VIN = 5 V<br>I <sub>O</sub> = 3 A                                                                                                                                                       | V <sub>OU</sub> .                                     | = 1.5V, f <sub>SW</sub> = 1 MHz     |                     | 90%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            | λ       A         λ       V         λ       V         λ       V         λ       V         λ       V         λ       V         λ       V         λ       V         λ       V         λ       V         λ       V         λ       V         λ       V         λ       V         λ       MVPP         Α       μs         mV       V         λ       V         λ       V         λ       KHz         λ       V         λ       KHz         λ       V                                                                                                                                                                                                              |

|                       |                                                                                                                                                                                                                                                                                                                                                                                            | 10 = 3 A                                                                                                                                                                                | V <sub>OUT</sub>                                      | = 1.2V, f <sub>SW</sub> =750 kHz    |                     | 0         6           (1)         6           3.05         3.135           2.5         2.75           2.8         3.6 $\pm 0.3\%$ $\pm 1.0\%$ (2) $\pm 0.3\%$ $\pm 1.0\%$ (2) $\pm 0.1\%$ $\pm 1.5\%$ (2)           96%         92%           90%         89%           92%         90%           85%         92%           90%         85%           85%         10           85%         10           90%         89%           85%         10           9         3           100         9           85%         10           10         100           93%         1.00           93%         1.00           93%         0.3           100%         91%           91%         0.3           100%         2000           22         3.3           0.3         0.4 |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                       |                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                         | V <sub>OUT</sub> :                                    | = 1.0V, f <sub>SW</sub> = 650 kHz   |                     | 87%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            | A           V           V           V           V           V           M           M           M           M           M           M           M           M           M           M           M           M           M           M           M           M           M           M           M           M           M           M           M           M           M           M           M           M           M           M           M           M           M           M           M           M           M           M           M           M           V           M           K           V           N           N           N           N |

| η                     | Efficiency                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                         | V <sub>OUT</sub> :                                    | = 0.8V, f <sub>SW</sub> = 650 kHz   |                     | 85%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                       |                                                                                                                                                                                                                                                                                                                                                                                            | VIN = 3.3V                                                                                                                                                                              | V <sub>OUT</sub> = 1.8V, f <sub>SW</sub> = 1 MHz      |                                     |                     | 92%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                       |                                                                                                                                                                                                                                                                                                                                                                                            | I <sub>O</sub> = 3 A                                                                                                                                                                    | V <sub>OU</sub> .                                     | = 1.5V, f <sub>SW</sub> = 1 MHz     |                     | 90%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                       |                                                                                                                                                                                                                                                                                                                                                                                            | $I_{O} = 3 \text{ A}$ $V_{OUT} = 1.5V, f_{SW} = 1 \text{ M}$ $V_{OUT} = 1.2V, f_{SW} = 750 \text{ k}$ $V_{OUT} = 1.0V, f_{SW} = 650 \text{ k}$ $V_{OUT} = 0.8V, f_{SW} = 650 \text{ k}$ | = 1.2V, f <sub>SW</sub> = 750 kHz                     |                                     | 89%                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                       |                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                         | V <sub>OUT</sub> :                                    | = 1.0V, f <sub>SW</sub> = 650 kHz   |                     | 87%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                       |                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                         |                                                       |                                     |                     | 85%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            | A<br>V<br>V<br>V<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                       | Output voltage ripple                                                                                                                                                                                                                                                                                                                                                                      | 20 MHz bandwith                                                                                                                                                                         |                                                       | -                                   |                     | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                            | mV <sub>PP</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| I <sub>LIM</sub>      | Overcurrent threshold                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                         |                                                       |                                     |                     | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                            | А                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                       |                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                         |                                                       | Recovery time                       |                     | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                            | μs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

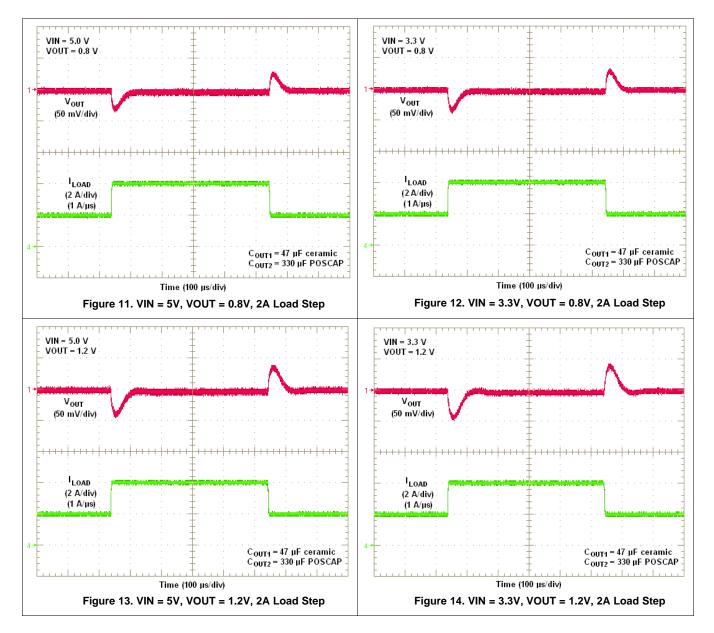

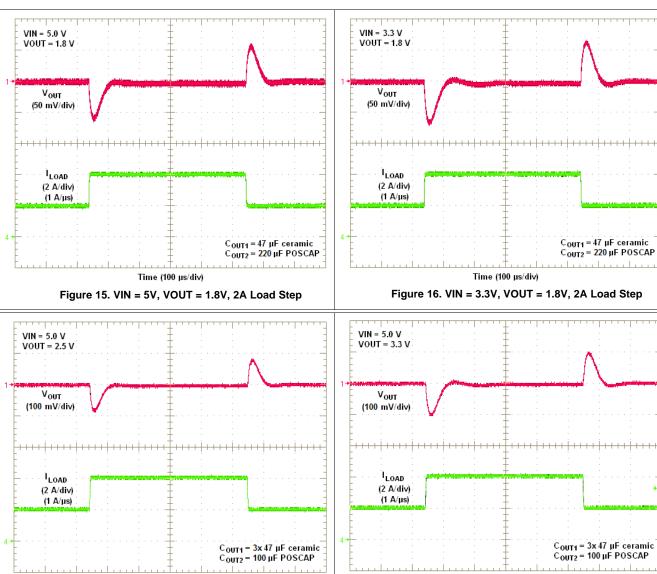

|                       | Transient response                                                                                                                                                                                                                                                                                                                                                                         | 1.0 A/µs load step from 1.                                                                                                                                                              | 5A to 4.5A                                            | V <sub>OUT</sub><br>over/undershoot |                     | 120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            | mV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

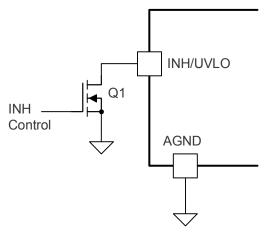

| V <sub>INH-H</sub>    |                                                                                                                                                                                                                                                                                                                                                                                            | Inhibit High Voltage                                                                                                                                                                    |                                                       |                                     |                     | 1.25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Open (3)                   | .,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| V <sub>INH-L</sub>    | - Inhibit Control                                                                                                                                                                                                                                                                                                                                                                          | Inhibit Low Voltage                                                                                                                                                                     |                                                       |                                     | -0.3                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.0                        | V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| I <sub>I(stby)</sub>  | Input standby current                                                                                                                                                                                                                                                                                                                                                                      | INH pin to AGND                                                                                                                                                                         |                                                       |                                     |                     | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 100                        | μA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                       |                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                         |                                                       | Good                                |                     | 93%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

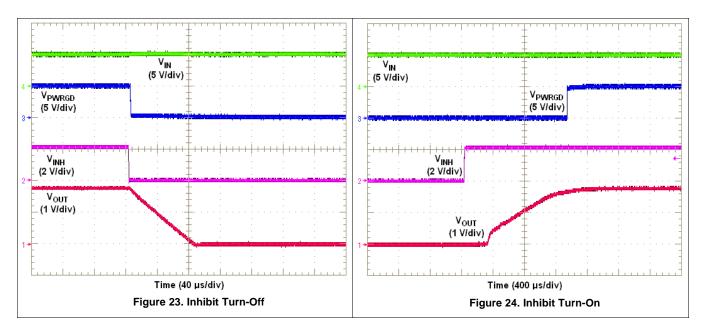

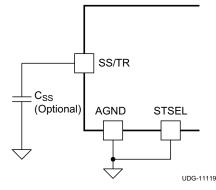

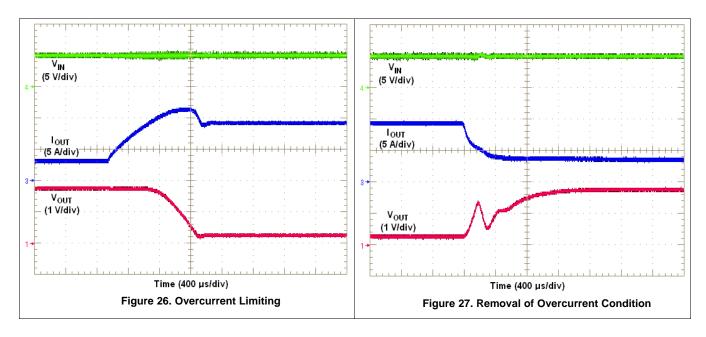

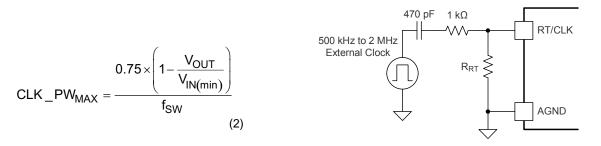

|                       |                                                                                                                                                                                                                                                                                                                                                                                            | V <sub>OUT</sub> rising                                                                                                                                                                 |                                                       | Fault                               |                     | 109%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |