AMC80

ZHCS128B - MAY 2011 - REVISED OCTOBER 2015

# AMC80 具有双线制和 SMBus 串行接口的系统硬件监控器

### 1 特性

- 具有七个模拟输入的 10 位模数转换器 (ADC)

- 风扇转速监控输入

- 输入范围/分辨率:

- 默认值: 2.56V/2.5mV

- 可编程: V<sub>DD</sub>/6mV

- 机箱入侵检测输入

- 中断报警:

- 上限

- 下限值

- 外部温度传感器的中断状态寄存器输入

- 关断模式

- 可编程 RST OUT/OS

- 与 LM96080 和 LM80 引脚兼容

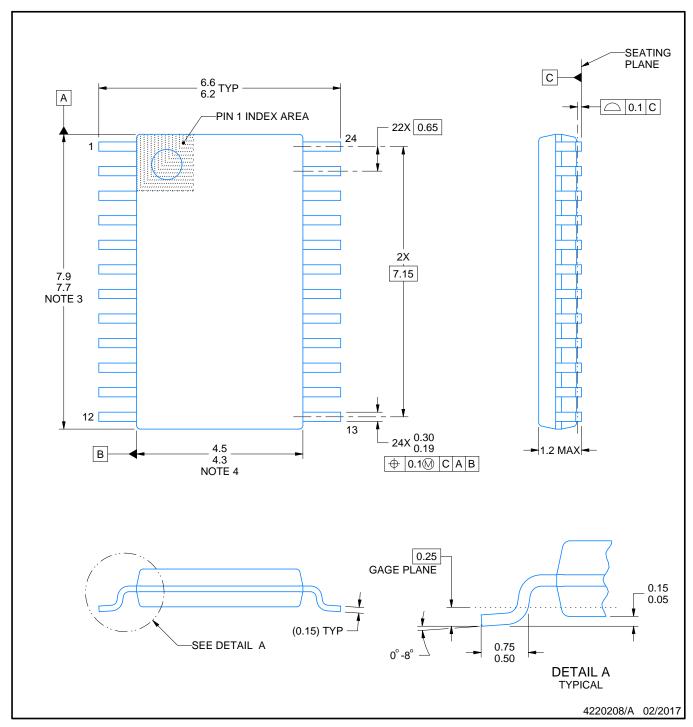

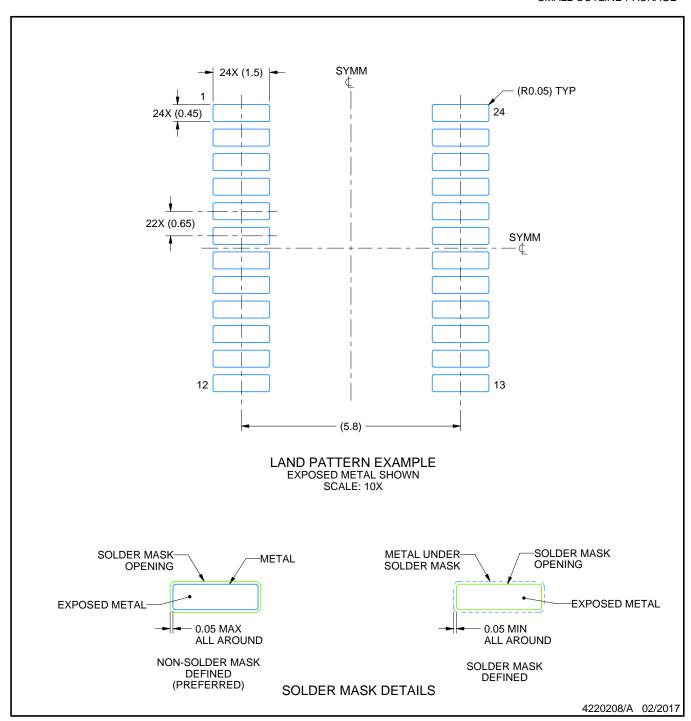

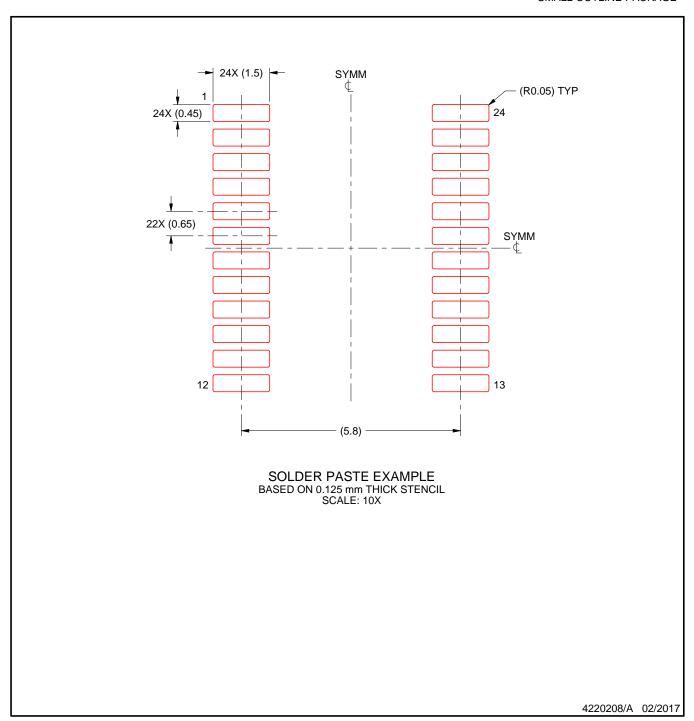

- 封装: 24 引脚薄型小外形尺寸 (TSSOP)

#### 2 应用

- 通信设备

- 服务器

- 工业用和医疗用设备

- 存储区域网络

- 机顶盒

- 测试和测量仪器

### 3 说明

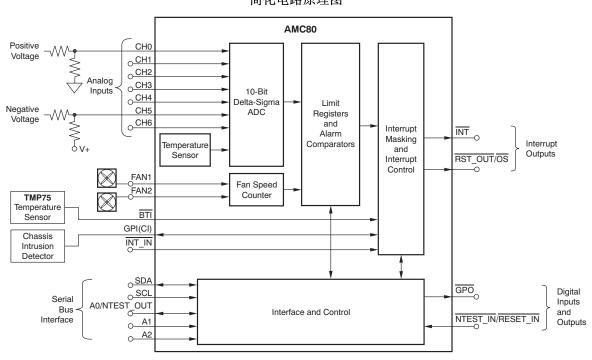

AMC80 是一款系统硬件监控和控制电路,其中包括一个七通道 10 位模数转换器 (ADC)、两个可编程风扇转速监控器和一个双线制接口。AMC80 还具有可编程上限值及下限值报警功能。当超出编程设定的限值后,该报警即启动。

AMC80 可与线性温度传感器和数字温度传感器相连。 凭借 2.5mV 最低有效位 (LSB) 和 2.56V 输入范围,该 器件可接收线性传感器(例如 TMP20)的输入。BTI 引脚用作数字传感器(例如 TMP75)的输入。AMC80 可由电压介于 3V 至 5.5V 范围内的电源供电运行,其 电源电流较低并可通过双线制接口配置,因此适用于各 类 集成电机驱动器解决方案。。

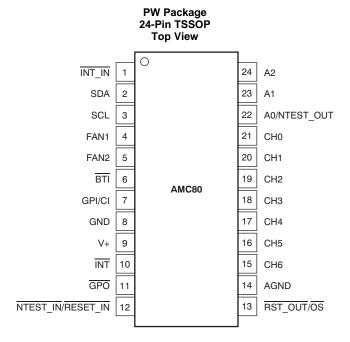

AMC80 采用 24 引脚 TSSOP 封装,可在 -40°C 至 +125°C 的温度范围内完全额定运行。

#### 器件信息(1)

| 器件型号  | 封装         | 封装尺寸 (标称值)      |

|-------|------------|-----------------|

| AMC80 | TSSOP (24) | 7.80mm × 4.40mm |

(1) 要了解所有可用封装,请参见数据表末尾的封装选项附录。

### 简化电路原理图

|                            | 1  | 目录          |                                                                                                                                                                                                                                                                              |  |

|----------------------------|----|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1<br>2<br>3<br>4<br>5<br>6 | 特性 | 7<br>8<br>9 | Detailed Description 7.1 Overview 7.2 Functional Block Diagram 7.3 Feature Description 7.4 Programming 7.5 Register Map  Application and Implementation 8.1 Application Information 8.1 Application Information 8.1 社区资源 9.1 社区资源 9.2 商标 9.3 静电放电警告 9.4 Glossary 机械、封装和可订购信息 |  |

# 4 修订历史记录

| Changes from Revision A (January 2012) to Revision B                | Page |

|---------------------------------------------------------------------|------|

| Changed INT pin description                                         | 4    |

| Added pins to input voltage range in Absolute Maximum Ratings table | 5    |

| Added ESD Ratings table                                             | 5    |

| Added new note 1 to <i>Timing Requirements</i> table                |      |

| Added Detailed Description section                                  | 10   |

| Added Application and Implementation section                        |      |

| • 已添加器件和文档支持章节                                                      | 23   |

| Changes from Original (May 2011) to Revision A                      | Page |

| Added SMBus timeout parameter to Electrical Characteristics         | 6    |

| Changed Bit 0 = '1' in Table 10                                     | 18   |

# 5 Pin Configuration and Functions

### **Pin Functions**

|    | PIN               |        |         |                                                                                                                                                                                                                                                                                                |

|----|-------------------|--------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |                   | I/O    | TYPE    | DESCRIPTION                                                                                                                                                                                                                                                                                    |

| 1  | ĪNT_ĪN            | Input  | Digital | Interrupt input pin. An active low input that extends the $\overline{\text{INT\_IN}}$ signal to the $\overline{\text{INT}}$ output of the AMC80.                                                                                                                                               |

| 2  | SDA               | I/O    | Digital | Serial bus data line for SMBus, open-drain; requires pull-up resistor.                                                                                                                                                                                                                         |

| 3  | SCL               | I/O    | Digital | Serial bus clock line for SMBus, open-drain; requires pull-up resistor.                                                                                                                                                                                                                        |

| 4  | FAN1              | Input  | Digital | Fan tachometer input pin                                                                                                                                                                                                                                                                       |

| 5  | FAN2              | Input  | Digital | Fan tachometer input pin                                                                                                                                                                                                                                                                       |

| 6  | BTI               | Input  | Digital | Board temperature interrupt pin. $\overline{BTI}$ is driven by the over-temperature shutdown (OS) outputs of the additional temperature sensors. This pin has an internal 10-k $\Omega$ pull-up resistor.                                                                                      |

| 7  | GPI(CI)           | Input  | Digital | General-purpose input pin (chassis interrupt). An active high interrupt input pin to latch a chassis interrupt event.                                                                                                                                                                          |

| 8  | DGND              | Power  | Analog  | Digital ground.                                                                                                                                                                                                                                                                                |

| 9  | V+                | Power  | Analog  | Positive supply voltage (3V to 5.5V).                                                                                                                                                                                                                                                          |

| 10 | ĪNT               | Output | Digital | Non-maskable interrupt (active high, PMOS, push-pull) or interrupt request (active low, NMOS, push-pull) pin. The $\overline{\text{INT}}$ pin becomes active when $\overline{\text{INT_IN}}$ , $\overline{\text{BTI}}$ , or GPI interrupts. This pin does not require a pullup resistor to V+. |

| 11 | GPO               | Output | Digital | General-purpose output pin. GPO is an active low, NMOS, open-drain output. This pin is intended to drive an external power PMOS for software power control or to control power to a cooling fan.                                                                                               |

| 12 | NTEST_IN/RESET_IN | Input  | Digital | This pin is an active-low input that enables NAND tree board-level connectivity testing. The AMC80 resets to its power-on state when NAND tree connectivity is enabled.                                                                                                                        |

| 13 | RST_OUT/OS        | Output | Digital | This pin is an NMOS open-drain output. RST_OUT provides a master reset to devices connected to this line. OS is dedicated to the temperature reading alarm.                                                                                                                                    |

| 14 | AGND              | Power  | Analog  | Analog ground. This pin must be tied to a low-noise analog ground plane for optimum performance.                                                                                                                                                                                               |

| 15 | CH6               | Input  | Analog  | Analog input channel 6                                                                                                                                                                                                                                                                         |

| 16 | CH5               | Input  | Analog  | Analog input channel 5                                                                                                                                                                                                                                                                         |

| 17 | CH4               | Input  | Analog  | Analog input channel 4                                                                                                                                                                                                                                                                         |

| 18 | CH3               | Input  | Analog  | Analog input channel 3                                                                                                                                                                                                                                                                         |

| 19 | CH2               | Input  | Analog  | Analog input channel 2                                                                                                                                                                                                                                                                         |

| 20 | CH1               | Input  | Analog  | Analog input channel 1                                                                                                                                                                                                                                                                         |

| 21 | CH0               | Input  | Analog  | Analog input channel 0                                                                                                                                                                                                                                                                         |

| 22 | A0/NTEST_OUT      | I/O    | Digital | The lowest order bit of the serial bus address. During a NAND tree test for ATE board-level connectivity, this pin functions as an output.                                                                                                                                                     |

| 23 | A1                | Input  | Digital | Address pin 1                                                                                                                                                                                                                                                                                  |

| 24 | A2                | Input  | Digital | Address pin 2                                                                                                                                                                                                                                                                                  |

### 6 Specifications

# 6.1 Absolute Maximum Ratings<sup>(1)</sup>

Over operating free-air temperature range, unless otherwise noted.

|                                                |                                                | MIN  | MAX        | UNIT                                  |

|------------------------------------------------|------------------------------------------------|------|------------|---------------------------------------|

| Power-supply voltage range                     | , V+                                           | -0.3 | 7          | V                                     |

| lanut valtana nana V                           | Pins 6, 10, 15, 16, 17, 18, 19, 20, 21, 22, 24 | -0.3 | (V+) + 0.3 |                                       |

| Input voltage range, V <sub>IN</sub>           | Pins 1, 2, 3, 4, 5, 7, 9, 11, 12, 13, 23       | -0.3 | 7          | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

| Input current, I <sub>IN</sub>                 |                                                |      | 10         | mA                                    |

| Operating temperature range, T <sub>A</sub>    |                                                | -55  | 127        | °C                                    |

| Junction temperature range, T <sub>J</sub> max |                                                |      | 150        | °C                                    |

| Storage temperature range,                     | T <sub>STG</sub>                               | -65  | 150        | °C                                    |

<sup>(1)</sup> Stresses above these ratings my cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

### 6.2 ESD Ratings

|                    |                         |                                                                     | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±2500 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±1000 | V    |

|                    |                         | Machine model (MM)                                                  | ±200  |      |

<sup>(1)</sup> JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

#### 6.3 Recommended Operating Conditions

|                                             | MIN   | NOM MAX     | UNIT |

|---------------------------------------------|-------|-------------|------|

| Supply voltage range, V+                    | 3     | 5.5         | V    |

| Input voltage range, V <sub>IN</sub>        | -0.05 | (V+) + 0.05 | V    |

| Operating temperature range, T <sub>A</sub> | -40   | 125         | °C   |

#### 6.4 Thermal Information

|                      |                                              | AMC80      |      |

|----------------------|----------------------------------------------|------------|------|

|                      | THERMAL METRIC <sup>(1)</sup>                | PW (TSSOP) | UNIT |

|                      |                                              | 24 PINS    |      |

| $R_{\theta JA}$      | Junction-to-ambient thermal resistance       | 100.72     | °C/W |

| $R_{\theta JC(top)}$ | Junction-to-case (top) thermal resistance    | 31.4       | °C/W |

| $R_{\theta JB}$      | Junction-to-board thermal resistance         | 54.7       | °C/W |

| ΨJΤ                  | Junction-to-top characterization parameter   | 1.0        | °C/W |

| ΨЈВ                  | Junction-to-board characterization parameter | 54.2       | °C/W |

| $R_{\theta JC(bot)}$ | Junction-to-case (bottom) thermal resistance | N/A        | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

<sup>(2)</sup> JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process. ance.

#### 6.5 Electrical Characteristics

At  $T_A$  –40°C to +125°C and V+ = 3 V to 5.5 V, unless otherwise noted.

|                               | PARAMETER                             | TEST CONDITIONS                                                                | MIN       | TYP          | MAX  | UNIT               |

|-------------------------------|---------------------------------------|--------------------------------------------------------------------------------|-----------|--------------|------|--------------------|

| DIGITAL                       | INPUTS                                | ,                                                                              | 1         |              |      |                    |

| V <sub>IH</sub>               | Input high voltage                    |                                                                                | 2         |              |      | V                  |

| V <sub>IL</sub>               | Input low voltage                     |                                                                                |           |              | 0.8  | V                  |

|                               |                                       | V+ = 3.3 V                                                                     |           | 0.23         |      | V                  |

| $V_{HYS}$                     | Hysteresis voltage                    | V+ = 5 V                                                                       |           | 0.33         |      | V                  |

|                               |                                       | V <sub>IH</sub> = V+, all pins except BTI                                      | -1        | -0.005       |      | μΑ                 |

| I <sub>IH</sub>               | Input high current                    | V <sub>IH</sub> = V+, <del>BTI</del> pin                                       | -10       | -1           |      | μΑ                 |

|                               | Land Investment                       | V <sub>IL</sub> = 0 V, all pins except BTI                                     |           | 0.005        | 1    | μΑ                 |

| IIL                           | Input low current                     | $V_{IL} = 0 \text{ V}, \text{ V+} = 5.5 \text{ V}, \overline{BTI} \text{ pin}$ |           |              | 2    | mA                 |

| C <sub>IN</sub>               | Input capacitance                     |                                                                                |           | 20           |      | pF                 |

| ANALOG                        | INPUTS                                | ,                                                                              | 1         |              |      |                    |

|                               | Langet and transfer and an area       | Default                                                                        | 0         |              | 2.56 | V                  |

| $V_{IN}$                      | Input voltage range                   | Programmable                                                                   | 0         |              | V+   | V                  |

| I <sub>L-ON</sub>             | Input leakage current (on)            |                                                                                |           | ±0.005       |      | μA                 |

| I <sub>L-OFF</sub>            | Input leakage current (off)           |                                                                                |           | ±0.005       |      | μA                 |

| R <sub>IN</sub>               | Input resistance                      |                                                                                |           | 2            | 10   | kΩ                 |

|                               | OUTPUTS (A0/NTEST_OUT, INT)           |                                                                                | <b></b> ₩ |              |      |                    |

| V <sub>OH</sub>               | Output high voltage                   | I <sub>OUT</sub> = 3 mA/5 mA, V+ = 3 V/4.5 V                                   | 2.4       |              |      | V                  |

| V <sub>OL</sub>               | Output low voltage                    | I <sub>OUT</sub> = 3 mA/5 mA, V+ = 3 V/4.5 V                                   |           |              | 0.4  | V                  |

|                               | OPEN-DRAIN OUTPUTS (GPO, R            | ST_OUT/OS, GPI/CI, SDA)                                                        | 11.       |              |      |                    |

|                               | Output low voltage                    | $I_{OUT} = 3 \text{ mA/5 mA}, V+ = 3 \text{ V/4.5 V},$                         |           |              | 0.4  |                    |

| $V_{OL}$                      |                                       | all pins except SDA                                                            |           |              | 0.4  | V                  |

|                               |                                       | $I_{OUT} = 4 \text{ mA}, V+ = 3 \text{ V}, SDA pin$                            |           |              | 0.4  |                    |

| I <sub>OH</sub>               | Output high current                   | V <sub>OUT</sub> = V+                                                          |           | 0.005        | 1    | μΑ                 |

| $t_{w}$                       | Pulse duration                        | RST_OUT/OS, GPI/CI                                                             | 10        | 22.5         |      | ms                 |

| SMBus                         |                                       |                                                                                |           |              |      |                    |

|                               | SMBus timeout <sup>(1)</sup>          |                                                                                |           | 28           | 35   | ms                 |

| TEMPER                        | ATURE ERROR                           | ,                                                                              | *         |              | •    |                    |

| _                             | T                                     | $T_A = -40^{\circ}\text{C to } +125^{\circ}\text{C}$                           |           |              | ±3   | °C                 |

| TE                            | Temperature error                     | $T_A = -25^{\circ}\text{C to } +100^{\circ}\text{C}$                           |           |              | ±2   | °C                 |

| T <sub>R</sub>                | Temperature resolution                |                                                                                | 0.0625    |              |      | °C                 |

| ANALOG                        | -TO-DIGITAL CONVERTER                 |                                                                                |           |              |      |                    |

| \/                            | Decelution                            | V <sub>IN</sub> = 2.56 V                                                       |           | 2.5          |      |                    |

| $V_R$                         | Resolution                            | $V_{IN} = V+$                                                                  |           | 6            |      | mV                 |

| DNL                           | Differential linearity                |                                                                                | -1        |              | 1    | LSB <sup>(2)</sup> |

| ADC <sub>ERR</sub>            | Total unadjusted error <sup>(3)</sup> |                                                                                | -1%       |              | 1%   |                    |

| PSRR                          | Power supply rejection ratio          |                                                                                |           | ±0.0008<br>% |      |                    |

| t <sub>C</sub> <sup>(4)</sup> | Total conversion time                 |                                                                                | 662       | 728          | 810  | ms                 |

<sup>(1)</sup> The SMBus timeout in the AMC80 resets the interface anytime SCL or SDA is low for over 28 ms.

<sup>(2)</sup> LSB means least significant bit.

<sup>(3)</sup> Total unadjusted error contains offset, gain, and linearity errors of the ADC.

<sup>(4)</sup> Total conversion time contains the temperature conversion, the seven analog input voltage conversions, and the two tachometer readings.

# **Electrical Characteristics (continued)**

At  $T_A$  –40°C to +125°C and V+ = 3 V to 5.5 V, unless otherwise noted.

|                    | PARAMETER                        | TEST CONDITIONS              | MIN      | TYP  | MAX  | UNIT   |

|--------------------|----------------------------------|------------------------------|----------|------|------|--------|

| FAN RPM            | 1-TO-DIGITAL CONVERTER           |                              | T.       |      |      |        |

| FAN <sub>ERR</sub> | Fan RPM error                    |                              | -10%     |      | 10%  |        |

| f <sub>CLK</sub>   | Internal clock frequency         |                              | 20.2     | 22.5 | 24.8 | kHz    |

|                    |                                  | Divisor = 1, fan count = 153 |          | 8800 |      |        |

|                    | FANA and FANO naminal input DDM  | Divisor = 2, fan count = 153 |          | 4400 |      | DDM    |

| FAN <sub>RPM</sub> | FAN1 and FAN2 nominal input RPM  | Divisor = 3, fan count = 153 |          | 2200 |      | RPM    |

|                    |                                  | Divisor = 4, fan count = 153 |          | 1100 |      |        |

| FSC                | Full-scale count                 |                              |          |      | 255  | Counts |

| POWER S            | SUPPLY                           |                              | <u>.</u> |      |      |        |

| V+                 | Specified voltage range          |                              | 3        |      | 5.5  | V      |

|                    | Quiescent current, average       | V+ = 5.5 V                   |          |      | 100  | ^      |

| $I_{QA}$           |                                  | V+ = 3.8 V                   |          |      | 25   | μA     |

|                    | Outroped summer should sum and s | V+ = 5.5 V                   |          |      | 100  | ^      |

| I <sub>QSD</sub>   | Quiescent current, shutdown mode | V+ = 3.8 V                   |          |      | 25   | μA     |

| TEMPER.            | ATURE                            |                              | ·        |      |      |        |

| T <sub>A</sub>     | Specified range                  |                              | -40      |      | 125  | °C     |

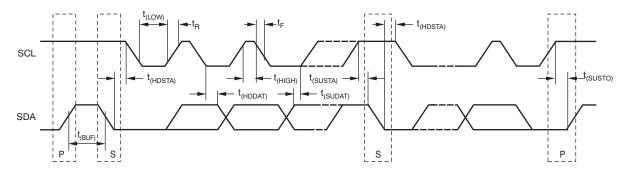

### 6.6 Timing Requirements

At  $T_A$  –40°C to +125°C and  $V_S$  = 3V to 5.5V, unless otherwise noted.

|                      |                                                                                            | FAST MOD         | )E <sup>(1)</sup> | HIGH-SPEED M | IODE <sup>(1)</sup> |      |

|----------------------|--------------------------------------------------------------------------------------------|------------------|-------------------|--------------|---------------------|------|

|                      |                                                                                            | MIN              | MAX               | MIN          | MAX                 | UNIT |

| f <sub>(SCL)</sub>   | SCL operating frequency                                                                    | 10               | 400               | 10           | 3400                | kHz  |

| t <sub>(BUF)</sub>   | Bus free time between STOP and START conditions                                            | 600              |                   | 160          |                     | ns   |

| t <sub>(HDSTA)</sub> | Hold time after repeated START condition. After this period, the first clock is generated. | 600              |                   | 160          |                     | ns   |

| t <sub>(SUSTA)</sub> | Repeated START condition setup time                                                        | 600              |                   | 160          |                     | ns   |

| t <sub>(SUSTO)</sub> | STOP condition setup time                                                                  | 600              |                   | 160          |                     | ns   |

| t <sub>(HDDAT)</sub> | Data hold time                                                                             | 0 <sup>(2)</sup> |                   | 0(3)         |                     | ns   |

| t <sub>(SUDAT)</sub> | Data setup time                                                                            | 100              |                   | 10           |                     | ns   |

| t <sub>(LOW)</sub>   | Clock low period                                                                           | 1300             |                   | 160          |                     | ns   |

| t <sub>(HIGH)</sub>  | Clock high period                                                                          | 600              |                   | 60           |                     | ns   |

| t <sub>R</sub>       | Clock/Data input rise time                                                                 |                  | 300               |              | 160                 | ns   |

| t <sub>F</sub>       | Clock/Data input fall time                                                                 |                  | 300               |              | 160                 | ns   |

- (1) Values based on a statistical analysis of a one-time sample of devices. Minimum and maximum values are not specified and not

- production tested.

For cases when the fall time of SCL is less than 20 ns and/or the rise time or fall time of SDA is less than 20 ns, the hold time should be

- greater than 20 ns. For cases when the fall time of SCL is less than 10 ns and/or the rise or fall time of SDA is less than 10 ns, the hold time should be greater than 10 ns.

Figure 1. Serial Bus Interface Timing

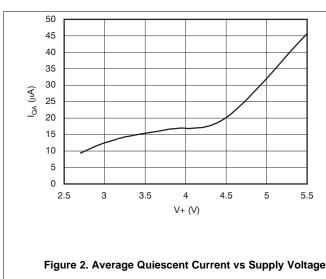

### 6.7 Typical Characteristics

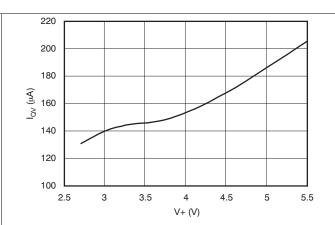

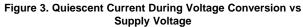

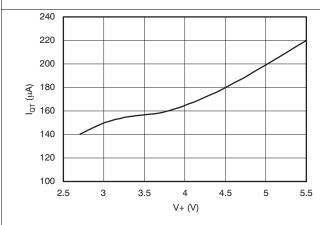

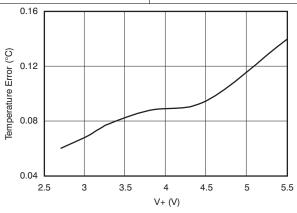

At  $T_A = +25$ °C and V+ = 3 V to 5.5 V, unless otherwise noted.

Figure 4. Quiescent Current During Temperature **Conversion vs Supply Voltage**

Figure 5. Quiescent Current During Shutdown vs Supply Voltage

Figure 6. Temperature Error vs Supply Voltage

### 7 Detailed Description

#### 7.1 Overview

The AMC80 provides seven analog inputs, a temperature sensor, a delta-sigma analog-to-digital converter (ADC), and a variety of inputs and outputs on a single chip. A two-wire SMBus interface is also provided. The AMC80 can continuously perform power-supply, temperature, and fan monitoring for a variety of applications. The AMC80 is fully pin- and software-compatible with the LM96080 and LM80.

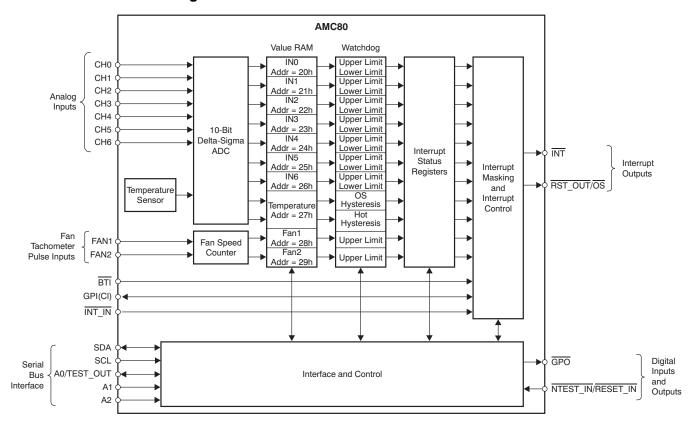

#### 7.2 Functional Block Diagram

### 7.3 Feature Description

#### 7.3.1 Block Level Description

The AMC80 continuously converts analog inputs to 10-bit resolution using a 2.5-mV least significant bit (LSB) with a default input range of 0 V to 2.56 V, or a 6-mV LSB with a programmable input range of 0 V to V+. The analog inputs (CH0 to CH6) are intended for connection to the several power supplies present in any typical system. Temperature can be converted to a 9-bit or 12-bit resolution with either 0.5°C or 0.0625°C LSB, respectively. The FAN1 and FAN2 inputs can be programmed to accept either a fan failure indicator or tachometer signals. Fan failure signals can be programmed to be either active high or active low. Fan inputs measure the period of tachometer pulses from the the fans, providing a higher count for lower fan speeds. The fan inputs are digital inputs with transition levels according to the Digital Inputs section of the *Electrical Characteristics* table. Full-scale fan counts are 255 (8-bit counter), which represent a stopped or very slow fan. Nominal speeds, based on a count of 153, are programmable from 1100 RPM to 8800 RPM. Signal conditioning circuitry is included to accommodate slow rise and fall times.

The AMC80 provides a number of internal registers:

- Configuration Register: Provides control and configuration.

- Interrupt Status Registers: Two registers that provide the status of each interrupt alarm.

- Interrupt Mask Registers: Allows masking of individual interrupt sources, as well as separate masking for

#### **Feature Description (continued)**

both hardware interrupt outputs.

- Fan Divisor/RST\_OUT/OS Register: Bits 0 to 5 of this register contain the divisor bits for the FAN1 and FAN2 inputs. Bits 6 and 7 control the function of the RST\_OUT/OS output.

- OS Configuration/Temperature Resolution Register: The configuration of the overtemperature shutdown (OS) is controlled by the lower three bits of this register. Bit 3 enables 12-bit temperature conversions. In 12-bit mode, bits 4 to 7 represent the four LSBs of the temperature measurement. In 9-bit mode, bit 4 represents the LSB of the temperature measurement.

- **Conversion Rate Register:** Sets the time interval of the continuous monitoring cycle to either fixed or programmable (see the Conversion Rate Count Register for setting the programmable time interval).

- Voltage/Temperature Channel Disable Register: Allows voltage inputs and the local temperature conversion to be disabled.

- Input Mode Register: Allows voltage inputs to be configured as single-ended or as a differential pair with normal or reverse polarity.

- ADC Control Register: Bits 0 to 2 set the programmable conversion rate for the 10-bit ADC. Bits 3 to 5 allow for programmable input full-scale voltage.

- Conversion Rate Count Register: Selects the adjustable time interval when the conversion rate of the continuous monitoring cycle is set to programmable.

- Value RAM: The monitoring results (for temperature, voltages, fan counts, and Fan Divisor/RST\_OUT/OS Register limits) are all contained in the Value RAM. The Value RAM consists of 32 bytes. The first 10 bytes are all of the results, the next 20 bytes are the interrupt alarm limits, and the last two bytes are at the upper locations for manufacturer ID and die revision ID.

The AMC80 SMBus is compatible with both fast mode (400 kHz) and high-speed mode (3.4 MHz) two-wire interface modes of operation. The AMC80 supports a timeout reset function on SDA and SCL that prevents two-wire bus lockup, and includes an analog filter on the two-wire digital control lines that improves noise immunity. Three address pins (A0 to A2), allow up to eight devices on a single bus. When enabled, the AMC80 starts by cycling through each measurement in sequence, and continuously loops through the sequence based on the Conversion Rate Register (address 07h) setting. Each measured value is compared to values stored in the Value RAM Registers (addresses 2Ah to 3Dh). When the measured value exceeds the programmed limit, the AMC80 sets a corresponding interrupt in the Interrupt Status Registers (addresses 01h and 02h). Two output interrupt lines (INT and RST\_OUT/OS) are available. INT is fully programmable with the ability to mask each interrupt source and each output. The Fan Divisor/RST\_OUT/OS Register (address 05h) has control bits that enable or disable the hardware interrupts. Additional digital inputs are provided for daisy-chaining the interrupt output pin, INT. This configuration is achieved by connecting multiple external temperature sensors (for example, the TMP75) to the board temperature interrupt (BTI) input and/or the GPI/CI input. The chassis intrusion (CI) input is designed to accept an active high signal from an external circuit that latches (for example, when the chassis from a server rack is removed).

#### **Feature Description (continued)**

#### 7.3.2 Temperature Measurement

The AMC80  $\Delta V_{BE}$ -type temperature sensor, is a  $\Delta \Sigma$  ADC that performs 9-bit or 12-bit twos complement temperature conversions. An 8-bit comparator that compares the readings to the user-programmable hot and overtemperature setpoints, and hysteresis values is also incorporated into the AMC80.

Temperature data can be read from the Temperature Reading Register (address 27h). Temperature limits can be read from and written to the Hot Temperature  $(T_{HOT})$ , Hot Temperature Hysteresis  $(T_{HOT\_HYST})$ ,  $\overline{OS}$  Temperature  $(T_{OS})$ , and  $\overline{OS}$  Temperature Hysteresis  $(T_{OS\_HYST})$  Limit Registers (addresses 38h to 38h). Each limit is represented in 12-bit, 9-bit, or 8-bit resolution, as shown in Table 1.

12-BIT DIGITAL OUTPUT (HEX) 9-BIT DIGITAL OUTPUT (HEX) **8-BIT DIGITAL OUTPUT (HEX) TEMPERATURE** LSB = 0.0625°C LSB = 0.5°C LSB = 1°C +125°C 07D 0FA 7D +25°C 019 032 19 +1°C 010 003 01 0.0625°C 001 0°C 000 000 00 FFF -0.0625°C -1°C FF0 1FF FF -25°C E70 1CE E7 -55°C C90 192 C9

**Table 1. Temperature Lookup**

When using a single-byte read, the eight MSBs of the temperature reading can be found in the Value RAM Register (address 27h). The remainder of the temperature reading can be found in the OS Configuration/Temperature Resolution Register (address 06h), bits 4 to 7. In 9-bit format, bit 7 is the only valid bit. In addition, all nine or 12 bits can be read using a double-byte read at register address 27h.

There are four Value RAM Register limits for the temperature reading that affect the  $\overline{\text{INT}}$  and  $\overline{\text{OS}}$  outputs of the AMC80. These are the T<sub>HOT</sub>, T<sub>HOT\_HYST</sub>, T<sub>OS</sub>, T<sub>OS\_HYST</sub> Limit Registers (addresses 38h to 3Bh); see Table 15. There are three interrupt modes of operation: Default Interrupt, One-Time Interrupt, and Comparator. The  $\overline{\text{OS}}$  output of the AMC80 can be programmed for One-Time Interrupt mode and Comparator mode.  $\overline{\text{INT}}$  can be programmed for Default Interrupt mode and One-Time Interrupt mode. These modes are explained in the following subsections.

#### 7.3.2.1 Default Interrupt Mode

In Default Interrupt mode, exceeding  $T_{HOT}$  causes an interrupt that remains active indefinitely until reset by reading Interrupt Status Register 1 (address 01h) or cleared by the INT\_Clear bit in the Configuration Register (address 00h, bit 3). When an interrupt event has occurred by exceeding  $T_{HOT}$ , and is then reset, another interrupt occurs again when the next temperature conversion has completed. The interrupts continue to occur in this manner until the temperature falls below  $T_{HOT}$  HYST, at which time the interrupt output automatically clears.

#### 7.3.2.2 One-Time Interrupt Mode

In One-Time Interrupt mode, exceeding  $T_{HOT}$  causes an interrupt that remains active indefinitely until reset by reading Interrupt Status Register 1 or cleared by the INT\_Clear bit in the Configuration Register. When an interrupt event has occurred by exceeding  $T_{HOT}$ , and is then reset, an interrupt does not occur again until the temperature falls below  $T_{HOT}$  HYST.

#### 7.3.2.3 Comparator Mode

In Comparator mode, exceeding  $T_{OS}$  causes the  $\overline{OS}$  output to go low (default) and remain low until the temperature falls below  $T_{OS\_HYST}$ . When the temperature falls below  $T_{OS\_HYST}$ ,  $\overline{OS}$  goes high.

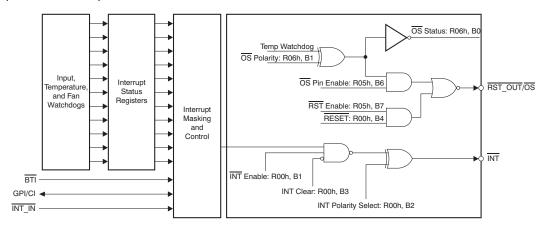

#### 7.3.3 Interrupt Structure

Figure 7 depicts the interrupt structure of the AMC80.

Figure 7. Interrupt Structure

External interrupt inputs can come from the following sources:

- Board Temperature Interrupt (BTI) This pin is an active low interrupt recommended to come from the overtemperature shutdown (OS) output of TMP75 temperature sensors. The TMP75 OS output activates when its temperature exceeds a programmed threshold. If the temperature of any TMP75 exceeds its programmed limit, BTI is driven low. This action generates an interrupt through bit 1 of Interrupt Status Register 2 (address 02h) that notifies the host of a possible overtemperature condition. To disable this feature, set bit 1 of Interrupt Mask Register 2 (address 04h) to high. This pin also provides an internal, 10-kΩ pull-up resistor.

- GPI/CI This pin is an active high interrupt from any type of device that detects and captures chassis intrusion violations. This action could be accomplished mechanically, optically, or electrically; circuitry external to the AMC80 is expected to latch the event. Read this interrupt using bit 4 of Interrupt Status Register 2 (address 02h), and disable it using bit 4 of Interrupt Mask Register 2 (address 04h). The design of the AMC80 allows this input to go high even with no power applied, and no clamping or other interference with the line occurs. This line can also be pulled low by the AMC80 for at least 10ms to reset a typical chassis-intrusion circuit. Accomplish this reset by setting bit 5 of the Configuration Register (address 00h) to high; this bit is self-clearing.

- INT\_IN This pin is an active low interrupt that provides a way to connect an INT from other devices through the AMC80 to the processor. If this pin is pulled low, then bit 7 of Interrupt Status Register 1 (address 01h) goes high, indicating this interrupt detection. Setting bit 1 of the Configuration Register (address 00h) also allows the INT pin to go low when INT\_IN goes low. To disable this feature, set bit 7 of Interrupt Mask Register 1 (address 03h) to high.

Device interrupt outputs can come from the following sources:

- INT This pin becomes active whenever INT\_IN, BTI, or GPI/CI interrupts. INT is enabled when bit 1 of the Configuration Register (address 00h) is set high. Bits 2 and 3 of the Configuration Register are also used to set the polarity and state of the INT interrupt line.

- OS In the Fan Divisor/RST\_OUT/OS Register (address 05h), bit 6 (OS Pin Enable), must be set high and bit 7 (RST Enable) must be set to low in order to enable the OS function on the RST\_OUT/OS pin. The OS pin has two modes of operation: One-Time Interrupt and Comparator. One-Time Interrupt mode is selected by taking bit 2 of the OS Configuration/Temperature Resolution Register (address 06h) high. If bit 2 is taken low, then Comparator mode is selected. Unlike the OS pin, the OS bit in Interrupt Status Register 2 (address 02h, bit 5) functions in Default Interrupt and One-Time Interrupt modes. The OS bit can be masked to the INT pin by taking bit 5 in Interrupt Mask Register 2 (address 04h) low.

Reading the Interrupt Status Registers (addresses 01h to 02h) outputs the contents and then resets the registers and the INT pin. The INT pin is also cleared by the INT\_Clear bit (address 00h, bit 3) without affecting the contents of the Interrupt Status Registers. When this bit is high, the AMC80 monitoring loop is inactive; monitoring resumes when this bit is low.

#### 7.4 Programming

#### 7.4.1 Interface and Control

The SMBus control lines in the AMC80 include SDA, SCL, and the A0 to A2 address pins, which allow up to eight AMC80 devices to be on the same bus. The AMC80 can only operate as a slave device. The SCL line controls only the serial interface; all other clock-related functions within the AMC80 (such as the ADC and fan counters) operate with a separate asynchronous internal clock. The default power-on SMBus address for the AMC80 is '0101'(A2)(A1)(A0) binary, where (A2)(A1)(A0) is the SMBus address.

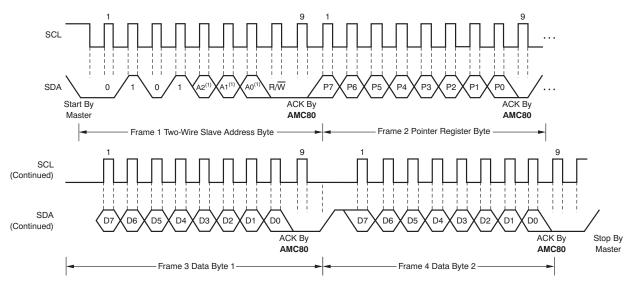

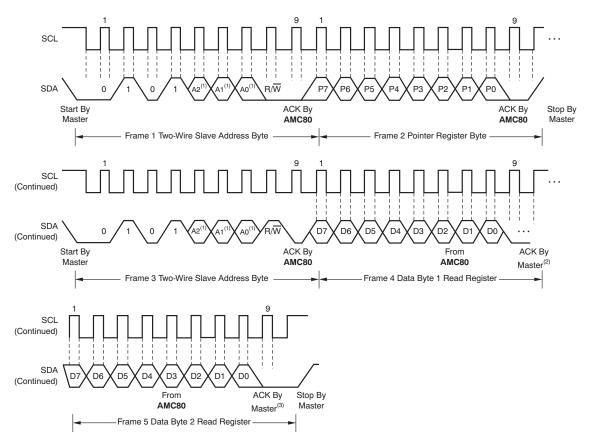

When using the SMBus interface, a write command always consists of the AMC80 SMBus interface address byte, followed by the internal address register byte, and then the data byte (see Figure 8).

See Figure 9 for the read operation timing. There are two cases for a read operation:

- 1. If the contents of the Internal Address Register are known, simply read the AMC80 with the SMBus interface address byte, followed by the data byte read from the ADC80.

- 2. If the internal Address Register contents are unknown, write to the AMC80 with the SMBus interface address byte, followed by the internal address register bye. Then restart the serial communication with a read that consist of the SMBus interface address byte, followed by the data byte read from the AMC80.

**Table 2. Register Overview**

| INTERNAL<br>ADDRESS<br>(HEX) | POWER-ON<br>VALUE<br>(HEX)                                                            | NOTES                                                                                                                              |  |  |  |  |  |

|------------------------------|---------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 00                           | 08                                                                                    |                                                                                                                                    |  |  |  |  |  |

| 01                           | xx                                                                                    | Indeterminate                                                                                                                      |  |  |  |  |  |

| 02                           | xx                                                                                    | Indeterminate                                                                                                                      |  |  |  |  |  |

| 03                           | 00                                                                                    |                                                                                                                                    |  |  |  |  |  |

| 04                           | 00                                                                                    |                                                                                                                                    |  |  |  |  |  |

| 05                           | 14                                                                                    | FAN1 and FAN2 divisor = 2 (count of 153 = 4400 RPM)                                                                                |  |  |  |  |  |

| 06                           | x1                                                                                    | Four MSBs are indeterminate                                                                                                        |  |  |  |  |  |

| 07                           | 40                                                                                    |                                                                                                                                    |  |  |  |  |  |

| 08                           | 00                                                                                    | Allows voltage monitoring inputs to be disabled                                                                                    |  |  |  |  |  |

| 09                           | 00                                                                                    |                                                                                                                                    |  |  |  |  |  |

| 0A                           | 02                                                                                    |                                                                                                                                    |  |  |  |  |  |

| 0B                           | 40                                                                                    |                                                                                                                                    |  |  |  |  |  |

| 20 to 29                     | xx                                                                                    | Indeterminate                                                                                                                      |  |  |  |  |  |

| 2A to 3D                     | xx                                                                                    | Indeterminate                                                                                                                      |  |  |  |  |  |

| 3E                           | 80                                                                                    |                                                                                                                                    |  |  |  |  |  |

| 3F                           | 09                                                                                    |                                                                                                                                    |  |  |  |  |  |

|                              | ADDRESS (HEX)  00  01  02  03  04  05  06  07  08  09  0A  0B  20 to 29  2A to 3D  3E | ADDRESS (HEX)  00 08  01 xx  02 xx  03 00  04 00  05 14  06 x1  07 40  08 00  09 00  0A 02  0B 40  20 to 29 xx  2A to 3D xx  38 80 |  |  |  |  |  |

(1) The values of A0, A1, and A2 are determined by the A0, A1, and A2 pins, respectively.

Figure 8. Two-Wire Timing for Write Word Format

- (1) The values of A0, A1, and A2 are determined by the A0, A1, and A2 pins, respectively.

- (2) Master should leave SDA high to terminate a single-byte read operation.

- (3) Master should leave SDA high to terminate a two-byte read operation.

Figure 9. Two-Wire Timing for Read Word Format

### 7.5 Register Map

# 7.5.1 Configuration Register

Table 3. Configuration Register (Address = 00h, Default = 08h)

| BIT | NAME                | TYPE | DESCRIPTION                                                                                                                                                                                                |

|-----|---------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Start               | R/W  | '1' enables startup of monitoring activity; '0' puts device in shutdown mode.                                                                                                                              |

| 1   | INT Enable          | R/W  | '1' enables the $\overline{\text{INT}}$ output.                                                                                                                                                            |

| 2   | INT Polarity Select | R/W  | '1' selects active-high, open-source output; '0' selects active-low, open-drain output.                                                                                                                    |

| 3   | INT_Clear           | R/W  | '1' disables the INT output without affecting the contents of the Interrupt Status Registers. The device stops monitoring and resumes on a '0'.                                                            |

| 4   | RESET               | R/W  | '1' outputs an active-low reset signal at RST_OUT, if bit 7 and bit 6 in the Fan Divisor/Register (address 05h) are set to '1' and '0', respectively. This bit is cleared when the pulse becomes inactive. |

| 5   | Chassis Clear       | R/W  | '1' clears the GPI/CI pin. This bit clears itself after 10ms.                                                                                                                                              |

| 6   | GPO                 | R/W  | '1' drives the GPO pin low.                                                                                                                                                                                |

| 7   | INITIALIZATION      | R/W  | '1' restores power-on-default values to the registers. This bit is self-clearing                                                                                                                           |

### 7.5.2 Interrupt Status Registers

### Table 4. Interrupt Status Register 1 (Address = 01h, Default = xxh; see Table 2)

| BIT | NAME   | TYPE | DESCRIPTION                                                          |

|-----|--------|------|----------------------------------------------------------------------|

| 0   | CH0    | Read | '1' indicates a high or low limit has been exceeded.                 |

| 1   | CH1    | Read | '1' indicates a high or low limit has been exceeded.                 |

| 2   | CH2    | Read | '1' indicates a high or low limit has been exceeded.                 |

| 3   | CH3    | Read | '1' indicates a high or low limit has been exceeded.                 |

| 4   | CH4    | Read | '1' indicates a high or low limit has been exceeded.                 |

| 5   | CH5    | Read | '1' indicates a high or low limit has been exceeded.                 |

| 6   | CH6    | Read | '1' indicates a high or low limit has been exceeded.                 |

| 7   | ĪNT_IN | Read | '1' indicates that a low signal has been detected on the INT_IN pin. |

### Table 5. Interrupt Status Register 2 (Address = 02h, Default = xxh; see Table 2)

| BIT | NAME            | TYPE | DESCRIPTION                                                                                                                                                                                       |

|-----|-----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Hot Temperature | Read | '1' indicates a high or low limit has been exceeded. One-Time Interrupt and Default Interrupt modes are supported and can be set by bit 6 of Interrupt Mask Register 2 (address 04h).             |

| 1   | BTI             | Read | '1' indicates that an interrupt has occurred from the BTI input pin.                                                                                                                              |

| 2   | FAN 1           | Read | '1' indicates that a fan count limit has been exceeded.                                                                                                                                           |

| 3   | FAN 2           | Read | '1' indicates that a fan count limit has been exceeded.                                                                                                                                           |

| 4   | GPI/CI          | Read | '1' indidates that GPI/CI has gone high.                                                                                                                                                          |

| 5   | ŌS              | Read | '1' indicates a high or low temperature limit has been exceeded. One-Time Interrupt and Default Interrupt modes are supported and can be set by bit 7 of Interrupt Mask Register 2 (address 04h). |

| 6   | Reserved        | Read | This bit is reserved.                                                                                                                                                                             |

| 7   | Reserved        | Read | This bit is reserved.                                                                                                                                                                             |

### 7.5.3 Interrupt Mask Registers

### Table 6. Interrupt Mask Register 1 (Address = 03h, Default = 00h)

| BIT | NAME   | TYPE | DESCRIPTION                                                                                  |

|-----|--------|------|----------------------------------------------------------------------------------------------|

| 0   | CH0    | R/W  |                                                                                              |

| 1   | CH1    | R/W  |                                                                                              |

| 2   | CH2    | R/W  |                                                                                              |

| 3   | CH3    | R/W  | Id disables the sources and is a intermed state whit in Table 4 to be seen the INIT intermed |

| 4   | CH4    | R/W  | '1' disables the corresponding interrupt status bit in Table 4 to trigger the INT interrupt. |

| 5   | CH5    | R/W  |                                                                                              |

| 6   | CH6    | R/W  |                                                                                              |

| 7   | ĪNT_IN | R/W  |                                                                                              |

### Table 7. Interrupt Mask Register 2 (Address = 04h, Default = 00h)

| BIT | NAME                         | TYPE | DESCRIPTION                                                                                  |

|-----|------------------------------|------|----------------------------------------------------------------------------------------------|

| 0   | Hot Temperature              | R/W  |                                                                                              |

| 1   | BTI                          | R/W  |                                                                                              |

| 2   | FAN 1                        | R/W  | 141 disables the sources of inglishes with the trible for the tribute the INIT interment     |

| 3   | FAN 2                        | R/W  | '1' disables the corresponding interrupt status bit in Table 5 to trigger the INT interrupt. |

| 4   | GPI/CI                       | R/W  |                                                                                              |

| 5   | ŌS                           | R/W  |                                                                                              |

| 6   | INT Interrupt Mode<br>Select | R/W  | '0' selects Default Interrupt mode. '1' selects One-Time Interrupt mode.                     |

| 7   | OS Interrupt Mode<br>Select  | R/W  | '0' selects Comparator mode. '1' selects One-Time Interrupt mode.                            |

# 7.5.4 Fan Divisor/RST\_OUT/OS Register

# Table 8. Fan Divisor/RST\_OUT/OS Register (Address = 05h, Default = 14h)

| BIT | NAME               | TYPE | DESCRIPTION                                                                                                                                                                                                    |

|-----|--------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | FAN1 Mode Select   | R/W  | '1' selects the level-sensitive input mode. '0' selects the fan count mode for the FAN1 input.                                                                                                                 |

| 1   | FAN2 Mode Select   | R/W  | '1' selects the level-sensitive input mode. '0' selects the fan count mode for the FAN2 input.                                                                                                                 |

| 2   | FAN1 RPM Control 1 | R/W  | FAN1 speed control:                                                                                                                                                                                            |

| 3   | FAN1 RPM Control 0 | R/W  | '00' = divide by 1. '01' = divide by 2. '10' = divide by 4. '11' = divide by 8. If level-sensitive input is selected, '01' selects an active-low input and '00' selects an active-high input.                  |

| 4   | FAN2 RPM Control 1 | R/W  | FAN2 speed control:                                                                                                                                                                                            |

| 5   | FAN2 RPM Control 0 | R/W  | '00' = divide by 1. '01' = divide by 2. '10' = divide by 4. '11' = divide by 8. If level select input is selected, '01' selects an active-low input and '00' selects an active-high input.                     |

| 6   | OS Pin Enable      | R/W  | '1' enables $\overline{\text{OS}}$ mode on the $\overline{\text{RST\_OUT/OS}}$ pin when bit 7 is set to '0'. NOTE: When bits 6 and 7 are both set to '1', the $\overline{\text{RST\_OUT/OS}}$ pin is disabled. |

| 7   | RST_OUT Pin Enable | R/W  | '1' enables RST_OUT mode on the RST_OUT/OS pin when bit 6 is set to '0'.  NOTE: When bits 6 and 7 are both set to '1', the RST_OUT/OS pin is disabled.                                                         |

### 7.5.5 OS Configuration/Temperature Resolution Register

# Table 9. OS Configuration/Temperature Resolution Register (Address = 06h, Default = x1h; see Table 2)

| BIT | NAME                              | TYPE | DESCRIPTION                                                                                                                                |

|-----|-----------------------------------|------|--------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | OS Status                         | Read | This bit mirrors the state of the RST_OUT/OS pin when in OS mode.                                                                          |

| 1   | OS Polarity                       | R/W  | '1' selects $\overline{\text{OS}}$ to be active-high '0' selects $\overline{\text{OS}}$ to be active-low.                                  |

| 2   | OS Mode Select                    | R/W  | '1' selects One-Time-Interrupt mode; '0' selects Comparator mode.                                                                          |

| 3   | Temperature<br>Resolution Control | R/W  | '1' selects 11-bit plus sign resolution temperature conversion; '0' selects the default 8-bit plus sign resolution temperature conversion. |

| 4   | Temp3                             | R/W  |                                                                                                                                            |

| 5   | Temp2                             | R/W  | The lower four LSBs of the 11-bit plus sign temperature data. For 8-bit plus sign temperature                                              |

| 6   | Temp1                             | R/W  | data, bit 7 is the LSB and bits 4 to 6 are undefined.                                                                                      |

| 7   | Temp0                             | R/W  |                                                                                                                                            |

### 7.5.6 Conversion Rate Register

Table 10. Conversion Rate Register (Address = 07h, Default = 40h)

| BIT | NAME     | TYPE | DESCRIPTION                                                                                                                                                                                                                                                           |

|-----|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | CR1      | R/W  | Controls conversion rate:  '0' = Programmable conversion rate by the following formula:  Monitoring delay = $(ms) = 1.42 \times (8 \times N + 6)$ where $N$ can be set by bits 7:0 in the Conversion Rate Count Register (address 0Bh).  '1' = Continuous conversion. |

| 1   | Reserved | R/W  | '0' must be written to this bit.                                                                                                                                                                                                                                      |

| 2   | Reserved | R/W  | '0' must be written to this bit.                                                                                                                                                                                                                                      |

| 3   | Reserved | R/W  | '0' must be written to this bit.                                                                                                                                                                                                                                      |

| 4   | Reserved | R/W  | '0' must be written to this bit.                                                                                                                                                                                                                                      |

| 5   | Reserved | R/W  | '0' must be written to this bit.                                                                                                                                                                                                                                      |

| 6   | Reserved | R/W  | '0' must be written to this bit.                                                                                                                                                                                                                                      |

| 7   | Reserved | R/W  | '0' must be written to this bit.                                                                                                                                                                                                                                      |

### 7.5.7 Voltage/Temperature Channel Disable Register

Table 11. Voltage/Temperature Channel Disable Register (Address = 08h, Default = 00h)

| BIT | NAME | TYPE | DESCRIPTION                                                                                         |

|-----|------|------|-----------------------------------------------------------------------------------------------------|

| 0   | CH0  | R/W  | '1' disables conversions and suppresses error events; Value RAM Register reads '0' for CH0.         |

| 1   | CH1  | R/W  | '1' disables conversions and suppresses error events; Value RAM Register reads '0' for CH1.         |

| 2   | CH2  | R/W  | '1' disables conversions and suppresses error events; Value RAM Register reads '0' for CH2.         |

| 3   | CH3  | R/W  | '1' disables conversions and suppresses error events; Value RAM Register reads '0' for CH3.         |

| 4   | CH4  | R/W  | '1' disables conversions and suppresses error events; Value RAM Register reads '0' for CH4.         |

| 5   | CH5  | R/W  | '1' disables conversions and suppresses error events; Value RAM Register reads '0' for CH5.         |

| 6   | CH6  | R/W  | '1' disables conversions and suppresses error events; Value RAM Register reads '0' for CH6.         |

| 7   | Temp | R/W  | '1' disables conversions and suppresses error events; Value RAM Register reads '0' for temperature. |

### 7.5.8 Input Mode Register

### Table 12. Input Mode Register (Address = 09h, Default = 00h)

| BIT | NAME     | TYPE | DESCRIPTION                                                                                                                                                                                                               |

|-----|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Diff01   | R/W  | When set to '1', CH0 and CH1 operate as a differential input. When set to '0', CH0 and CH1 operate as 2 single-ended inputs.                                                                                              |

| 1   | Pol01    | R/W  | When bit 0 = '1', CH0 and CH1 differential inputs are setup in normal polarity mode when this bit is set to '1', and in reverse polarity mode when this bit is set to '0'. When bit 0 is set to "0", this bit is ignored. |

| 2   | Diff23   | R/W  | When set to '1', CH2 and CH3 operate as a differential input. When set to '0', CH2 and CH3 operate as 2 single-ended inputs.                                                                                              |

| 3   | Pol23    | R/W  | When bit 0 = '1', CH2 and CH3 differential inputs are setup in normal polarity mode when this bit is set to '1', and in reverse polarity mode when this bit is set to '0'. When bit 0 is set to "0", this bit is ignored. |

| 4   | Diff45   | R/W  | When set to '1', CH4 and CH5 operate as a differential input. When set to '0', CH4 and CH5 operate as 2 single-ended inputs.                                                                                              |

| 5   | Pol45    | R/W  | When bit 0 = '1', CH4 and CH5 differential inputs are setup in normal polarity mode when this bit is set to '1', and in reverse polarity mode when this bit is set to '0'. When bit 0 is set to "0", this bit is ignored. |

| 6   | Reserved | R/W  | '0' must be written to this bit.                                                                                                                                                                                          |

| 7   | Reserved | R/W  | '0' must be written to this bit.                                                                                                                                                                                          |

### 7.5.9 ADC Control Register

# Table 13. ADC Control Register (Address = 0Ah, Default = 02h)

| BIT | NAME     | TYPE | DESCRIPTION                                                                                                                                                        |

|-----|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | DR2      | R/W  | The 10-bit ADC conversion rate for the analog inputs is set as follows:                                                                                            |

| 1   | DR1      | R/W  | 000 = 0.512 kHz<br>001 = 1 kHz                                                                                                                                     |

| 2   | DR0      | R/W  | 010 = 1.98 kHz<br>011 = 3.6 kHz<br>100 = 6.3 kHz<br>101 = 9.8 kHz<br>110 = 13.15 kHz<br>111 = 13.15 kHz                                                            |

| 3   | PGA2     | R/W  | The full-scale analog input range is set as follows:                                                                                                               |

| 4   | PGA1     | R/W  | 000 = 2.56 V<br>001 = V <sub>DD</sub>                                                                                                                              |

| 5   | PGA0     | R/W  | 010 = V <sub>DD</sub><br>010 = 4.096 V or V <sub>DD</sub> (whichever is less)<br>011 = 2.048 V<br>100 = 1.024 V<br>101 = 0.512 V<br>110 = 0.256 V<br>111 = 0.256 V |

| 6   | Reserved | R/W  | '0' must be written to this bit.                                                                                                                                   |

| 7   | Reserved | R/W  | '0' must be written to this bit.                                                                                                                                   |

### 7.5.10 Conversion Rate Count Register

Table 14. Conversion Rate Count Register (Address = 0Bh, Default = 40h)

| BIT | NAME | TYPE | DESCRIPTION                                                                            |

|-----|------|------|----------------------------------------------------------------------------------------|

| 0   | CRC7 | R/W  |                                                                                        |

| 1   | CRC6 | R/W  | When bit 0 of the Conversion Rate Register (address 07h) is set to '0', the monitoring |

| 2   | CRC5 | R/W  | conversion delay can be programmed as follows:                                         |

| 3   | CRC4 | R/W  | 0000000 = 0<br>0000001 = 1<br>0000010 = 2<br><br>1111111 = 255                         |

| 4   | CRC3 | R/W  |                                                                                        |

| 5   | CRC2 | R/W  |                                                                                        |

| 6   | CRC1 | R/W  | When bit 0 of the Conversion Rate Register is set to '1', these bits are ignored.      |

| 7   | CRC0 | R/W  |                                                                                        |

### 7.5.11 Value Ram Register

Table 15. Value RAM Register (Addresses = 20h to 3Fh)

| ADDRESS (HEX) | DESCRIPTION                                                   |

|---------------|---------------------------------------------------------------|

| 20            | CH0 reading (10-bit)                                          |

| 21            | CH1 reading (10-bit)                                          |

| 22            | CH2 reading (10-bit)                                          |

| 23            | CH3 reading (10-bit)                                          |

| 24            | CH4 reading (10-bit)                                          |

| 25            | CH5 reading (10-bit)                                          |

| 26            | CH6 reading (10-bit)                                          |

| 27            | Temperature reading (9-bit or 12-bit for easy readback)       |

| 28            | FAN1 reading                                                  |

| 29            | FAN2 reading                                                  |

| 2A            | CH0 high limit                                                |

| 2B            | CH0 low limit                                                 |

| 2C            | CH1 high limit                                                |

| 2D            | CH1 low limit                                                 |

| 2E            | CH2 high limit                                                |

| 2F            | CH2 low limit                                                 |

| 30            | CH3 high limit                                                |

| 31            | CH3 low limit                                                 |

| 32            | CH4 high limit                                                |

| 33            | CH4 low limit                                                 |

| 34            | CH5 high limit                                                |

| 35            | CH5 low limit                                                 |

| 36            | CH6 high limit                                                |

| 37            | CH6 low limit                                                 |

| 38            | Hot temperature high limit (T <sub>HOT</sub> )                |

| 39            | Hot temperature hysteresis low limit (T <sub>HOT_HYST</sub> ) |

| 3A            | OS temperature high limit (T <sub>OS</sub> )                  |

| 3B            | OS temperature hysteresis low limit (T <sub>OS_HYST</sub> )   |

| 3C            | FAN1 fan count limit                                          |

| 3D            | FAN2 fan count limit                                          |

| 3E            | Manufacturer ID (always defaults to 80h)                      |

| 3F            | Die revision ID (always defaults to 08h)                      |

## 8 Application and Implementation

#### NOTE