### 4.5V to 18V Input, 4-A Synchronous Step-Down SWIFT™ Converter with Eco-Mode™

Check for Samples: TPS54426

#### **FEATURES**

- D-CAP2<sup>™</sup> Mode Enables Fast Transient Response

- Low Output Ripple and Allows Ceramic Output Capacitor

- Wide V<sub>IN</sub> Input Voltage Range: 4.5 V to 18 V

- Output Voltage Range: 0.76 V to 5.5 V

- Highly Efficient Integrated FET's Optimized for Lower Duty Cycle Applications

- 65 mΩ (High Side) and 55 mΩ (Low Side)

- High Efficiency, less than 10 µA at shutdown

- High Initial Bandgap Reference Accuracy

- · Adjustable Soft Start

- Pre-Biased Soft Start

- 700-kHz Switching Frequency (f<sub>SW</sub>)

- Cycle By Cycle Over Current Limit

- Power Good Output

- Auto-Skip Eco-mode<sup>™</sup> for High Efficiency at Light Load

#### **APPLICATIONS**

- Wide Range of Applications for Low Voltage System

- Digital TV Power Supply

- High Definition Blu-ray Disc™ Players

- Networking Home Terminal

- Digital Set Top Box (STB)

#### DESCRIPTION

The TPS54426 is an adaptive on-time D-CAP2™ mode synchronous buck converter. The TPS54426 enables system designers to complete the suite of various end equipment's power bus regulators with a cost effective, low component count, low standby current solution. The main control loop for the TPS54426 uses the D-CAP2™ mode control which provides a very fast transient response with no external compensation components. The adaptive on-time control supports seamless transition between PWM mode at higher load conditions Eco-mode™ operation at light loads. Eco-mode™ allows the TPS54426 to maintain high efficiency during lighter load conditions. The TPS54426 also has a proprietary circuit that enables the device to adopt to both low equivalent series resistance (ESR) output capacitors, such as POSCAP, SP-CAP, and ultra-low ESR ceramic capacitors. The device operates from 4.5-V to 18-V VIN input. The output voltage can be programmed between 0.76 V and 5.5 V. The device also features an adjustable soft start time and a power good function. The TPS54426 is available in the 14-pin HTSSOP package and the 16 pin QFN package, designed to operate from -40°C to 85°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

D-CAP2, Eco-mode, PowerPAD are trademarks of Texas Instruments.

Blu-ray Disc is a trademark of Blu-ray Disc Association.

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### ORDERING INFORMATION(1)

| T <sub>A</sub> | PACKAGE <sup>(2) (3)</sup>   | ORDERABLE PART NUMBER | PIN | TRANSPORT MEDIA |  |

|----------------|------------------------------|-----------------------|-----|-----------------|--|

|                | PowerPAD™                    | TPS54426PWP           | 1.1 | Tube            |  |

| 45°C to 95°C   | (HTSSOP) – PWP               | TPS54426PWPR          | 14  | Tape and Reel   |  |

| –45°C to 85°C  | Plastic Quad Flat Pack (OFN) |                       | 16  | Tape and Reel   |  |

|                | Plastic Quad Flat Pack (QFN) | TPS54426RSAR          | 16  | Tape and Reel   |  |

- (1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

- Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

- (3) All package options have Cu NIPDAU lead/ball finish.

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted) (1)

|                   |                        |                                           | VALUE       | UNIT |

|-------------------|------------------------|-------------------------------------------|-------------|------|

|                   |                        | V <sub>IN1</sub> , V <sub>IN2</sub> , EN  | -0.3 to 20  | V    |

|                   |                        | V <sub>BST</sub>                          | -0.3 to 26  | V    |

| V                 | Input voltage range    | V <sub>BST</sub> (10 ns transient)        | -0.3 to 28  | V    |

| VI                |                        | V <sub>FB</sub> , V <sub>O</sub> , SS, PG | -0.3 to 6.5 | V    |

|                   |                        | SW1, SW2                                  | –2 to 20    | V    |

|                   |                        | SW1, SW2 (10 ns transient)                | -3 to 22    | V    |

| V                 | Output valtage renge   | V <sub>REG5</sub>                         | -0.3 to 6.5 | V    |

| Vo                | Output voltage range   | P <sub>GND1</sub> , P <sub>GND2</sub>     | -0.3 to 0.3 | V    |

| V <sub>diff</sub> | Voltage from GND to F  | OWERPAD                                   | -0.2 to 0.2 | V    |

| ECDti             | Electrostatic          | Human Body Model (HBM)                    | 2           | kV   |

| ESD rating        | discharge              | Charged Device Model (CDM)                | 500         | V    |

| $T_J$             | Operating junction tem | perature                                  | -40 to 150  | °C   |

| T <sub>stg</sub>  | Storage temperature    |                                           | -55 to 150  | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### THERMAL INFORMATION

| 111111111        | MAE IN ORMATION                                                                                                             |               |               |       |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------|---------------|-------|--|--|--|

|                  | THERMAL METRIC(1)                                                                                                           | TPS:          | TPS54426      |       |  |  |  |

|                  | Junction-to-case (top) thermal resistance  Junction-to-board thermal resistance  Junction-to-top characterization parameter | PWP (14) PINS | RSA (16) PINS | UNITS |  |  |  |

| $\theta_{JA}$    | Junction-to-ambient thermal resistance                                                                                      | 55.6          | 37.3          |       |  |  |  |

| $\theta_{JCtop}$ | Junction-to-case (top) thermal resistance                                                                                   | 51.3          | 42.5          |       |  |  |  |

| $\theta_{JB}$    | Junction-to-board thermal resistance                                                                                        | 36.4          | 14.9          | °C/W  |  |  |  |

| ΨЈТ              | Junction-to-top characterization parameter                                                                                  | 1.8           | 0.8           | C/VV  |  |  |  |

| $\Psi_{JB}$      | Junction-to-board characterization parameter                                                                                | 20.6          | 14.8          |       |  |  |  |

| $\theta_{JCbot}$ | Junction-to-case (bottom) thermal resistance                                                                                | 4.3           | 4.9           |       |  |  |  |

| □JCbot           | Junction-to-case (bottom) thermal resistance                                                                                | 4.3           | 4.9           |       |  |  |  |

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

2

Product Folder Link(s): TPS54426

#### **RECOMMENDED OPERATING CONDITIONS**

over operating free-air temperature range (unless otherwise noted)

|                 |                                |                            | MIN  | MAX | UNIT |

|-----------------|--------------------------------|----------------------------|------|-----|------|

| V <sub>IN</sub> | Supply input voltage range     |                            | 4.5  | 18  | V    |

|                 |                                | VBST                       | -0.3 | 24  |      |

|                 |                                | VBST (10 ns transient)     | -0.3 | 27  |      |

|                 |                                | SS, PG                     | -0.1 | 5.7 |      |

| .,              | lanut valta na na na           | EN                         |      |     | V    |

| VI              | Input voltage range            | VO, VFB                    | -0.1 | 5.5 | V    |

|                 |                                | SW1, SW2                   | -1.8 | 18  |      |

|                 |                                | SW1, SW2 (10 ns transient) | -3   | 21  |      |

|                 |                                | PGND1, PGND2               | -0.1 | 0.1 |      |

| Vo              | Output voltage range           | VREG5                      | -0.1 | 5.7 | V    |

| lo              | Output Current range           | I <sub>VREG5</sub>         | 0    | 10  | mA   |

| T <sub>A</sub>  | Operating free-air temperature |                            | -40  | 85  | °C   |

| TJ              | Operating junction temperature |                            | -40  | 150 | °C   |

#### **ELECTRICAL CHARACTERISTICS**

over operating free-air temperature range,  $V_{IN}$  = 12V (unless otherwise noted)

| PARAMETER            |                                          | TEST CONDITIONS                                                                                                                                                         | MIN | TYP | MAX      | UNIT |  |

|----------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|----------|------|--|

| SUPPLY               | CURRENT                                  |                                                                                                                                                                         |     |     | <u> </u> |      |  |

| I <sub>VIN</sub>     | Operating - non-switching supply current | Operating - non-switching supply current $\begin{vmatrix} V_{IN} \text{ current, } T_A = 25^{\circ}\text{C, EN} = 5 \text{ V,} \\ V_{FB} = 0.8 \text{ V} \end{vmatrix}$ |     |     |          |      |  |

| I <sub>VINSDN</sub>  | Shutdown supply current                  | $V_{IN}$ current, $T_A = 25$ °C, $EN = 0$ V                                                                                                                             |     | 1.8 | 10       | μΑ   |  |

| LOGIC T              | HRESHOLD                                 |                                                                                                                                                                         | •   |     |          |      |  |

| V <sub>ENH</sub>     | EN high-level input voltage              | EN                                                                                                                                                                      | 2   |     |          | V    |  |

| V <sub>ENL</sub>     | EN low-level input voltage               | EN                                                                                                                                                                      |     |     | 0.4      | V    |  |

| V <sub>FB</sub> VOL  | TAGE AND DISCHARGE RESISTANCE            |                                                                                                                                                                         |     |     |          |      |  |

|                      |                                          | VFB voltage light load mode, $T_A = 25$ °C, $V_O = 1.05$ V, $I_O = 10$ mA                                                                                               |     | 771 |          |      |  |

|                      |                                          | $T_A = 25$ °C, $V_O = 1.05$ V, continuous mode                                                                                                                          | 757 | 765 | 773      |      |  |

| $V_{FBTH}$           | V <sub>FB</sub> threshold voltage        | $T_A = 0$ °C to 85 °C, $V_O = 1.05$ V, continuous mode <sup>(1)</sup>                                                                                                   | 753 |     | 777      | mV   |  |

|                      |                                          | $T_A = -40$ °C to 85°C, $V_O = 1.05$ V, continuous mode <sup>(1)</sup>                                                                                                  | 751 |     | 779      |      |  |

| I <sub>VFB</sub>     | V <sub>FB</sub> input current            | V <sub>FB</sub> = 0.8 V, T <sub>A</sub> = 25°C                                                                                                                          |     | 0   | ±0.1     | μA   |  |

| R <sub>Dischg</sub>  | V <sub>O</sub> discharge resistance      | EN = 0 V, V <sub>O</sub> = 0.5 V, T <sub>A</sub> = 25°C                                                                                                                 |     | 50  | 100      | Ω    |  |

| V <sub>REG5</sub> OL | JTPUT                                    | •                                                                                                                                                                       | •   |     |          |      |  |

| V <sub>VREG5</sub>   | V <sub>REG5</sub> output voltage         | T <sub>A</sub> = 25°C, 6 V < V <sub>IN</sub> < 18 V,<br>0 < I <sub>VREG5</sub> < 5 mA                                                                                   | 5.3 | 5.5 | 5.7      | V    |  |

| $V_{LN5}$            | Line regulation                          | 6.0 V < V <sub>IN</sub> < 18 V, I <sub>VREG5</sub> = 5 mA                                                                                                               |     |     | 20       | mV   |  |

| $V_{LD5}$            | Load regulation                          | 0 mA < I <sub>VREG5</sub> < 5 mA                                                                                                                                        |     |     | 100      | mV   |  |

| I <sub>VREG5</sub>   | Output current                           | V <sub>IN</sub> = 6 V, V <sub>REG5</sub> = 4 V, T <sub>A</sub> = 25°C                                                                                                   |     | 70  |          | mA   |  |

| MOSFET               |                                          |                                                                                                                                                                         | *   |     | *        |      |  |

| R <sub>dsonh</sub>   | High side switch resistance              | 25°C, V <sub>BST</sub> - SW1,2 = 5.5 V                                                                                                                                  |     | 63  |          | mΩ   |  |

| R <sub>dsonl</sub>   | Low side switch resistance               | 25°C                                                                                                                                                                    |     | 55  |          | mΩ   |  |

<sup>(1)</sup> Not production tested.

### **ELECTRICAL CHARACTERISTICS (continued)**

over operating free-air temperature range,  $V_{\rm IN}$  = 12V (unless otherwise noted)

|                       | PARAMETER                                 | TEST CONDITIONS                                                             | MIN  | TYP   | MAX  | UNIT |  |

|-----------------------|-------------------------------------------|-----------------------------------------------------------------------------|------|-------|------|------|--|

| CURREN                | T LIMIT                                   | ·                                                                           |      |       |      |      |  |

| I <sub>ocl</sub>      | Current limit                             | L <sub>OUT</sub> = 1.5 μH <sup>(2)</sup> , T <sub>A</sub> = -20 °C to 85 °C | 4.7  | 5.4   | 7.5  | Α    |  |

| THERMA                | L SHUTDOWN                                |                                                                             | ,    |       |      |      |  |

| _                     | The area of a few data was thought at all | Shutdown temperature (2)                                                    |      | 165   |      |      |  |

| T <sub>SDN</sub>      | Thermal shutdown threshold                | Hysteresis (2)                                                              |      | 30    |      | °C   |  |

| ON-TIME               | TIMER CONTROL                             | ·                                                                           |      |       |      |      |  |

| T <sub>ON</sub>       | On time                                   | V <sub>IN</sub> = 12 V, V <sub>O</sub> = 1.05 V                             |      | 145   |      | ns   |  |

| T <sub>OFF(MIN)</sub> | Minimum off time                          | T <sub>A</sub> = 25°C, V <sub>FB</sub> = 0.7 V                              |      | 260   | 310  | ns   |  |

| SOFT ST               | ART                                       |                                                                             |      |       |      |      |  |

| I <sub>SSC</sub>      | SS charge current                         | V <sub>SS</sub> = 0 V                                                       | 1.4  | 2.0   | 2.6  | μΑ   |  |

| I <sub>SSD</sub>      | SS discharge current                      | V <sub>SS</sub> = 0.5 V                                                     | 0.1  | 0.2   |      | mA   |  |

| POWER (               | GOOD                                      | •                                                                           |      |       | •    |      |  |

| \/                    | DC threehold                              | V <sub>FB</sub> rising (good)                                               | 85   | 90    | 95   | %    |  |

| $V_{THPG}$            | PG threshold                              | V <sub>FB</sub> falling (fault)                                             |      | 85    |      | %    |  |

| I <sub>PG</sub>       | PG sink current                           | PG = 0.5 V                                                                  | 2.5  | 5     |      | mA   |  |

| OUTPUT                | UNDERVOLTAGE AND OVERVOLTA                | AGE PROTECTION                                                              |      |       |      |      |  |

| V <sub>OVP</sub>      | Output OVP trip threshold                 | OVP detect                                                                  | 115  | 120   | 125  | %    |  |

| T <sub>OVPDEL</sub>   | Output OVP prop delay                     |                                                                             |      | 10    |      | μs   |  |

| \ /                   | Output IIV/D trip through old             | UVP detect                                                                  | 60   | 65    | 70   | %    |  |

| $V_{UVP}$             | Output UVP trip threshold                 | Hysteresis                                                                  |      | 10    |      | %    |  |

| T <sub>UVPDEL</sub>   | Output UVP delay                          |                                                                             |      | 0.25  |      | ms   |  |

| T <sub>UVPEN</sub>    | Output UVP enable delay                   | Relative to soft-start time                                                 |      | x 1.7 |      |      |  |

| UVLO                  |                                           |                                                                             | •    |       |      |      |  |

| \ /                   | LIV/I O there also also                   | Wake up V <sub>REG5</sub> voltage                                           | 3.5  | 3.8   | 4.1  |      |  |

| $V_{UVLO}$            | UVLO threshold                            | Hysteresis V <sub>REG5</sub> voltage                                        | 0.23 | 0.35  | 0.47 | V    |  |

<sup>(2)</sup> Not production tested.

Product Folder Link(s): TPS54426

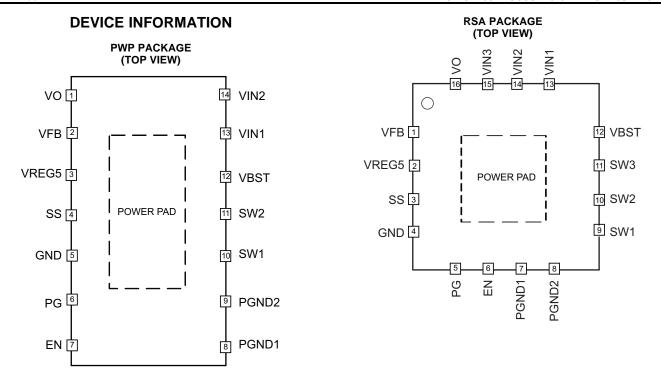

#### **PIN FUNCTIONS**

|                 | PIN       |            | DECORPTION                                                                                                                                                                                   |  |  |  |  |

|-----------------|-----------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME            | NUM       | IBER       | DESCRIPTION                                                                                                                                                                                  |  |  |  |  |

|                 | PWP 14    | RSA 16     |                                                                                                                                                                                              |  |  |  |  |

| VO              | 1         | 16         | Connect to output of converter. This terminal is used for On-Time Adjustment.                                                                                                                |  |  |  |  |

| VFB             | 2         | 1          | Converter feedback input. Connect to output voltage with feedback resistor divider.                                                                                                          |  |  |  |  |

| VREG5           | 3         | 2          | $5.5~V$ power supply output. A capacitor (typical 1 $\mu$ F) should be connected to GND. VREG5 is not active when EN is low.                                                                 |  |  |  |  |

| SS              | 4         | 3          | Soft-start control. A external capacitor should be connected to GND.                                                                                                                         |  |  |  |  |

| GND             | 5         | 4          | Signal ground pin.                                                                                                                                                                           |  |  |  |  |

| PG              | 6         | 5          | Open drain power good output.                                                                                                                                                                |  |  |  |  |

| EN              | 7         | 6          | Enable control input. EN is active high and must be pulled up to enable the device.                                                                                                          |  |  |  |  |

| PGND1,<br>PGND2 | 8, 9      | 7, 8       | Ground returns for low-side MOSFET. Also serve as inputs of current comparators. Connect PGND and GND strongly together near the IC.                                                         |  |  |  |  |

| SW1, SW2        | 10, 11    | 9, 10, 11  | Switch node connection between high-side NFET and low-side NFET. Also serve as inputs to current comparators.                                                                                |  |  |  |  |

| VBST            | 12        | 12         | Supply input for high-side NFET gate driver (boost terminal). Connect capacitor from this pin to respective SW1, SW2 terminals. An internal PN diode is connected between VREG5 to VBST pin. |  |  |  |  |

| VIN1, VIN2      | 13, 14    | 13, 14, 15 | Power input and connected to high side NFET drain. Supply input for 5-V internal linear regulator for the control circuitry.                                                                 |  |  |  |  |

| PowerPAD™       | Back side | Back side  | Thermal pad of the package. Must be soldered to achieve appropriate dissipation. Should be connected to PGND.                                                                                |  |  |  |  |

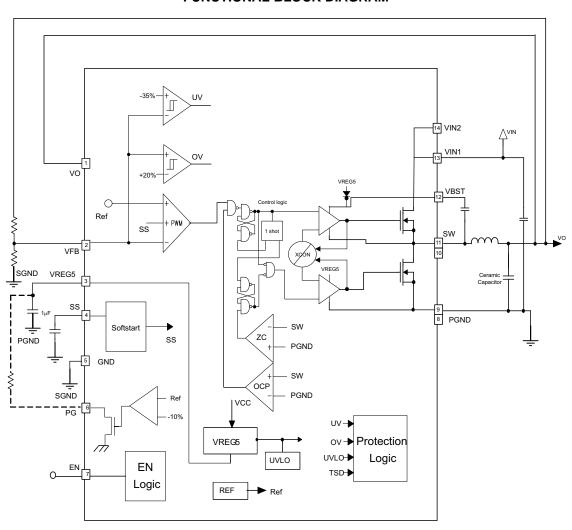

#### **FUNCTIONAL BLOCK DIAGRAM**

A. The block diagram shown is for the PWP 14 pin package. The QFN 16 pin package block diagram is identical except for the pin out.

#### **OVERVIEW**

The TPS54426 is a 4-A synchronous step-down (buck) converter with two integrated N-channel MOSFETs and auto-skip Eco-mode™ to improve light lode efficiency. It operates using D-CAP2™ mode control. The fast transient response of D-CAP2™ control reduces the output capacitance required to meet a specific level of performance. Proprietary internal circuitry allows the use of low ESR output capacitors including ceramic and special polymer types.

#### **DETAILED DESCRIPTION**

#### **PWM Operation**

The main control loop of the TPS54426 is an adaptive on-time pulse width modulation (PWM) controller that supports a proprietary D-CAP2™ mode control. D-CAP2™ mode control combines constant on-time control with an internal compensation circuit for pseudo-fixed frequency and low external component count configuration with both low ESR and ceramic output capacitors. It is stable with virtually no ripple at the output.

At the beginning of each cycle, the high-side MOSFET is turned on. The MOSFET is turned off after the internal one-shot timer expires. The one-shot timer is set by the converter input voltage, VIN, and the output voltage, VO, to maintain a pseudo-fixed frequency over the input voltage range, hence it is called adaptive on-time control. The one-shot timer is reset and the high-side MOSFET is turned on again when the feedback voltage falls below the reference voltage. An internal ramp is added to reference voltage to simulate output ripple, eliminating the need for ESR induced output ripple from D-CAP2<sup>TM</sup> mode control.

#### **PWM Frequency and Adaptive On-Time Control**

TPS54426 uses an adaptive on-time control scheme and does not have a dedicated on board oscillator. The TPS54426 runs with a pseudo-constant frequency of 700 kHz by using the input voltage and output voltage to set the on-time one-shot timer. The on-time is inversely proportional to the input voltage and proportional to the output voltage, therefore, when the duty ratio is VOUT/VIN, the frequency is constant.

#### Auto-Skip Eco-Mode™ Control

The TPS54426 is designed with Auto-Skip Eco-mode<sup>TM</sup> to increase light load efficiency. As the output current decreases from heavy load condition, the inductor current is also reduced and eventually comes to point that its rippled valley touches zero level, which is the boundary between continuous conduction and discontinuous conduction modes. The rectifying MOSFET is turned off when its zero inductor current is detected. As the load current further decreases the converter run into discontinuous conduction mode. The on-time is kept almost the same as is was in the continuous conduction mode so that it takes longer time to discharge the output capacitor with smaller load current to the level of the reference voltage. The transition point to the light load operation  $I_{OUT(LL)}$  current can be calculated in Equation 1.

$$I_{OUT(LL)} = \frac{1}{2 \cdot L \cdot fsw} = \frac{\left(V_{IN} - V_{OUT}\right) \cdot V_{OUT}}{V_{IN}} \tag{1}$$

#### Soft Start and Pre-Biased Soft Start

The soft start function is adjustable. When the EN pin becomes high, 2  $\mu$ A current begins charging the capacitor which is connected from the SS pin to GND. Smooth control of the output voltage is maintained during start up. The equation for the slow start time is shown in Equation 2. VFB voltage is 0.765 V and SS pin source current is 2  $\mu$ A.

$$Tss(ms) = \frac{C6(nF) \cdot Vref}{Iss(\mu A)} = \frac{C6(nF) \cdot 0.765}{2}$$

(2)

The TPS54426 contains a unique circuit to prevent current from being pulled from the output during startup if the output is pre-biased. When the soft-start commands a voltage higher than the pre-bias level (internal soft start becomes greater than feedback voltage  $V_{FB}$ ), the controller slowly activates synchronous rectification by starting the first low side FET gate driver pulses with a narrow on-time. It then increments that on-time on a cycle-by-cycle basis until it coincides with the time dictated by (1-D), where D is the duty cycle of the converter. This scheme prevents the initial sinking of the pre-bias output, and ensure that the out voltage (VO) starts and ramps up smoothly into regulation and the control loop is given time to transition from pre-biased start-up to normal mode operation.

#### **Power Good**

The TPS54426 has power-good open drain output. The power good function is activated after soft start has finished. The power good function becomes active after 1.7 times soft-start time. When the output voltage is within -10% of the target value, internal comparators detect power good state and the power good signal becomes high. Rpg resister value ,which is connected between PG and VREG5, is required from  $20k\Omega$  to  $150k\Omega$ . If the feedback voltage goes under 15% of the target value, the power good signal becomes low after a 5  $\mu$ s internal delay.

#### VREG5

VREG5 is an internally generated voltage source used by the TPS54425. It is derived directly from the input voltage and is nominally regulated to 5.5 V when the input voltage is above 5.6 V. The output of the VREG5 regulator is the input to the internal UVLO function. VREG5 must be above the UVLO wake up threshold voltage (3.8 V typical) for the TPS54425 to function. Connect a 1.0 µF capacitor between pin 3 of the TPS54425 and power ground for proper regulation of the VREG5 output. The VREG5 output voltage is available for external use and can typically source up to 70 mA. The VREG5 output is disabled when the TPS54425 EN pin is open or pulled low.

#### **Output Discharge Control**

TPS54426 discharges the output when EN is low, or the controller is turned off by the protection functions (OVP, UVP, UVLO and thermal shutdown). The output is discharged by an internal  $50-\Omega$  MOSFET which is connected from VO to PGND. The internal low-side MOSFET is not turned on during the output discharge operation to avoid the possibility of causing negative voltage at the output.

#### **Current Protection**

The output overcurrent protection (OCP) is implemented using a cycle-by-cycle valley detect control circuit. The switch current is monitored by measuring the low-side FET switch voltage between the SW pin and GND. This voltage is proportional to the switch current. To improve accuracy, the voltage sensing is temperature compensated.

During the on-time of the high-side FET switch, the switch current increases at a linear rate determined by  $V_{IN}$ ,  $V_{OUT}$ , the on-time, and the output inductor value. During the on-time of the low-side FET switch, this current decreases linearly. The average value of the switch current is the load current  $I_{OUT}$ . If the measured voltage is above the voltage proportional to the current limit. Then, the device constantly monitors the low-side FET switch voltage, which is proportional to the switch current, during the low-side on-time.

The converter maintains the low-side switch on until the measured voltage is below the voltage corresponding to the current limit at which time the switching cycle is terminated and a new switching cycle begins. In subsequent switching cycles, the on-time is set to a fixed value and the current is monitored in the same manner.

There are some important considerations for this type of overcurrent protection. The load current one half of the peak-to-peak inductor current higher than the overcurrent threshold. Also when the current is being limited, the output voltage tends to fall as the demanded load current may be higher than the current available from the converter. This may cause the output under-voltage protection circuit to be activated. When the overcurrent condition is removed, the output voltage will return to the regulated value. This protection is non-latching.

#### **Over/Under Voltage Protection**

TPS54426 monitors a resistor divided feedback voltage to detect over and under voltage. When the feedback voltage becomes higher than 120% of the target voltage, the OVP comparator output goes high and the circuit latches as the high-side MOSFET driver turns off and the low-side MOSFET turns on. When the feedback voltage becomes lower than 65% of the target voltage, the UVP comparator output goes high and an internal UVP delay counter begins. After 250  $\mu$ s, the device latches off both internal top and bottom MOSFET. This function is enabled approximately 1.7 x softstart time.

#### **UVLO Protection**

Undervoltage lock out protection (UVLO) monitors the voltage of the  $V_{REG5}$  pin. When the  $V_{REG5}$  voltage is lower than UVLO threshold voltage, the TPS54426 is shut off. This is protection is non-latching.

8

#### **Thermal Shutdown**

TPS54426 monitors the temperature of itself. If the temperature exceeds the threshold value (typically 165°C), the device is shut off. This is non-latch protection.

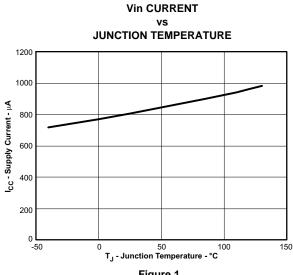

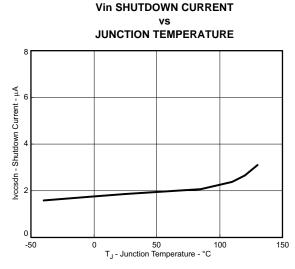

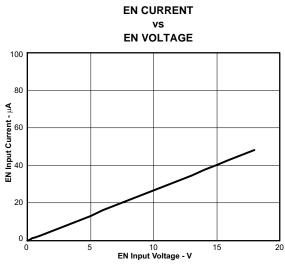

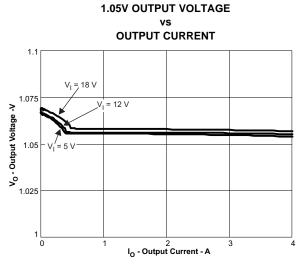

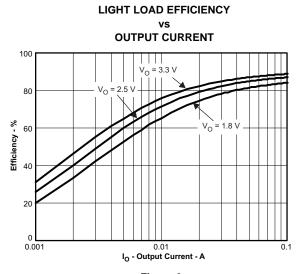

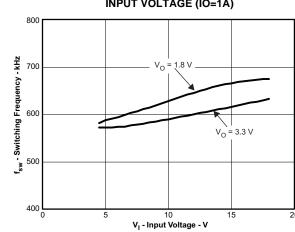

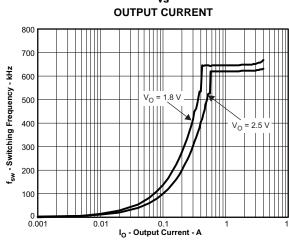

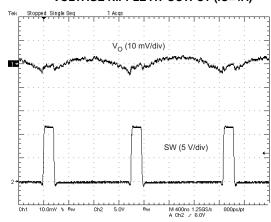

#### TYPICAL CHARACTERISTICS

Figure 1.

Figure 2.

Figure 3.

Figure 4.

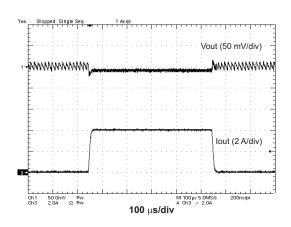

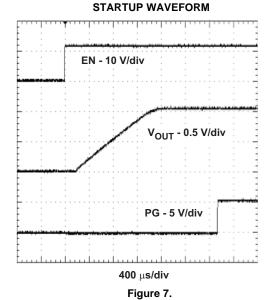

### **TYPICAL CHARACTERISTICS (continued)**

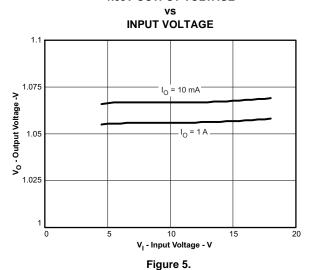

#### 1.05V OUTPUT VOLTAGE

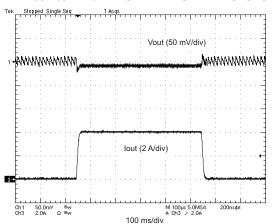

#### 1.05V 50mA to 4A LOAD TRANSIENT RESPONSE

Figure 6.

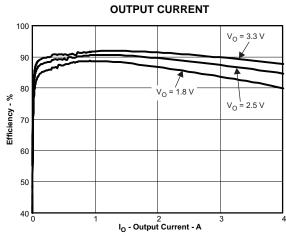

### EFFICIENCY vs

Figure 8.

### **TYPICAL CHARACTERISTICS (continued)**

#### SWITCHING FREQUENCY vs INPUT VOLTAGE (IO=1A)

Figure 9.

WITCHING FREQUENCY

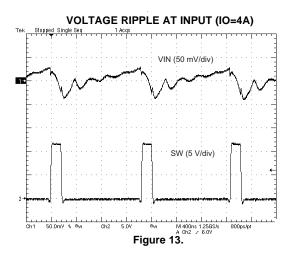

**VOLTAGE RIPPLE AT OUTPUT (IO=4A)**

Figure 10.

Figure 11.

Figure 12.

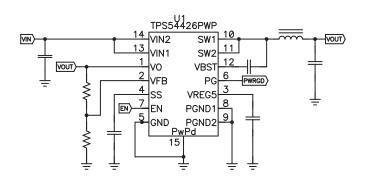

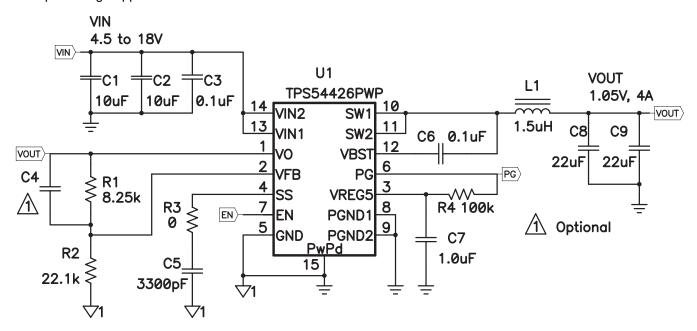

#### **DESIGN GUIDE**

#### Step By Step Design Procedure

To begin the design process, you must know a few application parameters:

- Input voltage range

- Output voltage

- · Output current

- · Output voltage ripple

- · Input voltage ripple

Figure 14. Schematic Diagram for This Design Example

#### **Output Voltage Resistors Selection**

The output voltage is set with a resistor divider from the output node to the VFB pin. It is recommended to use 1% tolerance or better divider resistors. Start by using Equation 3 and Equation 4 to calculate V<sub>OUT</sub>

To improve efficiency at very light loads consider using larger value resistors, too high of resistance will be more susceptible to noise and voltage errors from the VFB input current will be more noticeable

For output voltage from 0.76 V to 2.5 V:

$$V_{OUT} = 0.765 \bullet \left(1 + \frac{R1}{R2}\right) \tag{3}$$

For output voltage over 2.5 V:

$$V_{OUT} = (0.763 + 0.0017 \bullet V_{OUT\_SET}) \bullet \left(1 + \frac{R1}{R2}\right)$$

(4)

Where:

$V_{OUT\ SET} = Target\ V_{OUT}\ voltage$

#### **Output Filter Selection**

The output filter used with the TPS54426 is an LC circuit. This LC filter has double pole at:

$$F_{P} = \frac{1}{2\pi\sqrt{L_{OUT} \times C_{OUT}}}$$

(5)

At low frequencies, the overall loop gain is set by the output set-point resistor divider network and the internal gain of the TPS54426. The low frequency phase is 180 degrees. At the output filter pole frequency, the gain rolls off at a -40 dB per decade rate and the phase drops rapidly. D-CAP2™ introduces a high frequency zero that reduces the gain roll off to -20 dB per decade and increases the phase to 90 degrees one decade above the zero frequency. The inductor and capacitor selected for the output filter must be selected so that the double pole of Equation 5 is located below the high frequency zero but close enough that the phase boost provided be the high frequency zero provides adequate phase margin for a stable circuit. To meet this requirement use the values recommended in Table 1

C4 (pF)<sup>(1)</sup> Output Voltage (V) R1 ( $k\Omega$ ) R2 ( $k\Omega$ ) L1 (µH)  $C8 + C9 (\mu F)$ 1.5 6.81 22.1 22 - 68 1.05 1.5 8.25 22.1 22 - 68 1.2 12.7 22.1 1.5 22 - 68 2.2 1.8 30.1 22.1 10 - 22 22 - 68 2.5 49.9 22.1 10 - 22 2.2 22 - 68 3.3 73.2 2.2 22 - 68 22.1 10 - 22 5 3.3 121 22.1 10 - 22 22 - 68

**Table 1. Recommended Component Values**

#### (1) Optional

For higher output voltages at or above 1.8 V, additional phase boost can be achieved by adding a feed forward capacitor (C4) in parallel with R1.

Since the DC gain is dependent on the output voltage, the required inductor value will increase as the output voltage increases. For higher output voltages above 1.8 V, additional phase boost can be achieved by adding a feed forward capacitor (C4) in parallel with R1

The inductor peak-to-peak ripple current, peak current and RMS current are calculated using Equation 6, Equation 7 and Equation 8. The inductor saturation current rating must be greater than the calculated peak current and the RMS or heating current rating must be greater than the calculated RMS current. Use 700 kHz for  $f_{\text{SW}}$ .

$$Ilp - p = \frac{V_{OUT}}{V_{IN\,(max)}} \bullet \frac{V_{IN\,(max)} - V_{OUT}}{L_O \bullet f_{SW}}$$

$$\tag{6}$$

$$I_{lpeak} = I_O + \frac{Ilp - p}{2} \tag{7}$$

$$I_{Lo(RMS)} = \sqrt{I_o^2 + \frac{1}{12} I l p - p^2}$$

(8)

For this design example, the calculated peak current is 4.47A and the calculated RMS current is 4.009 A. The inductor used is a TDK SPM6530-1R5M100 with a peak current rating of 11.5 A and an RMS current rating of 11 A.

The capacitor value and ESR determines the amount of output voltage ripple. The TPS54426 is intended for use with ceramic or other low ESR capacitors. Recommended values range from 22uF to 68uF. Use Equation 9 to determine the required RMS current rating for the output capacitor

$$I_{CO(RMS)} = \frac{V_{OUT} \bullet (V_{IN} - V_{OUT})}{\sqrt{12} \bullet V_{IN} \bullet L_O \bullet f_{SW}}$$

(9)

For this design two TDK C3216X5R0J226M 22uF output capacitors are used. The typical ESR is 2 m $\Omega$  each. The calculated RMS current is .271A and each output capacitor is rated for 4A.

#### **Input Capacitor Selection**

The TPS54426 requires an input decoupling capacitor and a bulk capacitor is needed depending on the application. A ceramic capacitor over 10 uF. is recommended for the decoupling capacitor. An additional 0.1  $\mu$ F capacitor from pin 14 to ground is recommended to improve the stability of the over-current limit function. The capacitor voltage rating needs to be greater than the maximum input voltage.

#### **Bootstrap Capacitor Selection**

A 0.1  $\mu$ F ceramic capacitor must be connected between the VBST to SW pin for proper operation. It is recommended to use a ceramic capacitor.

#### **VREG5 Capacitor Selection**

A 1.0  $\mu$ F ceramic capacitor must be connected between the VREG5 to GND pin for proper operation. It is recommended to use a ceramic capacitor.

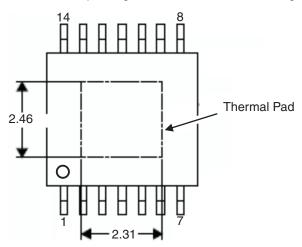

#### THERMAL INFORMATION

This PowerPad™ package incorporates an exposed thermal pad that is designed to be directly to an external heatsink. The thermal pad must be soldered directly to the printed board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD™ package and how to use the advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD™ Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD™ Made Easy, Texas Instruments Literature No. SLMA004.

The exposed thermal pad dimensions for this package are shown in the following illustration.

Figure 15. Thermal Pad Dimensions

Product Folder Link(s): TPS54426

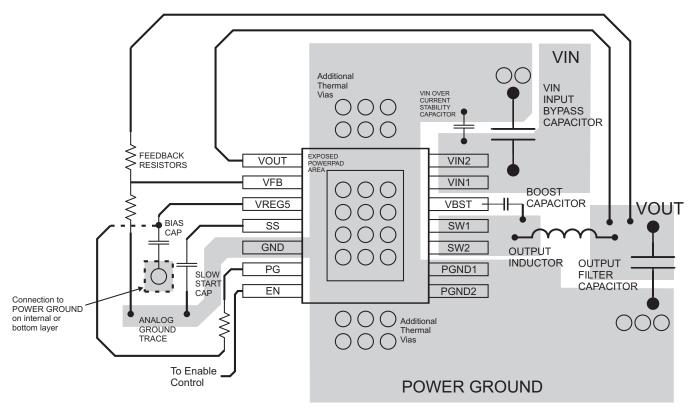

#### LAYOUT CONSIDERATIONS

- 1. Keep the input switching current loop as small as possible.

- 2. Keep the SW node as physically small and short as possible to minimize parasitic capacitance and inductance and to minimize radiated emissions. Kelvin connections should be brought from the output to the feedback pin of the device.

- 3. Keep analog and non-switching components away from switching components.

- 4. Make a single point connection from the signal ground to power ground.

- 5. Do not allow switching current to flow under the device.

- 6. Keep the pattern lines for VIN and PGND broad.

- 7. Exposed pad of device must be connected to PGND with solder.

- 8. VREG5 capacitor should be placed near the device, and connected PGND.

- 9. Output capacitor should be connected to a broad pattern of the PGND.

- 10. Voltage feedback loop should be as short as possible, and preferably with ground shield.

- 11. Lower resistor of the voltage divider which is connected to the VFB pin should be tied to SGND.

- 12. Providing sufficient via is preferable for VIN, SW and PGND connection.

- 13. PCB pattern for VIN, SW, and PGND should be as broad as possible.

- 14. VIN Capacitor should be placed as near as possible to the device.

VIA to Ground Plane

- - - Etch on Bottom Layer or Under Component

Figure 16. PCB Layout

### **REVISION HISTORY**

| Changes from Revision # (August 2010) to Revision A                                                                            | Page |

|--------------------------------------------------------------------------------------------------------------------------------|------|

| Added V <sub>IN</sub> = 12V to condition in Electrical Characteristics table                                                   | 3    |

| Changes from Revision A (November 2010) to Revision B                                                                          | Page |

| Added the RSA (16 pin QFN package) to: DESCRIPTION, ORDERING INFORMATION, THERMAL INFORMATION, and DEVICE INFORMATION sections | 1    |

| Changed the Functional Block Diagram                                                                                           | 6    |

| Changed the Power Good and Current Protection sections                                                                         | 8    |

| Added Note 1 to Table 1                                                                                                        | 13   |

| Changes from Revision B (November 2010) to Revision C                                                                          | Page |

| <ul> <li>Changed ELEC CHAR table, UVLO threshold MIN from 3.55 V to 3.5 V, MAX from 4.05 V to 4.1 V</li> </ul>                 | 4    |

Product Folder Link(s): TPS54426

10-Dec-2020

#### **PACKAGING INFORMATION**

| Orderable Device | Status (1) | Package Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan     | Lead finish/<br>Ball material | MSL Peak Temp       | Op Temp (°C) | Device Marking<br>(4/5) | Samples |

|------------------|------------|--------------|--------------------|------|----------------|--------------|-------------------------------|---------------------|--------------|-------------------------|---------|

| TPS54426PWP      | ACTIVE     | HTSSOP       | PWP                | 14   | 90             | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | PS54426                 | Samples |

| TPS54426PWPR     | ACTIVE     | HTSSOP       | PWP                | 14   | 2000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | PS54426                 | Samples |

| TPS54426RSAR     | ACTIVE     | QFN          | RSA                | 16   | 3000           | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | TPS<br>54426            | Samples |

| TPS54426RSAT     | ACTIVE     | QFN          | RSA                | 16   | 250            | RoHS & Green | NIPDAU                        | Level-2-260C-1 YEAR | -40 to 85    | TPS<br>54426            | Samples |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) RoHS: TI defines "RoHS" to mean semiconductor products that are compliant with the current EU RoHS requirements for all 10 RoHS substances, including the requirement that RoHS substance do not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, "RoHS" products are suitable for use in specified lead-free processes. TI may reference these types of products as "Pb-Free".

RoHS Exempt: TI defines "RoHS Exempt" to mean products that contain lead but are compliant with EU RoHS pursuant to a specific EU RoHS exemption.

Green: TI defines "Green" to mean the content of Chlorine (CI) and Bromine (Br) based flame retardants meet JS709B low halogen requirements of <=1000ppm threshold. Antimony trioxide based flame retardants must also meet the <=1000ppm threshold requirement.

- (3) MSL, Peak Temp. The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

- (4) There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

- (5) Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

- (6) Lead finish/Ball material Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead finish/Ball material values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and

### PACKAGE OPTION ADDENDUM

10-Dec-2020

continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

### **PACKAGE MATERIALS INFORMATION**

www.ti.com 17-Feb-2023

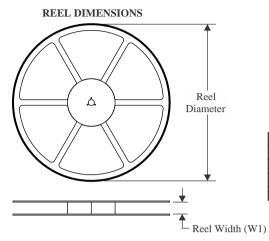

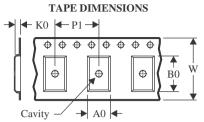

#### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

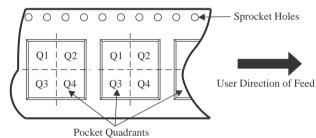

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|----|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TPS54426PWPR | HTSSOP          | PWP                | 14 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

| TPS54426PWPR | HTSSOP          | PWP                | 14 | 2000 | 330.0                    | 12.4                     | 6.9        | 5.6        | 1.6        | 8.0        | 12.0      | Q1               |

| TPS54426RSAR | QFN             | RSA                | 16 | 3000 | 330.0                    | 12.4                     | 4.25       | 4.25       | 1.15       | 8.0        | 12.0      | Q2               |

| TPS54426RSAT | QFN             | RSA                | 16 | 250  | 180.0                    | 12.4                     | 4.25       | 4.25       | 1.15       | 8.0        | 12.0      | Q2               |

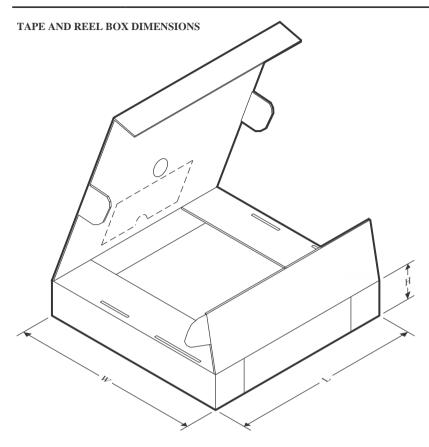

www.ti.com 17-Feb-2023

#### \*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS54426PWPR | HTSSOP       | PWP             | 14   | 2000 | 350.0       | 350.0      | 43.0        |

| TPS54426PWPR | HTSSOP       | PWP             | 14   | 2000 | 356.0       | 356.0      | 35.0        |

| TPS54426RSAR | QFN          | RSA             | 16   | 3000 | 367.0       | 367.0      | 35.0        |

| TPS54426RSAT | QFN          | RSA             | 16   | 250  | 210.0       | 185.0      | 35.0        |

### **PACKAGE MATERIALS INFORMATION**

www.ti.com 17-Feb-2023

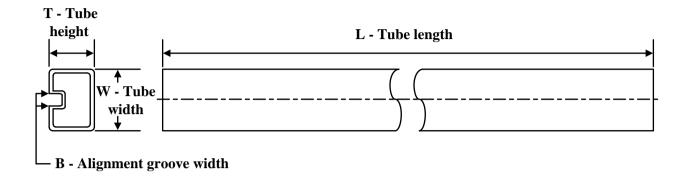

#### **TUBE**

#### \*All dimensions are nominal

| Device      | Package Name | Package Type | Pins | SPQ | L (mm) | W (mm) | T (µm) | B (mm) |

|-------------|--------------|--------------|------|-----|--------|--------|--------|--------|

| TPS54426PWP | PWP          | HTSSOP       | 14   | 90  | 530    | 10.2   | 3600   | 3.5    |

| TPS54426PWP | PWP          | HTSSOP       | 14   | 90  | 530    | 10.2   | 3600   | 3.5    |

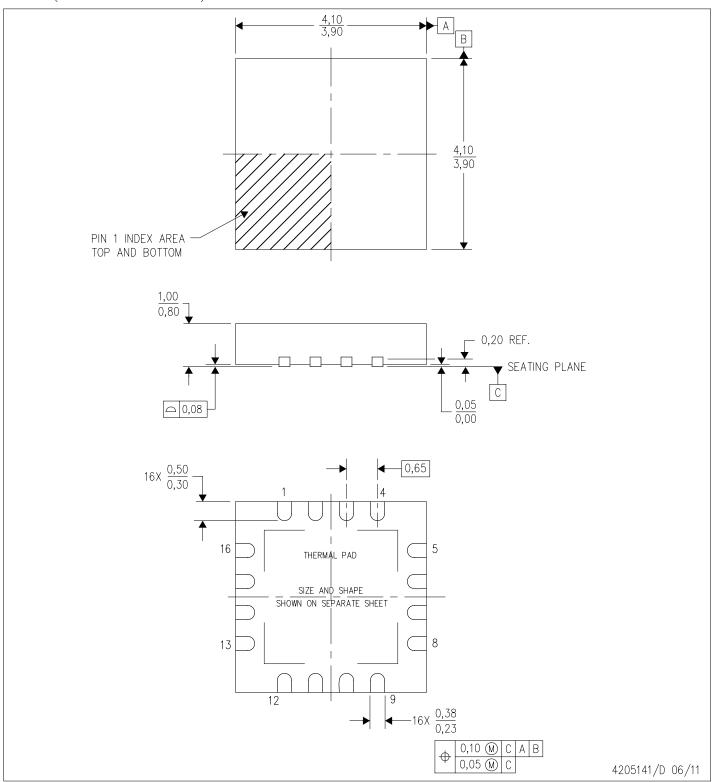

4.4 x 5.0, 0.65 mm pitch

PLASTIC SMALL OUTLINE

This image is a representation of the package family, actual package may vary. Refer to the product data sheet for package details.

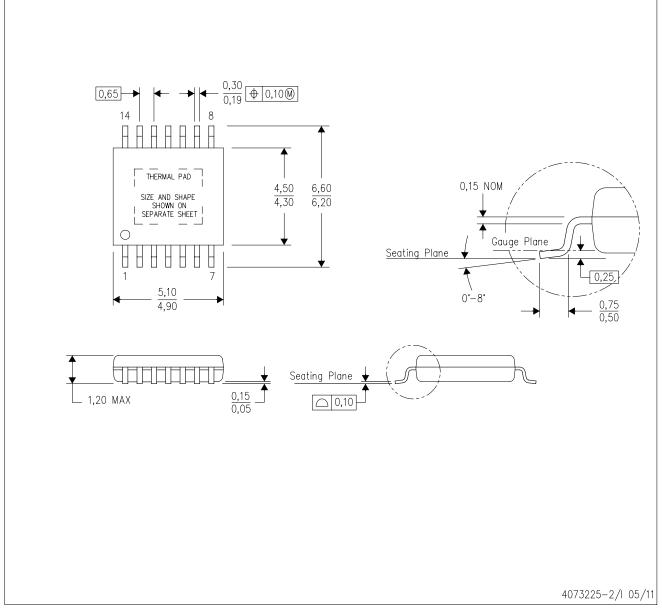

PWP (R-PDSO-G14)

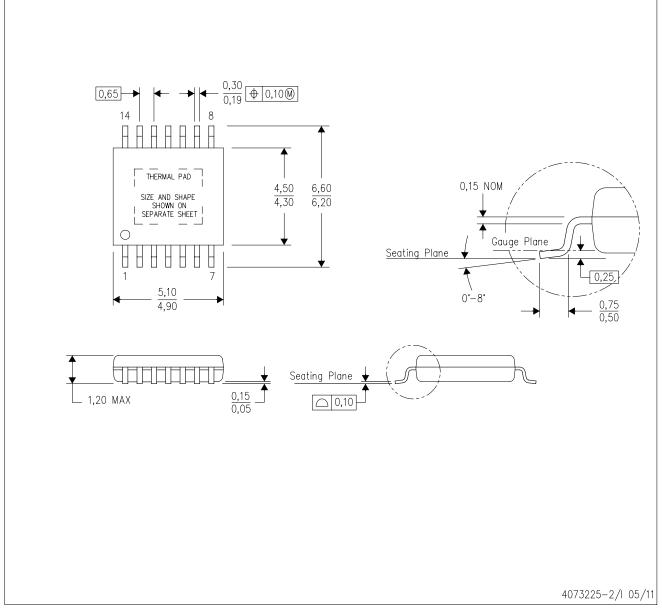

### PowerPAD™ PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusions. Mold flash and protrusion shall not exceed 0.15 per side.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>>.

- E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- E. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

# PWP (R-PDSO-G14) PowerPAD™ SMALL PLASTIC OUTLINE

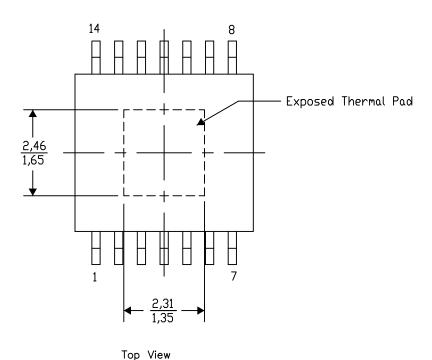

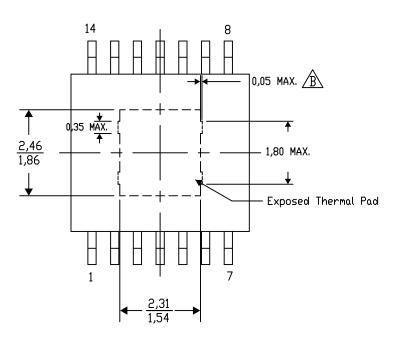

#### THERMAL INFORMATION

This PowerPAD<sup>TM</sup> package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

·

Exposed Thermal Pad Dimensions

4206332-2/AO 01/16

NOTE: A. All linear dimensions are in millimeters

PowerPAD is a trademark of Texas Instruments

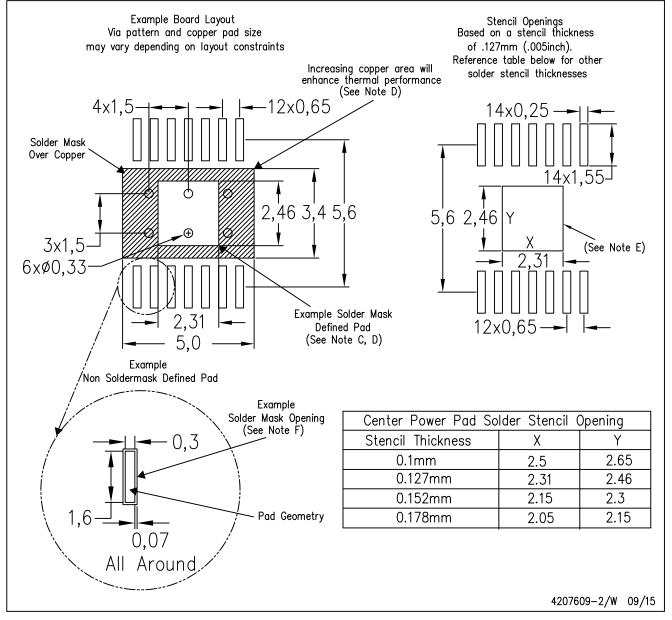

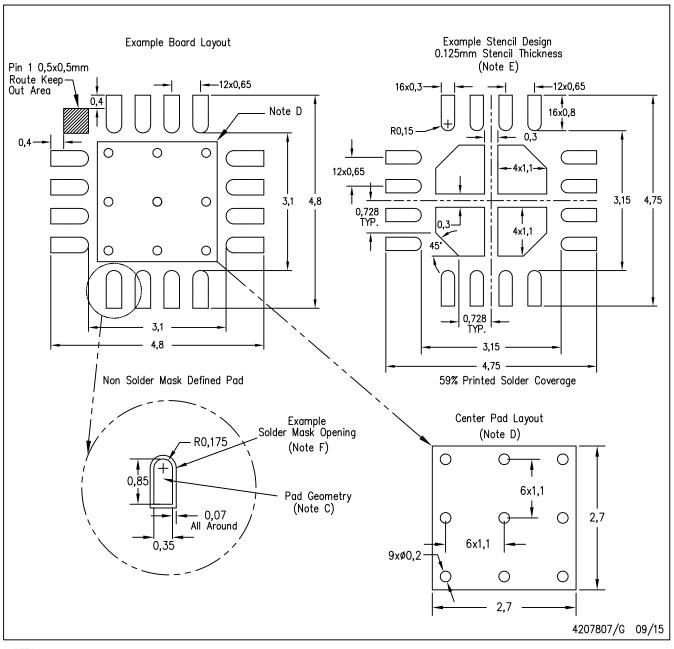

### PWP (R-PDSO-G14)

### PowerPAD™ PLASTIC SMALL OUTLINE

#### NOTES:

- All linear dimensions are in millimeters.

- This drawing is subject to change without notice.

- Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad.

- This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002, SLMA004, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>. Publication IPC-7351 is recommended for alternate designs.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil recommendations. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

PWP (R-PDSO-G14)

### PowerPAD™ PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusions. Mold flash and protrusion shall not exceed 0.15 per side.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 for information regarding recommended board layout. This document is available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>>.

- E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- E. Falls within JEDEC MO-153

PowerPAD is a trademark of Texas Instruments.

# PWP (R-PDSO-G14) PowerPAD™ SMALL PLASTIC OUTLINE

#### THERMAL INFORMATION

This PowerPAD<sup>TM</sup> package incorporates an exposed thermal pad that is designed to be attached to a printed circuit board (PCB). The thermal pad must be soldered directly to the PCB. After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For additional information on the PowerPAD package and how to take advantage of its heat dissipating abilities, refer to Technical Brief, PowerPAD Thermally Enhanced Package, Texas Instruments Literature No. SLMA002 and Application Brief, PowerPAD Made Easy, Texas Instruments Literature No. SLMA004. Both documents are available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

Exposed Thermal Pad Dimensions

Top View

4206332-44/AO 01/16

NOTE: A. All linear dimensions are in millimeters

🛕 Exposed tie strap features may not be present.

PowerPAD is a trademark of Texas Instruments

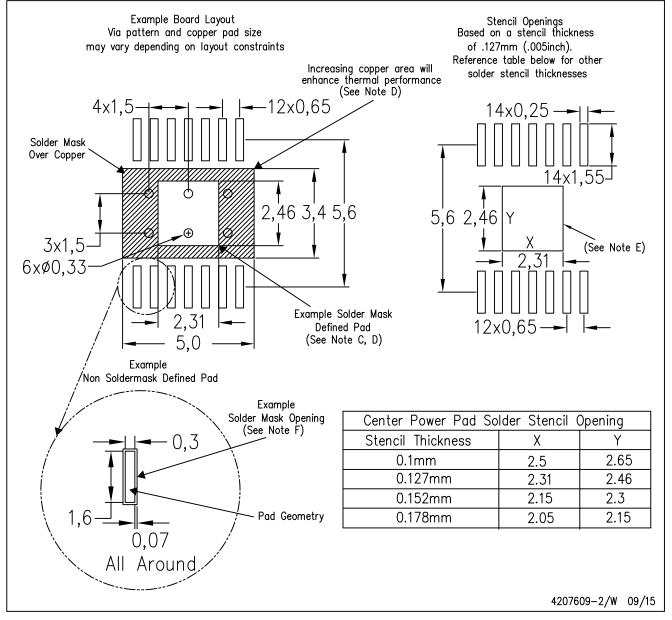

### PWP (R-PDSO-G14)

### PowerPAD™ PLASTIC SMALL OUTLINE

#### NOTES:

- All linear dimensions are in millimeters.

- This drawing is subject to change without notice.

- Customers should place a note on the circuit board fabrication drawing not to alter the center solder mask defined pad.

- This package is designed to be soldered to a thermal pad on the board. Refer to Technical Brief, PowerPad Thermally Enhanced Package, Texas Instruments Literature No. SLMA002, SLMA004, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>. Publication IPC-7351 is recommended for alternate designs.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Example stencil design based on a 50% volumetric metal load solder paste. Refer to IPC-7525 for other stencil recommendations. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

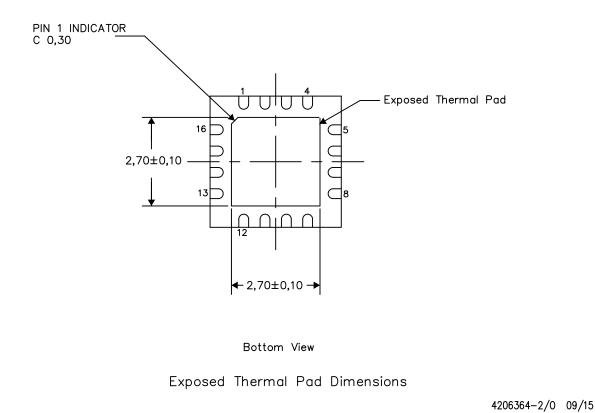

### RSA (S-PVQFN-N16)

### PLASTIC QUAD FLATPACK NO-LEAD

NOTES: A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M—1994.

- B. This drawing is subject to change without notice.

- C. Quad Flatpack, No—leads (QFN) package configuration.

- D. The package thermal pad must be soldered to the board for thermal and mechanical performance.

- E. See the additional figure in the Product Data Sheet for details regarding the exposed thermal pad features and dimensions.

- F. Falls within JEDEC MO-220.

### RSA (S-PVQFN-N16)

PLASTIC QUAD FLATPACK NO-LEAD

#### THERMAL INFORMATION

This package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For information on the Quad Flatpack No-Lead (QFN) package and its advantages, refer to Application Report, QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271. This document is available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

NOTES:

A. All linear dimensions are in millimeters

## RSA (S-PVQFN-N16)

## PLASTIC QUAD FLATPACK NO-LEAD

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Application Note, QFN Packages, Texas Instruments Literature No. SLUA271, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="https://www.ti.com">http://www.ti.com</a>.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC 7525 for stencil design considerations.

- F. Customers should contact their board fabrication site for solder mask tolerances.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2023, Texas Instruments Incorporated