# SGM5200 12-Bit, 1MSPS, 16 Channels, Single-Ended, Serial Interface ADC

## **GENERAL DESCRIPTION**

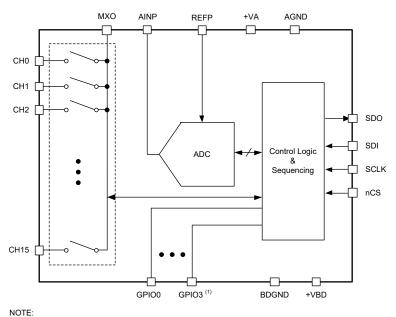

The SGM5200 is a 12-bit, multi-channel input, successive approximation (SAR) analog-to-digital converter (ADC).

The SGM5200 analog power supply range is 2.7V to 5.25V. The SGM5200 has an SPI-compatible interface that digital power supply range is 1.7V to 5.25V.

The input signal is sampled on the nCS falling edge. The ADC conversion is droved by external clock SCLK.

The SGM5200 supports manual channel selection and two kinds of auto channel scan modes.

The input range of SGM5200 is software configurable, 0 to reference voltage or 0 to two times of reference voltage. It also supports two programmable alarm thresholds for each channel.

The SGM5200 provides power-down mode.

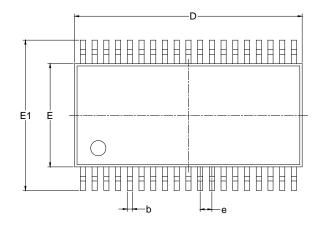

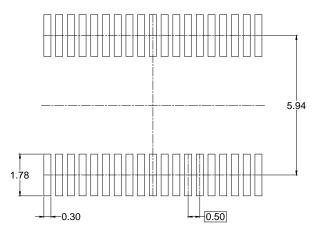

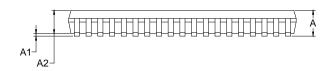

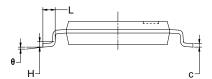

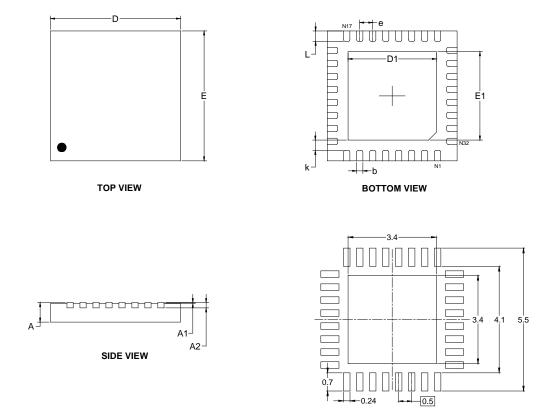

The SGM5200 is available in Green TSSOP-38 and TQFN-5×5-32L packages. It operates over an ambient temperature range -40°C to +125°C.

# **FEATURES**

- 12-Bit Resolution

- 16 Channels

- Sampling Rate: Up to 1MHz

- Supply Voltage Ranges:

- Analog Supply: 2.7V to 5.25V

- Digital Supply: 1.7V to 5.25V

- Two Software Selectable Unipolar Input Ranges:

- Range 1: 0V to V<sub>REF</sub>

- Range 2: 0V to 2 × V<sub>REF</sub>

- Supports Auto and Manual Channel Selections

- Individually Configurable GPIOs Function:

- Four GPIOs in TSSOP Package

- One GPIO in TQFN Package

- 20MHz SPI-Compatible Serial Interface

- Power-Down Current: 1.4µA (TYP)

- Input Bandwidth: 45MHz (TYP) at -3dB

- Typical Power Consumption: 24mW at 1MSPS (V<sub>A</sub> = 5V, V<sub>BD</sub> = 3V)

- Available in Green TSSOP-38 and TQFN-5×5-32L Packages

# **APPLICATIONS**

PLC

Optical Module Signal Monitoring Digital Power Supplies Industrial Automation Systems

### PACKAGE/ORDERING INFORMATION

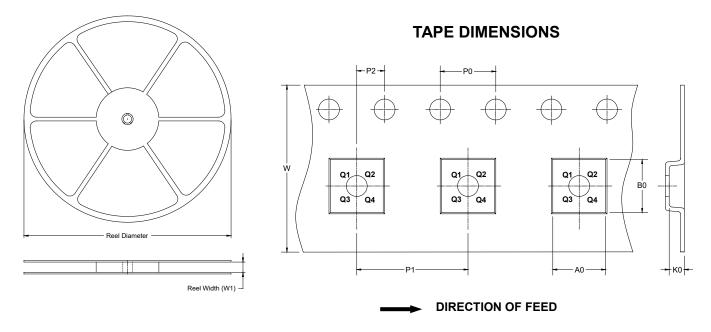

| MODEL   | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING         | PACKING<br>OPTION   |

|---------|------------------------|-----------------------------------|--------------------|----------------------------|---------------------|

| SGM5200 | TSSOP-38               | -40℃ to +125℃                     | SGM5200XTS38G/TR   | SGM5200<br>XTS38<br>XXXXX  | Tape and Reel, 4000 |

| 3GM5200 | TQFN-5×5-32L           | -40℃ to +125℃                     | SGM5200XTQL32G/TR  | SGM5200<br>XTQL32<br>XXXXX | Tape and Reel, 3000 |

### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

Trace Code

Date Code - Year

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

### **ABSOLUTE MAXIMUM RATINGS**

Voltage Range (with Respect to AGND)

### **RECOMMENDED OPERATING CONDITIONS**

| Analog Supply Voltage Range      | 2.7V to 5.25V          |

|----------------------------------|------------------------|

| Digital I/O Supply Voltage Range | 1.7V to V <sub>A</sub> |

| Reference Voltage Range          | 2V to 3V               |

| SCLK Frequency                   | 20MHz                  |

| Operating Temperature Range      | 40°C to +125°C         |

### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

### ESD SENSITIVITY CAUTION

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

### DISCLAIMER

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

### 12-Bit, 1MSPS, 16 Channels, Single-Ended, Serial Interface ADC

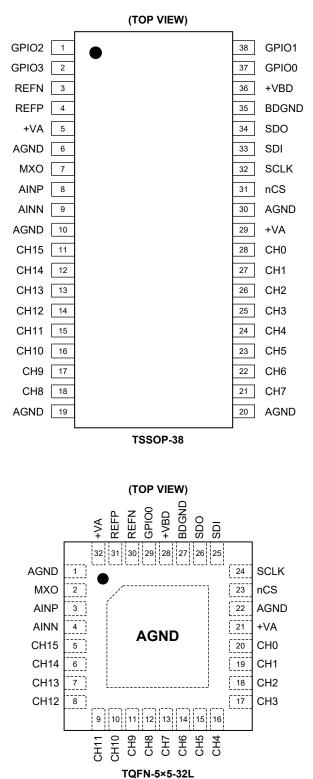

### **PIN CONFIGURATIONS**

SG Micro Corp

## 12-Bit, 1MSPS, 16 Channels, Single-Ended, Serial Interface ADC

### **PIN DESCRIPTION**

| PI                | N                      |           |                     | FUNCTION                                                                                                                         |  |  |  |  |  |

|-------------------|------------------------|-----------|---------------------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| TSSOP-38          | TQFN-5×5-32L           | NAME      | TYPE <sup>(1)</sup> | FUNCTION                                                                                                                         |  |  |  |  |  |

|                   |                        | GPIO2     | DIO                 | General-Purpose Input or Output.                                                                                                 |  |  |  |  |  |

| 1                 | -                      | Range     | DI                  | Selects ADC Input Range.<br>High (1): select Range 2 (0V to $2 \times V_{REF}$ ).<br>Low (0): select Range 1 (0V to $V_{REF}$ ). |  |  |  |  |  |

| 2                 |                        | GPIO3     | DIO                 | General-Purpose Input or Output.                                                                                                 |  |  |  |  |  |

| Σ                 | _                      | nPD       | DI                  | Power-Down Input. Active low.                                                                                                    |  |  |  |  |  |

| 3                 | 30                     | REFN      | AI                  | Reference Ground.                                                                                                                |  |  |  |  |  |

| 4                 | 31                     | REFP      | AI                  | Reference Input.                                                                                                                 |  |  |  |  |  |

| 5, 29             | 21, 32                 | +VA       | -                   | Analog Power Supply.                                                                                                             |  |  |  |  |  |

| 6, 10, 19, 20, 30 | 1, 22                  | AGND      | -                   | Analog Ground.                                                                                                                   |  |  |  |  |  |

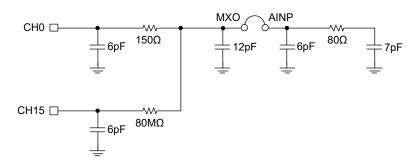

| 7                 | 2                      | MXO       | AO                  | Multiplexer Output.                                                                                                              |  |  |  |  |  |

| 8                 | 3                      | AINP      | AI                  | ADC Input Signal.                                                                                                                |  |  |  |  |  |

| 9                 | 4                      | AINN      | AI                  | ADC Input Ground.                                                                                                                |  |  |  |  |  |

| 11                | 5                      | CH15      | AI                  |                                                                                                                                  |  |  |  |  |  |

| 12                | 6                      | CH14      | AI                  |                                                                                                                                  |  |  |  |  |  |

| 13                | 7                      | CH13      | AI                  |                                                                                                                                  |  |  |  |  |  |

| 14                | 8                      | CH12      | AI                  |                                                                                                                                  |  |  |  |  |  |

| 15                | 15 9 CH11   16 10 CH10 |           |                     |                                                                                                                                  |  |  |  |  |  |

| 16                | 10                     | CH10      | AI                  |                                                                                                                                  |  |  |  |  |  |

| 17                | 11                     | CH9       | AI                  |                                                                                                                                  |  |  |  |  |  |

| 18                | 12                     | CH8       | AI                  |                                                                                                                                  |  |  |  |  |  |

| 21                | 13                     | CH7       | AI                  | Analog Channel Inputs for Multiplexer.                                                                                           |  |  |  |  |  |

| 22                | 14                     | CH6       | AI                  |                                                                                                                                  |  |  |  |  |  |

| 23                | 15                     | CH5       | AI                  |                                                                                                                                  |  |  |  |  |  |

| 24                | 16                     | CH4       | AI                  |                                                                                                                                  |  |  |  |  |  |

| 25                | 17                     | CH3       | AI                  |                                                                                                                                  |  |  |  |  |  |

| 26                | 18                     | CH2       | AI                  |                                                                                                                                  |  |  |  |  |  |

| 27                | 19                     | CH1       | AI                  |                                                                                                                                  |  |  |  |  |  |

| 28                | 20                     | CH0       | AI                  |                                                                                                                                  |  |  |  |  |  |

| 31                | 23                     | nCS       | DI                  | Chip Select. Active low.                                                                                                         |  |  |  |  |  |

| 32                | 24                     | SCLK      | DI                  | Serial Clock Input.                                                                                                              |  |  |  |  |  |

| 33                | 25                     | SDI       | DI                  | Serial Data Input.                                                                                                               |  |  |  |  |  |

| 34                | 26                     | SDO       | DI                  | Serial Data Output.                                                                                                              |  |  |  |  |  |

| 35                | 27                     | BDGND     | -                   | Digital Ground.                                                                                                                  |  |  |  |  |  |

| 36                | 28                     | +VBD      | -                   | Digital Power Supply.                                                                                                            |  |  |  |  |  |

|                   |                        | GPIO0     | DIO                 | General-Purpose Input or Output.                                                                                                 |  |  |  |  |  |

| 37                | 29                     | Alarm     | DO                  | Alarm Output. Active high. Refer to Programming section for a detailed configuration.                                            |  |  |  |  |  |

| 20                |                        | GPIO1     | DIO                 | General-Purpose Input or Output.                                                                                                 |  |  |  |  |  |

| 38                | _                      | Low Alarm | DO                  | Low Alarm Output Indication. Active high.                                                                                        |  |  |  |  |  |

NOTE:

1. AI = Analog Input, AO = Analog Output, DI = Digital Input, DO = Digital Output, DIO = Digital Input or Output.

# **ELECTRICAL CHARACTERISTICS**

(V<sub>A</sub> = 2.7V to 5.25V, V<sub>BD</sub> = 1.7V to V<sub>A</sub>, V<sub>REF</sub> = 2.5V  $\pm$  0.1V, f<sub>SAMPLE</sub> = 1MHz, Full = -40°C to +125°C, typical values are at T<sub>A</sub> = +25°C, unless otherwise noted.)

| PARAMETER                                | SYMBOL | CON                                                                   | DITIONS                            | MIN   | TYP     | MAX                        | UNITS              |  |

|------------------------------------------|--------|-----------------------------------------------------------------------|------------------------------------|-------|---------|----------------------------|--------------------|--|

| Analog Input                             |        |                                                                       |                                    |       |         |                            |                    |  |

|                                          |        | Range 1                                                               |                                    | 0     |         | V <sub>REF</sub>           |                    |  |

| Full-Scale Input Span <sup>(1)</sup>     |        | Range 2 while 2 × \                                                   | $V_{\text{REF}} \leq V_{\text{A}}$ | 0     |         | 2 × V <sub>REF</sub>       | V                  |  |

|                                          |        | Range 1                                                               |                                    | -0.2  |         | V <sub>REF</sub> + 0.2     |                    |  |

| Absolute Input Range                     |        | Range 2 while 2 × \                                                   | $V_{\text{REF}} \leq V_{\text{A}}$ | -0.2  |         | 2 × V <sub>REF</sub> + 0.2 | V                  |  |

| Input Capacitance                        |        |                                                                       |                                    |       | 31      |                            | pF                 |  |

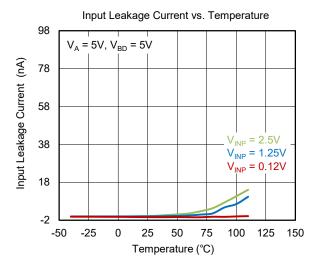

| Input Leakage Current                    |        | T <sub>A</sub> = +125°C                                               |                                    |       | 60      |                            | nA                 |  |

| System Performance                       |        | I                                                                     |                                    |       |         |                            |                    |  |

| Resolution                               |        |                                                                       |                                    |       | 12      |                            | Bits               |  |

|                                          |        | Range 1                                                               |                                    | 11    |         |                            |                    |  |

| No Missing Codes                         |        | Range 2                                                               |                                    | 12    |         |                            | Bits               |  |

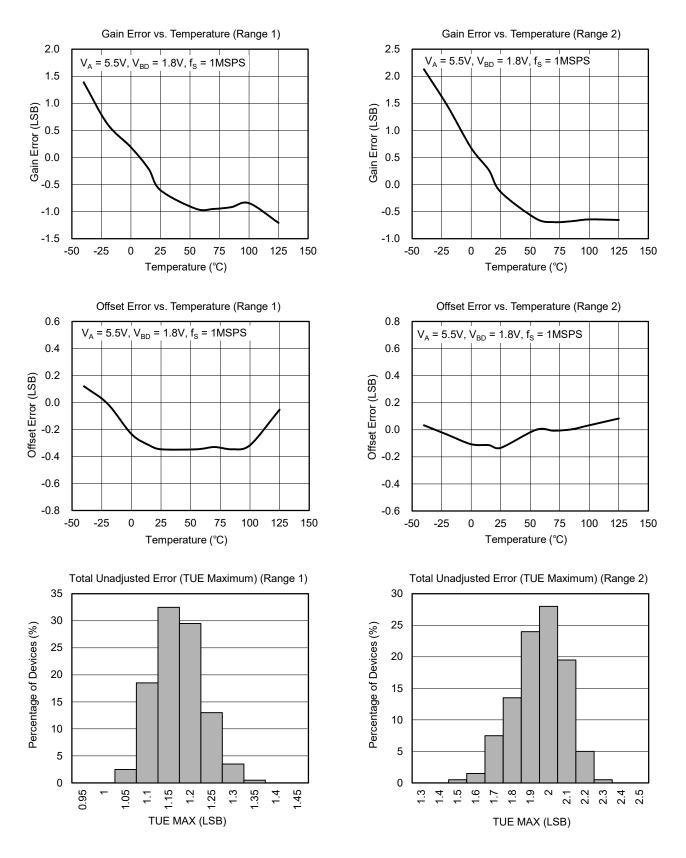

|                                          |        | Range 1                                                               |                                    | -3.50 | ±1.6    | 2.60                       | (2)                |  |

| Integral Linearity                       |        | Range 2                                                               |                                    | -1.32 | ±0.8    | 1.32                       | LSB <sup>(2)</sup> |  |

|                                          |        | Range 1                                                               |                                    | -1.00 | -1/+1.3 | 2.20                       |                    |  |

| Differential Linearity                   |        | Range 2                                                               |                                    | -0.99 | ±0.5    | 1.00                       | LSB                |  |

|                                          |        | Range 1                                                               |                                    | -8.00 | ±1.2    | 8.00                       |                    |  |

| Offset Error <sup>(3)</sup>              |        | Range 2                                                               |                                    | -5.60 | ±1.6    | 5.60                       | LSB                |  |

|                                          |        | Range 1                                                               |                                    | -5.20 | ±0.8    | 4.40                       |                    |  |

| Gain Error                               |        | Range 2                                                               |                                    | -4.10 | ±0.8    | 3.10                       | LSB                |  |

|                                          |        | Range 1                                                               |                                    |       | ±1.8    |                            |                    |  |

| Total Unadjusted Error                   | TUE    | Range 2                                                               |                                    |       | ±1.9    |                            | LSB                |  |

| Sampling Dynamics                        |        | I                                                                     |                                    |       | 1       |                            |                    |  |

| Conversion Time                          |        | 20MHz SCLK                                                            |                                    |       | 800     |                            | ns                 |  |

| Acquisition Time                         |        |                                                                       |                                    |       | 325     |                            | ns                 |  |

| Maximum Throughput Rate                  |        | 20MHz SCLK                                                            |                                    |       |         | 1                          | MHz                |  |

| Aperture Delay                           |        |                                                                       |                                    |       | 6       |                            | ns                 |  |

| Dynamic Characteristics                  |        | I                                                                     |                                    |       | 1       |                            |                    |  |

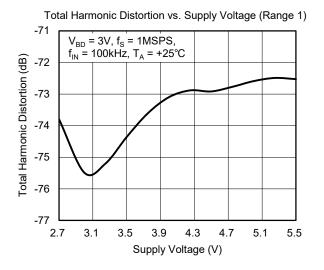

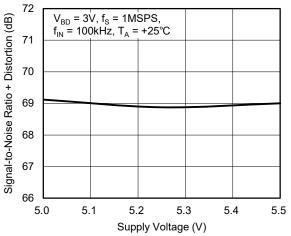

|                                          |        |                                                                       | Range 1                            |       | -77     |                            |                    |  |

| Total Harmonic Distortion <sup>(4)</sup> | THD    | 100kHz                                                                | Range 2                            |       | -79     |                            | dB                 |  |

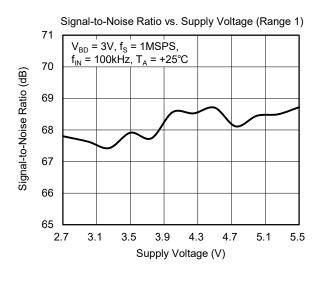

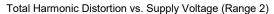

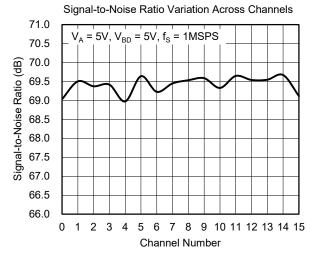

|                                          |        |                                                                       | Range 1                            | 66.4  | 70.4    |                            |                    |  |

| Signal-to-Noise Ratio                    | SNR    | 100kHz                                                                | Range 2                            | 67.9  | 71.4    |                            | dB                 |  |

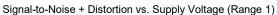

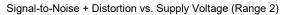

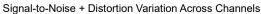

|                                          |        |                                                                       | Range 1                            | 65.6  | 69.5    |                            | 15                 |  |

| Signal-to-Noise + Distortion             |        | 100kHz                                                                | Range 2                            | 66.7  | 70.7    |                            | dB                 |  |

|                                          |        |                                                                       | Range 1                            |       | 78      |                            |                    |  |

| Spurious Free Dynamic Range              |        | 100kHz                                                                | Range 2                            |       | 81      |                            | dB                 |  |

| Small Signal Bandwidth                   |        | At -3dB                                                               |                                    |       | 45      |                            | MHz                |  |

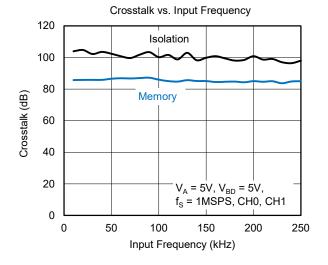

| Channel-to-Channel Crosstalk             |        | Any off-channel witl<br>input to channel bei<br>input (isolation cros | ng sampled with DC                 |       | -100    |                            | dB                 |  |

| Channorto-Onannel Olussialk              |        | From previously sar<br>100kHz, full-scale ir<br>sampled with DC in    |                                    | -84   |         | чD                         |                    |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

(V<sub>A</sub> = 2.7V to 5.25V, V<sub>BD</sub> = 1.7V to V<sub>A</sub>, V<sub>REF</sub> = 2.5V  $\pm$  0.1V, f<sub>SAMPLE</sub> = 1MHz, Full = -40°C to +125°C, typical values are at T<sub>A</sub> = +25°C, unless otherwise noted.)

| PARAMETER                                      | SYMBOL           | CONDITIONS                                  | MIN                   | TYP       | MAX  | UNITS      |

|------------------------------------------------|------------------|---------------------------------------------|-----------------------|-----------|------|------------|

| External Reference Input                       | •                | •                                           |                       |           |      | •          |

| Reference Voltage at REFP (5)                  | V <sub>REF</sub> |                                             | 2                     | 2.5       | 3    | V          |

| Reference Input Resistance                     |                  | f <sub>SAMPLE</sub> = 1MHz                  |                       | 31        |      | kΩ         |

| Alarm Setting                                  | •                | •                                           | •                     | <u> </u>  |      | •          |

| High Threshold Range                           |                  |                                             | 0                     |           | 4092 | LSB        |

| Low Threshold Range                            |                  |                                             | 0                     |           | 4092 | LSB        |

| Digital Input/Output                           | •                | •                                           | •                     | <u> </u>  |      | •          |

| 1 Balt Jacoust Maltana                         |                  | V <sub>BD</sub> = 5.25V                     | 3.10                  |           |      |            |

| High Input Voltage                             | V <sub>IH</sub>  | V <sub>BD</sub> = 1.7V                      | 1.25                  |           |      | - V        |

|                                                |                  | V <sub>BD</sub> = 5.25V                     |                       |           | 1.90 |            |

| Low Input Voltage                              | VIL              | V <sub>BD</sub> = 1.7V                      |                       |           | 0.45 | - V        |

| High Output Voltage                            | V <sub>OH</sub>  | I <sub>SOURCE</sub> = 200µA                 | V <sub>BD</sub> - 0.2 |           |      | V          |

| Low Output Voltage                             | Vol              | I <sub>SINK</sub> = 200μA                   |                       |           | 0.4  | V          |

| Data Format MSB First                          |                  |                                             |                       | MSB First |      |            |

| Power Requirements                             | •                | •                                           | •                     | <u> </u>  |      | •          |

| Analog Supply Voltage                          | V <sub>A</sub>   |                                             | 2.7                   | 3.3       | 5.25 | V          |

| Digital I/O Supply Voltage                     | V <sub>BD</sub>  |                                             | 1.7                   | 3.3       | 5.25 | V          |

|                                                |                  | $V_A$ = 2.7V to 3.6V and 1MHz throughput    |                       | 3         |      |            |

| Analog Supply Current                          |                  | V <sub>A</sub> = 2.7V to 3.6V static state  | 1.1                   | 1.1       |      |            |

| (Normal Mode)                                  | I <sub>A</sub>   | $V_A$ = 4.7V to 5.25V and 1MHz throughput   |                       | 4.1       | 5.4  | - mA       |

|                                                |                  | V <sub>A</sub> = 4.7V to 5.25V static state |                       | 1.1       | 2.2  |            |

| Power-Down State Supply<br>Current             |                  |                                             |                       | 1.4       |      | μA         |

| Digital I/O Supply Current                     | I <sub>BD</sub>  | $V_A = 5.25V, f_{SAMPLE} = 1MHz$            |                       | 1.3       |      | mA         |

| Power-Up Time                                  |                  |                                             |                       | 1         |      | μs         |

| Invalid Conversions after<br>Power-Up or Reset |                  |                                             |                       | 1         |      | Conversion |

#### NOTES:

1. Ideal input span; not consider gain error and offset error.

2. LSB = Least Significant Bit.

3. The measurement is performed relative to the ideal full-scale input.

4. The calculation is performed on the first nine harmonics of the input frequency.

5. The device is designed to operate that reference voltage is 2V to 3V. While, when  $V_{REF} < 2.4V$ , it expects lower noise performance It is due to SNR degradation resulting from lowered signal range.

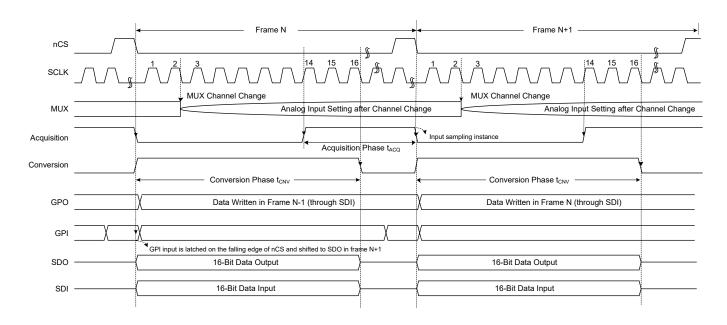

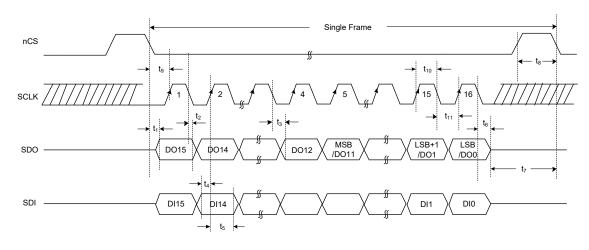

## TIMING CHARACTERISTICS

$(V_A = 2.7V \text{ to } 5.25V, \text{ Full} = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \text{ unless otherwise noted.})^{(1)(2)}$  (See Figure 1 and Figure 2)

| PARAMETER                                               | SYMBOL            | CONDITIONS             | MIN | TYP | MAX | UNITS |  |  |

|---------------------------------------------------------|-------------------|------------------------|-----|-----|-----|-------|--|--|

|                                                         |                   | V <sub>BD</sub> = 1.8V |     |     | 16  |       |  |  |

| Conversion Time                                         | t <sub>CONV</sub> | V <sub>BD</sub> = 3V   |     |     | 16  | SCLK  |  |  |

|                                                         |                   | V <sub>BD</sub> = 5V   |     |     | 16  |       |  |  |

|                                                         |                   | V <sub>BD</sub> = 1.8V |     |     | 38  |       |  |  |

| Delay Time<br>(nCS Low to First Data DO15 Out)          | t <sub>1</sub>    | V <sub>BD</sub> = 3V   |     |     | 27  | ns    |  |  |

|                                                         |                   | V <sub>BD</sub> = 5V   |     |     | 17  |       |  |  |

|                                                         |                   | V <sub>BD</sub> = 1.8V | 13  |     |     |       |  |  |

| Hold Time<br>(SCLK Falling to SDO Data Bit Valid)       | t <sub>2</sub>    | V <sub>BD</sub> = 3V   | 12  |     |     | ns    |  |  |

|                                                         |                   | V <sub>BD</sub> = 5V   | 12  |     |     |       |  |  |

|                                                         |                   | V <sub>BD</sub> = 1.8V |     |     | 35  |       |  |  |

| Delay Time<br>(SCLK Falling to SDO Next Data Bit Valid) | t <sub>3</sub>    | V <sub>BD</sub> = 3V   |     |     | 27  | ns    |  |  |

|                                                         |                   | V <sub>BD</sub> = 5V   |     |     | 17  |       |  |  |

|                                                         |                   | V <sub>BD</sub> = 1.8V | 2   |     |     |       |  |  |

| Setup Time<br>(SDI Valid to Rising Edge of SCLK)        | t4                | V <sub>BD</sub> = 3V   | 3   |     |     | ns    |  |  |

| (SDI Valid to Hising Edge of SCER)                      |                   | V <sub>BD</sub> = 5V   | 4   |     |     | 1     |  |  |

|                                                         |                   | V <sub>BD</sub> = 1.8V | 12  |     |     |       |  |  |

|                                                         | t <sub>5</sub>    | V <sub>BD</sub> = 3V   | 10  |     |     | ns    |  |  |

| (Rising Edge of SCLK to SDI Valid)                      |                   | V <sub>BD</sub> = 5V   | 6   |     |     |       |  |  |

|                                                         |                   | V <sub>BD</sub> = 1.8V |     |     | 26  |       |  |  |

| Delay Time                                              | t <sub>6</sub>    | V <sub>BD</sub> = 3V   |     |     | 22  | ns    |  |  |

| (16 <sup>th*</sup> SCLK Falling Edge to SDO 3-State)    |                   | V <sub>BD</sub> = 5V   |     |     | 13  | 1     |  |  |

|                                                         |                   | V <sub>BD</sub> = 1.8V | 40  |     |     |       |  |  |

| Minimum Quiet Sampling Time Needed from Bus             | t <sub>7</sub>    | V <sub>BD</sub> = 3V   | 40  |     |     | ns    |  |  |

| 3-State to Start of Next Conversion                     |                   | V <sub>BD</sub> = 5V   | 40  |     |     | -     |  |  |

|                                                         |                   | V <sub>BD</sub> = 1.8V | 20  |     |     |       |  |  |

| Pulse Duration nCS High                                 | t <sub>8</sub>    | V <sub>BD</sub> = 3V   | 20  |     |     | ns    |  |  |

| Ū.                                                      |                   | V <sub>BD</sub> = 5V   | 20  |     |     | _     |  |  |

|                                                         |                   | V <sub>BD</sub> = 1.8V | 8   |     |     |       |  |  |

| Setup Time                                              | t <sub>9</sub>    | V <sub>BD</sub> = 3V   | 6   |     |     | ns    |  |  |

| (nCS Low to First Rising Edge of SCLK)                  | 0                 | V <sub>BD</sub> = 5V   | 4   |     |     | -     |  |  |

|                                                         |                   | V <sub>BD</sub> = 1.8V | 20  |     |     |       |  |  |

| Pulse Duration SCLK High                                | t <sub>10</sub>   | V <sub>BD</sub> = 3V   | 20  |     |     | ns    |  |  |

| 3                                                       | 10                | V <sub>BD</sub> = 5V   | 20  |     |     |       |  |  |

|                                                         |                   | V <sub>BD</sub> = 1.8V | 20  |     | 1   |       |  |  |

| Pulse Duration SCLK Low                                 | t <sub>11</sub>   | $V_{BD} = 3V$          | 20  |     |     | ns    |  |  |

|                                                         | •11               | $V_{BD} = 5V$          | 20  |     |     | - 115 |  |  |

|                                                         |                   | $V_{BD} = 1.8V$        |     |     | 20  |       |  |  |

| SCLK Frequency                                          |                   | $V_{BD} = 3V$          |     |     | 20  | MHz   |  |  |

| COLICE I OQUONOY                                        |                   | $V_{BD} = 5V$          |     |     | 20  |       |  |  |

NOTES: 1. 1.6V to 1.9V range is applied for 1.8V specifications; 2.7V to 3.6V range is applied for 3V specifications; 4.75V to 5.25V range is applied for 5V specifications.

2. With 50pF load.

### **TIMING DIAGRAM**

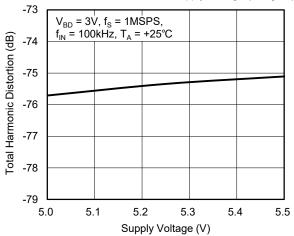

## **TYPICAL PERFORMANCE CHARACTERISTICS**

Signal-to-Noise Ratio vs. Supply Voltage (Range 2) 73 V<sub>BD</sub> = 3V, f<sub>S</sub> = 1MSPS,  $f_{IN} = 100 \text{kHz}, T_A = +25^{\circ}\text{C}$ 72 Signal-to-Noise Ratio (dB) 71 70 69 68 67 5.0 5.1 5.2 5.3 5.4 5.5 Supply Voltage (V)

SG Micro Corp

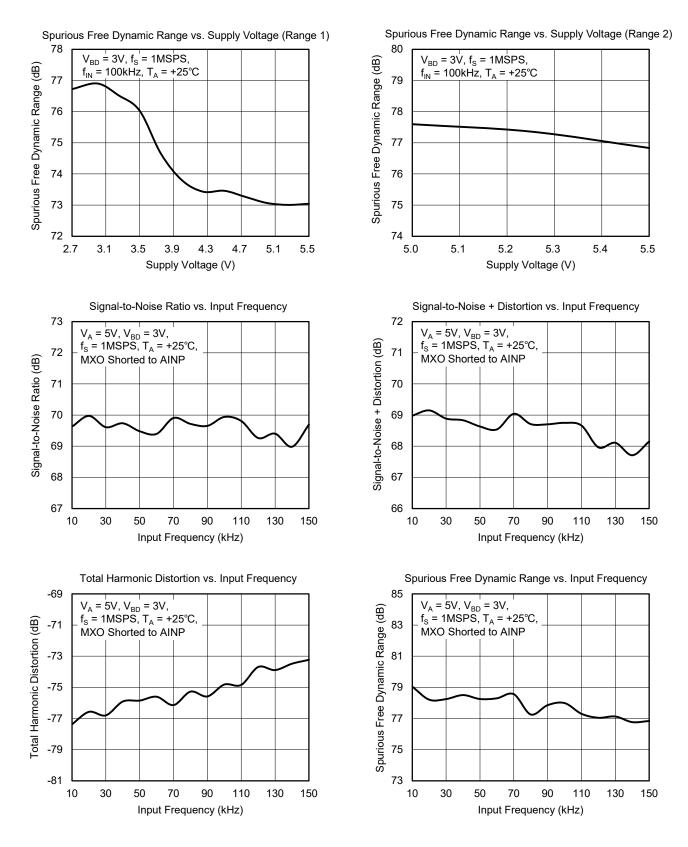

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

SG Micro Corp

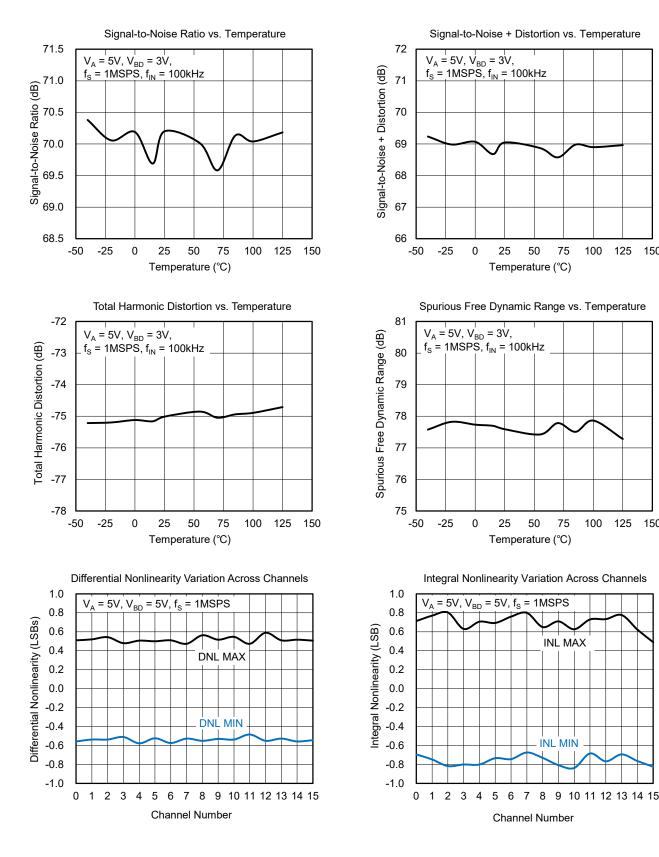

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

SG Micro Corp SGMICRO www.sg-micro.com 150

150

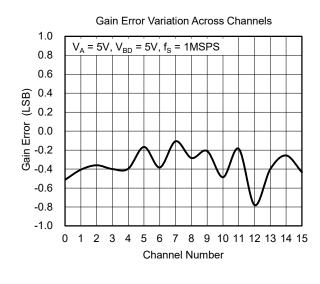

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

Offset Error Variation Across Channels 1.0 V<sub>A</sub> = 5V, V<sub>BD</sub> = 5V, f<sub>S</sub> = 1MSPS 0.8 0.6 0.4 Offset Error (LSB) 0.2 0.0 -0.2 -0.4 -0.6 -0.8 -1.0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 0 Channel Number

SG Micro Corp SGMICRO www.sg-micro.com

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

SG Micro Corp

# **TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

# FUNCTIONAL BLOCK DIAGRAM

1. Four GPIOs for TSSOP package and one GPIO for TQFN package.

Figure 3. Block Diagram

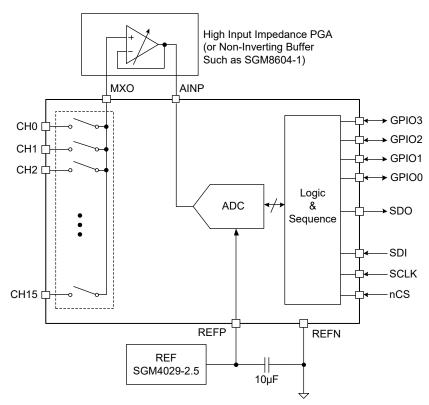

# **TYPICAL APPLICATION CIRCUIT**

Figure 4. Typical Application Circuit

## **DETAILED DESCRIPTION**

### Overview

The SGM5200 is a 12-bit, SAR ADC. It needs an external voltage reference. An Amplifier can be used between MXO and AINP for signal conditioning. Figure 1 and Figure 2 show the chip operating time sequences.

The SGM5200 output data is composed of 4-bit channel address and 12-bit ADC conversion result. To read and write GPIOs, more details refer to Table 1, Table 2 and Table 5.

The SGM5200 switches to new multiplexer channel on the  $2^{nd}$  falling edge of SCLK. The input acquisition phase (equal input capacitor starts charging) begins on the  $14^{th}$  falling edge of SCLK. The input signal is sampled on the nCS falling edge.

The TSSOP package of the SGM5200 has four general-purpose IO (GPIO) pins, and the TQFN package has one GPIO pin.

The chip refreshes the GPIO status (Input and output) at the nCS falling edge. The GPI data will be in the same frame starting with the nCS falling edge (if GPI read enabled).

The operating time sequence is shown in Figure 2, the falling edge of nCS clocks out DO15, the remain bits are shifted out on the falling edge of SCLK. The ADC result is a 12-bit binary data, MSB is shifted out on the 4<sup>th</sup> falling edge of SCLK, and LSB is shifted out on the 15<sup>th</sup> falling edge of SCLK. Refer to Figure 2, when the ADC conversion ends on the 16<sup>th</sup> SCLK falling edge, SDO goes to 3-state. The chip 16-bit data (on SDI pin) is shifted in on the every rising edge of SCLK.

The SGM5200 has threshold alarm function per channel. If ADC results exceed these limits (high and low), the chip can give alert on GPIO0/GPIO1 pins (detail configurations in Table 9). If there is an alarm, the alert will be set on the 12<sup>th</sup> SCLK falling edge in the same frame of ADC conversion in progress. It will reset on the 10<sup>th</sup> SCLK falling edge in the next frame.

### Reference

The SGM5200 needs an external reference.

### **Power Saving**

The SGM5200 provides two kinds of ways to power down the chip. The first way is command control. It depends on setting DI5 = '1', more details see Table 1, Table 2 and Table 5. If DI5 is set, the chip will be powered down on the

16<sup>th</sup> falling edge of SCLK in the next frame. If D15 is reset, the chip will be powered up on the nCS falling edge. The second way is asynchronous control by GPIO3. GPIO3 can be configured as an nPD input (see Table 9). Its output is active low. The chip goes to power-down at same time when nPD is '0'. The chip will be powered up when nPD is '1'.

### **Device Functional Modes**

#### **Channel Sequencing Modes**

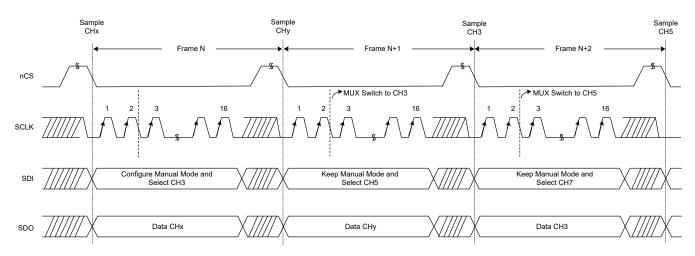

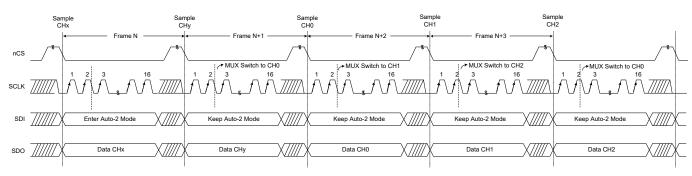

The SGM5200 has three channel sequencing modes: manual mode, auto-1 mode and auto-2 mode. Mode selection is configured by the mode control register (see Table 1, Table 2 and Table 5). The new channel selection is valid on the 2<sup>nd</sup> SCLK falling edge in the next frame in all three modes (refer to Figure 1).

Once the chip is configured to working in a selected mode, it keeps working in this mode until the chip is powered down, reset or reprogrammed. Allows it to exit multiple times and re-enter this mode without disturbing program register settings.

#### Manual Mode

When power-up or after reset the default channel is 'channel 0' and the default mode is manual mode.

#### Auto-1 Mode

In auto-1 mode, the chip scans all selected channels in ascending order. The selected channels are configured in a program register. The auto-1 program register setting is shown in Table 3 and Table 4. The auto-1 program register is reset to '0hFFFF'.

#### Auto-2 Mode

In auto-2 mode, the chip scans all selected channels from channel 0 to the last channel. The last channel is configured in a program register. The auto-2 program register setting is shown in Table 6. The auto-2 program register are reset to '0hF'.

#### **Device Programming and Mode Control**

The chip has two kinds of registers named mode registers and program registers.

#### Power-Up Sequence

After power-up, the chip is in default manual mode and channel 0 is set as default channel. User needs to configure program register and mode register to set the chip working in target mode.

#### **Operating in Manual Mode**

The mode control register settings for manual mode are shown in Table 1. In manual mode, no program register is required.

The example for the chip how to work in manual mode and scan channels CH3, CH5 and CH7 is shown in Figure 5. In this sequence, in the frame N manual mode and channel CH3 is selected. In the frame N+1, keep in manual mode

and channel CH5 is selected, internal MUX is switched to channel CH3 on the  $2^{nd}$  falling edge of SCLK. In the frame N+2, keep in manual mode and channel CH7 is selected, on the falling edge of nCS, channel CH3 input signal is sampling and conversion result is sent out in this frame, internal MUX is switched to CH5. And the chip repeats this sequence and sends out ADC conversion result data of CH5 and CH7 in the following two frames.

| BITS      | DESCRIPTION                                                                                                                                                                                                                                                                                                     |      |      |      |      |  |  |  |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|--|--|--|--|

| DI[15:12] | 0001 = Selects manual mode                                                                                                                                                                                                                                                                                      | e    |      |      | 0001 |  |  |  |  |

| DI11      | 0 = Chip retains values of DI[6:0] from the previous frame<br>1 = Enables programming of bits DI[6:0]                                                                                                                                                                                                           |      |      |      |      |  |  |  |  |

| DI[10:7]  | The 4-bit data means the next channel address to be selected in the next frame. DI10 is MSB and DI7 is LSB. For example, 0000 = channel 0, 0001 = channel 1 and so on.                                                                                                                                          |      |      |      |      |  |  |  |  |

| DI6       | 0 = Selects 0V to V <sub>REF</sub> input range (Range 1)<br>1 = Selects 0V to 2 × V <sub>REF</sub> input range (Range 2)                                                                                                                                                                                        |      |      |      |      |  |  |  |  |

| DI5       | 0 = Normal operation (no power-down).<br>1 = Powers down on the 16 <sup>th</sup> SCLK falling edge.                                                                                                                                                                                                             |      |      |      |      |  |  |  |  |

| DI4       | 0 = SDO outputs current channel address of the channel on DO[15:12], and the 12-bit conversion results on DO[11:0]<br>1 = GPIO3 to GPIO0 data (both input and output) corresponds to DO[15:12] in the following order as shown. Lower data bits DO[11:0] means 12-bit conversion result for the current channel |      |      |      |      |  |  |  |  |

|           | DO15                                                                                                                                                                                                                                                                                                            | DO14 | DO13 | DO12 |      |  |  |  |  |

|           | GPI03 <sup>(1)</sup> GPI02 <sup>(1)</sup> GPI01 <sup>(1)</sup> GPI00 <sup>(1)</sup>                                                                                                                                                                                                                             |      |      |      |      |  |  |  |  |

|           | GPIO data of the channels is used as output. The data of the channel configured as input will be ignored by the device. The SDI bits and corresponding GPIO are shown below.                                                                                                                                    |      |      |      |      |  |  |  |  |

| DI[3:0]   | DI3 DI2 DI1 DI0                                                                                                                                                                                                                                                                                                 |      |      |      |      |  |  |  |  |

|           | GPIO3 <sup>(1)</sup> GPIO2 <sup>(1)</sup> GPIO1 <sup>(1)</sup> GPIO0 <sup>(1)</sup>                                                                                                                                                                                                                             |      |      |      |      |  |  |  |  |

NOTE: 1. GPIO1 to GPIO3 are available only for TSSOP package. TQFN packaged device offers GPIO0 only.

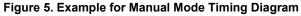

#### **Operating in Auto-1 Mode**

The mode control register settings for auto-1 mode are shown in Table 2. There are both mode registers and program registers for auto-1 mode operation.

To let the chip work in auto-1 mode, it is necessary to configure auto-1 program register firstly to select which channels are going to be scanned.

The program register settings for auto-1 mode are shown in Table 3 and Table 4.

Before running in auto-1 mode, the target channels CH2, CH3 and CH5 (examples) must be configured in auto-1 program registers (details see auto-1 program registers configuration sequence).

The example for the chip how to work in auto-1 mode and scan channels CH2, CH3 and CH5 automatically is shown in Figure 6. In this sequence, in the frame N sent entering auto-1 mode command and channel CH2 is selected automatically (the chip find the first selected channel in ascending order automatically). In the frame N+1, the chip switches MUX to CH2. In the frame N+2, the chip samples

Table 2. Mode Control Register Details for Auto-1 Mode

the CH2 input and gives out ADC conversion result, and the MUX is switched to CH3 automatically. In the frame N+3, the chip samples CH3 and gives out ADC conversion results, and the MUX is switched to CH5 automatically, and so on. This process repeats until the last selected channel is reached, and the process loops back from the first selected channel.

In any case, re-entering auto-1 mode (It may be from auto-1 mode, manual mode and auto-2 mode) will cause the chip channel scan sequence restarts from the first selected channel.

Note that changing the auto-1 program register during the chip is working in auto-1 mode, the chip scan restarts from the first selected channel in ascending.

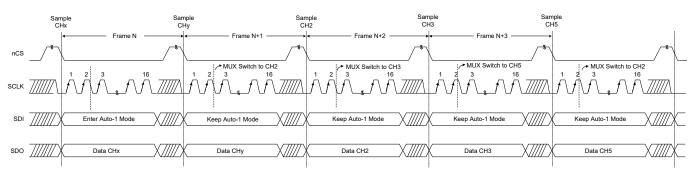

Figure 7 shows how the auto-1 program registers is configured. It is used to pre-select the channels for auto-1 scanning. It needs two operation frames for a complete configuration. More setting details are shown in Table 3 and Table 4.

| BITS      | DESCRIPTION                                                                                                                                                                                                                                                                                                     |      |      |      |  |  |  |  |  |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|--|--|--|--|--|--|

| DI[15:12] | 0010 = Selects auto-1 mode                                                                                                                                                                                                                                                                                      |      |      |      |  |  |  |  |  |  |

| DI11      | 0 = Chip retains values of DI[10:0] from previous frame<br>1 = Enables programming of bits DI[10:0]                                                                                                                                                                                                             |      |      |      |  |  |  |  |  |  |

| DI10      | 0 = The channel counter increments every conversion (no reset)<br>1 = The channel counter is reset to the lowest programmed channel in the auto-1 program register                                                                                                                                              |      |      |      |  |  |  |  |  |  |

| DI[9:7]   | xxx = Do not care                                                                                                                                                                                                                                                                                               |      |      |      |  |  |  |  |  |  |

| DI6       | 0 = Selects 0V to V <sub>REF</sub> input range (Range 1)<br>1 = Selects 0V to 2 × V <sub>REF</sub> input range (Range 2)                                                                                                                                                                                        |      |      |      |  |  |  |  |  |  |

| DI5       | 0 = Normal operation (no power-down).<br>1 = Powers down on the 16 <sup>th</sup> SCLK falling edge.                                                                                                                                                                                                             |      |      |      |  |  |  |  |  |  |

| DI4       | 0 = SDO outputs current channel address of the channel on DO[15:12], and the 12-bit conversion results on DO[11:0]<br>1 = GPIO3 to GPIO0 data (both input and output) corresponds to DO[15:12] in the following order as shown. Lower data bits DO[11:0] means 12-bit conversion result for the current channel |      |      |      |  |  |  |  |  |  |

|           | DO15                                                                                                                                                                                                                                                                                                            | DO14 | DO13 | DO12 |  |  |  |  |  |  |

|           | GPIO3 <sup>(1)</sup> GPIO2 <sup>(1)</sup> GPIO1 <sup>(1)</sup> GPIO0 <sup>(1)</sup>                                                                                                                                                                                                                             |      |      |      |  |  |  |  |  |  |

|           | GPIO data of the channels is used as output. The data of the channel configured as input will be ignored by the device. The SDI bits and corresponding GPIO are shown below.                                                                                                                                    |      |      |      |  |  |  |  |  |  |

| DI[3:0]   | DI3 DI2 DI1 DI0                                                                                                                                                                                                                                                                                                 |      |      |      |  |  |  |  |  |  |

|           | GPIO3 <sup>(1)</sup> GPIO2 <sup>(1)</sup> GPIO1 <sup>(1)</sup> GPIO0 <sup>(1)</sup>                                                                                                                                                                                                                             |      |      |      |  |  |  |  |  |  |

NOTE: 1. GPIO1 to GPIO3 are available only for TSSOP package. TQFN packaged device offers GPIO0 only.

Figure 6. Example for Auto-1 Mode Timing Diagram

NOTE: During the programming process, the chip continues to run in the selected mode. The SDO is valid, but it is impossible to change the range or write GPIO data to the device during programming.

#### Figure 7. Auto-1 Program Register Setting

#### Table 3. Program Register Details for Auto-1 Mode

| BITS      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |         |  |  |  |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|--|--|

| Frame 1   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |  |  |  |

| DI[15:12] | 1000 = Enters the sequence of auto-1 program. Configuration is done in the next frame                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | NA      |  |  |  |

| DI[11:0]  | Do not care.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | NA      |  |  |  |

| Frame 2   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |  |  |  |

| DI[15:0]  | 1 (Individual Bit) = According bit is set to '1' means the according channel is selected in scanning sequence.<br>The channel numbers are one-to-one associated with the SDI bits. For example, DI15 corresponds to CH15, DI14 corresponds to CH14 DI0 corresponds to CH0<br>0 (Individual Bit) = According bit is set to '0' means the according channel is skipped in scanning sequence.<br>The channel numbers are one-to-one associated with the SDI bits. For example, DI15 corresponds to CH15, DI14 corresponds to CH14 DI0 corresponds to CH0 | All '1' |  |  |  |

#### Table 4. Channels Mapping to SDI Bits for the SGM5200

| Device (1) |     |      |      |      |      |      |     | SDI | Bits |     |     |     |     |     |     |     |

|------------|-----|------|------|------|------|------|-----|-----|------|-----|-----|-----|-----|-----|-----|-----|

| Device     |     | DI14 | DI13 | DI12 | DI11 | DI10 | DI9 | DI8 | DI7  | DI6 | DI0 | DI4 | DI3 | DI2 | DI1 | DI0 |

| 16 Chan    | 1/0 | 1/0  | 1/0  | 1/0  | 1/0  | 1/0  | 1/0 | 1/0 | 1/0  | 1/0 | 1/0 | 1/0 | 1/0 | 1/0 | 1/0 | 1/0 |

#### NOTE:

1. The chip only scans the selected channels when in auto-1 mode.

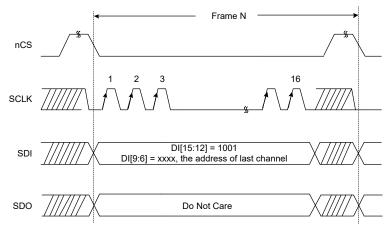

#### **Operating in Auto-2 Mode**

The mode control register settings for auto-2 mode are shown in Table 5. There are both mode registers and program registers for auto-1 mode operation.

To let the chip work in auto-2 mode, it is necessary configure auto-2 program register firstly to configure the last channel which is going to be reached.

The program register settings for auto-2 mode are shown in Table 6.

Before running in auto-2 mode, the last target channel CH2 (example) must be configured in auto-2 program registers (details see auto-2 program registers configuration sequence).

The example about the chip how to work in auto-2 mode and scan channels CH0, CH1 and CH2 automatically is shown in Figure 8. In this sequence, in the frame N sent entering auto-2 mode command and channel CH0 is selected automatically (the chip switches to CH0 automatically). In the frame N+1, the chip switches MUX to

| Table 5. Mode Control | <b>Register Detai</b> | Is for Auto-2 Mode |

|-----------------------|-----------------------|--------------------|

|-----------------------|-----------------------|--------------------|

CH02. In the frame N+2, the chip samples the CH0 input and gives out ADC conversion result, and the MUX is switched to CH1 automatically. In the frame N+3, the chip samples CH1 and gives out ADC conversion, and the MUX is switched to CH2 automatically, and so on. This process repeats until the last selected channel is reached (In this example, the last channel is CH2), and the process loops back from channel CH0.

In any case, re-entering auto-2 mode possibly from auto-1 mode, manual mode and auto-2 mode will cause the chip channel scan sequence to restart from the channel CH0.

Note that changing the auto-2 program register during the chip is working in auto-2 mode, the chip scan restarts from channel CH0.

Figure 9 shows how the auto-2 program registers is configured. It's for pre-select the last channel for auto-2 scanning. It needs one operation frames for a complete configuration. Refer to Table 6 for more setting details

| BITS      | DESCRIPTION                                                                                                                                                                                                                                                                                                     |                      |           |                      |      |  |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------|----------------------|------|--|--|

| DI[15:12] | 0011 = Selects auto-2 mode                                                                                                                                                                                                                                                                                      |                      |           |                      | 0001 |  |  |

| DI11      | 0 = Chip retains values of DI<br>1 = Enables programming of                                                                                                                                                                                                                                                     |                      | le        |                      | 0    |  |  |

| DI10      | 0 = Channel counter increme<br>1 = Channel number is reset                                                                                                                                                                                                                                                      |                      | set)      |                      | 0    |  |  |

| DI[9:7]   | xxx = Do not care                                                                                                                                                                                                                                                                                               |                      |           |                      | 000  |  |  |

| DI6       | 0 = Selects V <sub>REF</sub> input range (Range 1)<br>1 = Selects 2 × V <sub>REF</sub> input range (Range 2)                                                                                                                                                                                                    |                      |           |                      |      |  |  |

| DI5       | 0 = Normal operation (no power-down)<br>1 = Powers down on the 16 <sup>th</sup> SCLK falling edge                                                                                                                                                                                                               |                      |           |                      |      |  |  |

| DI4       | 0 = SDO outputs current channel address of the channel on DO[15:12], and the 12-bit conversion results on DO[11:0]<br>1 = GPIO3 to GPIO0 data (both input and output) corresponds to DO[15:12] in the following order as shown. Lower data bits DO[11:0] means 12-bit conversion result for the current channel |                      |           |                      |      |  |  |

|           | DO15                                                                                                                                                                                                                                                                                                            | DO14                 | DO13      | DO12                 |      |  |  |

|           | GPI03 <sup>(1)</sup> GPI02 <sup>(1)</sup> GPI01 <sup>(1)</sup> GPI00 <sup>(1)</sup>                                                                                                                                                                                                                             |                      |           |                      |      |  |  |

|           | GPIO data of the channels is used as output. The data of the channel configured as input will be ignored by the device. The SDI bits and corresponding GPIO are shown below.                                                                                                                                    |                      |           |                      |      |  |  |

| DI[3:0]   | DI3                                                                                                                                                                                                                                                                                                             | DI2                  | DI1       | DI0                  | 0000 |  |  |

|           | GPIO3 <sup>(1)</sup>                                                                                                                                                                                                                                                                                            | GPIO2 <sup>(1)</sup> | GPIO1 (1) | GPIO0 <sup>(1)</sup> |      |  |  |

NOTE: 1. GPIO1 to GPIO3 are available only for TSSOP package. TQFN packaged device offers GPIO0 only.

Figure 8. Example for Auto-2 Mode Timing Diagram

NOTE: During the programming process, the chip continues to run in the selected mode. The SDO is valid, but it is impossible to change the range or write GPIO data to the device during programming.

#### Figure 9. Auto-2 Program Register Setting

#### Table 6. Program Register Details for Auto-2 Mode

| BITS      | DESCRIPTION                                                                                                                                                                                                                                   |    |  |  |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|

| DI[15:12] | 1001 = Configure auto-2 program register                                                                                                                                                                                                      | NA |  |  |  |

| DI[11:10] | Do not care.                                                                                                                                                                                                                                  | NA |  |  |  |

| DI[9:6]   | aaaa = The 4-bit data means the address of the last channel in the scanning sequence. In auto-2 mode, the channel counter begins at CH0, increasing each frame until equal to 'aaaa'. The channel counter roles over to CH0 in the next frame |    |  |  |  |

| DI[5:0]   | Do not care.                                                                                                                                                                                                                                  | NA |  |  |  |

#### **Continued Operation in a Selected Mode**

When the chip is configured to working in one mode, the user may want to keep working in this mode. How to continue operating in a selected mode is shown in Table 7.

#### Table 7. Continued Operation in a Selected Mode

| BITS      | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                              |         |  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|

| DI[15:12] | 0000 = The chip continues to operate in current mode. When in auto-1 and auto-2 modes, the channel counter increments automatically; when in the manual mode, it continues with the last selected channel. The chip ignores datas on DI[11:0] and continues operating with the previous settings. SDI can be held low when there is no changes are required in the mode control register |         |  |

| DI[11:0]  | Chip ignores these bits when DI[15:12] is '0000'.                                                                                                                                                                                                                                                                                                                                        | All '0' |  |

### Programming

#### **Digital Output**

Table 8 shows the theory output codes according to different input ranges. The ADC codes are in straight binary format.

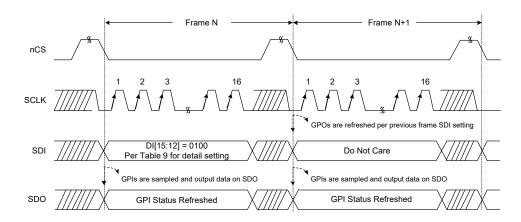

#### **GPIO Registers**

The GPIO pins can be used as GPO (general-purpose output) or GPI (general-purpose input).

Table 8. Ideal Input Voltages and Output Codes

The GPIO functions and GPO status are set in GPIO program registers, more details refer to Table 9.

The GPO refresh include two steps, first step setting in operation frame N, second steps the chip refresh GPO data on the nCS falling edge in frame N+1. More details refer to Figure 10.

The chip samples the GPI input on the falling edge of nCS in frame N, and outputs GPI data on SDO in the same frame N.

| Description                 | Analog Value                           |                                            | Digital Output     |          |  |

|-----------------------------|----------------------------------------|--------------------------------------------|--------------------|----------|--|

| Full Scale Range            | Range 1 $\rightarrow$ V <sub>REF</sub> | Range 2 $\rightarrow$ 2 × V <sub>REF</sub> | Straight Binary    |          |  |

| Least Significant Bit (LSB) | V <sub>REF</sub> /4096                 | 2 × V <sub>REF</sub> /4096                 | Binary Code        | Hex Code |  |

| Full Scale                  | V <sub>REF</sub> - 1LSB                | 2 × V <sub>REF</sub> - 1LSB                | 1111 1111 1111 FFF |          |  |

| Midscale                    | V <sub>REF</sub> /2                    | V <sub>REF</sub>                           | 1000 0000 0000 800 |          |  |

| Midscale - 1LSB             | V <sub>REF</sub> /2 - 1LSB             | V <sub>REF</sub> - 1LSB                    | 0111 1111 1111     | 7FF      |  |

| Zero                        | 0V                                     | 0V                                         | 0000 0000 0000     | 000      |  |

NOTE: During the programming process, the chip continues to run in the selected mode. The SDO is valid, but it is impossible to change the range or write GPIO data to the device during programming.

#### Figure 10. GPIO Program Register Setting

#### Table 9. GPIO Program Register Details

| BITS               | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | RESET<br>STATE |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| DI[15:12]          | 0100 = Selects GPIO program registers for programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | NA             |

| DI[11:10]          | 00 = Reserved bits, must be '00'                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 00             |

| DI9                | 0 = Normal operation<br>1 = Resets all registers in the next nCS frame to default value (it also resets itself)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0              |

| DI8                | 0 = GPIO3 is still as general-purpose I/O. Program 0 for TQFN packaged device<br>1 = Configures GPIO3 as the chip power-down input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0              |

| DI7                | 0 = GPIO2 is still as general-purpose I/O. Program 0 for TQFN packaged device<br>1 = Configures GPIO2 as device range input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0              |

| DI[6:4]            | 000 = GPIO1 and GPIO0 are still as general-purpose I/Os. Valid setting for TQFN packaged device<br>xx1 = Configures GPIO0 as 'high or low' alarm output. It is an active high output. GPIO1 is still as general-purpose<br>I/O. Valid setting for TQFN packaged device<br>010 = Configures GPIO0 as high alarm output. It is an active high output. GPIO1 is still as general-purpose I/O. Valid<br>setting for TQFN packaged device<br>100 = Configures GPIO1 as low alarm output. It is an active high output. GPIO0 is still as general-purpose I/O. Valid<br>configuration is not valid for TQFN packaged device<br>110 = Configures GPIO1 as low alarm output and GPIO0 as a high alarm output. These are active high outputs.<br>Configuration is not valid for TQFN packaged device | 000            |