# Positive High-Voltage Hot Swap and Inrush Current Controller with Power-Limiting

### **GENERAL DESCRIPTION**

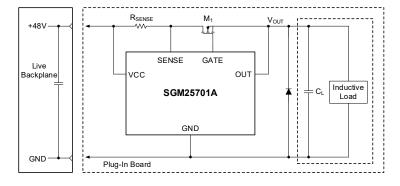

The SGM25701A is a positive hot swap controller that allows a board to be safely inserted or removed from a live backplane. Inrush current control function can effectively reduce the voltage drop on the power supply rail.

The SGM25701A offers programmable power-limiting and current limit to ensure that the external MOSFET operates within its safe operating area (SOA) at all times.

The chip has a good output indication function when the  $V_{OUT}$  increases to within the 1.4V range of the  $V_{IN}$ .

Programmable under-voltage lockout or over-voltage lockout is used to turn off the device if the  $V_{\text{IN}}$  drops below or raises over a threshold value. The fault detection time and initial insertion delay time can also be adjusted by the user.

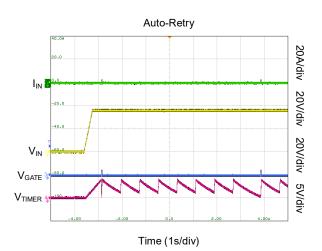

When a fault is detected, the device will go into auto-retry mode.

SGM25701A is available in a Green MSOP-10 package.

### **FEATURES**

- Wide Input Voltage Range: 9V to 70V

- Inrush Current Limit, PCB can be Safely Inserted into Live Equipment

SGM25701A

- External Device Programming Maximum Loss Limit

- Programmable Current Limit

- Adjustable Under-Voltage Lockout (EN/UVLO)

- Adjustable Over-Voltage Lockout (OVLO)

- Open-Drain for Good Output Indication

- Quick Cut-Off Function when Severe Over-Current Occurs

- Configure Charge Pump/Gate Driver for External N-MOSFET

- The Setting of the Insertion Time Allowing the Ringing and Transient Recovery Process after the System Connected

- Adjustable Fault Timing to Prevent False Shutdown

- Retry Behavior after Fault: Auto-Retry

- Available in a Green MSOP-10 Package

### **APPLICATIONS**

24V/48V Industrial Systems Server Backplane Systems Solid State Circuit Breaker Base Station

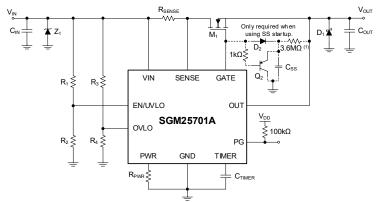

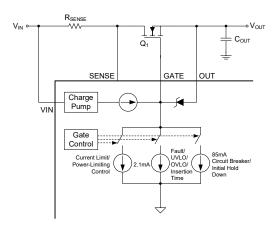

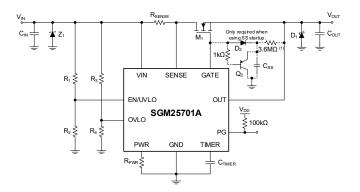

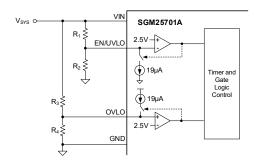

### TYPICAL APPLICATION

NOTE: 1. The resistance provides a stable leaking path for the GATE pin when the VIN is quickly pulled low in the case of repeated restarts.

**Figure 1. Typical Application Circuit**

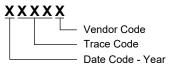

### PACKAGE/ORDERING INFORMATION

| MODEL     | PACKAGE<br>DESCRIPTION | SPECIFIED<br>TEMPERATURE<br>RANGE | ORDERING<br>NUMBER | PACKAGE<br>MARKING       | PACKING<br>OPTION   |

|-----------|------------------------|-----------------------------------|--------------------|--------------------------|---------------------|

| SGM25701A | MSOP-10                | -40°C to +125°C                   | SGM25701AXMS10G/TR | SGM004<br>XMS10<br>XXXXX | Tape and Reel, 4000 |

### MARKING INFORMATION

NOTE: XXXXX = Date Code, Trace Code and Vendor Code.

Green (RoHS & HSF): SG Micro Corp defines "Green" to mean Pb-Free (RoHS compatible) and free of halogen substances. If you have additional comments or questions, please contact your SGMICRO representative directly.

### **ABSOLUTE MAXIMUM RATINGS**

| ADSULUTE MAXIMUM KATIN            | 163            |

|-----------------------------------|----------------|

| VIN to GND <sup>(1)</sup>         | 0.3V to 80V    |

| SENSE, OUT and PG to GND          | 0.3V to 80V    |

| GATE to GND (1)                   | 0.3V to 80V    |

| OUT to GND (1ms Transient) (2)    | 1V to 80V      |

| EN/UVLO to GND                    | 0.3V to 80V    |

| OVLO to GND                       | 0.3V to 6V     |

| VIN to SENSE                      | 0.3V to 0.3V   |

| Package Thermal Resistance        |                |

| MSOP-10, θ <sub>JA</sub>          | 147°C/W        |

| MSOP-10, θ <sub>JB</sub>          | 94°C/W         |

| MSOP-10, θ <sub>JC</sub>          | 52°C/W         |

| Junction Temperature              | +150°C         |

| Storage Temperature Range         | 65°C to +150°C |

| Lead Temperature (Soldering, 10s) | +260°C         |

| ESD Susceptibility                |                |

| HBM                               | 2000V          |

| CDM                               | 1000V          |

|                                   |                |

### NOTES:

- 1. When the chip is enabled, the voltage of GATE pin is generally 12.7V higher than the VIN pin voltage. Therefore, the absolute maximum rating of  $V_{\text{IN}}$  (80V) is only applicable when the chip is stopped, or since the absolute maximum rating of the GATE pin is also 80V, the 80V of  $V_{\text{IN}}$  is only applicable when the pin is momentarily surged.

- 2. An external MOSFET with  $V_{\text{GS\_TH}}$  higher than  $V_{\text{OUT}}$  is required during -ve transients. This effectively prevents false turn-on of the MOSFET during -ve transients.

### RECOMMENDED OPERATING CONDITIONS

| Supply Voltage, V <sub>IN</sub> | .9V to | 70V |

|---------------------------------|--------|-----|

| PG Voltage                      | .0V to | 70V |

| Junction Temperature Range40°C  | to +12 | 5°C |

### **OVERSTRESS CAUTION**

Stresses beyond those listed in Absolute Maximum Ratings may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect reliability. Functional operation of the device at any conditions beyond those indicated in the Recommended Operating Conditions section is not implied.

### **ESD SENSITIVITY CAUTION**

This integrated circuit can be damaged if ESD protections are not considered carefully. SGMICRO recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage. ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because even small parametric changes could cause the device not to meet the published specifications.

### **DISCLAIMER**

SG Micro Corp reserves the right to make any change in circuit design, or specifications without prior notice.

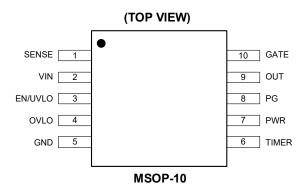

# **PIN CONFIGURATION**

# **PIN DESCRIPTION**

| PIN | NAME    | I/O | FUNCTION                                                                                                                                                                                                                                                                                                     |

|-----|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | SENSE   | I   | Current Sense Pin. The voltage from the input pin to this pin is measured by the current flowing into the sense resistor. When the detected voltage at the R <sub>SENSE</sub> exceeds 55mV, it indicates that the circuit is in an overload state at this time, and the fault timer is started at this time. |

| 2   | VIN     | 1   | Input Supply Voltage. It is recommended to place a small bypass capacitor close this pin.                                                                                                                                                                                                                    |

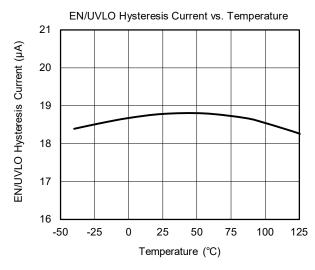

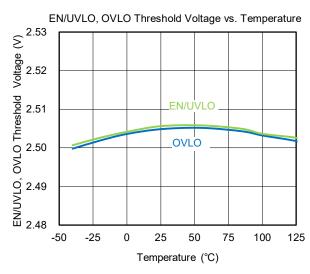

| 3   | EN/UVLO | I   | Enable and Under-Voltage Lockout Pin. The EN/UVLO threshold is programmed by an external resistor divider. Internal hysteresis is controlled by a 19µA current source. The threshold of the turn-on voltage is set to 2.5V. It is also possible to control this pin for remote shutdown.                     |

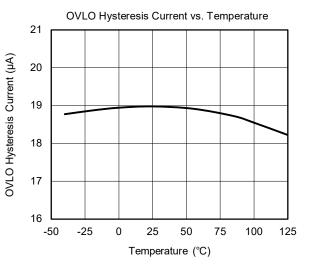

| 4   | OVLO    | I   | Over-Voltage Lockout Pin. The over-voltage threshold is programmed by the resistor divider from the power supply to the OVLO terminal to GND. Hysteretic control is achieved through an internally programmed $19\mu A$ current source. The over-voltage shutdown threshold is set to 2.5V.                  |

| 5   | GND     | -   | Ground.                                                                                                                                                                                                                                                                                                      |

| 6   | TIMER   | I/O | Fault Timer Pin. An external capacitor between TIMER and GND pins provides the fault time delay and insertion delay time. The chip's restart time is also controlled by this capacitor.                                                                                                                      |

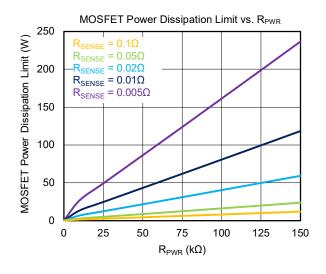

| 7   | PWR     | I   | Power-Limiting Programmable Pin. The $R_{\text{PWR}}$ and $R_{\text{SENSE}}$ determine the maximum allowable dissipation of the external MOSFET.                                                                                                                                                             |

| 8   | PG      | 0   | Power Good Indicator Pin. The V <sub>DS</sub> voltage of the external MOSFET determines its state.                                                                                                                                                                                                           |

| 9   | OUT     | ı   | Power Output Pin. Connect this pin to output (i.e., external MOSFET source). The chip monitors MOSFET V <sub>DS</sub> voltage through this pin to limit the MOSFET power and control the PG signal accordingly.                                                                                              |

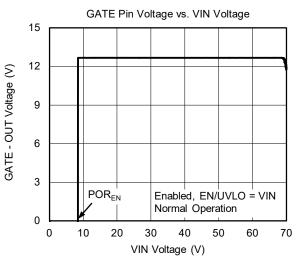

| 10  | GATE    | 0   | Gate Drive Output. This pin is connected to the gate of the external MOSFET. During normal operation, the voltage on this pin will be 12.7V higher than the OUT pin.                                                                                                                                         |

# **ELECTRICAL CHARACTERISTICS**

$(T_J = -40^{\circ}C \text{ to } +125^{\circ}C, \text{ typical values are at } T_J = +25^{\circ}C, V_{IN} = 48V, \text{ unless otherwise noted.})$

| PARAMETER                                                  | SYMBOL                    | CONDITIONS                                                                  | MIN  | TYP  | MAX  | UNITS |

|------------------------------------------------------------|---------------------------|-----------------------------------------------------------------------------|------|------|------|-------|

| VIN                                                        |                           |                                                                             |      |      |      |       |

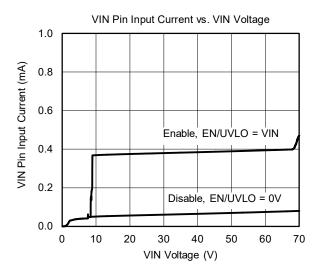

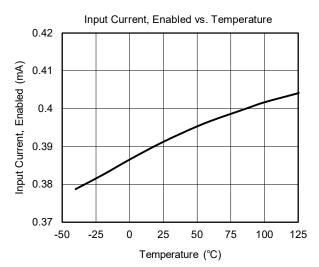

| Input Current, Enabled                                     | I <sub>IN_EN</sub>        | V <sub>EN/UVLO</sub> > 2.5V and V <sub>OVLO</sub> < 2.5V                    |      | 0.40 | 0.55 | mA    |

| Input Current, Disabled                                    | I <sub>IN_DIS</sub>       | V <sub>EN/UVLO</sub> < 2.5V or V <sub>OVLO</sub> > 2.5V                     |      | 70   | 110  | μΑ    |

| Power-On Reset Threshold at VIN to Trigger Insertion Timer | POR <sub>IT</sub>         | V <sub>IN</sub> increasing                                                  |      | 7.6  | 8.1  | V     |

| Power-On Reset Threshold at VIN to Enable All Functions    | POR <sub>EN</sub>         | V <sub>IN</sub> increasing                                                  |      | 8.4  | 9.0  | V     |

| POR <sub>EN</sub> Hysteresis                               | POR <sub>EN_HYS</sub>     | V <sub>IN</sub> decreasing                                                  |      | 90   |      | mV    |

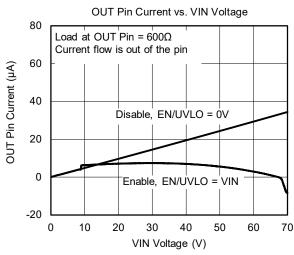

| оит                                                        |                           |                                                                             |      |      |      |       |

| OUT Bias Current, Enabled                                  | I <sub>OUT_EN</sub>       | V <sub>OUT</sub> = V <sub>IN</sub> , normal operation                       |      | 6    |      |       |

| OUT Bias Current, Disabled (1)                             | I <sub>OUT_DIS</sub>      | Disabled, V <sub>OUT</sub> = 0V, V <sub>SENSE</sub> = V <sub>IN</sub>       |      | 25   |      | μA    |

| EN/UVLO, OVLO                                              |                           |                                                                             |      |      |      |       |

| EN/UVLO Threshold Voltage                                  | V <sub>EN/UVLO</sub>      |                                                                             | 2.4  | 2.5  | 2.6  | V     |

| EN/UVLO Hysteresis Current                                 | I <sub>EN/UVLO_HYS</sub>  | V <sub>EN/UVLO</sub> = 1V                                                   | 12   | 19   | 26   | μΑ    |

| ENUNA O Dalas Time                                         |                           | Delay to GATE high                                                          |      | 15   |      | μs    |

| EN/UVLO Delay Time                                         | t <sub>EN/UVLO_DLY</sub>  | Delay to GATE low                                                           |      | 1    |      |       |

| EN/UVLO Bias Current                                       | V <sub>EN/UVLO_BIAS</sub> | V <sub>EN/UVLO</sub> = 48V                                                  |      |      | 1    | μΑ    |

| OVLO Threshold Voltage                                     | V <sub>OVLO</sub>         |                                                                             | 2.4  | 2.5  | 2.6  | V     |

| OVLO Hysteresis Current                                    | I <sub>OVLO_HYS</sub>     | V <sub>OVLO</sub> = 2.6V                                                    | 12   | 19   | 26   | μΑ    |

| OVI O Delevi Time                                          | 4                         | Delay to GATE high                                                          |      | 15   |      |       |

| OVLO Delay Time                                            | tovlo_dly                 | Delay to GATE low                                                           |      | 1    |      | μs    |

| OVLO Bias Current                                          | V <sub>OVLO_BIAS</sub>    | V <sub>OVLO</sub> = 2.4V                                                    |      |      | 1    | μΑ    |

| PWR                                                        |                           |                                                                             | •    | •    | •    |       |

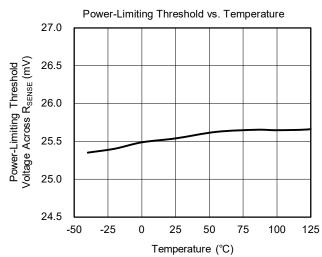

| Power-Limiting Sense Voltage                               | PWR <sub>LIM-1</sub>      | $V_{(SENSE - OUT)} = 48V$ , $R_{PWR} = 150k\Omega$                          | 19   | 25   | 31   | mV    |

| (VIN - SENSE)                                              | PWR <sub>LIM-2</sub>      | $V_{(SENSE - OUT)} = 24V, R_{PWR} = 75k\Omega$                              |      | 25   |      | mV    |

| PWR Pin Current                                            | I <sub>PWR</sub>          | V <sub>PWR</sub> = 2.5V                                                     |      | 20   |      | μΑ    |

| GATE Pin                                                   |                           |                                                                             | •    |      |      | •     |

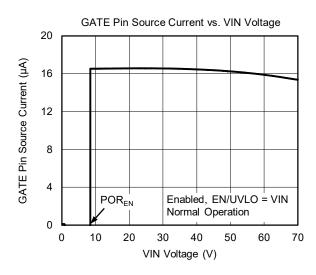

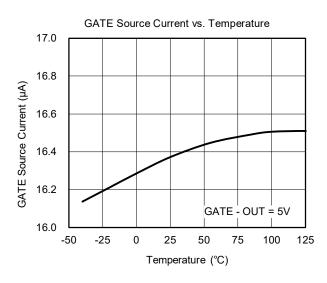

| Source Current                                             |                           | Normal operation, V <sub>(GATE - OUT)</sub> = 5V                            | 10   | 16   | 22   | μΑ    |

| Circle Command                                             | I <sub>GATE</sub>         | V <sub>EN/UVLO</sub> < 2.5V                                                 | 1.8  | 2.1  | 2.4  | mA    |

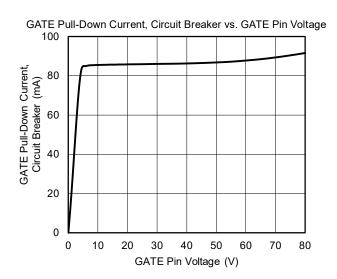

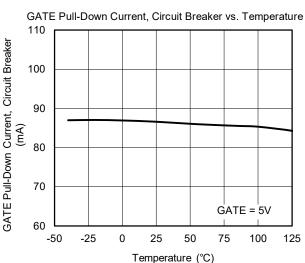

| Sink Current                                               |                           | $V_{(VIN-SENSE)}$ = 150mV or $V_{IN}$ < POR <sub>IT</sub> , $V_{GATE}$ = 5V | 55   | 85   | 115  | mA    |

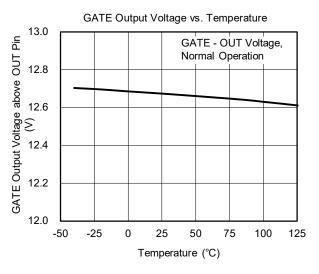

| Gate Output Voltage in Normal Operation                    | $V_{GATE}$                | GATE - OUT voltage                                                          | 12.2 | 12.7 | 13.2 | V     |

NOTE: 1. A  $1M\Omega$  resistor between OUT and SENSE pins determines the bias current (disabled) of  $V_{OUT}$ .

# **ELECTRICAL CHARACTERISTICS (continued)**

$(T_J = -40^{\circ}\text{C to } + 125^{\circ}\text{C}, \text{ typical values are at } T_J = +25^{\circ}\text{C}, V_{IN} = 48\text{V}, \text{ unless otherwise noted.})$

| PARAMETER                           | SYMBOL              | CONDITIONS                                                       | MIN  | TYP  | MAX  | UNITS |

|-------------------------------------|---------------------|------------------------------------------------------------------|------|------|------|-------|

| Current Limit                       |                     |                                                                  |      |      |      |       |

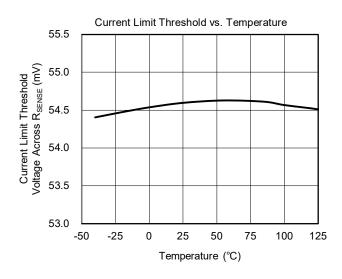

| Threshold Voltage                   | V <sub>CL</sub>     | VIN - SENSE voltage                                              | 48.5 | 55.0 | 61.5 | mV    |

| Response Time                       | t <sub>CL</sub>     | VIN - SENSE stepped from 0mV to 80mV                             |      | 10   |      | μs    |

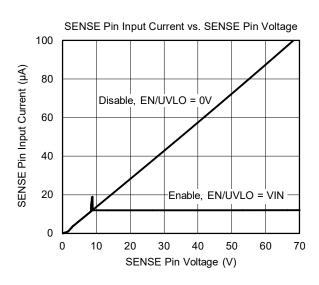

| OFNICE In most Command              |                     | Enabled, V <sub>SENSE</sub> = V <sub>OUT</sub>                   |      | 12   |      |       |

| SENSE Input Current                 | I <sub>SENSE</sub>  | Disabled, V <sub>OUT</sub> = 0V                                  |      | 70   |      | μA    |

| Circuit Breaker                     |                     |                                                                  |      |      |      |       |

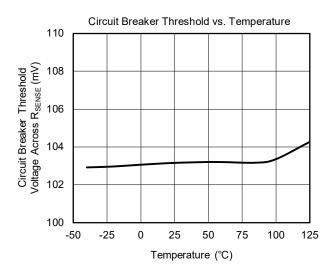

| Threshold Voltage                   | V <sub>CB</sub>     | VIN - SENSE voltage                                              | 80   | 105  | 130  | mV    |

| Response Time                       | t <sub>CB</sub>     | VIN - SENSE stepped from 0mV to 150mV, time to GATE low, no load |      | 0.4  | 1.2  | μs    |

| TIMER                               |                     |                                                                  |      |      |      |       |

| Upper Threshold                     | $V_{TMRH}$          |                                                                  | 3.85 | 4.00 | 4.15 | V     |

| Lower Threshold                     | \/                  | Restart cycles                                                   | 1.20 | 1.25 | 1.30 | V     |

| Lower Trireshold                    | $V_{TMRL}$          | End of 8th cycle                                                 |      | 0.3  |      | V     |

| Insertion Time Current              |                     |                                                                  | 3    | 5    | 7    | μA    |

| Sink Current, End of Insertion Time | ] ,                 | V <sub>TIMER</sub> = 2V                                          | 1.2  | 1.6  | 2.0  | mA    |

| Fault Detection Current             | I <sub>TIMER</sub>  |                                                                  | 70   | 95   | 120  | μA    |

| Fault Sink Current                  |                     |                                                                  | 1.5  | 2.4  | 3.3  | μΑ    |

| Fault Restart Duty Cycle            | DC <sub>FAULT</sub> |                                                                  |      | 0.43 |      | %     |

| Fault to GATE Low Delay             | t <sub>FAULT</sub>  | TIMER pin reaches 4V                                             |      | 1    |      | μs    |

| PG                                  |                     |                                                                  |      |      |      |       |

| Threshold Measured at SENSE -       | DC                  | Decreasing                                                       | 0.8  | 1.4  | 2.0  | V     |

| OUT                                 | PG <sub>TH</sub>    | Increasing, relative to decreasing threshold                     | 0.8  | 1.4  | 2.0  | V     |

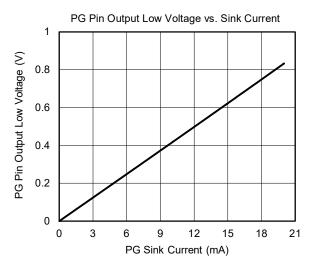

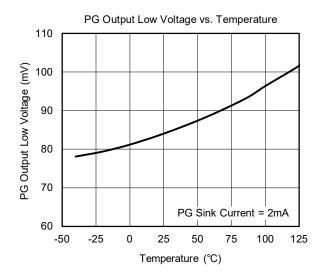

| Output Low Voltage                  | PG <sub>VOL</sub>   | I <sub>SINK</sub> = 2mA                                          |      | 85   | 150  | mV    |

| Off Leakage Current                 | PG <sub>IOH</sub>   | V <sub>PG</sub> = 70V                                            |      |      | 2    | μΑ    |

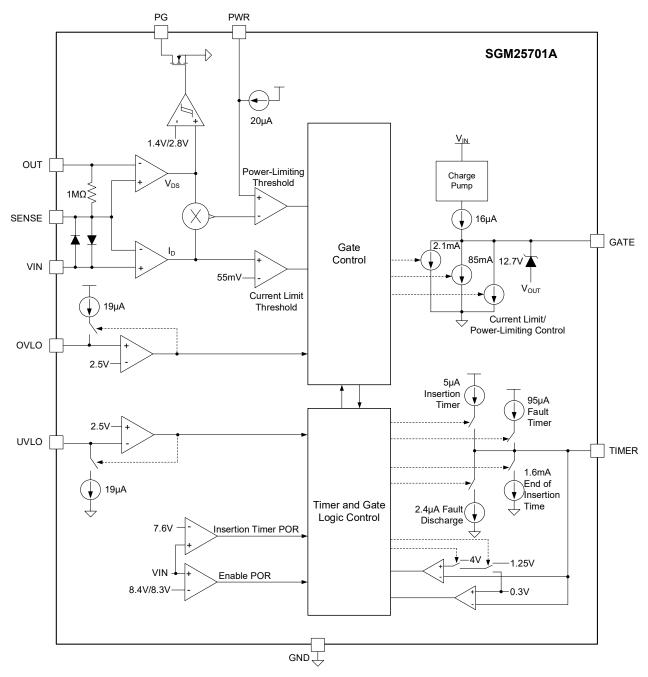

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 2. Block Diagram

# TYPICAL PERFORMANCE CHARACTERISTICS

### **DETAILED DESCRIPTION**

### Overview

The SGM25701A is designed to limit the generated inrush current when the circuit card is plugged into and removed from the live backplane or hot power supply, reduce the voltage sag and dV/dt on the load during power-on, and avoid unnecessary reset and other impacts. The SGM25701A not only has current limit function, but also detects power dissipation when used in series to ensure the operations within SOA. Once the current limit or power-limiting exceeds the preset value, the SGM25701A components will repeatedly try to recover until the faults are removed. When the input voltage range exceeds EN/UVLO and OVLO ranges, the device breaks during the period.

### **Current Limit**

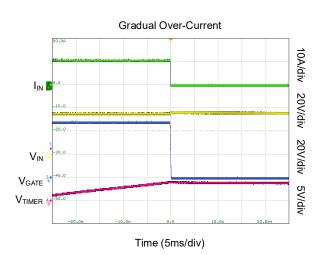

The device triggers over-current protection when the voltage on the  $R_{\text{SENSE}}$  reaches the current limit threshold of 55mV. In this event, the device limits the current in  $M_1$  by controlling GATE pin, and the TIMER pin is active. If the current is lower than the threshold before the fault timeout period ends, the device recovers. Note that  $R_{\text{SENSE}}$  cannot be larger than  $100\text{m}\Omega$ .

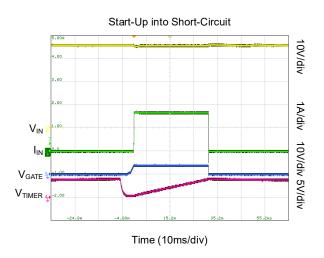

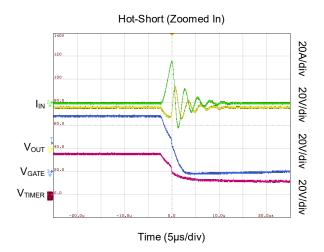

### Circuit Breaker

Once the load current rises rapidly, the current on  $R_{\mathsf{SENSE}}$  may exceed the current limit value before the current limit control loop responds. When the current on  $R_{\mathsf{SENSE}}$  exceeds two times the current limit value,  $M_1$  is pulled down by the 85mA current source to turn off quickly, and the fault timeout starts timing until the voltage on  $R_{\mathsf{SENSE}}$  drops below 105mV. If  $V_{\mathsf{TIMER}}$  reaches 4V before current limit or power-limiting ceases,  $M_1$  will be pulled off by the 2.1mA current source.

### **Power-Limiting**

The power-limiting ensures that the power dissipation (MAX) of  $M_1$  is within the SOA of the SGM25701A. The device defines the power dissipation of the  $M_1$  by sensing the  $V_{DS}$  of the  $M_1$  and the drain current flowing through  $R_{SENSE}$ . The current and voltage values will be compared to the resistor that is used to program the power-limiting value on the PWR pin. The fault timer is activated if the power-limiting circuit is active.

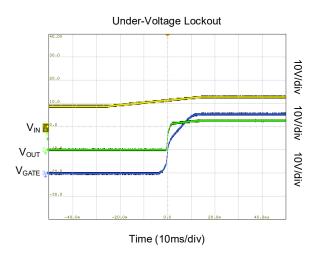

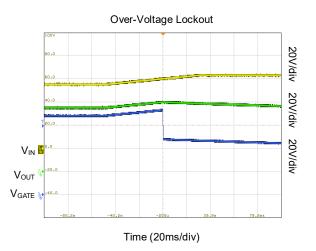

### **EN/UVLO and OVLO**

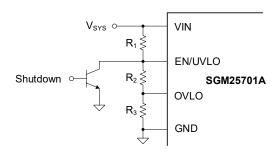

$M_1$  starts to work when the power supply voltage  $(V_{IN})$ operates between the under-voltage lockout value and the over-voltage lockout value programmed by the resistor network (R<sub>1</sub>, R<sub>2</sub>, R<sub>3</sub> and R<sub>4</sub>). When the input supply voltage is lower than the EN/UVLO threshold, the 19µA current sink inside the EN/UVLO is enabled, the current source inside the OVLO is turned off, and M<sub>1</sub> is kept off by the 2.1mA current source pull-down of the GATE pin. As the input supply voltage increases, when V<sub>EN/UVLO</sub> exceeds 2.5V, its internal 19µA current sink turns off to increase the EN/UVLO voltage, providing a threshold of hysteresis when M<sub>1</sub> is enabled by the 16µA current source at GATE pin. The EN/UVLO pin can be connected to VIN to set the minimum EN/UVLO level, when the  $V_{\text{IN}}$  reaches the power-on reset threshold (POR<sub>EN</sub>), M<sub>1</sub> is enabled. When the power supply voltage rises so that the voltage on the OVLO pin exceeds 2.5V,  $M_1$  is pulled down by the 2.1mA current source at GATE pin. At this time, the OVLO pin voltage is higher than 2.5V, the internal 19µA current source is turned on, and the V<sub>OVLO</sub> is decreased to provide threshold hysteresis. Please refer to the application and implementation to calculate the resistance value of  $R_1 \sim R_4$  to program the threshold.

# **DETAILED DESCRIPTION (continued)**

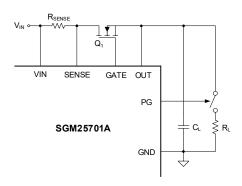

### **Power Good Pin**

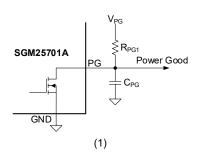

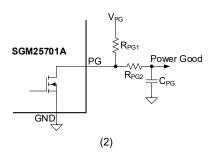

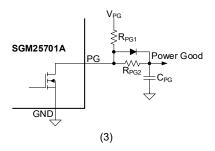

The PG pin remains high during the turn-on period until the  $V_{IN}$  increases above  $\approx$  1V. At this time, as  $V_{IN}$ increases, PG continues to pull low. When the  $V_{\text{OUT}}$ increases to within 1.4V of the SENSE pin voltage, (V<sub>DS</sub> < 1.4V), PG is switched high. If  $V_{DS}$  of  $M_1$  increases above 2.8V, PG switches low. PG requires a pull-up resistor and the pull-up voltage (VPG) may be as high as 70V for transient capability up to 80V. If PG requires a delay, please refer to Figure 3. Capacitor CPG adds a delay to the rising edge in Figure 3 (1). The slew rate of the rising edge is determined by  $R_{PG1}$  +  $R_{PG2}$  and  $C_{PG}$ , and the slew rate of the falling edge is determined by R<sub>PG2</sub> and C<sub>PG</sub> in Figure 3 (2). Add a diode as shown in Figure 3 (3) to achieve an equal slope of rising edge and falling edge. For most applications, the typical values in Figure 3 (2) are recommended:  $R_{PG1} = 100k\Omega$ ,  $R_{PG2} = 0\Omega$ ,  $C_{PG} = 1\mu F$ .

Figure 3. Adding Delay to the Power Good Output Pin

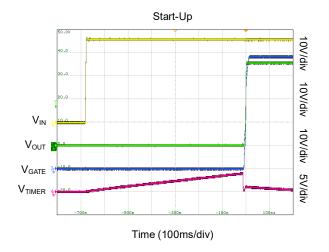

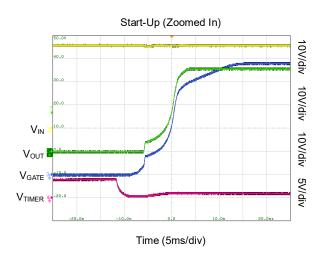

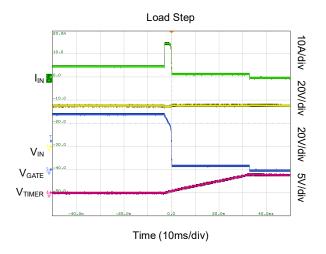

The SGM25701A has a power-up sequence that can be divided into 3 distinct parts: insertion time, inrush limit and normal operation. Once in normal operation, the TIMER and GATE pins depend on whether the output has a fault condition.

### **Power-Up Sequence**

The SGM25701A has an input voltage range of 9V to 70V, and the transient input can reach 80V. Please refer to Figure 4 for details of this section. When the input voltage begins to increase, a strong pull-down 85mA current source inside the GATE pin prevents the Miller capacitance of the MOSFET from being charged. Furthermore, the TIMER pin is pulled low until the V<sub>IN</sub> reaches the POR<sub>IT</sub> threshold. At this time, between insertions, the C<sub>TIMER</sub> begins to be charged by the internal  $5\mu A$  current source when the  $M_1$  is still turned off by the internal 2.1mA current source without being affected by  $V_{\text{IN}}.$   $V_{\text{IN}}$  is allowed to stabilize gradually during the insertion time. When the voltage of the TIMER pin reaches 4V, the insertion time is over, and the charge on the C<sub>TIMER</sub> is quickly discharged by the internal 1.6mA current source. After the insertion time, when the  $V_{\text{IN}}$  reaches the power-on reset threshold (POR<sub>EN</sub>), the control circuit is enabled. If the input voltage exceeds the under-voltage lockout threshold, the 16µA current source inside the GATE pin starts to work and turns on M<sub>1</sub>, and the V<sub>GS</sub> of M<sub>1</sub> is limited to 12.7V by the internal Zener diode. When the OUT pin voltage increases, the SGM25701A detects the drain current and power dissipation of the M<sub>1</sub>, and enables the current limit circuit and power-limiting circuit. During the inrush limit period, the C<sub>TIMER</sub> is charged by the internal 95µA current source at the TIMER pin. If the power dissipation on M<sub>1</sub> and the input current decrease below their respective limit thresholds before the C<sub>TIMER</sub> voltage value reaches 4V, the 95µA current source is turned off and the charge of the C<sub>TIMER</sub> is discharged by the internal 2.4µA current sink.

When the OUT pin voltage increases to within 1.4V of the input voltage, the current limit interval is completed and the PG pin is pulled high. If the voltage of TIMER pin reaches 4V before the current limit or power-limiting ceases, the TIMER pin will be enabled and the GATE pin of  $M_1$  will be pulled low by the internal 2.1mA current source and shut down until the next power-up sequence starts or the restart sequence ends.

# VIN UVLO POR<sub>IT</sub> 0V 4V TIMER 0.3V 0V GATE 85mA Pull-Down Current Limit Load Current OUT 1.4V

# **DETAILED DESCRIPTION (continued)**

PG

Figure 4. Power-Up Sequence (Power-Limiting Only)

Insertion Time

### **Gate Control**

An internal charge pump can provide an internal bias higher than the output voltage to boost the gate of the N-MOSFET. The  $V_{GS}$  of  $M_1$  is limited to 12.7V by an internal Zener diode. During normal operation (see Figure 4), the GATE pin is charged to approximately 12.7V above the OUT pin by the internal 16µA current source. If the maximum gate-source voltage of the external N-MOSFET is less than 12.7V, a low voltage Zener diode with a forward current of at least 100mA must be added outside the device. A strong pull-down current source of 85mA for the initial operation of the device can prevent  $M_1$  from being mis-turned through the drain-to-gate capacitance.

When the system is initially powered up, the GATE pin is pulled low by an internal 85mA current source to prevent misleading MOSFET on through the drain-gate capacitance. The GATE pin is pulled low by a 2.1mA current source in insertion time (see Figure 4) while the MOSFET is always turned off. During the following inrush limit time (see Figure 4), the voltage of the GATE pin is limited to the programmed current or power-limiting level when the TIMER pin is charged by the 95µA current source. If SGM25701A exits current limit or power-limiting state before the TIMER pin is charged to 4V, the circuit will enter normal operating

mode and the TIMER will be discharged by the internal 2.4µA current. When the TIMER pin is charged to 4V, and the device is still in current limit or power-limiting state, the load cannot be started properly. The GATE will continue to be pulled down by the 2.1mA current source and enter the restart sequence. The GATE pin is also pulled down by the 2.1mA current source when the supply voltage is lower than EN/UVLO threshold voltage or above OVLO threshold voltage. Please refer to Figure 5 for the detailed structure.

Figure 5. Gate Control

# **DEVICE FUNCTIONAL MODELS (continued)**

### **Shutdown Control**

In addition, the remote control device can be turned off and safely started by connecting an open collector device or an open-drain device on the EN/UVLO pin, as shown in the Figure 6.

Figure 6. Shutdown Control

### **Fault Timer and Restart**

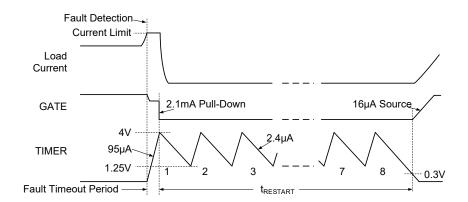

When the current limit or power-limiting value is reached during the startup process, the GATE pin voltage is limited to regulate the load current and power dissipation. Then a 95µA current source will charge the TIMER, please refer to the Figure 7. If the current or power-limiting situation fades before the TIMER pin is charged to 4V, the device enters normal operation mode. Otherwise, the GATE pin of M<sub>1</sub> will be continuously pulled low by the 2.1mA current source. The TIMER pin is discharged by the 2.4µA current sink and enters a restart sequence of repeated charge and discharge. After seven failure timeout cycles, the restart sequence ends when the voltage of the eighth descent ramp of the TIMER pin drops below 0.3V, and the 16µA current source of the GATE pin turns on M<sub>1</sub>. If the fault persists, the restart sequence will be repeated.

Figure 7. Restart Sequence

### APPLICATION INFORMATION

The SGM25701A is a hot swap controller used for fault case protections and inrush current management. Consider startup, hot-short and start-into-short scenarios in detail before proceeding with applications.

In addition, for the safety of the equipment and systems, please carefully review the SOA (safe operating area) section of the choice of MOSFET. It is recommended to use the SGM25701A design calculator provided in the datasheet. The following design cases and calculation formulas can be used for reference.

### **Typical Application**

Figure 8. Typical Application Schematic (36V/11A)

### **Design Requirements**

Table 1 lists the necessary parameters which are needed to know before designing. The power dissipation of the hot swap MOSFET during startup is stored in the output capacitor. Therefore, the  $V_{\text{IN}}$  and  $C_{\text{OUT}}$  value determine the stress of the MOSFET. The selection of sense resistor is determined by the maximum operating load current. Additionally, the maximum operating load current, ambient temperature, and thermal characteristics of the PCB ( $R_{\text{\thetaCA}}$ ), all affect the  $R_{\text{DSON}}$  requirements and the number of power MOSFETs used. The  $R_{\text{\thetaCA}}$  value is extremely sensitive to copper area and PCB layout. Note that the drain is not electrically grounded, so the ground plane does not

help dissipate heat. The following example uses a value of 30°C/W, which is similar to SGM25701A EVB.

The test conditions for hot swap are needed to know before the test. The design must ensure that the MOSFET is safe even if the output is shorted. It is recommended not to carry the load until the MOSFET is successfully started. Loading the MOSFET too early may cause the startup failure.

Figure 9. No Load Current during Turn-On

**Table 1. Design Parameters**

| Parameter                                           | Value               |  |  |  |  |

|-----------------------------------------------------|---------------------|--|--|--|--|

| Input Voltage                                       | 24V to 48V          |  |  |  |  |

| Operating Load Current (MAX)                        | 11A                 |  |  |  |  |

| Lower EN/UVLO Threshold                             | 22V                 |  |  |  |  |

| Upper EN/UVLO Threshold                             | 24V                 |  |  |  |  |

| Lower OVLO Threshold                                | 48V                 |  |  |  |  |

| Upper OVLO Threshold                                | 50V                 |  |  |  |  |

| Load Capacitance (MAX)                              | 1000µF              |  |  |  |  |

| Ambient Temperature (MAX)                           | 85°C                |  |  |  |  |

| MOSFET R <sub>θCA</sub><br>(Function of Layout)     | 30°C/W              |  |  |  |  |

| Pass Hot-Short on Output.  Pass A Start into Short. |                     |  |  |  |  |

|                                                     |                     |  |  |  |  |

| A Hot Board cannot                                  | be Plugged Back in. |  |  |  |  |

### **Detailed Design Procedure**

### Select R<sub>SENSE</sub> and CL Setting

The device measures real-time current by monitoring the voltage across the  $R_{\text{SENSE}}.$  When the voltage across  $R_{\text{SENSE}}$  exceeds 55mV, the GATE pin is pulled low. Note the power and size of the  $R_{\text{SENSE}}$  and the selected over-current value. Use Equation 1 to calculate the appropriate sense resistance.

$$R_{\text{SENSE}} = \frac{V_{\text{CL}}}{I_{\text{LIM}}} = \frac{55mV}{11A} = 5m\Omega$$

(1)

### Selecting the Hot Swap MOSFET(s)

Selecting the right MOSFET for hot swap applications is critical. Please ensure that the device meets the requirements as below:

- The V<sub>DS</sub> of the MOSFET can withstand the maximum input voltage of the system along with the ringing introduced during transients.

- The SOA of the MOSFET can meet the following scenarios: startup, hot-short, and start-into-short.

- Try to keep the R<sub>DSON</sub> as small as possible to avoid excessive temperature rise. It recommends a steady state of less than +125°C for MOSFETs.

- The maximum continuous current must be greater than the maximum load current, and the drain pulse current must be greater than the threshold current of the circuit breaker.

For the design, the KNB2710A is selected. The maximum steady state case temperature can be calculated as Equation 2 after selecting the MOSFET.

$$T_{C,MAX} = T_{A,MAX} + R_{\theta CA} \times I_{LOAD,MAX}^2 \times R_{DSON,MAX}(T_J)$$

(2)

Note that  $R_{DSON}$  is a strong function of junction temperature. According to the KNB datasheet,  $R_{DSON}$  is about 1.4× at 85°C. Equation 3 is used to calculate  $T_{C.MAX}$ .

$$T_{C.MAX} = 85^{\circ}C + 30^{\circ}C/W \times (11A)^{2} \times (1.4 \times 4.5 \text{m}\Omega) = 107.87^{\circ}C$$

(3)

If the calculated temperature value of a single MOSFET is too high, the power dissipation can be dispersed by increasing the number of MOSFETs.

When using multiple MOSFETs in parallel, please use Equation 4 as below.

$$T_{C,MAX} = T_{A,MAX} + R_{\theta CA} \times (\frac{I_{LOAD,MAX}}{\# \text{ of MOSFETs}})^2 \times R_{DSON} (T_J)$$

(4)

### **Select Power-Limiting**

It is usually best to use power-limiting to reduce stress on the MOSFET. However, when the power-limiting is set very low and the current flowing through the MOSFET is controlled, the voltage across the  $R_{\text{SENSE}}$  will very low. Equation 5 can be used to calculate the voltage across the  $R_{\text{SENSE}}$ .

$$V_{\text{SENSE}} = \frac{P_{\text{LIM}} \times R_{\text{SENSE}}}{V_{\text{DS}}}$$

(5)

$V_{\text{SENSE}}$  below 5mV is not recommended to avoid low power-limiting accuracy. In this application, it can use Equation 6 to calculate the corresponding power-limiting value.

$$P_{\text{LIM,MIN}} = \frac{V_{\text{SENSE,MIN}} \times V_{\text{IN,MAX}}}{R_{\text{SENSE}}} = \frac{5mV \times 48V}{5m\Omega} = 48W \tag{6}$$

It can further calculate the corresponding minimum  $R_{\text{PWR}}$  at this power-limiting according to Equation 7.

$$R_{PWR} = 1.30 \times 10^5 \times R_{SENSE} \times (P_{LIM} - 1.18 \text{mV} \times \frac{V_{DS}}{R_{SENSE}})$$

(7)

Note that the minimum  $R_{PWR}$  corresponds to the  $V_{DS}$  =  $V_{IN,MAX}$ . It can be calculated by Equation 8.

$$R_{PWR} = 1.30 \times 10^{5} \times 5 m\Omega \times (48W - 1.18mV \times \frac{48V}{5m\Omega}) = 24k\Omega \quad \mbox{(8)}$$

For a more accurate power-limiting, select a power-limiting value lager than 48W. It can use a slightly larger resistance of  $33k\Omega$ , which sets a power-limiting of 62.1W.

### **Set Fault Timer**

Please ensure that the fault timer has enough time to ensure that it does not time out in the power-limiting or current limit operation during this period. If the device is running in current limit state from the start, the maximum startup time can be calculated by Equation 9.

$$t_{\text{START,MAX}} = \frac{C_{\text{OUT}} \times V_{\text{IN,MAX}}}{I_{\text{I,IM}}}$$

(9)

For this example, the device enters a conversion from power-limiting to current limit during startup. The startup time can be estimated according to Equation 10.

$$t_{\text{START}} = \frac{C_{\text{OUT}}}{2} \times \left[ \frac{V_{\text{IN,MAX}}^2}{P_{\text{LIM}}} + \frac{P_{\text{LIM}}}{I_{\text{LIM}}^2} \right]$$

$$= \frac{1000 \mu F}{2} \times \left[ \frac{(48 V)^2}{62.1 W} + \frac{62.1 W}{(11 A)^2} \right]$$

$$= 18.81 mc$$

Please note that the time calculated above is the ideal constant power conversion to constant current startup. Because power-limiting is a function of  $V_{DS}$ , the actual startup time will be longer than calculated time. In addition, it needs to consider errors introduced by some device specifications, such as  $C_{TIMER}$  and constant current source, power-limiting value, etc., and also needs an additional 50% time margin to ensure that the startup time does not time out. Therefore, use Equation 11 to determine the value of the fault timer capacitance.

$$C_{\text{TIMER}} = \frac{t_{\text{FLT}} \times I_{\text{TIMER(TYP)}}}{V_{\text{TIMER(TYP)}}} \times 1.5 = \frac{18.81 \text{ms} \times 95 \mu A}{4 \text{V}} \times 1.5 = 670 \text{nF} \quad \text{(11)}$$

The capacitor of 680nF with a slightly larger capacitance can be selected to calculate the programming time of the fault timer according to Equation 12.

$$t_{\text{FLT}} = \frac{C_{\text{TIMER}} \times V_{\text{TIMER,TYP}}}{I_{\text{TIMER,TYP}}} = \frac{680 \text{nF} \times 4V}{95 \mu \text{A}} = 28.6 \text{ms}$$

(12)

If the system has not started successfully beyond this time, the SGM25701A will shut down the KNB2710A MOSFET.

### **Check MOSFET SOA**

Once the power-limiting and timer capacitance values are selected, it is important to confirm the SOA characteristics of the MOSFET. SOA characteristics describe how long a MOSFET can safely operate at a certain current under a  $V_{\rm DS}$ . In the worst case, the MOSFET operates in a power-limiting state all the time. The current flowing value is  $P_{\rm LIM}/V_{\rm IN,MAX}$  and the duration is  $t_{\rm FLT}$ . Taking this application as an example, it must ensure that the MOSFET may handle 1A at 48V for 28.9ms. Based on the SOA of the KNB2710A, it can handle 48V, 19A for 1ms and it can handle 48V, 5A for 100ms. Refer to Equations 13 to 15 to calculate the corresponding safe working period.

$$I_{SOA}(t) = a \times t^{m} \tag{13}$$

$$m = \frac{\ln \frac{I_{SOA}(t_1)}{I_{SOA}(t_2)}}{\ln (\frac{t_1}{t_2})} = \frac{\ln (\frac{19A}{5A})}{\ln (\frac{1ms}{100ms})} = -0.29$$

(14)

$$a = \frac{I_{SOA}(t_1)}{t_1^m} = \frac{19A}{(1ms)^{0.29}} = 19A \times (1ms)^{0.29}$$

(15)

$$I_{SOA}(28.9 \text{ms}) = 19 \text{A} \times (1 \text{ms})^{0.29} \times (28.9 \text{ms})^{-0.29}$$

(16)

= 7.163A

Note that the current calculated above is an ideal calculation considering the MOSFET case temperature to be +25 °C. A certain ambient temperature and thermal increase during operation can make the MOSFET more possible to hot-short. It can use Equation 17 to calculate the approximate current.

$$I_{SOA}(28.9\text{ms}, T_{C,MAX}) = I_{SOA}(28.9\text{ms}, 25^{\circ}\text{C}) \times \frac{T_{J,ABSMAX} - T_{C,MAX}}{I_{J,ABSMAX} - 25^{\circ}\text{C}}$$

$$= 7.163\text{A} \times \frac{175^{\circ}\text{C} - 107.87^{\circ}\text{C}}{175^{\circ}\text{C} - 25^{\circ}\text{C}}$$

$$= 3.21\text{A}$$

(17)

Based on this calculation, the MOSFET can handle 3.21A, 48V for 28.9ms at elevated case temperature. This value is larger than the 1.29A required for power-limiting startup, indicating that there is little risk of hot-short to the MOSFET during startup. It is recommended that the selected MOSFET may calculate an equivalent current value that exceeds the required value by 1.3× to provide sufficient margin.

Set Under-Voltage and Over-Voltage Threshold By setting the EN/UVLO and OVLO thresholds, SGM25701A turns on the main power MOSFET  $M_1$  when the input voltage is within the normal operating range. Conversely,  $M_1$  switches off, stopping the output current.

The four thresholds can be accurately calculated using the configuration shown in Figure 10.

Figure 10. Programming the Four Thresholds

Use the following Equations 18 and 19 to calculate the upper and lower threshold of EN/UVLO.

$$R_{1} = \frac{V_{UVH} - V_{UVL}}{19\mu A} = \frac{V_{UV(HYS)}}{19\mu A}$$

(18)

$$R_2 = \frac{2.5V \times R_1}{(V_{1,V_1} - 2.5V)} \tag{19}$$

Use the following Equations 20 and 21 to calculate the upper and lower threshold of OVLO.

$$R_3 = \frac{V_{OVH} - V_{OVL}}{19\mu A} = \frac{V_{OV(HYS)}}{19\mu A}$$

(20)

$$R_4 = \frac{2.5V \times R_3}{(V_{OVH} - 2.5V)}$$

(21)

$V_{UVH}$  = 24V,  $V_{UVL}$  = 22V,  $V_{OVH}$  = 50V, and  $V_{OVL}$  = 48V. Therefore,  $V_{UV(HYS)}$  = 2V and  $V_{OV(HYS)}$  = 2V.

The resistor values are:  $R_1$  = 100k $\Omega$ ,  $R_2$  = 13k $\Omega$ ,  $R_3$  = 100k $\Omega$ , and  $R_4$  = 5.6k $\Omega$ .

Under the condition that  $R_1$  -  $R_4$  is calculated, the threshold voltage and hysteresis voltage are calculated using Equation 22 to Equation 27.

$$V_{UVH} = 2.5V + [R_1 \times (\frac{2.5V}{R_2} + 19\mu A)]$$

(22)

$$V_{UVL} = \frac{2.5V \times (R_1 + R_2)}{R_2}$$

(23)

$$V_{UV(HYS)} = R_1 \times 19\mu A \tag{24}$$

$$V_{\text{OVH}} = \frac{2.5V \times (R_3 + R_4)}{R_4} \tag{25}$$

$$V_{\text{OVL}} = 2.5V + [R_3 \times (\frac{2.5V}{R_4} - 19\mu\text{A})]$$

(26)

$$V_{OV(HYS)} = R_3 \times 19\mu A \tag{27}$$

### **Input and Output Protection**

The SGM25701A needs to connect voltage clamping devices on the input side under hot plug conditions. It is necessary to select an appropriate TVS as shown in Figure 1. When the hot plug circuit is suddenly pulled out of the socket under the load condition, TVS needs to suppress the voltage surge at this time. The principle of TVS selection is that there is a small leakage current at  $V_{\text{IN(MAX)}}$ , and it is clamped below the set voltage when the input surge voltage is large.

### **Component Values**

Table 2 provides the selected device values under the condition of 36V/11A, and the application curve is also based on these device values.

**Table 2. Component Values**

| Component          | Value        |

|--------------------|--------------|

| R <sub>SENSE</sub> | 5mΩ          |

| R₁                 | 100kΩ        |

| $R_2$              | 13kΩ         |

| R <sub>3</sub>     | 100kΩ        |

| $R_4$              | 5.6kΩ        |

| $R_{PWR}$          | 33kΩ         |

| $M_1$              | KNB2710A     |

| $Z_1$              | SMBJ70A-13-F |

| $D_1$              | MBRS3100T3G  |

| $C_{TIMER}$        | 680nF        |

| $C_OUT$            | 1000µF       |

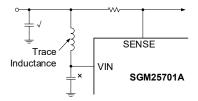

### **Power Supply Recommendations**

Generally speaking, SGM25701A can provide stable power supply with reliable performance. However, when other card slots on the backplane are inserted, the high frequency dynamics on the backplane will appear. When this happens in the system, it is recommended to place a capacitor of  $1\mu F$  on the drain of MOSFET. This will reduce the common mode voltage between VIN and SENSE pins, which needs to be suppressed to prevent over-current shutdown.

### **PC Board Guidelines**

SGM25701A should observe the following principles when laying PCB:

SGM25701A needs to be placed near the input connector to reduce the lead inductance from the connector to the power MOSFET.

The bypass capacitor of  $V_{\text{IN}}$  should be placed carefully. When MOSFET is turned off due to short-circuit, the input terminal has a very large dV/dt. When the capacitor is placed close to the VIN pin, the LC filter is formed due to the long routing from SENSE to VIN. At this time, a large voltage difference may be formed between VIN and SENSE. To prevent this, place the capacitor on the  $R_{\text{SENSE}}$  terminal instead of VIN terminal.

Figure 11. Layout Trace Inductance

- The R<sub>SENSE</sub> needs to be close to the controller chip and use the Kelvin connection.

- The current path and return path from the input to the load side should be parallel and close to each other to reduce the loop inductance.

- GND of components around SGM25701A can be connected with each other and connected with GND pin of SGM25701A. Then connect GND to the system ground uniformly. Do not separately connect the ground of the devices around the chip to the ground of the system with high current.

- PCB layout provides good heat dissipation conditions for MOSFET M<sub>1</sub> to reduce the junction temperature when it is turned on and off.

### **System Considerations**

As shown in Figure 12, the normal operation of SGM25701A requires a capacitor on the backplane side. The capacitor with live backplane needs to absorb the input surge voltage generated when the controller cuts off the load. If there is no capacitance, TVS needs to be placed in the input measurement to prevent large voltage generated during voltage transient from exceeding the maximum rated value of VIN pin.

When the output of SGM25701A is inductive load, it is necessary to reverse parallel diode on the load side. When the load is cut off, a reverse path is provided for the current of the inductive load to prevent negative voltage from damaging the device.

Figure 12. Output Diode Required for Inductive Loads

# SGM25701A

# Positive High-Voltage Hot Swap and Inrush **Current Controller with Power-Limiting**

# **REVISION HISTORY**

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

Changes from Original (DECEMBER 2022) to REV.A

Page

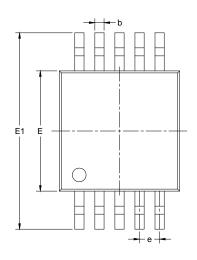

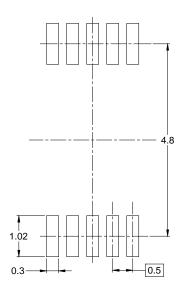

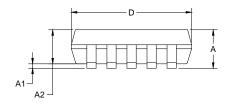

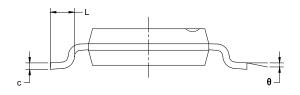

# **PACKAGE OUTLINE DIMENSIONS** MSOP-10

### RECOMMENDED LAND PATTERN (Unit: mm)

| Symbol | Dimer<br>In Milli | nsions<br>meters | Dimen<br>In Inc |       |

|--------|-------------------|------------------|-----------------|-------|

|        | MIN               | MAX              | MIN             | MAX   |

| А      | 0.820             | 1.100            | 0.032           | 0.043 |

| A1     | 0.020             | 0.150            | 0.001           | 0.006 |

| A2     | 0.750             | 0.950            | 0.030           | 0.037 |

| b      | 0.180             | 0.280            | 0.007           | 0.011 |

| С      | 0.090             | 0.230            | 0.004           | 0.009 |

| D      | 2.900             | 3.100            | 0.114           | 0.122 |

| E      | 2.900             | 3.100            | 0.114           | 0.122 |

| E1     | 4.750             | 5.050            | 0.187           | 0.199 |

| е      | 0.500 BSC         |                  | 0.020           | BSC   |

| L      | 0.400             | 0.800            | 0.016           | 0.031 |

| θ      | 0°                | 6°               | 0°              | 6°    |

### NOTES:

- Body dimensions do not include mode flash or protrusion.

This drawing is subject to change without notice.

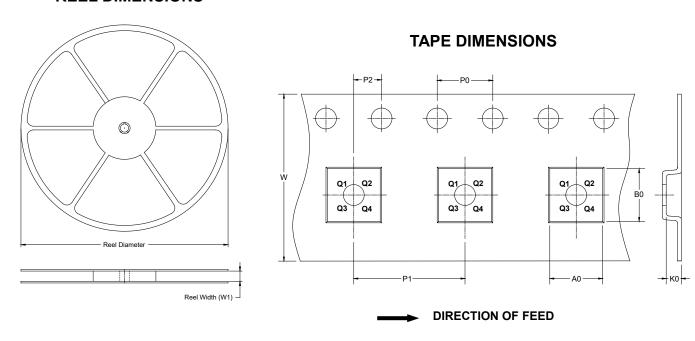

# TAPE AND REEL INFORMATION

### **REEL DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

### **KEY PARAMETER LIST OF TAPE AND REEL**

| Package Type | Reel<br>Diameter | Reel Width<br>W1<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P0<br>(mm) | P1<br>(mm) | P2<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|------------------|--------------------------|------------|------------|------------|------------|------------|------------|-----------|------------------|

| MSOP-10      | 13"              | 12.4                     | 5.20       | 3.30       | 1.50       | 4.0        | 8.0        | 2.0        | 12.0      | Q1               |

### **CARTON BOX DIMENSIONS**

NOTE: The picture is only for reference. Please make the object as the standard.

### **KEY PARAMETER LIST OF CARTON BOX**

| Reel Type | Length<br>(mm) | Width<br>(mm) | Height<br>(mm) | Pizza/Carton |

|-----------|----------------|---------------|----------------|--------------|

| 13"       | 386            | 280           | 370            | 5            |