## **GENERAL DESCRIPTION**

The ft2725 is a highly efficient 2X10W stereo Class-D audio power amplifier with automatic level control (ALC) and dynamic range compression (DRC). It operates with a wide range of supply voltages from 3.7V to 9V. When powered with 9V supply voltage, the ft2725 is capable of delivering 10W per channel into a pair of  $4\Omega$  speakers in a bridge-tied-load (BTL) configuration, or 15W into a single  $3\Omega$  speaker in parallel BTL (PBTL) configuration, with 10% THD+N.

The ft2725 features ALC with an adjustable threshold for dynamic range control (DRC). The ALC constantly monitors and safeguards the audio outputs against a user-defined threshold voltage, preventing output clipping distortion, excessive power dissipation, or hazardous speaker over-load. Once an over-level condition is detected, the ALC lowers the voltage gain of the audio amplifiers proportionally to eliminate output clipping while maintaining a maximally-allowed dynamic range of the audio outputs. The threshold voltage of the ALC can be set at either the supply voltage or an externally defined value.

As a filterless Class-D audio amplifier, the ft2725 features high efficiency (up to 89%), high PSRR (76dB at 1kHz), and low EMI emissions, which reduce design and manufacturing complexities, lower system cost and PCB space.

In ft2725, comprehensive protection features against various operating faults ensure its safe and reliable operation.

## FEATURES

- Wide supply voltage range from 3.7V to 9V

- Automatic level control with adjustable threshold

- High efficiency up to 89%

- Maximum output power in Non-ALC mode (VDD=9V, VALC≥0.8\*GVDD, 10% THD+N)

6W/Ch (8Ω load)

10W/Ch (4Ω load)

15W (3Ω load in PBTL configuration)

- ALC output power in ALC Mode (VDD=9V, VALC=0V, 0.3% THD+N)

4.5W/Ch (8Ω load)

8.5W/Ch (4Ω load)

11.5W (3Ω load in PBTL configuration)

- Low THD+N: 0.06%

(VDD=9V, f=1kHz, 4Ω load, Po=5W)

- High PSRR: 76dB @ 1kHz

- Wide ALC dynamic range: 10dB

- Maximum voltage gain: 32.4dB

- Volume fade-in and fade-out

- Optional spread-spectrum (SS) audio outputs to suppress EMI

- Optional mono mode for PBTL configuration with low-impedance audio speakers

- Auto-recovering over-current & short-circuit protection

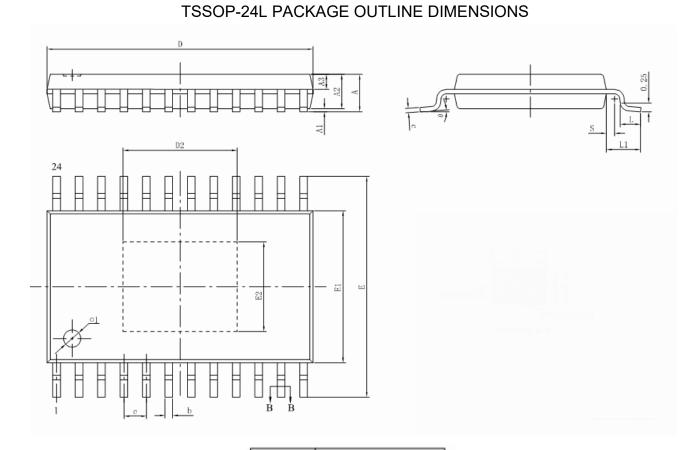

- Available in TSSOP-24L package

## APPLICATIONS

- Blue Tooth Speakers

- Performance Audio Speakers

- TV/Monitors

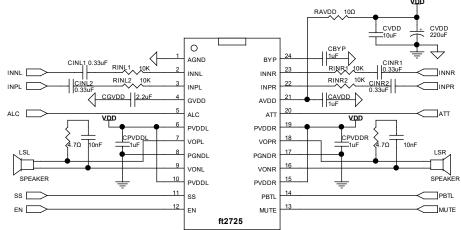

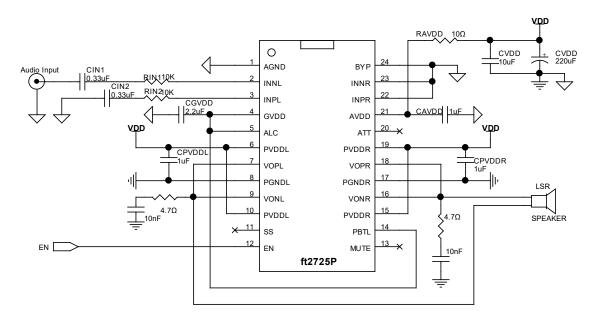

#### Figure 1: Typical Audio Power Amplifier Application Circuit

## APPLICATION CIRCUIT

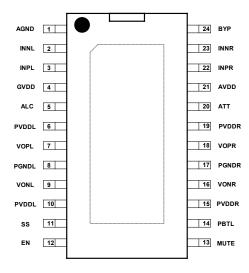

## PIN CONFIGURATION AND DESCRIPTION

#### ft2725P (TOP VIEW)

| NAME  | PIN #  | TYPE | DESCRIPTION                                                                                                                                                                 |

|-------|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AGND  | 1      | G    | Analog ground. Connect to the system ground GND.                                                                                                                            |

| INNL  | 2      | AI   | Left-channel inverting audio input terminal.                                                                                                                                |

| INPL  | 3      | AI   | Left-channel non-inverting audio input terminal.                                                                                                                            |

| GVDD  | 4      | AO   | Internally generated voltage supply. Connect to a 2.2µF capacitor for decoupling.                                                                                           |

| ALC   | 5      | AI   | ALC and Dynamic Range Control. Connect to a 0.1µF capacitor for decoupling.                                                                                                 |

| PVDDL | 6, 10  | Р    | Power supply for the left-channel power amplifier's output stage. Connect directly to the system power supply VDD and add a $1\mu$ F capacitor for decoupling.              |

| VOPL  | 7      | AO   | Left-channel non-inverting audio output terminal.                                                                                                                           |

| PGNDL | 8      | G    | Power ground for the output stage of the left-channel power amplifier. Connect to the system ground GND.                                                                    |

| VONL  | 9      | AO   | Left-channel inverting audio output terminal.                                                                                                                               |

| SS    | 11     | DI   | Spread-Spectrum Select (Active High) with a $300k\Omega$ internal pulldown resister.                                                                                        |

| EN    | 12     | DI   | Chip Enable (Active High) with a $300k\Omega$ internal pulldown resister to ground.                                                                                         |

| MUTE  | 13     | DI   | <b>Mute Control</b> (Active High) with a 300k $\Omega$ internal pulldown resistor to ground.                                                                                |

| PBTL  | 14     | DI   | <b>PBTL Select</b> (Active High) with a $300k\Omega$ internal pulldown resistor to ground.                                                                                  |

| PVDDR | 15, 19 | Р    | Power supply for the right-channel power amplifier's output stage. Connect directly to the system power supply VDD and add a $1\mu$ F capacitor for decoupling.             |

| VONR  | 16     | AO   | Right-channel inverting audio output terminal.                                                                                                                              |

| PGNDR | 17     | G    | Power ground for the output stage of the right-channel power amplifier. Connect to the system ground GND.                                                                   |

| VOPR  | 18     | AO   | Right-channel non-inverting audio output terminal.                                                                                                                          |

| ATT   | 20     | DI   | ALC Attack Time Select with a $300k\Omega$ internal pulldown resistor to ground.                                                                                            |

| AVDD  | 21     | Р    | Power supply for internal analog circuitry. Connect to the system power supply through a small decoupling resistor $(10\Omega)$ . Also, add a 1µF capacitor for decoupling. |

| INPR  | 22     | AI   | Right-channel non-inverting audio input terminal.                                                                                                                           |

| INNR  | 23     | AI   | Right-channel inverting audio input terminal.                                                                                                                               |

| BYP   | 24     | AO   | Common-mode bias for audio inputs. Connect to a 1µF capacitor for decoupling.                                                                                               |

## **ORDERING INFORMATION**

| PART NUMBER | TEMPERATURE RANGE | PACKING OPTION      | PACKAGE   |

|-------------|-------------------|---------------------|-----------|

| ft2725P     | -40°C to +85°C    | Tape and Reel, 4000 | TSSOP-24L |

## **REVISION HISTORY**

#### Initial Release 1.0 (Jan., 2015)

#### Changed from Initial 1.0 (January, 2015) to Revision 1.1 (January, 2017)

- 1. Deleted the package option of QFN5x5-28L.

- 2. Changed input capacitors ( $C_{INL1}$ ,  $C_{INL2}$ ,  $C_{INR1}$ , and  $C_{INR2}$ ) from 1.0µF to 0.33µF in Typical Application Circuits.

- 3. Revised Table 4, Typical Voltage Gain Settings & Input Resistor Values for Various Input Levels.

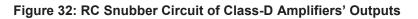

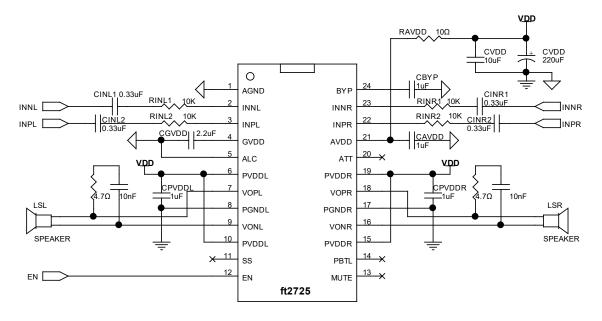

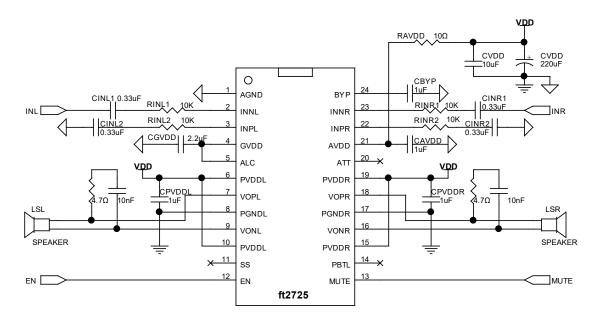

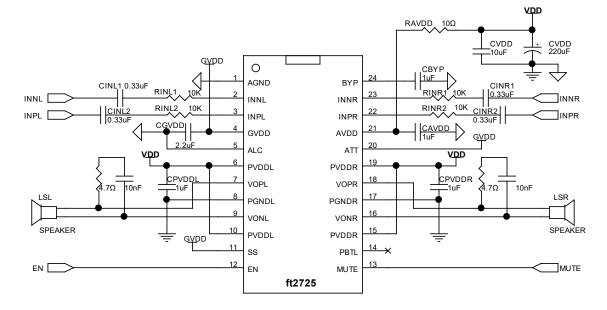

- 4. Added snubber circuits across audio outputs VOPL/R and VONL/R in Figure 1, 33, 34, 35, and 36.

#### Changed from Revision 1.1 (June, 2017) to Revision 1.2 (November, 2017)

- 1. Changed  $C_{PVDDL/R}$  from 10µF to 1µF.

- 2. Added  $C_{VDD}$  of  $10\mu F//220\mu F$  onto the system power supply.

- 3. Updated Figure 1, Typical Application Circuit, on Page 1.

- 4. Updated Figure 33 and 34 on Page 24; Figure 35 and 36 on Page 25.

#### Changed from Revision 1.2 (November, 2017) to Revision 1.3 (September, 2022)

1. Added PACKING OPTION.

# ABSOLUTE MAXIMUM RATINGS (Note 1)

| PARAMETER                                           | VALUE             |

|-----------------------------------------------------|-------------------|

| Supply voltage, AVDD, PVDDL/R                       | -0.3V to 9.2V     |

| All other Pins                                      | -0.3V to VDD+0.3V |

| Storage Temperature                                 | -65°C to +150°C   |

| ESD Ratings-Human Body Model (HBM)                  | 2000V             |

| Junction Temperature                                | 150°C             |

| Maximum Soldering Temperature (@10 second duration) | 260°C             |

Note 1: Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may damage the device or affect device reliability.

# POWER DISSIPATION RATINGS (Note 2, 3)

| PACKAGE   | TA <u>&lt;</u> +25°C | TA = +70°C | TA = +85°C | ΘJA    |

|-----------|----------------------|------------|------------|--------|

| TSSOP-24L | 3.1W                 | 2.0W       | 1.7W       | 40°C/W |

Note 2: The thermal pad of the package must be directly soldered onto a grounded metal island (as a thermal sink) on the system board. Note 3: The power dissipation ratings are for a two-side, two-plane printed circuit board (PCB).

## **RECOMMENDED OPERATING CONDITIONS**

| Parameter                                      | Conditions    | MIN | TYP | MAX | UNIT |

|------------------------------------------------|---------------|-----|-----|-----|------|

| Supply Voltage, VDD (Note 4)                   | AVDD, PVDDL/R | 3.7 |     | 9.0 | V    |

| Operating Free-Air Temperature, T <sub>A</sub> |               | -40 |     | 85  | °C   |

| Minimum Load Resistance, RL                    |               | 3.0 |     |     | Ω    |

Note 4: The peak supply voltage including its tolerance over various operating conditions must not exceed its absolute-maximum-rated value (9.2v). Exposure to absolute-maximum-rated supply voltage may damage the device or affect device reliability permantly. For applications where the system supply voltage might momentarily exceed the rating, it is strongly suggested to add an external Schottky diode in series from the system power supply to ensure the peak suppy voltage not exceeding the absolute maximum rating.

## **IMPORTANT APPLICATION NOTES**

- 1. For best noise performance, it is recommended to use differential inputs from the audio source for ft2725. In a single-ended input application, the unused input of ft2725 should be AC-grounded at the audio source. The impedance seen at the two differential inputs should be the same.

- 2. The ft2725 requires adequate power supply decoupling to ensure its optimum operation and performance in output power, efficiency, distortion, and EMI emissions. Place respective decoupling capacitors individually as close as possible to the device's AVDD, GVDD, BYP, and PVDDL/R pins.

- 3. The ft2725 is a high performance, high power, stereo Class-D audio amplifier with an exposed thermal pad on the underside of the device. The thermal pad should be directly soldered onto a ground plane, where AGND and PGNDL/R pins are directly connected, as a thermal sink for proper power dissipation. Failure to do so may result in the device prematurely going into thermal overload protection.

- 4. It is strongly recommended to employ power (PVDD) and ground (GND) planes for ft2725 on the system board. Also, place a small decoupling resistor (10Ω) between AVDD and PVDD to prevent high frequency Class-D transient spikes from interfering with the on-chip linear amplifiers.

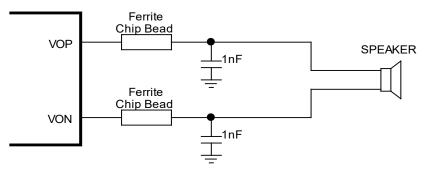

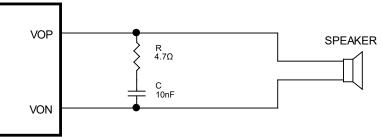

- 5. Use a simple ferrite bead filter for further EMI suppression, as shown in Figure 31. Choose a ferrite bead with a rated current no less than 3A or greater for applications with a load resistance less than 4Ω. Also, place respective ferrite beard filters as individually close to VOPL/R and VONL/R pins as possible

- 6. To enhance long-term reliability, it is strongly recommended to add an RC snubber circuit, as shown in Figure 32, between the two output pins of each individual channel, VOPL/R and VONL/R, to prevent the device from accelerated deterioration or abrupt destruction due to excessive inductive flybacks that are induced on fast output switching or by an over-current or short-circuit condition.

- 7. Do not short audio outputs (VOPL/R and VONL/R) directly to ground (AGND, PGNDL/R) or the supply voltage (AVDD, PVDDL/R) as this might damage the device permanently, particularly when the supply voltage is higher than 8.4V.

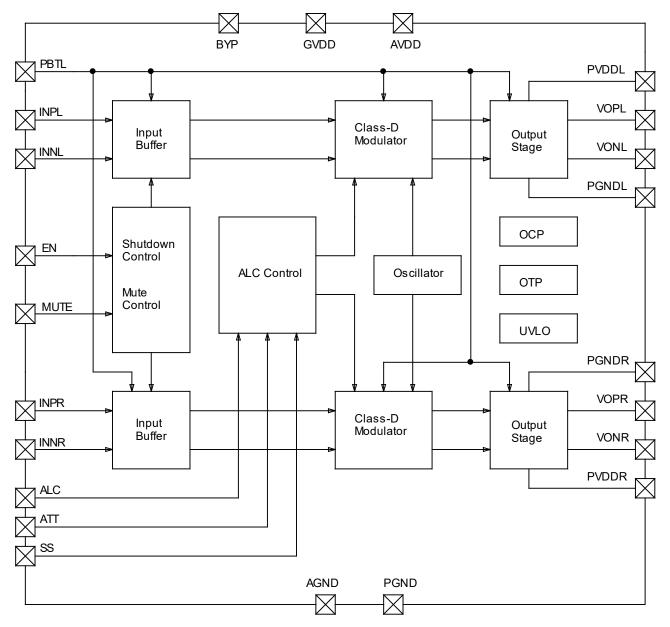

## FUNCTIONAL BLOCK DIAGRAM

Figure 2: Simplified Functional Block Diagram of ft2725

## **ELECTRICAL CHARACTERISTICS**

VDD=9V, CIN=0.33 $\mu$ F, RIN=10k $\Omega$ , MUTE=Low, PBTL=Low, SS=Low, ATT=High, CBYP=1 $\mu$ F, CGVDD=2.2 $\mu$ F, CAVDD=1 $\mu$ F, CPVDDL/R=1 $\mu$ F, f=1kHz, Load=4 $\Omega$ +33 $\mu$ H, TA=25°C, unless otherwise specified.

| SYMBOL                            | PARAMETER                                | CONDITIONS                 | MIN | TYP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | MAX | UNIT |

|-----------------------------------|------------------------------------------|----------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------|

| V <sub>DD</sub>                   | Supply Voltage                           | AVDD, PVDDL/R              | 3.7 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 9.0 | V    |

| VUVLOUP                           | Power-Up Threshold Voltage               | VDD from Low to High       |     | 3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | V    |

| VUVLODN                           | Power-Off Threshold Voltage              | VDD from High to Low       |     | 2.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | V    |

| GVDD                              | Regulator Output Voltage                 | VDD=9V                     | 5.8 | 6.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6.6 | V    |

| BYP                               | Common-Mode Bias Voltage                 | VDD=9V                     | 2.8 | 3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3.4 | V    |

| I <sub>VDD</sub>                  | Supply Quiescent Current                 | VDD=9V, PBTL=Low           | 13  | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 23  | mA   |

| (Normal Mode)                     | Inputs AC-Grounded<br>MUTE=Low, No Load  | VDD=9V, PBTL=High          |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     | mA   |

| I <sub>VDD_MUTE</sub>             | Mute Current<br>Inputs AC-Grounded       | VDD=9V, PBTL=Low           | 4   | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8   | mA   |

| (Mute Mode)                       | Mute=High, No Load                       | VDD=9V, PBTL=High          |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     | mA   |

| I <sub>SD</sub>                   | Shutdown Current                         | EN Low                     |     | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     | μA   |

| VIH                               | Digital High Level Input Voltage         | EN, MUTE, SS, PBTL, ATT    | 1.2 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     | V    |

| VIL                               | Digital Low Level Input Voltage          | EN, MUTE, SS, PBTL, ATT    |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0.4 | V    |

| RDOWN                             | Pulldown Resistor to Ground              | EN, MUTE, SS, PBTL, ATT    |     | 300                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | kΩ   |

| CLASS-D A                         | MPLIFIER                                 |                            |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |      |

|                                   | THD+N=10%,                               | $R_L=4\Omega$              |     | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     | W/Ch |

| P <sub>O, MAX</sub>               | VALC <u>&gt;</u> 0.8*GVDD (Non-ALC Mode) | $R_L=3\Omega$ in Mono Mode |     | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     | W    |

| (VDD=9V)                          | THD+N=1%                                 | $R_L=4\Omega$              |     | 9.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | W/Ch |

|                                   | VALC <u>&gt;</u> 0.8*GVDD (Non-ALC Mode) | $R_L=3\Omega$ in Mono Mode |     | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     | W    |

| P <sub>O, ALC</sub>               | V <sub>IN</sub> =0.36V <sub>RMS</sub>    | $R_L=4\Omega$              |     | 8.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | W/Ch |

| (VDD=9V)                          | VALC <u>&lt;</u> 0.4V (ALC Mode)         | $R_L=3\Omega$ in Mono Mode |     | 11.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |     | W    |

|                                   | V <sub>IN</sub> =0.40V <sub>RMS</sub>    | $R_L=4\Omega$              |     | 8.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | W/Ch |

| P <sub>O, DRC</sub>               | VALC=2.7V (DRC Mode)                     | $R_L=3\Omega$ in Mono Mode |     | $\begin{array}{c c c c c c c c c } 3.2 & & & \\ 2.9 & & & \\ 2.8 & 3.1 & 3.4 & \\ 13 & 18 & 23 & \\ & & & & \\ 13 & 18 & 23 & \\ & & & & \\ 4 & 6 & 8 & \\ & & & & \\ 4 & 6 & 8 & \\ & & & & \\ 10 & & & \\ 10 & & & \\ 1.2 & & & & \\ 10 & & & \\ 1.2 & & & & \\ 10 & & & \\ 1.2 & & & & \\ 10 & & & \\ 1.2 & & & & \\ 10 & & & & \\ 1.2 & & & & \\ 10 & & & & \\ 1.2 & & & & \\ 10 & & & & \\ 1.2 & & & & \\ 10 & & & & \\ 1.2 & & & & \\ 11.5 & & & & \\ 11.5 & & & & \\ 11.5 & & & \\ \end{array}$ | W   |      |

| (VDD=9V)                          | V <sub>IN</sub> =0.40V <sub>RMS</sub>    | $R_L=4\Omega$              |     | 4.9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | W/Ch |

|                                   | VALC=1.8V (DRC Mode)                     | $R_L=3\Omega$ in Mono Mode |     | 6.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | W    |

|                                   | THD+N=10%,                               | $R_L=4\Omega$              |     | 7.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | W/Ch |

| P <sub>O, MAX</sub>               | VALC <u>&gt;</u> 0.8*GVDD (Non-ALC Mode) | $R_L=3\Omega$ in Mono Mode |     | 9.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | W    |

| (VDD=7.2V)                        | THD+N=1%                                 | $R_L=4\Omega$              |     | 5.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | W/Ch |

|                                   | VALC <u>&gt;</u> 0.8*GVDD (Non-ALC Mode) | $R_L=3\Omega$ in Mono Mode |     | 7.7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | W    |

| P <sub>O, ALC</sub>               | V <sub>IN</sub> =0.36V <sub>RMS</sub>    | $R_L=4\Omega$              |     | 5.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | W/Ch |

| (VDD=7.2V)                        | VALC <u>&lt;</u> 0.4V (ALC Mode)         | $R_L=3\Omega$ in Mono Mode |     | 7.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | W    |

|                                   | V <sub>IN</sub> =0.40V <sub>RMS</sub>    | $R_L=4\Omega$              |     | 6.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | W/Ch |

| P <sub>O, DRC</sub>               | VALC=2.16V (DRC Mode)                    | $R_L=3\Omega$ in Mono Mode |     | 8.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | W    |

| (VDD=7.2V)                        | V <sub>IN</sub> =0.40V <sub>RMS</sub>    | $R_L=4\Omega$              |     | 3.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | W/Ch |

|                                   | VALC=1.44V (DRC Mode)                    | $R_L=3\Omega$ in Mono Mode |     | 5.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | W    |

|                                   | THD+N=10%,                               | $R_L=4\Omega$              |     | 5.8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | W/Ch |

| P <sub>O, MAX</sub>               | VALC <u>&gt;</u> 0.8*GVDD (Non-ALC Mode) | $R_L=3\Omega$ in Mono Mode |     | 8.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | W    |

| (VDD=6.5V)                        | THD+N=1%                                 | $R_L=4\Omega$              |     | 4.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | W/Ch |

|                                   | VALC <u>&gt;</u> 0.8*GVDD (Non-ALC Mode) | $R_L=3\Omega$ in Mono Mode |     | 6.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | W    |

| P <sub>O, ALC</sub>               | V <sub>IN</sub> =0.36V <sub>RMS</sub>    | R <sub>L</sub> =4Ω         |     | 4.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | W/Ch |

| (VDD=6.5V)                        | VALC <u>&lt;</u> 0.4V (ALC Mode)         | $R_L=3\Omega$ in Mono Mode |     | 6.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | W    |

|                                   | V <sub>IN</sub> =0.40V <sub>RMS</sub>    | $R_L=4\Omega$              |     | 5.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | W/Ch |

| P <sub>O, DRC</sub><br>(VDD=6.5V) | VALC=1.95V (DRC Mode)                    | $R_L=3\Omega$ in Mono Mode |     | 6.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | W    |

| (0.00-0.00)                       | V <sub>IN</sub> =0.40V <sub>RMS</sub>    | $R_L=4\Omega$              |     | 3.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | W/Ch |

|                                   | VALC=1.3V (DRC Mode)                     | $R_L=3\Omega$ in Mono Mode |     | 4.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |     | W    |

# ELECTRICAL CHARACTERISTICS (Cont'd)

$VDD=9V, CIN=0.33\mu F, RIN=10k\Omega, MUTE=Low, PBTL=Low, SS=Low, ATT=High, CBYP=1\mu F, CGVDD=2.2\mu F, CAVDD=1\mu F, CPVDDL/R=1\mu F, f=1kHz, Load=4\Omega+33\mu H, TA=25^{\circ}C, unless otherwise specified.$

| SYMBOL               | PARAMETER                                                                   | CONDITIONS                                                                                    | MIN      | ΤΥΡ  | MAX     | UNIT              |

|----------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|----------|------|---------|-------------------|

| CLASS-D A            | AMPLIFIER (Cont'd)                                                          |                                                                                               |          |      |         |                   |

|                      | Total Harmonic Distortion+Noise<br>VALC <u>&gt;</u> 0.8*GVDD (Non-ALC Mode) | R <sub>L</sub> =4Ω, Po=5W                                                                     |          | 0.06 |         | %                 |

|                      | Total Harmonic Distortion+Noise                                             | R <sub>L</sub> =4Ω, Po=8.5W                                                                   |          | 0.3  |         | %                 |

|                      | VALC <u>&lt;</u> 0.4V (ALC Mode)<br>V <sub>IN</sub> =0.36V <sub>RMS</sub>   | R <sub>L</sub> =3Ω, Po=11.5W                                                                  |          | 0.4  |         | %                 |

| THD+N                | Total Harmonic Distortion+Noise                                             | R <sub>L</sub> =4Ω, Po=8.8W                                                                   |          | 0.6  |         | %                 |

|                      | VALC=2.7V (DRC Mode)<br>V <sub>IN</sub> =0.40V <sub>RMS</sub>               | R <sub>L</sub> =3Ω, Po=11.5W                                                                  |          | 0.6  |         | %                 |

|                      | Total Harmonic Distortion+Noise                                             | R <sub>L</sub> =4Ω, Po=4.9W                                                                   |          | 0.3  |         | %                 |

|                      | VALC=1.8V (DRC Mode)<br>V <sub>IN</sub> =0.40V <sub>RMS</sub>               | R <sub>L</sub> =3Ω, Po=6.5W                                                                   |          | 0.4  |         | %                 |

| A <sub>V</sub>       | Overall Voltage Gain                                                        | R <sub>IN</sub> =10kΩ                                                                         |          | 28   |         | dB                |

| R <sub>IN</sub>      | Input Resistance                                                            | @ INNL/R, INPL/R                                                                              |          | 15   |         | kΩ                |

| R <sub>OUT-SD</sub>  | Output Resistance in Shutdown                                               | @ VOPL/R, VONL/R, EN=Low                                                                      |          | 2.5  |         | kΩ                |

| V <sub>OS</sub>      | Output Offset Voltage                                                       | No Load                                                                                       |          | ±10  |         | mV                |

| V <sub>N</sub>       | Idle-Channel Noise                                                          | AV=28dB, Inputs AC-Grounded<br>A-weighted                                                     |          | 150  |         | μV <sub>RMS</sub> |

| η                    | Power Efficiency                                                            | Vdd=9V, Po=8W, RL=4Ω                                                                          |          | 89   |         | %                 |

| PSRR                 | Power Supply Rejection Ratio                                                | f=1kHz                                                                                        |          | 76   |         | dB                |

| CMRR                 | Common Mode Rejection Ratio                                                 | f=1kHz                                                                                        |          | 70   |         | dB                |

| SNR                  | Signal-to-Noise Ratio                                                       | Maximum Output ( $6V_{RMS}$ ) with THD+N<1%, R <sub>L</sub> =4 $\Omega$ , AV=20dB, A-weighted |          | 92   |         | dB                |

| Crosstalk            | Channel Separation                                                          | Po=5W, f=1kHz                                                                                 |          | 80   |         | dB                |

| T <sub>STUP</sub>    | Startup Time                                                                |                                                                                               |          | 160  |         | ms                |

| T <sub>SD</sub>      | Shutdown Mode Settling Time                                                 |                                                                                               |          | 20   |         | ms                |

| f <sub>SW</sub>      | PWM Output Carrier Frequency                                                |                                                                                               |          | 360  |         | kHz               |

|                      |                                                                             | VDD=9V, Stereo Mode                                                                           |          | 3.2  |         | A/Ch              |

| Ilimit               | Over-Current Limit                                                          | VDD=7.2V, Mono Mode                                                                           |          | 2.7  |         | A/Ch              |

|                      |                                                                             | VDD=9V, Stereo Mode                                                                           |          | 4.2  |         | А                 |

|                      |                                                                             | VDD=7.2V, Mono Mode                                                                           |          | 3.6  |         | А                 |

| T <sub>OCP</sub>     | Over-Current Recovery Time                                                  |                                                                                               |          | 40   |         | ms                |

| T <sub>OTP</sub>     | Over-Temperature Threshold                                                  |                                                                                               |          | 160  |         | °C                |

| T <sub>HYS</sub>     | Over-Temperature Hysteresis                                                 |                                                                                               |          | 20   |         | °C                |

| AUTOMATI             | IC LEVEL CONTROL (ALC)                                                      |                                                                                               |          |      |         |                   |

| A <sub>MAX</sub>     | Maximum ALC Attenuation                                                     |                                                                                               |          | 10   |         | dB                |

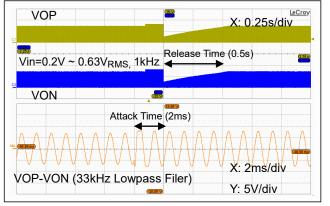

|                      |                                                                             | ATT=Low                                                                                       |          | 2    |         | ms                |

| T <sub>ATTACK</sub>  | ALC Attack Time                                                             | ATT=High                                                                                      |          | 50   |         | ms                |

| T <sub>RELEASE</sub> | ALC Release Time                                                            |                                                                                               |          | 500  |         | ms                |

|                      |                                                                             | ALC Mode                                                                                      |          |      | 0.4     | V                 |

| V <sub>ALC</sub>     | Operating Mode Threshold                                                    | DRC Mode                                                                                      | 0.6      |      | 0.5*GVD | V                 |

|                      |                                                                             | Non-ALC Mode                                                                                  | 0.8*GVDD |      |         | V                 |

| FADE-IN &            | FADE-OUT                                                                    |                                                                                               |          |      |         |                   |

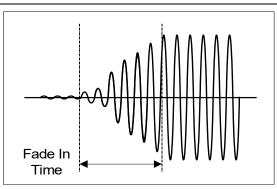

| T <sub>FADEIN</sub>  | Fade-In Time                                                                |                                                                                               |          | 20   |         | ms                |

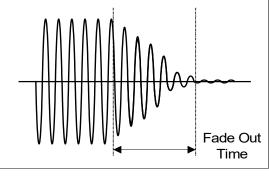

| T <sub>FADEOUT</sub> | Fade-Out Time                                                               |                                                                                               |          | 10   |         | ms                |

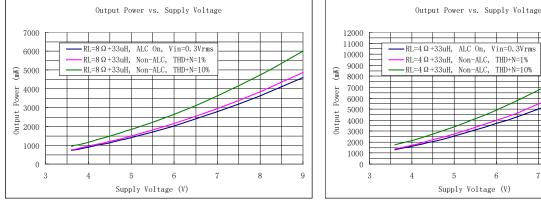

## **TYPICAL PERFORMANCE CHARACTERISTICS**

VDD=9V, CIN=0.33 $\mu$ F, RIN=10k $\Omega$ , MUTE=Low, PBTL=Low, SS=Low, ATT=High, CBYP=1 $\mu$ F, CGVDD=2.2 $\mu$ F, CAVDD=1 $\mu$ F, CPVDDL/R=1 $\mu$ F, f=1kHz, Load=4 $\Omega$ +33 $\mu$ H, Ta=25°C, unless otherwise specified.

| DESCRIPTION                          | CONDITIONS                                                                                                | FIGURE # |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------|----------|

|                                      | $R_L$ =8 $\Omega$ +33 $\mu$ H, Vin=0.3 $V_{RMS}$ , ALC & Non-ALC Modes, PBTL=Low                          | 3        |

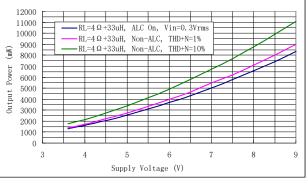

| Output Power vs. Supply Voltage      | $R_L$ =4 $\Omega$ +33µH Vin=0.3V <sub>RMS</sub> , ALC & Non-ALC Modes, PBTL=Low                           | 4        |

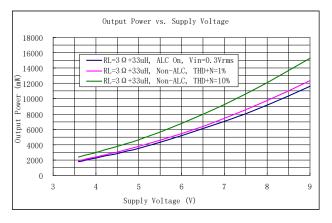

|                                      | $R_L=3\Omega+33\mu H$ , Vin=0.3V <sub>RMS</sub> , ALC & Non-ALC Modes, PBTL=High                          | 5        |

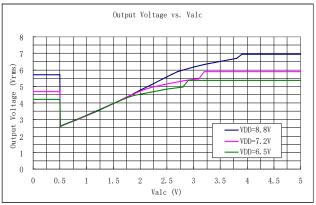

| Output Power vs. VALC                | R <sub>L</sub> =4Ω+33µH, Vin=0.4V <sub>RMS</sub> , DRC Mode<br>VDD=8.8V & 7.2V & 6.5V                     | 6        |

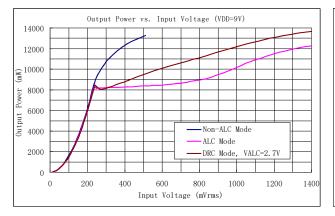

|                                      | R∟=4Ω+33µH, DRC (VaLc=2.7V)<br>Non-ALC, ALC, DRC Modes                                                    | 7        |

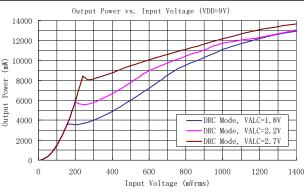

| Output Power vs. Input Voltage       | R <sub>L</sub> =4Ω+33μH, DRC Mode<br>VALC=1.8V, 2.2V, 2.7V                                                | 8        |

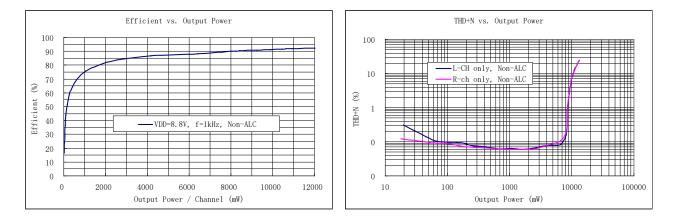

| Efficiency vs. Output Power          | VDD=8.8V, $R_L$ =4 $\Omega$ +33 $\mu$ H, Non-ALC Mode                                                     | 9        |

| THD+N vs. Output Power               | R∟=4Ω+33µH, Non-ALC Mode                                                                                  | 10       |

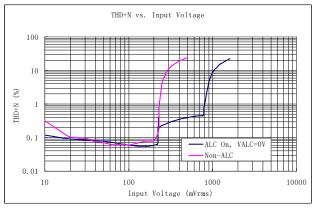

|                                      | $R_L=4\Omega+33\mu H$ , ALC & Non-ALC Modes                                                               | 11       |

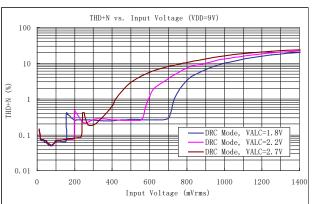

| THD+N vs. Input Voltage              | R <sub>L</sub> =4Ω+33μH, DRC Mode<br>VALC=1.8V, 2.2V, 2.7V                                                | 12       |

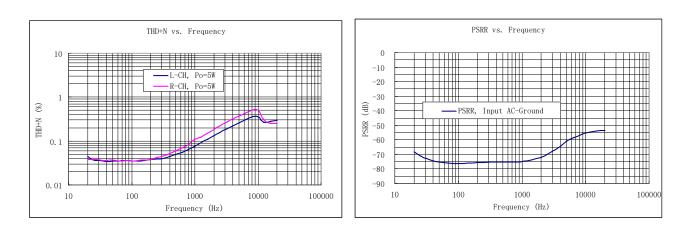

| THD+N vs. Input Frequency            | R <sub>L</sub> =4Ω+33μH, ALC Mode, Po=5W                                                                  | 13       |

| PSRR vs. Frequency                   | R∟=4Ω+33µH, Inputs AC-Grounded                                                                            | 14       |

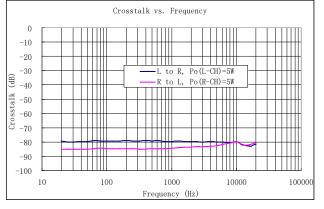

| Crosstalk vs. Input Frequency        | R <sub>L</sub> =4Ω+33µH, Vo=2.0V <sub>RMS</sub> , R-CH to L-CH                                            | 15       |

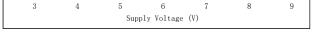

| Quiescent Current vs. Supply Voltage | Input AC-Grounded, No Load, ALC Mode                                                                      | 16       |

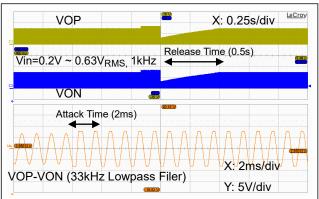

| ALC Attack & Release Time            | Vin=0.2V <sub>RMS</sub> ~ 0.63V <sub>RMS</sub> , R <sub>L</sub> =4Ω+33μH<br>VALC=0V (ALC Mode), ATT=Low   | 17       |

| ALC Attack & Release Time            | Vin=0.2V <sub>RMS</sub> ~ 0.63V <sub>RMS</sub> , R <sub>L</sub> =4Ω+33μH<br>VALC=2.7V (DRC Mode), ATT=Low | 18       |

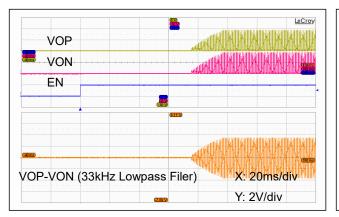

| (VOP-VON) Startup Waveforms          | $R_L$ =4 $\Omega$ +33µH, Vin=0.1V <sub>RMS</sub> , ALC Mode                                               | 19       |

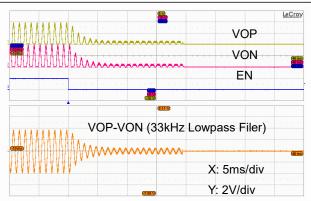

| (VOP-VON) Shutdown Waveforms         | $R_L=4\Omega+33\mu H$ , Vin=0.1V <sub>RMS</sub> , ALC Mode                                                | 20       |

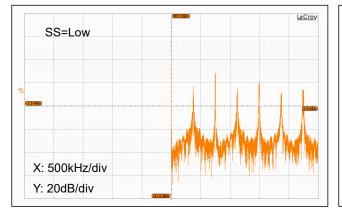

| Breadhand Output Speatrum            | $R_L=4\Omega+33\mu H$ , Vin=0.2V <sub>RMS</sub> , SS=Low                                                  | 21       |

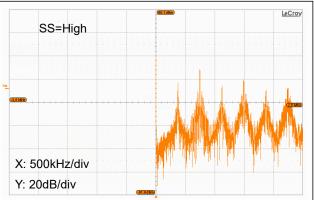

| Broadband Output Spectrum            | $R_L=4\Omega+33\mu H$ , Vin=0.2V <sub>RMS</sub> , SS=High                                                 | 22       |

# TYPICAL PERFORMANCE CHARACTERISTICS (Cont'd)

Figure 4: Output Power vs. Supply Voltage

Figure 5: Output Power vs. Supply Voltage

Figure 6: Output Power vs. VALC (DRC Mode)

Figure 7: Output Power vs. Input Voltage

Figure 8: Output Power vs. Input Voltage (DRC Mode)

## TYPICAL PERFORMANCE CHARACTERISTICS (Cont'd)

Figure 9: Efficiency vs. Output Power

Figure 11: THD+N vs. Input Voltage

Figure 12: THD+N vs. Input Voltage (DRC Mode)

Figure 13: THD+N vs. Frequency

Figure 14: PSRR vs. Frequency

9

# **TYPICAL PERFORMANCE CHARACTERISTICS (Cont'd)**

18

16

12

10

8

4

2

0

€ 14

Current

Quiescent 6

Figure 15: Crosstalk vs. Frequency

Quiescent Current

Quiescent Current vs. Supply Voltage

Figure 17: ALC Attack & Release Time (ALC Mode)

Figure 18: ALC Attack & Release Time (DRC Mode)

Figure 19: (VOP-VON) Startup Waveforms

Figure 20: (VOP-VON) Shutdown Waveforms

# TYPICAL PERFORMANCE CHARACTERISTICS (Cont'd)

Figure 21: Broadband Output Spectrum

Figure 22: Broadband Output Spectrum

## **APPLICATION INFORMATION**

The ft2725 is a highly efficient 2X10W stereo Class-D audio power amplifier with automatic level control (ALC) and dynamic range compression (DRC). It operates with a wide range of supply voltages from 3.7V to 9V. When powered with 9V supply voltage, the ft2725 is capable of delivering 10W per channel into a pair of 4 $\Omega$  speakers in a bridge-tied-load (BTL) configuration, or 15W into a single 3 $\Omega$  speaker in parallel BTL (PBTL) configuration, with 10% THD+N.

The ft2725 features ALC with an adjustable threshold for dynamic range control (DRC). The ALC constantly monitors and safeguards the audio outputs against a user-defined threshold voltage, preventing output clipping distortion, excessive power dissipation, or hazardous speaker over-load. Once an over-level condition is detected, the ALC lowers the voltage gain of the audio amplifiers proportionally to eliminate output clipping while maintaining for a maximally-allowed dynamic range of the audio outputs. The threshold voltage of the ALC can be set at either the supply voltage or an externally defined value.

In ft2725, three operating modes, i.e., ALC, DRC, and Non-ALC, are available that can be selected via the ALC pin. The Non-ALC mode configures the device in a conventional Class-D operation, where the output power is maximized without ALC operation. In ALC mode, the output limiting voltage is set at the supply voltage. In DRC mode, the threshold voltage for dynamic range compression is adjustable and set at a user-defined value that is linearly proportional to the voltage applied onto the ALC pin.

As a filterless Class-D audio amplifier, the ft2725 features high efficiency (up to 89%), high PSRR (76dB at 1kHz), and low EMI emissions, which reduce design and manufacturing complexities, lower system cost and PCB space. These features make ft2725 an ideal audio solution for portable and plug-in consumer electronic devices.

As specifically designed for portable applications, the ft2725 incorporates a shutdown mode to minimize the power consumption by holding the EN pin to ground. It also includes comprehensive protection features against various operating faults such as over-current, short-circuit, over-temperature, or under-voltage for a safe and reliable operation.

### AUTOMATIC LEVEL CONTROL (ALC)

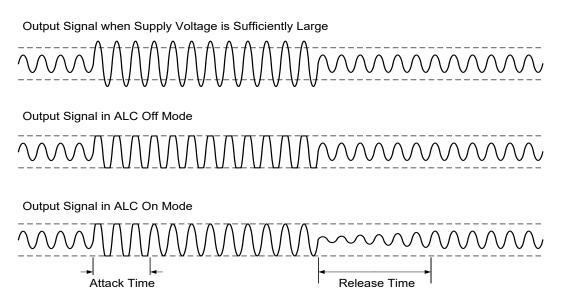

The automatic level control is to maintain the audio output signals for a maximum voltage swing without distortion when an excessive input that may cause output clipping is applied. With the ALC function, the ft2725 lowers the gain of the amplifier to an appropriate value such that the clipping at the outputs is substantially eliminated. It also eliminates the clipping of the output signal due to the reduction of the power-supply voltage.

#### Figure 23: Automatic Level Control Diagram

The attack time and release time of the ALC are shown in Table 1. The attack time is defined as the time interval required for the gain to fall to its steady-state gain less 3dB approximately, assumed that a sufficiently large input signal is applied. The release time is the time interval required for the amplifier to exit out of the present mode of operation.

| ATT Logic Level | Attack Time (ms) | Release Time (ms) |  |  |

|-----------------|------------------|-------------------|--|--|

| Low             | 2                | 500               |  |  |

| High            | 50               | 500               |  |  |

| Table 1: Attack | Time & Release Time |

|-----------------|---------------------|

|-----------------|---------------------|

### **OPERATING MODE CONTROL**

As described in Table 2, depending upon the voltage applied onto the ALC pin, the ft2725 can be configured in one of the three operating modes: ALC (automatic level control with a fixed threshold voltage at VDD), DRC (automatic level control with an adjustable threshold voltage defined by the voltage at the ALC pin), and Non-ALC. If the voltage at the ALC pin is set less than 0.4V, the ft2725 operates in ALC mode, where the threshold voltage of ALC is set at the supply voltage, VDD. In this case, the output peak voltage is limited to a value that is substantially close to the supply voltage VDD. If the voltage at the ALC pin is set in the range from 0.6V to 0.5\*GVDD, the ft2725 operates in DRC mode, where audio compression will be performed for the audio outputs exceeding the defined threshold voltage. In this case, the threshold voltage of DRC is linearly proportional to the voltage at the ALC pin. If the voltage at the ALC pin is set higher than 0.8\*GVDD, the ft2725 operates in Non-ALC mode, where the ft2725 operates as a conventional Class-D amplifier without ALC or DRC function. In this case, the output voltage will clip when the output peak voltage reaches beyond VDD.

| Voltage at ALC                             | Mode of Operation                         |

|--------------------------------------------|-------------------------------------------|

| VALC <u>&lt;</u> 0.4V                      | ALC (with fixed threshold voltage at VDD) |

| 0.6V <u>&lt;</u> VALC <u>&lt;</u> 0.5*GVDD | DRC (with adjustable threshold voltage)   |

| VALC <u>&gt;</u> 0.8*GVDD                  | Non-ALC                                   |

**Table 2: Operating Mode Control**

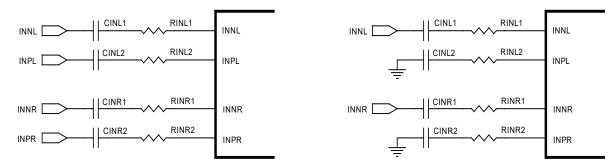

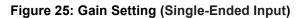

## VOLTAGE GAIN SETTING

In ft2725, the voltage gain of the audio amplifier can be externally adjusted by inserting external input resistors, Rin, in series with the input capacitors, as depicted in Figure 24 and 25. In both figures, it is required that CIN = CINL1 = CINL2 = CINR1 = CINR2, RIN = RINL1 = RINL2 = RINR1 = RINR2.

Figure 24: Gain Setting (Differential Inputs)

The value of R<sub>IN</sub> (in k $\Omega$ ) for a given voltage gain can be calculated by Equation 1, where A<sub>V</sub> is the voltage gain of the audio amplifier.

$$A_{V} = \frac{625}{R_{IN} + 15}$$

(1)

Table 3 shows suitable resistor values of R<sub>IN</sub> that can be used for various voltage gains.

| RIN (kΩ) | 10 | 16 | 20 | 24 | 30 | 36 | 39 | 47 | 56 | 62 |

|----------|----|----|----|----|----|----|----|----|----|----|

| AV (dB)  | 28 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 |

#### Table 3: External Input Resistor Values Required for Various Voltage Gains

The choice of the voltage gain will strongly influence the loudness and quality of audio sounds. In general, the higher the voltage gain is, the louder the sound is perceived. However an excessive voltage gain may cause audio outputs to be severely clipped for high-level (loud) audio sounds. On the other hand, an unusually low gain may cause relatively low-level (quiet) sounds soft or inaudible. Thus it is crucial to choose a proper voltage gain for well balanced audio quality.

The voltage gain is chosen based upon various system-level considerations including the supply voltage, the dynamic range of audio sources and speaker loads, and the desired sound effects. As a general guideline, the voltage gain can be simply expressed in Equation 2. In the equation, VIN, MAX (in VRMS) is the maximum input level from the audio source, PVDD (in volts) is the supply voltage, and  $\alpha$  is the design parameter, which ranges from 0.65 to 2.2. The higher  $\alpha$  is, the higher the average output power (louder) is, with some degree of compression for high-level audio sounds.

$$A_V = \frac{\alpha \times PVDD}{V_{IN, MAX}}$$

(2)

As an example, Table 4 shows the voltage gains for various input levels and PVDD settings with  $\alpha$  at about 1.2. In the table, R<sub>IN</sub> is the external input resistor in series with the input capacitor.

| PVDD<br>(V) | V <sub>IN, MAX</sub><br>(V <sub>RMS</sub> ) | R <sub>IN</sub><br>(kΩ) | A <sub>V</sub><br>(V/V) | A <sub>V</sub><br>(dB) | Po, ALC (W)<br>with 4Ω+33μH Load |  |

|-------------|---------------------------------------------|-------------------------|-------------------------|------------------------|----------------------------------|--|

| 9.0         | 0.3                                         | 10                      | 25                      | 28                     |                                  |  |

|             | 0.5                                         | 20                      | 18                      | 25                     | 8.5                              |  |

|             | 0.7                                         | 36                      | 12                      | 22                     | 0.0                              |  |

|             | 1.0                                         | 62                      | 8                       | 18                     |                                  |  |

| 7.2         | 0.3                                         | 16                      | 20                      | 26                     |                                  |  |

|             | 0.5                                         | 33                      | 13                      | 22                     | 5.2                              |  |

|             | 0.7                                         | 47                      | 10                      | 20                     |                                  |  |

|             | 0.3                                         | 20                      | 18                      | 25                     |                                  |  |

| 6.5         | 0.5                                         | 36                      | 12                      | 22                     | 4.2                              |  |

|             | 0.7                                         | 56                      | 9                       | 19                     |                                  |  |

Table 4: Typical Voltage Gain Settings & Input Resistor Values for Various Input Levels

## **GVDD SUPPLY**

The GVDD is an internally generated supply voltage for internal circuitry. It can also be used as the supply voltage for the resistor divider to set the voltage at the ALC pin. It is recommended to decouple GVDD with a 2.2µF ceramic capacitor to ground for stable operation. Note that the current drawn from GVDD by external circuitry, including the resistor divider at the ALC pin, must be kept less than 0.5mA.

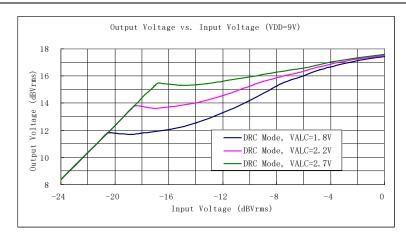

## ADJUSTABLE DRC THRESHOLD VOLTAGE

In conventional Class-D audio amplifiers with ALC operation, the output peak voltage is limited with respect to the supply voltage applied to the device. The ft2725 features a DRC mode whose threshold (knee) voltage can be externally set via the ALC pin. The threshold voltage (VKNEE) is linearly proportional to the voltage at the ALC pin, as described by Equation 3.

$$V_{\text{KNEE}} = 3 \times V_{\text{ALC}} \tag{3}$$

In Equation 3, V<sub>ALC</sub> is the voltage at the ALC pin and can be set by a resistor divider from GVDD (an internally generated reference voltage) to ground, as shown in Figure 26. It is strongly recommended to add a  $0.1\mu$ F capacitor from the ALC pin to ground for a stable operation. For best accuracy, the parallel combination of the resistor divider should be close to  $100k\Omega$ .

Figure 26: Typical Circuit Setting VALC

Table 5 shows typical values of R1 and R2 that can be used to derive various VALC. In the table, the corresponding DRC threshold voltage and the output power where DRC commences for each individual setting are also shown.

| <b>R1 (</b> kΩ) | <b>R2 (</b> kΩ) | R2/(R1+R2) | GVDD (V) | VALC (V) | VKNEE (V) | <b>Ρο (W) @ 4</b> Ω |

|-----------------|-----------------|------------|----------|----------|-----------|---------------------|

| 200             | 82              | 0.29       | 6.2      | 1.8      | 5.4       | 3.6                 |

| 170             | 82              | 0.32       | 6.2      | 2.0      | 6.0       | 4.5                 |

| 180             | 100             | 0.36       | 6.2      | 2.2      | 6.6       | 5.4                 |

| 150             | 100             | 0.40       | 6.2      | 2.5      | 7.5       | 7.0                 |

| 130             | 100             | 0.43       | 6.2      | 2.7      | 8.1       | 8.2                 |

Table 5: Typical Resistor Values of R1 & R2 (VDD=9V) for Various DRC Threshold Voltages

In DRC mode, the ALC lowers the voltage gain for high-level (loud) audio outputs that are above the threshold, while maintaining a constant and relatively high voltage gain for low-level (quiet) audio outputs. In this manner, relatively quiet sounds become louder while louder sounds remain unclipped. The net effect of DRC is to keep the audio volume fairly constant over a range from medium to high level sounds while allowing relatively quiet sounds of the music much more audible. For most applications, it is recommended to set the voltage gain at its highest value (Av=32.4dB), if possible, for the device operating in DRC mode.

For most applications, V<sub>ALC</sub> can be set in the range from 0.3\*GVDD (or 0.2\*VDD) to 0.45\*GVDD (or 0.3\*VDD). A lower V<sub>ALC</sub> allows audio compression commencing at a lower audio output with a lower compression ratio. On the contrary, a higher V<sub>ALC</sub> makes audio compression commencing at a higher audio output with a higher compression ratio. Note that the ALC mode (V<sub>ALC</sub>  $\leq 0.4$ V) is one of the exceptional cases of DRC where the DRC threshold is set at a value substantially close to the supply voltage with a fairly large compression ratio.

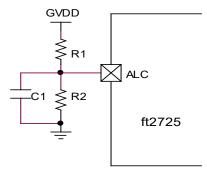

Figure 27 illustrates the transfer (gain) function of the output (in dBVrms) with respect to the input (in dBVrms) for ft2725 operating with VDD=9V and Av=32.4dB in DRC mode for three different values of VALC. As shown in the figure, the voltage gain is constant at 32.4dB for low-level audio output (less than the threshold) while the voltage gain for high-level audio output (more than the threshold) is gradually lowered as the audio output grows larger. In a sense, the audio output is compressed as the audio output is larger than the threshold.

Figure 27: Output Voltage vs. Input Voltage (in dBVrms)

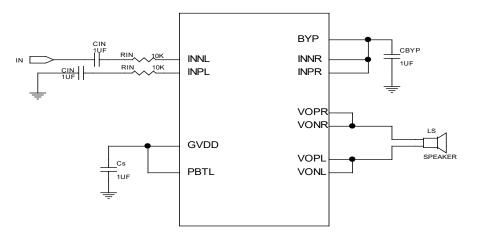

### MONO MODE

The ft2725 features an optional mono mode that allows the left and right channels to operate in parallel BTL configuration, delivering up to 15W into a single  $3\Omega$  speaker. Apply a logic-high to PBTL pin to enable mono mode. In mono mode, as shown in Figure 28, an audio input signal applied to the left channel is routed to the H-bridge of both channels. The ft2725 operates in stereo mode by driving a logic-low to PBTL pin or leave the pin unconnected. Driving PBTL low or leaving it unconnected while the audio outputs VOPL/R and VONL/R are wired together in PBTL configuration can trigger the over-current or thermal overload protection or both. The mono mode of ft2725 is configured by:

- Connect PBTL to logic-high to set the device in mono mode.

- Connect INPR and INNR pins (pin 22 and 23) directly to BYP.

- Audio input signals are applied to INPL and INNL pins (pin 2 and 3).

- Connect VOPL to VONL and VOPR to VONR using heavy PCB traces as close as possible to the device.

- Place the speaker between the left and right-channel outputs.

Figure 28: Application Circuit of Mono Mode in PBTL Configuration

## VOLUME FADE-IN & FADE-OUT

The volume fade-in/out function operates when toggled EN or MUTE state. This function is used to reduce intermittent sound considerably and eliminate uncomfortable feeling.

Figure 29: Fade-In Waveform

Figure 30 Fade-Out Waveform

### SHUTDOWN AND STARTUP

The ft2725 employs the EN pin to minimize power consumption while it is not in use. When the EN pin is pulled to ground, the ft2725 is forced into shutdown mode, where all the analog circuitry is de-biased and the supply current is thus reduced to less than  $10\mu$ A, and the differential outputs are shorted to ground through an internal resistor (2.5k $\Omega$ ) individually. Once in shutdown mode, the EN pin must remains low for at least 20ms (T<sub>SD</sub>), the shutdown settling time, before it can be brought high again. When the EN pin is asserted high, the device exits out of the shutdown mode and enters into the normal mode of operation after the startup time (T<sub>STUP</sub>) of 160ms.

Note that an internal pulldown resistor of  $300k\Omega$  is implemented onto the EN pin. Furthermore, the shutdown mode is the state when the power supply is first applied to the device. Whenever possible, it is recommended to assert EN high to exit the device out of the shutdown mode only after the device is properly started up. Also, place the amplifiers in the shutdown mode prior to removing the power supply voltage for best power-off pop performance.

### **MUTE CONTROL**

In ft2725, the MUTE pin is used to control the operation of the output stages of both channels. When playing music, the MUTE pin is pulled low and the output stages of audio amplifiers are enabled. When the MUTE pin is asserted high, the output stages of audio amplifiers are de-biased while the differential audio outputs VOPL/R and VONL/R are pulled to ground through on-chip resistors individually.

### CLICK-AND-POP SUPPRESSION

The ft2725 features comprehensive click-and-pop suppression. During startup, the click-and-pop suppression circuitry reduces any audible transients internal to the device. When entering into shutdown, the differential audio outputs VOPL/R and VONL/R ramp down to ground quickly and simultaneously.

### **PSRR ENHANCEMENT**

With a dedicated pin for the common-mode voltage bias and an external holding capacitor onto the pin, the ft2725 achieves a PSRR, 76dB at 1kHz.

### **PROTECTION MODES**

The ft2725 incorporates various protection functions against possible operating faults for a safe operation. It includes Under-voltage Lockout (UVLO), Over-Current Protection (OCP), and Over-Temperature Shutdown (OTSD).

### Under-Voltage Lockout (UVLO)

The ft2725 incorporates a circuitry to detect a low supply voltage for a safe and reliable operation. When the supply voltage is first applied, the ft2725 will remain inactive until the supply voltage exceeds 3.2V ( $V_{UVLU}$ ). When the supply voltage is removed and drops below 2.9V ( $V_{UVLD}$ ), the ft2725 enters into shutdown mode immediately.

#### Over-Temperature Shutdown (OTSD)

When the die temperature exceeds a preset threshold, the device enters into the over-temperature shutdown mode, where the differential audio outputs VOPL/R and VONL/R are pulled to ground through on-chip resistors individually. The device will resume normal operation once the die temperature returns to a lower temperature, which is about 20°C lower than the threshold.

#### **Over-Current Protection (OCP)**

During operation, the output of Class-D amplifier constantly monitors for any over-current and/or short-circuit conditions. When a short-circuit condition between two differential outputs, differential output to AVDD, PVDDL, PVDDR or ground is detected, the output stage of the amplifier is immediately forced into high impedance state. Once the fault condition persists over a prescribed period, the ft2725 then enters into the shutdown mode and remains in this mode for about 40ms ( $T_{OCP}$ ), the over-current recovery time. When the shutdown mode times out, the ft2725 will initiate another start-up sequence and then check if the short-circuit condition has been removed. If the fault condition is still present, the ft2725 will repeat itself for the process of a startup followed by detection, qualification, and shutdown. It is so-called the hiccup mode of operation. Once the fault condition is removed, the ft2725 automatically restores to its normal mode of operation.

Although the output stages of the Class-D audio amplifiers can withstand a short between VOPL/R and VONL/R pins, do not short audio output pins (VOPL/R and VONL/R) directly to ground pins (AGND, PGNDL/R) or the supply voltage pins (AVDD, PVDDL/R) as this might damage the device permanently, particularly when the supply voltage is higher than 8.4V.

#### LOW-EMI FILTERLESS OUTPUT STAGE

Traditional Class-D amplifiers require for the use of external LC filters, or shielding, to meet EN55022B electromagnetic-interference (EMI) regulation standards. The ft2725 applies an edge-rate control circuitry to reduce EMI emission, while maintaining high power efficiency. Above 10MHz, the wideband spectrum looks like noise for EMI purposes.

#### **EMI REDUCTION**