# ADJUSTABLE MICROPOWER VOLTAGE REGULATORS WITH SHUTDOWN

# FEATURES

- Wide Input Range:up to 30 V

- Rated Output Current of 100 mA

- Low Dropout:380 mV (Typ) at 100 mA

- Low Quiescent Current:75 µA (Typ)

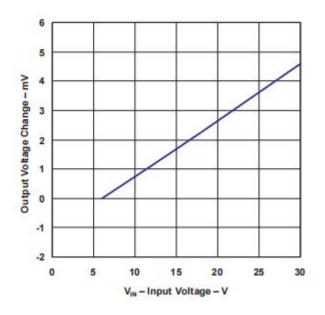

- Tight Line Regulation:0.03% (Typ)

- Tight Load Regulation:0.04% (Typ)

- High VO Accuracy

- **-1.4% at 25**℃

- -2% Over Temperature

- Can Be Used as a Regulator or Reference

- Stable With Low ESR (>12 mΩ) Capacitors

- Current- and Thermal-Limiting Features

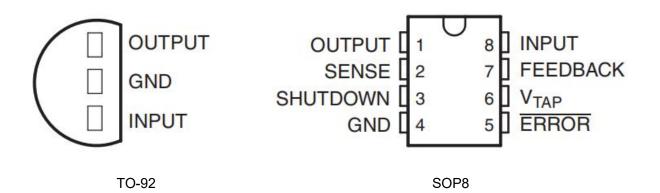

- LP2950 Only (3-Pin Package)

-Fixed-Output Voltages of 5 V, 3.3 V,and 3 V

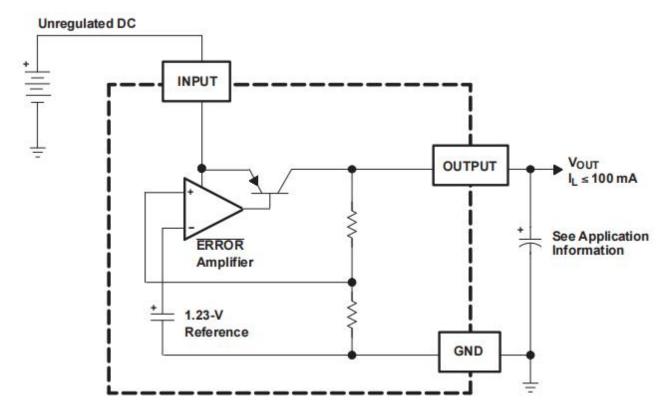

- LP2951 Only (8-Pin Package)

-Fixed- or Adjustable-Output Voltages: 5 V/ADJ, 3.3 V/ADJ, and 3 V/ADJ

-Low-Voltage Error Signal on Falling Output

-Shutdown Capability

- -Remote Sense Capability for Optimal Output Regulation and Accuracy

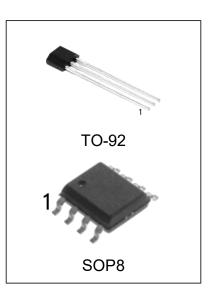

# **ORDERING INFORMATION**

| DEVICE        | Package Type | MARKING    | Packing | Packing Qty  |

|---------------|--------------|------------|---------|--------------|

| LP2950-3.0LPG | TO-92        | LP2950-3.0 | TUBE    | 1000pcs/box  |

| LP2950-3.3LPG | TO-92        | LP2950-3.3 | TUBE    | 1000pcs/box  |

| LP2950-5.0LPG | TO-92        | LP2950-5.0 | TUBE    | 1000pcs/box  |

| LP2951-3.0DRG | SOP8         | LP2951-3.0 | REEL    | 2500pcs/reel |

| LP2951-3.3DRG | SOP8         | LP2951-3.3 | REEL    | 2500pcs/reel |

| LP2951-5.0DRG | SOP8         | LP2951-5.0 | REEL    | 2500pcs/reel |

| LP2951DRG     | SOP8         | LP2951     | REEL    | 2500pcs/reel |

# DESCRIPTION

The LP2950 and LP2951 devices are bipolar, low-dropout voltage regulators that can accommodate a wide input supply-voltage range of up to 30 V. The easy-to-use, 3-pin LP2950 is available in fixed-output voltages of 5 V,3.3 V, and 3 V. However, the 8-pin LP2951 is able to output either a fixed or adjustable output from the same device. By tying the OUTPUT and SENSE pins together, and the FEEDBACK and VTAP pins together, the LP2951 outputs a fixed 5 V, 3.3 V, or 3 V (depending on the version). Alternatively, by leaving the SENSE and VTAP pins open and connecting FEEDBACK to an external resistor divider, the output can be set to any value between 1.235 V to 30 V.

The 8-pin LP2951 also offers additional functionality that makes it particularly suitable for battery-powered applications. For example, a logic-compatible shutdown feature allows the regulator to be put in standby mode for power savings. In addition, there is a built-in supervisor reset function in which the  $\overline{\text{ERROR}}$  output goes low when VOUT drops by 6% of its nominal value for whatever reasons – due to a drop in VIN, current limiting, or thermal shutdown.

The LP2950 and LP2951 are designed to minimize all error contributions to the output voltage. With a tight output tolerance (0.5% at 25 C), a very low output voltage temperature coefficient (20 ppm typical), extremely good line and load regulation (0.3% and 0.4% typical), and remote sensing capability, the parts can be used as either low-power voltage references or 100-mA regulators.

# **Pin Configuration**

# LP2950FUNCTIONALBLOCKDIAGRAM

# LP2951 FUNCTIONAL BLOCK DIAGRAM

# Absolute Maximum Ratings<sup>(1)</sup>

| over energing free air ter  | noroturo rondo | (uplease otherwise poted) |

|-----------------------------|----------------|---------------------------|

| over operating free-air tem |                |                           |

|                             |                | (                         |

|       |                                          |               | MIN  | MAX | UNIT |

|-------|------------------------------------------|---------------|------|-----|------|

| VIN   | Continuous input voltage range           |               | -0.3 | 30  | V    |

| VSHDN | SHUTDOWN input voltage range             |               | -1.5 | 30  | V    |

|       | ERROR comparator output voltage range(2) |               | -1.5 | 30  | V    |

| VFDBK | FEEDBACK input voltage range(2)(3)       |               | -1.5 | 30  | V    |

|       |                                          | SOP8 package  |      | 97  |      |

| θJA   | Package thermal impedance(4)(5)          | TO-92 package |      | 140 | °C/W |

| TJ    | Operating virtual junction temperature   |               |      | 150 | °C   |

| Tstg  | Storage temperature range                |               | -65  | 150 | °C   |

1. Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- 2. May exceed input supply voltage

- 3. If load is returned to a negative power supply, the output must be diode clamped to GND.

- Maximum power dissipation is a function of TJ(max), θJA, and TA. The maximum allowable power dissipation at any allowable ambient temperature is PD = (TJ(max) TA)/θJA. Operating at the absolute maximum TJ of 150°C can affect reliability.

- 5. The package thermal impedance is calculated in accordance with JESD 51-7.

# **Recommended Operating Conditions**

|     |                                        | MIN | MAX | UNIT |

|-----|----------------------------------------|-----|-----|------|

| VIN | Supply input voltage                   | (1) | 30  | V    |

| TJ  | Operating virtual junction temperature | -40 | 125 | °C   |

(1) Minimum VIN is the greater of:

- a. 2 V (25°C), 2.3 V (over temperature), or

- b. VOUT(MAX) + Dropout (Max) at rated IL

# **Electrical Characteristics**

$V_{IN} = V_{OUT}$  (nominal) + 1 V, I<sub>L</sub> = 100µA, C<sub>L</sub> = 1µF (5-V versions) or C<sub>L</sub> = 2.2 µF (3-V and 3.3-V versions),8-pin version: FEEDBACK tied to V<sub>TAP</sub>, OUTPUT tied to SENSE, V<sub>SHUTDOWN</sub> ≤ 0.7 V

| P                             | ARAMETER            | TEST CONDITIONS                          | TJ             | MIN   | TYP   | MAX   | UNIT   |  |

|-------------------------------|---------------------|------------------------------------------|----------------|-------|-------|-------|--------|--|

| 3-V VERSION                   | (LP295x-30)         |                                          |                |       |       |       |        |  |

| VOUT                          | Output valtage      | II = 100+4                               | 25°C           | 2.970 | 3     | 3.030 | × 1    |  |

| VOUT                          | Output voltage      | IL = 100µA                               | –40°C to 125°C | 2.940 | 3     | 3.060 | V      |  |

| 3.3-V VERSIO                  | N (LP295x-33)       |                                          |                |       |       |       |        |  |

|                               | 0 / / //            |                                          | 25°C           | 3.267 | 3.3   | 3.333 |        |  |

| VOUT Output voltage           |                     | IL = 100µA                               | –40°C to 125°C | 3.234 | 3.3   | 3.366 | V      |  |

| 5-V VERSION                   | (LP295x-50)         |                                          |                |       |       |       |        |  |

| VOUT                          | Outrastication      | 1 100.14                                 | 25°C           | 4.950 | 5     | 5.050 |        |  |

| VOUT Output voltage           |                     | IL = 100µA                               | –40°C to 125°C | 4.900 | 5     | 5.100 |        |  |

| ALL VOLTAGE                   | OPTIONS             |                                          |                |       |       |       |        |  |

| Output voltage coefficient(1) | e temperature       | IL = 100μA                               | –40°C to 125°C |       | 20    | 100   | ppm/°  |  |

| Line regulation(2)            |                     | VIN = [VOUT(NOM) + 1 V]                  | 25°C           |       | 0.03  | 0.2   |        |  |

|                               |                     | to 30 V                                  | –40°C to 125°C |       |       | 0.4   | - %/V  |  |

|                               |                     | II. 100 A.L. 100 A.                      | 25°C           |       | 0.04  | 0.2   |        |  |

| Load regulation(2)            |                     | IL = 100 µA to 100 mA                    | –40°C to 125°C |       |       | 0.3   | - %    |  |

|                               |                     |                                          | 25°C           |       | 50    | 80    |        |  |

| VIN –VOUT                     |                     | IL = 100μA                               | –40°C to 125°C |       |       | 150   | 1.     |  |

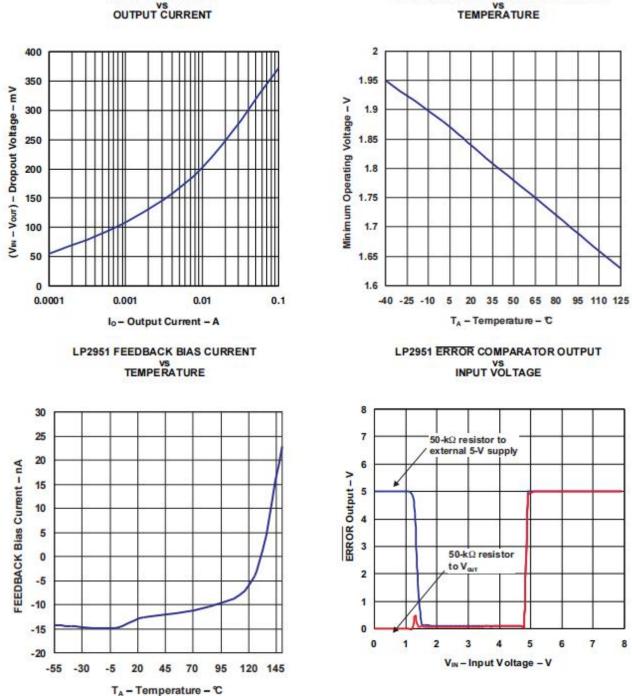

|                               | Dropout voltage(3)  |                                          | 25°C           |       | 380   | 450   | - mV   |  |

|                               |                     | IL = 100 mA                              | –40°C to 125°C |       |       | 600   | -      |  |

|                               | 1                   |                                          | 25°C           |       | 75    | 120   |        |  |

|                               | GND current         | IL = 100 μA                              | –40°C to 125°C |       |       | 140   | μA     |  |

| IGND                          |                     | ll                                       | 25°C           |       | 8     | 12    | mA     |  |

|                               |                     | IL = 100 mA                              | –40°C to 125°C |       |       | 14    |        |  |

| 2                             |                     | VIN = VOUT(NOM) - 0.5 V,                 | 25°C           |       | 110   | 170   |        |  |

| Dropout groun                 | d current           | IL = 100μA                               | –40°C to 125°C |       | 200   |       | μA     |  |

|                               |                     |                                          | 25°C           |       | 160   | 200   |        |  |

| Current limit                 |                     | VOUT = 0 V                               | –40°C to 125°C |       |       | 220   | mA     |  |

| Thermal regula                | ation(4)            | IL = 100µA                               | 25°C           |       | 0.05  | 0.2   | %/W    |  |

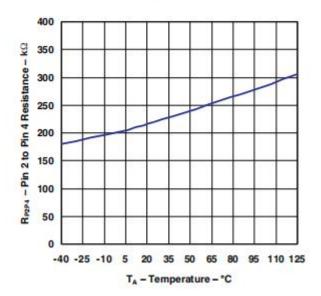

|                               |                     | CL = 1 µF (5 V only)                     |                |       | 430   |       |        |  |

| Outract and in a l            | DMO)                | CL = 200 μF                              |                |       | 160   |       |        |  |

| Output noise (                |                     | LP2951-50: CL = 3.3 µF,                  | 25°C           |       |       |       | μV     |  |

| 10 Hz to 100 k                | ιHZ                 | CBypass = 0.01 µF between pins           |                |       | 100   |       |        |  |

|                               |                     | 1 and 7                                  |                |       |       |       |        |  |

| (LP2951-xx) 8                 | -PIN VERSION ONLY A | DJ                                       |                |       |       |       |        |  |

| Reference voltage             |                     |                                          | 25°C           | 1.218 | 1.235 | 1.252 |        |  |

|                               |                     |                                          | –40°C to 125°C | 1.212 |       | 1.257 |        |  |

|                               |                     | VOUT = VREF to $(VIN - 1 V)$ ,           |                |       |       |       | V      |  |

|                               |                     | VIN = 2.3 V to 30 V,                     | –40°C to 125°C | 1.200 |       | 1.272 |        |  |

|                               |                     | IL = 100 μA to 100 mA                    |                |       |       |       |        |  |

| Reference volt                | tage                |                                          | 25°C           |       | 20    |       | nnm /0 |  |

| temperature co                | oefficient(1)       | coefficient is defined as the worst-case |                |       | 20    |       | ppm/°  |  |

(1) Output or reference voltage temperature coefficient is defined as the worst-case voltage change divided by the total temperature range.

(2) Regulation is measured at constant junction temperature, using pulse testing with a low duty cycle. Changes in output voltage due to heating effects are covered under the specification for thermal regulation.

(3) Dropout voltage is defined as the input-to-output differential at which the output voltage drops 100 mV, below the value measured at 1-V differential. The minimum input supply voltage of 2 V (2.3 V over temperature) must be observed.

(4) Thermal regulation is defined as the change in output voltage at a time (T) after a change in power dissipation is applied, excluding load or line regulation effects. Specifications are for a 50-mA load pulse at V<sub>IN</sub> = 30 V, V<sub>OUT</sub> = 5 V (1.25-W pulse) for t = 10 ms.

# **Electrical Characteristics (continued)**

$V_{IN} = V_{OUT}$  (nominal) + 1 V, I<sub>L</sub> = 100µA, C<sub>L</sub> = 1µF (5-V versions) or C<sub>L</sub> = 2.2 µF (3-V and 3.3-V versions),8-pin version: FEEDBACK tied to V<sub>TAP</sub>, OUTPUT tied to SENSE, V<sub>SHUTDOWN</sub> ≤ 0.7 V

| PARAMETER                                        | TEST CONDITIONS                               | TJ             | MIN | TYP  | MAX    | UNIT       |  |

|--------------------------------------------------|-----------------------------------------------|----------------|-----|------|--------|------------|--|

|                                                  |                                               | 25°C           |     | 20   | 40     | <b>n</b> A |  |

| FEEDBACK bias current                            |                                               | –40°C to 125°C |     |      | 60     | nA         |  |

| FEEDBACK bias current<br>temperature coefficient |                                               | 25°C           |     | 0.1  |        | nA/°C      |  |

| ERROR COMPARATOR                                 |                                               |                |     |      |        |            |  |

| Output leakage current                           | VOUT = 30 V                                   | 25°C           |     | 0.01 | 0.01 1 |            |  |

|                                                  | VO01 = 30 V                                   | –40°C to 125°C |     |      | 2      | μA         |  |

| Output low voltage                               | VIN = VOUT(NOM) - 0.5 V,                      | 25°C           |     | 150  | 250    | mV         |  |

| Output low voltage                               | IOL = 400 µA                                  | –40°C to 125°C |     |      | 400    | IIIV       |  |

| Upper threshold voltage                          |                                               | 25°C           | 40  | 60   |        |            |  |

| (ERROR output high)(5)                           |                                               | –40°C to 125°C | 25  |      |        | mV         |  |

| Lower threshold voltage                          |                                               | 25°C           |     | 75   | 95     | mV         |  |

| (ERROR output low)(5)                            |                                               | –40°C to 125°C |     |      | 140    | IIIV       |  |

| Hysteresis(6)                                    |                                               | 25°C           |     | 15   |        | mV         |  |

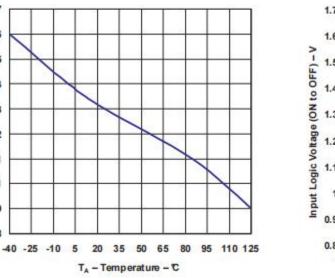

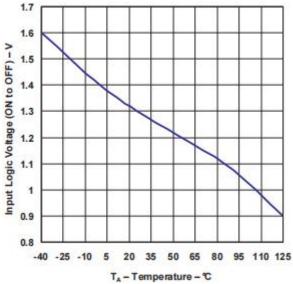

| SHUTDOWN INPUT                                   |                                               |                |     |      |        |            |  |

| Input logic voltage                              | Low (regulator ON)                            | 40°0 to 405°0  |     |      | 0.7    | v          |  |

| Input logic voltage                              | High (regulator OFF)                          | –40°C to 125°C | 2   |      |        | V          |  |

|                                                  | VTAP = 2.4 V                                  | 25°C           |     | 30   | 50     | 1          |  |

|                                                  | V TAP - 2.4 V                                 | –40°C to 125°C |     |      | 100    | 1          |  |

| SHUTDOWN input current                           | VTAP = 30 V                                   | 25°C           |     | 450  | 600    | μA         |  |

|                                                  | VIAP - 30 V                                   | –40°C to 125°C |     |      | 750    |            |  |

| Regulator output                                 | VSHUTDOWN ≥ 2 V,                              | 25°C           |     | 3    | 10     |            |  |

| current in shutdown                              | VIN≤ 30 V, VOUT = 0,<br>FEEDBACK tied to VTAP | –40°C to 125°C |     |      | 20     | μA         |  |

(5) Comparator thresholds are expressed in terms of a voltage differential equal to the nominal reference voltage(measured at VIN – VOUT = 1 V) minus FEEDBACK terminal voltage. To express these thresholds in terms of output voltage change, multiply by the error amplifier gain = VOUT/VREF = (R1 + R2)/R2. For example, at a programmed output voltage of 5 V, the ERROR output is specified to go low when the output drops by 95 mV×5 V/1.235 V = 384 mV. Thresholds remain constant as a percentage of VOUT (as VOUT is varied), with the low-output warning occurring at 6% below nominal (typ) and 7.7% (max).

(6) Comparator thresholds are expressed in terms of a voltage differential equal to the nominal reference voltage (measured at VIN – VOUT = 1 V) minus FEEDBACK terminal voltage. To express these thresholds in terms of output voltage change, multiply by the error amplifier gain = VOUT/VREF = (R1 + R2)/R2. For example, at a programmed output voltage of 5 V, the ERROR output is specified to go low when the output drops by 95 mV × 5 V/1.235 V = 384 mV. Thresholds remain constant as a percentage of VOUT (as VOUT is varied), with the low-output warning occurring at 6% below nominal (typ) and 7.7% (max).

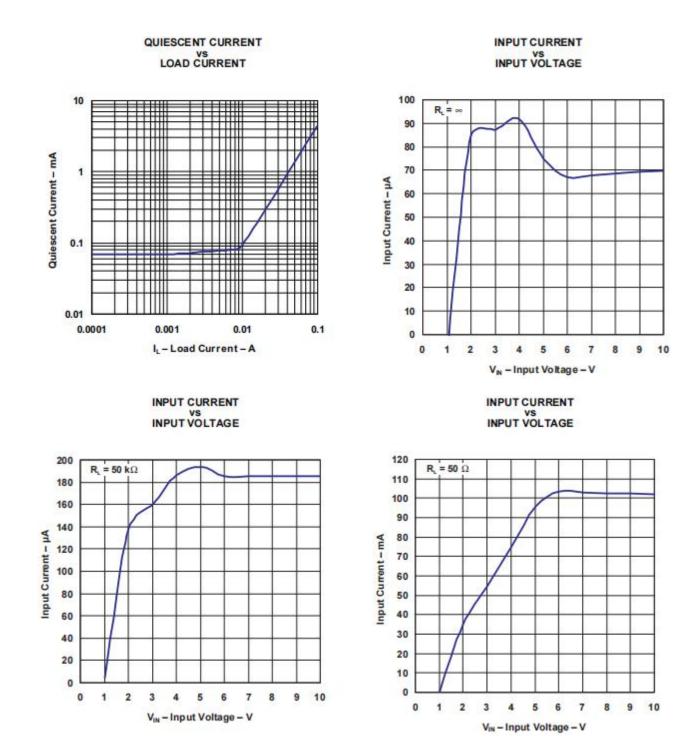

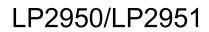

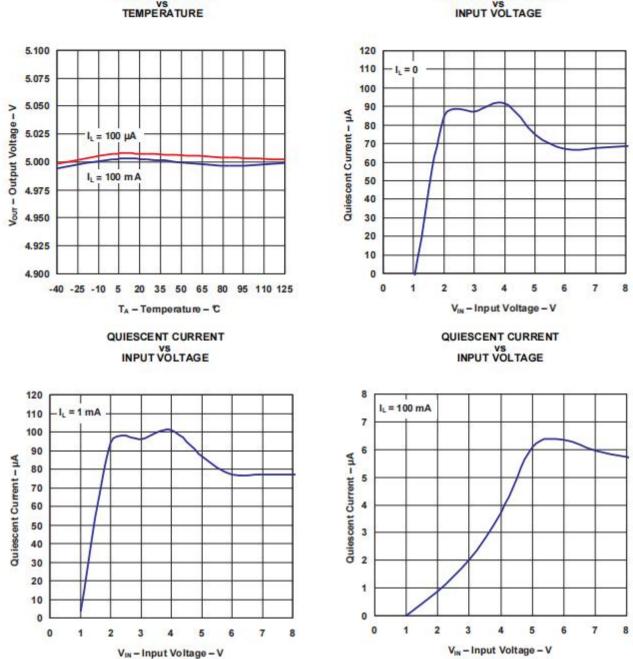

# **TYPICAL CHARACTERISTICS**

QUIESCENT CURRENT

# QUIESCENT CURRENT

QUIESCENT CURRENT

LP2951 MINIMUM OPERATING VOLTAGE

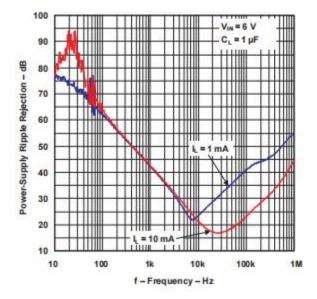

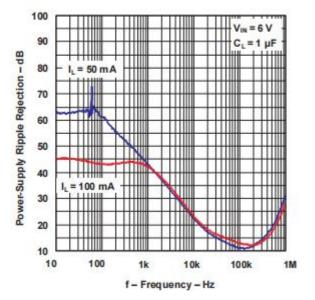

#### RIPPLE REJECTION FREQUENCY

#### RIPPLE REJECTION FREQUENCY

#### LP 2951 OUTPUT NOISE FREQUENCY

1.7

1.6

1.5

1.4

1.3

1.2

1.1

1

0.9

0.8

Input Logic Voltage (OFF to ON) - V

# SHUTDOWN THRESHOLD VOLTAGE (OFF TO ON)

SHUTDOWN THRESHOLD VOLTAGE (ON TO OFF)

# **APPLICATION INFORMATION**

#### Input Capacitor (C<sub>IN</sub>)

A 1- $\mu$ F (tantalum, ceramic, or aluminum) electrolytic capacitor should be placed locally at the input of the LP2950 or LP2951 if there is, or will be, significant impedance between the ac filter capacitor and the input; for example, if a battery is used as the input or if the ac filter capacitor is located more than 10 in away. There are no ESR requirements for this capacitor, and the capacitance can be increased without limit.

### Output Capacitor (COUT)

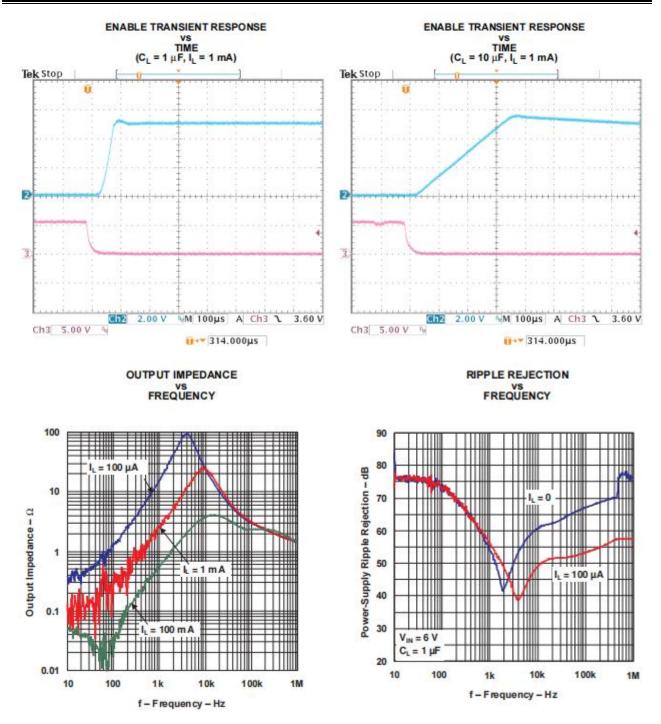

As with most PNP LDOs, stability conditions require the output capacitor to have a minimum capacitance and an ESR that falls within a certain range.

#### Capacitance Value

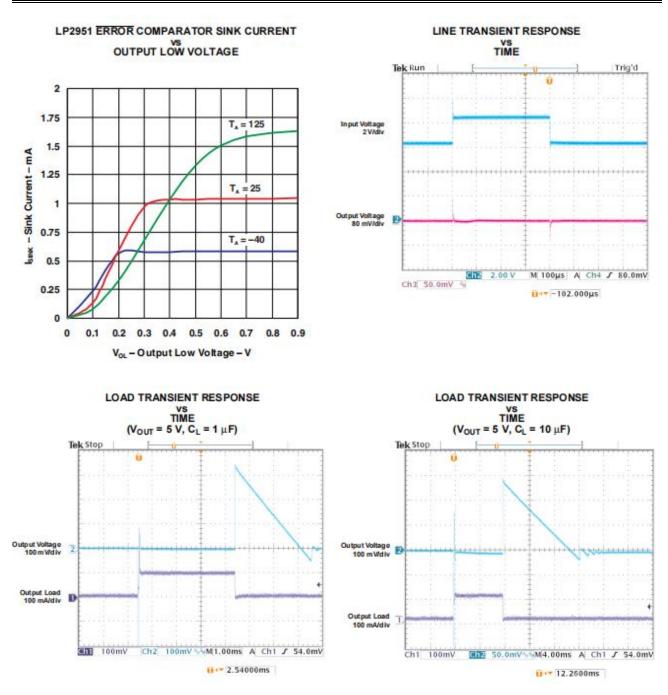

For VOUT  $\geq$ 5 V, a minimum of 1 µF is required. For lower VOUT, the regulator 'sloop gain is running closer to unity gain and, thus, has lower phase margins. Consequently, a larger capacitance is needed for stability. For VOUT = 3 V or 3.3 V, a minimum of 2.2µF is recommended. For worst case, VOUT = 1.23 V (using the ADJ version), a minimum of 3.3 µF is recommended. COUT can be increased without limit and only improves the regulator stability and transient response. Regardless of its value, the output capacitor should have a resonant frequency less than 500 kHz.

The minimum capacitance values given above are for maximum load current of 100 mA. If the maximum expected load current is less than 100 mA, then lower values of COUT can be used. For instance, if IOUT < 10 mA, then only  $0.33\mu$ F is required for COUT. For IOUT < 1 mA, 0.1  $\mu$ F is sufficient for stability requirements. Thus, for a worst-case condition of 100-mA load and VOUT = VREF = 1.235 V (representing the highest load current and lowest loop gain), a minimum COUT of 3.3  $\mu$ F is recommended.

For the LP2950, no load stability is inherent in the design — a desirable feature in CMOS circuits that are put in standby (such as RAM keep-alive applications). If the LP2951 is used with external resistors to set the output voltage, a minimum load current of 1  $\mu$ A is recommended through the resistor divider.

### ESR Range

The regulator control loop relies on the ESR of the output capacitor to provide a zero to add sufficient phase margin to ensure unconditional regulator stability; this requires the closed-loop gain to intersect the open-loop response in a region where the open-loop gain rolls off at 20 dB/decade. This ensures that the phase always is less than 180° (phase margin greater than 0°) at unity gain. Thus, a minimum-maximum range for the ESR must be observed.

The upper limit of this ESR range is established by the fact that too high an ESR could result in the zero occurring too soon, causing the gain to roll off too slowly, which, in turn allows a third pole to appear before unity gain and introduce enough phase shift to cause instability. This typically limits the max ESR to approximately  $5\Omega$ .

Conversely, the lower limit of the ESR is tied to the fact that too low an ESR shifts the zero too far out

(past unity gain) and, thus, allows the gain to roll off at 40 dB/decade at unity gain, with a resulting phase shift of greater than 180 $\Omega$ . Typically, this limits the minimum ESR to approximately 20 m $\Omega$  to 30 m $\Omega$ .

For specific ESR requirements, see Typical Characteristics .

#### Capacitor Types

Most tantalum or aluminum electrolytics are suitable for use at the input. Film-type capacitors also work, but at higher cost. When operating at low temperature, care should be taken with aluminum electrolytics, as their electrolytes often freeze at  $-30^{\circ}$ C. For this reason, solid tantalum capacitors should be used at temperatures below  $-25^{\circ}$ C.

Ceramic capacitors can be used, but due to their low ESR (as low as  $5 \text{ m}\Omega$  to  $10 \text{ m}\Omega$ ), they may not meet the minimum ESR requirement previously discussed. If a ceramic capacitor is used, a series resistor between  $0.1\Omega$  to  $2\Omega$  must be added to meet the minimum ESR requirement. In addition, ceramic capacitors have one glaring disadvantage that must be taken into account — a poor temperature coefficient, where the capacitance can vary significantly with temperature. For instance, a large-value ceramic capacitor ( $\geq 2.2\mu$ F) can lose more than half of its capacitance as temperature rises from 25°C to 85°C. Thus, a 2.2- $\mu$ F capacitor at 25°C drops well below the minimum COUT required for stability as ambient temperature rises. For this reason, select an output capacitor that maintains the minimum 2.2- $\mu$ F required for stability for the entire operating temperature range.

#### **C**<sub>BYPASS</sub>: Noise and Stability Improvement

In the LP2951, an external FEEDBACK pin directly connected to the error amplifier noninverting input can allow stray capacitance to cause instability by shunting the error amplifier feedback to GND, especially at high frequencies. This is worsened if high-value external resistors are used to set the output voltage, because a high resistance allows the stray capacitance to play a more significant role; i.e., a larger RC time delay is introduced between the output of the error amplifier and its FEEDBACK input, leading to more phase shift and lower phase margin. A solution is to add a 100-pF bypass capacitor (CBYPASS) between OUTPUT and FEEDBACK; because CBYPASS is in parallel with R1, it lowers the impedance seen at FEEDBACK at high frequencies, in effect offsetting the effect of the parasitic capacitance by providing more feedback at higher frequencies. More feedback forces the error amplifier to work at a lower loop gain, so COUT should be increased to a minimum of 3.3  $\mu$ F to improve the regulator 'sphase margin.

C<sub>BYPASS</sub> can be also used to reduce output noise in the LP2951. This bypass capacitor reduces the closed loop gain of the error amplifier at the high frequency, so noise no longer scales with the output voltage. This improvement is more noticeable with higher output voltages, because loop gain reduction is greatest. A suitable CBYPASS is calculated as shown in Equation 1:

f(CBYPASS) 200 Hz

$$\rightarrow$$

CBYPASS =  $\frac{1}{2u \times R1 \times 200 \text{HZ}}$  (1)

On the 3-pin LP2950, noise reduction can be achieved by increasing the output capacitor, which causes the regulator bandwidth to be reduced, therefore, eliminating high-frequency noise. However, this method is relatively inefficient, as increasing COUT from  $1\mu$ F to  $220\mu$ F only reduces the regulator 'soutput noise from  $430\mu$ V to  $160\mu$ V (over a 100-kHz bandwidth)

# ERROR Function (LP2951 Only)

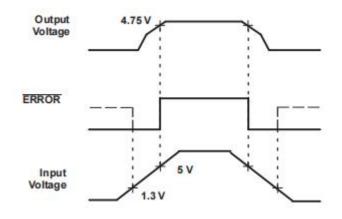

The LP2951 has a low-voltage detection comparator that outputs a logic low when the output voltage drops by $\approx$ 6% from its nominal value, and outputs a logic high when VOUT has reached  $\approx$ 95% of its nominal value. This 95% of nominal figure is obtained by dividing the built-in offset of  $\approx$ 60 mV by the 1.235-V bandgap reference, and remains independent of the programmed output voltage. For example, the trip-point threshold (ERROR output goes high) typically is 4.75 V for a 5-V output and 11.4 V for a 12-V output. Typically, there is a hysteresis of 15 mV between the thresholds for high and low ERROR output.

A timing diagram is shown in Figure 1 for ERROR vs VOUT (5 V), as VIN is ramped up and down. ERROR becomes valid (low) when VIN $\approx$ 1.3 V. When VIN $\approx$ 5 V, VOUT = 4.75 V, causing ERROR to go high. Because the dropout voltage is load dependent, the output trip-point threshold is reached at different values of VIN, depending on the load current. For instance, at higher load current, ERROR goes high at a slightly higher value of VIN, and vice versa for lower load current. The output-voltage trip point remains at  $\approx$ 4.75 V, regardless of the load. Note that when VIN $\leq$ 1.3 V, the ERROR comparator output is turned off and pulled high to its pullup voltage. If VOUT is used as the pullup voltage, rather than an external 5-V source, ERROR typically is  $\leq$ 1.2 V. In this condition, an equal resistor divider (10 k $\Omega$  is suitable) can be tied to ERROR to divide down the voltage to a valid logic low during any fault condition, while still enabling a logic high during normal operation.

# **APPLICATION INFORMATION (continued)**

Figure 1. ERROR Output Timing

Because the ERROR comparator has an open-collector output, an external pullup resistor is required to pull the output up to VOUT or another supply voltage (up to 30 V). The output of the comparator is rated to sink up to 400  $\mu$ A. A suitable range of values for the pullup resistor is from 100 k $\Omega$  to 1 M $\Omega$ . If ERROR is not used, it can be left open.

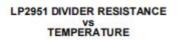

#### Programming Output Voltage (LP2951 Only)

A unique feature of the LP2951 is its ability to output either a fixed voltage or an adjustable voltage, depending on the external pin connections. To output the internally programmed fixed voltage, tie the SENSE pin to the OUTPUT pin and the FEEDBACK pin to the VTAP pin. Alternatively, a user-programmable voltage ranging from the internal 1.235-V reference to a 30-V max can be set by using an external resistor divider pair. The resistor divider is tied to VOUT, and the divided-down voltage is tied directly to FEEDBACK for comparison against the internal 1.235-V reference. To satisfy the steady-state condition in which its two inputs are equal, the error amplifier drives the output to equal Equation 2:

$V_{OUT} = VREF \times (1 + \frac{R1}{R2}) - IFBR1$  (2)

Where:

VREF = 1.235 V applied across R2

IFB = FEEDBACK bias current, typically 20 nA

A minimum regulator output current of 1  $\propto$ A must be maintained. Thus, in an application where a no-load condition is expected (for example, CMOS circuits in standby), this 1- $\propto$ A minimum current must be provided by the resistor pair, effectively imposing a maximum value of R2 = 1.2 M $\Omega$  (1.235 V/1.2 M $\Omega \approx$  1  $\mu$ A).

IFB = 20 nA introduces an error of  $\approx$ 0.02% in Vout. This can be offset by trimming R1. Alternatively, increasing the divider current makes IFB less significant, thus, reducing its error contribution. For instance, using R2 = 100 k $\Omega$  reduces the error contribution of IFB to 0.17% by increasing the divider current to  $\approx$ 12 µA. This increase in the divider current still is small compared to the 600- $\infty$ A typical quiescent current of the LP2951 under no load.

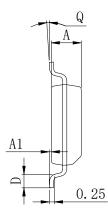

# **Physical Dimensions**

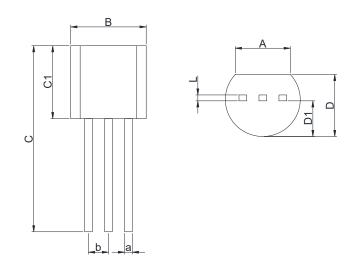

TO-92

| Dimensions In Millimeters(TO-92) |      |      |      |      |      |      |      |      |         |  |

|----------------------------------|------|------|------|------|------|------|------|------|---------|--|

| Symbol:                          | A    | В    | С    | C1   | D    | D1   | L    | а    | b       |  |

| Min:                             | 3.43 | 4.44 | 11.2 | 4.32 | 3.17 | 2.03 | 0.33 | 0.40 | 1 27050 |  |

| Max:                             | 3.83 | 5.21 | 12.7 | 5.34 | 4.19 | 2.67 | 0.42 | 0.52 | 1.27BSC |  |

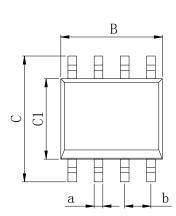

SOP8 (150mil)

| Dimensions In Millimeters(SOP8) |      |      |      |      |      |      |    |      |          |  |

|---------------------------------|------|------|------|------|------|------|----|------|----------|--|

| Symbol:                         | A    | A1   | В    | С    | C1   | D    | Q  | а    | b        |  |

| Min:                            | 1.35 | 0.05 | 4.90 | 5.80 | 3.80 | 0.40 | 0° | 0.35 | 1.07.000 |  |

| Max:                            | 1.55 | 0.20 | 5.10 | 6.20 | 4.00 | 0.80 | 8° | 0.45 | 1.27 BSC |  |

#### **IMPORTANT STATEMENT:**

Hanschip Semiconductor reserves the right to change its products and services without notice. Before ordering, the customer shall obtain the latest relevant information and verify whether the information is up to date and complete. Hanschip Semiconductor does not assume any responsibility or obligation for the altered documents.

Customers are responsible for complying with safety standards and taking safety measures when using Hanschip Semiconductor products for system design and machine manufacturing. You will bear all the following responsibilities: select the appropriate Hanschip Semiconductor products for your application; Design, validate and test your application; Ensure that your application meets the appropriate standards and any other safety, security or other requirements. To avoid the occurrence of potential risks that may lead to personal injury or property loss.

Hanschip Semiconductor products have not been approved for applications in life support, military, aerospace and other fields, and Hanschip Semiconductor will not bear the consequences caused by the application of products in these fields.

The technical and reliability data (including data sheets), design resources (including reference designs), application or other design suggestions, network tools, safety information and other resources provided for the performance of semiconductor products produced by Hanschip Semiconductor are not guaranteed to be free from defects and no warranty, express or implied, is made. The use of testing and other quality control technologies is limited to the quality assurance scope of Hanschip Semiconductor. Not all parameters of each device need to be tested.

The documentation of Hanschip Semiconductor authorizes you to use these resources only for developing the application of the product described in this document. You have no right to use any other Hanschip Semiconductor intellectual property rights or any third party intellectual property rights. It is strictly forbidden to make other copies or displays of these resources. You should fully compensate Hanschip Semiconductor and its agents for any claims, damages, costs, losses and debts caused by the use of these resources. Hanschip Semiconductor accepts no liability for any loss or damage caused by infringement.