### Differential Bus Transceivers

#### **DESCRIPTION**

The HT65176 and HT75176 differential bus transceivers are integrated circuits designed for bidirectional data communication on multipoint bus transmission lines. They are designed for balanced transmission lines and meet ANSI Standards TIA/EIA-422-B and TIA/EIA-485-A and ITU Recommendations V.11 and X.27.

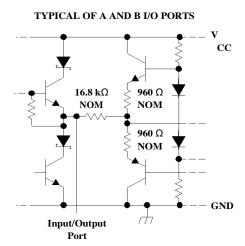

The HT65176 and HT75176 devices combine a 3-state differential line driver and a differential input line receiver, both of which operate from a single 5-V power supply. The driver and receiver have active-high and active-low enables, respectively, that can be connected together externally to function as a direction control. The driver differential outputs and the receiver differential inputs are connected internally to form differential input/output (I/O) bus ports that are designed to offer minimum loading to the bus when the driver is disabled or  $V_{\rm CC}=0$ . These ports feature wide positive and negative common-mode voltage ranges, making the device suitable for party-line applications.

The driver is designed for up to 60 mA of sink or source current. The driver features positive and negative current limiting and thermal shutdown for protection from line-fault conditions. Thermal shutdown is designed to occur at a junction temperature of approximately 150°C. The receiver features a minimum input impedance of 12 k $\Omega$ , an input sensitivity of  $\pm 200$  mV, and a typical input hysteresis of 50 mV.

#### **FEATURES**

- · Bidirectional Transceivers

- Meet or Exceed the Requirements of ANSI Standards TIA/EIA-422-B and TIA/EIA-485 and ITU Recommendations V.11 and X.27

- Designed for Multipoint Transmission on Long Bus Lines in Noisy Environments

- · 3-State Driver and Receiver Outputs

- Individual Driver and Receiver Enables

- Wide Positive and Negative Input/Output Bus Voltage Ranges

- ± 60-mA Max Driver Output Capability

- · Thermal Shutdown Protection

- Driver Positive and Negative Current Limiting

- 12-kΩ Min Receiver Input Impedance

- ± 200-mV Receiver Input Sensitivity

- 50-mV Typ Receiver Input Hysteresis

- Operate From Single 5-V Supply

DFN-8\* D SUFFIX HT65176ARDZ HT75176ARDZ

MSOP-8 M SUFFIX HT65176ARMZ HT75176ARMZ

SOP-8 R SUFFIX HT65176ARZ HT75176ARZ

DIP-8\* D SUFFIX HT65176ANZ HT75176ANZ

NOTE: suffix A is version, suffix R is roll tape, suffix Z environmental protection.

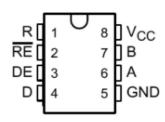

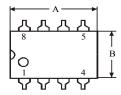

#### **PIN CONFIGURATIONS**

#### **Function Tables**

Driver (1)

|       | <b>2</b> 11101 (1) |     |      |

|-------|--------------------|-----|------|

| INPUT | ENABLE             | OUT | PUTS |

| D     | DE                 | Α   | В    |

| Н     | Н                  | Н   | L    |

| L     | Н                  | L   | Н    |

| X     | L                  | Z   | Z    |

(1) H = high level, L = low level, ? = indeterminate, X = irrelevant,

Z = high impedance (off)

## Receiver<sup>(1)</sup>

| DIFFERENTIAL<br>INPUTS<br>A-B    | EN <u>AB</u> LE<br>RE | OUTPUT<br>R |

|----------------------------------|-----------------------|-------------|

| V <sub>ID</sub> ≥ 0.2 V          | L                     | Н           |

| -0.2 V < V <sub>ID</sub> < 0.2 V | L                     | ?           |

| V <sub>ID</sub> ≤ -0.2 V         | L                     | L           |

| X                                | Н                     | Z           |

| Open                             | L                     | ?           |

(1) H = high level, L = low level, ? = indeterminate,

X = irrelevant, Z = high impedance (off)

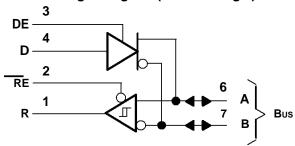

#### **Logic Diagram (Positive Logic)**

# HT65176,HT75176

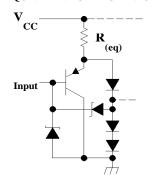

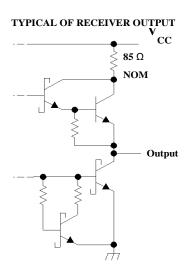

#### EQUIVALENT OF EACH INPUT

Driver input:  $R(eq) = 3 \text{ k}\Omega \text{ NOM}$ Enable inputs:  $R(eq) = 8 \text{ k}\Omega \text{ NOM}$

R(eq) = Equivalent Resistor

## HT65176,HT75176

#### **Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted) (1)

|                           |                                                              |                       | MIN | MAX | UNIT |

|---------------------------|--------------------------------------------------------------|-----------------------|-----|-----|------|

| V                         | Supply voltage <sup>(2)</sup>                                | (2)                   |     | 7   | V    |

|                           | Voltage range at any bus terminal                            | e at any bus terminal |     | 15  | V    |

| ٧ı                        | Enable input voltage                                         |                       |     | 5.5 | V    |

|                           |                                                              | D package             |     | 97  |      |

| $\theta_{_{\mathrm{JA}}}$ | Package thermal impedance (3)(4)                             | P package             |     | 85  | °C/W |

|                           |                                                              | PS package            |     | 95  |      |

| TJ                        | Operating virtual junction temperature                       |                       |     | 150 | °C   |

|                           | Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds |                       |     | 260 | °C   |

| stg                       | Storage temperature range                                    |                       | -65 | 150 | °C   |

- (1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

- All voltage values, except differential input/output bus voltage, are with respect to network ground terminal.

- Maximum power dissipation is a function of  $T_{J(max)}$ ,  $\theta_{JA}$ , and  $T_A$ . The maximum allowable power dissipation at any allowable ambient temperature is  $P_D = (T_{J(max)} - T_A) / \theta_{JA}. \ \, \text{Operating at the absolute maximum T}_J \ \, \text{of } 150^{\circ}\text{C} \ \, \text{can affect reliability}.$  The package thermal impedance is calculated in accordance with JESD 51-7.

#### **Recommended Operating Conditions**

|           |                                                         |               | MIN  | TYP | MAX  | UNIT |

|-----------|---------------------------------------------------------|---------------|------|-----|------|------|

| CC        | Supply voltage                                          |               | 4.75 | 5   | 5.25 | V    |

| VI or VIC | Voltage at any bus terminal (separately or common mode) |               |      |     | 12   | V    |

| V<br>IH   | High-level input voltage                                | D, DE, and RE | 2    |     | -7   | V    |

| V<br>IL   | Low-level input voltage                                 | D, DE, and RE |      |     | 0.8  | V    |

| V         | Differential input voltage (1)                          |               |      |     | ±12  | V    |

|           |                                                         | Driver        |      |     | -60  | mA   |

| ОН        | High-level output current                               | Receiver      |      |     | -400 | μΑ   |

|           |                                                         | Driver        |      |     | 60   |      |

| OL        | Low-level output current                                | Receiver      |      |     | 8    | mA   |

|           |                                                         | HT65176       | -40  |     | 105  |      |

| TA        | Operating free-air temperature                          | HT75176       | 0    |     | 70   | °C   |

<sup>(1)</sup> Differential input/output bus voltage is measured at the noninverting terminal A, with respect to the inverting terminal B.

#### **Driver Section**

#### **Electrical Characteristics**

over recommended ranges of supply voltage and operating free-air temperature (unless otherwise noted)

|                  | PARAMETER                                             | TEST CON                                  | DITIONS <sup>(1)</sup>                       | MIN            | TYP(2) | MAX       | UNIT |

|------------------|-------------------------------------------------------|-------------------------------------------|----------------------------------------------|----------------|--------|-----------|------|

| V<br>IK          | Input clamp voltage                                   | $I_{I} = -18 \text{ mA}$                  |                                              |                |        | -1.5      | V    |

| VO               | Output voltage                                        | IO = 0                                    |                                              | 0              |        | 6         | V    |

| VOD1             | Differential output voltage                           | IO = 0                                    |                                              | 1.5            | 3.6    | 6         | V    |

|                  |                                                       | $R_{L} = 100 \Omega$ , see Figure         | 9 1                                          | 1/2 V or 2 (3) |        |           |      |

| VOD2             | Differential output voltage                           | $R_L$ = 54 Ω, see Figure                  | 1                                            | 1.5            | 2.5    | 5         | V    |

| V <sub>OD3</sub> | Differential output voltage                           | See <sup>(4)</sup>                        |                                              | 1.5            |        | 5         | V    |

| 050              | Change in magnitude of                                |                                           |                                              |                |        |           |      |

| $\Delta  VOD $   | differential output voltage <sup>(5)</sup>            | $R_L$ = 54 $\Omega$ or 100 $\Omega$ , s   | ee Figure 1                                  |                |        | ±0.2      | V    |

| V                | Common-mode output voltage                            | RL = 54 $\Omega$ or 100 $\Omega$ , s      | ee Figure 1                                  |                |        | +3<br>–1  | V    |

| Δ VOC            | Change in magnitude of common-mode output voltage (3) | $R_L$ = 54 $\Omega$ or 100 $\Omega$ , see | Figure 1                                     |                |        | ±0.2      | V    |

| 0                | Output current                                        | Output disabled <sup>(6)</sup>            | $V_O = 12 \text{ V}$<br>$V_O = -7 \text{ V}$ |                |        | 1<br>-0.8 | mA   |

| IH IH            | High-level input current                              | V <sub>I</sub> = 2.4 V                    |                                              |                |        | 20        | μA   |

| IL.              | Low-level input current                               | VI = 0.4 V                                |                                              |                |        | -400      | μA   |

|                  |                                                       | V <sub>O</sub> = -7 V                     |                                              |                |        | -250      |      |

| lı               |                                                       | VO = 0                                    |                                              |                |        | -150      |      |

| os               | Short-circuit output current                          | O CC                                      |                                              |                |        | 250       | mA   |

|                  |                                                       | V <sub>O</sub> = 12 V                     |                                              |                |        | 250       |      |

| 1                |                                                       |                                           | Outputs enabled                              |                | 42     | 70        |      |

| CC               | Supply current (total package)                        | No load                                   | Outputs disabled                             | ·              | 26     | 35        | mA   |

<sup>(1)</sup> The power-off measurement in ANSI Standard TIA/EIA-422-B applies to disabled outputs only and is not applied to combined inputs and

- (2) All typical values are at V<sub>CC</sub> = 5 V and T<sub>A</sub> = 25°C.

(3) The minimum V<sub>OD2</sub> with a 100-Ω load is either 1/2 V<sub>OD1</sub> or 2 V, whichever is greater.

(4) See ANSI Standard TIA/EIA-485-A, Figure 3.5, Test Termination Measurement 2.

- (5) |VOD| and |VOC| are the changes in magnitude of VOD and VOC, respectively, that occur when the input is changed from a high level to a low level.

- (6) This applies for both power on and off; refer to ANSI Standard TIA/EIA-485-A for exact conditions. The TIA/EIA-422-B limit does not apply for a combined driver and receiver terminal.

#### **Switching Characteristics**

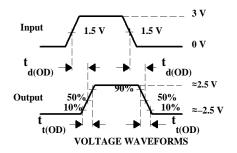

$V_{CC} = 5 \text{ V}, R_L = 110 \Omega, T_A = 25^{\circ}\text{C}$  (unless otherwise noted)

|       | PARAMETER                           | TEST CONDITIONS                  | MIN TYP | MAX | UNIT |

|-------|-------------------------------------|----------------------------------|---------|-----|------|

| d(OD) | Differential-output delay time      | $R_L = 54 \Omega$ , see Figure 3 | 15      | 22  | ns   |

| t(OD) | Differential-output transition time | $R_L = 54 \Omega$ , see Figure 3 | 20      | 30  | ns   |

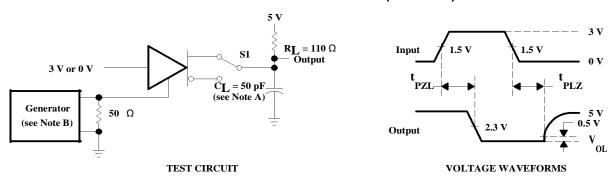

| PZH   | Output enable time to high level    | See Figure 4                     | 85      | 120 | ns   |

| PZL   | Output enable time to low level     | See Figure 5                     | 40      | 60  | ns   |

| PHZ   | Output disable time from high level | See Figure 4                     | 150     | 250 | ns   |

| PLZ   | Output disable time from low level  | See Figure 5                     | 20      | 30  | ns   |

#### **Symbol Equivalents**

| DATA SHEET<br>PARAMETER | TIA/EIA-422-B                       | TIA/EIA-485-A                                   |

|-------------------------|-------------------------------------|-------------------------------------------------|

| Vo                      | v , v<br>oa ob                      | v , v<br>oa ob                                  |

| VOD1                    | 0                                   | 0                                               |

| OD2                     | $V_t (R_L = 100 \Omega)$            | $V_t (R_L = 54 \Omega)$                         |

| VOD3                    |                                     | V <sub>t</sub> (test termination measurement 2) |

| Δ V <sub>OD</sub>       | V <sub>t</sub>                      | V <sub>t</sub> -   <del>V</del> t               |

| OC                      | V <sub>os</sub>                     | V <sub>0S</sub>                                 |

| ∆ VOC                   | V <sub>OS</sub> - V <sub>os</sub>   | V <sub>OS</sub> -V <sub>os</sub>                |

| OS                      | I <sub>sa</sub>  ,  I <sub>sb</sub> |                                                 |

| lo                      | I <sub>xa</sub>  ,  I <sub>xb</sub> | ia ib                                           |

#### **Receiver Section Electrical Characteristics**

over recommended ranges of common-mode input voltage, supply voltage, and operating free-air temperature (unless otherwise noted)

|                  | PARAMETER                              | TEST C                                              | ONDITIONS             | MIN TYP(1)          | MAX  | UNIT |

|------------------|----------------------------------------|-----------------------------------------------------|-----------------------|---------------------|------|------|

| V<br>IT+         | Positive-going input threshold voltage | $V_0 = 2.7 \text{ V}, I_0 = -0.4 \text{ mA}$        |                       |                     | 0.2  | V    |

| V <sub>II-</sub> | Negative-going input threshold voltage | V = 0.5 V, I = 8 mA                                 |                       | -0.2 <sup>(2)</sup> |      | V    |

| V<br>hys         | Input hysteresis voltage (VIT+ - VIT-) |                                                     |                       | 50                  |      | mV   |

| V<br>IK          | Enable Input clamp voltage             | II = -18 mA                                         |                       |                     | -1.5 | V    |

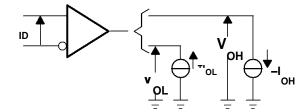

| OH               | High-level output voltage              | $V_{ID} = 200 \text{ mV}, I_{OH} = -400 \text{ mV}$ | ) μA, see Figure 2    | 2.7                 |      | V    |

| V<br>OL          | Low-level output voltage               | $V_{ID} = -200 \text{ mV}, I_{OL} = 8 \text{ m}$    | A, see Figure 2       |                     | 0.45 | V    |

| OZ               | High-impedance-state output current    | Vo = 0.4 V to 2.4 V                                 |                       |                     | ±20  | μΑ   |

|                  | Line input current                     | Other input = 0 V <sup>(3)</sup>                    | V <sub>I</sub> = 12 V |                     | 1    | mΑ   |

| i                | Zine inpat carrent                     | , , , , , , , , , , , , , , , , , , ,               | $V_I = -7 V$          |                     | -0.8 |      |

| ı<br>IH          | High-level enable input current        | VIH = 2.7 V                                         |                       |                     | 20   | μA   |

| IL.              | Low-level enable input current         | VIL = 0.4 V                                         |                       |                     | -100 | μΑ   |

| rį               | Input resistance                       | V <sub>I</sub> = 12 V                               |                       | 12                  |      | kΩ   |

| OS               | Short-circuit output current           |                                                     |                       | -15                 | -85  | mA   |

| I                | _                                      |                                                     | Outputs enabled       | 42                  | 55   |      |

| CC               | Supply current (total package)         | No load                                             | Outputs disabled      | 26                  | 35   | mA   |

- (1) All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C.

(2) The algebraic convention, in which the less positive (more negative) limit is designated minimum, is used in this data sheet for common-

- mode input voltage and threshold voltage levels only.

This applies for both power on and power off. Refer to EIA Standard TIA/EIA-485-A for exact conditions.

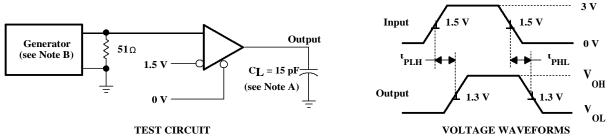

#### **Switching Characteristics**

$V_{CC} = 5 \text{ V} \cdot \text{Cu} = 15 \text{ nF} \cdot \text{Ta} = 25^{\circ}\text{C}$

| <u> </u> | : 5 V, C[ = 15 pr, 1A = 25 C                      |                                          |     |     |     |      |

|----------|---------------------------------------------------|------------------------------------------|-----|-----|-----|------|

|          | PARAMETER                                         | TEST CONDITIONS                          | MIN | TYP | MAX | UNIT |

| PLH      | Propagation delay time, low- to high-level output | V 04-0V                                  |     | 21  | 35  | ns   |

| PHL      | Propagation delay time, high- to low-level output | V <sub>ID</sub> = 0 to 3 V, see Figure 6 |     | 23  | 35  | 115  |

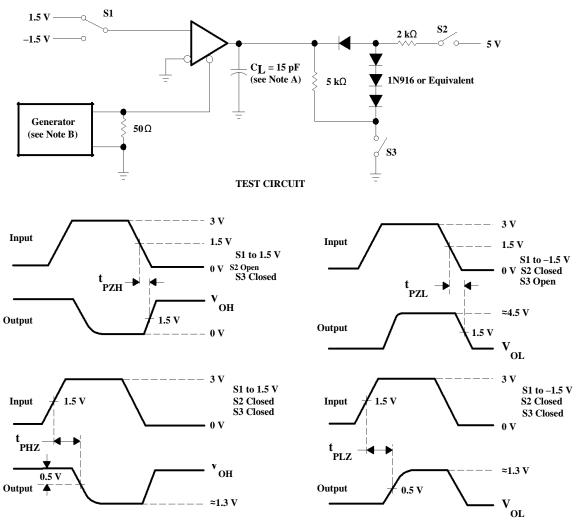

| PZH      | Output enable time to high level                  | See Figure 7                             |     | 10  | 20  | nc   |

| PZL      | Output enable time to low level                   | See Figure 7                             |     | 12  | 20  | ns   |

| PHZ      | Output disable time from high level               | On a Firmura 7                           |     | 20  | 35  | ns   |

| ι<br>PLZ | Output disable time from low level                | See Figure 7                             |     | 17  | 25  | 115  |

#### **Parameter Measurement Information**

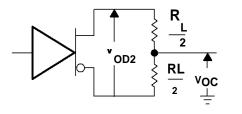

Figure 1. Driver  $V_{\mbox{\scriptsize OD}}$  and  $V_{\mbox{\scriptsize OC}}$

Figure 2. Receiver VOH and VOL

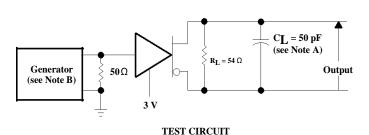

- A. CL includes probe and jig capacitance.

- B. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$ 1 MHz, 50% duty cycle,  $t_f \leq$  6 ns,  $t_f \leq$  6 ns,  $Z_Q = 50 \ \Omega$ .

Figure 3. Driver Test Circuit and Voltage Waveforms

- A. CL includes probe and jig capacitance.

- B. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$ 1 MHz, 50% duty cycle,  $t_r \leq$  6 ns,  $t_f \leq$  6 ns,  $Z_O = 50 \ \Omega$ .

Figure 4. Driver Test Circuit and Voltage Waveforms

#### **Parameter Measurement Information (continued)**

- A. C<sub>L</sub> includes probe and jig capacitance.

- B. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$ 1 MHz, 50% duty cycle,  $t_f \leq$  6 ns,  $t_f \leq$  6 ns,  $Z_O = 50 \Omega$ .

Figure 5. Driver Test Circuit and Voltage Waveforms

- A. C<sub>L</sub> includes probe and jig capacitance.

- B. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$ 1 MHz, 50% duty cycle,  $t_f \leq$  6 ns,  $t_f \leq$  6 ns,  $Z_O = 50 \Omega$ .

Figure 6. Receiver Test Circuit and Voltage Waveforms

#### **Parameter Measurement Information (continued)**

#### VOLTAGE WAVEFORMS

- A.  $C_L$  includes probe and jig capacitance.

- B. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$ 1 MHz, 50% duty cycle,  $t_r \leq$  6 ns,  $t_f \leq$  6 ns,  $Z_O =$  50  $\Omega$ .

Figure 7. Receiver Test Circuit and Voltage Waveforms

#### **Typical Characteristics**

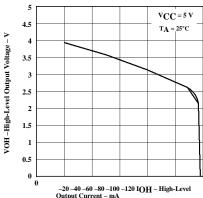

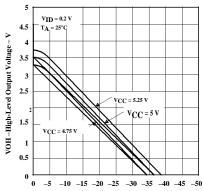

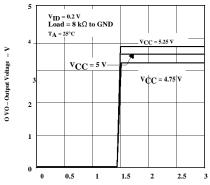

0 -20 -40 -60 -80 -100 -120 IOH - High-Level Output Current - mA Figure 8. Driver High-Level Output Voltage vs High-Level Output Current

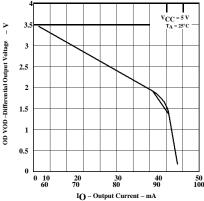

Figure 10. Driver Differential Output Voltage

vs

Output Current

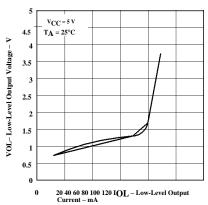

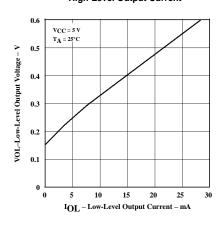

Figure 9. Driver Low-Level Output Voltage

vs

Low-Level Output Current

IOH – High-Level Output Current – mA

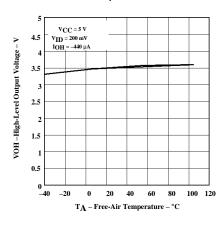

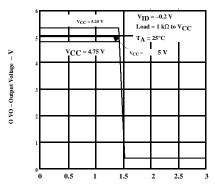

Figure 11. Receiver High-Level Output Voltage

VS

High-Level Output Current

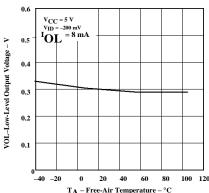

#### **Typical Characteristics (continued)**

TA - Free-Air Temperature - °C

Figure 14. Receiver Low-Level Output Voltage vs

Free-Air Temperature

V<sub>I</sub> - Enable Voltage - V Figure 15. Receiver Output Voltage Vs Enable Voltage

V<sub>I</sub> – Enable Voltage – V Figure 16. Receiver Output Voltage VS Enable Voltage

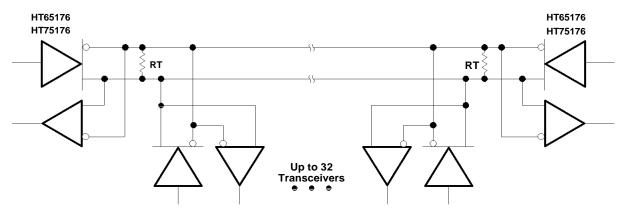

#### **APPLICATION INFORMATION**

The line should be terminated at both ends in its characteristic impedance (RT = ZO). Stub lengths off the main line should be kept as short as possible.

Figure 17. Typical Application Circuit

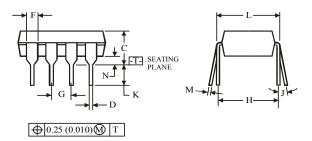

(DIP8)

#### NOTES:

1. Dimensions "A", "B" do not include mold flash or protrusions.

Maximum mold flash or protrusions 0.25 mm (0.010) per side.

|        | Dimension, mm |      |  |

|--------|---------------|------|--|

| Symbol | MIN           | MAX  |  |

| A      | 8.51 10.16    |      |  |

| В      | 6.1 7.11      |      |  |

| C      |               | 5.33 |  |

| D      | 0.36          | 0.56 |  |

| F      | 1.14          | 1.78 |  |

| G      | 2             | 54   |  |

| Н      | 7.            | 62   |  |

| J      | 0°            | 10°  |  |

| K      | 2.92          | 3.81 |  |

| L      | 7.62          | 8.26 |  |

| M      | 0.2 0.36      |      |  |

| N      | 0.38          |      |  |

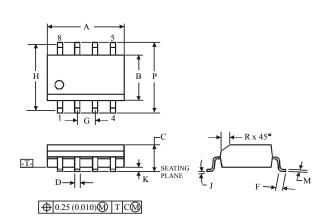

(SOP8)

#### NOTES:

- 1. Dimensions A and B do not include mold flash or protrusion.

- 2. Maximum mold flash or protrusion 0.15 mm (0.006) per side for A; for B 0.25 mm (0.010) per side.

|        | Dimens    | ion, mm |  |

|--------|-----------|---------|--|

| Symbol | MIN       | MAX     |  |

| A      | 4.8       | 5       |  |

| В      | 3.8       | 4       |  |

| C      | 1.35      | 1.75    |  |

| D      | 0.33 0.51 |         |  |

| F      | 0.4 1.27  |         |  |

| G      | 1.3       | 27      |  |

| Н      | 5.        | 72      |  |

| J      | 0°        | 8°      |  |

| K      | 0.1       | 0.25    |  |

| M      | 0.19      | 0.25    |  |

| P      | 5.8 6.2   |         |  |

| R      | 0.25      | 0.5     |  |