# Ultra-Low-EMI, RNS, Mono, Filter-Free, Class-D Audio Amplifier

## **Features**

- EEE Function, Greatly reduces EMI over the full bandwidth

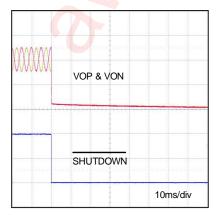

- Excellent Pop-Click Suppression

- RNS (RF-TDD Noise Suppression)

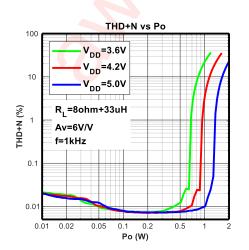

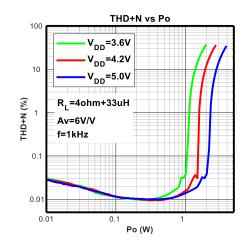

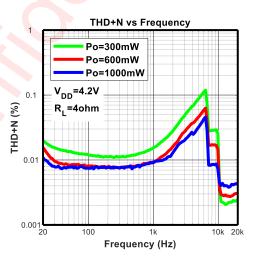

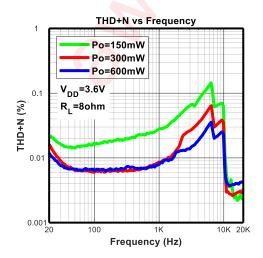

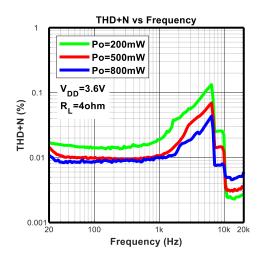

- 0.008%THD+N (Pout=0.4W,V<sub>DD</sub>=4.2V)

- Filter-Free Class-D Architecture

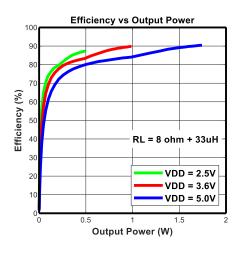

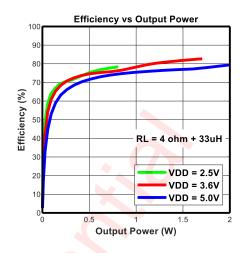

- Up to 90% Efficiency

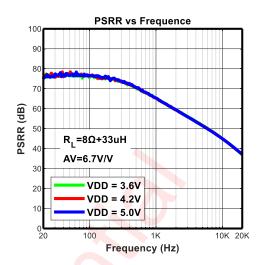

- High PSRR (75dB at 217Hz)

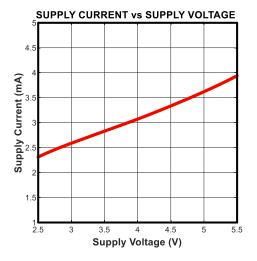

- Low Quiescent Current (2.8mA)

- Low Shutdown Current (<0.1μA)

- Power Supply Range: 2.5V~5.5V

- Over-Current Protection

- Over-Temperature Protection

- Small FCQFN 1.5mmX1.5mm-9L Package

- RoHS compliant, lead-free packages

## **Applications**

- Cellular Phones

- MP3/PMP

- GPS

- Digital Photo Frame

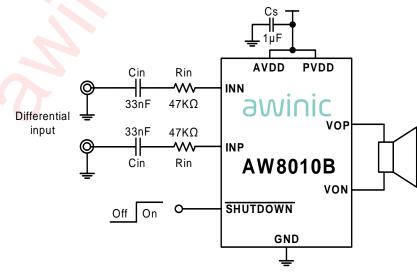

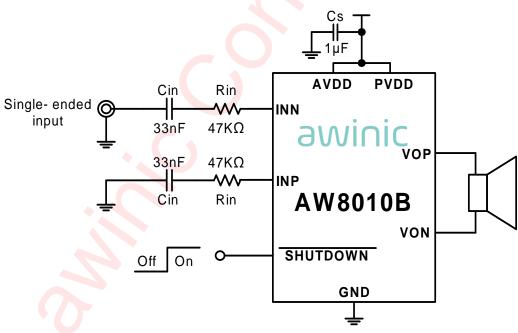

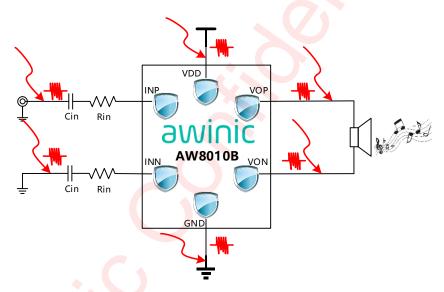

# **Typical Application Circuits**

## **General Description**

The AW8010B is a ultra-low-EMI,RNS, mono, filter-free, Class-D audio amplifier. Unique RNS, which effectively reduces RF energy, attenuate the RF TDD-noise, an acceptable audible level to the customer.

The AW8010B features the EEE (Enhanced Emission Elimination) function which greatly reduces EMI over the full bandwidth. The AW8010B achieves better than 20dB margin under FCC limits with 24 inch of cable.

The filter-free PWM architecture and internal gain setting reduces external components count, board area consumption, system cost and simplifies the design. In addition, The AW8010B offers efficiencies above 90%. The over-current and over-temperature is prepared inside of the device.

The AW8010B is available in an ultra small FCQFN 1.5mmX1.5mmX0.55mm-9L package. The AW8010B is specified over the industrial temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C.

Figure 1 AW8010B Application Schematic With Differential Input

1

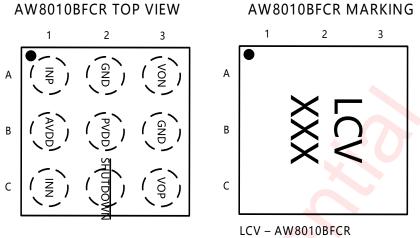

# **Pin Configuration And Top Mark**

awinic

XXX – Production Tracing Code

#### Figure 2 Pin Configuration and Top Mark of AW8010B

## **Pin Definition**

| No. | NAME     | DESCRIPTION           |

|-----|----------|-----------------------|

| A1  | INP      | Positive audio input  |

| A2  | GND      | Ground                |

| A3  | VON      | Negative audio output |

| B1  | AVDD     | Power Supply          |

| B2  | PVDD     | Power Supply          |

| B3  | GND      | Ground                |

| C1  | INN      | Negative audio input  |

| C2  | SHUTDOWN | Shutdown pin          |

| C3  | VOP      | Positive audio output |

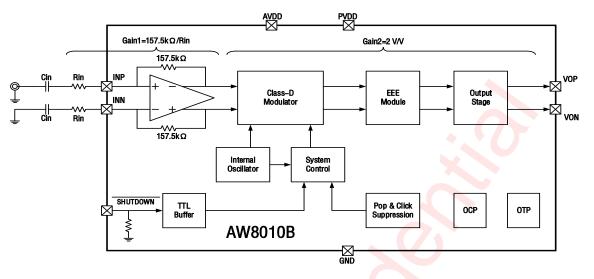

# **Functional Block Diagram**

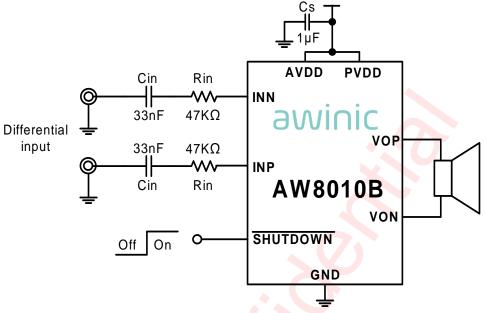

# **Typical Application Circuits**

awinic

Figure 4 AW8010B Application Schematic With Differential Input

## **Ordering Information**

awinic

| Part Number | r Temperature Package |                                    | ature Package Marking Moisture<br>Sensitivity Level |      | Environmental<br>Information | Delivery Form                |

|-------------|-----------------------|------------------------------------|-----------------------------------------------------|------|------------------------------|------------------------------|

| AW8010BFCR  | -40°C∼85°C            | FCQFN<br>1.5mm×1.5mm×<br>0.55mm-9L | LCV                                                 | MSL3 | ROHS+HF                      | 3000 units/<br>Tape and Reel |

# Absolute Maximum Ratings(NOTE1)

| PARAMETERS                                               | RANGE                          |  |  |  |  |  |

|----------------------------------------------------------|--------------------------------|--|--|--|--|--|

| Supply voltage range V <sub>DD</sub>                     | -0.3V to 6V                    |  |  |  |  |  |

| Input voltage range                                      | -0.3V to V <sub>DD</sub> +0.3V |  |  |  |  |  |

| Junction-to-ambient thermal resistance $\theta_{JA}$     | 90°C/W                         |  |  |  |  |  |

| Operating free-air temperature range                     | -40°C to 85°C                  |  |  |  |  |  |

| Maximum operating junction temperature T <sub>JMAX</sub> | 125°C                          |  |  |  |  |  |

| Storage temperature T <sub>STG</sub>                     | -65°C to 150°C                 |  |  |  |  |  |

| Lead temperature (soldering 10 seconds)                  | 260°C                          |  |  |  |  |  |

| ESD(Including CDM HBM MM                                 | Λ) <sup>(NOTE 2)</sup>         |  |  |  |  |  |

| HBM (human body m <mark>o</mark> del)                    | ±2kV                           |  |  |  |  |  |

| CDM (charged-device model)                               | ±1.5kV                         |  |  |  |  |  |

| Latch-Up                                                 |                                |  |  |  |  |  |

| Test condition:                                          | +IT: 200mA                     |  |  |  |  |  |

| JESD78E                                                  | -IT: -200mA                    |  |  |  |  |  |

|                                                          |                                |  |  |  |  |  |

NOTE1: Conditions out of those ranges listed in "absolute maximum ratings" may cause permanent damages to the device. In spite of the limits above, functional operation conditions of the device should within the ranges listed in "recommended operating conditions". Exposure to absolute-maximum-rated conditions for prolonged periods may affect device reliability.

NOTE2: The human body model is a 100pF capacitor discharged through a  $1.5k\Omega$  resistor into each pin. Test method: ESDA/JEDEC JS-001-2017

Test method of the charged-device model: ESDA/JEDEC JS-002-2018

# **Electrical Characteristics**

#### Test Condition: V<sub>DD</sub>=3.6V ,T<sub>A</sub>=25°C, R<sub>L</sub>=8Ω+33uH, Cin=33nF, f=1kHz (Unless otherwise specified)

|                  | Parameter                                                                  | Conditions                                                              | Min   | Тур                 | Мах  | Units |

|------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------|-------|---------------------|------|-------|

| Electric         | al Characteristics                                                         |                                                                         |       |                     |      |       |

| VDD              | Power voltage                                                              |                                                                         | 2.5   |                     | 5.5  | V     |

| V <sub>IH</sub>  | High-level input voltage                                                   |                                                                         | 1.3   |                     | VDD  | V     |

| VIL              | Low-level input voltage                                                    |                                                                         | 0     |                     | 0.35 | V     |

| Vos              | Output offset voltage                                                      | V <sub>IN</sub> =0V                                                     | -25   |                     | 25   | mV    |

| lα               | Quiescent current                                                          | V <sub>DD</sub> =3.6V                                                   |       | 2.8                 |      | mA    |

| $I_{SD}$         | Shutdown current                                                           | $V_{DD}$ =3.6V, SHUTDOWN =0V                                            |       | 0.1                 |      | μA    |

| PSRR             | Power supply rejection ratio                                               | 217Hz                                                                   |       | 75                  |      | dB    |

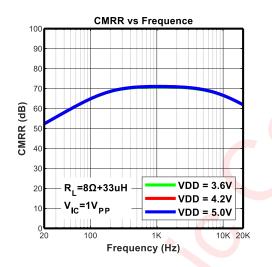

| CMRR             | Common mode rejection ratio                                                |                                                                         |       | 70                  |      | dB    |

| f <sub>sw</sub>  | Switching frequency                                                        | V <sub>DD</sub> =2.5V to 5.5V                                           |       | 800                 |      | kHz   |

| A <sub>V</sub>   | Gain                                                                       |                                                                         |       | <u>315kΩ</u><br>Rin |      |       |

| Operati          | ng Characteristics                                                         |                                                                         |       |                     |      |       |

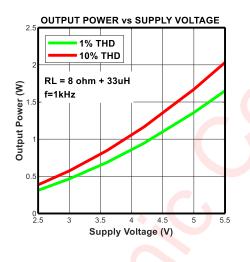

|                  |                                                                            | THD+N=10%, $R_L=4\Omega+33uH$ , $V_{DD}=5V$                             | 2.85  |                     |      | W     |

|                  |                                                                            | THD+N=1%, $R_L=4\Omega+33uH$ , $V_{DD}=5V$                              | 2.31  |                     |      | W     |

|                  |                                                                            | THD+N=10%, $R_L=8\Omega$ +33uH, $V_{DD}=5V$                             | 1.66  |                     |      | W     |

|                  |                                                                            | THD+N=1%,R <mark>L=8Ω+33u</mark> H,V <sub>DD</sub> =5V                  | 1.35  |                     |      | W     |

|                  |                                                                            | THD+N=10%, $R_L=4\Omega+33$ uH, $V_{DD}=4.2V$                           | 1.97  |                     |      | W     |

| _                | Output power                                                               | THD <mark>+</mark> N=1%,R <mark>L</mark> =4Ω+33uH,V <sub>DD</sub> =4.2V |       | 1.60                |      | W     |

| Po               | (NCNOFF mode )                                                             | THD+ <mark>N=10%,R</mark> L=8Ω+33uH,V <sub>DD</sub> =4.2V               |       | 1.16                |      | W     |

|                  |                                                                            | THD+N=1%, $R_L$ =8 $\Omega$ +33uH, $V_{DD}$ =4.2V                       |       | 0.94                |      | W     |

|                  |                                                                            | THD+N=10%, $R_L=4\Omega+33uH$ , $V_{DD}=3.6V$                           |       | 1.41                |      | W     |

|                  |                                                                            | THD+N=1%, $R_L=4\Omega+33uH$ , $V_{DD}=3.6V$                            |       | 1.14                |      | W     |

|                  |                                                                            | THD+N=10%, $R_L=8\Omega+33uH$ , $V_{DD}=3.6V$                           |       | 0.84                |      | W     |

|                  |                                                                            | THD+N=1%, $R_L=8\Omega+33uH$ , $V_{DD}=3.6V$                            | 0.68  |                     | W    |       |

| E <sub>N</sub>   | Output noise Gain=6V/V , 20Hz to 20kHz , input ac grounded, A-weighting 46 |                                                                         |       | μV                  |      |       |

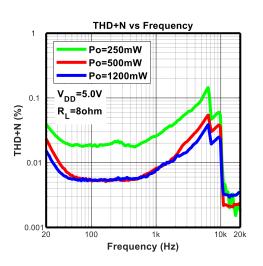

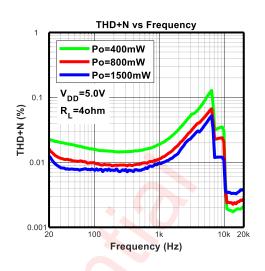

|                  |                                                                            | $V_{DD}=5V$ , Po=0.6W, R <sub>L</sub> =8 $\Omega$ +33uH                 | 0.008 |                     | %    |       |

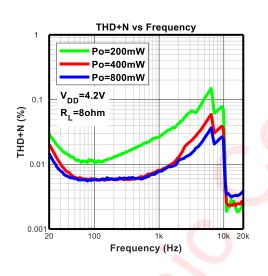

| THD+N            | Total harmonic distortion plus noise                                       | V <sub>DD</sub> =4.2V, Po=0.4W, R <sub>L</sub> =8Ω+33uH                 | 0.008 |                     | %    |       |

|                  |                                                                            | $V_{DD}=3.6V, Po=0.3W, R_{L}=8\Omega+33uH$                              | 0.008 |                     |      | %     |

| η                | Efficiency                                                                 | VDD=5V, Po=1W, R <sub>L</sub> =8Ω+33uH                                  | 85    |                     |      | %     |

| t <sub>s⊤</sub>  | Start-up time                                                              |                                                                         |       | 40                  |      | ms    |

| t <sub>OFF</sub> | Turn-off time                                                              |                                                                         |       | 4                   |      | μs    |

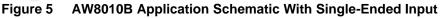

## **MEASUREMENT SETUP**

awinic

AW8010B features switching digital output, as shown in Figure 6. Need to connect a low pass filter to VOP/VON output respectively to filter out switch modulation frequency, then measure the differential output of filter to obtain analog output signal.

Low pass filter uses resistance and capacitor values listed in Table 1.

| Table 1 AW8010B | recommended | values fo | r low pass filter |

|-----------------|-------------|-----------|-------------------|

|                 |             |           |                   |

| R <sub>filter</sub> | Cfilter | Low-pass cutoff frequency |

|---------------------|---------|---------------------------|

| 500Ω                | 10nF    | 32kHz                     |

| 1kΩ                 | 4.7nF   | 34kHz                     |

#### **Output Power Calculation**

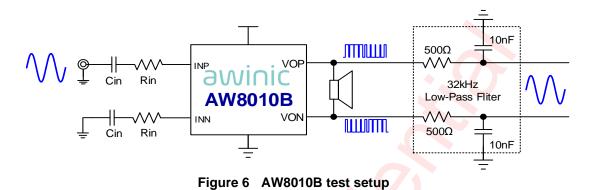

According to the above test methods, the differential analog output signal is obtained at the output of the low pass filter. The valid values Vo\_rms of the differential signal as shown below:

Figure 7 Valid value of AW8010B output signal

The power calculation of Speaker is as follows:

$$P_{L} = \frac{(Vo \_ rms)^{2}}{R_{L}} \qquad (R_{L}: \text{ load impedance of the speaker })$$

# **Typical Characteristics**

awinic

3.5 1% THD 10% THD RL = 4 ohm + 33uH f=1kHz 0.5 0.5 0.5 3.5 4.5 5.5

OUTPUT POWER vs SUPPLY VOLTAGE

awinic

# awinic

| VOP & VOI | <b>₩₩₩₩₩₩₩₩₩₩</b> |

|-----------|-------------------|

| SHUTDOW   | N<br>10ms/div     |

## **Detailed Functional Description**

The AW8010B is a ultra-low-EMI,RNS, mono, filter-free, Class-D audio amplifier. Unique RNS, which effectively reduces RF energy, attenuate the RF TDD-noise, an acceptable audible level to the customer.

The AW8010B features the EEE (Enhanced Emission Elimination) function which greatly reduces EMI over the full bandwidth. The AW8010B achieves better than 20dB margin under FCC limits with 24 inch of cable.

The filter-free PWM architecture and internal gain setting reduces external components count, board area consumption, system cost and simplifies the design. The over-current and over-temperature protection is prepared inside of the device, which prevent the device from damage during fault conditions. When the fault condition is removed, the AW8010B reactivate itself again.

#### FILTER-FREE MODULATION SCHEME

The AW8010B features a filter-free PWM architecture that reduces the LC filter of the traditional Class-D amplifier, increasing efficiency, reducing board area consumption and system cost.

#### **POP-CLICK SUPPRESSION**

awinic

The AW8010B features unique timing control circuit, that comprehensively suppresses pop-click noise, eliminates audible transients on shutdown, wakeup, and power-up/down

#### EEE TECHNOLOGY

The AW8010B features a unique Enhanced Emission Elimination (EEE) technology, that controls fast transition on the output, greatly reduces EMI over the full bandwidth. The AW8010B achieves better than 20dB margin under FCC limits with 24 inch of cable.

#### EFFICIENCY

Efficiency of a Class D amplifier is attributed to the switching operation of the output stage transistors. In a Class D amplifier, the output transistors act as current steering switches and consume negligible additional power. Any power loss associated with the Class D output stage is mostly due to the I<sup>2</sup>R loss of the MOSFET on-resistance and supply current. The AW8010B features efficiency of 90%.

#### **PROTECTION FUNCTION**

When a short-circuit occurs between VOP/VON pin and VDD/GND or VOP and VON, the over-current circuit shutdown the device, preventing the device from being damaged. When the condition is removed, the AW8010B reactivate itself. When the junction temperature is high, the over-temperature circuit shutdown the device. The circuit switches back to normal operation when the temperature decreases to safe level.

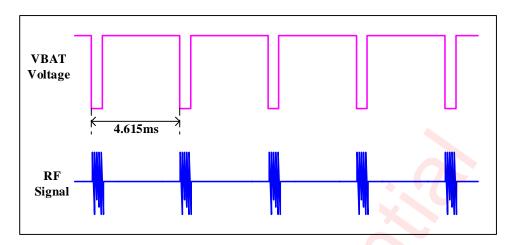

#### RNS(RF TDD NOISE SUPPRESSION)

#### TDD Noise Causes

GSM cell phones use TDMA (Time Division Multiple Access) slot sharing technology. The time is divided into periodic frames in TDMA, and each frame is subdivided into a plurality of time slots. In order to transmit signals to the base station, the signals sent from the base stations to the plurality of mobile terminals are arranged in a predetermined time slot in the transmission. In this case, each TDMA frame contains 8 time slots, the entire frame is about 4.615ms long, and each slot time is 0.577ms.

With GSM handset, the RF power amplifier will transmit once every 4.615ms (217Hz), and the signal will produce intermittent Burst current and strong electromagnetic radiation. Intermittent Burst current will form a power fluctuation of 217 Hz; High frequency (900MHz and 1800MHz) RF signals form a 217Hz RF envelope signal. 217Hz power fluctuations will be conducted through the conduction to the audio signal path, 217Hz RF envelope signal will be coupled through the radiation into the audio signal path, if the protection is not good, it will produce an audible TDD Noise, which includes the 217Hz noise And a harmonic noise signal of 217 Hz.

RNS fully inhibit the conduction and radiation interference by the AWINIC unique circuit architecture. Effectively improve the ability to suppress TDD Noise.

#### **Conduction noise suppression**

awinic

When the RF power amplifier is operating, it will draw the current from the battery by 217Hz frequency, Power supply will be introduced to 217Hz power ripple since the battery has a certain internal resistance, it will be coupled to the speaker through the audio power amplifier. The ability to suppress power fluctuations depends on the PSRR of the audio power amplifier.

$$PSRR = 20 \log(\frac{vdd_{ac}}{vout_{ac}})$$

Due to the input and output of the fully differential amplifier is perfectly symmetrical, theoretically, the effect of the power supply fluctuation on the two outputs is exactly the same, and the differential output is completely unaffected by the power supply fluctuation. In practice, due to process bias and other factors, the amplifier will have a certain mismatch, PSRR is generally better than 60dB, it shows the output relative to the power fluctuations can be reduced by 1000 times, such as 500mVp power fluctuations, the differential output of 0.5 mV, which basically can meet the application requirements.

But in practical applications, the power amplifier may encounter conduction of TDD Noise problem even if its PSRR is 60dB or 80dB, why is this? Because we also need to consider the impact of peripheral power mismatches of audio power amplifiers.

For conventional audio power amplifiers, when the input resistor Rin and the input capacitor Cin mismatch, will greatly affect the audio power amplifier PSRR indicators, in the case of 24 times gain, PSRR will be weakened to 46dB or so if the input resistance and Capacitor with 1% mismatch. PSRR will be weakened to 28dB or so if the input resistance and input capacitance mismatch with 10% mismatch, when the power fluctuations, it is easy to produce audible TDD Noise.

In order to enhance the audio power amplifier PSRR in the input resistance and input capacitance mismatch case, AW8010B features a unique conduction noise suppression circuit, making the power amplifier to maintain a high PSRR value even in the input resistance, the input capacitance deviation of 10% or more, this greatly inhibits the generation of conducted noise.

#### **Radiation noise suppression**

Input traces, output traces, horn loops, and even power and ground loops are likely to be subject to RF radiation interference in the audio signal module, longer input traces and output traces similar to the antenna, especially vulnerable RF radiation effects.

The reasonable PCB layout can reduce the influence of RF radiation in the design, such as shorten the line length of input and output as much as possible; audio devices should be shielded and far away from the RF antenna, maintain the integrity of the device to audio signal pathway; to increase the small bypass capacitor RF signals in the sensitive nodes. However, in practical applications, PCB layout is difficult to fully consider the influence of RF radiation on the audio signal path, and some RF energy will still be coupled to the audio signal path to form audible TDD Noise. Therefore, AW8010B features a unique RF radiation suppression circuit, a shielding layer inside the chip, effectively prevent high frequency energy into RF chip, to ensure that the drive single of the amplifier provided to the speaker will not be affected by the antenna RF radiation, thus avoiding the antenna RF Radiation caused by TDD Noise.

Figure 9 RF Energy Coupling Diagram

## **Application Information**

#### SUPPLY DECOUPLING CAPACITOR

The AW8010B is a high-performance class-D audio amplifier that requires adequate power supply decoupling to ensure the efficiency is high and total harmonic distortion (THD) is low. For higher frequency transients, a good low equivalent-series-resistance (ESR) ceramic capacitor, typically  $1\mu$ F, placed as close as possible to the device VDD pin works best. For filtering lower-frequency noise signals, a 10  $\mu$ F or greater capacitor placed near the audio power amplifier would also help.

#### **INPUT RESISTORS**

The input resistors set the gain of the amplifier according to equation as follow.

$$Gain = \frac{2 \times 157.5 k\Omega}{Rin} \quad \left(\frac{V}{V}\right)$$

The resistors matching is very important. CMRR, PSRR and THD diminish if resistor mismatch occurs. Therefore, it is recommended use 1% tolerance resistors or better to keep the performance optimized. Place the input resistors very close to the AW8010B to limit noise injection on the high- impedance nodes.

#### INPUT CAPACITOR

The input coupling capacitor blocks the DC voltage at the amplifier input terminal. The input capacitors and input resistors form a high-pass filter with the corner frequency, fc.

$$f_c = \frac{1}{2\pi RinCin}.$$

Setting the high-pass filter point high can block the 217Hz GSM noise coupled to inputs. Better matching of the input capacitors improves performance of the circuit and also help to suppress pop-click noise.

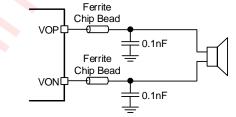

#### FERRITE CHIP BEAD AND CAPACITOR

The AW8010B passed FCC and CE radiated emissions with no ferrite chip beads and capacitors with speaker trace wires 24 inch.Use ferrite chip beads and capacitors if device near the EMI sensitive circuits and/or there are long leads from amplifier to speaker, placed as close as possible to the output pin.

Figure 10 Ferrite Chip Bead and capacitor

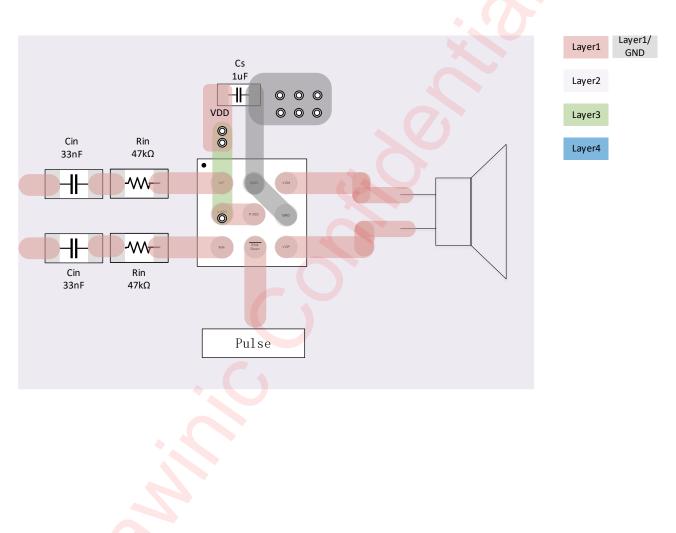

## **PCB Layout Consideration**

In order to obtain excellent performance of AW8010B, PCB layout must be carefully considered. The design consideration should follow the following principles:

1. Try to provide a separate short and thick power line to AW8010B, the copper width is recommended to be larger than 1.2mm. The decoupling capacitors should be placed as close as possible to power supply pin.

2. The input capacitors and resistors should be close to AW8010B INN and INP input pin, the input line should be parallel to suppress noise coupling.

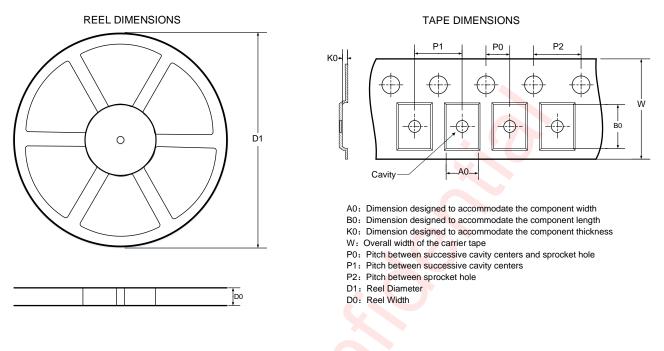

## **Tape And Reel Information**

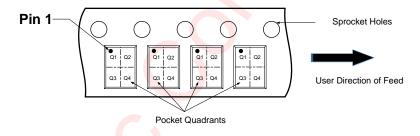

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

Note: The above picture is for reference only. Please refer to the value in the table below for the actual size

#### DIMENSIONS AND PIN1 ORIENTATION

| D1<br>(mm) | D0<br>(mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) |   | P1<br>(mm) |   |   | Pin1 Quadrant |

|------------|------------|------------|------------|------------|---|------------|---|---|---------------|

| 178        | 8.4        | 1.7        | 1.7        | 0.76       | 2 | 4          | 4 | 8 | Q1            |

All dimensions are nominal

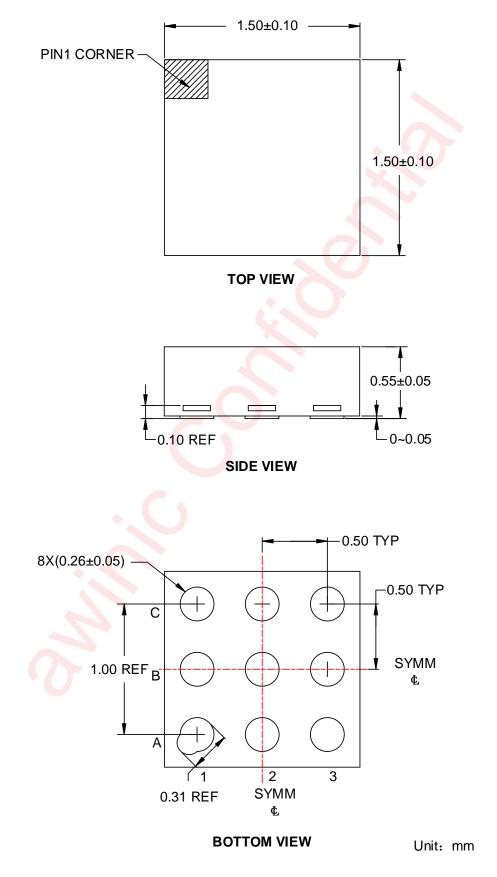

## **Package Description**

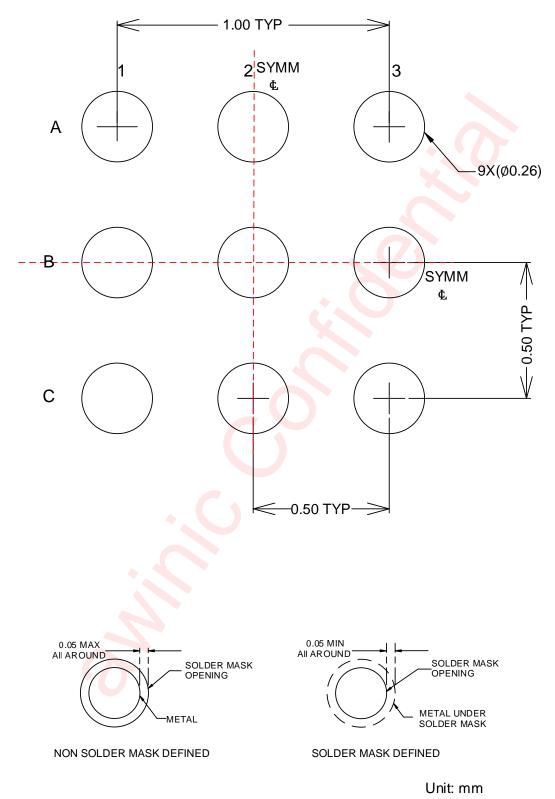

## Land Pattern Data

## **Revision History**

| Version | Release date | Description                      |

|---------|--------------|----------------------------------|

| V1.0    | Mar. 2022    | Officially released              |

| V1.1    | June. 2022   | Update POD and Land Pattern Data |

| V1.2    | July. 2022   | Update Functional Block Diagram  |

### **Disclaimer**

All trademarks are the property of their respective owners. Information in this document is believed to be accurate and reliable. However, Shanghai AWINIC Technology Co., Ltd (AWINIC Technology) does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

AWINIC Technology reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. Customers shall obtain the latest relevant information before placing orders and shall verify that such information is current and complete. This document supersedes and replaces all information supplied prior to the publication hereof.

AWINIC Technology products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an AWINIC Technology product can reasonably be expected to result in personal injury, death or severe property or environmental damage. AWINIC Technology accepts no liability for inclusion and/or use of AWINIC Technology products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

Applications that are described herein for any of these products are for illustrative purposes only. AWINIC Technology makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

All products are sold subject to the general terms and conditions of commercial sale supplied at the time of order acknowledgement.

Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

Reproduction of AWINIC information in AWINIC data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. AWINIC is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of AWINIC components or services with statements different from or beyond the parameters stated by AWINIC for that component or service voids all express and any implied warranties for the associated AWINIC component or service and is an unfair and deceptive business practice. AWINIC is not responsible or liable for any such statements.