## **MIC2133**

## 75V Dual Phase, Advanced COT Buck Controller with Selectable Droop Feature and Phase Shedding

#### **Features**

- Input Voltage Range: 8V to 75V

- Input Down to 2V when V<sub>DD</sub> = 5V from External Supply

- Adjustable Output Voltage from 0.6V to 28V

- · Adaptive Constant On-Time Control:

- High Delta V operation

- Any Capacitor™ stable

- 0.6V Internal Reference with ±1% Accuracy

- Ripple Injection from Third Node Allows Greater than 50% Duty Cycles

- HyperLight Load<sup>®</sup> and Automatic Phase Shedding

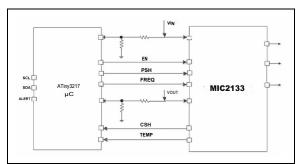

- · Ability to Interface with External MCU

- · Accurate Current Balancing Between Phases

- · Accurate 180° Phasing of Outputs

- 100 kHz to 1 MHz Switching Frequency per Phase

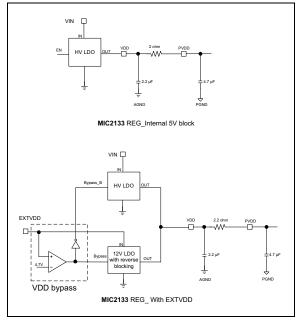

- High-Voltage Internal 5V LDO for Single-Supply Operation

- Secondary LDO to Improve System Efficiency

- · Supports Start-up to Pre-Bias Output

- Remote Sense Amplifier for Tight Output Regulation

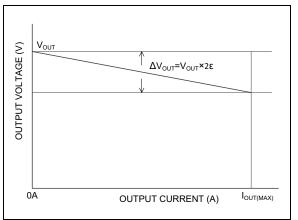

- Droop Feature to Support Adaptive Voltage Positioning (AVP) for Improved Load Transient Response

- Precision Enable Function for Low Standby Current

- External Programmable Soft Start to Reduce Inrush Current

- Lossless R<sub>DSON</sub> Current Sensing with NTC Temperature Compensation or Resistor Sensing Method

- Programmable Current Limit and Hiccup Mode Short-Circuit Protection

- Thermal Shutdown with Hysteresis

- -40°C to +125°C Junction Temperature Range

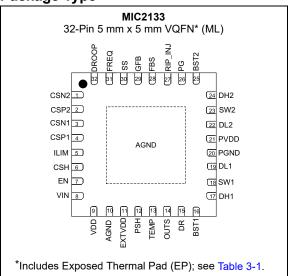

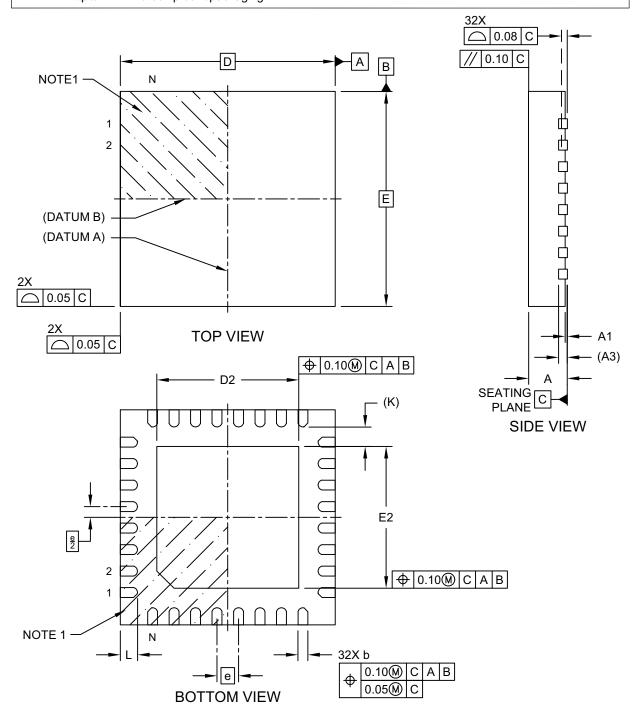

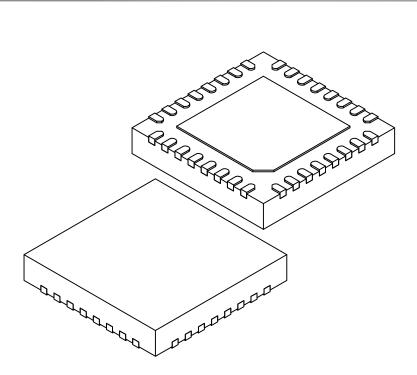

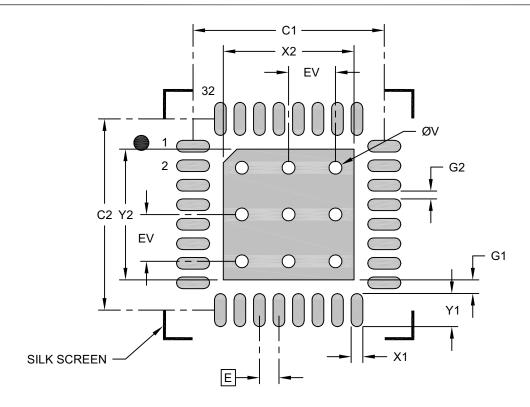

- Compact Size 5 mm x 5 mm, 32-Pin VQFN Package

- AEC-Q100 Qualified (VAO Suffix)

#### **Applications**

- · Distributed Power Systems

- · Communications/Networking Infrastructure

- · Printers, Scanners, Graphic and Video Cards

- FPGA, CPU, Memory, GPU Core Supplies

- Automotive POL

#### **General Description**

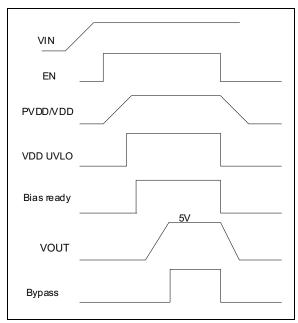

The MIC2133 is a constant on-time, dual phase, synchronous buck controller featuring a unique adaptive on-time control architecture with HyperLight Load and phase shedding features enabled. The MIC2133 operates over an input supply range from 8V to 75V. The output voltage is adjustable down to 0.6V with an ensured accuracy of  $\pm 1\%$  at the FBS pin. The device operates with programmable switching frequency from 100 kHz to 1 MHz per phase.

The Hyper Speed Control architecture supports an ultrafast transient response under medium to heavy loads. The soft start is also programmable externally with a capacitor, thus, enabling safe start-ups into heavy loads. The MIC2133 has a remote sense amplifier for accurate output voltage control.

MIC2133 offers a full suite of protection features to ensure protection of the IC during Fault conditions. These include undervoltage lockout to ensure proper operation, programmable soft start to reduce inrush current, overvoltage discharge, Hiccup mode short-circuit protection and thermal shutdown.

MIC2133 is available in a 5 mm x 5 mm, 32-pin VQFN package with a -40°C to +125°C operating junction temperature range.

#### Package Type

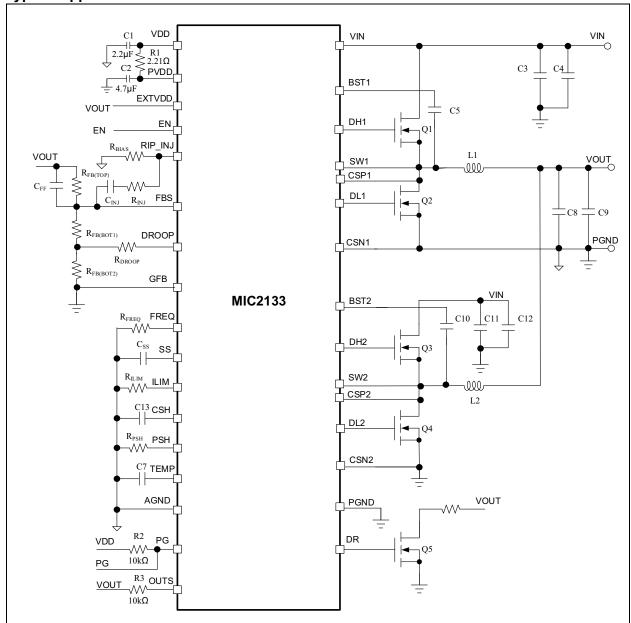

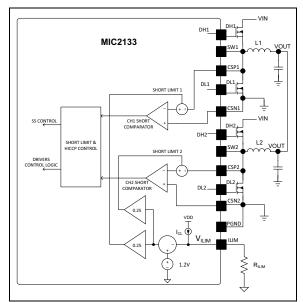

### **Typical Application Circuit**

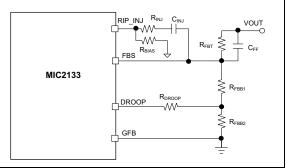

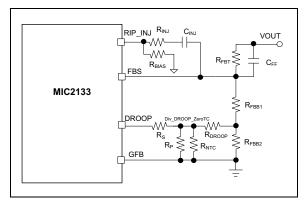

Application circuit based on R<sub>DSON</sub> current sensing without temperature compensated ILIM, Phase Shedding and Droop. Temperature compensation can be done using NTC resistors (refer to **Section 4.0 "Functional Description"**).

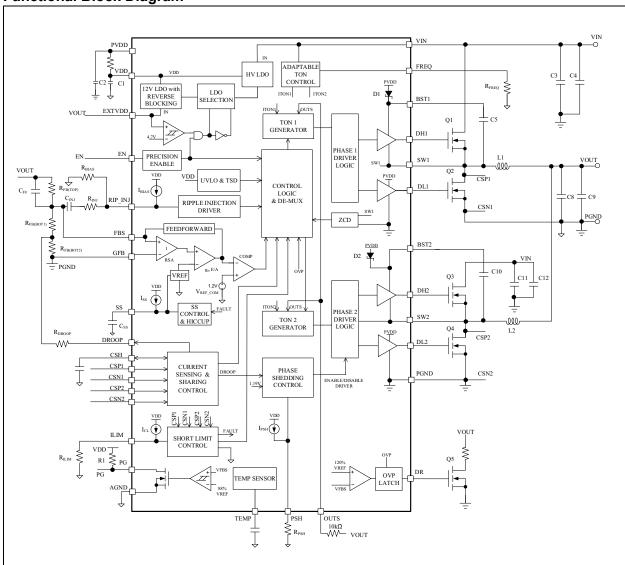

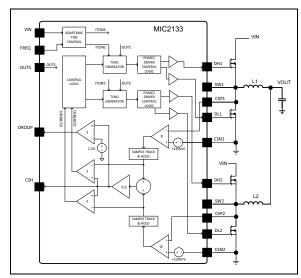

### **Functional Block Diagram**

#### 1.0 ELECTRICAL CHARACTERISTICS

#### Absolute Maximum Ratings<sup>†</sup>

| V <sub>IN</sub> to AGNDV <sub>DD</sub> , OUTS to AGND                            | 0.3V to +76V                              |

|----------------------------------------------------------------------------------|-------------------------------------------|

| V <sub>DD</sub> , OUTS to AGND                                                   | 0.3V to +6V                               |

| PV <sub>DD</sub> to PGND                                                         | 0.3V to +6V                               |

| PV <sub>DD</sub> to PGNDEN to AGND                                               | 0.3V to (V <sub>IN</sub> + 0.3V)          |

| SW1_SW2_CSP1_CSP2 to PGND                                                        | $-0.3V$ to $(V_{INI} + 0.3V)$             |

| BST1 to SW1, BST2 to SW2                                                         | 0.3V to 6V                                |

| DH1 to SW1, DH2 to SW2                                                           | $V_{SW1.2} - 0.3V$ to $V_{BST1.2} + 0.3V$ |

| I <sub>LIM</sub> , FREQ, SS, RIP_INJ, FBS, DROOP, PG, CSH, PSH, TEMP, DR to AGND | 0.3V to (V <sub>DD</sub> + 0.3V)          |

| EXTVDD to AGND                                                                   | 0.3V to +14V                              |

| CSN1, CSN2, GFB, PGND to AGND                                                    | 0.3V to +0.3V                             |

| Maximum Junction Temperature (T <sub>J</sub> )                                   |                                           |

| Storage Temperature (T <sub>S</sub> )                                            | 65°C to +150°C                            |

| Lead Temperature (T <sub>LEAD</sub> )                                            | +300°C                                    |

| ESD Rating <sup>(1)</sup> (HBM)                                                  | 2000V                                     |

| ESD Rating <sup>(1)</sup> (MM)                                                   | 200V                                      |

| ESD Rating <sup>(1)</sup> (CDM)                                                  | 2000V                                     |

| Operating Ratings <sup>‡</sup>                                                   |                                           |

|                                                                                  | <b></b>                                   |

| Supply Voltage (V <sub>IN</sub> )                                                |                                           |

| DV V Din Voltage                                                                 | 1 5\/ to 5 5\/                            |

- † Notice: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational sections of this specification is not intended. Exposure to maximum rating conditions for extended periods may affect device reliability.

- **‡ Notice:** The device is not ensured to function outside its operating ratings.

- Note 1: Specification for packaged product only.

- 2:  $P_{D(MAX)} = (T_{J(MAX)} T_A)/\theta_{JA}$ , where  $\theta_{JA}$  depends upon the printed circuit layout.

## ELECTRICAL CHARACTERISTICS(1)

Electrical Characteristics:  $V_{IN}$  = 12V;  $V_{OUT}$  = 5V;  $f_{SW}$  = 500 kHz/phase;  $V_{BST} - V_{SW}$  = 5V;  $T_A$  = +25°C; unless noted. Boldface values indicate -40°C  $\leq T_J \leq$  +125°C.

| Boldiace Values indicate 40 0 2 1 3 1 120 0.            |                        |       |      |       |                       |                                                                                 |  |  |

|---------------------------------------------------------|------------------------|-------|------|-------|-----------------------|---------------------------------------------------------------------------------|--|--|

| Parameters                                              | Symbol                 | Min.  | Тур. | Max.  | Units                 | Conditions                                                                      |  |  |

| Power Supply Input                                      |                        |       |      |       |                       |                                                                                 |  |  |

| Input Voltage Range                                     | V <sub>IN</sub>        | 8     | _    | 75    | V                     | _                                                                               |  |  |

| Quiescent Supply Current                                | ΙQ                     | _     | 5000 | 8000  | μΑ                    | V <sub>FBS</sub> = +1.5V                                                        |  |  |

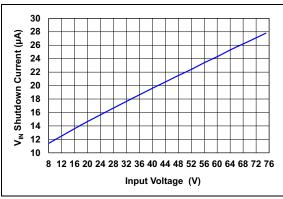

| Shutdown Current                                        | $I_{SD}$               | _     | 25   | 50    | μA                    | V <sub>EN</sub> = 0V                                                            |  |  |

| V <sub>DD</sub> and EXTVDD                              |                        |       |      |       |                       |                                                                                 |  |  |

| V <sub>DD</sub> Voltage Range                           | $V_{DD}$               | 4.7   | 5.1  | 5.4   | V                     | V <sub>IN</sub> = 8V to 75V, I <sub>VDD</sub> = 20 mA (Note 5)                  |  |  |

| V <sub>DD</sub> Undervoltage Lockout Upper<br>Threshold | V <sub>DDUV_R</sub>    | 3.7   | 4.2  | 4.5   | V                     | V <sub>DD</sub> rising                                                          |  |  |

| V <sub>DD</sub> UVLO Hysteresis                         | V <sub>DDUV_HYS</sub>  |       | 600  | _     | mV                    | Hysteresis                                                                      |  |  |

| V <sub>DD</sub> Regulation                              | ΔV <sub>DD</sub>       | _     | 1    | 2.5   | %                     | V <sub>IN</sub> = 24V,<br>I <sub>VDD</sub> from 1 mA to 40 mA ( <b>Note 5</b> ) |  |  |

| V <sub>DD</sub> Regulator Dropout Voltage               | V <sub>DROP_VDD</sub>  |       | 8.0  | 1.05  | V                     | V <sub>IN</sub> = 5.5V, I <sub>VDD</sub> = 25 mA                                |  |  |

| EXTVDD Switchover Voltage                               | V <sub>SO_EVDD</sub>   | 4.5   | 4.7  | 4.9   | V                     | V <sub>IN</sub> = 24V, EXTVDD rising,<br>I <sub>VDD</sub> = 40 mA               |  |  |

| EXTVDD Switchover Voltage<br>Hysteresis                 | V <sub>SO_HYS</sub>    | _     | 250  | _     | mV                    | Hysteresis                                                                      |  |  |

| EXTVDD Dropout Voltage                                  | V <sub>DROP_EVDD</sub> | _     | 250  | _     | mV                    | V <sub>EXTVDD</sub> = 5V, I <sub>VDD</sub> = 40 mA                              |  |  |

| EXTVDD Leakage Current                                  | I <sub>LK_EVDD</sub>   | _     | 0.1  | _     | μA                    | V <sub>EXTVDD</sub> = 14V, V <sub>EN</sub> = 0V                                 |  |  |

| Soft Start                                              |                        |       |      |       |                       |                                                                                 |  |  |

| Soft Start Source Current                               | I <sub>SS</sub>        | 0.8   | 1.2  | 1.7   | μA                    | _                                                                               |  |  |

| DC-DC Regulator                                         |                        |       |      |       |                       |                                                                                 |  |  |

| Output Voltage Adjustable Range                         | V <sub>OUT</sub>       | 0.6   | _    | 28    | V                     | Note 2                                                                          |  |  |

| Reference and Remote Sensing                            | Amplifier              |       |      |       |                       |                                                                                 |  |  |

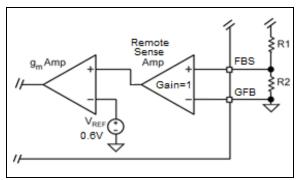

| Feedback Regulation Voltage                             | V <sub>FBS-GFB</sub>   | 0.593 | 0.6  | 0.606 | V                     | Measured with EA in servo loop                                                  |  |  |

| FBS Bias Current                                        | I <sub>FBS</sub>       | _     | 2    | _     | nA                    | V <sub>FBS</sub> = +0.6V (Note 2)                                               |  |  |

| GFB Bias Current                                        | $I_{GFB}$              |       | 12   | _     | μA                    | _                                                                               |  |  |

| Remote Sense Amplifier Gain                             | G <sub>RSA</sub>       |       | 1.00 | _     | V/V                   | _                                                                               |  |  |

| Enable                                                  |                        |       |      |       |                       |                                                                                 |  |  |

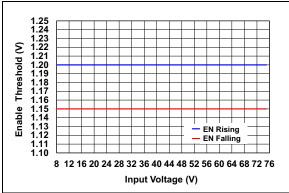

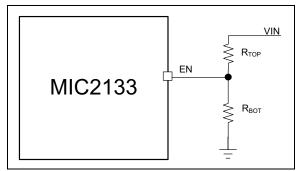

| Enable Upper Threshold Voltage                          | V <sub>EN_TH</sub>     | 1.05  | 1.2  | 1.36  | V                     | Enable Rising                                                                   |  |  |

| Enable Hysteresis                                       | V <sub>EN_HYS</sub>    |       | 65   |       | mV                    | _                                                                               |  |  |

| Enable Bias Current                                     |                        |       |      |       | V <sub>EN</sub> = 12V |                                                                                 |  |  |

|                                                         |                        |       |      |       |                       |                                                                                 |  |  |

- Note 1: Specification for packaged product only.

- 2: Ensured by design and characterization. Not production tested.

- 3: Measured in Test mode.

- 4: The maximum duty cycle is limited by the fixed mandatory off-time of typically 360 ns.

- **5:** Limited by maximum junction temperature  $T_J = +125$ °C.

## ELECTRICAL CHARACTERISTICS<sup>(1)</sup> (CONTINUED)

**Electrical Characteristics:**  $V_{IN}$  = 12V;  $V_{OUT}$  = 5V;  $f_{SW}$  = 500 kHz/phase;  $V_{BST} - V_{SW}$  = 5V;  $T_A$  = +25°C; unless noted. **Boldface** values indicate -40°C  $\leq T_J \leq$  +125°C.

| Parameters                               | Symbol                | Min.  | Тур. | Max.  | Units  | Conditions                                                                                                                                                                                         |

|------------------------------------------|-----------------------|-------|------|-------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| On Timer                                 |                       |       |      |       | •      |                                                                                                                                                                                                    |

| Nominal Switching Frequency per Phase    | f <sub>SWNOM_PH</sub> | 400   | 500  | 600   | kHz    | $V_{IN}$ = 12V, $V_{OUTS}$ = 5V,<br>R <sub>FREQ</sub> = 40.2 k $\Omega$                                                                                                                            |

| Minimum Switching Frequency per Phase    | f <sub>SWMIN_PH</sub> | _     | 100  | _     | kHz    | $V_{IN}$ = 12V, $V_{OUTS}$ = 5V,<br>$R_{FREQ}$ = 200 kΩ                                                                                                                                            |

| Maximum Switching Frequency per Phase    | f <sub>SWMAX_PH</sub> | _     | 800  | _     | kHz    | $V_{IN}$ = 12V, $V_{OUTS}$ = 5V,<br>$R_{FREQ}$ = 25.5 kΩ                                                                                                                                           |

| Minimum On-Time                          | T <sub>ONMIN</sub>    | _     | 60   | _     | ns     | Measured in application (Note 2)                                                                                                                                                                   |

| Minimum Off-Time                         | T <sub>OFFMIN</sub>   | _     | 360  | _     | ns     | V <sub>FBS</sub> = 0V                                                                                                                                                                              |

| Maximum Duty Cycle                       | D <sub>MAX</sub>      | _     | 85   | _     | %      | f <sub>SW</sub> = 400 kHz per phase (Note 4)                                                                                                                                                       |

| Minimum Duty Cycle                       | D <sub>MIN</sub>      | _     | 0    | _     | %      | V <sub>FBS</sub> = +1V (Note 2)                                                                                                                                                                    |

| Current Limit                            |                       |       |      |       |        |                                                                                                                                                                                                    |

| ILIM Source Current                      | I <sub>CL</sub>       | 8.3   | 9.6  | 10.56 | μA     | _                                                                                                                                                                                                  |

| ILIM Source Current Tempco               | TC <sub>ICL</sub>     |       | 0    | _     | ppm/°C | Note 2                                                                                                                                                                                             |

| Nominal Current Limit Threshold          | $V_{ILIM\_TH}$        | 139   | 156  | 174   | mV     | $R_{ILIM} = 60.4 \text{ k}\Omega$                                                                                                                                                                  |

| Voltage per Phase                        |                       |       | 47   | _     | mV     | $R_{ILIM}$ = 105 k $\Omega$                                                                                                                                                                        |

|                                          |                       | _     | 250  | _     | mV     | $R_{ILIM} = 21 k\Omega$                                                                                                                                                                            |

| Negative Current Limit Threshold Voltage | $V_{ILIM\_NTH}$       | 60    | 75   | 90    | mV     | $R_{ILIM} = 60.4 \text{ k}\Omega$                                                                                                                                                                  |

| Zero-Crossing Detection                  |                       |       |      |       |        |                                                                                                                                                                                                    |

| Zero-Crossing Detection Threshold        | V <sub>ZCD_TH</sub>   | -10   | -4   | -0.6  | mV     | _                                                                                                                                                                                                  |

| Current Sharing Amplifier                |                       | •     |      |       |        |                                                                                                                                                                                                    |

| CSH Operating Point                      | V <sub>CSH_OP</sub>   | 1.154 | 1.19 | 1.244 | V      | $V_{CSN1} = V_{CSN2} = V_{CSP1} = V_{CSP2} = 0V$                                                                                                                                                   |

| Current Sense Amplifier(s) Gain          | G <sub>CSA</sub>      | _     | 8    | _     | V/V    | As reflected on CSH pin and DROOP pin                                                                                                                                                              |

| Current Sense Input Voltage<br>Range     | V <sub>CS</sub>       | -120  | _    | +120  | mV     | -40°C ≤ T <sub>J</sub> ≤ +125°C                                                                                                                                                                    |

| Phase to Phase Current Balance           | ΔI <sub>PH</sub>      | _     | 5    |       | %      | Using equal sense resistors on the bottom, equal inductances, $f_{SW} = 500 \text{ kHz}$ , $V_{IN} = 12V$ , $V_{OUT} = 5V$ , $VCSP1 - VCSN1 = -120 \text{ mV}$ , $VCSP2 - VCSN2 = -120 \text{ mV}$ |

- Note 1: Specification for packaged product only.

- 2: Ensured by design and characterization. Not production tested.

- 3: Measured in Test mode.

- 4: The maximum duty cycle is limited by the fixed mandatory off-time of typically 360 ns.

- **5:** Limited by maximum junction temperature  $T_J = +125$ °C.

### ELECTRICAL CHARACTERISTICS<sup>(1)</sup> (CONTINUED)

**Electrical Characteristics:**  $V_{IN}$  = 12 $\overline{V}$ ;  $V_{OUT}$  = 5 $\overline{V}$ ;  $V_{OUT}$  = 500 kHz/phase;  $V_{BST} - V_{SW}$  = 5 $\overline{V}$ ;  $V_{A}$  = +25 $^{\circ}$ C; unless noted. **Boldface** values indicate -40 $^{\circ}$ C  $\leq$   $V_{A}$   $\leq$  +125 $^{\circ}$ C.

| Parameters                                         | Symbol                 | Min. | Тур. | Max. | Units             | Conditions                                                                                        |  |  |

|----------------------------------------------------|------------------------|------|------|------|-------------------|---------------------------------------------------------------------------------------------------|--|--|

| Adaptive Voltage Positioning (AVP), i.e., DROOP    |                        |      |      |      |                   |                                                                                                   |  |  |

| V <sub>DROOP</sub> at No Load                      | V <sub>DRP_NLOAD</sub> | _    | 10   | _    | mV                | Measure DROOP voltage $\sim$ 0V when $V_{CSP1} - V_{CSN1} = 0V$ , $V_{CSP2} - V_{CSN2} = 0V$      |  |  |

| V <sub>DROOP</sub> at Maximum Positive<br>Range    | V <sub>DRP(PMAX)</sub> | _    | 0.96 |      | V                 | Measure DROOP voltage ~1.2V when $V_{CSP1} - V_{CSN1} = -120$ mV, $V_{CSP2} - V_{CSN2} = -120$ mV |  |  |

| Ripple Injection                                   |                        |      |      |      |                   |                                                                                                   |  |  |

| Ripple Injection Pulse Width                       | t <sub>PW(RI)</sub>    | _    | 100  | 120  | ns                | _                                                                                                 |  |  |

| Ripple Injection Prepositioning<br>Current         | I <sub>BIAS</sub>      | _    | 4.8  | 6    | μА                | Force V <sub>RIPINJ</sub> = 0V,<br>V <sub>SS</sub> = 0V,<br>measure current                       |  |  |

| Injection Driver ON Resistance R <sub>DSON(I</sub> |                        | _    | 50   | _    | Ω                 | _                                                                                                 |  |  |

| Internal MOSFET Drivers                            |                        |      |      |      |                   |                                                                                                   |  |  |

| DHx On-Resistance, High State                      | R <sub>ON_DHH</sub>    | _    | 2.5  | 4.5  | Ω                 | I <sub>SOURCE</sub> = 0.1A                                                                        |  |  |

| DHx On-Resistance, Low State                       | R <sub>ON_DHL</sub>    |      | 1.6  | 3.2  | Ω                 | I <sub>SINK</sub> = 0.1A                                                                          |  |  |

| DLx On-Resistance, High State                      | R <sub>ON_DLH</sub>    | _    | 2.5  | 4.5  | Ω                 | I <sub>SOURCE</sub> = 0.1A                                                                        |  |  |

| DLx On-Resistance, Low State                       | R <sub>ON_DLL</sub>    | _    | 8.0  | 1.5  | Ω                 | I <sub>SINK</sub> = 0.1A                                                                          |  |  |

| SW, VIN and BST Leakage                            |                        |      |      |      |                   |                                                                                                   |  |  |

| BST Leakage                                        | I <sub>LEAK(BST)</sub> | _    | _    | 10   | μΑ                | V <sub>BST</sub> = 75V                                                                            |  |  |

| VIN Leakage                                        | I <sub>LEAK(VIN)</sub> |      | _    | 60   | μA                | V <sub>IN</sub> = 70V                                                                             |  |  |

| SW Leakage                                         | I <sub>LEAK(SW)</sub>  | _    | _    | 20   | μA                | V <sub>SW</sub> = 70V                                                                             |  |  |

| Power Good (PG)                                    |                        |      |      |      |                   |                                                                                                   |  |  |

| PG Threshold from Low to High                      | V <sub>PG_TH</sub>     | 83   | 88   | 94   | %V <sub>OUT</sub> | V <sub>FBS</sub> rising                                                                           |  |  |

| PG Threshold Hysteresis                            | V <sub>PG_HYS</sub>    | _    | 7    |      | %V <sub>OUT</sub> | V <sub>FBS</sub> falling                                                                          |  |  |

| PG Delay                                           | t <sub>D_PG</sub>      | _    | 100  | _    | μs                | V <sub>FBS</sub> rising                                                                           |  |  |

| PG Low State Voltage                               | V <sub>PG_L</sub>      |      | 70   | 200  | mV                | V <sub>FBS</sub> < 90% x V <sub>NOM</sub> ,<br>I <sub>PG</sub> = 1 mA                             |  |  |

| PG Leakage Current                                 | I <sub>LEAK(PG)</sub>  | _    |      | 500  | nA                | V <sub>PG</sub> = 5.5V                                                                            |  |  |

- Note 1: Specification for packaged product only.

- 2: Ensured by design and characterization. Not production tested.

- 3: Measured in Test mode.

- **4:** The maximum duty cycle is limited by the fixed mandatory off-time of typically 360 ns.

- **5:** Limited by maximum junction temperature  $T_J = +125$ °C.

### ELECTRICAL CHARACTERISTICS<sup>(1)</sup> (CONTINUED)

**Electrical Characteristics:**  $V_{IN}$  = 12 $\overline{V}$ ;  $V_{OUT}$  = 5 $\overline{V}$ ;  $V_{OUT}$  = 500 kHz/phase;  $V_{BST} - V_{SW}$  = 5 $\overline{V}$ ;  $V_{A}$  = +25 $^{\circ}$ C; unless noted. **Boldface** values indicate -40 $^{\circ}$ C  $\leq$   $V_{A}$   $\leq$  +125 $^{\circ}$ C.

| Parameters                         | Symbol                 | Min. | Тур. | Max. | Units                                                              | Conditions                                                                                                              |  |

|------------------------------------|------------------------|------|------|------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--|

| Phase Shedding                     |                        |      |      |      |                                                                    |                                                                                                                         |  |

| Phase Shedding Exit Threshold      | V <sub>PSH_EXIT</sub>  | 170  | 244  | 300  | mV                                                                 | V <sub>PSH</sub> = 0.96V, V <sub>DROOP</sub> ramp-up (Note 3)                                                           |  |

| Phase Shedding Entry Threshold     | V <sub>PSH_ENTRY</sub> | 135  | 195  | 240  | mV V <sub>PSH</sub> = 0.96V, V <sub>DROOP</sub> ramp-down (Note 3) |                                                                                                                         |  |

| DROOP High-to-Low Transition Time  | t <sub>TRAN_HL</sub>   |      | 30   | _    | μs                                                                 | MIC2133 sheds the secondary;<br>moving V <sub>PSH_TH</sub> from high to<br>0 mV, the delay of the action is<br>measured |  |

| PSH Current                        | I <sub>PSH</sub>       | 9    | 10   | 11   | μA                                                                 | _                                                                                                                       |  |

| PSH Current Tempco                 | TC <sub>IPSH</sub>     | _    | 0    | _    | ppm/°C                                                             | Note 2                                                                                                                  |  |

| Output Overvoltage Protection (DR) |                        |      |      |      |                                                                    |                                                                                                                         |  |

| OVP Threshold                      | V <sub>OVP_TH</sub>    | 0.64 | 0.67 | 0.7  | V                                                                  | OVP is activated after UVLO goes high and V <sub>FBS</sub> soft start                                                   |  |

| OVP Deglitch Timer                 | t <sub>DEGLITCH</sub>  |      | 12   | _    | μs                                                                 |                                                                                                                         |  |

| DR Output High R <sub>DSON</sub>   | R <sub>ON_DRH</sub>    | _    | 30   | _    | Ω                                                                  | I <sub>DR</sub> = 10 mA                                                                                                 |  |

| DR Output Low R <sub>DSON</sub>    | R <sub>ON_DRL</sub>    | _    | 25   | _    | Ω                                                                  | I <sub>DR</sub> = 10 mA                                                                                                 |  |

| DR Rise Time                       | t <sub>R_DR</sub>      | _    | 160  | _    | ns                                                                 | C <sub>LOAD</sub> = 1 nF (Note 2)                                                                                       |  |

| Temperature Sense                  |                        |      |      |      |                                                                    |                                                                                                                         |  |

| Thermal Sense Gain                 | G <sub>TS</sub>        | _    | 6    | _    | mV/°C                                                              |                                                                                                                         |  |

| Thermal Sense Offset Voltage       | V <sub>OS_TS</sub>     |      | 1.8  | _    | V                                                                  | V <sub>IN</sub> = V <sub>DD</sub> = 5V (Note 2)                                                                         |  |

| Thermal Sense Nonlinearity         | T <sub>SNL</sub>       |      | ±6   | _    | °C                                                                 | TEMP = -40°C to +125°C,<br>ensured by design and<br>measured at characterization                                        |  |

| Thermal Shutdown                   |                        |      |      |      |                                                                    |                                                                                                                         |  |

| Thermal Shutdown Threshold         | T <sub>SD</sub>        |      | 160  | _    | °C                                                                 | T <sub>J</sub> Rising (Note 2)                                                                                          |  |

| Thermal Shutdown Hysteresis        | T <sub>SD_HYS</sub>    |      | 20   | _    | °C                                                                 | Note 2                                                                                                                  |  |

- Note 1: Specification for packaged product only.

- 2: Ensured by design and characterization. Not production tested.

- 3: Measured in Test mode.

- 4: The maximum duty cycle is limited by the fixed mandatory off-time of typically 360 ns.

- **5:** Limited by maximum junction temperature  $T_J = +125$ °C.

#### **TEMPERATURE SPECIFICATIONS**

| Parameters                                    | Symbol                 | Min. | Тур. | Max. | Units | Conditions          |

|-----------------------------------------------|------------------------|------|------|------|-------|---------------------|

| Temperature Ranges                            |                        |      |      |      |       |                     |

| Operating Junction Temperature Range          | $T_J$                  | -40  | _    | +125 | °C    | Note 1              |

| Maximum Junction Temperature                  | T <sub>J(ABSMAX)</sub> | _    | _    | +150 | °C    | _                   |

| Storage Temperature                           | T <sub>S</sub>         | -65  | _    | +150 | °C    | _                   |

| Lead Temperature                              | T <sub>LEAD</sub>      | _    | _    | +300 | °C    | Soldering, 10s      |

| Package Thermal Resistance                    |                        |      |      |      |       |                     |

| Thermal Resistance, 5 mm x 5 mm, 32-Lead VQFN | $\theta_{\sf JC}$      | _    | 2    | _    | °C/W  | Junction to Case    |

| Thermal Resistance, 5 mm x 5 mm, 32-Lead VQFN | $\theta_{JA}$          | _    | 34   | _    | °C/W  | Junction to Ambient |

Note 1: The maximum allowable power dissipation is a function of ambient temperature, the maximum allowable junction temperature and the thermal resistance from junction to air (i.e.,  $T_A$ ,  $T_J$ ,  $\theta_{JA}$ ). Exceeding the maximum allowable power dissipation will cause the device operating junction temperature to exceed the maximum +125°C rating. Sustained junction temperatures above +125°C can impact the device reliability.

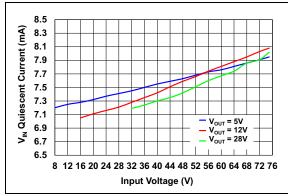

#### 2.0 TYPICAL PERFORMANCE CURVES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and, therefore, outside the warranted range.

**Note:** Unless otherwise indicated,  $V_{IN}$  = 12V;  $V_{OUT}$  = 5V;  $f_{SW}$  = 500 kHz/phase;  $V_{BST} - V_{SW}$  = 5V;  $T_A$  = +25°C.

**FIGURE 2-1:**  $V_{IN}$  Quiescent Current vs. Input Voltage.

**FIGURE 2-2:** V<sub>IN</sub> Shutdown Current vs. Input Voltage.

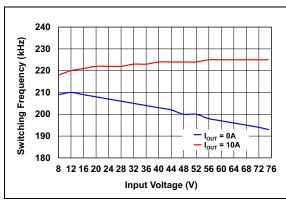

**FIGURE 2-3:** Switching Frequency vs. Input Voltage.

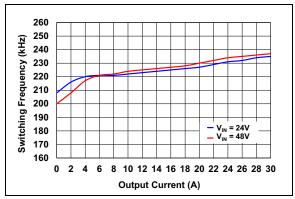

FIGURE 2-4: Switching Frequency vs. Output Current.

FIGURE 2-5: Enable Threshold vs. Input Voltage.

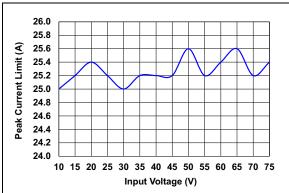

FIGURE 2-6: Peak Current Limit vs. Input Voltage.

**Note:** Unless otherwise indicated,  $V_{IN}$  = 12V;  $V_{OUT}$  = 5V;  $f_{SW}$  = 500 kHz/phase;  $V_{BST} - V_{SW}$  = 5V;  $T_A$  = +25°C.

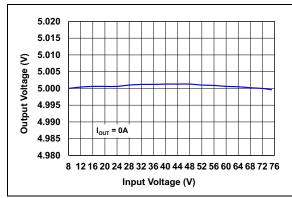

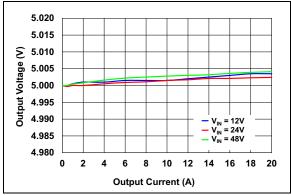

FIGURE 2-7: Line Regulation  $(V_{OUT} = 5V)$ .

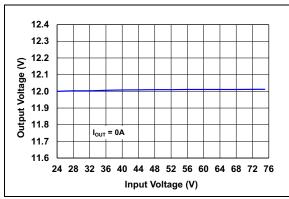

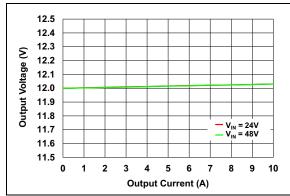

FIGURE 2-8: Line Regulation  $(V_{OUT} = 12V)$ .

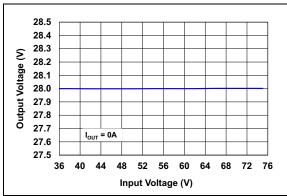

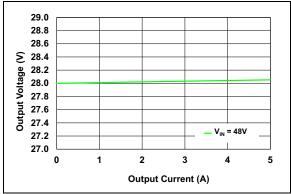

FIGURE 2-9: Line Regulation  $(V_{OUT} = 28V)$ .

FIGURE 2-10: Load Regulation  $(V_{OUT} = 5V)$ .

**FIGURE 2-11:** Load Regulation  $(V_{OUT} = 12V)$ .

FIGURE 2-12: Load Regulation (V<sub>OUT</sub> =28V).

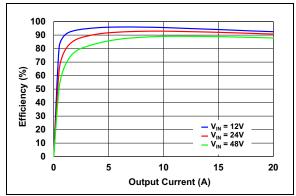

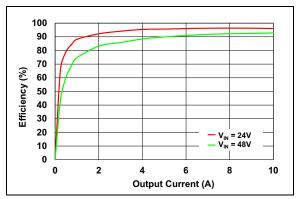

**FIGURE 2-13:** Efficiency vs. Output Current ( $V_{OUT} = 5V$ ).

**FIGURE 2-14:** Efficiency vs. Output Current ( $V_{OUT} = 12V$ ).

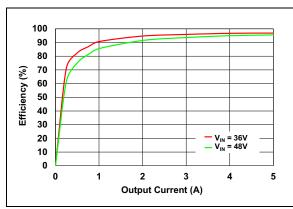

**FIGURE 2-15:** Efficiency vs. Output Current ( $V_{OUT} = 28V$ ).

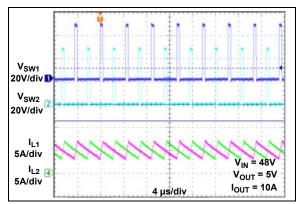

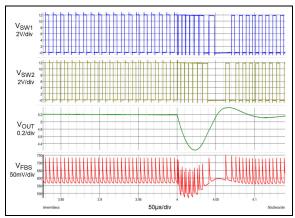

**FIGURE 2-16:** Switching Waveforms Phasing  $(V_{OUT} = 5V, I_{OUT} = 10A)$ .

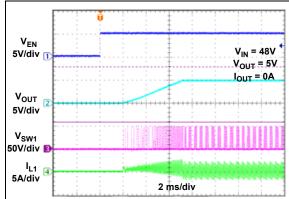

FIGURE 2-17: Soft Start with Enable  $(V_{OUT} = 5V, I_{OUT} = 0A)$ .

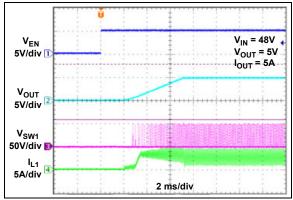

**FIGURE 2-18:** Soft Start with Enable  $(V_{OUT} = 5V, I_{OUT} = 5A)$ .

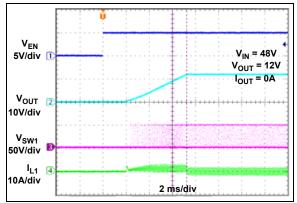

**FIGURE 2-19:** Soft Start with Enable  $(V_{OUT} = 12V, I_{OUT} = 0A)$ .

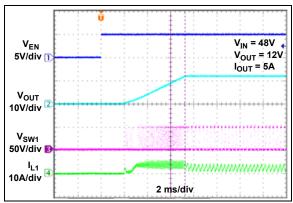

**FIGURE 2-20:** Soft Start with Enable  $(V_{OUT} = 12V, I_{OUT} = 5A)$ .

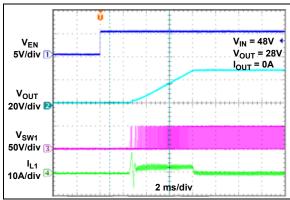

**FIGURE 2-21:** Soft Start with Enable  $(V_{OUT} = 28V, I_{OUT} = 0A)$ .

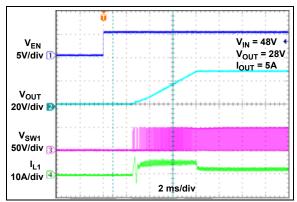

**FIGURE 2-22:** Soft Start with Enable  $(V_{OUT} = 28V, I_{OUT} = 5A)$ .

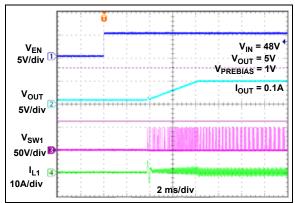

**FIGURE 2-23:** Pre-Bias Start-Up  $(V_{PREBIAS} = 1V, I_{OUT} = 0.1A)$ .

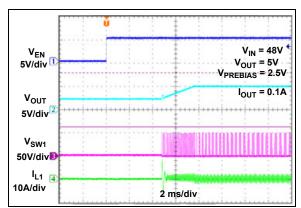

**FIGURE 2-24:** Pre-Bias Start-Up  $(V_{PREBIAS} = 2.5V, I_{OUT} = 0.1A)$ .

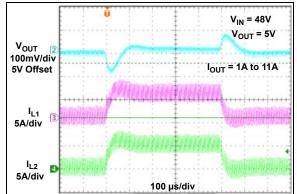

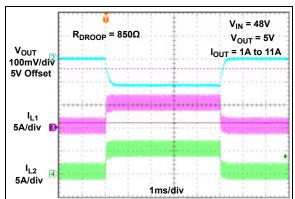

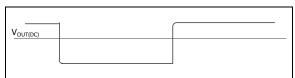

**FIGURE 2-25:** Load Transient without Droop ( $V_{OUT} = 5V$ ,  $I_{OUT} = 1A$  to 11A).

FIGURE 2-26: Load Transient with Droop  $(V_{OUT} = 5V, I_{OUT} = 1A \text{ to } 11A).$

FIGURE 2-27: Current Limit per Phase.

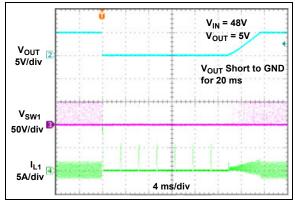

**FIGURE 2-28:** Output Short-Circuit Protection and Recovery  $(V_{OUT} = 5V)$ .

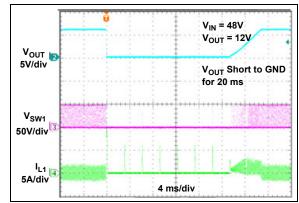

**FIGURE 2-29:** Output Short-Circuit Protection and Recovery  $(V_{OUT} = 12V)$ .

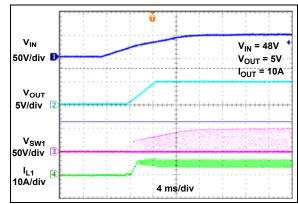

**FIGURE 2-30:** Power-Up with  $V_{IN}$  and 10A Load.

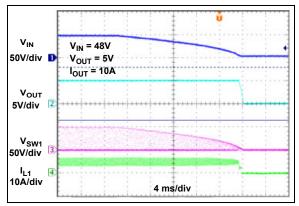

**FIGURE 2-31:** Power-Down with  $V_{IN}$  and 10A Load.

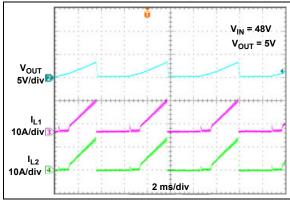

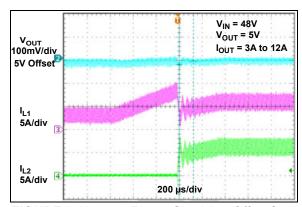

FIGURE 2-32: Phase Shedding Off to On.

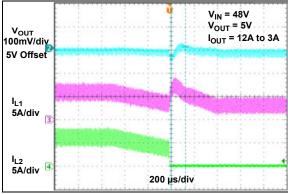

FIGURE 2-33: Phase Shedding On to Off.

### 3.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in the following table.

TABLE 3-1: PIN FUNCTION TABLE

| Pin<br>Number | Symbol | Description                                                                                                                                                                                                                                                                                                                                                               |

|---------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | CSN2   | Current Sense Return pin for Phase 2. Connect Kelvin connection from the low-side FET source to CSN2 to avoid ground drops due to high current.                                                                                                                                                                                                                           |

| 2             | CSP2   | Current Sense Positive pin for Phase 2. Connect Kelvin connection from the low-side FET drain to CSP2 to avoid ground drops due to high current.                                                                                                                                                                                                                          |

| 3             | CSN1   | Current Sense Return pin for Phase 1. Connect Kelvin connection from the low-side FET source to CSN1 to avoid ground drops due to high current.                                                                                                                                                                                                                           |

| 4             | CSP1   | Current Sense Positive pin for Phase 1. Connect Kelvin connection from the low-side FET drain to CSP1 to avoid ground drops due to high current.                                                                                                                                                                                                                          |

| 5             | ILIM   | Current Limit Adjust Input pin. Connect a resistor from ILIM to AGND to set the current limit. Refer to Section 4.5.4 "Current Limit" for more details. Both channels share the same current limit threshold.                                                                                                                                                             |

| 6             | CSH    | Average Current Sense Voltage Output pin. Used for current sharing; see Section 4.5.1 "Current Balancing between Phases", Section 4.5.11 "Adaptive Voltage Positioning (AVP), Also Known as Droop Function (Recommended for CCM Only)" and Section 4.5.13 "Telemetry Knobs". Connect 100 pF from CSH to AGND.                                                             |

| 7             | EN     | Active-High Enable Input pin. 75V compatible with 1.2V precise threshold. Pull EN to GND to disable the buck converter output. Connect to VIN for always-on operation. EN can be used for power sequencing and as a UVLO adjustment input. For a precision UVLO, put an appropriate sized resistor divider from VIN to AGND and tie the midpoint to the EN pin.           |

| 8             | VIN    | Input Voltage to Controller pin. Connect to VIN through 1.21 $\Omega$ resistor. Connect 1 $\mu$ F capacitor from this pin to PGND.                                                                                                                                                                                                                                        |

| 9             | VDD    | 5V LDO Output pin. Bias supply for the MIC2133 control logic circuit. Connect a minimum 2.2 μF low-ESR ceramic capacitor from VDD to AGND.                                                                                                                                                                                                                                |

| 10            | AGND   | Analog Ground pin. Reference node for all control logic circuits inside the MIC2133. Connect AGND to PGND at one point.                                                                                                                                                                                                                                                   |

| 11            | EXTVDD | Auxiliary LDO Input pin. Connect to a supply higher than 4.7V (typ.) to bypass the internal high-voltage 5V LDO or leave unconnected/connect to ground when the EXTVDD pin is not used. Connect a 2.2 $\mu$ F low-ESR ceramic capacitor between EXTVDD and AGND. EXTVDD can be connected to an external supply.                                                           |

| 12            | PSH    | Phase Shedding Threshold Programming pin. Connect a resistor from PSH to AGND. The voltage drop across the resistor decides the phase shedding threshold.                                                                                                                                                                                                                 |

| 13            | TEMP   | Die Junction Temperature Sense Output pin from Internal Diode. Connect a 1 $\mu F$ capacitor from the TEMP pin to AGND.                                                                                                                                                                                                                                                   |

| 14            | OUTS   | Output Voltage Sense pin. It is required to connect the OUTS pin to output through a 10 k $\Omega$ resistor and decouple to ground with a 100 nF capacitor for $V_{OUT} \le 5V$ . For $V_{OUT} > 5V$ , it is required to connect the OUTS pin through a resistive divider from $V_{OUT}$ to AGND. The OUTS pin will set the correct frequency adaptive to output voltage. |

| 15            | DR     | Gate Driver Output pin for Output OVP Discharge MOSFET. One single event of overvoltage over the OVP upper threshold for a duration longer than 12 $\mu$ s sets DR = High. The MIC2133 has to be restarted by EN or VIN cycling.                                                                                                                                          |

| 16            | BST1   | Phase 1 Bootstrap Capacitor Connection pin. BST1 pin is the supply voltage input for the Phase 1 high-side MOSFET driver. Connect a 0.1 µF low-ESR ceramic capacitor between the BST1 pin and the SW1 pin.                                                                                                                                                                |

| 17            | DH1    | Phase 1 High-Side Gate Driver Output pin. Connect DH1 to the Phase 1 high-side MOSFET gate.                                                                                                                                                                                                                                                                               |

| 18            | SW1    | Phase 1 Switch Node Output pin. Connect one terminal of the Phase 1 inductor to the SW1 node.                                                                                                                                                                                                                                                                             |

TABLE 3-1: PIN FUNCTION TABLE (CONTINUED)

| Pin<br>Number | Symbol  | Description                                                                                                                                                                                                                                                          |

|---------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19            | DL1     | Phase 1 Low-Side Gate Driver Output pin. Connect DL1 to the Phase 1 low-side MOSFET gate.                                                                                                                                                                            |

| 20            | PGND    | Power Ground pin. PGND is the return path for the low-side MOSFET current and for the low-side MOSFET driver. Connect all the PGND pins together and connect to the power ground plane.                                                                              |

| 21            | PVDD    | PVDD is Supply pin for Low-Side MOSFET Driver. Connect to VDD through $2.2\Omega$ series resistor. Connect a minimum 4.7 $\mu$ F low-ESR ceramic capacitor from PVDD to PGND.                                                                                        |

| 22            | DL2     | Phase 2 Low-Side Gate Driver Output pin. Connect DL2 to Phase 2 low-side MOSFET gate.                                                                                                                                                                                |

| 23            | SW2     | Phase 2 Switch Node Output pin. Connect one terminal of the Phase 2 inductor to the SW2 node.                                                                                                                                                                        |

| 24            | DH2     | Phase 2 High-Side Gate Driver Output pin. Connect DH2 to the Phase 2 high-side MOSFET gate.                                                                                                                                                                          |

| 25            | BST2    | Phase 2 Bootstrap Capacitor Connection pin. The BST2 pin is the supply voltage input for the phase 2 high-side MOSFET driver. Connect a 0.1 µF low-ESR ceramic capacitor between the BST2 pin and the SW2 pin.                                                       |

| 26            | PG      | Open-Drain Power Good Output pin. PG is pulled to ground when the output voltage is below 80% of the target voltage. Pull-up to VDD through a 10 k $\Omega$ resistor to set logic to a high level when the output voltage is above 90% of the target voltage.        |

| 27            | RIP_INJ | Ripple Injection Node pin. Connect series RC network from the RIP_INJ pin to FBS for injecting sufficient ripple for stable operation. Also connect a preposition resistor from this pin to AGND to set the RIP_INJ pin voltage to its steady-state value.           |

| 28            | FBS     | Remote Feedback Input pin. Connect to midpoint of a resistor divider from output voltage to GFB to set the desired output voltage.                                                                                                                                   |

| 29            | GFB     | Ground Feedback Remote Sense pin. Connect Kelvin sense directly across the output capacitor ground through the low-side FB resistor ground connection.                                                                                                               |

| 30            | SS      | Soft Start Adjustment pin. Connect a capacitor from the SS pin to AGND to adjust soft start time. See more details in <b>Section 4.5.7 "Soft Start"</b> .                                                                                                            |

| 31            | FREQ    | Frequency Programming Input pin. Connect to ground through resistor set to the same switching frequency for each phase.                                                                                                                                              |

| 32            | DROOP   | Analog Output DROOP pin. This pin is for implementing the "Adaptive Voltage Positioning" feature. Connect a resistor from the DROOP pin to the feedback resistor divider. The DROOP voltage is proportional with inductor current for load currents greater than 0A. |

| _             | EP      | Exposed Pad pin. Connect it to AGND.                                                                                                                                                                                                                                 |

#### 4.0 FUNCTIONAL DESCRIPTION

#### 4.1 Control Architecture

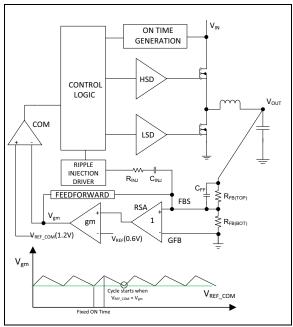

The MIC2133 is an adaptive on-time, dual phase, synchronous step-down DC/DC controller. It is designed to operate over a wide 8V to 75V input voltage range and provides a regulated output voltage. An adaptive on-time control scheme is employed in order to obtain a constant switching frequency and simplify the control compensation.

The MIC2133 has a differential remote sense amplifier with unity gain for sensing output voltage. The differential remote sense amplifier helps regulate the output voltage at target level, over the entire load range, by avoiding parasitic voltage drops on the PCB. The output of the differential amplifier will be used as output voltage to the controller. The output voltage is sensed across the MIC2133 device's feedback remote sense FBS pin and the ground feedback remote sense GFB pin via the voltage divider, and compared to a 0.6V reference voltage V<sub>REF</sub> at a low-gain transconductance  $(g_m)$  amplifier. The output of the gm amplifier,  $V_{qm}$ , is, then, further compared with another 1.2V reference, V<sub>REF COM</sub>, at the error comparator. If the feedback voltage decreases and the output of the g<sub>m</sub> amplifier is below 1.2V, then the error comparator will trigger the control logic and generate an on-time period. The on-time period length is predetermined by the  $T_{ON1}$  and T<sub>ON2</sub> generation circuitries for Phase 1 and Phase 2, respectively.

#### **EQUATION 4-1:**

$$T_{ON(EST)} = \frac{V_{OUT}}{V_{IN} \times f_{SW}}$$

Where:

$V_{OUT}$  = Output Voltage

$V_{IN}$  = Power Stage Input Voltage

$f_{SW}$  = Switching Frequency of Each Phase

The internal logic starts maintaining the same switching frequency and phasing for each phase (180° for two phases).

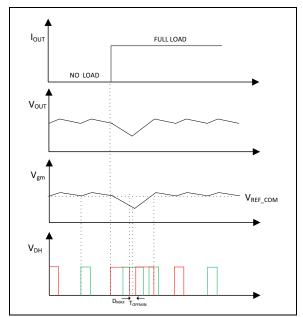

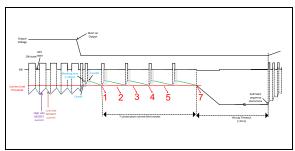

Figure 4-1 shows the MIC2133 control loop timing during steady-state operation. During steady-state operation, the  $g_{\rm m}$  amplifier senses the feedback voltage ripple, which is proportional to the output voltage ripple and the external ripple from the RIP\_INJ pin, injected to the FBS node at the turn-on instant of each phase. When the output of the  $g_{\rm m}$  error amplifier falls below the reference voltage, the on-time period is triggered. The on-time of Phase 1 is determined by the  $T_{\rm ON1}$  generator. The Phase 1  $T_{\rm ON1}$  generator also includes the current sharing error between phases. The Phase 1 high-side driver turns on the Phase 1 high-side FET during  $T_{\rm ON1}$ .

The Phase 1 high-side FET turn-off instant depends on both the T<sub>ON</sub> estimation and current sharing error. At the end of Phase 1 T<sub>ON1</sub>, the internal high-side driver turns off the Phase 1 high-side FET and the low-side driver turns on the Phase 1 low-side FET. The Phase 1 off-time period length depends upon the feedback voltage error in the next cycle for Phase 1. When the output of the g<sub>m</sub> error amplifier falls below the reference voltage in the second cycle, the Phase 2 on-time period is triggered. The on-time of Phase 2 is determined by the  $T_{ON2}$  generator. The Phase 2  $T_{ON2}$  generator also includes the current sharing error between phases. The Phase 2 high-side driver turns on the Phase 2 high-side FET during T<sub>ON2</sub>. The high-side FET turn-off instant depends on both the TON estimation and current sharing error. At the end of Phase 2 TON2, the internal high-side driver turns off the Phase 2 high-side FET and the low-side driver turns on the Phase 2 low-side FET. The duration of the Phase 2 off-time period depends upon the feedback voltage error in the next Phase 2 cycle. The above cycles repeat in a daisy-chain ring, and both phases support the load current alternately and maintain output voltage. In steady-state operation,  $T_{ON1} = T_{ON2}$ ,  $T_{OFF1} = T_{OFF2}$ and this way, the resulting phase difference is 180 degrees.

If the off-time period determined by the feedback voltage is less than the Minimum Off-Time,  $T_{OFF(MIN)}$ , which is about 360 ns, then the MIC2133 control logic will apply the  $T_{OFF(MIN)}$  instead to either phase. The minimum  $T_{OFF(MIN)}$  period is required to maintain enough energy in the Boost Capacitor ( $C_{BST}$ ) to drive the high-side MOSFET.

The maximum duty cycle is obtained from the 360 ns  $T_{OFF(MIN)}$ :

#### **EQUATION 4-2:**

$$D_{MAX} = \frac{T_S - T_{OFF(MIN)}}{T_S} = 1 - \frac{360 \text{ ns}}{T_S}$$

Where:

$T_S = 1/f_{SW}$

It is not recommended to use the MIC2133 with an off-time close to  $T_{OFF(MIN)}$  during steady-state operation. It is recommended that Equation 4-2 be used to choose the  $T_S$  for a lower switching frequency when the  $D_{MAX}$  is reached if  $V_{IN}$  is very close to  $V_{OUT}$ , knowing that the buck converter duty cycle equals  $V_{OUT}$  divided by  $V_{IN}$ .

The actual on-time and the resulting switching frequency will vary with the part-to-part variation in the rise and fall times of the external MOSFETs, the output load current and the variations in the  $V_{DD}$  voltage. Also, the minimum  $T_{ON}$  results in a lower switching frequency in high  $V_{IN}$  to  $V_{OUT}$  applications, such as 28V to 1.0V.

**FIGURE 4-1:** Steady-State Operation (FB Ripple Shows Injected and ESR Ripple Only, Reactive Impedances Neglected).

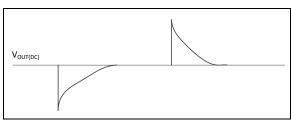

Figure 4-2 shows the operation of the MIC2133 during load transient. The output voltage drops due to the sudden load increase, which causes the V<sub>FBS</sub> to decrease and the output voltage of the  $\mathbf{g}_{\mathbf{m}}$  amplifier,  $\mathbf{V}_{\mathbf{gm}},$  to be less than V<sub>REF COM</sub>. This will cause the error comparator to trigger an on-time period. At the end of the on-time period, a Minimum Off-Time, TOFF(MIN), is generated to charge C<sub>BST</sub> because the feedback voltage is still below V<sub>REF</sub>. Then, the next on-time period is triggered and applies D<sub>MAX</sub> due to the low feedback voltage. Therefore, the switching frequency changes during the load transient to deliver D<sub>MAX</sub> and zero duty cycle when the high-current load disappears for both phases, but returns to the nominal fixed frequency once the output has stabilized at the new load current level. With the varying duty cycle and switching frequency, the output recovery time is fast and the output voltage deviation is small in the MIC2133 converter. The phases will overlap during load transient until the output voltage error is corrected. The transient response is shown in Figure 4-3.

**FIGURE 4-2:** MIC2133 Load Transient Response Timing.

FIGURE 4-3: MIC2133 Load Transient Response.

Unlike true Current-mode control, the MIC2133 uses the output voltage ripple to trigger an on-time period. The output voltage ripple is proportional to the inductor current ripple if the ESR of the output capacitor is large enough. To meet the stability requirements, the MIC2133 feedback voltage ripple must be in phase with the inductor current ripple, and large enough to be sensed by the  $g_{\text{m}}$  amplifier and the error comparator. The recommended feedback voltage ripple is 20 mV ~ 100 mV. If a low-ESR output capacitor is selected, then the feedback voltage ripple may be too small to be sensed by the g<sub>m</sub> amplifier and the error comparator. Also, the output voltage ripple and the feedback voltage ripple are not necessarily in phase with the inductor current ripple if the ESR of the output capacitor is very low. In these cases, ripple injection is required to ensure proper operation.

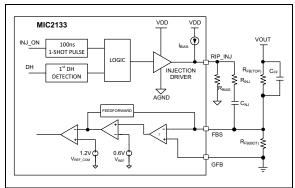

#### 4.2 Start-up Into Pre-Bias Load

To get proper pre-bias start-up performance, the voltage at the junction of CINI and RINI needs to be at its steady-state value when the device starts switching. This is done by biasing the RIP\_INJ pin voltage using a current source (I<sub>BIAS</sub>) at the RIP\_INJ pin and a resistor (R<sub>BIAS</sub>) at the RIP\_INJ pin before the device starts switching. The Injection (INJ) driver will be in High-Impedance mode before the device starts switching. This results in a voltage equal to  $I_{BIAS} x R_{BIAS}$  at the RIP INJ pin before switching starts. This voltage charges the  $C_{INJ}$  cap to the value of  $I_{BIAS}$  x  $R_{BIAS}$ . As the C<sub>INJ</sub> takes time to charge to the final voltage, depending on the  $C_{INJ}$  x  $(R_{INJ}$  +  $R_{FB(BOT)}$ ), the  $I_{BIAS}$  must be enabled before the switching starts. The MIC2133 has a POK delay of ≈4 ms (i.e., when EN is high, the device starts switching after ≈4 ms). Therefore, this 4 ms delay is enough to charge C<sub>INJ</sub> to the final value. Once the device starts switching, the IBIAS will no longer have any effect, as the INJ driver will be either high or low (the INJ driver will not be in High-Impedance mode when the device starts switching).

**FIGURE 4-4:** Circuit to Obtain Proper Pre-Bias Start-Up Performance and Ripple Injection.

$I_{BIAS}$  is an internal current source.  $R_{BIAS}$  is an external resistor from RIP\_INJ to AGND.  $R_{BIAS}$  can be calculated using the formula below:

#### **EQUATION 4-3:**

$$R_{BIAS} = \frac{5V \times 100 \text{ ns } \times f_{SW}}{I_{BIAS}}$$

Where:

$5Vx\ 100\ ns\ xf_{SW}\ =\ {

m Average\ Voltage\ on\ the\ RIP\_INJ\ Pin}$

Note that as  $R_{BIAS}$  is always present, it draws an additional current from the injection driver when the RIP\_INJ pin is 5V for 100 ns. This adds to the device's  $I_Q$ . However, its contribution to the device's  $I_Q$  will be low, because this current will be present for 100 ns only. Another thing to note is that the INJ driver must be capable of supplying this additional current.

#### 4.3 Stability Analysis

The MIC2133 uses ripple-based constant on-time architecture to generate switching pulses. The magnitude of the ripple needs to be in the range of 20 mV to 100 mV. To avoid ripple voltage variation with input voltage, the ripple voltage is injected from the third node through the RIP\_INJ pin. The figure below shows the ripple injection at the FBS node with respect to the reference voltage.

**FIGURE 4-5:** MIC2133 Ripple Injection at FBS Node.

The output capacitors generally have three components. The capacitive ripple lags the inductor current ripple. The ESR ripple is in phase with the inductor current. The ESL ripple effect is very minimal in low-voltage capacitors.

## 4.4 Ripple Injection Circuit Components Selection

Follow the steps below for selecting the ripple injection circuit components if low-ESR output capacitors are used. The below procedures provide a good starting point for selecting the ripple injection components. It is recommended that the final values be confirmed by laboratory measurements.

Calculate the product of R<sub>INJ</sub> and C<sub>FF</sub> for a given injected Feedback Ripple Voltage, ΔV<sub>FB</sub>, using the equation below. Choose ΔV<sub>FB</sub> in the range from 40 mV to 500 mV. A good starting point for ΔV<sub>FB</sub> is 50 mV.

#### **EQUATION 4-4:**

$$R_{INJ} \times C_{FF} = \frac{5V \times 100ns}{\Delta V_{FB}}$$

Where:

$\Delta V_{FB}$  = Injected Feedback Ripple Voltage

- 2. Choose C<sub>FF</sub> in the range from 0.47 nF to 10 nF.

- 3. Calculate R<sub>IN.I</sub> using the equation above.

- Calculate the Top Feedback Resistor, R<sub>FB(TOP)</sub>, value using the equation below:

#### **EQUATION 4-5:**

$$R_{FB(TOP)} \ge \frac{1}{2 \times \pi \times C_{FF} \times 0.8 \times f_{LC}}$$

Where

$f_{LC}$  = LC Resonant Frequency = 1/(2 x  $\pi$  x sqrt (L x C<sub>OUT</sub>))

Calculate the Bottom Feedback Resistor, R<sub>FB(BOT)</sub>, value using the equation below:

#### **EQUATION 4-6:**

$$R_{FB(BOT)} = \frac{R_{FB(TOP)}}{\left\lceil \frac{V_{OUT}}{V_{BEE}} - 1 \right\rceil}$$

Where:

$V_{OUT}$  = Target Output Voltage

$V_{RFF}$  = Reference Voltage = 0.6V for MIC2133

Estimate the crossover frequency using the following equation. If f<sub>CO(EST)</sub> is above f<sub>SW</sub>/5, lower the C<sub>FF</sub> value and repeat procedure 6.

#### **EQUATION 4-7:**

$$f_{CO(EST)} = \frac{R_{INJ} \times C_{FF}}{\pi \times L \times C_{OUT}} \times \frac{V_{OUT} \times 10^6}{f_{SW}}$$

Where:

L = Inductance

$C_{OUT}$  = Output Capacitance

$V_{OUT}$  = Output Voltage

$f_{SW}$  = Switching Frequency

7a) Select C<sub>INJ</sub> using the below equation if f<sub>CO(EST)</sub> calculated above meets Equation 5-11.

#### **EQUATION 4-8:**

$$C_{INJ} \ge \frac{1}{0.8 \times R_{INJ} \times f_{CO(EST)}}$$

Add a resistor in parallel with the soft start capacitor, connected to the SS pin, if

$C_{INJ} > C_{FF} \times (R_{FB(TOP)}/R_{FB(BOT)}).$

This ensures that there is no overshoot at the end of the soft start. Use the equation below to select the parallel resistor value.

#### **EQUATION 4-9:**

$$R_{SS} \ge \frac{0.8V}{I_{SS}}$$

Where:

$I_{SS}$  = Soft Start Current Source = 1.2  $\mu$ A

7b) Select  $C_{INJ}$  using the below guidelines if  $f_{CO(EST)}$  is low (typically below  $f_{SW}/15$ ) when  $f_{CO}$  is limited by the minimum  $\Delta V_{FB}$  required in lower  $V_{OUT}$  applications. Assume  $f_{CO} = f_{SW}/10$ . Calculate the maximum Equivalent Series Resistance (ESR) of the output capacitor using the following equation.

#### **EQUATION 4-10:**

$$ESR_{COUT} \le \frac{\Delta V_{OUT\_TRANS}}{\Delta I_{LOAD\_STEP}}$$

Where:

$\Delta I_{LOAD\_STEP}$  = Magnitude of the Load Transient

$\Delta V_{OUT\_TRANS}$  = Acceptable Output Voltage Deviation during Load Transient

Calculate the output capacitance using the following equation.

#### **EQUATION 4-11:**

$$C_{OUT} \ge \frac{1}{\pi \times f_{CO} \times ESR_{COUT}}$$

Calculate C<sub>INJ</sub> using the following equation.

#### **EQUATION 4-12:**

$$C_{INJ} = C_{FF} \times \frac{ESR_{COUT}}{2 \times \pi \times f_{CO} \times L} \times \frac{V_{OUT}}{5V \times 100 \; ns \times f_{SW}}$$

Using too low a  $C_{\text{INJ}}$  may result in oscillations at the beginning of the soft start. These oscillations can be reduced either by using a higher  $C_{\text{INJ}}$  or  $C_{\text{OUT}}$  by reducing the feedback ripple.

#### 4.5 Detailed Device Description

## 4.5.1 CURRENT BALANCING BETWEEN PHASES

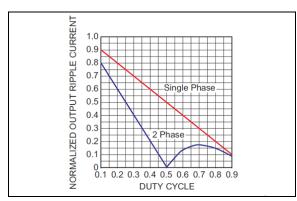

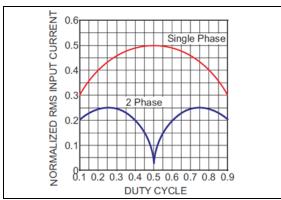

One important benefit of the two-phase operation is the thermal advantage gained by distributing the heat over multiple devices and a greater PCB area. By doing this, the system designer avoids the complexity of driving parallel MOSFETs and the expense of using expensive heatsinks.

To accomplish the thermal advantage, it is important that each phase carries the same amount of current at any load level. In the MIC2133, both phase currents are sensed across a low-side MOSFET,  $R_{\rm DS(ON)}$ , during off-time. The low-side MOSFET current is tracked during off-time and held close to peak value in the valley point. The average current information is generated by summing all the phases' sensed currents and dividing by the number of phases (two for two phases). An error current per phase is generated by making the difference between the average current information and each phase current, which is used to modulate  $T_{\rm ON1}$  and  $T_{\rm ON2}$  to cancel the error in the current sharing.

FIGURE 4-6: MIC2133 Current Sharing Circuit.

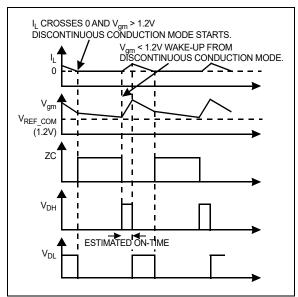

#### 4.5.2 HyperLight Load (HLL) MODE

The MIC2133 always operates in Continuous Conduction Mode (CCM) and both phases support the load current equally at high loads. To operate the system at a higher efficiency, the MIC2133 will shed the Phase 2 when the load current drops below the programmed threshold level, below the full load current value. In CCM mode, the inductor current can go negative at light loads. However, at light loads, the MIC2133 is able to force the inductor current to operate in Discontinuous Conduction Mode (DCM) when it operates in HLL mode. In HLL mode, the efficiency is optimized by shutting down all the non-essential circuits and minimizing the supply current. The MIC2133 wakes up and turns on the high-side MOSFET when the Feedback Voltage,  $V_{FBS}$ , drops and  $V_{gm}$  is below  $V_{REF\_COM}$  (1.2V).

The MIC2133 has a Zero-Crossing (ZC Detection) comparator that monitors the inductor current by sensing the voltage drop across the low-side MOSFET during its on-time. If  $V_{gm} > V_{REF\_COM}$  and the inductor current goes slightly negative, the MIC2133 automatically powers down most of the IC circuitry and goes into a Low-Power mode.

Once the MIC2133 goes into DCM mode, both the high-side and low-side MOSFETs are kept in the OFF state. Then, the load current is supplied by the output capacitors and  $V_{OUT}$  drops. If the load current is sufficiently large, the drop of  $V_{OUT}$  causes  $V_{FBS}$  to drop and  $V_{gm}$  to go below  $V_{REF\_COM}$  (1.2V), and the high-side MOSFET is turned on for  $T_{ON}$ . Then, at the end of the  $T_{ON}$  period, the low-side MOSFET is turned on for  $T_{OFF}$  until the next  $T_{ON}$  starts because the inductor current during the low-side MOSFET on-time is larger than zero. Then, the cycle repeats and all the circuits wake-up into normal CCM mode. The following figure shows the control loop timing in DCM mode.

During DCM mode, the bias current of most circuits is reduced. As a result, the total power supply current during DCM mode is only about 400  $\mu$ A, allowing the MIC2133 to achieve high efficiency in light load applications.

FIGURE 4-7: MIC2133 Control Loop Timing in Discontinuous Conduction Mode.

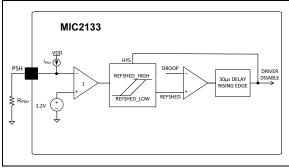

#### 4.5.3 PHASE SHEDDING

To achieve higher efficiency at lighter medium loads, the Phase 2 is shed off when the DROOP Voltage,  $V_{DROOP}$ , drops below the Phase 2 shed-off threshold, and the DROOP voltage is equal to eight times the current sensing voltage in Phase 1. The Phase 2 is shed on when the DROOP voltage rises above the Phase 2 shed-on threshold.

The phase shedding thresholds for on and off are calculated using the following formulas in the equation below.

#### **EQUATION 4-13:**

$$V_{SHED\_ON} = 1.2V - V_{PSH}$$

$V_{SHED\_OFF} = 0.8 \times V_{SHED\_ON}$

Where:

$V_{PSH}$  = PSH Pin Voltage Programmable by an External Resistor

As shown in Figure 4-8, the PSH pin voltage can be programmed by an external resistor connected from the PSH pin to AGND using the equation below.

#### **EQUATION 4-14:**

$$V_{PSH} = I_{PSH} \times R_{PSH}$$

Where:

$I_{PSH}$  = PSH Current Source (10  $\mu$ A typical)

$R_{PSH}$  = Resistor Connected from PSH Pin to AGND

FIGURE 4-8:

Phase Shedding Circuit.

The output load currents at which the secondary phase will be turned on and off can be calculated from Equation 5-39.

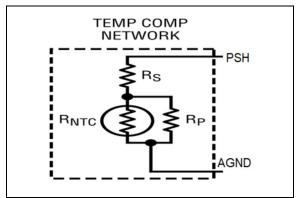

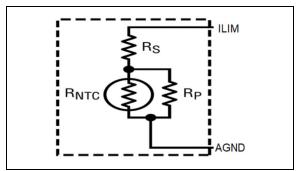

The reason for this indirect way for setting phase shedding thresholds is the fact that the DROOP pin voltage has a strong positive temperature coefficient in case the bottom FETs  $R_{DSON}$  are used for sensing current. To keep the shedding level constant in the current level with temperature, an NTC resistor can be used to generate a  $V_{PSH}$  voltage with a negative temperature coefficient, which becomes a positive temperature coefficient identical to the temperature coefficient of the DROOP voltage when the  $R_{DSON}$  of bottom FETs are used (see Equation 4-13). Also, the NTC resistor must be placed close to the Phase 1 bottom FETs to pick up the temperature of the FET.

#### **EQUATION 4-15:**

$$\frac{dV_{SHED}}{dT} = -\frac{dV_{PSH}}{dT} = \frac{dV_{DROOP}}{dT} = \frac{I_{LOAD} \times dR_{DSON}}{dT}$$

The equation above is a description of the necessary temperature coefficient of  $V_{PSH}$ , achieved externally using an NTC resistor on the PSH pin, combined with a zero temperature coefficient 10  $\mu$ A current source.

If sensing is done with a sense resistor in series with the bottom FET, then no NTC resistor is needed on the PSH pin and sizing the shedding of the secondary phase (Phase 2) is done using Equation 4-13.

If no phase shedding is desired, then the PSH pin is floating and will go to  $V_{DD}$ , and internally, the level will be sensed and the secondary shedding will not be done

If the PSH pin is externally driven between 0V and 5V, then an externally controlled action on the shedding can be done. In that case, the system designers need to decide when the secondary is shed based on the information about the load they obtained on their own at the system level.

Shedding the secondary phase will be an action conditioned by a hysteresis on the shedding threshold voltage and a delay of approximately 30 µs.

Going out of shedding for the secondary phase will be done at maximum speed to generate a good response in case of a load transient.

After the phase shedding is done, the host phase (Phase 1) will automatically allow the DCM mode if needed by the circuit. Also, the RIP\_INJ pulse will have 200 ns to keep the correct prepositioning when adding back the Phase 2. The shedding Phase 2 will not add any RIP\_INJ pulse. When the Phase 2 is working again, the device controller will disable the DCM mode and go into CCM completely.

The figure below is an example of a resistance network on the PSH pin using an NTC resistor and ensuring the temperature compensation of phase-shedding action.

**FIGURE 4-9:** Temperature Compensation Network on the PSH Pin.

## EXAMPLE 4-1: CALCULATION of R<sub>PSH</sub> BASED ON BOTTOM FET CURRENT SENSING

- Supposing that a 25°C nominal load current generates a voltage drop of V<sub>DS</sub> = 75 mV at 25°C on the bottom FET used for sensing current.

- Then, for that level of nominal load,

V<sub>DROOP</sub> = 8 \* 75 mV = 600 mV at 25°C.

- V<sub>DROOP</sub> ≈1.2V at 125°C in the defined case above because the R<sub>DSON</sub> is 2x greater and V<sub>DS</sub> =150 mV at 125°C.

- In the case of wanting to shed the secondary phase at 0.5 \* nominal load, then the shedding threshold at 25°C needs to be +300 mV. It will become +600 mV at 125°C if it is temperature compensated.

- From Equation 4-13, it can be derived that the imposed V<sub>PSH</sub> = 1.2V - 1.25 \* 0.3V = 0.825V at 25°C. From Equation 4-14,

$R_{PSH} = 0.825 V/10 \mu A = 82.5 k\Omega$  at 25°C.

At 125°C, the necessary shedding threshold is 600 mV, which requires

$V_{PSH}$  = 1.2V – 1.25 \* 0.6V = 0.45V at 125°C and the programming resistor on the PSH pin,

$R_{PSH}$  = 0.45V/10  $\mu A$  = 45 k $\Omega$  at 125°C. Then, the temperature compensation network with the NTC resistor can be linearized based on the  $R_{PSH}$  values at 25°C and 125°C.

The MIC2133 can also be used to report the average output current via the CSH pin while working with a PMBus <sup>™</sup> macro. While working with a PMBus macro, DCM and phase shedding need to be disabled through the PSH pin. The die temperature is reported through the TEMP pin, the input voltage is reported through the VIN pin and the output voltage is reported via the Output Sense (OUTS) pin while working with a PMBus macro.

#### 4.5.4 CURRENT LIMIT

The MIC2133 uses the  $R_{DS(ON)}$  of the external low-side power MOSFET to sense overcurrent conditions, or a sense resistor inserted with the source of the bottom FET can be used for more accurate results and does not require temperature compensation. The bottom FET  $R_{DS(ON)}$  sensing method will avoid adding cost, use of additional board space and power losses taken by a discrete current sense resistor.

The current limit threshold can be programmed by connecting a resistance from the ILIM pin to AGND. Both phases use the same current limit threshold.

FIGURE 4-10: MIC2133 Current-Limiting Circuit.

The MIC2133 forces a constant 9.6  $\mu$ A current through the resistor tied from the ILIM pin to AGND to program  $V_{ILIM}$ .

In each switching cycle of both phases of the MIC2133 converter, the inductor valley current is sensed by monitoring the V<sub>DS</sub> voltage across the low-side MOSFET during the off period. There is a 150 ns (typical) blanking period before each current sense signal considered for protection. The blanking period improves noise immunity. If the valley low-side MOSFET current is greater than the current limit threshold current for seven consecutive cycles in either phase, then the MIC2133 turns off the high-side MOSFET of both phases and a soft start sequence is triggered after the hiccup timer has expired. This mode of operation, called Hiccup mode, and its purpose is to protect the downstream load in case of a hard short. The figure below illustrates the MIC2133 operation during overload conditions. When the load current is increased gradually, the inductor current also increases, as shown in the figure below. When the load current is around the current limit threshold, the high-side and the low-side MOSFET current can be higher than the current limit, as highlighted in the figure below as Case#1. In Case#1, even though the low-side MOSFET instantaneous current exceeds the current limit threshold for some duration, the low-side MOSFET current is lower than the current limit at the end of the blanking time of 150 ns. This causes the MIC2133 to not enter the current limit protection and initiate the next high-side MOS-FET turn-on cycle. After the high-side MOSFET is turned on, the current ramps up to a value that is determined by the operating duty cycle and inductor value. When the high-side MOSFET is turned off and the low-side MOS-FET is turned on, as shown as Case#2 in the figure below, the current through the low-side MOSFET is higher than the current limit for seven consecutive cycles. This causes the MIC2133 to enter the current limit protection.

As shown in the figure below, the inductor valley current is higher than the current limit threshold as the MIC2133 senses the low-side MOSFET current.