#### 4 Data Lane 2:1 MIPI Switch

#### **Features**

10-Channel 2:1 Switch

Signal Types: MIPI, D-PHY & C-PHY

Supply Voltage Range(Vcc): 1.65V to 5.0V

Input Signals: 0V to 1.3V

Ron: 7Ω Typical

ΔR<sub>ON</sub>: 0.1Ω Typical

I<sub>CC</sub>: 25µA Typical

-3dB Bandwidth: 2.1 GHz Typical

Low Crosstalk: -30 dB Typical

Low Off Isolation: −23 dB Typical

Con: 3 pF Typical

## **General Description**

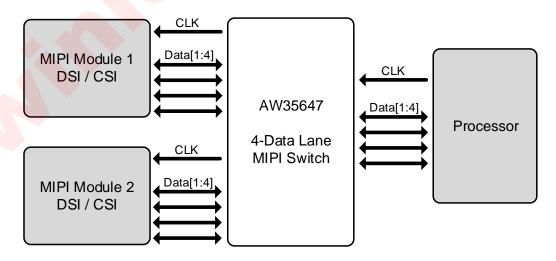

The AW35647 is a four-data-lane MIPI D-PHY switch. The AW35647 can also be configured as three-data-lane MIPI C-PHY switch.

This 10 channel single-pole double-throw switch is optimized for high speed MIPI applications. The AW35647 is designed to facilitate multiple MIPI compliant devices to connect to a CSI or DSI module.

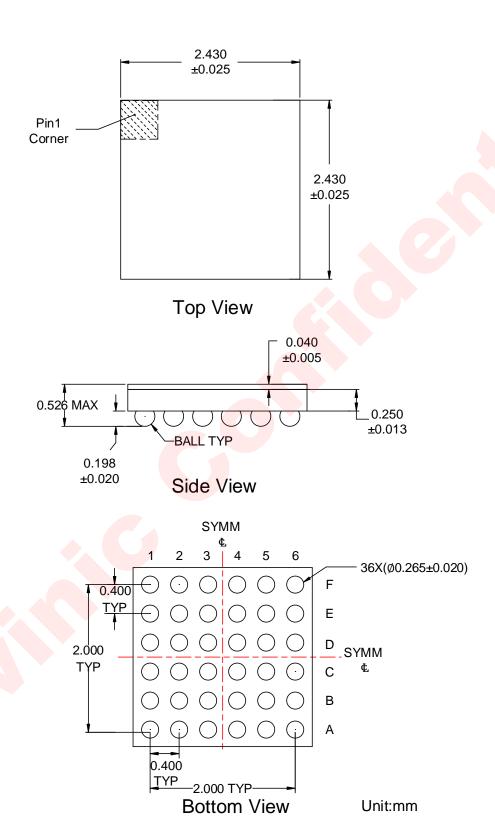

The AW35647 is available in a WLCSP 2.43mmX2.43mmX0.488mm-36B package.

## **Applications**

- Smartphones

- Tablets

- Laptops

- Displays

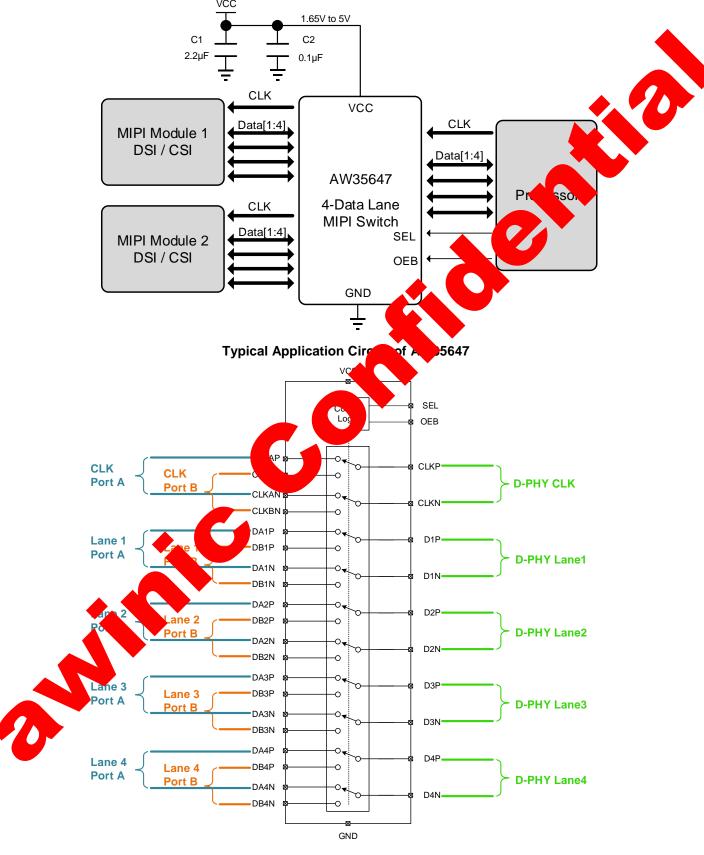

## **Typical Application Circuit**

**Typical Application Circuit of AW35647**

All the trademarks mentioned in the document are the property of their owners.

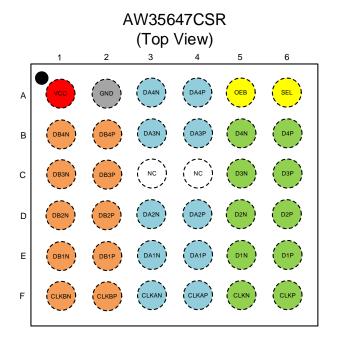

# **Pin Configuration And Top Mark**

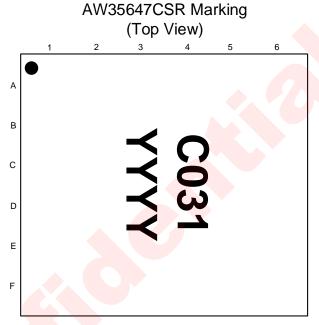

C031 - AW35647CSR

YYYY - Production Tracing Code

Pin Configuration and Top Mark

#### **Pin Definition**

| PIN | NAME | DESCRIPTION                        |

|-----|------|------------------------------------|

| A1  | VCC  | Power supply input                 |

| A2  | GND  | Ground                             |

| A3  | DA4N | A side data port 4, differential - |

| A4  | DA4P | A side data port 4, differential + |

| A5  | OEB  | Output enable, active low          |

| A6  | SEL  | Channel select                     |

| B1  | DB4N | B side data port 4, differential - |

| B2  | DB4P | B side data port 4, differential + |

| B3  | DA3N | A side data port 3, differential - |

| B4  | DA3P | A side data port 3, differential + |

| B5  | D4N  | Common data port 4, differential - |

| B6  | D4P  | Common data port 4, differential + |

# **Pin Definition (Continued)**

| PIN | NAME  | DESCRIPTION                        |

|-----|-------|------------------------------------|

| C1  | DB3N  | B side data port 3, differential - |

| C2  | DB3P  | B side data port 3, differential + |

| C3  | NC    | No connect                         |

| C4  | NC    | No connect                         |

| C5  | D3N   | Common data port 3, differential - |

| C6  | D3P   | Common data port 3, differential + |

| D1  | DB2N  | B side data port 2, differential - |

| D2  | DB2P  | B side data port 2, differential + |

| D3  | DA2N  | A side data port 2, differential - |

| D4  | DA2P  | A side data port 2, differential + |

| D5  | D2N   | Common data port 2, differential - |

| D6  | D2P   | Common data port 2, differential + |

| E1  | DB1N  | B side data port 1, differential - |

| E2  | DB1P  | B side data port 1, differential + |

| E3  | DA1N  | A side data port 1, differential - |

| E4  | DA1P  | A side data port 1, differential + |

| E5  | D1N   | Common data port 1, differential - |

| E6  | D1P   | Common data port 1, differential + |

| F1  | CLKBN | B side clock port, differential -  |

| F2  | CLKBP | B side clock port, differential +  |

| F3  | CLKAN | A side clock port, differential -  |

| F4  | CLKAP | A side clock port, differential +  |

| F5  | CLKN  | Common clock port, differential -  |

| F6  | CLKP  | Common clock port, differential +  |

## **Pin Functions**

| OEB | SEL | Function                            |  |

|-----|-----|-------------------------------------|--|

| Н   | Х   | Clock and Data ports High Impedance |  |

| L   | L   | CLKP/N=CLKAP/N, DnP/N=DAnP/N        |  |

| L   | Н   | CLKP/N=CLKBP/N, DnP/N=DBnP/N        |  |

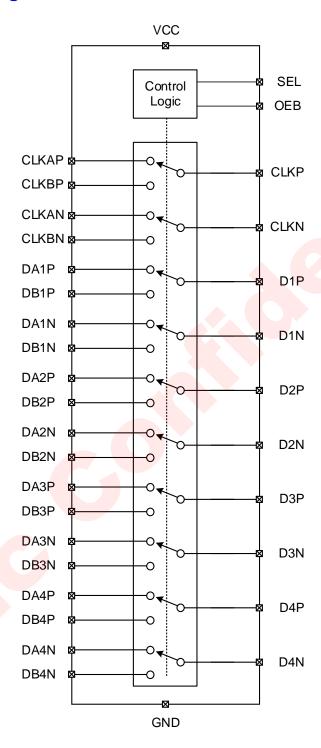

# **Functional Block Diagram**

**Functional Block Diagram**

# **Typical Application Circuits**

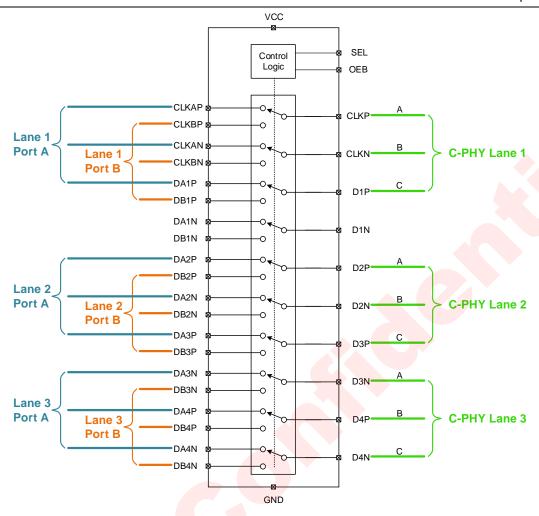

Recommended D-PHY Configuration of AW35647

#### Recommended C-PHY Configuration of AW35647

The control inputs OEB,SEL must be held HIGH or LOW, and cannot be left floating

# **Ordering Information**

| Part Number | Temperature | Package                                | Marking | Moisture<br>Sensitivity<br>Level | Environmental<br>Information | Delivery Form                |

|-------------|-------------|----------------------------------------|---------|----------------------------------|------------------------------|------------------------------|

| AW35647CSR  | -40°C∼85°C  | WLCSP<br>2.43mmX2.43mm<br>X0.488mm-36B | C031    | MSL1                             | ROHS+HF                      | 3000 units/<br>Tape and Reel |

# **Absolute Maximum Ratings**(NOTE1)

| PARAMETER                          | PARAMETERS                                              |               |  |  |  |  |

|------------------------------------|---------------------------------------------------------|---------------|--|--|--|--|

| Supply voltage ran                 | ge Vcc                                                  | -0.3V to 6V   |  |  |  |  |

| Input/Output DC switch vol         | tage V <sub>I/O</sub> (NOTE2)                           | -0.3V to 6V   |  |  |  |  |

| Input voltage range                | SEL, OEB                                                | -0.3V to 6V   |  |  |  |  |

| Junction-to-ambient therma         | I resistance θ <sub>JA</sub>                            | 61°C/W        |  |  |  |  |

| Maximum operating junction to      | emperature T <sub>JMAX</sub>                            | 150°C         |  |  |  |  |

| Operating free-air tempe           | rature range                                            | -40°C to 85°C |  |  |  |  |

| Storage temperature                | Storage temperature T <sub>STG</sub>                    |               |  |  |  |  |

| Lead temperature (soldering        | Lead temperature (soldering 10 seconds)                 |               |  |  |  |  |

|                                    | ESD                                                     |               |  |  |  |  |

| Human Body Model (All pins, per AN | Human Body Model (All pins, per ANSI/ESDA/JEDEC JS-001) |               |  |  |  |  |

| Charged Device Model (All pins,    | Charged Device Model (All pins, per JESD22-C101)        |               |  |  |  |  |

| Machine Model (All pins, per       | ±200V                                                   |               |  |  |  |  |

|                                    | •                                                       |               |  |  |  |  |

| Test condition: JED                | DEC78                                                   | ±200mA        |  |  |  |  |

NOTE1: Conditions out of those ranges listed in "absolute maximum ratings" may cause permanent damages to the device. In spite of the limits above, functional operation conditions of the device should within the ranges listed in "recommended operating conditions". Exposure to absolute-maximum-rated conditions for prolonged periods may affect device reliability.

NOTE2: V<sub>I/O</sub> refers to analog data/clock switch ports

## **Electrical Characteristics**

$T_A = -40$ °C to 85°C unless otherwise noted. Typical values are guaranteed for  $V_{CC} = 3.3$ V  $T_A = 25$ °C.

| F                      | PARAMETER                                                                    | TEST CONDITION                                                                   | MIN  | TYP | MAX | UNIT |

|------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------|-----|-----|------|

| Vcc                    | Supply voltage                                                               |                                                                                  | 1.65 | 3.3 | 5.0 | V    |

| Icc                    | Active supply current                                                        | OEB=0V, SEL=0V or Vcc                                                            |      | 25  | 45  | μΑ   |

| I <sub>CC_PD</sub>     | Standby supply current                                                       | OEB=V <sub>CC</sub> , SEL=0V or V <sub>CC</sub>                                  |      |     | 1   | μA   |

| I <sub>CC_PD_1.5</sub> | Standby supply current                                                       | Vcc=5V<br>OEB=1.5V, SEL=0V or Vcc                                                |      | 1   |     | μА   |

| DC Characte            | eristics                                                                     |                                                                                  | 1    |     |     |      |

| Ron_hs                 | On-state resistance for                                                      | V <sub>I/O</sub> =0.2V, I <sub>ON</sub> =8mA<br>Vcc=1.65V                        |      | 7   | 11  | Ω    |

| KON_HS                 | high speed MIPI mode                                                         | V <sub>I/O</sub> =0.2V, I <sub>ON</sub> =8mA<br>V <sub>CC</sub> =1.8V to 5.0V    |      | 7   | 11  | Ω    |

| Ron lp                 | On-state resistance for                                                      | V <sub>I/O</sub> =1.2V, I <sub>ON</sub> =8mA<br>V <sub>CC</sub> =1.65V           |      | 8   | 12  | Ω    |

| TKON_LP                | low power MIPI mode                                                          | V <sub>I/O</sub> =1.2V, I <sub>ON</sub> =8mA<br>V <sub>CC</sub> =1.8V to 5.0V    |      | 7.5 | 12  | Ω    |

| ΔRon_Hs                | On-state resistance<br>match between<br>channels for high speed<br>MIPI mode | V <sub>I/O</sub> =0.2V, I <sub>ON</sub> =8mA                                     |      | 0.1 |     | Ω    |

| $\Delta R_{ON\_LP}$    | On-state resistance<br>match between<br>channels for low power<br>MIPI mode  | V <sub>I/O</sub> =1.2V, I <sub>ON</sub> =8mA                                     |      | 0.1 |     | Ω    |

| Ron_flat_hs            | ON-state resistance<br>flatness for high speed<br>MIPI mode                  | V <sub>I/O</sub> =0V to 0.3V, I <sub>ON</sub> =8mA                               |      | 0.9 |     | Ω    |

| Ron_flat_lp            | ON-state resistance<br>flatness for low power<br>MIPI mode                   | V <sub>I/O</sub> =0V to 1.3V, I <sub>ON</sub> =8mA                               |      | 0.9 |     | Ω    |

| loff                   | Switch off leakage current                                                   | Vcc=1.65V to 5.0V OEB, SEL=0V or 5.0V Dn,CLKn,DAn,CLKAn,DBn, CLKBn=0V to 1.3V    | -0.5 |     | 0.5 | μΑ   |

| Ion                    | Switch on leakage current                                                    | Vcc=1.65V to 5.0V OEB=0V, SEL=0V or 5.0V Dn,CLKn,DAn,CLKAn,DBn, CLKBn=0V to 1.3V | -0.5 |     | 0.5 | μА   |

# **Electrical Characteristics (Continued)**

$T_A = -40$ °C to 85°C unless otherwise noted. Typical values are guaranteed for  $V_{CC} = 3.3$ V  $T_A = 25$ °C.

|             | PARAMETER                                        | TEST CONDITION                                                                                                        | MIN  | TYP | MAX | UNIT |

|-------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------|-----|-----|------|

| Digital Cha | aracteristics                                    |                                                                                                                       |      |     |     |      |

| VIH         | Input logic high (SEL, OEB)                      | V <sub>CC</sub> =1.65V to 5.0V                                                                                        | 1.3  |     |     | V    |

| VIL         | Input logic low<br>(SEL, OEB)                    | Vcc=1.65V to 5.0V                                                                                                     |      |     | 0.5 | V    |

| ILEAK_IN    | Input leakage<br>(SEL, OEB)                      | SEL,OEB=0V to 5.0V                                                                                                    | -0.5 |     | 0.5 | μΑ   |

| Cin         | Digital Input capacitance (SEL, OEB)             | f=1MHz                                                                                                                |      | 5   |     | pF   |

| Dynamic (   | Characteristics                                  |                                                                                                                       |      |     | •   |      |

| Con         | ON capacitance <sup>(NOTE3)</sup>                | OEB=0V,<br>Dn,CLKn,DAn,DBn,CLKAn,<br>CLKBn=0V or 0.2V                                                                 |      | 3   |     | pF   |

| Coff        | OFF capacitance <sup>(NOTE3)</sup>               | f = 750 MHz, switch ON  OEB=Vcc,  Dn,CLKn,DAn,DBn,CLKAn, CLKBn=0V or 0.2V  f = 750MHz, switch OFF                     |      | 2   |     | pF   |

| Oiso        | Differential off isolation <sup>(NOTE3)</sup>    | $R_L$ = 50 $\Omega$ , $C_L$ = 0pF<br>$V_{I/O}$ =200mV+200mV <sub>PP</sub><br>(differential)<br>f = 750MHz, switch OFF |      | -23 |     | dB   |

| Xtalk       | Differential Channel to channel crosstalk(NOTE3) | $R_L = 50\Omega$ , $C_L = 0pF$<br>$V_{I/O}=200mV+200mV_{PP}$<br>(differential)<br>f = 750MHz, switch ON               |      | -30 |     | dB   |

| BW          | -3dB bandwidth <sup>(NOTE3)</sup>                | $R_L = 50\Omega$ , $C_L = 0pF$<br>$V_{I/O}=200mV+200mV_{PP}$<br>(differential), switch ON                             | 1.6  | 2.1 |     | GHz  |

NOTE3: Guaranteed by characterization

# **Electrical Characteristics (Continued)**

$T_A = -40$ °C to 85°C unless otherwise noted. Typical values are guaranteed for  $V_{CC} = 3.3$ V  $T_A = 25$ °C.

|                   | PARAMETER                               | TEST CONDITION                                                             | MIN | TYP | MAX  | UNIT |

|-------------------|-----------------------------------------|----------------------------------------------------------------------------|-----|-----|------|------|

| Dynamic C         | haracteristics                          |                                                                            |     |     |      |      |

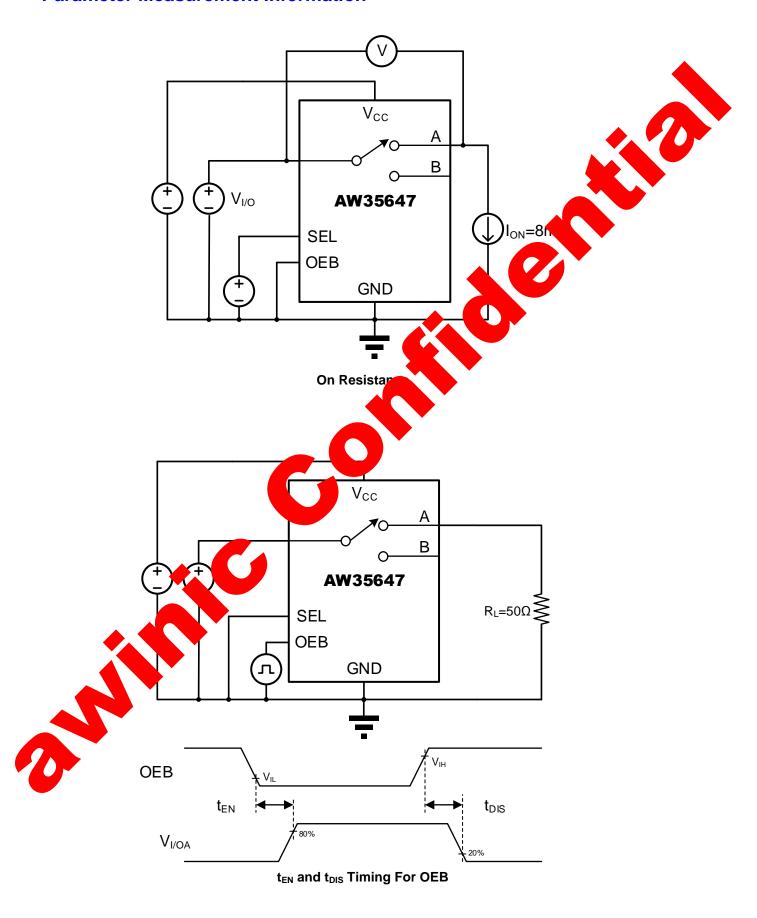

| t <sub>INIT</sub> | Initialization time (Vcc to output)     | Dn,CLKn=0.6V<br>DAn,DBn,CLKAn,CLKBn:<br>$R_L = 50\Omega$ , $C_L = 0$ pF    |     | 1.5 | 200  | μs   |

| ten               | Device turn on time<br>(OEB to output)  | Dn,CLKn=0.6V<br>DAn,DBn,CLKAn,CLKBn:<br>$R_L = 50\Omega$ , $C_L = 0$ pF    |     | 0.5 | 200  | μs   |

| t <sub>DIS</sub>  | Device turn off time<br>(OEB to output) | Dn,CLKn=0.6V<br>DAn,DBn,CLKAn,CLKBn:<br>$R_L = 50\Omega$ , $C_L = 0$ pF    |     | 150 | 250  | ns   |

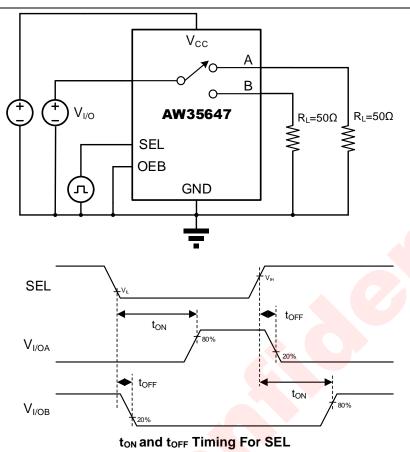

| ton               | Switch turn on time (SEL to output)     | Dn,CLKn=0.6V<br>DAn,DBn,CLKAn,CLKBn:<br>$R_L = 50\Omega$ , $C_L = 0$ pF    |     | 800 | 1600 | ns   |

| toff              | Switch turn off time (SEL to output)    | Dn,CLKn=0.6V<br>DAn,DBn,CLKAn,CLKBn:<br>$R_L = 50\Omega$ , $C_L = 0pF$     |     | 150 | 800  | ns   |

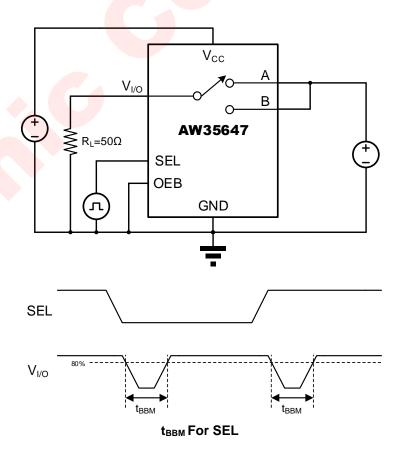

| t <sub>ввм</sub>  | Break before make time                  | Dn,CLKn: $R_L = 50\Omega$ ,<br>$C_L = 0pF$<br>DAn,DBn,CLKAn,CLKBn<br>=0.6V |     | 400 |      | ns   |

| t <sub>PD</sub>   | Propagation delay <sup>(NOTE4)</sup>    | Dn,CLKn=0.6V<br>DAn,DBn,CLKAn,CLKBn:<br>$R_L = 50\Omega$ , $C_L = 0$ pF    |     | 100 |      | ps   |

| tskew(INTRA)      | Intrapair skew <sup>(NOTE4)</sup>       | Dn,CLKn=0.3V<br>DAn,DBn,CLKAn,CLKBn:<br>$R_L = 50\Omega$ , $C_L = 0pF$     |     | 6   |      | ps   |

| tskew(inter)      | Interpair skew <sup>(NOTE4)</sup>       | Dn,CLKn=0.3V<br>DAn,DBn,CLKAn,CLKBn:<br>$R_L = 50\Omega$ , $C_L = 0pF$     |     | 6   |      | ps   |

NOTE4: Guaranteed by characterization

## **Detailed Functional Description**

The AW35647 is a four-data-lane MIPI D-PHY switch. This device is an optimized 10-channel (5 differential) single-pole, double-throw switch for use in high speed applications. The AW35647 can also be configured as three-data-lane MIPI C-PHY switch. The AW35647 is designed to facilitate multiple MIPI compliant devices to connect to a single CSI/DSI, C-PHY/D-PHY module.

#### High Impedance Mode

When OEB is logic high, the AW35647 is in high impedance mode, all the clock and data ports are in Hi-Z state.

| OEB | SEL | Function                            |

|-----|-----|-------------------------------------|

| Н   | Х   | Clock and Data ports High Impedance |

| L   | L   | CLKP/N=CLKAP/N, DnP/N=DAnP/N        |

| L   | Н   | CLKP/N=CLKBP/N, DnP/N=DBnP/N        |

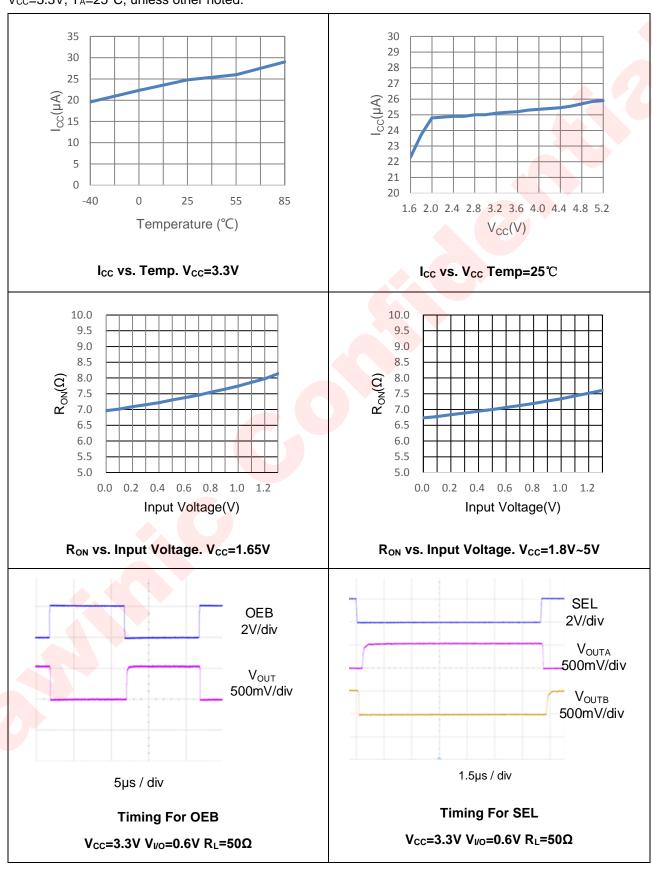

## **Typical characteristics**

Vcc=3.3V, TA=25°C, unless other noted.

## **Parameter Measurement Information**

AW35647

Sept. 2019 V1.1

## **PCB Layout Consideration**

To obtain the optimal performance of AW35647, PCB layout should be considered carefully. Here are some guidelines:

- 1. Place supply bypass capacitors as close to V<sub>CC</sub> and GND pin as possible and avoid placing the bypass capacitors near the high-speed traces.

- 2. The characteristic impedance of the traces must match that of the receiver and transmitter to maintain signal integrity.

- 3. Route the high-speed signals using a minimum amount of vias and corners which reduces signal reflections and impedance changes. When it becomes necessary to make the traces turn 90°, use an arc instead of making a single 90° turn.

- 4. Do not route high-speed traces under or near crystals, oscillators, clock signal generators, switching regulators, mounting holes, magnetic devices or ICs that use or duplicate clock signals.

- 5. Avoid stubs on the high-speed signal lines because they cause signal reflections.

- 6. Route all high-speed signal traces over continuous GND planes, with no interruptions.

- 7. High speed signal traces must be length matched as much as possible to minimize skew between data and clock lines. Width and spacing between differential traces must be equal line width and line spacing

# **Tape And Reel Information**

# REEL DIMENSIONS D1

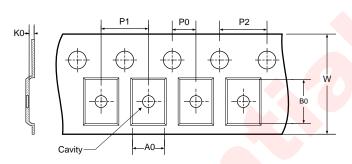

#### TAPE DIMENSIONS

- A0: Dimension designed to accommodate the component width

- B0: Dimension designed to accommodate the component length

- K0: Dimension designed to accommodate the component thickness

- W: Overall width of the carrier tape

- P0: Pitch between successive cavity centers and sprocket hole

- P1: Pitch between successive cavity centers

- P2: Pitch between sprocket hole D1: Reel Diameter

- D0: Reel Width

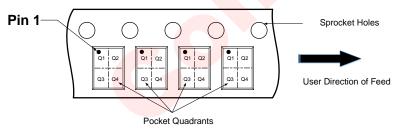

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### DIMENSIONS AND PIN1 ORIENTATION

| D1     | D0   | A0   | B0   | K0   | P0   | P1   | P2   | W    | Pin1 Quadrant  |

|--------|------|------|------|------|------|------|------|------|----------------|

| (mm)   | (mm) | (mm) | (mm) | (mm) | (mm) | (mm) | (mm) | (mm) | Fiiii Quadrani |

| 179.00 | 9.00 | 2.54 | 2.54 | 0.76 | 2.00 | 4.00 | 4.00 | 8.00 | Q1             |

All dimensions are nominal

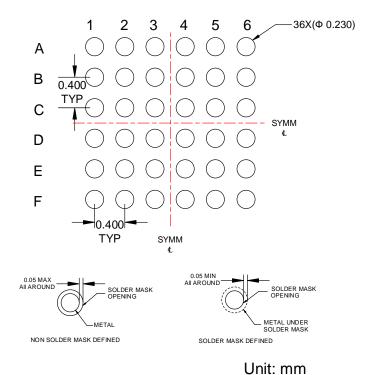

# **Package Description**

#### **Land Pattern Data**

Offic. IIIIII

AW35647

Sept. 2019 V1.1

# **Revision History**

| Version | Date      | Change Record              |

|---------|-----------|----------------------------|

| V1.0    | Mar 2019  | Datasheet V1.0 released    |

| V1.1    | Sept 2019 | Updated Description. (P19) |

AW35647

Sept. 2019 V1.1

#### **Disclaimer**

Information in this document is believed to be accurate and reliable. However, Shanghai AWINIC Technology Co., Ltd (AWINIC Technology) does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

AWINIC Technology reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. Customers shall obtain the latest relevant information before placing orders and shall verify that such information is current and complete. This document supersedes and replaces all information supplied prior to the publication hereof.

AWINIC Technology products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or malfunction of an AWINIC Technology product can reasonably be expected to result in personal injury, death or severe property or environmental damage. AWINIC Technology accepts no liability for inclusion and/or use of AWINIC Technology products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

Applications that are described herein for any of these products are for illustrative purposes only. AWINIC Technology makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

All products are sold subject to the general terms and conditions of commercial sale supplied at the time of order acknowledgement.

Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

Reproduction of AWINIC information in AWINIC data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. AWINIC is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of AWINIC components or services with statements different from or beyond the parameters stated by AWINIC for that component or service voids all express and any implied warranties for the associated AWINIC component or service and is an unfair and deceptive business practice. AWINIC is not responsible or liable for any such statements.