# Ultrasonic Parking Distance Measurement ASSP

### **General Description**

The NCV75215 ASSP is intended to operate with a piezoelectric ultrasonic transducer to provide time-of-flight measurement of an obstacle distance during vehicle parking. The high-sensitivity, low-noise operation allows detection from 0.25 m up to 4.5 m for a standard 75 mm pole. Actual minimum distance is determined by the length of reverberations. Under ideal conditions, with perfectly tuned and matched external circuitry, a minimum distance of 0.2 m is achievable. Actual detection range depends on a piezoelectric ultrasonic transducer and external analog parts.

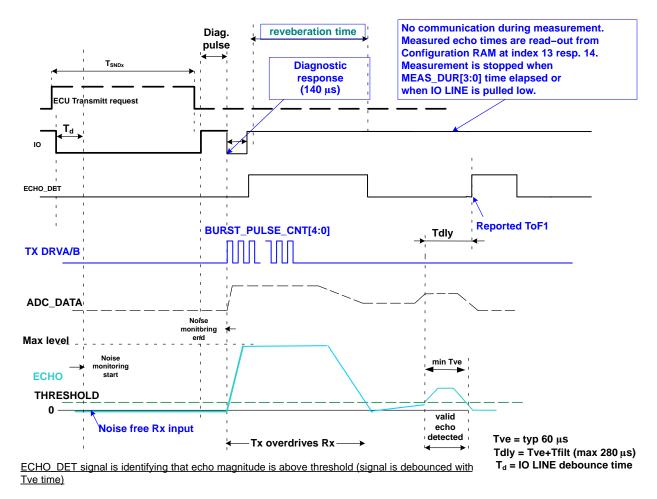

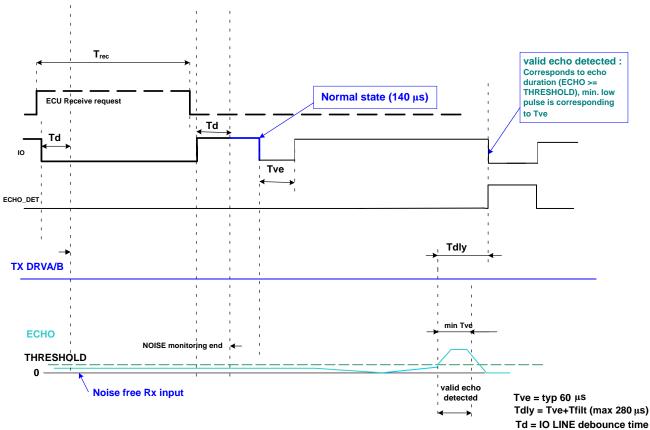

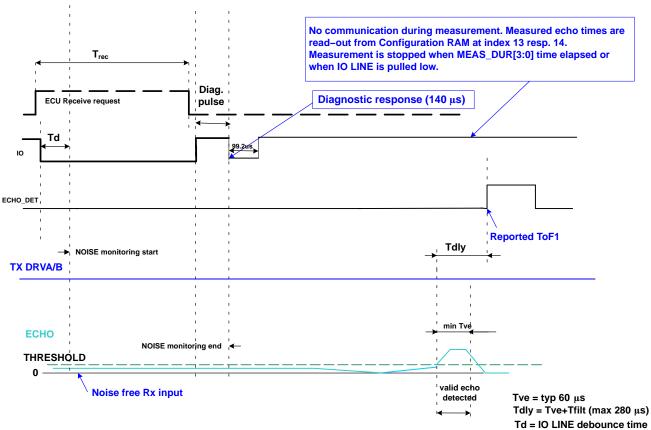

The device drives the ultrasonic transducer with a programmable frequency via a transformer. The received echo is amplified and converted to a digital signal, filtered, detected and the magnitude is compared to a time-dependent threshold which is stored in an internal RAM. Distance to the obstacle is determined by the time measured from a transmission burst to echo recognition.

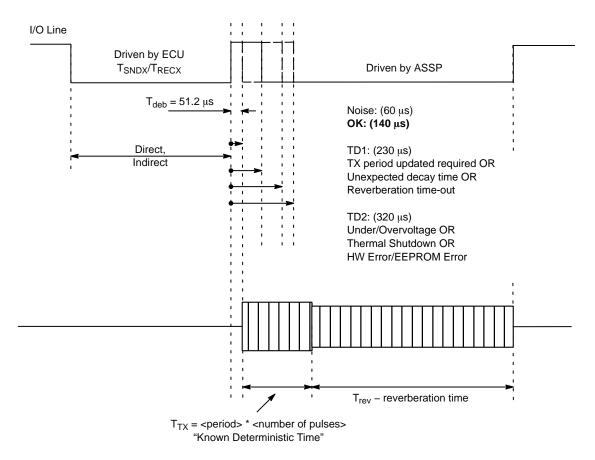

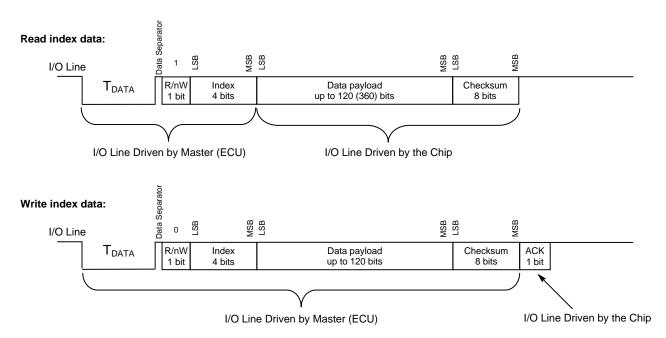

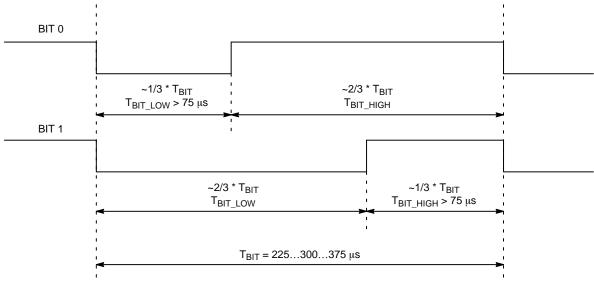

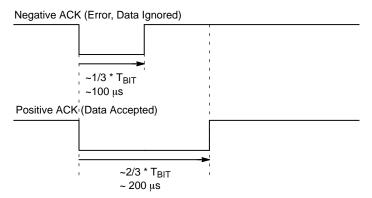

A bidirectional I/O Line is used to communicate with a master (ECU). The master issues I/O Line commands to the NCV75215 and data are reported back via the same line.

#### **Features**

- Measurement Distance Range from 0.25 m to 4.5 m (depends on External Parts)

- Acoustic Noise Monitoring

- Transducer Resonant Period Measurement

- Diagnosis of Transducer Performance

- Junction Temperature Monitoring and Thermal Shutdown

- Transducer Center Frequency Range from 35 to 90 kHz

- Direct and Indirect Measurement Modes

- EEPROM Memory for Configuration Setting and User Data

- Rx Gain Adjustable in 0.5 dB Steps in the Range from 50 to 110 dB

- Time-dependent Threshold Values for the Sensitivity Control

- Dynamic (Time-dependent) Gain Control

- Tx Current Range Adjustable from 50 mA to 350 mA

- Programmable Ultrasonic Burst Length

- On-chip Bidirectional I/O Line

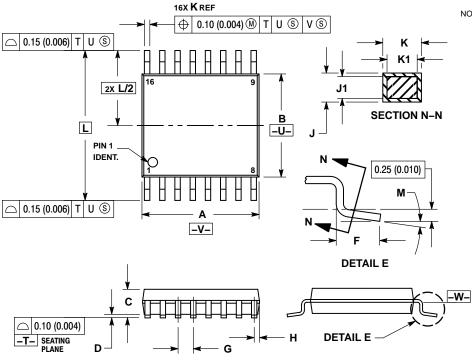

- Small TSSOP16 Package

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable\*

- These are Pb-free Devices

#### **Typical Applications**

- Automotive Park Assist

- Ultrasonic Distance Measurements

### ON Semiconductor®

www.onsemi.com

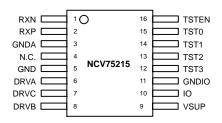

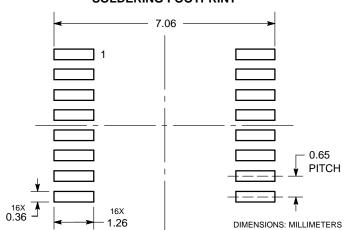

#### TSSOP-16 CASE 948F

#### MARKING DIAGRAM

In accordance with:

US:

7620021 Mark Specifications – for ceramic, plastic and tape–automated bond packages

Europe: 16020 Standard Marking Specification

#### **PIN CONNECTIONS**

#### ORDERING INFORMATION

| Device            | Package   | Shipping <sup>†</sup> |

|-------------------|-----------|-----------------------|

| NCV75215DB001R2G* | TSSOP-16  | 4000 / Tape           |

|                   | (Pb-Free) | & Reel                |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

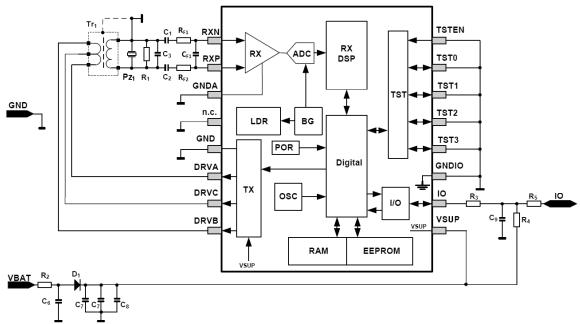

Figure 1. Application Schematic Diagram

**Table 1. RECOMMENDED EXTERNAL COMPONENTS**

| Name       | Description                                | Typical Value | Units | Rating | Tolerance | Comment                                                                                                             |

|------------|--------------------------------------------|---------------|-------|--------|-----------|---------------------------------------------------------------------------------------------------------------------|

| R1         | Resonator Damping                          | Optimal value | kΩ    |        | 5 %       | Value depends on used transducer & transformer                                                                      |

| R2         | Battery Filter Resistor                    | 100           | Ω     | Note ⇒ | 5 %       | Power rating according to required EMC robustness                                                                   |

| R3         | I/O Line Protection                        | 470           | Ω     | Note ⇒ | 5 %       | It may be omitted but system ESD robust-<br>ness is reduced<br>Power rating according to required EMC<br>robustness |

| R4         | I/O Line Pull Up                           | 10            | kΩ    | 100 mW | 5 %       | Optional. It is not used if I/O Line internal pull-up resistor is enabled (see Config RAM item IO_PUP_ENA)          |

| R5         | I/O Line High Frequency<br>Protection      | 47            | Ω     | Note ⇒ | 5 %       | Optional It improves high frequency EMC robustness Power rating according to required EMC robustness                |

| RF1<br>RF2 | Input EMC Filter Resistor<br>(Note 1)      | 100           | Ω     | Note ⇒ | 5 %       | Optional It improves high frequency EMC robustness Power rating according to required EMC robustness                |

| C1         | Receiver Input Coupling                    | 680           | pF    | 100 V  | 10 %      |                                                                                                                     |

| C2         | Receiver Input Coupling                    | 680           | pF    | 100 V  | 10 %      |                                                                                                                     |

| C3         | Serial and Parallel<br>Resonances Matching | optimal value | pF    | 100 V  | 5 %       | Value depends on used transducer & transformer                                                                      |

| CF1        | Input EMC Filter Capacitor (Note 1)        | 10            | pF    | 50 V   | 10 %      | Optional<br>It improves high frequency EMC<br>robustness                                                            |

| C6         | Battery Filter Capacitor                   | 100           | nF    | 50 V   | 10 %      |                                                                                                                     |

| C7         | Tank Capacitor for<br>Transmitting Current | 22            | μF    | 35 V   | 10 %      | 2x ceramic type capacitor                                                                                           |

<sup>1.</sup> Some of RF1, RF2 and CF1 components may be omitted. Use them according to required EMC robustness.

Table 1. RECOMMENDED EXTERNAL COMPONENTS (continued)

| Name | Description                 | Typical Value                                | Units | Rating | Tolerance               | Comment                                         |

|------|-----------------------------|----------------------------------------------|-------|--------|-------------------------|-------------------------------------------------|

| C8   | VBAT HF Filter              | 100                                          | nF    | 50 V   | 10 %                    |                                                 |

| C9   | I/O Line Capacitor          | 330                                          | pF    | 50 V   | 10 %                    | Standard I/O Line slope (60 μs) IO_SLP_FAST = 0 |

| C9   | I/O Line Capacitor          | 100                                          | pF    | 50 V   | 10 %                    | Fast I/O Line slope (20 μs) IO_SLP_FAST = 1     |

| Tr1  | Push-pull Transformer       | Transducer specific                          | mH    | 100V   | 5%                      |                                                 |

| PZ1  | Ultrasonic Transducer       | MA40MF14-1B<br>MA55AF15-07NA<br>MA48AF15-07N | kHz   | 100V   | the lower<br>the better | muRata series                                   |

| D1   | Reverse Polarity Protection | BAS321                                       | -     | 50 V   | _                       |                                                 |

<sup>1.</sup> Some of RF1, RF2 and CF1 components may be omitted. Use them according to required EMC robustness.

**Table 2. PIN FUNCTION DESCRIPTION**

| Pin No. | Pin Name       | Туре         | Description                                    |

|---------|----------------|--------------|------------------------------------------------|

| 1       | RXN (Note 2)   | Input        | Analog Receiver Negative Input                 |

| 2       | RXP            | Input        | Analog Receiver Positive Input                 |

| 3       | GNDA           | Ground       | Analog Ground                                  |

| 4       | n.c.           | n.c.         | Pin not connected                              |

| 5       | GND            | Ground       | TX Ground, Digital Ground                      |

| 6       | DRVA           | Output       | Driver Output A                                |

| 7       | DRVC           | Output       | Driver Output C (Center of winding)            |

| 8       | DRVB           | Output       | Driver Output B                                |

| 9       | VSUP           | Power Supply | Main Power Supply                              |

| 10      | IO             | Input/Output | I/O Line Bidirectional Interface to Master ECU |

| 11      | GNDIO          | Ground       | I/O Line Ground                                |

| 12      | TST3           | Input/Output | Test pin 3/Custom Diagnostic Interface         |

| 13      | TST2           | Input/Output | Test pin 2/Custom Diagnostic Interface         |

| 14      | TST1           | Input/Output | Test pin 1/Custom Diagnostic Interface         |

| 15      | TST0           | Input/Output | Test pin 0/Custom Diagnostic Interface         |

| 16      | TSTEN (Note 3) | Input        | Manufacturer Test Mode Enable                  |

Both receiver inputs are equal. Anyone of them can be used for signal input and the other for ground reference. But, using outer package pin for signal input may result in worse EMC robustness.

3. TSTEN pin has to be always grounded in customer application. There is no customer functionality.

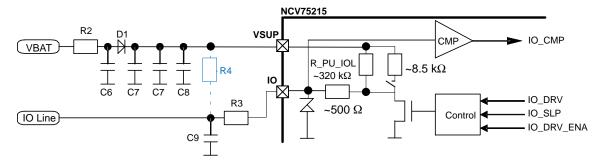

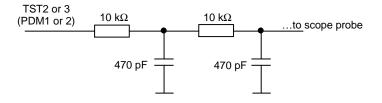

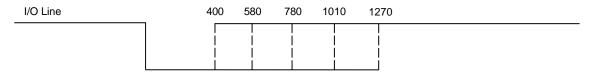

Figure 2. I/O Line Driver Structure and External Network

**Table 3. ABSOLUTE MAXIMUM RATINGS**

| Rating                                                                           | Symbol                                | Value                                      | Units |

|----------------------------------------------------------------------------------|---------------------------------------|--------------------------------------------|-------|

| Supply Voltage Range VSUP (Note 4)                                               | V <sub>SUP</sub>                      | -0.3 to 40                                 | V     |

| I/O Line Voltage Range                                                           | V <sub>IO</sub>                       | -5 to 40                                   | V     |

| I/O Line Voltage Range (T <sub>A</sub> = 25°C)                                   | V <sub>IO,A</sub>                     | -15 to 40                                  | V     |

| I/O Line Voltage Range (t <sub>PULSE</sub> < 1 second, T <sub>A</sub> = 25°C)    | V <sub>IO,PA</sub>                    | -30 to 40                                  | V     |

| Transmitter DRVA, DRVB voltage                                                   | V <sub>DRV</sub>                      | $-0.3$ to $(2 \times V_{SUP} + 0.3)$ or 40 | V     |

| Transmitter DRVC voltage                                                         | V <sub>DRV</sub>                      | -0.3 to (V <sub>SUP</sub> + 0.3) or 40     | V     |

| Receiver Input P, N Voltage                                                      | V <sub>RXP</sub> , V <sub>RXN</sub>   | -0.3 to 0.3                                | V     |

| Testmode Pin Voltage                                                             | V <sub>TST0</sub> – V <sub>TST3</sub> | 0 to (V <sub>DD</sub> + 0.3) or 3.6        | V     |

| Maximum Junction Temperature                                                     | T <sub>J(max)</sub>                   | 125                                        | °C    |

| Storage Temperature Range                                                        | TSTG                                  | -40 to 125                                 | °C    |

| ESD Capability, Human Body Model (Note 5)                                        | ESDHBM                                | 2                                          | kV    |

| ESD Capability, Charge Device Model, All Pins (Note 5)                           | ESDCDM-O                              | 500                                        | V     |

| ESD Capability, Charge Device Model, Corner Pins (Note 5)                        | ESDCDM-E                              | 750                                        | V     |

| Latch-up Immunity at 25°C (Note 5)                                               | LU25C                                 | 200                                        | mA    |

| Latch-up Immunity at 125°C (Note 5)                                              | LU125C                                | 100                                        | mA    |

| Lead Temperature Soldering<br>Reflow (SMD Styles Only), Pb-Free Versions (Note6) | T <sub>SLD</sub>                      | 260                                        | °C    |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

ESD Human Body Model tested per AEC-Q100-002 (EIA/JESD22-A114)

ESD Machine Model tested per AEC-Q100-003 (EIA/JESD22-A115)

Latch-up Current Maximum Rating: per JEDEC standard JESD78

**Table 4. THERMAL CHARACTERISTICS**

| Rating                                                                                 | Symbol        | Value | Units |

|----------------------------------------------------------------------------------------|---------------|-------|-------|

| Thermal Characteristics, TSSOP16 (Note 7) Thermal Resistance, Junction-to-Air (Note 8) | $R_{	hetaJA}$ | 135   | °C/W  |

<sup>7.</sup> Refer to ELECTRICAL CHARACTERISTICS, RECOMMENDED OPERATING RANGES and/or APPLICATION INFORMATION for Safe Operating parameters.

### **Table 5. RECOMMENDED OPERATING RANGES**

| Symbol         | Description                     | Min | Тур | Max              | Units |

|----------------|---------------------------------|-----|-----|------------------|-------|

| VSUP           | DC Supply Voltage               | 6   | 12  | 18               | V     |

| VIO            | I/O Line Voltage                | 0   |     | VSUP<br>(Note 9) | V     |

| T <sub>A</sub> | Ambient Temperature under Bias  | -40 |     | 85               | °C    |

| TJ             | Junction Temperature under Bias | -40 |     | 125              | °C    |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

Refer to ELECTRICAL CHĂRACTERISTICS, RECOMMENDED OPERATING RANGES and/or APPLICATION INFORMATION for Safe Operating parameters.

<sup>5.</sup> This device series incorporates ESD protection and is tested by the following methods:

<sup>6.</sup> For information, please refer to our Soldering and Mounting Techniques Reference Manual, SOLDERRM/D

<sup>8.</sup> Values based on copper area of 645 mm<sup>2</sup> (or 1 in<sup>2</sup>) of 1 oz. copper thickness and FR4 PCB substrate.

<sup>9.</sup> VSUP minimum voltage level might decrease the transmit burst ultrasonic power, it is external circuitry dependent. Transducer equivalent serial resistance is transformed on DRVA,B,C ASSP inputs and might be too high to satisfy both minimum VSUP and maximum TX current. In such a case, transmit driving current proportionally declines.

# **Table 6. ELECTRICAL CHARACTERISTICS**

(VSUP = 6 V to 18 V, TA =  $-40^{\circ}$ C to 85°C, external devices as in application circuit of Figure 1.)

| Symbol                                                                                                                                                    | Description                                                                                                                                                                                                                                                                                                                                                                        | Min                                        | Тур        | Max                               | Units                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------------|-----------------------------------|----------------------------------------------|

| I <sub>VSUP</sub>                                                                                                                                         | Total VSUP Current Consumption (Normal Mode, No Transmission)                                                                                                                                                                                                                                                                                                                      |                                            |            | 8                                 | mA                                           |

| I <sub>VSUP, LOW_PWR</sub>                                                                                                                                | Total VSUP Current Consumption (Low Power Mode)                                                                                                                                                                                                                                                                                                                                    |                                            |            | 1                                 | mA                                           |

| t <sub>WAKE</sub>                                                                                                                                         | Wake-up Time from Low Power Mode to Normal Mode                                                                                                                                                                                                                                                                                                                                    |                                            |            | 1                                 | ms                                           |

| RECEIVER AMP                                                                                                                                              | LIFIER                                                                                                                                                                                                                                                                                                                                                                             |                                            |            |                                   |                                              |

| $RX_{R\_IN}$                                                                                                                                              | Receiver Input Resistance                                                                                                                                                                                                                                                                                                                                                          |                                            | 87         |                                   | kΩ                                           |

| $RX_{C_{-IN}}$                                                                                                                                            | Receiver Input Capacitance                                                                                                                                                                                                                                                                                                                                                         |                                            | 100        |                                   | pF                                           |

| $RX_{GAIN}$                                                                                                                                               | Programmable Receiver Gain                                                                                                                                                                                                                                                                                                                                                         | 50                                         |            | 110                               | dB                                           |

| RX <sub>GSTEP</sub>                                                                                                                                       | Receiver Gain Step                                                                                                                                                                                                                                                                                                                                                                 |                                            | 0.5        |                                   | dB                                           |

| RX <sub>NSTEP</sub>                                                                                                                                       | Receiver Number of Gain Steps                                                                                                                                                                                                                                                                                                                                                      |                                            | 127        |                                   |                                              |

| RX <sub>SENS</sub>                                                                                                                                        | Receiver Sensitivity at Maximum Gain                                                                                                                                                                                                                                                                                                                                               | 12                                         |            |                                   | $\mu V_{PP}$                                 |

| RX <sub>BW</sub>                                                                                                                                          | Receiver Bandwidth                                                                                                                                                                                                                                                                                                                                                                 | 35                                         |            | 90                                | kHz                                          |

| TRANSDUCER D                                                                                                                                              | PRIVER                                                                                                                                                                                                                                                                                                                                                                             |                                            |            |                                   |                                              |

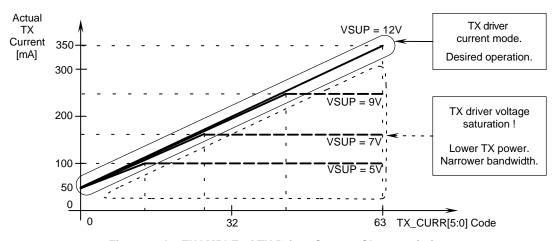

| TX <sub>CURR</sub>                                                                                                                                        | Programmable Transmitter Current                                                                                                                                                                                                                                                                                                                                                   | 50                                         |            | 350                               | mA                                           |

| TX <sub>CSTEP</sub>                                                                                                                                       | Transmitter Current Step                                                                                                                                                                                                                                                                                                                                                           |                                            | 4.76       |                                   | mA                                           |

| TX <sub>NSTEP</sub>                                                                                                                                       | Transmitter Number of Current Steps                                                                                                                                                                                                                                                                                                                                                |                                            | 63         |                                   |                                              |

| TX <sub>SPREC</sub>                                                                                                                                       | Transmitter Current Tolerance                                                                                                                                                                                                                                                                                                                                                      | -20                                        |            | 20                                | %                                            |

|                                                                                                                                                           | GE AND ITS MONITORING                                                                                                                                                                                                                                                                                                                                                              | II.                                        |            |                                   |                                              |

| VDD                                                                                                                                                       | Internal VDD Supply Voltage                                                                                                                                                                                                                                                                                                                                                        | 3.15                                       | 3.3        | 3.5                               | V                                            |

| VDD <sub>POR</sub>                                                                                                                                        | VDD Level for Power-on-Reset                                                                                                                                                                                                                                                                                                                                                       | 2.7                                        |            | 3.1                               | V                                            |

| VSUP <sub>UV</sub>                                                                                                                                        | VSUP Level for Power-on-Reset Release at Start-up,<br>Under-voltage Threshold                                                                                                                                                                                                                                                                                                      | 5.1                                        |            | 5.7                               | V                                            |

| VSUP <sub>OV</sub>                                                                                                                                        | VSUP Level for TX Driver Disable (to Protect Drivers), Over-voltage Threshold                                                                                                                                                                                                                                                                                                      | 18                                         |            | 20                                | V                                            |

| INTERNAL OSCI                                                                                                                                             | LLATOR                                                                                                                                                                                                                                                                                                                                                                             |                                            |            |                                   | I.                                           |

| Fosc                                                                                                                                                      | Internal Oscillator Frequency                                                                                                                                                                                                                                                                                                                                                      | 9.7                                        | 10         | 10.3                              | MHz                                          |

| I/O LINE INTERF                                                                                                                                           | ACE                                                                                                                                                                                                                                                                                                                                                                                | II.                                        |            |                                   |                                              |

| IO <sub>ILV</sub>                                                                                                                                         | Threshold Voltage for Digital Low                                                                                                                                                                                                                                                                                                                                                  | 0.3                                        | 0.33       | 0.36                              | VSUP                                         |

| IO <sub>IHV</sub>                                                                                                                                         | Threshold Voltage for Digital High                                                                                                                                                                                                                                                                                                                                                 | 0.62                                       | 0.66       | 0.7                               | VSUP                                         |

| IO <sub>OLV</sub>                                                                                                                                         | Output Voltage Low at I/O Pin (I <sub>OUT</sub> = 1 mA, Internal Pull-up Activated, R4 Not Used)                                                                                                                                                                                                                                                                                   | 0.4                                        | 0.65       | 1                                 | V                                            |

| IO <sub>SR, STD</sub>                                                                                                                                     | Output Slew Rate (Standard I/O Line Slope)                                                                                                                                                                                                                                                                                                                                         | 0.2                                        | 0.5        | 0.8                               | V/μs                                         |

| IO <sub>SR, FAST</sub>                                                                                                                                    | Output Slew Rate (Fast I/O Line Slope)                                                                                                                                                                                                                                                                                                                                             | 1                                          | 1.7        | 2.5                               | V/μs                                         |

| 011,17101                                                                                                                                                 | <del>                                     </del>                                                                                                                                                                                                                                                                                                                                   |                                            |            | 50                                | mA                                           |

| IO <sub>SCC</sub>                                                                                                                                         | I/O Short Circuit Current                                                                                                                                                                                                                                                                                                                                                          | 10                                         |            | 30                                | 1111/                                        |

| IO <sub>SCC</sub>                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                    |                                            | 320        |                                   |                                              |

| IO <sub>PU</sub>                                                                                                                                          | Fixed Internal Pull-up Resistor (R_PU_IOL)                                                                                                                                                                                                                                                                                                                                         | 10<br>200<br>6                             | 320<br>8.5 | 450<br>11                         | kΩ                                           |

| IO <sub>PU</sub><br>IO <sub>PU, SEL</sub>                                                                                                                 | Fixed Internal Pull-up Resistor (R_PU_IOL)  Selectable Internal Pull-up Resistor                                                                                                                                                                                                                                                                                                   | 200                                        |            | 450                               |                                              |

| IO <sub>PU</sub> IO <sub>PU, SEL</sub> TEMPERATURE                                                                                                        | Fixed Internal Pull-up Resistor (R_PU_IOL)  Selectable Internal Pull-up Resistor  MEASUREMENT AND SHUTDOWN                                                                                                                                                                                                                                                                         | 200                                        |            | 450<br>11                         | kΩ<br>kΩ                                     |

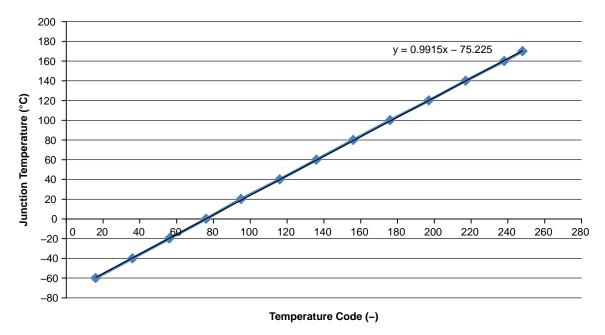

| $\begin{aligned} & IO_{PU} \\ & IO_{PU,SEL} \\ & \textbf{TEMPERATURE} \\ & T_{MR} \end{aligned}$                                                          | Fixed Internal Pull-up Resistor (R_PU_IOL)  Selectable Internal Pull-up Resistor  MEASUREMENT AND SHUTDOWN  Temperature Measurement Range                                                                                                                                                                                                                                          | 200                                        | 8.5        | 450                               | kΩ                                           |

| $IO_{PU}$ $IO_{PU, SEL}$ $TEMPERATURE$ $T_{MR}$ $T_{MRES}$                                                                                                | Fixed Internal Pull-up Resistor (R_PU_IOL)  Selectable Internal Pull-up Resistor  MEASUREMENT AND SHUTDOWN  Temperature Measurement Range  Temperature Measurement Resolution                                                                                                                                                                                                      | 200<br>6<br>-60                            |            | 450<br>11<br>150                  | kΩ<br>kΩ<br>°C<br>°C                         |

| IO <sub>PU</sub> IO <sub>PU, SEL</sub> TEMPERATURE T <sub>MR</sub> T <sub>MRES</sub> T <sub>A41</sub>                                                     | Fixed Internal Pull-up Resistor (R_PU_IOL)  Selectable Internal Pull-up Resistor  MEASUREMENT AND SHUTDOWN  Temperature Measurement Range  Temperature Measurement Resolution  Temperature Measurement Accuracy at T <sub>J</sub> = 42°C                                                                                                                                           | 200                                        | 8.5        | 450<br>11                         | kΩ<br>kΩ<br>°C                               |

| IO <sub>PU</sub> IO <sub>PU, SEL</sub> TEMPERATURE T <sub>MR</sub> T <sub>MRES</sub> T <sub>A41</sub> T <sub>A125</sub>                                   | Fixed Internal Pull-up Resistor (R_PU_IOL)  Selectable Internal Pull-up Resistor  MEASUREMENT AND SHUTDOWN  Temperature Measurement Range  Temperature Measurement Resolution  Temperature Measurement Accuracy at T <sub>J</sub> = 42°C  Temperature Measurement Accuracy at T <sub>J</sub> = 125°C                                                                               | 200<br>6<br>-60<br>-7<br>-10               | 8.5        | 450<br>11<br>150<br>7<br>10       | kΩ<br>kΩ<br>°C<br>°C<br>°C                   |

| IO <sub>PU</sub> IO <sub>PU, SEL</sub> TEMPERATURE T <sub>MR</sub> T <sub>MRES</sub> T <sub>A41</sub> T <sub>A125</sub> T <sub>A40</sub>                  | Fixed Internal Pull-up Resistor (R_PU_IOL)  Selectable Internal Pull-up Resistor  MEASUREMENT AND SHUTDOWN  Temperature Measurement Range  Temperature Measurement Resolution  Temperature Measurement Accuracy at T <sub>J</sub> = 42°C  Temperature Measurement Accuracy at T <sub>J</sub> = 125°C  Temperature Measurement Accuracy at T <sub>J</sub> = -40°C                   | 200<br>6<br>-60<br>-7<br>-10<br>-10        | 8.5        | 450<br>11<br>150<br>7<br>10<br>10 | kΩ<br>kΩ<br>°C<br>°C<br>°C<br>°C<br>°C       |

| IO <sub>PU</sub> IO <sub>PU, SEL</sub> TEMPERATURE T <sub>MR</sub> T <sub>MRES</sub> T <sub>A41</sub> T <sub>A125</sub> T <sub>A40-</sub> T <sub>SD</sub> | Fixed Internal Pull-up Resistor (R_PU_IOL)  Selectable Internal Pull-up Resistor  MEASUREMENT AND SHUTDOWN  Temperature Measurement Range  Temperature Measurement Resolution  Temperature Measurement Accuracy at T <sub>J</sub> = 42°C  Temperature Measurement Accuracy at T <sub>J</sub> = 125°C                                                                               | 200<br>6<br>-60<br>-7<br>-10               | 8.5        | 450<br>11<br>150<br>7<br>10       | kΩ<br>kΩ<br>°C<br>°C<br>°C<br>°C             |

| $IO_{PU}$ $IO_{PU, SEL}$ $TEMPERATURE$ $T_{MR}$ $T_{MRES}$ $T_{A41}$ $T_{A125}$ $T_{A40-}$ $T_{SD}$ $EEPROM$                                              | Fixed Internal Pull-up Resistor (R_PU_IOL)  Selectable Internal Pull-up Resistor  MEASUREMENT AND SHUTDOWN  Temperature Measurement Range  Temperature Measurement Resolution  Temperature Measurement Accuracy at T <sub>J</sub> = 42°C  Temperature Measurement Accuracy at T <sub>J</sub> = 125°C  Temperature Measurement Accuracy at T <sub>J</sub> = -40°C  Thermal Shutdown | 200<br>6<br>-60<br>-7<br>-10<br>-10<br>140 | 8.5        | 450<br>11<br>150<br>7<br>10<br>10 | kΩ<br>kΩ<br>°C<br>°C<br>°C<br>°C<br>°C<br>°C |

| IO <sub>PU</sub> IO <sub>PU, SEL</sub> TEMPERATURE T <sub>MR</sub> T <sub>MRES</sub> T <sub>A41</sub> T <sub>A125</sub> T <sub>A40-</sub> T <sub>SD</sub> | Fixed Internal Pull-up Resistor (R_PU_IOL)  Selectable Internal Pull-up Resistor  MEASUREMENT AND SHUTDOWN  Temperature Measurement Range  Temperature Measurement Resolution  Temperature Measurement Accuracy at T <sub>J</sub> = 42°C  Temperature Measurement Accuracy at T <sub>J</sub> = 125°C  Temperature Measurement Accuracy at T <sub>J</sub> = -40°C                   | 200<br>6<br>-60<br>-7<br>-10<br>-10        | 8.5        | 450<br>11<br>150<br>7<br>10<br>10 | kΩ<br>kΩ<br>°C<br>°C<br>°C<br>°C<br>°C       |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

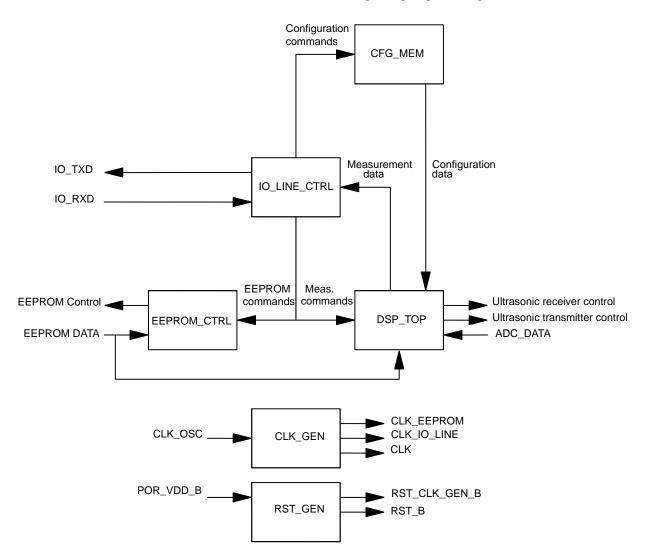

### **DIGITAL FUNCTIONALITY DESCRIPTION**

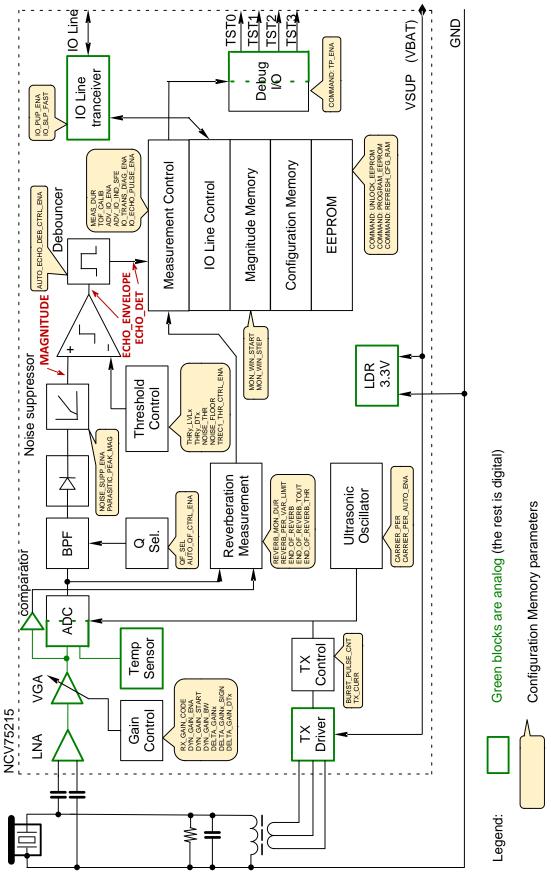

The digital circuitry consists of the following blocks:

- RST\_GEN based on POR (power-on reset) signals, generates internal reset of digital blocks

- CLK\_GEN generates CLK\_IO\_LINE and CLK\_EEPROM from internal oscillator

- CFG\_MEM configuration parameters storage for the chip functionality (EEPROM shadow RAM)

- EEPROM\_CTRL EEPROM controller for accessing EEPROM memory

- I/O\_LINE\_CTRL protocol and application layer for communication with I/O Line master (ECU) via I/O Line

- DSP\_TOP ultrasonic receiver and transmitter control, digital signal processing for ultrasonic receiver

Figure 3. Digital Block Diagram

### **RST\_GEN** (Reset Generator)

It generates internal reset signals according to VSUP and VDD levels. In case of thermal shutdown all major blocks, such as RX, TX, and IO\_LINE, go to power-down mode. This means that the chip doesn't communicate via I/O Line and its functionality is blocked. Functionality is restored when temperature falls back to a safe level.

### **CLK\_GEN (Clock Generator)**

This block generates the timing and internal clock signals based on an on-chip clock oscillator nominally running at 10 MHz (100 ns period).

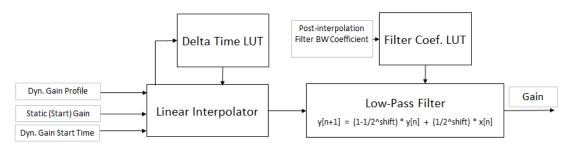

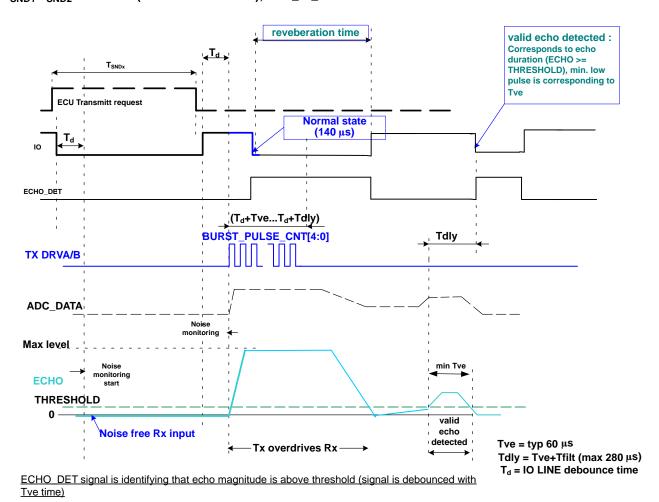

### **DSP\_TOP** (Digital Signal Processing)

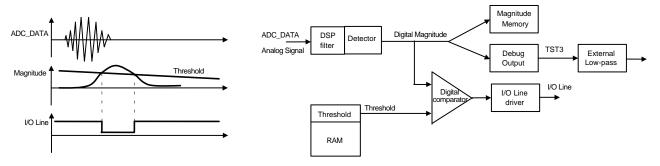

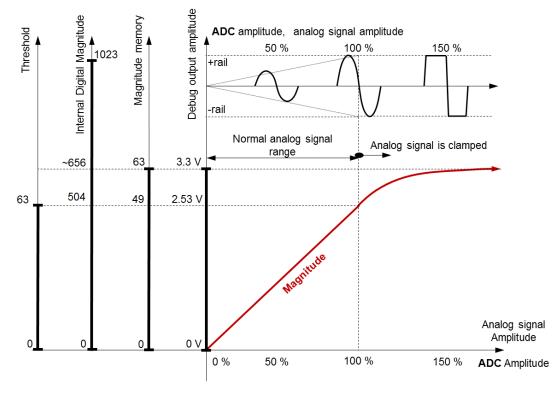

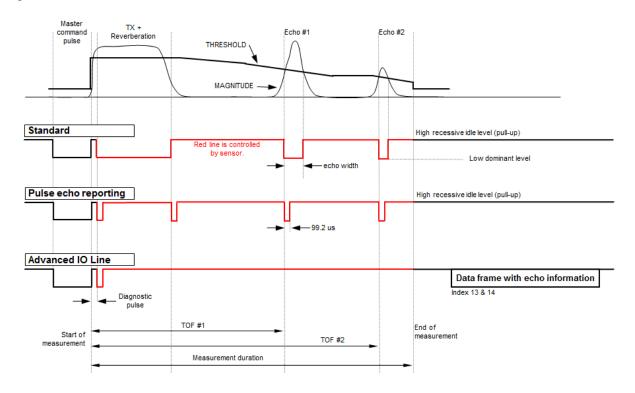

This block contains the core of the digital functionality of the NCV75215. The signal from ultrasonic transducer is amplified, converted to digital and fed to DSP\_TOP. Then, it is digitally processed and compared to a time-dependent threshold. The echo is reported on I/O Line when the signal magnitude exceeds the threshold. Distance to the obstacle can be determined from the time of the echo arrival. This block also controls transmission and reception at the ultrasonic transducer frequency. A simplified internal diagram of DSP\_TOP module is depicted in Figure 4.

Figure 4. Block Diagram of DST TOP Module (Simplified)

Figure 5. Understanding Internal Digital Magnitude, Thresholds and Debug Amplitude (the Processing is Fully Digital; Voltages Apply to PDM Debugging Outputs TST2 and TST3)

Figure 6. Block Diagram from Signal Processing Point of View

# **CFG\_MEM (Configuration Memory)**

Bit structure of configuration memory is described in Table 7. EEPROM Refresh is executed during reset and reset values of CFG\_MEM cells are preloaded from EEPROM

when available. For CFG\_MEM locations not associated to the EEPROM, default value is preloaded after reset.

Data is transferred over I/O Line LSBit first and lowest sub-index first (in case of data arrays).

**Table 7. STRUCTURE OF CONFIGURATION MEMORY**

| Conf.<br>Memory                                 |                                                   |                                                         | No<br>of |                                                                                                                                                                                                                                                                                                                                                      | EEPROM    |                                  |           |

|-------------------------------------------------|---------------------------------------------------|---------------------------------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------------------------|-----------|

| index                                           | Name                                              | Short Name                                              | bits     | Description                                                                                                                                                                                                                                                                                                                                          | (Note 11) | Default                          | R/W       |

| 0                                               | Measured Junction<br>Temperature                  | TEMP [7:0]                                              | 8        | Junction temperature code                                                                                                                                                                                                                                                                                                                            |           | Actual<br>value                  | R<br>only |

| 1                                               | Sensor Status<br>(sub-index 0)                    | SENSOR_STATUS<br>[7:0]                                  | 8        | Refer to Encoding of Sensor<br>Status Section                                                                                                                                                                                                                                                                                                        |           | Actual<br>value                  | R<br>only |

|                                                 | Measured<br>Reverberation Period<br>(sub-index 1) | MEASURED_<br>REVERB_PER [10:0]                          | 11       | 1–LSB ~ 25 ns                                                                                                                                                                                                                                                                                                                                        |           | 0<br>(Note 12)                   | R<br>only |

| 2a<br>Accessible only when<br>TX_RX_PER_ENA = 0 | Carrier TX / RX<br>Period                         | CARRIER_PER [10:0]                                      | 11       | 1-LSB ~ 25 ns  Transmission & Reverberation:     TX_CARRIER_PER =     CARRIER_PER + 2 ×     DTX_PER  Reception:     RX_CARRIER_PER =     CARRIER_PER + 2 ×     DRX_PER  Valid range: <30 kHz, 95 kHz>                                                                                                                                                | Yes       |                                  | R/W       |

| 2b<br>Accessible only when<br>TX_RX_PER_ENA = 1 | Delta TX Period<br>(sub-index 0)                  | DTX_PER [7:0]                                           | 8        | 1–LSB ~ 50 ns  Two's complement signed number  Range: <–6.4 μs, 6.35 μs>  See CARRIER_PER for explanation                                                                                                                                                                                                                                            |           | 0                                | R/W       |

| Acce<br>TX_F                                    | Delta Rx Period<br>(sub-index 1)                  | DRX_PER [7:0]                                           | 8        | The same coding as DTX_PER See CARRIER_PER for explanation                                                                                                                                                                                                                                                                                           |           | 0                                | R/W       |

| 3                                               | TX Burst Pulse Count                              | BURST_PULSE_<br>CNT [4:0]                               | 5        | Number of TX pulses (031)  0: TX driver is not activated 1: 1 × TX pulse 31: 31 × TX pulses                                                                                                                                                                                                                                                          |           | 16                               | R/W       |

| 4                                               | Measurement<br>Duration                           | MEAS_DUR [3:0]                                          | 4        | $\begin{array}{c} 0-T_{SNDx} \text{ and } T_{RECx} \text{ I/O Line} \\ \text{commands disabled (default)} \\ 1-6 \text{ ms, } 2-12 \text{ ms} \\ 3-18 \text{ ms, } 4-24 \text{ ms} \\ 5-30 \text{ ms, } 6-36 \text{ ms} \\ 7-42 \text{ ms, } 8-48 \text{ ms} \\ 9-54 \text{ ms, } 10-60 \text{ ms} \\ \text{other values}-60 \text{ ms} \end{array}$ |           | 0                                | R/W       |

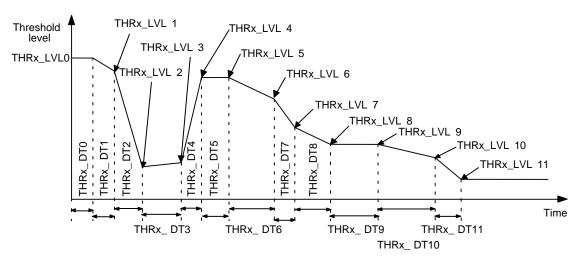

| 5                                               | THR1                                              | THR1_LVL0 [5:0] /<br>DT0 [3:0]<br><br>THR1_LVL11 / DT11 | 120      | Thresholds – THR1 table<br>See section THRESHOLDS                                                                                                                                                                                                                                                                                                    |           | THR1_<br>LVLx<br>= 32<br>DTx = 0 | R/W       |

| 6                                               | THR2                                              | THR2_LVL0 [5:0] /<br>DT0 [3:0]<br><br>THR2_LVL11 / DT11 | 120      | Thresholds – THR2 table<br>See section THRESHOLDS                                                                                                                                                                                                                                                                                                    |           | THR2_<br>LVLx<br>= 32<br>DTx = 0 | R/W       |

Table 7. STRUCTURE OF CONFIGURATION MEMORY (continued)

| Conf.<br>Memory |                                                        |                         | No<br>of |                                                                                                                                                                   | EEPROM    |         |     |

|-----------------|--------------------------------------------------------|-------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------|-----|

| index           | Name                                                   | Short Name              | bits     | Description                                                                                                                                                       | (Note 11) | Default | R/W |

| 7               | Static RX Gain Code<br>(sub-index 0)                   | RX_GAIN_CODE<br>[6:0]   | 7        | RX Gain Code<br>1-LSB ~ 0.476 dB                                                                                                                                  | Yes       |         | R/W |

|                 | Dynamic Gain<br>Control Enable<br>(sub-index 1)        | DYN_GAIN_ENA            | 1        | Enables / disables dynamic gain                                                                                                                                   | Yes       |         | R/W |

|                 | Noise Threshold<br>(sub-index 2)                       | NOISE_THR [5:0]         | 6        | Threshold applied during noise monitoring                                                                                                                         |           | 32      | R/W |

|                 | Noise Floor<br>(sub-index 3)                           | NOISE_FLOOR [5:0]       | 6        | All thresholds below NOISE_FLOOR[5:0] are clamped to NOISE_FLOOR[5:0]. Signal be- low NOISE_FLOOR[5:0] is con- sidered as noise. The same coding as thresh- olds. |           | 4       | R/W |

| 8               | Dynamic Gain –<br>Delta Gain #0<br>(sub-index 0)       | DELTA_GAIN0 [6:0]       | 7        | See DYNAMIC GAIN section.<br>Range 0127                                                                                                                           |           | 0       | R/W |

|                 | Dynamic Gain –<br>Delta Gain Sign #0<br>(sub-index 1)  | DELTA_GAIN0_SIGN        | 1        | See DYNAMIC GAIN section. 0positive, 1negative                                                                                                                    |           | 0       | R/W |

|                 | Dynamic Gain –<br>Delta Gain #1<br>(sub-index 2)       | DELTA_GAIN1 [6:0]       | 7        | See DYNAMIC GAIN section.<br>Range 0127                                                                                                                           |           | 0       | R/W |

|                 | Dynamic Gain –<br>Delta Gain Sign #1<br>(sub-index 3)  | DELTA_GAIN1_SIGN        | 1        | See DYNAMIC GAIN section. 0positive, 1negative                                                                                                                    |           | 0       | R/W |

|                 | Dynamic Gain –<br>Delta Gain #2<br>(sub-index 4)       | DELTA_GAIN2 [6:0]       | 7        | See DYNAMIC GAIN section.<br>Range 0127                                                                                                                           |           | 0       | R/W |

|                 | Dynamic Gain –<br>Delta Gain Sign #2<br>(sub-index 5)  | DELTA_GAIN2_SIGN        | 1        | See DYNAMIC GAIN section. 0positive, 1negative                                                                                                                    |           | 0       | R/W |

|                 | Dynamic Gain –<br>Delta Gain #3<br>(sub-index 6)       | DELTA_GAIN3 [6:0]       | 7        | See DYNAMIC GAIN section.<br>Range 0127                                                                                                                           |           | 0       | R/W |

|                 | Dynamic Gain –<br>Delta Gain Sign #3<br>(sub-index 7)  | DELTA_GAIN3_SIGN        | 1        | See DYNAMIC GAIN section. 0positive, 1negative                                                                                                                    |           | 0       | R/W |

|                 | Dynamic Gain –<br>Delta Gain #4<br>(sub-index 8)       | DELTA_GAIN4 [6:0]       | 7        | See DYNAMIC GAIN section.<br>Range 0127                                                                                                                           |           | 0       | R/W |

|                 | Dynamic Gain –<br>Delta Gain Sign #4<br>(sub-index 9)  | DELTA_GAIN4_SIGN        | 1        | See DYNAMIC GAIN section. 0positive, 1negative                                                                                                                    |           | 0       | R/W |

|                 | Dynamic Gain –<br>Delta Time Code #0<br>(sub-index 10) | DELTA_GAIN_DT0<br>[3:0] | 4        | See DYNAMIC GAIN section.                                                                                                                                         |           | 0       | R/W |

|                 | Dynamic Gain –<br>Delta Time Code #1<br>(sub-index 11) | DELTA_GAIN_DT1<br>[3:0] | 4        | See DYNAMIC GAIN section.                                                                                                                                         |           | 0       | R/W |

|                 | Dynamic Gain –<br>Delta Time Code #2<br>(sub-index 12) | DELTA_GAIN_DT2<br>[3:0] | 4        | See DYNAMIC GAIN section.                                                                                                                                         |           | 0       | R/W |

|                 | Dynamic Gain –<br>Delta Time Code #3<br>(sub-index 13) | DELTA_GAIN_DT3<br>[3:0] | 4        | See DYNAMIC GAIN section.                                                                                                                                         |           | 0       | R/W |

|                 | Dynamic Gain –<br>Delta Time Code #4<br>(sub-index 14) | DELTA_GAIN_DT4<br>[3:0] | 4        | See DYNAMIC GAIN section.                                                                                                                                         |           | 0       | R/W |

Table 7. STRUCTURE OF CONFIGURATION MEMORY (continued)

| Conf.<br>Memory |                                                                         |                                | No<br>of |                                                                                                                                                                                                         | EEPROM    |         |     |

|-----------------|-------------------------------------------------------------------------|--------------------------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------|-----|

| index           | Name                                                                    | Short Name                     | bits     | Description                                                                                                                                                                                             | (Note 11) | Default | R/W |

| 8               | Dynamic Gain<br>Control Start<br>(sub-index 15)                         | DYN_GAIN_START<br>[3:0]        | 4        | DYN_GAIN_START × 204.8 μs                                                                                                                                                                               |           | 0       | R/W |

|                 | Dynamic Gain – Filter<br>BW<br>(sub-index 16)                           | DYN_GAIN_BW [1:0]              | 2        | See DYNAMIC GAIN section.                                                                                                                                                                               |           | 0       | R/W |

| 9               | Generic User Data                                                       | USER_DATA [119:0]              | 120      | 120 bits of user data. User can select any structure. The chip doesn't internally use this data.                                                                                                        | Yes       |         | R/W |

| 10              | Reverberation /<br>Decay Monitoring<br>Window Duration<br>(sub-index 0) | REVERB_MON_DUR<br>[7:0]        | 8        | 1–LSB ~ 25.6 μs                                                                                                                                                                                         | Yes       |         | R/W |

|                 | Current Adjustment (sub-index 1)                                        | TX_CURR [5:0]                  | 6        | Default value is pre-loaded after POR.                                                                                                                                                                  | Yes       |         | R/W |

|                 | Reverberation Period<br>Variation Limit<br>(sub-index 2)                | REVERB_PER_<br>VAR_LIMIT [1:0] | 2        | 0 – 2.34 %<br>1 – 5.4 %<br>2 – 8.2 %<br>3 – 12.5 %                                                                                                                                                      | Yes       |         | R/W |

|                 | Monitoring Window<br>Start<br>(sub-index 3)                             | MON_WIN_START<br>[11:0]        | 12       | Start time of echo magnitude logging into measurement memory 1–LSB ~ 25.6 µs                                                                                                                            |           | 0       | R/W |

|                 | Monitoring Window<br>Step<br>(sub-index 4)                              | MON_WIN_STEP<br>[1:0]          | 2        | Magnitude sampling period 0: 25.6 μs 1: 51.2 μs 2: 102.4 μs 3: 204.8 μs                                                                                                                                 |           | 1       | R/W |

|                 | Automatic Carrier<br>Period Control<br>(sub-index 5)                    | CARRIER_PER_<br>AUTO_ENA       | 1        | When 1: CARRIER_PER is used as carrier period for 1st ultrasonic measurement only resp. each time CARRIER_PER is updated.  Following measurements will drive TX with measured MEASURED_REVERB_PER auto- | Yes       |         | R/W |

|                 |                                                                         |                                |          | matically only if difference be-<br>tween CARRIER_PER and<br>measured reverberation period<br>is less than RE-<br>VERB_PER_VAR_LIMIT other-<br>wise CARRIER_PER is used.                                |           |         |     |

|                 |                                                                         |                                |          | In case of indirect measure-<br>ment the CARRIER_PER will<br>be exclusively used for echo re-<br>ception.                                                                                               |           |         |     |

|                 |                                                                         |                                |          | When 0:  TX_CARRIER_PER resp.  RX_CARRIER_PER is used.                                                                                                                                                  |           |         |     |

|                 | Noise Suppression<br>Enable<br>(sub-index 6)                            | NOISE_SUPP_ENA                 | 1        | Echo magnitude is suppressed if it is below noise background level                                                                                                                                      | Yes       |         | R/W |

| 10              | ToF Calibration<br>(sub-index 7)                                        | TOF_CALIB [5:0]                | 6        | The time is subtracted from measured ToF prior storing it into the measurement result registers.                                                                                                        | Yes       |         | R/W |

|                 |                                                                         |                                |          | It needs to be adjusted for selected Q factor.  1–LSB ~ 25.6 μs                                                                                                                                         |           |         |     |

Table 7. STRUCTURE OF CONFIGURATION MEMORY (continued)

| Conf.<br>Memory |                                                                     |                            | No<br>of |                                                                                                                                                                                                                                                                                        | EEPROM    |         |     |

|-----------------|---------------------------------------------------------------------|----------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------|-----|

| index           | Name                                                                | Short Name                 | bits     | Description                                                                                                                                                                                                                                                                            | (Note 11) | Default | R/W |

|                 | Reverberation<br>Debounce Time<br>(sub-index 8)                     | END_OF_REVERB<br>[1:0]     | 2        | Debounce time is improving robustness towards chattering phenomena 0: 60 μs 1: 100 μs 2: 140 μs 3: 180 μs                                                                                                                                                                              |           | 1       | R/W |

|                 | DSP Filter Q Factor<br>Selection<br>(sub-index 9)                   | QF_SEL [1:0]               | 2        | 0: Q = 5 1: Q = 10 2: Q = 20 3: Q = depending on number of TX pulses  TX pulses Q 011 5 1223 10 2431 20                                                                                                                                                                                |           | 1       | R/W |

|                 | DSP Filter Auto Q<br>Factor Control Enable<br>(sub-index 10)        | AUTO_QF_CTRL_<br>ENA       | 1        | O: Fixed Q factor according to QF_SEL [1:0]  1: Q is automatically switched at 14.8 ms after start of measurement                                                                                                                                                                      |           | 0       | R/W |

|                 |                                                                     |                            |          | QF_SEL         Q start         Q after 14.8 ms           0         5         10           1         5         20           2         10         20           3         5         Depends on TX pulses                                                                                  |           |         |     |

|                 | Automatic Echo<br>Debounce Time<br>Control Enable<br>(sub-index 11) | AUTO_ECHO_DEB_<br>CTRL_ENA | 1        | 0: Fixed 60 μs 1: Fixed 60 μs is automatically switched to 200 μs at 14.8 ms after start of measurement                                                                                                                                                                                |           | 0       | R/W |

|                 | Internal I/O Line<br>Pull-up Enable<br>(sub-index 12)               | IO_PUP_ENA                 | 1        | O: Internal I/O Line pull-up disabled I: Internal I/O Line pull-up enabled                                                                                                                                                                                                             | Yes       |         | R/W |

|                 | I/O Line Slope<br>Control<br>(sub-index 13)                         | IO_SLP_FAST                | 1        | 0: Standard I/O Line slope<br>(60 μs)<br>1: Fast I/O Line slope (20 μs)                                                                                                                                                                                                                | Yes       |         | R/W |

|                 | Advance I/O Line<br>Protocol Enable<br>(sub-index 14)               | ADV_IO_ENA                 | 1        | O: Standard I/O Line protocols Advanced I/O Line protocol Please, see index 13 & 14 for more details.                                                                                                                                                                                  |           | 0       | R/W |

|                 | T <sub>REC1</sub> Threshold<br>Control Enable<br>(sub-index 15)     | TREC1_THR_CTRL_<br>ENA     | 1        | 0: T <sub>REC1</sub> utilizes THR1 curve 1: T <sub>REC1</sub> utilizes fixed threshold NOISE_THR and fixed static gain RX_GAIN_CODE. SENSOR_STATUS [0] (Acoustic Noise Flag) is ORed with SENSOR_STATUS[0] of following T <sub>SND1</sub> /T <sub>SND2</sub> resp. T <sub>REC2</sub> . |           | 0       | R/W |

Table 7. STRUCTURE OF CONFIGURATION MEMORY (continued)

| Conf.<br>Memory |                                                                                |                              | No<br>of |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | EEPROM    |               |     |

|-----------------|--------------------------------------------------------------------------------|------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------|-----|

| index           | Name                                                                           | Short Name                   | bits     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | (Note 11) | Default       | R/W |

| 10              | End of Reverberation<br>Time-out<br>(sub-index 16)                             | END_OF_REVERB_<br>TOUT [5:0] | 6        | Time-out of end-of-reverberation.  In presence of high noise, the signal magnitude at analog front-end may avoid proper detection of end-of-reverberation. Detection of end-of-reverberation is mandatory prior to start of echo detection. This function stops end-of-reverberation measurement by time-out. Improper use may lead to fake echo detection (reverberation detected as echo).  1–LSB ~ 51.2 μs  It is measured from TX end, end-of-reverberation time-out = TX end + END_OF_RE-VERB_TOUT[5:0]×51.2 μs  SENSOR_STATUS[5] is set in case the reverberation time-out is detected. |           | 39<br>(~2 ms) | R/W |