## **ESD Protection Diode**

# Low Capacitance Surface Mount ESD Protection for High-Speed Data Interfaces

The NUP4106 surge protection is designed to protect equipment attached to high speed communication lines from ESD and lightning.

#### **Features**

- SO-8 Package

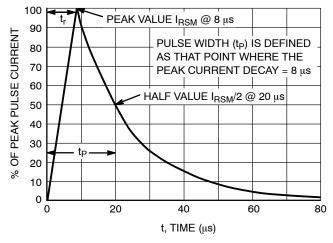

- Peak Power 500 W 8 x 20 μS

- ESD Rating: IEC 61000-4-2 (ESD) 15 kV (air) 8 kV (contact)

- UL Flammability Rating of 94 V-0

- This is a Pb-Free Device

#### **Typical Applications**

- High Speed Communication Line Protection

- T1/E1 Secondary Protection

- T3/E3 Secondary Protection

- Analog Video Protection

- Base Stations

- I<sup>2</sup>C Bus Protection

#### **MAXIMUM RATINGS**

| Rating                                                               | Symbol                            | Value       | Unit |

|----------------------------------------------------------------------|-----------------------------------|-------------|------|

| Peak Power Dissipation<br>8 x 20 μS @ T <sub>A</sub> = 25°C (Note 1) | P <sub>pk</sub>                   | 500         | W    |

| Junction and Storage Temperature Range                               | T <sub>J</sub> , T <sub>stg</sub> | -55 to +150 | °C   |

| Lead Solder Temperature –<br>Maximum 10 Seconds Duration             | TL                                | 260         | °C   |

| IEC 61000-4-2 Contact<br>Air                                         | ESD                               | ±8<br>±15   | kV   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1

1. Non–repetitive current pulse 8 x 20  $\mu S$  exponential decay waveform Pin 2/3 to Pin 5/8

#### ON Semiconductor®

www.onsemi.com

#### SO-8 LOW CAPACITANCE VOLTAGE SUPPRESSOR 500 WATTS PEAK POWER 3.3 VOLTS

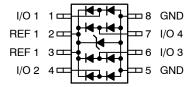

## PIN CONFIGURATION AND SCHEMATIC

SOIC-8 CASE 751 PLASTIC

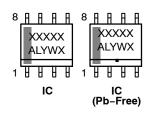

#### MARKING DIAGRAM

A = Assembly Location

Y = Year WW = Work Week ■ = Pb-Free Package

(Note: Microdot may be in either location)

#### **ORDERING INFORMATION**

| Device     | Pac | kage          | Shipping <sup>†</sup> |

|------------|-----|---------------|-----------------------|

| NUP4106DR2 | -   | O-8<br>-Free) | 2500/Tape & Reel      |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

#### **ELECTRICAL CHARACTERISTICS**

| Characteristic                                                | Symbol         | Min | Тур | Max | Unit |

|---------------------------------------------------------------|----------------|-----|-----|-----|------|

| Reverse Breakdown Voltage @ I <sub>t</sub> = 1.0 mA           | $V_{BR}$       | 5.0 | -   | -   | V    |

| Reverse Leakage Current @ V <sub>RWN</sub> = 3.3 V            | I <sub>R</sub> | N/A | -   | 5.0 | μΑ   |

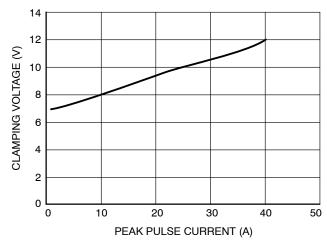

| Maximum Clamping Voltage @ I <sub>PP</sub> = 1.0 A, 8 x 20 μS | V <sub>C</sub> | N/A | -   | 7.0 | V    |

| Maximum Clamping Voltage @ I <sub>PP</sub> = 10 A, 8 x 20 μS  | V <sub>C</sub> | N/A | -   | 10  | V    |

| Maximum Clamping Voltage @ I <sub>PP</sub> = 25 A, 8 x 20 μS  | V <sub>C</sub> | N/A | -   | 15  | V    |

| Between I/O Pins and Ground @ V <sub>R</sub> = 0 V, 1.0 MHz   | Capacitance    | -   | 8.0 | 15  | pF   |

| Between I/O Pins @ V <sub>R</sub> = 0 Volts, 1.0 MHz          | Capacitance    | -   | 4.0 | -   | pF   |

#### **ELECTRICAL CHARACTERISTICS**

$(T_A = 25^{\circ}C \text{ unless otherwise noted})$

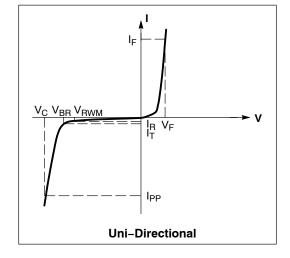

| Symbol           | Parameter                                          |

|------------------|----------------------------------------------------|

| I <sub>PP</sub>  | Maximum Reverse Peak Pulse Current                 |

| V <sub>C</sub>   | Clamping Voltage @ I <sub>PP</sub>                 |

| V <sub>RWM</sub> | Working Peak Reverse Voltage                       |

| I <sub>R</sub>   | Maximum Reverse Leakage Current @ V <sub>RWM</sub> |

| V <sub>BR</sub>  | Breakdown Voltage @ I <sub>T</sub>                 |

| I <sub>T</sub>   | Test Current                                       |

| ΙF               | Forward Current                                    |

| V <sub>F</sub>   | Forward Voltage @ I <sub>F</sub>                   |

| P <sub>pk</sub>  | Peak Power Dissipation                             |

| С                | Capacitance @ V <sub>R</sub> = 0 and f = 1.0 MHz   |

<sup>\*</sup>See Application Note AND8308/D for detailed explanations of datasheet parameters.

#### **TYPICAL CHARACTERISTICS**

Figure 1. 8 x 20 μs Pulse Waveform

Figure 2. Clamping Voltage vs. Peak Pulse Current (8 x 20 μs Waveform)

#### **APPLICATIONS INFORMATION**

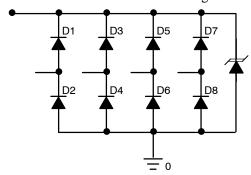

The NUP4106 is a low capacitance surge protection diode array designed to protect sensitive electronics such as communications systems, computers, and computer peripherals against damage due to ESD events or transient overvoltage conditions. Because of its low capacitance, it can be used in high speed I/O data lines. The integrated design of the NUP4106 offers surge rated, low capacitance steering diodes and a surge protection diode integrated in a single package (SO-8). If a transient condition occurs, the steering diodes will drive the transient to the positive rail of the power supply or to ground. The surge protection device protects the power line against overvoltage conditions avoiding damage to the power supply and other downstream components.

#### **NUP4106 Configuration Options**

The NUP4106 is able to protect up to four data lines against transient overvoltage conditions by driving them to a fixed reference point for clamping purposes. The steering diodes will be forward biased whenever the voltage on the protected line exceeds the reference voltage (Vf or  $V_{CC}$  + Vf). The diodes will force the transient current to bypass the sensitive circuit.

Data lines are connected at pins 1, 4, 6 and 7. The negative reference is connected at pins 5 and 8. These pins must be connected directly to ground using a ground plane to minimize the PCB's ground inductance. It is very important to reduce the PCB trace lengths as much as possible to minimize parasitic inductances.

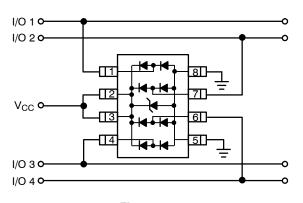

#### Option 1

Protection of four data lines and the power supply using  $V_{CC}$  as reference.

Figure 3.

For this configuration, connect pins 2 and 3 directly to the positive supply rail ( $V_{\rm CC}$ ). The data lines are referenced to the supply voltage. The internal surge protection diode prevents overvoltage on the supply rail. Biasing of the steering diodes reduces their capacitance.

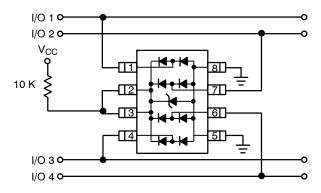

#### Option 2

Protection of four data lines with bias and power supply isolation resistor.

Figure 4.

The NUP4106 can be isolated from the power supply by connecting a series resistor between pins 2 and 3 and  $V_{\rm CC}$ . A  $10~{\rm k}\Omega$  resistor is recommended for this application. This will maintain a bias on the internal surge protection and steering diodes, reducing their capacitance.

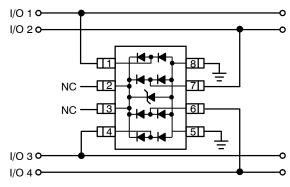

#### Option 3

Protection of four data lines using the internal surge protection diode as reference.

Figure 5.

In applications lacking a positive supply reference or those cases in which a fully isolated power supply is required, the internal surge protection can be used as the reference. For these applications, pins 2 and 3 are not connected. In this configuration, the steering diodes will conduct whenever the voltage on the protected line exceeds the working voltage of the surge protection plus one diode drop (Vc=Vf + VRWM).

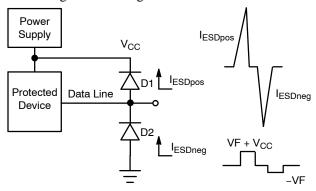

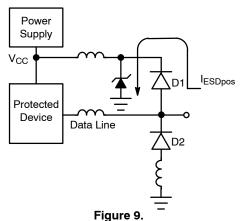

#### **ESD Protection of Power Supply Lines**

When using diodes for data line protection, referencing to a supply rail provides advantages. Biasing the diodes reduces their capacitance and minimizes signal distortion. Implementing this topology with discrete devices does have disadvantages. This configuration is shown below:

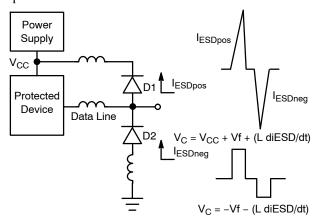

Figure 6.

Looking at the figure above, it can be seen that when a positive ESD condition occurs, diode D1 will be forward biased while diode D2 will be forward biased when a negative ESD condition occurs. For slower transient conditions, this system may be approximated as follows:

For positive pulse conditions:

$$Vc = V_{CC} + Vf_{D1}$$

For negative pulse conditions:

$$Vc = -Vf_{D2}$$

ESD events can have rise times on the order of some number of nanoseconds. Under these conditions, the effect of parasitic inductance must be considered. A pictorial representation of this is shown below.

Figure 7.

An approximation of the clamping voltage for these fast transients would be:

For positive pulse conditions:

$$Vc = V_{CC} + Vf + (L dieso/dt)$$

For negative pulse conditions:

$$Vc = -Vf - (L \operatorname{diesp}/\operatorname{dt})$$

As shown in the formulas, the clamping voltage (Vc) not only depends on the Vf of the steering diodes but also on the

L diesd/dt factor. A relatively small trace inductance can result in hundreds of volts appearing on the supply rail. This endangers both the power supply and anything attached to that rail. This highlights the importance of good board layout. Taking care to minimize the effects of parasitic inductance will provide significant benefits in transient immunity.

Even with good board layout, some disadvantages are still present when discrete diodes are used to suppress ESD events across datalines and the supply rail. Discrete diodes with good transient power capability will have larger die and therefore higher capacitance. This capacitance becomes problematic as transmission frequencies increase. Reducing capacitance generally requires reducing die size. These small die will have higher forward voltage characteristics at typical ESD transient current levels. This voltage combined with the smaller die can result in device failure.

The ON Semiconductor NUP4106 was developed to overcome the disadvantages encountered when using discrete diodes for ESD protection. This device integrates a surge protection diode within a network of steering diodes.

Figure 8. NUP4106 Equivalent Circuit

During an ESD condition, the ESD current will be driven to ground through the surge protection diode as shown below.

The resulting clamping voltage on the protected IC will be: Vc = VFD1 + VRWM.

The clamping voltage of the surge protection diode is provided in Figure 2 and depends on the magnitude of the ESD current. The steering diodes are fast switching devices with unique forward voltage and low capacitance characteristics.

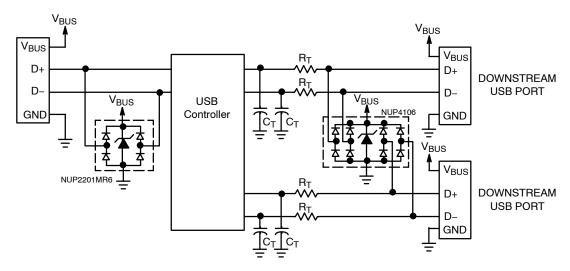

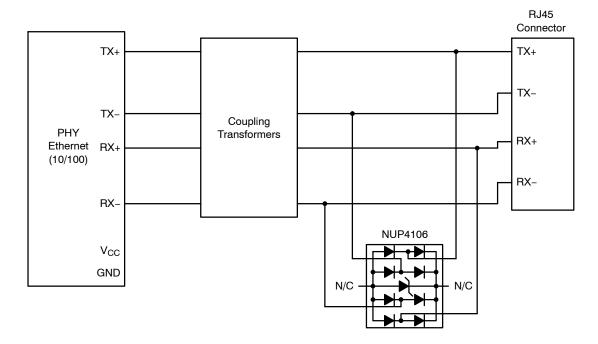

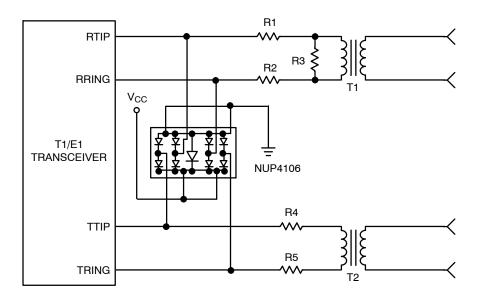

#### **TYPICAL APPLICATIONS**

UPSTREAM USB PORT

Figure 10. ESD Protection for USB Port

Figure 11. Protection for Ethernet 10/100 (Differential Mode)

Figure 12. TI/E1 Interface Protection

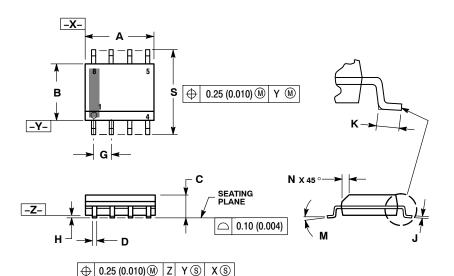

SOIC-8 NB CASE 751-07 **ISSUE AK**

**DATE 16 FEB 2011**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER

- ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

- DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

- MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE

- DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

- 751-01 THRU 751-06 ARE OBSOLETE. NEW STANDARD IS 751-07.

|     | MILLIMETERS |      | INCHES    |       |

|-----|-------------|------|-----------|-------|

| DIM | MIN         | MAX  | MIN       | MAX   |

| Α   | 4.80        | 5.00 | 0.189     | 0.197 |

| В   | 3.80        | 4.00 | 0.150     | 0.157 |

| С   | 1.35        | 1.75 | 0.053     | 0.069 |

| D   | 0.33        | 0.51 | 0.013     | 0.020 |

| G   | 1.27 BSC    |      | 0.050 BSC |       |

| Н   | 0.10        | 0.25 | 0.004     | 0.010 |

| J   | 0.19        | 0.25 | 0.007     | 0.010 |

| K   | 0.40        | 1.27 | 0.016     | 0.050 |

| М   | 0 °         | 8 °  | 0 °       | 8 °   |

| N   | 0.25        | 0.50 | 0.010     | 0.020 |

| S   | 5.80        | 6.20 | 0.228     | 0.244 |

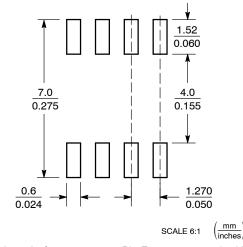

#### **SOLDERING FOOTPRINT\***

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### **GENERIC MARKING DIAGRAM\***

XXXXX = Specific Device Code = Assembly Location = Wafer Lot = Year = Work Week W

= Pb-Free Package

XXXXXX XXXXXX AYWW AYWW Ŧ  $\mathbb{H}$ Discrete **Discrete** (Pb-Free)

XXXXXX = Specific Device Code = Assembly Location Α = Year ww = Work Week = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

#### **STYLES ON PAGE 2**

| DOCUMENT NUMBER: | 98ASB42564B | Electronic versions are uncontrolled except when accessed directly from the Document Repositor<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | SOIC-8 NB   |                                                                                                                                                                                   | PAGE 1 OF 2 |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. **onsemi** does not convey any license under its patent rights nor the rights of others.

#### SOIC-8 NB CASE 751-07 ISSUE AK

#### **DATE 16 FEB 2011**

| STYLE 1: PIN 1. EMITTER 2. COLLECTOR 3. COLLECTOR 4. EMITTER 5. EMITTER 6. BASE 7. BASE 8. EMITTER                                                                 | STYLE 2: PIN 1. COLLECTOR, DIE, #1 2. COLLECTOR, #1 3. COLLECTOR, #2 4. COLLECTOR, #2 5. BASE, #2 6. EMITTER, #2 7. BASE, #1 8. EMITTER, #1               | STYLE 3: PIN 1. DRAIN, DIE #1 2. DRAIN, #1 3. DRAIN, #2 4. DRAIN, #2 5. GATE, #2 6. SOURCE, #2 7. GATE, #1 8. SOURCE, #1                            | STYLE 4: PIN 1. ANODE 2. ANODE 3. ANODE 4. ANODE 5. ANODE 6. ANODE 7. ANODE 8. COMMON CATHODE                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STYLE 5: PIN 1. DRAIN 2. DRAIN 3. DRAIN 4. DRAIN 5. GATE 6. GATE 7. SOURCE 8. SOURCE                                                                               | STYLE 6: PIN 1. SOURCE 2. DRAIN 3. DRAIN 4. SOURCE 5. SOURCE 6. GATE 7. GATE 8. SOURCE                                                                    | STYLE 7: PIN 1. INPUT 2. EXTERNAL BYPASS 3. THIRD STAGE SOURCE 4. GROUND 5. DRAIN 6. GATE 3 7. SECOND STAGE Vd 8. FIRST STAGE Vd                    | STYLE 8:<br>PIN 1. COLLECTOR, DIE #1<br>2. BASE. #1                                                                                                                             |

| STYLE 9: PIN 1. EMITTER, COMMON 2. COLLECTOR, DIE #1 3. COLLECTOR, DIE #2 4. EMITTER, COMMON 5. EMITTER, COMMON 6. BASE, DIE #2 7. BASE, DIE #1 8. EMITTER, COMMON | STYLE 10: PIN 1. GROUND 2. BIAS 1 3. OUTPUT 4. GROUND 5. GROUND 6. BIAS 2 7. INPUT 8. GROUND                                                              | STYLE 11: PIN 1. SOURCE 1 2. GATE 1 3. SOURCE 2 4. GATE 2 5. DRAIN 2 6. DRAIN 2 7. DRAIN 1 8. DRAIN 1                                               | STYLE 12: PIN 1. SOURCE 2. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                                         |

| STYLE 13: PIN 1. N.C. 2. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                              | STYLE 14: PIN 1. N-SOURCE 2. N-GATE 3. P-SOURCE 4. P-GATE 5. P-DRAIN 6. P-DRAIN 7. N-DRAIN 8. N-DRAIN                                                     | STYLE 15: PIN 1. ANODE 1 2. ANODE 1 3. ANODE 1 4. ANODE 1 5. CATHODE, COMMON 6. CATHODE, COMMON 7. CATHODE, COMMON 8. CATHODE, COMMON               | STYLE 16:  PIN 1. EMITTER, DIE #1  2. BASE, DIE #1  3. EMITTER, DIE #2  4. BASE, DIE #2  5. COLLECTOR, DIE #2  7. COLLECTOR, DIE #2  8. COLLECTOR, DIE #1  8. COLLECTOR, DIE #1 |

| STYLE 17: PIN 1. VCC 2. V2OUT 3. V1OUT 4. TXE 5. RXE 6. VEE 7. GND 8. ACC                                                                                          | STYLE 18: PIN 1. ANODE 2. ANODE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. CATHODE 8. CATHODE                                                                 | STYLE 19: PIN 1. SOURCE 1 2. GATE 1 3. SOURCE 2 4. GATE 2 5. DRAIN 2 6. MIRROR 2 7. DRAIN 1 8. MIRROR 1                                             | STYLE 20: PIN 1. SOURCE (N) 2. GATE (N) 3. SOURCE (P) 4. GATE (P) 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                           |

| STYLE 21: PIN 1. CATHODE 1 2. CATHODE 2 3. CATHODE 3 4. CATHODE 4 5. CATHODE 5 6. COMMON ANODE 7. COMMON ANODE 8. CATHODE 6                                        | STYLE 22: PIN 1. I/O LINE 1 2. COMMON CATHODE/VCC 3. COMMON CATHODE/VCC 4. I/O LINE 3 5. COMMON ANODE/GND 6. I/O LINE 4 7. I/O LINE 5 8. COMMON ANODE/GND | STYLE 23: PIN 1. LINE 1 IN 2. COMMON ANODE/GND 3. COMMON ANODE/GND 4. LINE 2 IN 5. LINE 2 OUT 6. COMMON ANODE/GND 7. COMMON ANODE/GND 8. LINE 1 OUT | STYLE 24: PIN 1. BASE 2. EMITTER 3. COLLECTOR/ANODE 4. COLLECTOR/ANODE 5. CATHODE 6. CATHODE 7. COLLECTOR/ANODE 8. COLLECTOR/ANODE                                              |

| STYLE 25: PIN 1. VIN 2. N/C 3. REXT 4. GND 5. IOUT 6. IOUT 7. IOUT 8. IOUT                                                                                         | STYLE 26: PIN 1. GND 2. dv/dt 3. ENABLE 4. ILIMIT 5. SOURCE 6. SOURCE 7. SOURCE 8. VCC                                                                    | STYLE 27: PIN 1. ILIMIT 2. OVLO 3. UVLO 4. INPUT+ 5. SOURCE 6. SOURCE 7. SOURCE 8. DRAIN                                                            | STYLE 28: PIN 1. SW TO GND 2. DASIC OFF 3. DASIC SW_DET 4. GND 5. V_MON 6. VBULK 7. VBULK 8. VIN                                                                                |

| STYLE 29: PIN 1. BASE, DIE #1 2. EMITTER, #1 3. BASE, #2 4. EMITTER, #2 5. COLLECTOR, #2 6. COLLECTOR, #2 7. COLLECTOR, #1 8. COLLECTOR, #1                        | STYLE 30: PIN 1. DRAIN 1 2. DRAIN 1 3. GATE 2 4. SOURCE 2 5. SOURCE 1/DRAIN 2 6. SOURCE 1/DRAIN 2 7. SOURCE 1/DRAIN 2 8. GATE 1                           |                                                                                                                                                     |                                                                                                                                                                                 |

| DOCUMENT NUMBER: | 98ASB42564B | Electronic versions are uncontrolled except when accessed directly from the Document Hepository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | SOIC-8 NB   |                                                                                                                                                                                     | PAGE 2 OF 2 |  |

onsemi and ONSEMi are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. onsemi does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMi., and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer p

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT: Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

TECHNICAL SUPPORT North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative