## ecoSwitch™ Advanced Load Management

# Controlled Load Switch with Reverse Current Protection and Ultra Low R<sub>ON</sub>

### **NCP45790**

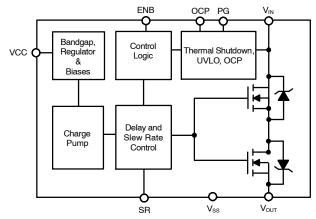

The NCP45790 load management device provides a component and area-reducing solution for efficient power domain switching with inrush current limit via soft start. This device is designed to integrate control and driver functionality with back-to-back high performance low on-resistance power MOSFETs in a single package. This cost effective solution is ideal for reverse current applications and the specific power management and disconnect functions used in USB Type-C and Type-C Power Delivery ports.

### **Features**

- Advanced Controller with Charge Pump

- Integrated N-Channel MOSFET with Ultra Low RON

- Soft-Start via Controlled Slew Rate

- Adjustable Slew Rate Control

- Fault Detection with Power Good Output

- Thermal Shutdown and Under Voltage Lockout

- Short-Circuit and Adjustable Over-Current Protections

- Reverse-Current Protection Option

- Input Voltage Range 3 V to 24 V

- Extremely Low Standby Current

- This is a Pb-free, RoHS/REACH Compliant Device

### **Typical Applications**

- USB Type C & Type-C Power Delivery

- Reverse Current Load Switching Applications

- Servers, Set-Top Boxes and Gateways

- Notebook and Tablet Computers

- Telecom, Networking, Medical and Industrial Equipment

- Hot-Swap Devices and Peripheral Ports

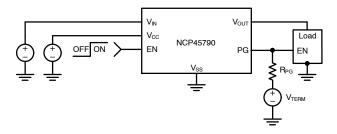

Figure 1. Block Diagram

### ON Semiconductor®

### www.onsemi.com

| R <sub>ON</sub> TYP    | I <sub>MAX</sub> * |

|------------------------|--------------------|

| $8.0~\mathrm{m}\Omega$ | 8 A                |

\*I<sub>MAX</sub> is defined as the maximum steady state current the load switch can pass at room ambient temperature without entering thermal lockout. See the SOA section for more information on transient current limitations.

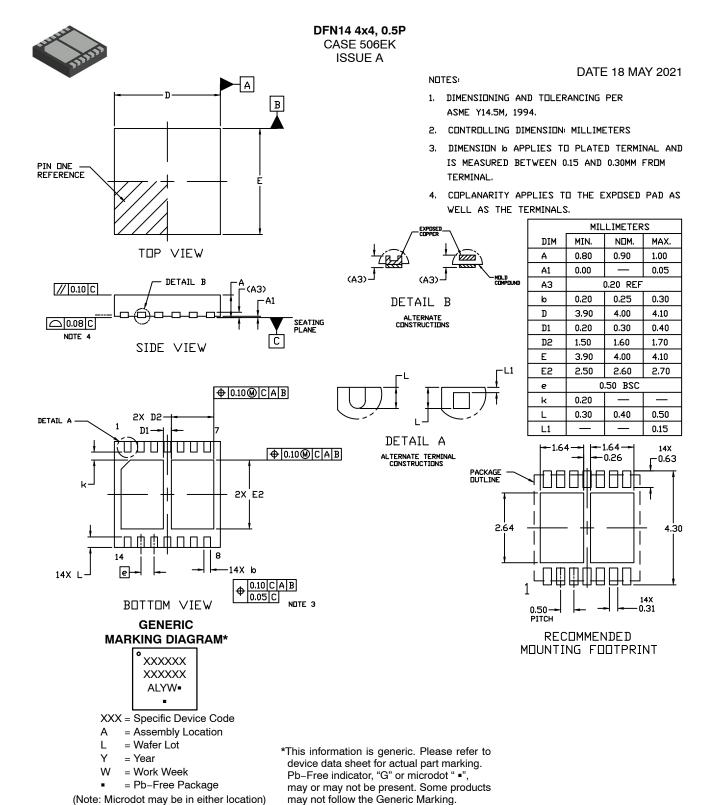

DFN14, 4x4 CASE 506EK

### **MARKING DIAGRAM**

45790 = Specific Device Code

A = Assembly Location

L = Wafer Lot

Y = Year W = Work

W = Work Week ■ Pb-Free Package

(Note: Microdot may be in either location)

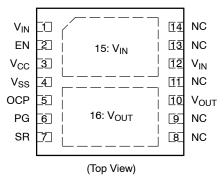

### **PIN CONFIGURATION**

### **ORDERING INFORMATION**

| Device            | Package   | Shipping      |

|-------------------|-----------|---------------|

| NCP45790IMN24RTWG | DFN14     | 3000 / Tape & |

|                   | (Pb-Free) | Reel          |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

**Table 1. PIN DESCRIPTION**

| Pin     | Name             | Function                                                                                                                                                                                       |

|---------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1,12,15 | $V_{IN}$         | Input voltage (3 V - 24 V) - Pin 15 should be used for high current (>0.5 A)                                                                                                                   |

| 2       | EN               | Active-high digital input used to turn on the MOSFET driver, pin has an internal pull down resistor to GND                                                                                     |

| 3       | V <sub>CC</sub>  | Driver supply voltage (3.0 V – 5.5 V)                                                                                                                                                          |

| 4       | $V_{SS}$         | Driver ground                                                                                                                                                                                  |

| 5       | OCP              | Over-current protection trip point adjustment made with a voltage applied (0 V - 1.2 V), pin has an internal pull up resistor to EN; short to ground if over-current protection is not needed  |

| 6       | PG               | Active–high, open–drain output that indicates when the gate of the MOSFET is fully charged, external pull up resistor ≥ 100 kΩ to an external voltage source required; tie to GND if not used. |

| 7       | SR               | Slew Rate control pin. Slew rate adjustment made with an external capacitor to GND; float if not used.                                                                                         |

| 10,16   | V <sub>OUT</sub> | Source of MOSFET connected to load. Includes an internal bleed resistor to GND. – Pin 16 should be used for high current (>0.5 A)                                                              |

### **Table 2. ABSOLUTE MAXIMUM RATINGS**

| Rating                                                                                         | Symbol             | Value                              | Unit       |

|------------------------------------------------------------------------------------------------|--------------------|------------------------------------|------------|

| Supply Voltage Range                                                                           | V <sub>CC</sub>    | -0.3 to 6                          | V          |

| Input Voltage Range                                                                            | V <sub>IN</sub>    | -0.3 to 30                         | V          |

| Output Voltage Range                                                                           | V <sub>OUT</sub>   | -0.3 to 30                         | V          |

| EN Input Voltage Range                                                                         | V <sub>EN</sub>    | GND-0.3 to (V <sub>CC</sub> + 0.3) | V          |

| PG Output Voltage Range (Note 1)                                                               | $V_{PG}$           | -0.3 to 6                          | V          |

| OCP Input Voltage Range                                                                        | V <sub>OCP</sub>   | -0.3 to 6                          | V          |

| Thermal Resistance, Junction-to-Ambient, Steady State (Note 2)                                 | $R_{	heta JA}$     | 28.6                               | °C/W       |

| Thermal Resistance, Junction-to-Case (V <sub>IN</sub> Paddle)                                  | $R_{	heta JC}$     | 1.7                                | °C/W       |

| Continuous MOSFET Current @ T <sub>A</sub> = 25°C (Note 2)                                     | I <sub>MAX</sub>   | 20                                 | Α          |

| Total Power Dissipation @ T <sub>A</sub> = 25°C (Note 2)<br>Derate above T <sub>A</sub> = 25°C | P <sub>D</sub>     | 3.49<br>34.9                       | W<br>mW/°C |

| Storage Temperature Range                                                                      | T <sub>STG</sub>   | -55 to 150                         | °C         |

| Lead Temperature, Soldering (10 sec.)                                                          | T <sub>SLD</sub>   | 260                                | °C         |

| ESD Capability, Human Body Model (Notes 3 and 4)                                               | ESD <sub>HBM</sub> | 2                                  | kV         |

| ESD Capability, Charged Device Model (Notes 3 and 4)                                           | ESD <sub>CDM</sub> | 1                                  | kV         |

| Latch-up Current Immunity (Note 3)                                                             | LU                 | 100                                | mA         |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- 1. PG is an open drain output that requires an external pull-up resistor > 100 k $\Omega$  to an external voltage source.

- FG is all open drain output that requires all external pull-up resistor > 100 ks2 to all external voltage source.

Surface-mounted on FR4 board using the minimum recommended pad size, 1 oz Cu. Over current protection will limit maximum realized current to 8 A at highest setting.

Tested by the following methods @ T<sub>A</sub> = 25°C:

ESD Human Body Model tested FSD STMS 0.4

- - ESD Charged Device Model per ESD STM5.3.1

- Latch-up Current tested per JESD78

- Rating is for all pins except for V<sub>IN</sub> and V<sub>OUT</sub> which are tied to the internal MOSFET's Drain and Source. Typical MOSFET ESD performance for V<sub>IN</sub> and V<sub>OUT</sub> should be expected and these devices should be treated as ESD sensitive.

**Table 3. OPERATING RANGES**

| Rating                                                                  | Symbol             | Min   | Max  | Unit |

|-------------------------------------------------------------------------|--------------------|-------|------|------|

| VCC - (V <sub>IN</sub> > 4.5 V)                                         | V <sub>CC</sub>    | 3     | 5.5  | V    |

| VCC - (V <sub>IN</sub> < 4.5 V)                                         | V <sub>CC</sub>    | 4.5   | 5.5  | V    |

| VIN - (V <sub>CC</sub> > 4.5 V)                                         | $V_{IN}$           | 3     | 24   | V    |

| VIN - (V <sub>CC</sub> < 4.5 V)                                         | $V_{IN}$           | 4.5   | 24   | V    |

| OCP External Resistor to VSS                                            | R <sub>OCP</sub>   | short | open | kΩ   |

| OFF to ON Transition Energy Dissipation Limit (See Application Section) | E <sub>TRANS</sub> | 0     | 200  | mJ   |

| VSS                                                                     | $V_{SS}$           | -     | 0    | V    |

| Ambient Temperature                                                     | $T_A$              | -40   | 85   | °C   |

| Junction Temperature                                                    | $T_J$              | -40   | 125  | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

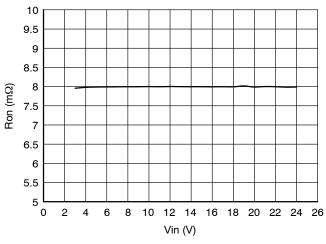

Table 4. ELECTRICAL CHARACTERISTICS (T<sub>J</sub> = 25°C, V<sub>CC</sub> = 3 V - 5.5 V, unless otherwise specified)

| Parameter                                                            | Conditions                                                               | Symbol             | Min  | Тур  | Max | Unit |

|----------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------|------|------|-----|------|

| On-Resistance                                                        | V <sub>CC</sub> = 4.5 V; V <sub>IN</sub> = 3 V                           | R <sub>ON</sub>    | -    | 8.0  | 9.0 | mΩ   |

|                                                                      | V <sub>CC</sub> = 3.3 V; V <sub>IN</sub> = 4.5 V                         |                    | -    | 8.0  | 9.0 | 1    |

|                                                                      | V <sub>CC</sub> = 3.3 V; V <sub>IN</sub> = 15 V                          |                    | -    | 8.0  | 9.0 | 1    |

|                                                                      | V <sub>CC</sub> = 3.3 V; V <sub>IN</sub> = 24 V                          |                    | -    | 8.0  | 9.0 | 1    |

| Leakage Current – V <sub>IN</sub> to V <sub>OUT</sub> (Note 5)       | V <sub>EN</sub> = 0 V; V <sub>IN</sub> = 24 V                            | I <sub>LEAK</sub>  | -    | 10.8 | 100 | nA   |

| Reverse Leakage – V <sub>OUT</sub> to V <sub>IN</sub>                | V <sub>EN</sub> = 0 V; V <sub>IN</sub> = 24 V (for typical)              | I <sub>RLEAK</sub> | -    | 35   | 100 | nA   |

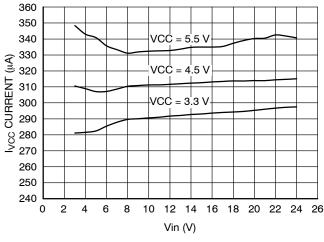

| V <sub>IN</sub> Control Current – V <sub>IN</sub> to V <sub>SS</sub> | V <sub>EN</sub> = 0 V; V <sub>IN</sub> = 24 V (for typical)              | I <sub>INCTL</sub> | -    | 0.8  | 1.5 | μΑ   |

|                                                                      | V <sub>EN</sub> = V <sub>CC</sub> ; V <sub>IN</sub> = 24 V (for typical) | I <sub>INCTL</sub> | -    | 150  | 300 | μΑ   |

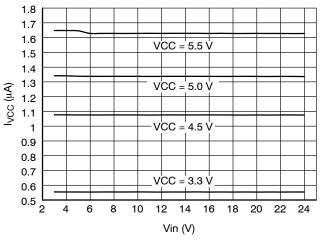

| Supply Standby Current (Note 6)                                      | V <sub>EN</sub> = 0 V; V <sub>IN</sub> = 24 V (for typical)              | I <sub>STBY</sub>  | -    | 1.3  | 5   | μΑ   |

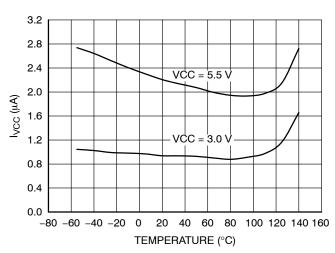

| Supply Dynamic Current (Note 7)                                      | V <sub>EN</sub> = V <sub>CC</sub> ; V <sub>IN</sub> = 24 V (for typical) | I <sub>DYN</sub>   | -    | 0.3  | 0.5 | mA   |

| EN Input High Voltage                                                |                                                                          | V <sub>IH</sub>    | 2    | -    | -   | V    |

| EN Input Low Voltage                                                 |                                                                          | $V_{IL}$           | -    | -    | 0.8 | V    |

| EN Input Leakage Current                                             | V <sub>EN</sub> = 0 V                                                    | I <sub>IL</sub>    | -1.0 | -    | 1   | μΑ   |

| EN Pull Down Resistance                                              |                                                                          | $R_{PD}$           | 76   | 100  | 124 | kΩ   |

| PG Output Low Voltage                                                | I <sub>SINK</sub> = 100 μA                                               | $V_{OL}$           | -    | 21.8 | 100 | mV   |

| PG Output Leakage Current                                            | V <sub>TERM</sub> = 3.3 V                                                | loh                | -    | 3.45 | 100 | nA   |

| Slew Rate Control Constant (Note 8)                                  |                                                                          | K <sub>SR</sub>    | 70   | 99   | 130 | μΑ   |

| FAULT PROTECTIONS                                                    |                                                                          |                    |      |      |     |      |

| Thermal Shutdown Threshold (Note 9)                                  |                                                                          | T <sub>SDT</sub>   | -    | 145  | -   | °C   |

| Thermal Shutdown Hysteresis (Note 9)                                 |                                                                          | T <sub>HYS</sub>   | -    | 20   | -   | °C   |

| V <sub>IN</sub> Under Voltage Lockout Threshold                      | V <sub>IN</sub> rising                                                   | V <sub>UVLO</sub>  | -    | 2.0  | 2.1 | V    |

| V <sub>IN</sub> Under Voltage Lockout Hysteresis                     |                                                                          | V <sub>HYS</sub>   | -    | 220  | 300 | mV   |

| Over-Current Protection Trip                                         | R <sub>OCP</sub> = open                                                  | I <sub>TRIP</sub>  | 0.6  | 1.0  | 1.2 | Α    |

|                                                                      | $R_{OCP} = 20 \text{ k}\Omega$                                           |                    | _    | 7.1  | -   |      |

|                                                                      | R <sub>OCP</sub> = short to GND (Note 10)                                | 1                  | -    | 11   | -   | 1    |

| Over-Current Protection Blanking Time                                |                                                                          | t <sub>OCP</sub>   | -    | 2.25 | -   | ms   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

$I_{SC}$

Soft Short & Hard Shorts (Note 12)

- 5. Average current from V<sub>IN</sub> to V<sub>OUT</sub> with MOSFET turned off.

- 6. Average current from V<sub>CC</sub> to GND with MOSFET turned off.

- 7. Average current from V<sub>CC</sub> to GND after charge up time of MOSFET.

8. See Applications Information section for details on how to adjust the gate slew rate.

- 9. Operation above T<sub>J</sub> = 125°C is not guaranteed.

Short-Circuit Protection Trip Current (Note 11)

- 10. Transient currents exceeding the short-circuit protection trip current will cause the device to fault. For OCP settings less than 20 k $\Omega$ , high steady state currents may cause an over temperature lockout before the OCP threshold is reached due to self-heating.

- 11. Short circuit protection testing assumed a 100 W supply capability limit on Vin.

- 12. Short Circuit Protection protects the device against hard shorts ( $R_{SHORT} \le 250 \text{ m}\Omega$  Vout to Ground) for Vin < 18 V, and against soft shorts  $(R_{SHORT} > 250 \text{ m}\Omega)$  for Vin < 24 V.

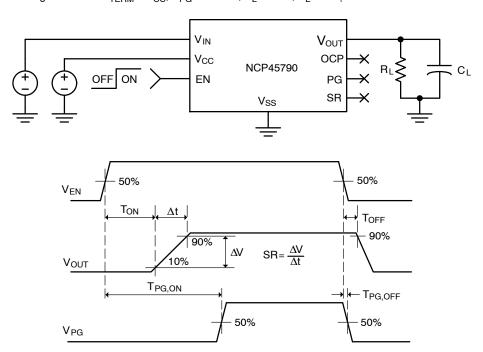

Table 5. SWITCHING CHARACTERISTICS ( $T_J = 25^{\circ}C$  unless otherwise specified) (Notes 13 and 14)

| Parameter                  | Conditions                                      | Symbol             | Min | Тур  | Max | Unit |

|----------------------------|-------------------------------------------------|--------------------|-----|------|-----|------|

| Output Slew Rate - Default | V <sub>CC</sub> = 4.5 V; V <sub>IN</sub> = 3 V  | SR                 | 13  | 19.4 | 28  | V/ms |

|                            | V <sub>CC</sub> = 5.0 V; V <sub>IN</sub> = 3 V  |                    | 13  | 19.7 | 28  |      |

|                            | V <sub>CC</sub> = 3.3 V; V <sub>IN</sub> = 24 V |                    | 13  | 22.4 | 28  |      |

|                            | V <sub>CC</sub> = 5.0 V; V <sub>IN</sub> = 24 V |                    | 13  | 22.5 | 28  |      |

| Output Turn-on Delay       | V <sub>CC</sub> = 4.5 V; V <sub>IN</sub> = 3 V  | T <sub>ON</sub>    | 100 | 188  | 700 | μs   |

|                            | V <sub>CC</sub> = 5.0 V; V <sub>IN</sub> = 3 V  |                    | 100 | 187  | 700 |      |

|                            | V <sub>CC</sub> = 3.3 V; V <sub>IN</sub> = 24 V |                    | 100 | 846  | 700 |      |

|                            | V <sub>CC</sub> = 5.0 V; V <sub>IN</sub> = 24 V |                    | 100 | 480  | 700 |      |

| Output Turn-off Delay      | V <sub>CC</sub> = 4.5 V; V <sub>IN</sub> = 3 V  | T <sub>OFF</sub>   | -   | 105  | _   | μs   |

|                            | V <sub>CC</sub> = 5.0 V; V <sub>IN</sub> = 3 V  |                    | -   | 96   | _   |      |

|                            | V <sub>CC</sub> = 3.3 V; V <sub>IN</sub> = 24 V |                    | -   | 90   | _   | 1    |

|                            | V <sub>CC</sub> = 5.0 V; V <sub>IN</sub> = 24 V |                    | -   | 78   | -   |      |

| Power Good Turn-on Time    | V <sub>CC</sub> = 4.5 V; V <sub>IN</sub> = 3 V  | T <sub>PG,ON</sub> | 0.4 | 0.88 | 3.5 | ms   |

|                            | V <sub>CC</sub> = 5.0 V; V <sub>IN</sub> = 3 V  |                    | 0.4 | 0.79 | 3.5 | 1    |

|                            | V <sub>CC</sub> = 3.3 V; V <sub>IN</sub> = 24 V |                    | 0.4 | 2.4  | 3.5 | 1    |

|                            | V <sub>CC</sub> = 5.0 V; V <sub>IN</sub> = 24 V |                    | 0.4 | 1.9  | 3.5 |      |

| Power Good Turn-off Time   | V <sub>CC</sub> = 4.5 V; V <sub>IN</sub> = 3 V  | $T_{PG,OFF}$       | -   | -    | 10  | ns   |

|                            | V <sub>CC</sub> = 5.0 V; V <sub>IN</sub> = 3 V  |                    | -   | -    | 10  |      |

|                            | V <sub>CC</sub> = 3.3 V; V <sub>IN</sub> = 24 V |                    | -   | -    | 10  |      |

|                            | V <sub>CC</sub> = 5.0 V; V <sub>IN</sub> = 24 V |                    | -   | -    | 10  | 1    |

<sup>13.</sup> See below figure for Test Circuit and Timing Diagram. 14. Tested with the following conditions:  $V_{TERM} = V_{CC}$ ;  $R_{PG} = 100 \text{ k}\Omega$ ;  $R_{L} = 10 \Omega$ ;  $C_{L} = 0.1 \mu F$ .

Figure 2. Switching Characteristics Test Circuit and Timing Diagrams

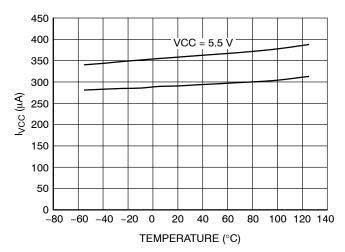

### **TYPICAL CHARACTERISTICS** ( $T_J = 25^{\circ}C$ unless otherwise specified)

14 12 10 Ron (m\O) 8 6 4 2 0 60 80 100 120 140 -80 -60 -40 -20 0 20 40 TEMPERATURE (°C)

Figure 3. On-Resistance vs. Input Voltage

Figure 4. On-Resistance vs. Temperature

Figure 5. Supply Standby Current vs. Supply Voltage

Figure 6. Supply Standby Current vs. Temperature

Figure 7. Dynamic Current vs. Input Voltage

Figure 8. Supply Dynamic Current vs. Temperature

### TYPICAL CHARACTERISTICS ( $T_J = 25$ °C unless otherwise specified) (continued)

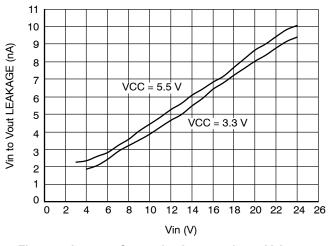

Figure 9. Input to Output Leakage vs. Input Voltage (EN = 0 V)

Figure 10. Input to Output Leakage vs. Temperature (EN = HIGH)

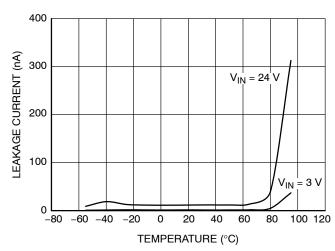

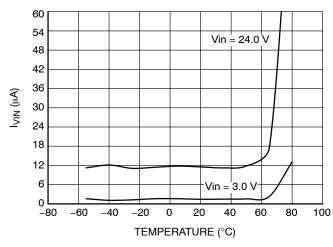

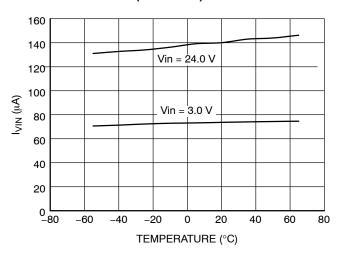

Figure 11. Vin Controller Current vs. Temperature (EN = 0)

Figure 12. Vin Controller Current vs. Temperature (EN = HIGH)

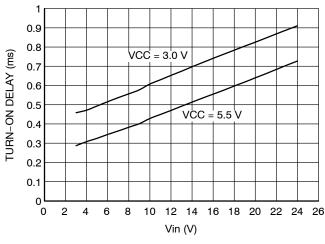

Figure 13. Output Turn-On Delay vs. Input Voltage

Figure 14. Output Turn-On Delay vs. Temperature

### **TYPICAL CHARACTERISTICS** (T<sub>J</sub> = 25°C unless otherwise specified) (continued)

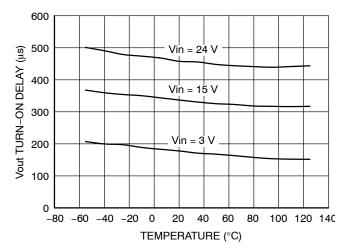

Figure 15. Power Good Turn-On Time vs. Input Voltage

Figure 16. Power Good Turn-On vs. Temperature

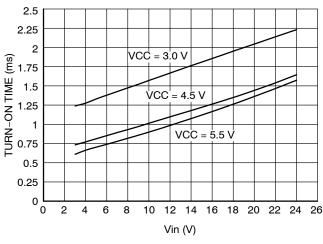

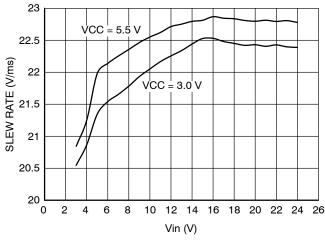

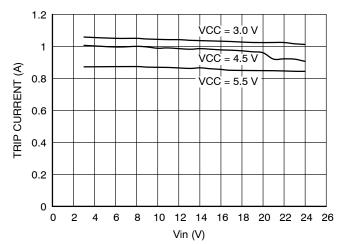

Figure 17. Default Slew Rate vs. Input Voltage (SR Pin = Floating)

Figure 18. Slew Rate vs. Input Voltage (SR Pin = 10 nF to GND)

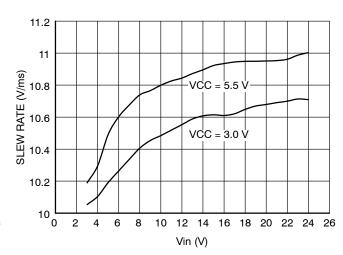

Figure 19. KSR vs. Temperature

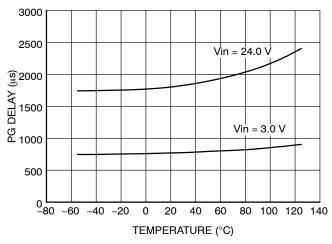

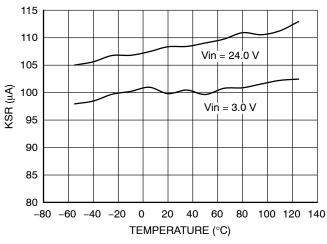

Figure 20. OCP Trip Current vs. Input Voltage (OCP = Float)

### $\textbf{TYPICAL CHARACTERISTICS} \ (T_J = 25^{\circ}\text{C unless otherwise specified)} \ (continued)$

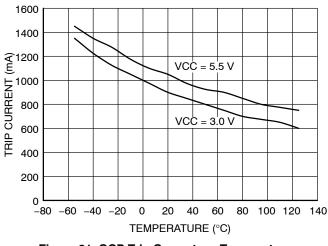

Figure 21. OCP Trip Current vs. Temperature (OCP = OPEN)

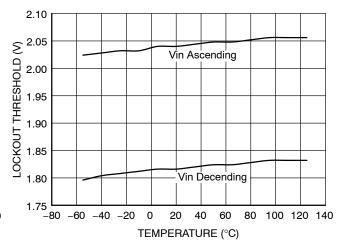

Figure 22. UVLO Trip Voltage vs. Temperature

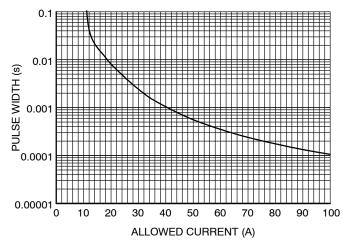

Figure 23. Safe Operating Area Transient Current

### **APPLICATIONS INFORMATION**

### **Enable Control**

The NCP45790 part enables the MOSFET in an active–high configuration. When the EN pin is at a logic high level and the  $V_{CC}$  supply pin has an adequate voltage applied, the MOSFET will be enabled. When the EN pin is at a logic low level, the MOSFET will be disabled. An internal pull down resistor to ground on the EN pin ensures that the MOSFET will be disabled when not driven.

### **Short-Circuit Protection (Hard short)**

The NCP45790 device is equipped with a short–circuit protection that helps protect the part and the system from a sudden high–current event, such as the output,  $V_{OUT}$ , being hard–shorted to ground.

Once active, the circuitry monitors the voltage difference between the  $V_{IN}$  pin and the  $V_{OUT}$  pin. When the difference is equal to the short–circuit protection threshold voltage, the MOSFET is turned off. The part remains off and is latched in the Fault state until EN is toggled or  $V_{CC}$  supply voltage is cycled, at which point the MOSFET will be turned on in a controlled fashion with the normal output turn–on delay and slew rate.

### **Over-Current Protection (Soft short)**

The NCP45790 device is equipped with an over–current protection (OCP) that helps protect the part and the system from a high current event which exceeds the expected operational current (e.g., a soft short).

In the event that the current from the  $V_{IN}$  pin to the  $V_{OUT}$  pin exceeds the OCP threshold for longer than the blanking time, the MOSFET will shut down and the PG pin is driven low. Like the short-circuit protection, the part remains latched in the Fault state until EN is toggled or  $V_{CC}$  supply voltage is cycled, at which point the MOSFET will be turned on in a controlled fashion with the normal output turn-on delay and slew rate.

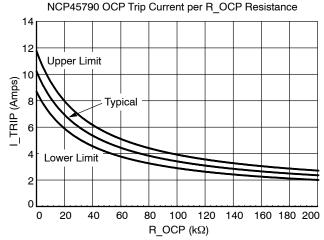

The over-current trip point is determined by the resistance between the OCP pin and ground. If no over-current protection is needed, then the OCP pin should be tied to GND; if the OCP protection is disabled in this way, the short-circuit protection will still remain active.

Figure 24. OCP Trip Current Setting

### Thermal Shutdown

The thermal shutdown of the NCP45790 device protects the part from internally or externally generated excessive temperatures. This circuitry is disabled when EN is not active to reduce standby current. When an over–temperature condition is detected, the MOSFET is turned off.

The part comes out of thermal shutdown when the junction temperature decreases to a safe operating temperature as dictated by the thermal hysteresis. Upon exiting a thermal shutdown state, and if EN remains active, the MOSFET will be turned on in a controlled fashion with the normal output turn—on delay and slew rate.

### **Under Voltage Lockout**

The under voltage lockout of the NCP45790 device turns the MOSFET off when the input voltage,  $V_{IN}$ , drops below the under voltage lockout threshold. This circuitry is disabled when EN is not active to reduce standby current.

If the  $V_{\rm IN}$  voltage rises above the under voltage lockout threshold, and EN remains active, the MOSFET will be turned on in a controlled fashion with the normal output turn–on delay and slew rate.

#### **Power Good**

The NCP45790 device has a power good output (PG) that can be used to indicate when the gate of the MOSFET is fully charged. The PG pin is an active–high, open–drain output that requires an external pull up resistor, RPG, greater than or equal to  $100~\text{k}\Omega$  to an external voltage source, VTERM, that is compatible with input levels of all devices connected to this pin (as shown in Figures 25). The power good output can be used as the enable signal for other active–high devices in the system (as shown in Figure 25). This allows for guaranteed by design power sequencing and reduces the number of enable signals needed from the system controller. If the power good feature is not used in the application, the PG pin should be tied to GND.

Figure 25. Guaranteed-by-Design Power Sequencing Example

### **Slew Rate Control**

The NCP45790 device is equipped with controlled output slew rate which provides soft start functionality. This limits the inrush current caused by capacitor charging and enables these devices to be used in hot swapping applications.

The slew rate can be decreased with an external capacitor added between the SR pin and ground. With an external capacitor present, the slew rate can be determined by the following equation:

Slew Rate =

$$\frac{K_{SR}}{C_{SR}}$$

[V/s] (eq. 1)

where  $K_{SR}$  is the specified slew rate control constant, found on page 3, and  $C_{SR}$  is the capacitor added between the SR pin and ground. Note that the slew rate of the device will always be the lower of the default slew rate and the adjusted slew rate. Therefore, if the  $C_{SR}$  is not large enough to decrease the slew rate more than the specified default value, the slew rate of the device will be the default value.

### **Capacitive Load**

The peak in-rush current associated with the initial charging of the application load capacitance needs to stay

below the specified  $I_{max}$ .  $C_L$  (capacitive load) should be less then  $C_{max}$  as defined by the following equation:

$$C_{\text{max}} = \frac{I_{\text{max}}}{SR_{\text{typ}}}$$

(eq. 2)

Where  $I_{max}$  is the maximum load current, and  $SR_{typ}$  is the typical default slew rate when no external load capacitor is added to the SR pin.

### **ecoSWITCH LAYOUT GUIDELINES**

### **Electrical Layout Considerations**

Correct physical PCB layout is important for proper low noise accurate operation of all ecoSWITCH products.

Power Planes: The ecoSWITCH is optimized for extremely low Ron resistance, however, improper PCB layout can substantially increase source to load series resistance by adding PCB board parasitic resistance. Solid connections to the VIN and VOUT pins of the ecoSWITCH to copper planes should be used to achieve low series resistance and good thermal dissipation. The ecoSWITCH requires ample heat dissipation for correct thermal lockout operation. The internal FET dissipates load condition dependent amounts of power in the milliseconds following the rising edge of enable, and providing good thermal conduction from the packaging to the board is critical. Direct coupling of VIN to VOUT should be avoided, as this will adversely affect slew rates. The figure below shows an example of correct power plane layout. The number and location of pins for specific ecoSWITCH products may vary. This demonstrates large planes for both VIN and VOUT, while avoiding capacitive coupling between the two planes.

ecoSwitch is trademark of Semiconductor Components Industries, LLC (SCILLC) or its subsidiaries in the United States and/or other countries.

| DOCUMENT NUMBER: | 98AON94406G     | Electronic versions are uncontrolled except when accessed directly from the Document Reposit<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |

|------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|

| DESCRIPTION:     | DFN14 4x4, 0.5P |                                                                                                                                                                                 | PAGE 1 OF 1 |  |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the rights of others.

onsemi, ONSEMI, and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. Onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product features, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi does not convey any license under any of its intellectual property rights nor the rights of others. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer pu

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT:

Email Requests to: orderlit@onsemi.com

onsemi Website: www.onsemi.com

TECHNICAL SUPPORT North American Technical Support: Voice Mail: 1 800-282-9855 Toll Free USA/Canada Phone: 011 421 33 790 2910

Europe, Middle East and Africa Technical Support:

Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative