# Power Factor Corrected Quasi-Resonant Primary Side Current-Mode Controller for LED Lighting with Line Step Dimming and Thermal Foldback

The NCL30185 is a controller targeting isolated and non-isolated "smart-dimmable" constant-current LED drivers. Designed to support flyback, buck-boost, and SEPIC topologies, its proprietary current-control algorithm provides near-unity power factor and tightly regulates a constant LED current from the primary side, thus eliminating the need for a secondary-side feedback circuitry or an optocoupler.

Housed in the SOIC8, the NCL30185 is specifically intended for very compact space–efficient designs. The device is highly integrated with a minimum number of external components. A robust suite of safety protections is built in to simplify the design. To ensure reliable operation at elevated temperatures, a user configurable current foldback circuit is also provided. In addition, it supports step dimming which allows light output reduction by toggling the main AC switch on and off.

Pin-to-pin compatible to the NCL30085, the NCL30185 provides the same benefits with in addition, an increased resolution of the digital current-control algorithm for a 75% reduction in the LED current quantization ripple.

### Features

- Quasi-resonant Peak Current-mode Control Operation

- Valley Lockout Optimizes Efficiency over the Line/Load Range

- Constant Current Control with Primary Side Feedback

- Tight LED Constant Current Regulation of ±2% Typical

- Power Factor Correction

- 3 Step Dimming (70/25/5%)

- Line Feedforward for Enhanced Regulation Accuracy

- Low Start-up Current (10 μA typ.)

- Wide V<sub>cc</sub> Range

- 300 mA / 500 mA Totem Pole Driver with 12 V Gate Clamp

- Robust Protection Features

- OVP on V<sub>CC</sub>

- Programmable Over Voltage / LED Open Circuit Protection

- ◆ Cycle-by-cycle Peak Current Limit

- Winding Short Circuit Protection

- Secondary Diode Short Protection

- Output Short Circuit Protection

- ◆ Current Sense Short Protection

- User Programmable NTC Based Thermal Foldback

### ON Semiconductor®

www.onsemi.com

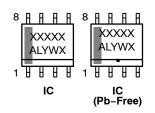

### MARKING DIAGRAM

L30185x = Specific Device Code

x = A, B

= Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

Pb-Free Package

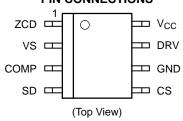

### PIN CONNECTIONS

### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 27 of this data sheet.

- ◆ Thermal Shutdown

- ullet  $V_{cc}$  Undervoltage Lockout

- ♦ Brown-out Protection

- Pb-Free, Halide-Free MSL1 Product

### **Typical Applications**

- Integral LED Bulbs and Tubes

- LED Light Engines

- LED Drivers/Power Supplies

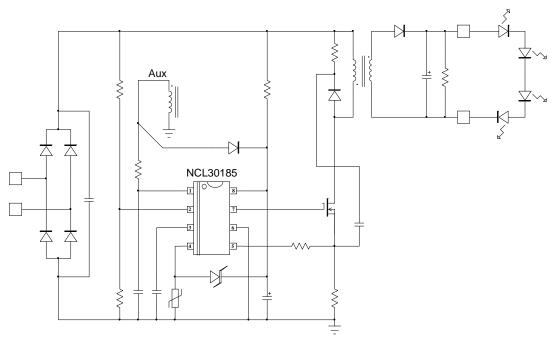

Figure 1. Typical Application Schematic in a Flyback Converter

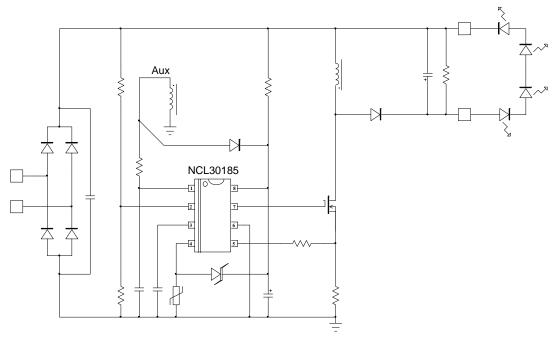

Figure 2. Typical Application Schematic in a Buck-Boost Converter

### **Table 1. PIN FUNCTION DESCRIPTION**

| Pin No | Pin Name        | Function                         | Pin Description                                                                                                                                                                                                                                            |

|--------|-----------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | ZCD             | Zero Crossing Detection          | Connected to the auxiliary winding, this pin detects the core reset event.                                                                                                                                                                                 |

| 2      | VS              | Input Voltage Sensing            | This pin observes the input voltage rail and protects the LED driver in case of too low mains conditions (brown–out).  This pin also observes the input voltage rail for:  - Power Factor Correction  - Valley lockout  - Step dimming                     |

| 3      | COMP            | Filtering Capacitor              | This pin receives a filtering capacitor for power factor correction. Typical values ranges from 1 – 4.70 $\mu\text{F}$                                                                                                                                     |

| 4      | SD              | Thermal Foldback and<br>Shutdown | Connecting an NTC to this pin allows the user to program thermal current fold-back threshold and slope. A Zener diode can also be used to pull–up the pin and stop the controller for adjustable OVP protection.                                           |

| 5      | CS              | Current Sense                    | This pin monitors the primary peak current.                                                                                                                                                                                                                |

| 6      | GND             | -                                | Controller ground pin.                                                                                                                                                                                                                                     |

| 7      | DRV             | Driver Output                    | The driver's output to an external MOSFET                                                                                                                                                                                                                  |

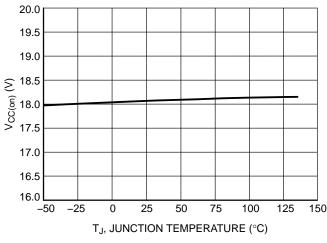

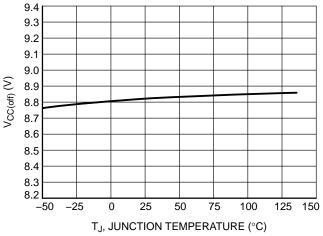

| 8      | V <sub>CC</sub> | IC Supply Pin                    | This pin is the positive supply of the IC. The circuit starts to operate when $V_{CC}$ exceeds 18 V and turns off when $V_{CC}$ goes below 8.8 V (typical values). After start–up, the operating range is 9.4 V up to 26 V ( $V_{CC(OVP)}$ minimum level). |

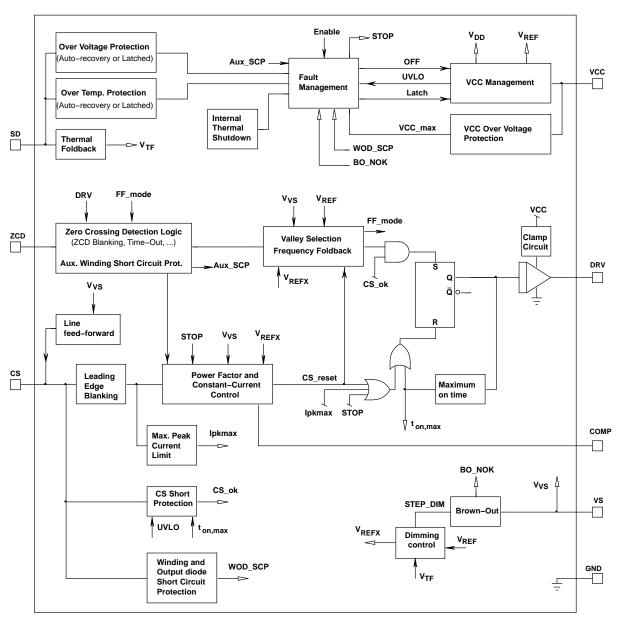

### **Internal Circuit Architecture**

Figure 3. Internal Circuit Architecture

**Table 2. MAXIMUM RATINGS TABLE**

| Symbol                                         | Rating                                                                                                                           | Value                                         | Unit    |

|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|---------|

| V <sub>CC(MAX)</sub>                           | Maximum Power Supply voltage, $V_{CC}$ pin, continuous voltage Maximum current for $V_{CC}$ pin                                  | -0.3 to 30<br>Internally limited              | V<br>mA |

| V <sub>DRV(MAX)</sub><br>I <sub>DRV(MAX)</sub> | Maximum driver pin voltage, DRV pin, continuous voltage  Maximum current for DRV pin                                             | -0.3, V <sub>DRV</sub> (Note 1)<br>-300, +500 | V<br>mA |

| V <sub>MAX</sub><br>I <sub>MAX</sub>           | Maximum voltage on low power pins (except DRV and $V_{CC}$ pins) Current range for low power pins (except DRV and $V_{CC}$ pins) | -0.3, 5.5 (Notes 2 and 5)<br>-2, +5           | V<br>mA |

| $R_{\theta J-A}$                               | Thermal Resistance Junction-to-Air                                                                                               | 180                                           | °C/W    |

| $T_{J(MAX)}$                                   | Maximum Junction Temperature                                                                                                     | 150                                           | °C      |

|                                                | Operating Temperature Range                                                                                                      | -40 to +125                                   | °C      |

|                                                | Storage Temperature Range                                                                                                        | -60 to +150                                   | °C      |

|                                                | ESD Capability, HBM model (Note 3)                                                                                               | 3.5                                           | kV      |

|                                                | ESD Capability, MM model (Note 3)                                                                                                | 250                                           | V       |

|                                                | ESD Capability, CDM model (Note 3)                                                                                               | 2                                             | kV      |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

- V<sub>DRV</sub> is the DRV clamp voltage V<sub>DRV(high)</sub> when V<sub>CC</sub> is higher than V<sub>DRV(high)</sub>. V<sub>DRV</sub> is V<sub>CC</sub> otherwise.

These levels are low enough not to exceed the maximum ratings of the internal ESD 5.5–V Zener diode. More positive and negative voltages

- can be applied if the pin current stays within the –2–mA / 5–mA range.

3. This device contains ESD protection and exceeds the following tests: Human Body Model 3500 V per JEDEC Standard JESD22–A114E, Machine Model Method 250 V per JEDEC Standard JESD22–A115B, Charged Device Model 2000 V per JEDEC Standard JESD22–C101E.

- This device contains latch-up protection and has been tested per JEDEC Standard JESD78D, Class I and exceeds ±100 mA

Recommended maximum V<sub>S</sub> voltage for optimal operation is 4 V. -0.3 V to +4.0 V is hence, the V<sub>S</sub> pin recommended range.

**Table 3. ELECTRICAL CHARACTERISTICS** (Unless otherwise noted: For typical values  $T_J = 25^{\circ}C$ ,  $V_{CC} = 12$  V,  $V_{ZCD} = 0$  V,  $V_{CS} = 0$  V,  $V_{SD} = 1.5$  V) For min/max values  $T_J = -40^{\circ}C$  to  $+125^{\circ}C$ ,  $V_{CC} = 12$  V)

| Description                                          | Test Condition                                      | Symbol                  | Min  | Тур  | Max  | Unit |

|------------------------------------------------------|-----------------------------------------------------|-------------------------|------|------|------|------|

| STARTUP AND SUPPLY CIRCUITS                          |                                                     | •                       |      |      |      | •    |

| Supply Voltage                                       |                                                     |                         |      |      |      | V    |

| Startup Threshold                                    | V <sub>CC</sub> rising                              | $V_{CC(on)}$            | 16.0 | 18.0 | 20.0 |      |

| Minimum Operating Voltage                            | V <sub>CC</sub> rising                              | $V_{CC(off)}$           | 8.2  | 8.8  | 9.4  |      |

| Hysteresis $V_{CC(on)} - V_{CC(off)}$                | V <sub>CC</sub> falling                             | V <sub>CC(HYS)</sub>    | 8    | _    | _    |      |

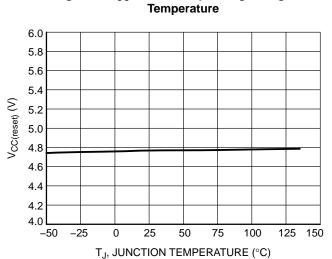

| Internal logic reset                                 |                                                     | V <sub>CC(reset)</sub>  | 4    | 5    | 6    |      |

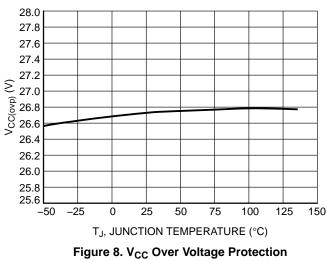

| V <sub>CC</sub> Over Voltage Protection Threshold    |                                                     | V <sub>CC(OVP)</sub>    | 25.5 | 26.8 | 28.5 | V    |

| V <sub>CC(off)</sub> noise filter                    |                                                     | t <sub>VCC(off)</sub>   | _    | 5    | -    | μS   |

| V <sub>CC(reset)</sub> noise filter                  |                                                     | t <sub>VCC(reset)</sub> | -    | 20   | -    |      |

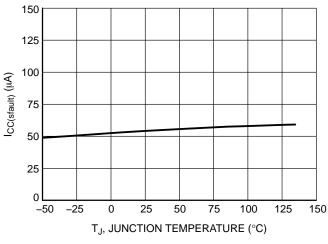

| Startup current                                      |                                                     | I <sub>CC(start)</sub>  | -    | 13   | 30   | μΑ   |

| Startup current in fault mode                        |                                                     | I <sub>CC(sFault)</sub> |      | 58   | 75   | μΑ   |

| Supply Current                                       |                                                     |                         |      |      |      | mA   |

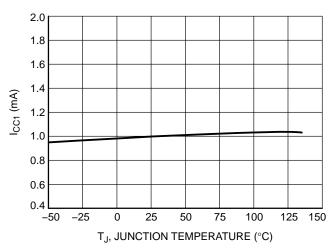

| Device Disabled/Fault                                | $V_{CC} > V_{CC(off)}$                              | I <sub>CC1</sub>        | 0.8  | 1.0  | 1.2  |      |

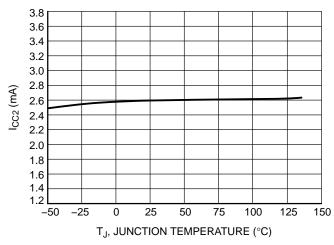

| Device Enabled/No output load on pin 7               | $F_{sw} = 65 \text{ kHz}$                           | I <sub>CC2</sub>        | _    | 2.5  | 4.0  |      |

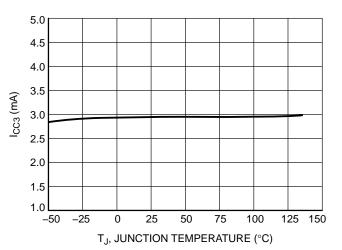

| Device Switching (F <sub>SW</sub> = 65 kHz)          | $C_{DRV} = 470 \text{ pF}, F_{sw} = 65 \text{ kHz}$ | I <sub>CC3</sub>        | -    | 3.0  | 4.5  |      |

| CURRENT SENSE                                        |                                                     |                         |      |      |      |      |

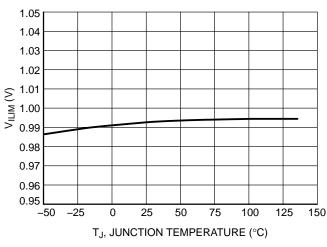

| Maximum Internal current limit                       |                                                     | V <sub>ILIM</sub>       | 0.95 | 1.00 | 1.05 | V    |

| Leading Edge Blanking Duration for V <sub>ILIM</sub> |                                                     | t <sub>LEB</sub>        | 240  | 300  | 360  | ns   |

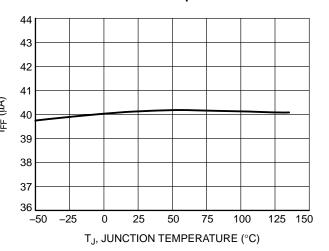

| Line feed-forward current                            | DRV high, V <sub>VS</sub> = 2 V                     | I <sub>FF</sub>         | 35   | 40   | 45   | μΑ   |

<sup>6.</sup> Guaranteed by Design

- A NTC is generally placed between the SD and GND pins. Parameters  $R_{TF(start)}$ ,  $R_{TF(stop)}$ ,  $R_{OTP(off)}$  and  $R_{OTP(on)}$  give the resistance the NTC must exhibit to respectively, enter thermal foldback, stop thermal foldback, trigger the OTP limit and allow the circuit recovery after

- 8. At startup, when  $V_{CC}$  reaches  $V_{CC(on)}$ , the controller blanks OTP for more than 250  $\mu s$  to avoid detecting an OTP fault by allowing the SD pin voltage to reach its nominal value if a filtering capacitor is connected to the SD pin.

$\textbf{Table 3. ELECTRICAL CHARACTERISTICS} \text{ (Unless otherwise noted: For typical values } T_J = 25^{\circ}\text{C}, \ V_{CC} = 12 \text{ V}, \ V_{ZCD} = 0 \text{ V}, \ V_{CS} = 0 \text{ V}, \ V_{SD} = 1.5 \text{ V}) \text{ For min/max values } T_J = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \ V_{CC} = 12 \text{ V})$

| Description                                                    | Test Condition                                                                                  | Symbol                               | Min    | Тур        | Max      | Unit |

|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--------------------------------------|--------|------------|----------|------|

| CURRENT SENSE                                                  |                                                                                                 |                                      |        |            |          |      |

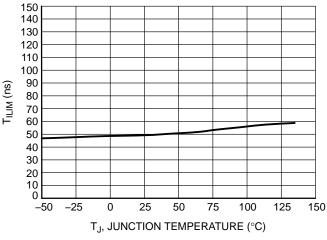

| Propagation delay from current detection to gate off–state     |                                                                                                 | t <sub>ILIM</sub>                    | _      | 100        | 150      | ns   |

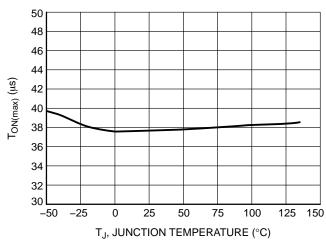

| Maximum on-time                                                |                                                                                                 | t <sub>on(MAX)</sub>                 | 26     | 36         | 46       | μS   |

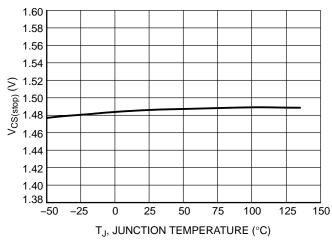

| Threshold for immediate fault protection activation            |                                                                                                 | V <sub>CS(stop)</sub>                | 1.35   | 1.50       | 1.65     | V    |

| Leading Edge Blanking Duration for V <sub>CS(stop)</sub>       |                                                                                                 | t <sub>BCS</sub>                     | -      | 150        | -        | ns   |

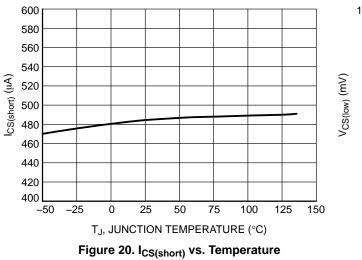

| Current source for CS to GND short detection                   |                                                                                                 | I <sub>CS(short)</sub>               | 400    | 500        | 600      | μΑ   |

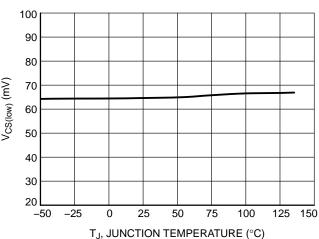

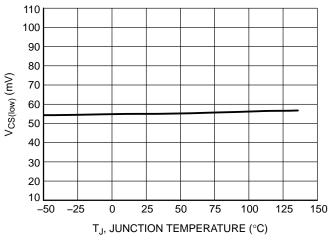

| Current sense threshold for CS to GND short detection          | V <sub>CS</sub> rising                                                                          | V <sub>CS(low)</sub>                 | 30     | 65         | 100      | mV   |

| GATE DRIVE                                                     |                                                                                                 |                                      |        |            |          |      |

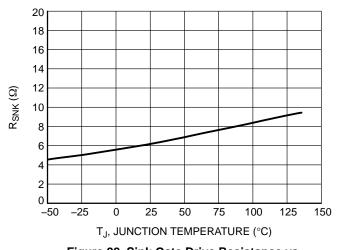

| Drive Resistance DRV Sink DRV Source                           |                                                                                                 | R <sub>SNK</sub><br>R <sub>SRC</sub> | -<br>- | 13<br>30   | -        | Ω    |

| Drive current capability DRV Sink (Note 6) DRV Source (Note 6) |                                                                                                 | I <sub>SNK</sub><br>I <sub>SRC</sub> |        | 500<br>300 |          | mA   |

| Rise Time (10% to 90%)                                         | C <sub>DRV</sub> = 470 pF                                                                       | t <sub>r</sub>                       | _      | 40         | -        | ns   |

| Fall Time (90% to 10%)                                         | C <sub>DRV</sub> = 470 pF                                                                       | t <sub>f</sub>                       | _      | 30         | -        | ns   |

| DRV Low Voltage                                                | $V_{CC} = V_{CC(off)} + 0.2 \text{ V}$ $C_{DRV} = 470 \text{ pF}, R_{DRV} = 33 \text{ k}\Omega$ | V <sub>DRV(low)</sub>                | 8      | _          | -        | V    |

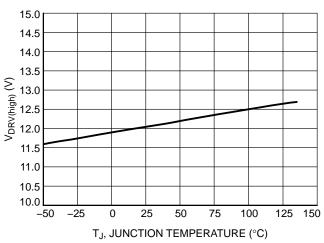

| DRV High Voltage                                               | $V_{CC} = V_{CC(MAX)}$ $C_{DRV} = 470 \text{ pF, } R_{DRV} = 33 \text{ k}\Omega$                | $V_{DRV(high)}$                      | 10     | 12         | 14       | V    |

| ZERO VOLTAGE DETECTION CIRCUIT                                 |                                                                                                 | •                                    |        |            | <u>I</u> |      |

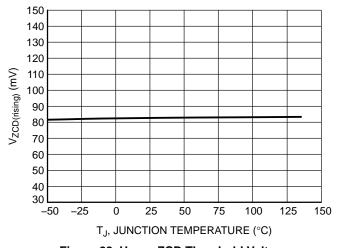

| Upper ZCD threshold voltage                                    | V <sub>ZCD</sub> rising                                                                         | V <sub>ZCD(rising)</sub>             | _      | 90         | 150      | mV   |

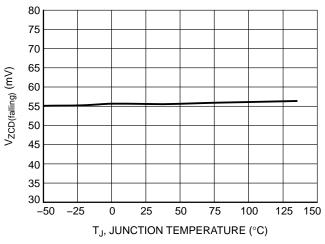

| Lower ZCD threshold voltage                                    | V <sub>ZCD</sub> falling                                                                        | V <sub>ZCD(falling)</sub>            | 35     | 55         | _        | mV   |

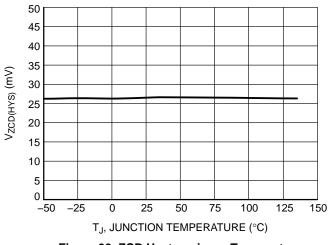

| ZCD hysteresis                                                 |                                                                                                 | V <sub>ZCD(HYS)</sub>                | 15     | -          | -        | mV   |

| Propagation Delay from valley detection to DRV high            | V <sub>ZCD</sub> falling                                                                        | T <sub>DEM</sub>                     | -      | 100        | 300      | ns   |

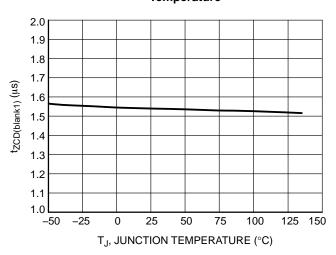

| Blanking delay after on-time                                   | V <sub>REFX</sub> > 30% V <sub>REF</sub>                                                        | T <sub>ZCD(blank1)</sub>             | 1.12   | 1.50       | 1.88     | μs   |

| Blanking Delay at light load                                   | V <sub>REFX</sub> < 25% V <sub>REF</sub>                                                        | T <sub>ZCD(blank2)</sub>             | 0.56   | 0.75       | 0.94     | μS   |

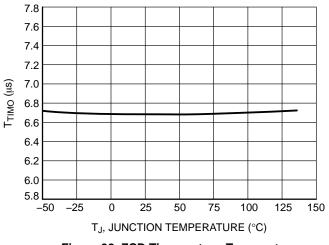

| Timeout after last DEMAG transition                            |                                                                                                 | T <sub>TIMO</sub>                    | 5.0    | 6.5        | 8.0      | μS   |

| Pulling-down resistor                                          | $V_{ZCD} = V_{ZCD(falling)}$                                                                    | R <sub>ZCD(PD)</sub>                 | -      | 200        | -        | kΩ   |

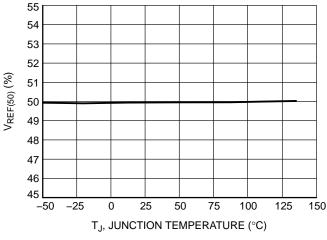

| CONSTANT CURRENT AND POWER FACTOR CON                          | TROL                                                                                            |                                      |        |            |          |      |

| Reference Voltage at T <sub>J</sub> = 25°C                     |                                                                                                 | $V_{REF}$                            | 245    | 250        | 255      | mV   |

| Reference Voltage T <sub>J</sub> = 25°C to 100°C               |                                                                                                 | $V_{REF}$                            | 242.5  | 250.0      | 257.5    | mV   |

| Reference Voltage $T_J = -40^{\circ}C$ to $125^{\circ}C$       |                                                                                                 | $V_{REF}$                            | 240    | 250        | 260      | mV   |

| Current sense lower threshold                                  | V <sub>CS</sub> falling                                                                         | V <sub>CS(low)</sub>                 | 20     | 50         | 100      | mV   |

| V <sub>control</sub> to current setpoint division ratio        |                                                                                                 | V <sub>ratio</sub>                   | _      | 4          | -        | _    |

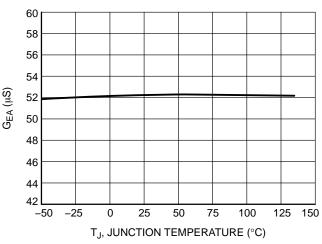

| Error amplifier gain                                           | V <sub>REFX</sub> =V <sub>REF</sub> (no dimming)<br>V <sub>REFX</sub> =25%* V <sub>REF</sub>    | G <sub>EA</sub>                      | 40     | 50<br>200  | 60       | μS   |

<sup>6.</sup> Guaranteed by Design

A NTC is generally placed between the SD and GND pins. Parameters R<sub>TF(start)</sub>, R<sub>TF(stop)</sub>, R<sub>OTP(off)</sub> and R<sub>OTP(on)</sub> give the resistance the NTC must exhibit to respectively, enter thermal foldback, stop thermal foldback, trigger the OTP limit and allow the circuit recovery after an OTP situation.

At startup, when V<sub>CC</sub> reaches V<sub>CC(on)</sub>, the controller blanks OTP for more than 250 μs to avoid detecting an OTP fault by allowing the SD pin voltage to reach its nominal value if a filtering capacitor is connected to the SD pin.

$\textbf{Table 3. ELECTRICAL CHARACTERISTICS} \text{ (Unless otherwise noted: For typical values } T_J = 25^{\circ}\text{C}, \ V_{CC} = 12 \text{ V}, \ V_{ZCD} = 0 \text{ V}, \ V_{CS} = 0 \text{ V}, \ V_{SD} = 1.5 \text{ V}) \text{ For min/max values } T_J = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \ V_{CC} = 12 \text{ V})$

| Description                                                                                                                                                                                                         | Test Condition                                                                               | Symbol                                                     | Min  | Тур                        | Max  | Unit |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------|------|----------------------------|------|------|

| CONSTANT CURRENT AND POWER FACTOR COM                                                                                                                                                                               | NTROL                                                                                        |                                                            |      |                            |      |      |

| Error amplifier current capability                                                                                                                                                                                  | V <sub>REFX</sub> =V <sub>REF</sub> (no dimming)<br>V <sub>REFX</sub> =25%* V <sub>REF</sub> | I <sub>EA</sub>                                            |      | ±60<br>±240                |      | μΑ   |

| COMP Pin Start-up Current Source                                                                                                                                                                                    | No dimming, COMP pin grounded                                                                | I <sub>EA_STUP</sub>                                       |      | 140                        |      | μΑ   |

| LINE FEED FORWARD                                                                                                                                                                                                   |                                                                                              |                                                            |      |                            |      |      |

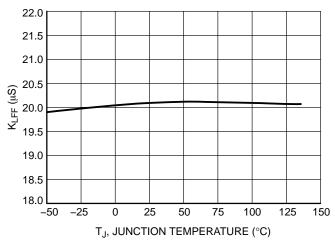

| V <sub>VS</sub> to I <sub>CS(offset)</sub> conversion ratio                                                                                                                                                         |                                                                                              | K <sub>LFF</sub>                                           | 18   | 20                         | 22   | μS   |

| Line feed-forward current on CS pin                                                                                                                                                                                 | DRV high, V <sub>VS</sub> = 2 V                                                              | I <sub>FF</sub>                                            | 35   | 40                         | 45   | μΑ   |

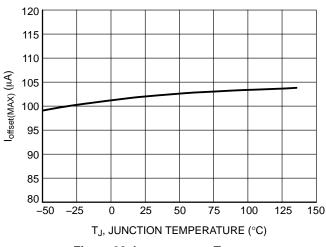

| Offset current maximum value                                                                                                                                                                                        | V <sub>VS</sub> > 5 V                                                                        | I <sub>offset(MAX)</sub>                                   | 80   | 100                        | 120  | μΑ   |

| VALLEY LOCKOUT SECTION                                                                                                                                                                                              |                                                                                              |                                                            |      |                            |      |      |

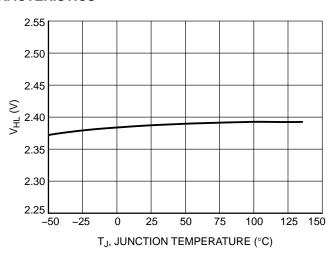

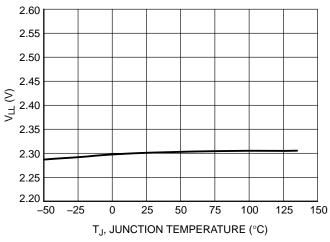

| Threshold for high– line range (HL) detection                                                                                                                                                                       | V <sub>VS</sub> rising                                                                       | $V_{HL}$                                                   | 2.28 | 2.40                       | 2.52 | ٧    |

| Threshold for low-line range (LL) detection                                                                                                                                                                         | V <sub>VS</sub> falling                                                                      | $V_{LL}$                                                   | 2.18 | 2.30                       | 2.42 | ٧    |

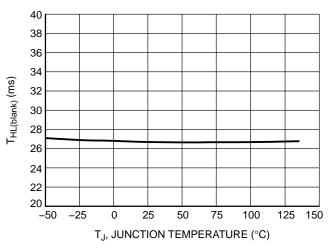

| Blanking time for line range detection                                                                                                                                                                              |                                                                                              | t <sub>HL(blank)</sub>                                     | 15   | 25                         | 35   | ms   |

| Valley Lockout  First step valley in High–Line.  Second step valley in High–Line.  Third step valley in High–Line.  First step valley in Low–Line.  Second step valley in Low–Line.  Third step valley in Low–Line. |                                                                                              | VHL100%<br>VHL70%<br>VHL25%<br>VLL100%<br>VLL70%<br>VLL25% |      | 2<br>3<br>6<br>1<br>2<br>5 |      |      |

| FREQUENCY FOLDBACK                                                                                                                                                                                                  |                                                                                              |                                                            |      |                            |      |      |

| Additional dead time                                                                                                                                                                                                | $V_{REFX} = 25\% * V_{REF}$                                                                  | t <sub>FF1LL</sub>                                         | 1.4  | 2.0                        | 2.6  | μS   |

| Additional dead time                                                                                                                                                                                                | V <sub>REFX</sub> = 5%*V <sub>REF</sub>                                                      | t <sub>FF2HL</sub>                                         | -    | 40                         | _    | μs   |

| FAULT PROTECTION                                                                                                                                                                                                    |                                                                                              |                                                            |      |                            |      |      |

| Thermal Shutdown (Note 6)                                                                                                                                                                                           | F <sub>SW</sub> = 65 kHz                                                                     | T <sub>SHDN</sub>                                          | 130  | 150                        | 170  | °C   |

| Thermal Shutdown Hysteresis                                                                                                                                                                                         |                                                                                              | T <sub>SHDN(HYS)</sub>                                     | -    | 50                         | _    | °C   |

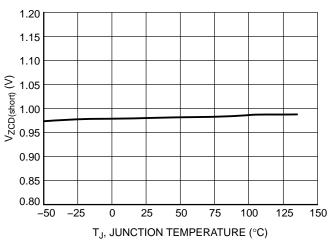

| Threshold voltage for output short circuit or aux. winding short circuit detection                                                                                                                                  |                                                                                              | V <sub>ZCD(short)</sub>                                    | 0.8  | 1.0                        | 1.2  | V    |

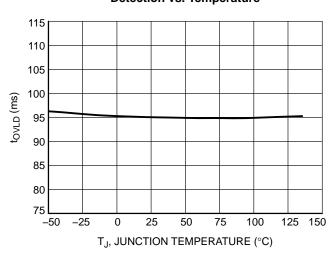

| Short circuit detection Timer                                                                                                                                                                                       | $V_{ZCD} < V_{ZCD(short)}$                                                                   | t <sub>OVLD</sub>                                          | 70   | 90                         | 110  | ms   |

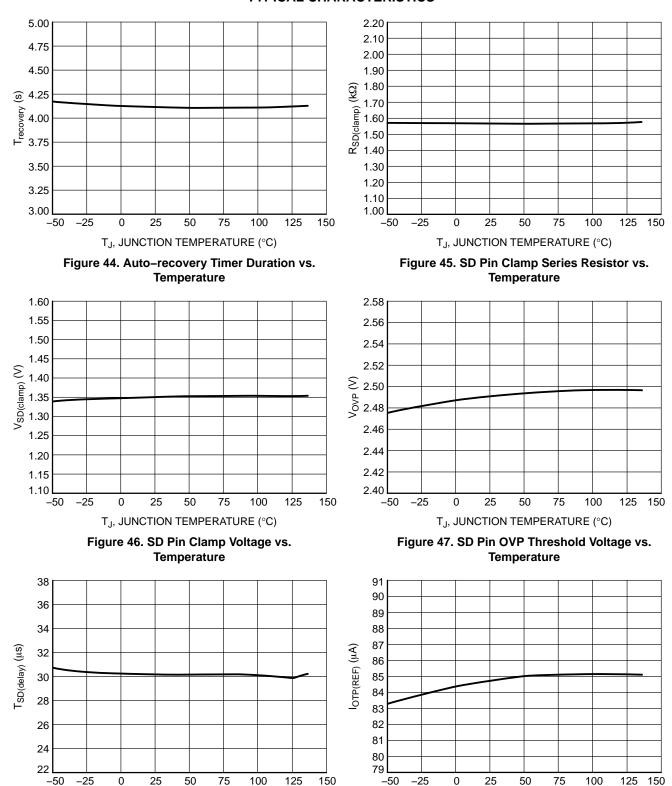

| Auto-recovery timer duration                                                                                                                                                                                        |                                                                                              | t <sub>recovery</sub>                                      | 3    | 4                          | 5    | s    |

| SD pin Clamp series resistor                                                                                                                                                                                        |                                                                                              | R <sub>SD(clamp)</sub>                                     |      | 1.6                        |      | kΩ   |

| Clamped voltage                                                                                                                                                                                                     | SD pin open                                                                                  | V <sub>SD(clamp)</sub>                                     | 1.13 | 1.35                       | 1.57 | V    |

| SD pin detection level for OVP                                                                                                                                                                                      | V <sub>SD</sub> rising                                                                       | V <sub>OVP</sub>                                           | 2.35 | 2.50                       | 2.65 | V    |

| Delay before OVP or OTP confirmation (OVP and OTP)                                                                                                                                                                  |                                                                                              | T <sub>SD(delay)</sub>                                     | 22.5 | 30.0                       | 37.5 | μS   |

| Reference current for direct connection of an NTC (Note 8)                                                                                                                                                          |                                                                                              | I <sub>OTP(REF)</sub>                                      | 80   | 85                         | 90   | μΑ   |

| Fault detection level for OTP (Note 7)                                                                                                                                                                              | V <sub>SD</sub> falling                                                                      | V <sub>OTP(off)</sub>                                      | 0.47 | 0.50                       | 0.53 | V    |

| SD pin level for operation recovery after an OTP detection                                                                                                                                                          | V <sub>SD</sub> rising                                                                       | V <sub>OTP(on)</sub>                                       | 0.66 | 0.70                       | 0.74 | V    |

<sup>6.</sup> Guaranteed by Design

<sup>7.</sup> A NTC is generally placed between the SD and GND pins. Parameters R<sub>TF(start)</sub>, R<sub>TF(stop)</sub>, R<sub>OTP(off)</sub> and R<sub>OTP(on)</sub> give the resistance the NTC must exhibit to respectively, enter thermal foldback, stop thermal foldback, trigger the OTP limit and allow the circuit recovery after an OTP situation.

<sup>8.</sup> At startup, when  $V_{CC}$  reaches  $V_{CC(on)}$ , the controller blanks OTP for more than 250  $\mu$ s to avoid detecting an OTP fault by allowing the SD pin voltage to reach its nominal value if a filtering capacitor is connected to the SD pin.

$\textbf{Table 3. ELECTRICAL CHARACTERISTICS} \text{ (Unless otherwise noted: For typical values } T_J = 25^{\circ}\text{C}, \ V_{CC} = 12 \text{ V}, \ V_{ZCD} = 0 \text{ V}, \ V_{CS} = 0 \text{ V}, \ V_{SD} = 1.5 \text{ V}) \text{ For min/max values } T_J = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \ V_{CC} = 12 \text{ V})$

| Description                                                                                          | Test Condition                                 | Symbol                  | Min  | Тур  | Max  | Unit |

|------------------------------------------------------------------------------------------------------|------------------------------------------------|-------------------------|------|------|------|------|

| FAULT PROTECTION                                                                                     |                                                | •                       |      |      |      |      |

| OTP blanking time when circuit starts operating (Note 8)                                             |                                                | t <sub>OTP(start)</sub> | 250  |      | 370  | μS   |

| SD pin voltage at which thermal fold–back starts (V <sub>REF</sub> is decreased)                     |                                                | V <sub>TF(start)</sub>  | 0.94 | 1.00 | 1.06 | V    |

| SD pin voltage at which thermal fold–back stops (V <sub>REF</sub> is clamped to V <sub>REF50</sub> ) |                                                | V <sub>TF(stop)</sub>   | 0.64 | 0.69 | 0.74 | V    |

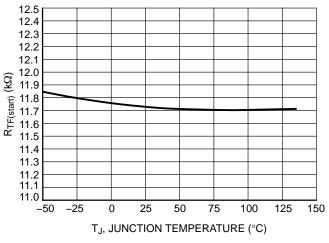

| V <sub>TF(start)</sub> over I <sub>OTP(REF)</sub> ratio (Note 7)                                     | $T_J = +25^{\circ}C \text{ to } +125^{\circ}C$ | R <sub>TF(start)</sub>  | 10.8 | 11.7 | 12.6 | kΩ   |

| V <sub>TF(stop)</sub> over I <sub>OTP(REF)</sub> ratio (Note 7)                                      | $T_J = +25^{\circ}C \text{ to } +125^{\circ}C$ | R <sub>TF(stop)</sub>   | 7.4  | 8.1  | 8.8  | kΩ   |

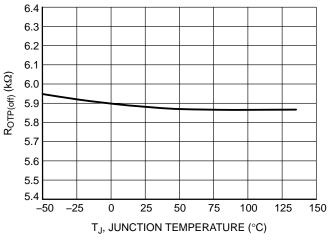

| V <sub>OTP(off)</sub> over I <sub>OTP(REF)</sub> ratio (Note 7)                                      | $T_J = +25^{\circ}C \text{ to } +125^{\circ}C$ | R <sub>OTP(off)</sub>   | 5.4  | 5.9  | 6.4  | kΩ   |

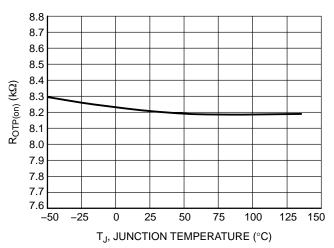

| V <sub>OTP(on)</sub> over I <sub>OTP(REF)</sub> ratio (Note 7)                                       | $T_J = +25^{\circ}C \text{ to } +125^{\circ}C$ | R <sub>OTP(on)</sub>    | 7.5  | 8.1  | 8.7  | kΩ   |

| V <sub>REFX</sub> @ V <sub>SD</sub> = 600 mV (percent of V <sub>REF</sub> )                          | SD pin falling, no OTP detection               | V <sub>REF(50)</sub>    | 40   | 50   | 60   | %    |

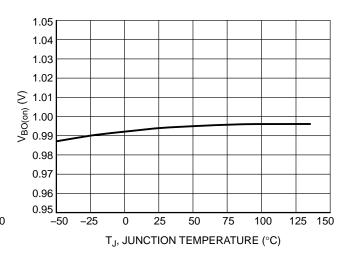

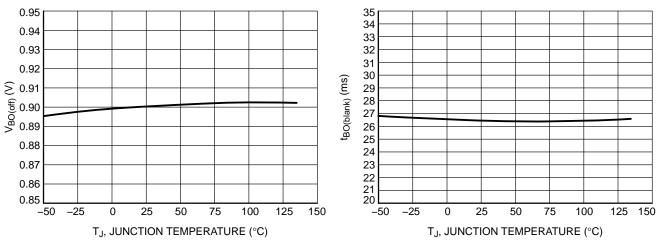

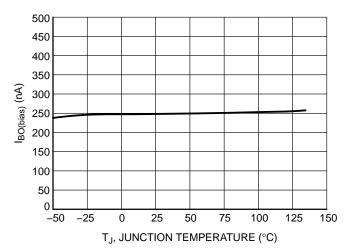

| BROWN-OUT                                                                                            | •                                              |                         |      |      |      |      |

| Brown-Out ON level (IC start pulsing)                                                                | V <sub>S</sub> rising                          | V <sub>BO(on)</sub>     | 0.95 | 1.00 | 1.05 | V    |

| Brown-Out OFF level (IC shuts down)                                                                  | V <sub>S</sub> falling                         | V <sub>BO(off)</sub>    | 0.85 | 0.90 | 0.95 | V    |

| BO comparators delay                                                                                 |                                                | t <sub>BO(delay)</sub>  |      | 30   |      | μs   |

| Brown-Out blanking time                                                                              |                                                | t <sub>BO(blank)</sub>  | 15   | 25   | 35   | ms   |

| V <sub>S</sub> pin Pulling-down Current                                                              | $V_S = V_{BO(on)}$                             | I <sub>BO(bias)</sub>   | 50   | 250  | 450  | nA   |

| Step Dimming Reset Time                                                                              | V <sub>S</sub> < V <sub>BO(off)</sub>          | t <sub>step-reset</sub> | 2.4  | 3.2  | 4.0  | s    |

<sup>6.</sup> Guaranteed by Design

A NTC is generally placed between the SD and GND pins. Parameters R<sub>TF(start)</sub>, R<sub>TF(stop)</sub>, R<sub>OTP(off)</sub> and R<sub>OTP(on)</sub> give the resistance the NTC must exhibit to respectively, enter thermal foldback, stop thermal foldback, trigger the OTP limit and allow the circuit recovery after an OTP situation.

At startup, when V<sub>CC</sub> reaches V<sub>CC(on)</sub>, the controller blanks OTP for more than 250 μs to avoid detecting an OTP fault by allowing the SD pin voltage to reach its nominal value if a filtering capacitor is connected to the SD pin.

Figure 4. V<sub>CC</sub> Start-up Threshold vs.

Temperature

Figure 5. V<sub>CC</sub> Minimum Operating Voltage vs.

Temperature

11.5 11.0 10.5 Vcc(hys) (V) 10.0 9.5 9.0 8.5 8.0 -50 -25 25 50 75 100 125 150 T<sub>J</sub>, JUNCTION TEMPERATURE (°C)

Figure 6. Hysteresis (V<sub>CC(on)</sub> – V<sub>CC(off)</sub>) vs. Temperature

Figure 7. V<sub>CC(reset)</sub> vs. Temperature

40 35 30 Icc(start) (µA) 25 20 15 10 5 0 -25 25 100 125 150 -50 50 75 T<sub>J</sub>, JUNCTION TEMPERATURE (°C)

Threshold vs. Temperature

Figure 9. Start-up Current vs. Temperature

Figure 10. Start-up Current in Fault Mode vs. **Temperature**

Figure 11. I<sub>CC1</sub> vs. Temperature

Figure 12.  $I_{CC2}$  vs. Temperature

Figure 13. I<sub>CC3</sub> vs. Temperature

400 380 360 340 320 300 280 260 240 220 200 25 125 150 -50 -2550 75 100 T<sub>J</sub>, JUNCTION TEMPERATURE (°C)

Figure 14. Maximum Internal Current Limit vs. Temperature

Figure 15. Leading Edge Blanking vs. Temperature

Figure 16. Current Limit Propagation Delay vs. Temperature

Figure 17. Maximum On-time vs. Temperature

Figure 18. V<sub>CS(stop)</sub> vs. Temperature

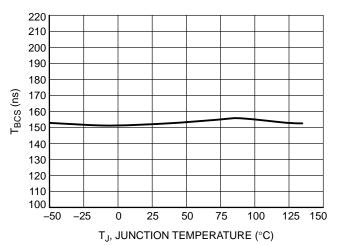

Figure 19. Leading Edge Blanking Duration for  $V_{CS(stop)}$  vs. Temperature

Figure 21. V<sub>CS(low)</sub>, V<sub>CS</sub> Rising vs. Temperature

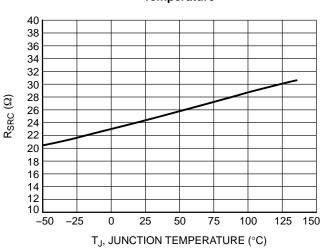

Figure 22. Sink Gate Drive Resistance vs. Temperature

Figure 23. Source Gate Drive Resistance vs. Temperature

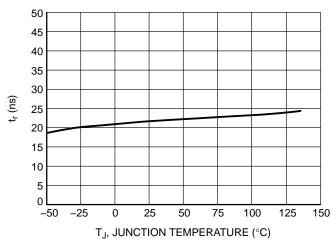

Figure 24. Gate Drive Rise Time vs.

Temperature

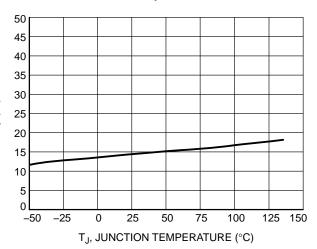

Figure 25. Gate Drive Fall Time (C<sub>DRV</sub> = 470 pF) vs. Temperature

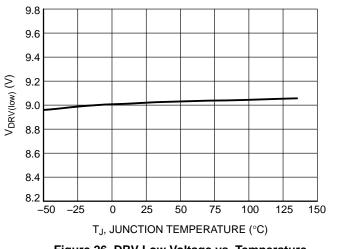

Figure 26. DRV Low Voltage vs. Temperature

Figure 27. DRV High Voltage vs. Temperature

Figure 28. Upper ZCD Threshold Voltage vs. Temperature

Figure 29. Lower ZCD Threshold vs. Temperature

Figure 30. ZCD Hysteresis vs. Temperature

Figure 31. ZCD Blanking Delay vs. Temperature

### **TYPICAL CHARACTERISTICS**

256

255 254 253 252 VREF (mV) 251 250 249 248 247 246 245 244 50 125 150 -50 -25 25 75 100 T<sub>J</sub>, JUNCTION TEMPERATURE (°C)

Figure 32. ZCD Time-out vs. Temperature

Figure 33. Reference Voltage vs. Temperature

Figure 34. Current Sense Lower Threshold (V<sub>CS</sub> Falling) vs. Temperature

Figure 35. Error Amplifier Trans-conductance

Gain vs. Temperature

Figure 36. Feedforward V<sub>VS</sub> to I<sub>CS(offset)</sub> Conversion Ratio vs. Temperature

Figure 37. Line Feedforward Current on CS Pin (@ V<sub>VS</sub> = 2 V) vs. Temperature

Figure 38. I<sub>offset(MAX)</sub> vs. Temperature

Figure 39. Threshold for High-line Range Detection vs. Temperature

Figure 40. Threshold for Low-line Range Detection vs. Temperature

Figure 41. Blanking Time for Low-line Range Detection vs. Temperature

Figure 42. Threshold Voltage for Output Short Circuit Detection vs. Temperature

Figure 43. Short Circuit Detection Timer vs.

Temperature

$T_J$ , JUNCTION TEMPERATURE (°C) Figure 48.  $T_{SD(delay)}$  vs. Temperature

T<sub>J</sub>, JUNCTION TEMPERATURE (°C)

Figure 49. I<sub>OTP(REF)</sub> vs. Temperature

8.8 8.7 8.6 8.5 8.4  $R_{TF(stop)}$  (k $\Omega$ ) 8.3 8.2 8.1 8.0 7.9 7.8 7.7 7.6 -25 125 150 -50 25 50 75 100 T<sub>J</sub>, JUNCTION TEMPERATURE (°C)

Figure 50. R<sub>TF(start)</sub> vs. Temperature

Figure 51. R<sub>TF(stop)</sub> vs. Temperature

Figure 52. R<sub>OTP(off)</sub> vs. Temperature

Figure 53. R<sub>OTP(on)</sub> vs. Temperature

Figure 54. Ratio  $V_{REF(50)}$  over  $V_{REF}$  vs. Temperature

Figure 55. Brown-out ON Level vs.

Temperature

Figure 56. Brown-out OFF Level vs. Temperature

Figure 57. Brown-out Blanking Time vs. Temperature

Figure 58. V<sub>S</sub> Pin Pulling-down Current vs. Temperature

### **Application Information**

The NCL30185 is a driver for power–factor corrected flyback and non–isolated buck–boost and SEPIC converters. It implements a current–mode, quasi–resonant architecture including valley lockout and frequency fold–back capabilities for maintaining high–efficiency performance over a wide load range. A proprietary circuitry ensures both accurate regulation of the output current (without the need for a secondary–side feedback) and near–unity power factor correction. The circuit contains a suite of powerful protections to ensure a robust LED driver design without the need for extra external components or overdesign.

- Quasi-Resonance Current-Mode Operation: implementing quasi-resonance operation in peak current-mode control, the NCL30185 optimizes the efficiency by turning on the MOSFET when its drain-source voltage is minimal (valley). In light-load conditions, the circuit changes valleys to reduce the switching losses. For stable operation, the valley at which the MOSFET switches on remains locked until the input voltage or the output current set-point significantly changes.

- Primary–Side Constant–Current Control with Power Factor Correction: a proprietary circuitry allows the LED driver to achieve both near–unity power factor correction and accurate regulation of the output current without requiring any secondary–side feedback (no optocoupler needed). A power factor as high as 0.99 and an output current deviation below ±2% are typically obtained.

- Step dimming: The step dimming function decreases

the output current from 100% to 5% of its nominal

value in 3 discrete steps. Whenever a brown—out is

detected, the output current is decreased by reducing

the reference voltage V<sub>REF</sub>. The step—dimming function

is reset if the V<sub>S</sub> pin remains below the lower

brown—out threshold (V<sub>BO(off)</sub>) for more than 3 s

typically.

- Main protection features:

- Over Temperature Thermal Fold-back / Shutdown/ Over Voltage Protection: the NCL30185 features a gradual current foldback to protect the driver from excessive temperature down to 50% of the programmed current. This represents a power reduction of the LED by more than 50%. If the temperature continues to rise after this point to a

- second level, the controller stops operating. This mode would only be expected to be reached if there is a severe fault. The first and second temperature thresholds depend on the value of the NTC connected to the SD pin. Note, the SD pin can also be used to shutdown the device by pulling this pin below the  $V_{OTP(off)}$  min level. A Zener diode can also be used to pull—up the pin and stop the controller for adjustable OVP protection. Both protections are latching—off (A version) or auto—recovery (the circuit can recover operation after 4–s delay has elapsed B version).

- Cycle-by-cycle peak current limit: when the current sense voltage exceeds the internal threshold V<sub>ILIM</sub>, the MOSFET is immediately turned off for that switch cycle.

- Winding or Output Diode Short-Circuit Protection: an additional comparator senses the CS signal and stops the controller if it exceeds 150% x V<sub>ILIM</sub> for 4 consecutive cycles. This feature can protect the converter if a winding is shorted or if the output diode is shorted or simply if the transformer saturates. This protection is latching-off (A version) or auto-recovery (B version).

- Output Short-circuit protection: if the ZCD pin voltage remains low for a 90-ms time interval, the controller detects that the output or the ZCD pin is grounded and hence, stops operation. This protection is latching-off (A version) or auto-recovery (B version).

- Open LED protection: if the V<sub>CC</sub> pin voltage exceeds the OVP threshold, the controller shuts down and waits 4 seconds before restarting switching operation.

- Floating or Short Pin Detection: the circuit can detect most of these situations which helps pass safety tests.

### **Power Factor and Constant Current Control**

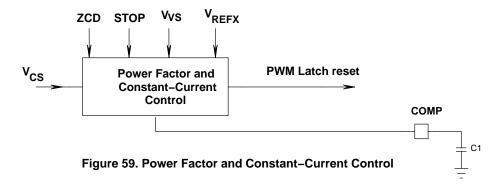

The NCL30185 embeds an analog/digital block to control the power factor and regulate the output current by monitoring the ZCD,  $V_S$  and CS pin voltages (signals ZCD,  $V_{VS}$  and  $V_{CS}$  of Figure 59). This circuitry generates the current setpoint ( $V_{CONTROL}/4$ ) and compares it to the current sense signal ( $V_{CS}$ ) to dictate the MOSFET turning off event when  $V_{CS}$  exceeds  $V_{CONTROL}/4$ .

As illustrated in Figure 59, the  $V_S$  pin provides the sinusoidal reference necessary for shaping the input current. The obtained current reference is further modulated so that when averaged over a half-line period, it is equal to the output current reference ( $V_{REFX}$ ). This averaging process is made by an internal Operational Trans-conductance Amplifier (OTA) and the capacitor connected to the COMP pin (C1 of Figure 59). Typical COMP capacitance is 1  $\mu$ F and should not be less than 470 nF to ensure stability. The COMP ripple does not affect the power factor performance as the circuit digitally eliminates it when generating the current setpoint.

If the  $V_S$  pin properly conveys the sinusoidal shape, power factor will be close to unity and the Total Harmonic Distortion (THD) will be low. In any case, the output current will be well regulated following the equation below:

$$I_{out} = \frac{V_{REFX}}{2N_{PS}R_{sense}}$$

(eq. 1)

Where:

- $N_{PS}$  is the secondary to primary transformer turns  $N_{PS} = N_S/N_P$

- R<sub>sense</sub> is the current sense resistor (see Figure 1).

- V<sub>REFX</sub> is the output current internal reference.

V<sub>REFX</sub> = V<sub>REF</sub> (250 mV typically) at full load.

The output current reference ( $V_{REFX}$ ) is 250 mV typically ( $V_{REF}$ ). In the event that step dimming is engaged,  $V_{REFX}$  takes a lower value based on the step–dimming level (see "step dimming" section) or if the temperature is high enough to activate the thermal fold–back (see "protections" section).

If a major fault is detected, the circuit enters the latched-off or auto-recovery mode and the COMP pin is grounded (except in an UVLO condition). This ensures a clean start-up when the circuit resumes operation.

### Start-up Sequence

Generally an LED lamp is expected to emit light in < 1 sec and typically within 300 ms. The start–up phase consists of the time to charge the  $V_{CC}$  capacitor, initiate startup and begin switching and the time to charge the output capacitor until sufficient current flows into the LED string.

To speed—up this phase, the following defines the start—up sequence:

- The COMP pin is grounded when the circuit is off. The average COMP voltage needs to exceed the V<sub>S</sub> pin peak value to have the LED current properly regulated (whatever the current target is). To speed—up the COMP capacitance charge and shorten the start—up phase, an internal 80—μA current source adds to the OTA sourced current (60 μA max typically) to charge up the COMP capacitance. The 80—μA current source remains on until the OTA starts to sink current as a result of the COMP pin voltage sufficient rise. At that moment, the COMP pin being near its steady—state value, it is only driven by the OTA.

- Whatever the step–dimming state is, the output current reference is set maximum ( $V_{REFX} = V_{REF}$ ) until the ZCD pin voltage reaches the 1–V  $V_{ZCD(short)}$  threshold. This prevents the circuit from detecting an output short (AUX\_SCP protection trips if the ZCD pin voltage does not exceed 1–V  $V_{ZCD(short)}$  threshold within a 90–ms delay) just because dimming would make the output voltage charge up slowly. If the system cannot start–up in one  $V_{CC}$  cycle, the AUX\_SCP 90–ms blanking time is not reset and  $V_{REFX}$  remains maximum for all the necessary  $V_{CC}$  cycles until the ZCD pin voltage reaches the 1–V  $V_{ZCD(short)}$  threshold.

- If V<sub>CC</sub> drops below the V<sub>CC(off)</sub> threshold because the circuit fails to start—up properly on the first attempt, a new try takes place as soon as V<sub>CC</sub> is recharged to V<sub>CC(on)</sub>. The COMP voltage is not reset at that moment. Instead, the new attempt starts with the COMP level obtained at the end of the previous operating phase.

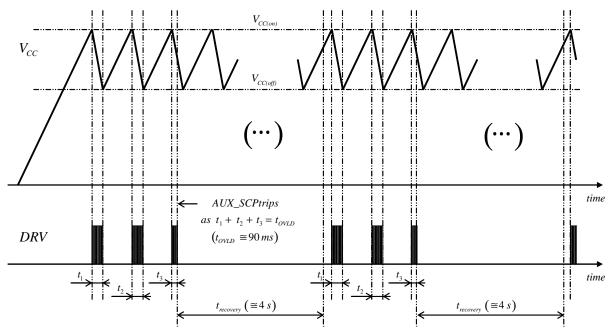

- If the load is shorted, the circuit will operate in hiccup mode with V<sub>CC</sub> oscillating between V<sub>CC(off)</sub> and V<sub>CC(on)</sub> until the AUX\_SCP protection trips (AUX\_SCP is triggered if the ZCD pin voltage does not exceed 1 V within a 90-ms operation period of time thus indicating a short to ground of the ZCD pin or an excessive load preventing the output voltage from rising). The NCL30185A latches off in this case. With the B version, the AUX\_SCP protection forces the 4-s auto-recovery delay to reduce the operation duty-ratio. Figure 60 illustrates a start-up sequence with the output shorted to ground, in this second case.

Figure 60. Start-up Sequence in a Load Short-circuit Situation (auto-recovery version)

### **Step Dimming**

The step dimming function decreases the output current from 100% to 5% of its nominal value in 3 discrete steps. The table below shows the different steps value and the corresponding reference voltage value. Each time a brown—out is detected, the output current is decreased by decreasing the reference voltage  $V_{REF}$ .

A counter is incremented by the BO\_NOK (brown-out not OK) signal and selects one of the four corresponding reference thresholds: V<sub>REF</sub>, V<sub>REF70</sub>, V<sub>REF25</sub>, V<sub>REF5</sub>. After counting up to 4, the counter is reset.

**Table 4. DIMMING STEPS**

| Dimming Step | lout |

|--------------|------|

| ON           | 100% |

| 1            | 70%  |

| 2            | 25%  |

| 3            | 5%   |

### Note:

The step dimming state is memorized until  $V_{CC}$  crosses  $V_{CC(reset)}$  or  $V_{VS}$  is below  $V_{BO(off)}$  for 3 s (typical).

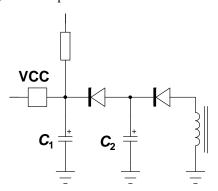

The circuit consumption is optimized (in particular, it equals  $I_{CC(fault)}$  when  $V_{CC}$  is lower than  $V_{CC(off)}$ ) so that the  $V_{CC}$  voltage does not drop too fast for the step dimming brown—out event.

The power supply designer should use a split  $V_{CC}$  circuit as shown in Figure 61 where a small capacitor  $C_1$  is used for a fast start-up while a larger  $C_2$  capacitance provides the necessary storage capability for step dimming. During step dimming, at startup, the controller generates the first DRV pulses after 1 time-out pulse even if a higher valley number

is selected by V<sub>REFX</sub>. This avoids long startup time while dimming at low output current value.

Figure 61. Split V<sub>CC</sub> Supply

The step-dimming function is reset if the  $V_S$  pin is maintained below the  $V_{BO(off)}$  brown-out threshold for the  $T_{step\_reset}$  time.  $T_{step\_reset}$  is 3 s typically. In other words, any brown-out event that is longer than  $T_{step\_reset}$ , leads the controller to re-start at 100% current setting.

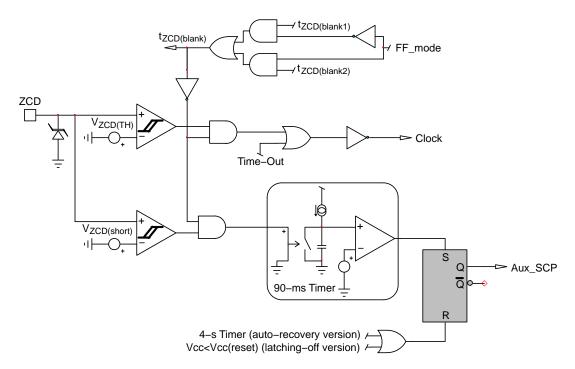

### **Zero Crossing Detection Block**

The ZCD pin detects when the drain-source voltage of the power MOSFET reaches a valley by crossing below the 55-mV internal threshold. At startup or in case of extremely damped free oscillations, the ZCD comparator may not be able to detect the valleys. To avoid such a situation, the NCL30185 features a time-out circuit that generates pulses if the voltage on ZCD pin stays below the 55-mV threshold for 6.5 µs. The time-out also acts as a substitute clock for the valley detection and simulates a missing valley in case the free oscillations are too damped.

Figure 62. Zero Current Detection Block

If the ZCD pin or the auxiliary winding happen to be shorted, the time–out function would normally make the controller keep switching and hence lead to improper LED current value. The "AUX\_SCP" protection prevents such a stressful operation: a secondary timer starts counting that is only reset when the ZCD voltage exceeds the  $V_{ZCD(short)}$  threshold (1 V typically). If this timer reaches 90 ms (no ZCD voltage pulse having exceeded  $V_{ZCD(short)}$  for this time period), the controller detects a fault and stops operation for 4 seconds (B version) or latches off (A version).

The "clock" shown in Figure 62 is used by the "valley selection frequency foldback" circuitry of the block diagram (Figure 3), to generate the next DRV pulse (if no fault prevents it):

Immediately when the clock occurs in QR mode (heavy load)

• After the appropriate number of "clock" pulses in thermal foldback or step-dimming mode (see Table 5)

For an optimal operation, the maximum ZCD level should be maintained below 5 V to stay safely below the built in clamping voltage of the pin.

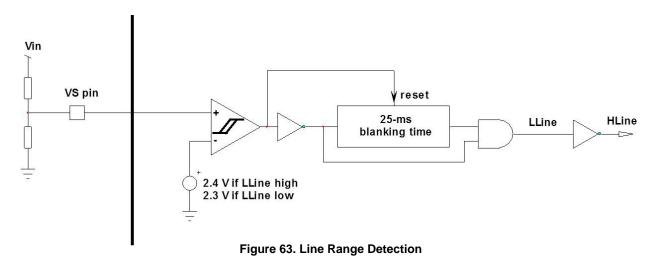

### **Line Range Detection and Valley Lockout**

As sketched in Figure 63, this circuit detects the low–line range if the  $V_S$  pin remains below the  $V_{LL}$  threshold (2.3 V typical) for more than the 25–ms blanking time. High–line is detected as soon as the  $V_S$  pin voltage exceeds  $V_{HL}$  (2.4 V typical). These levels roughly correspond to 184–V rms and 192–V rms line voltages if the external resistors divider applied to the  $V_S$  pin is designed to provide a 1–V peak value at 80 V rms.

Quasi-square wave resonant systems have a wide switching frequency excursion. The switching frequency increases when the output load decreases or when the input voltage increases. The switching frequency of such systems must be limited.

**Table 5. VALLEY SELECTION**

| Load | Low Line           | High Line          |

|------|--------------------|--------------------|

| 100% | Valley 1 (QR)      | Valley 2           |

| 70%  | Valley 2           | Valley 3           |

| 25%  | Valley 5           | Valley 6           |

| 5%   | Frequency foldback | Frequency foldback |

A decimal counter counts the valley detected by the ZCD logic block. In the low-line range, conduction losses are generally dominant. Hence, only a short dead-time is necessary to reach the MOSFET valley. In high-line conditions, switching losses generally are the most critical. It is thus efficient to skip a valley to lower the switching frequency. Hence, when the current is not dimmed, the

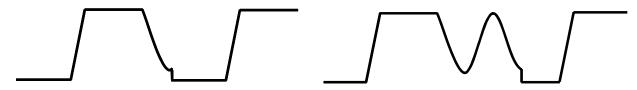

NCL30185 optimizes the efficiency over the line range by turning on the MOSFET at the first valley in low-line conditions and at the second valley in the high-line case. This is illustrated in Figure 64 that sketches the MOSFET Drain-source voltage in both cases. In dimming cases, more valleys can be skipped. Table 5 summarizes the valley selection as a function of the output current.

Figure 64. Full-load Operation – Quasi-resonant Mode in low line (left), turn on at valley 2 when in high line (right)

### Frequency Foldback (FF)

The valley lockout function can make the circuit skip operation until the 5<sup>th</sup> valley (6<sup>th</sup> valley) is detected in low–line case (high–line case) as obtained at 25% of the nominal load. At the lowest step (5% of the nominal load), the switching frequency is decreased by further adding dead–time after the 5<sup>th</sup> valley (low line) or the 6<sup>th</sup> valley (high line) is detected. This extra dead–time is typically  $40~\mu s$ .

### **Line Feedforward**

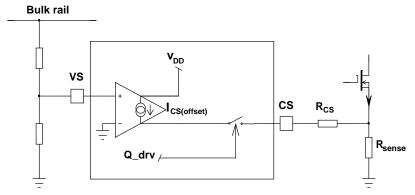

As illustrated by Figure 65, the input voltage is sensed by the  $V_S$  pin and converted into a current. By adding an external resistor in series between the sense resistor and the CS pin, a voltage offset proportional to the input voltage is added to the CS signal for the MOSFET on–time to compensate for the  $I_{peak}$  increase due to the propagation delay.

Figure 65. Line Feed-Forward Schematic

In Figure 65, Q\_drv designates the output of the PWM latch which is high for the on-time and low otherwise.

### **Protections**

The circuit incorporates a large variety of protections to make the LED driver very rugged. Among them, we can list:

### **Output Short Circuit Situation**

An overload fault is detected if the ZCD pin voltage remains below  $V_{ZCD(short)}$  for 90 ms. In such a situation, the circuit stops generating pulses until the 4–s delay auto–recovery time has elapsed (B version) or latches off (A version).

### Winding or Output Diode Short Circuit Protection

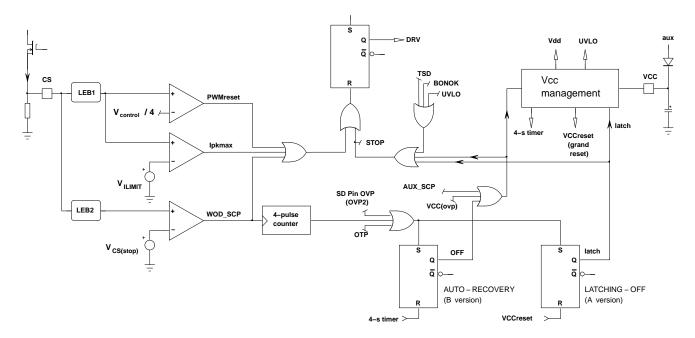

If a transformer winding happens to be shorted, the primary inductance will collapse leading the current to ramp up in a very abrupt manner. The V<sub>ILIM</sub> comparator (current limitation threshold) will trip to open the MOSFET and eventually stop the current rise. However, because of the

abnormally steep slope of the current, internal propagation delays and the MOSFET turn–off time will make possible the current rise up to 50% or more of the nominal maximum value set by  $V_{ILIM}$ . As illustrated in Figure 66, the circuit uses this current overshoot to detect a winding short circuit. The leading edge blanking (LEB) time for short circuit protection (LEB2) is significantly faster than the LEB time for cycle–by–cycle protection (LEB1). Practically, if four consecutive switching periods lead the CS pin voltage to exceed ( $V_{CS(stop)}$ =150% \* $V_{ILIM}$ ), the controller enters auto–recovery mode in version B (4–s operation interruption between active bursts) and latches off in version A. Similarly, this function can also protect the power supply if the output diode is shorted or if the transformer simply saturates.

Figure 66. Winding Short Circuit Protection, Max. Peak Current Limit Circuits

### **V<sub>CC</sub>** Over Voltage Protection

The circuit stops generating pulses if  $V_{CC}$  exceeds  $V_{CC(OVP)}$  and enters auto-recovery mode. This feature protects the circuit if the output LED string happens to open or is disconnected.

### **Programmable Over Voltage Protection (OVP2)**

Connect a Zener diode between  $V_{CC}$  and the SD pin to set a programmable  $V_{CC}$  OVP ( $D_Z$  of Figure 67). The triggering level is ( $V_Z+V_{OVP}$ ) where  $V_{OVP}$  is the 2.5–V internal threshold. If this protection trips, the NCL30185A latches off while the NCL30185B enters the auto–recovery mode.

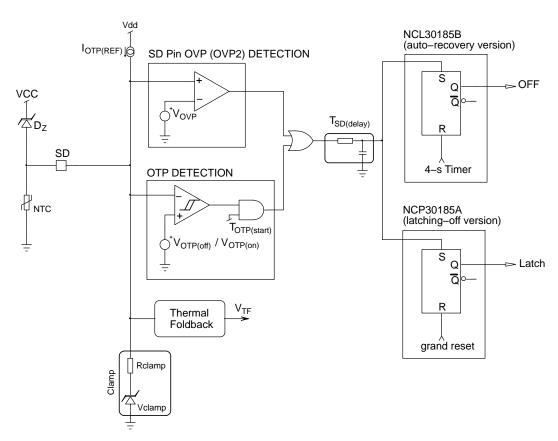

Figure 67. Thermal Foldback and OVP/OTP Circuitry

The SD pin is clamped to about 1.35 V ( $V_{clamp}$ ) through a 1.6–k $\Omega$  resistor ( $R_{clamp}$ ). It is then necessary to inject about

$$\left(\frac{\mathsf{V}_{\mathsf{OVP}}-\mathsf{V}_{\mathsf{clamp}}}{\mathsf{R}_{\mathsf{clamp}}}\right)$$

that is

$$\left(\frac{2.50 - 1.35}{1.6 \text{ k}} \cong 700 \,\mu\text{A}\right)$$

typically, to trigger the OVP protection. This current helps ensure an accurate detection by using the Zener diode far from its knee region.

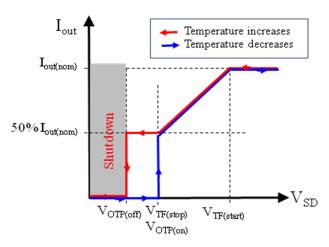

# Programmable Over Temperature Foldback Protection (OTP)

Connect an NTC between the SD pin and ground to detect an over-temperature condition. In response to a high temperature (detected if  $V_{SD}$  drops below  $V_{TF(start)}$ ), the

circuit gradually reduces the LED current down 50% of its initial value when  $V_{SD}$  reaches  $V_{TF(stop)}$ , in accordance with the characteristic of Figure 68 (Note 9).

If this thermal foldback cannot prevent the temperature from rising (testified by  $V_{SD}$  drop below  $V_{OTP}$ ), the circuit latches off (A version) or enters auto-recovery mode (B version) and cannot resume operation until  $V_{SD}$  exceeds  $V_{OTP(on)}$  to provide some temperature hysteresis (around  $10^{\circ}\text{C}$  typically). The OTP thresholds nearly correspond to the following resistances of the NTC:

- Thermal foldback starts when  $R_{NTC} \le R_{TF(start)}$ (11.7 k $\Omega$ , typically)

- Thermal foldback stops when  $R_{NTC} \le R_{TF(stop)}$  (8.0 k $\Omega$ , typically)

- OTP triggers when  $R_{NTC} \le R_{OTP(off)}$  (5.9 k $\Omega$ , typically)

- OTP is removed when  $R_{NTC} \ge R_{OTP(on)}$  (8.0 k $\Omega$ , typically) (Note 10)

- The above mentioned initial value is the output current before the system enters the thermal foldback, that is, its maximum level if step-dimming is not engaged or a lower one based on the step-dimming value.

- 10. This condition is sufficient for operation recovery of the B version. For the A version which latches off when OTP triggers, the circuit further needs to be reset by a V<sub>CC</sub> drop below V<sub>CC(reset)</sub>.

Figure 68. Output Current Reduction versus SD Pin Voltage

At startup, when  $V_{CC}$  reaches  $V_{CC(on)}$ , the OTP comparator is blanked for at least 180  $\mu s$  in order to allow the SD pin voltage to reach its nominal value if a filtering capacitor is connected to the SD pin. This avoids flickering of the LED light during turn on.

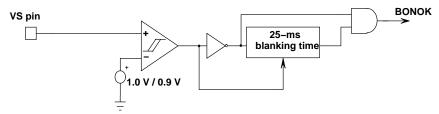

### **Brown-Out Protection**

The NCL30185 prevents operation when the line voltage is too low for proper operation. As illustrated in Figure 69, the circuit detects a brown–out situation if the  $V_S$  pin remains below the  $V_{BO(off)}$  threshold (0.9 V typical) for more than the 25–ms blanking time. In this case, the controller stops operating. Operation resumes as soon as the  $V_S$  pin voltage exceeds  $V_{BO(on)}$  (1.0 V typical) and  $V_{CC}$  is higher than  $V_{CC(on)}$ . To ease recovery, the circuit overrides the  $V_{CC}$  normal sequence (no need for  $V_{CC}$  cycling down below  $V_{CC(off)}$ ). Instead, its consumption immediately reduces to  $I_{CC(start)}$  so that  $V_{CC}$  rapidly charges up to  $V_{CC(on)}$ . Once done, the circuit re–starts operating.

Figure 69. Brown-out Circuit

### Die Over Temperature (TSD)

The circuit stops operating if the junction temperature  $(T_J)$  exceeds 150°C typically. The controller remains off until  $T_J$  goes below nearly 100°C.

### **Pin Connection Faults**

The circuit addresses most pin connection fault cases:

### • CS pin short to ground

The circuit senses the CS pin impedance every time it starts—up and after DRV pulses terminated by the 36– $\mu s$  maximum on—time. If the measured impedance does not exceed 120 ohm typically, the circuit stops operating. In practice, it is recommended to place a minimum of 250–ohm in series between the CS pin and the current sense resistor to take into account possible parametric deviations.

### • Fault of the GND connection

If the GND pin is properly connected, the supply current drawn from the positive terminal of the  $V_{CC}$  capacitor, flows out of the GND pin to return to the negative terminal of the  $V_{CC}$  capacitor. If the GND pin is not connected, the circuit ESD diodes offer another return path. The accidental non–connection of the GND pin is monitored by detecting that one of the ESD diode is conducting. Practically, the ESD diode of CS pin is monitored. If such a fault is detected for 200  $\mu$ s, the circuit stops generating DRV pulses.

More generally, incorrect pin connection situations (open, grounded, shorted to adjacent pin) are covered by AND9204/D.

### **Fault Modes**

The circuit turns off whenever a major faulty condition prevents it from operating:

- Severe OTP (V<sub>SD</sub> level below V<sub>OTP(off)</sub>)

- V<sub>CC</sub> OVP

- OVP2 (additional OVP provided by SD pin)

- Output diode short circuit protection: "WOD\_SCP high"

- Output / Auxiliary winding Short circuit protection: "Aux\_SCP high"

- Die over temperature (TSD)

In this mode, the DRV pulses generation is interrupted.

In the case of a latching–off fault, the circuit stops pulsing until the LED driver is unplugged and  $V_{CC}$  drops below  $V_{CC(reset)}$ . At that moment, the fault is cleared and the circuit could resume operation.

In the auto-recovery case, the circuit cannot generate DRV pulses for the auto-recovery 4–s delay. When this time has elapsed, the circuit recovers operation as soon as the  $V_{CC}$  voltage has exceeded  $V_{CC(on)}$ .

In the B version, all these protections are auto-recovery. The SD pin OTP and OVP, WOD\_SCP and AUX\_SCP are latching off in the A version (see Table 6).

### **Table 6. PROTECTION MODES**

|            | AUX_SCP       | WOD_SCP       | SD Pin OTP    | SD Pin OVP    |

|------------|---------------|---------------|---------------|---------------|

| NCL30185A* | Latching off  | Latching off  | Latching off  | Latching off  |

| NCL30185B  | Auto-recovery | Auto-recovery | Auto-recovery | Auto-recovery |

### **ORDERING INFORMATION**

| Device         | Package Type                 | Shipping         |

|----------------|------------------------------|------------------|

| NCL30185ADR2G* | SOIC-8 (Pb-Free/Halide Free) | 2500/Tape & Reel |

| NCL30185BDR2G  | SOIC-8 (Pb-Free/Halide Free) | 2500/Tape & Reel |

<sup>\*</sup>Please contact local sales representative for availability

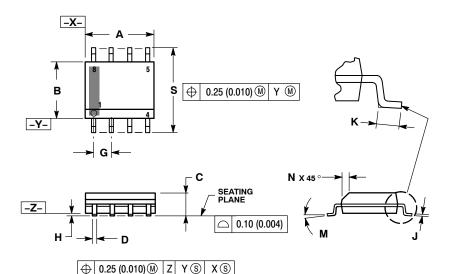

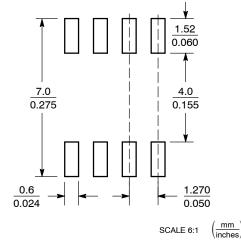

### SOIC-8 NB CASE 751-07 **ISSUE AK**

**DATE 16 FEB 2011**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER

- ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

- DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

- MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE

- DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

- 751-01 THRU 751-06 ARE OBSOLETE. NEW STANDARD IS 751-07.

|     | MILLIMETERS |       | INC   | HES   |

|-----|-------------|-------|-------|-------|

| DIM | MIN         | MAX   | MIN   | MAX   |

| Α   | 4.80        | 5.00  | 0.189 | 0.197 |

| В   | 3.80        | 4.00  | 0.150 | 0.157 |

| С   | 1.35        | 1.75  | 0.053 | 0.069 |

| D   | 0.33        | 0.51  | 0.013 | 0.020 |

| G   | 1.27        | 7 BSC | 0.05  | 0 BSC |

| Н   | 0.10        | 0.25  | 0.004 | 0.010 |

| J   | 0.19        | 0.25  | 0.007 | 0.010 |

| K   | 0.40        | 1.27  | 0.016 | 0.050 |

| М   | 0 °         | 8 °   | 0 °   | 8 °   |

| N   | 0.25        | 0.50  | 0.010 | 0.020 |

| S   | 5.80        | 6.20  | 0.228 | 0.244 |

### **SOLDERING FOOTPRINT\***

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

### **GENERIC MARKING DIAGRAM\***

XXXXX = Specific Device Code = Assembly Location = Wafer Lot = Year = Work Week W

= Pb-Free Package

XXXXXX XXXXXX AYWW AYWW Ŧ  $\mathbb{H}$ Discrete **Discrete** (Pb-Free)

XXXXXX = Specific Device Code = Assembly Location Α = Year ww = Work Week = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "•", may or may not be present. Some products may not follow the Generic Marking.

### **STYLES ON PAGE 2**

| DOCUMENT NUMBER: | 98ASB42564B | Electronic versions are uncontrolled except when accessed directly from the Document Reposit<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |             |  |  |

|------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|

| DESCRIPTION:     | SOIC-8 NB   |                                                                                                                                                                                 | PAGE 1 OF 2 |  |  |

onsemi and ONSEMI are trademarks of Semiconductor Components Industries, LLC dba onsemi or its subsidiaries in the United States and/or other countries. onsemi reserves the right to make changes without further notice to any products herein. onsemi makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does **onsemi** assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. **onsemi** does not convey any license under its patent rights nor the rights of others.

### SOIC-8 NB CASE 751-07 ISSUE AK

### **DATE 16 FEB 2011**

| STYLE 1: PIN 1. EMITTER 2. COLLECTOR 3. COLLECTOR 4. EMITTER 5. EMITTER 6. BASE 7. BASE 8. EMITTER                                                                 | STYLE 2: PIN 1. COLLECTOR, DIE, #1 2. COLLECTOR, #1 3. COLLECTOR, #2 4. COLLECTOR, #2 5. BASE, #2 6. EMITTER, #2 7. BASE, #1 8. EMITTER, #1               | STYLE 3: PIN 1. DRAIN, DIE #1 2. DRAIN, #1 3. DRAIN, #2 4. DRAIN, #2 5. GATE, #2 6. SOURCE, #2 7. GATE, #1 8. SOURCE, #1                            | STYLE 4: PIN 1. ANODE 2. ANODE 3. ANODE 4. ANODE 5. ANODE 6. ANODE 7. ANODE 8. COMMON CATHODE                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STYLE 5: PIN 1. DRAIN 2. DRAIN 3. DRAIN 4. DRAIN 5. GATE 6. GATE 7. SOURCE 8. SOURCE                                                                               | STYLE 6: PIN 1. SOURCE 2. DRAIN 3. DRAIN 4. SOURCE 5. SOURCE 6. GATE 7. GATE 8. SOURCE                                                                    | STYLE 7: PIN 1. INPUT 2. EXTERNAL BYPASS 3. THIRD STAGE SOURCE 4. GROUND 5. DRAIN 6. GATE 3 7. SECOND STAGE Vd 8. FIRST STAGE Vd                    | STYLE 8:<br>PIN 1. COLLECTOR, DIE #1<br>2. BASE. #1                                                                                                                             |

| STYLE 9: PIN 1. EMITTER, COMMON 2. COLLECTOR, DIE #1 3. COLLECTOR, DIE #2 4. EMITTER, COMMON 5. EMITTER, COMMON 6. BASE, DIE #2 7. BASE, DIE #1 8. EMITTER, COMMON | STYLE 10: PIN 1. GROUND 2. BIAS 1 3. OUTPUT 4. GROUND 5. GROUND 6. BIAS 2 7. INPUT 8. GROUND                                                              | STYLE 11: PIN 1. SOURCE 1 2. GATE 1 3. SOURCE 2 4. GATE 2 5. DRAIN 2 6. DRAIN 2 7. DRAIN 1 8. DRAIN 1                                               | STYLE 12: PIN 1. SOURCE 2. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                                         |

| STYLE 13: PIN 1. N.C. 2. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                              | STYLE 14: PIN 1. N-SOURCE 2. N-GATE 3. P-SOURCE 4. P-GATE 5. P-DRAIN 6. P-DRAIN 7. N-DRAIN 8. N-DRAIN                                                     | STYLE 15: PIN 1. ANODE 1 2. ANODE 1 3. ANODE 1 4. ANODE 1 5. CATHODE, COMMON 6. CATHODE, COMMON 7. CATHODE, COMMON 8. CATHODE, COMMON               | STYLE 16:  PIN 1. EMITTER, DIE #1  2. BASE, DIE #1  3. EMITTER, DIE #2  4. BASE, DIE #2  5. COLLECTOR, DIE #2  7. COLLECTOR, DIE #2  8. COLLECTOR, DIE #1  8. COLLECTOR, DIE #1 |

| STYLE 17: PIN 1. VCC 2. V2OUT 3. V1OUT 4. TXE 5. RXE 6. VEE 7. GND 8. ACC                                                                                          | STYLE 18: PIN 1. ANODE 2. ANODE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. CATHODE 8. CATHODE                                                                 | STYLE 19: PIN 1. SOURCE 1 2. GATE 1 3. SOURCE 2 4. GATE 2 5. DRAIN 2 6. MIRROR 2 7. DRAIN 1 8. MIRROR 1                                             | STYLE 20: PIN 1. SOURCE (N) 2. GATE (N) 3. SOURCE (P) 4. GATE (P) 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                           |

| STYLE 21: PIN 1. CATHODE 1 2. CATHODE 2 3. CATHODE 3 4. CATHODE 4 5. CATHODE 5 6. COMMON ANODE 7. COMMON ANODE 8. CATHODE 6                                        | STYLE 22: PIN 1. I/O LINE 1 2. COMMON CATHODE/VCC 3. COMMON CATHODE/VCC 4. I/O LINE 3 5. COMMON ANODE/GND 6. I/O LINE 4 7. I/O LINE 5 8. COMMON ANODE/GND | STYLE 23: PIN 1. LINE 1 IN 2. COMMON ANODE/GND 3. COMMON ANODE/GND 4. LINE 2 IN 5. LINE 2 OUT 6. COMMON ANODE/GND 7. COMMON ANODE/GND 8. LINE 1 OUT | STYLE 24: PIN 1. BASE 2. EMITTER 3. COLLECTOR/ANODE 4. COLLECTOR/ANODE 5. CATHODE 6. CATHODE 7. COLLECTOR/ANODE 8. COLLECTOR/ANODE                                              |