# **MIC22601**

# 4 MHz, 6A Integrated Switch Synchronous Buck Regulator

## **Features**

- Input Voltage Range: 2.6V to 5.5V

- 4 MHz PWM Frequency

- Output Voltage Adjustable Down to 0.7V

- · Output Current Up to 6A

- Small Passive Components: 0.22 μH and 22 μF

- · Full Sequencing and Tracking Ability

- · Power-on-Reset/Power Good

- Ultra-Fast Transient Response, Easy RC Compensation

- · 100% Maximum Duty Cycle

- · Fully Integrated MOSFET Switches

- · Micropower Shutdown

- · Thermal Shutdown and Current-Limit Protection

- 24-Pin 4 mm x 4 mm QFN

- –40°C to +125°C Junction Temperature Range

## **Applications**

- · High Power Density Point-of-Load Conversion

- Servers and Routers

- · Blu-Ray/DVD Players and Recorders

- · Computing Peripherals

- Base Stations

- · FPGAs, DSP, and Low Voltage ASIC Power

## **General Description**

The MIC22601 is a high efficiency 6A Integrated switch synchronous buck (step-down) regulator. The MIC22601 is optimized for highest efficiency (greater than 90%), while still switching at 4 MHz over a broad load range with only 0.22 µH inductor and down to 22 µF output capacitor. The ultra-high speed control loop keeps the output voltage within regulation even under extreme transient load swings commonly found in FPGAs and low voltage ASICs. The output voltage can be adjusted down to 0.7V to address all low voltage power needs. A full range of sequencing and tracking options is available with the MIC22601. The EN/DLY pin combined with the Power Good PG/POR pin allows multiple outputs to be sequenced in any way during turn-on and turn-off. The RC (Ramp Control) pin allows the device to be connected to another product in the MIC22xxx and/or MIC68xxx family, to keep the output voltages within a certain  $\Delta V$  on start up.

The MIC22601 is available in a 24-pin 4mm x 4mm QFN with a junction operating range from -40°C to +125°C.

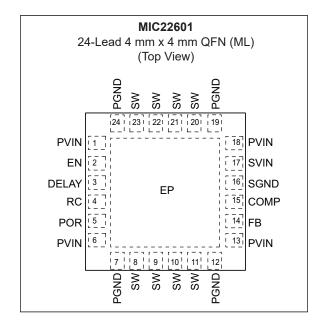

## Package Type

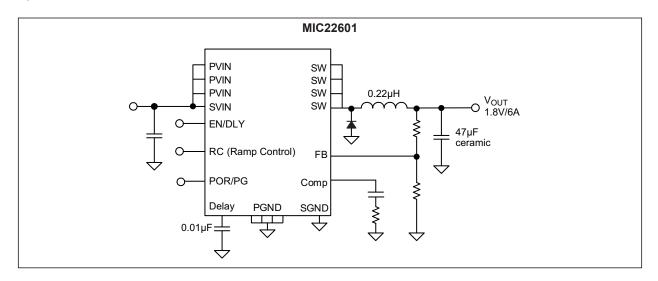

# **Typical Application Circuit**

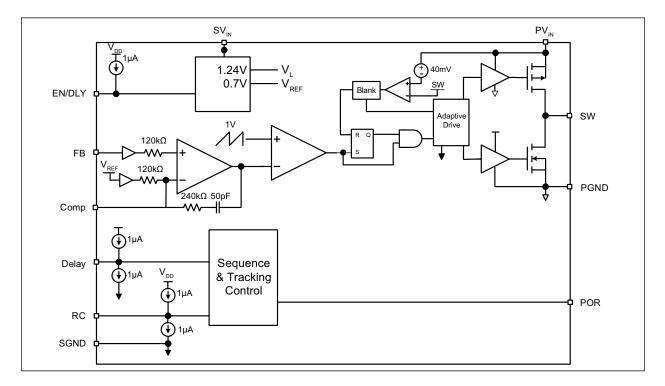

# **Functional Block Diagram**

## 1.0 ELECTRICAL CHARACTERISTICS

## **Absolute Maximum Ratings †**

| Supply Voltage (V <sub>IN</sub> )                        | +6V                      |

|----------------------------------------------------------|--------------------------|

| Output Switch Voltage (V <sub>SW</sub> )                 | +6V                      |

| Output Switch Current (I <sub>SW</sub> )                 |                          |

| Logic Input Voltage (V <sub>EN</sub> , V <sub>LQ</sub> ) | V <sub>IN</sub> to -0.3V |

| ESD Rating (Note 1)                                      | 2 kV                     |

| Operating Ratings ††                                     |                          |

† Notice: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational sections of this specification is not intended. Exposure to maximum rating conditions for extended periods may affect device reliability.

Supply Voltage (V<sub>IN</sub>) ......+2.6V to +5.5V

**†† Notice:** The device is not guaranteed to function outside its operating ratings.

Note 1: Devices are ESD sensitive. Handling precautions recommended.

## **ELECTRICAL CHARACTERISTICS**

**Electrical Characteristics:**  $T_A = +25^{\circ}C$  with  $V_{IN} = V_{EN} = 3.3V$ ;  $V_{OUT} = 1.8V$ , unless otherwise specified. **Bold** values indicate  $-40^{\circ}C \le T_J \le +125^{\circ}C$ . Note 1

| Parameter                      | Sym.                  | Min.  | Тур.  | Max.  | Units | Conditions                                                      |

|--------------------------------|-----------------------|-------|-------|-------|-------|-----------------------------------------------------------------|

| Supply Voltage Range           |                       | 2.6   | _     | 5.5   | V     | _                                                               |

| UVLO Threshold                 |                       | 2.4   | 2.5   | 2.6   | V     | Turn-on                                                         |

| UVLO Hysteresis                |                       |       | 280   | 1     | mV    | _                                                               |

| Quiescent Current, PWM Mode    |                       |       | 850   | 1300  | μA    | $V_{EN} \ge 1.34V$ ; $V_{FB} = 0.9V$ (not switching)            |

| Shutdown Current               | I <sub>SHDN</sub>     | _     | 5     | 10    | μA    | V <sub>EN</sub> = 0V                                            |

| Adjustable Feedback Voltage    | V <sub>FB</sub>       | 0.686 | 1     | 0.714 | V     | ±2% (over temperature)                                          |

| FB Pin Input Current           |                       |       | 1     | 1     | nA    | _                                                               |

| Current Limit                  | I <sub>LIM</sub>      | 6     | 10    | 14    | Α     | $V_{FB} = 0.9*V_{NOM}$                                          |

| Output Voltage Line Regulation |                       | _     | 0.2   | ı     | %     | $V_{OUT}$ = 1.8V, $V_{IN}$ = 2.6 to 5.5V, $I_{LOAD}$ = 100 mA   |

| Output Voltage Load Regulation |                       |       | 0.2   |       | %     | 100 mA < I <sub>LOAD</sub> < 6000 mA,<br>V <sub>IN</sub> = 3.3V |

| Maximum Duty Cycle             |                       | 100   | _     | _     | %     | V <sub>FB</sub> ≤ 0.5V                                          |

| Switch ON-Resistance PFET      |                       |       | 0.03  |       | Ω     | I <sub>SW</sub> = 1000 mA; V <sub>FB</sub> = 0.5V               |

| Switch ON-Resistance NFET      |                       |       | 0.025 | 1     | Ω     | I <sub>SW</sub> = 1000 mA; V <sub>FB</sub> = 0.9V               |

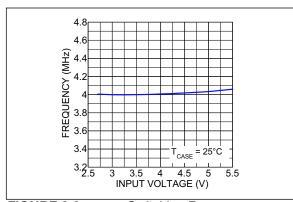

| Oscillator Frequency           | f <sub>O</sub>        | 3.2   | 4     | 4.8   | MHz   | _                                                               |

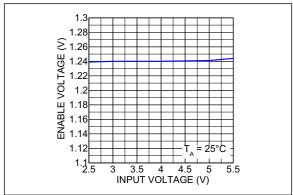

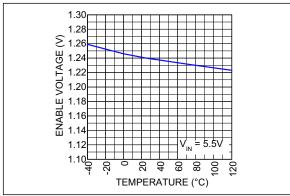

| EN/DLY Threshold Voltage       |                       | 1.14  | 1.24  | 1.34  | V     |                                                                 |

| EN/DLY Source Current          |                       | 0.6   | 1     | 1.8   | μA    | V <sub>IN</sub> = 2.6V to 5.5V                                  |

| RC Pin Current                 | I <sub>RAMP</sub>     | 0.5   | 1     | 1.7   | μA    | Ramp Control current                                            |

| Power-on-Reset                 |                       | _     | _     | 1     | μA    | - 5 5\/: DOD - High                                             |

| rower-on-neset                 | I <sub>PG(LEAK)</sub> | _     | _     | 2     | μA    | V <sub>PORH</sub> = 5.5V; POR = High                            |

Note 1: Specification for packaged product only.

## **ELECTRICAL CHARACTERISTICS (CONTINUED)**

**Electrical Characteristics:**  $T_A = +25^{\circ}C$  with  $V_{IN} = V_{EN} = 3.3V$ ;  $V_{OUT} = 1.8V$ , unless otherwise specified. **Bold** values indicate  $-40^{\circ}C \le T_J \le +125^{\circ}C$ . Note 1

| Parameter                              | Sym.                | Min. | Тур. | Max. | Units | Conditions                                                                       |

|----------------------------------------|---------------------|------|------|------|-------|----------------------------------------------------------------------------------|

| Power-on-Reset                         | V <sub>PG(LO)</sub> |      | 130  | l    | mV    | Output Logic Low Voltage<br>(undervoltage condition),<br>I <sub>POR</sub> = 5 mA |

| Power-on-Reset                         | V <sub>PG</sub>     | 7.5  | 10   | 12.5 | %     | Threshold,% of V <sub>OUT</sub> below nominal                                    |

|                                        |                     | _    | 2    | _    | %     | Hysteresis                                                                       |

| Overtemperature Shutdown               |                     | _    | 160  | _    | °C    | _                                                                                |

| Overtemperature Shutdown<br>Hysteresis |                     | _    | 20   | _    | °C    | _                                                                                |

Note 1: Specification for packaged product only.

## **TEMPERATURE SPECIFICATIONS**

| Parameters                    | Sym.           | Min. | Тур. | Max. | Units | Conditions         |  |  |

|-------------------------------|----------------|------|------|------|-------|--------------------|--|--|

| Temperature Ranges            |                |      |      |      |       |                    |  |  |

| Junction Temperature Range    | TJ             | -40  | _    | +125 | °C    | _                  |  |  |

| Storage Temperature Range     | T <sub>S</sub> | -65  | _    | +150 | °C    | _                  |  |  |

| Lead Temperature              | _              | _    | +260 | _    | °C    | Soldering, 10 sec. |  |  |

| Package Thermal Resistance    |                |      |      |      |       |                    |  |  |

| Thermal Decistance, OFN 241 d | $\theta_{JC}$  | _    | 14   | _    | °C/W  | _                  |  |  |

| Thermal Resistance, QFN 24-Ld | $\theta_{JA}$  | _    | 40   | _    | °C/W  | _                  |  |  |

Note 1: The maximum allowable power dissipation is a function of ambient temperature, the maximum allowable junction temperature and the thermal resistance from junction to air (i.e., T<sub>A</sub>, T<sub>J</sub>, θ<sub>JA</sub>). Exceeding the maximum allowable power dissipation will cause the device operating junction temperature to exceed the maximum +125°C rating. Sustained junction temperatures above +125°C can impact the device reliability.

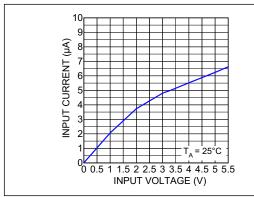

## 2.0 TYPICAL PERFORMANCE CURVES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

FIGURE 2-1: Shutdown Current vs. Input Voltage.

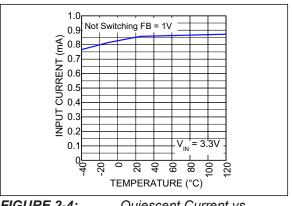

**FIGURE 2-4:** Quiescent Current vs. Temperature.

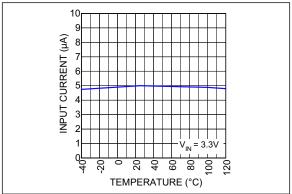

FIGURE 2-2: Shutdown Current vs. Temperature.

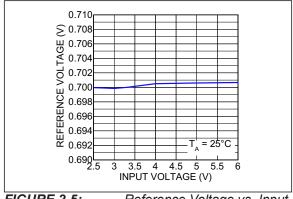

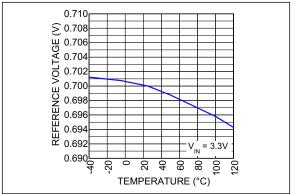

FIGURE 2-5: Reference Voltage vs. Input Voltage.

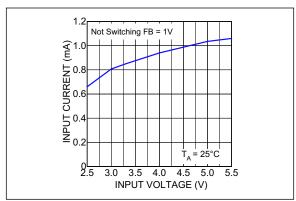

**FIGURE 2-3:** Quiescent Current vs. Input Voltage.

FIGURE 2-6: Reference Voltage vs.

Temperature.

FIGURE 2-7: Voltage.

Enable Voltage vs. Input

FIGURE 2-8: Temperature.

Enable Voltage vs.

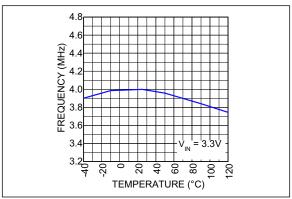

FIGURE 2-9: Input Voltage.

Switching Frequency vs.

**FIGURE 2-10:** Temperature.

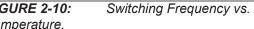

**FIGURE 2-11:** Voltage.

P-Channel R<sub>DS(ON)</sub> vs. Input

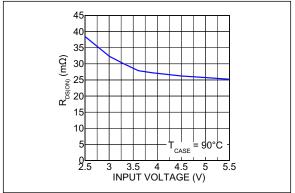

**FIGURE 2-12:** Control Voltage.

Output Voltage vs. Ramp

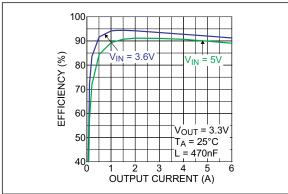

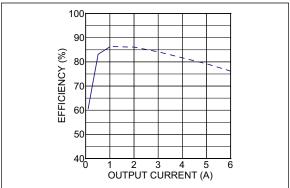

FIGURE 2-13: Efficiency vs. Load Current.

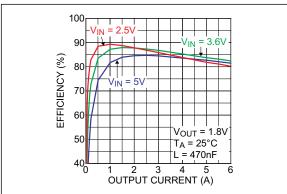

FIGURE 2-14: Efficiency vs. Output Current.

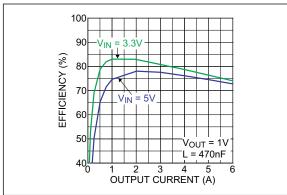

FIGURE 2-15: Efficiency vs. Output Current.

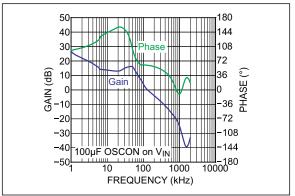

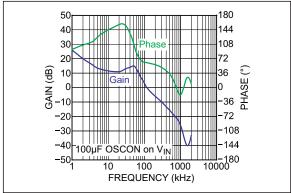

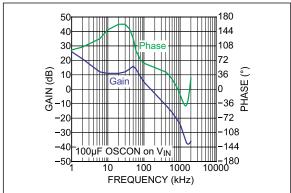

**FIGURE 2-16:** Bode Plot ( $V_{IN} = 5V$ ,  $V_{O} = 1.8V$ ), 6A, 470 nH and 47  $\mu$ F.

**FIGURE 2-17:** Bode Plot ( $V_{IN} = 3.3V$ ,  $V_{O} = 1.8V$ ), 6A, 470 nH and 47  $\mu$ F.

**FIGURE 2-18:** Bode Plot ( $V_{IN} = 5.0V$ ,  $V_{O} = 3.3V$ ), 6A, 470 nH and 47  $\mu$ F.

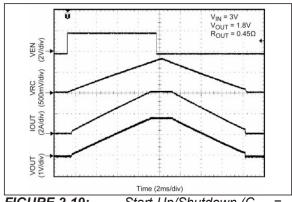

Start-Up/Shutdown ( $C_{RC}$  = **FIGURE 2-19:** 10 nF).

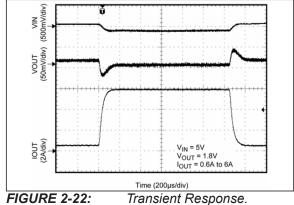

Transient Response.

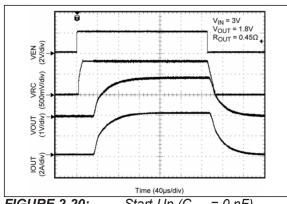

**FIGURE 2-20:** Start-Up ( $C_{RC} = 0 nF$ ).

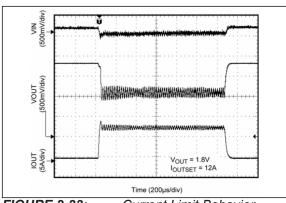

**FIGURE 2-23:** Current Limit Behavior.

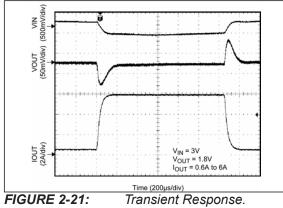

**FIGURE 2-21:**

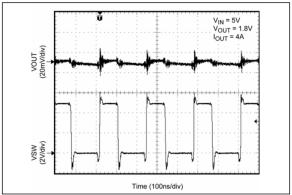

**FIGURE 2-24:** Output Noise and Ripple.

# **Typical Circuits and Waveforms**

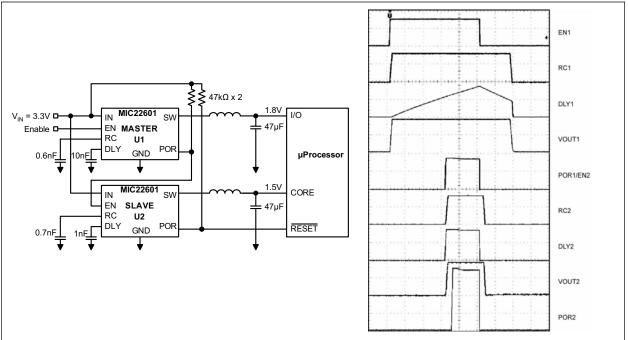

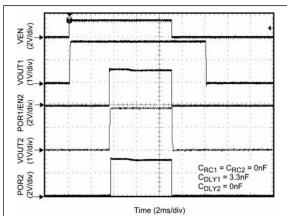

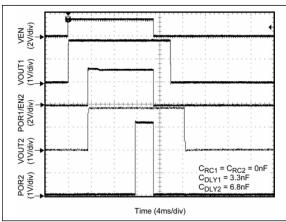

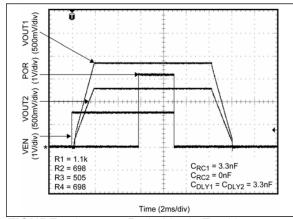

FIGURE 2-25: Sequencing Circuit and Waveform.

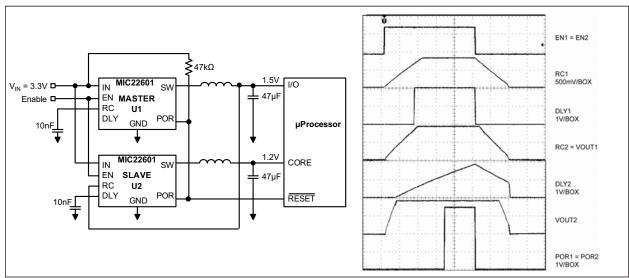

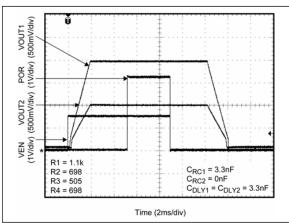

FIGURE 2-26: Tracking Circuit and Waveform.

## 3.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 3-1.

TABLE 3-1: PIN FUNCTION TABLE

| Pin Number                      | Pin Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 6, 13, 18                    | PVIN     | Power Supply Voltage (Input): Requires bypass capacitor to GND.                                                                                                                                                                                                                                                                                                                                                                   |

| 17                              | SVIN     | Signal Power Supply Voltage (Input): Requires bypass capacitor to GND.                                                                                                                                                                                                                                                                                                                                                            |

| 2                               | EN       | Enable/Delay (Input): This pin has a 1.24V band gap reference. When the pin is pulled higher than this, the part will start up. Below this voltage, the device is in its low quiescent current mode. The pin has a 1 $\mu A$ current source charging it to $V_{IN}.$ By adding a capacitor to this pin, a delay may easily be generated. The enable function will not operate with an input voltage lower than the min specified. |

| 4                               | RC       | Ramp Control: A capacitor-to-ground from this pin determines the slew rate of the output voltage during start-up. This can be used for tracking capability as well as soft start.                                                                                                                                                                                                                                                 |

| 14                              | FB       | Feedback: Input to the error amplifier. Connect to the external resistor divider network to set the output voltage.                                                                                                                                                                                                                                                                                                               |

| 15                              | COMP     | Compensation pin (Input): Place a RC network to GND to compensate the device, see the Applications section.                                                                                                                                                                                                                                                                                                                       |

| 5                               | POR/PG   | Power-on-Reset (Output): Open-drain output device indicates when the output is out of regulation and is active after the delay set by the DELAY pin. High when the Power is Good.                                                                                                                                                                                                                                                 |

| 7, 12, 19, 24                   | PGND     | Power Ground (Signal): Ground                                                                                                                                                                                                                                                                                                                                                                                                     |

| 16                              | SGND     | Signal Ground (Signal): Ground                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3                               | DELAY    | Delay (Input): Add a capacitor to set the delay from FB reaching 90% nominal to POR asserting high.                                                                                                                                                                                                                                                                                                                               |

| 8, 9, 10, 11,<br>20, 21, 22, 23 | SW       | Switch (Output): Internal power MOSFET output switches.                                                                                                                                                                                                                                                                                                                                                                           |

| EP                              | GND      | Exposed Pad (Power): Must make a full connection to a GND plane for full output power to be realized.                                                                                                                                                                                                                                                                                                                             |

## 4.0 FUNCTIONAL DESCRIPTION

#### **4.1 PVIN**

PVIN is the input supply to the internal 30 m $\Omega$  P-channel Power MOSFET. This should be connected externally to the SVIN pin. The supply voltage range is from 2.6V to 5.5V. A 10  $\mu$ F ceramic is recommended for bypassing each PVIN supply.

### 4.2 EN/DLY

This pin is internally fed with a 1  $\mu$ A current source from VIN. A delayed turn on is implemented by adding a capacitor to this pin. The delay is proportional to the capacitor value. The internal circuits are held off until EN/DLY reaches the enable threshold of 1.24V.

## 4.3 RC

RC allows the slew rate of the output voltage to be programmed by the addition of a capacitor from RC to ground. RC is internally fed with a 1  $\mu$ A current source and  $V_{OUT}$  slew rate is proportional to the capacitor and the 1  $\mu$ A source.

#### 4.4 DELAY

Adding a capacitor to this pin allows the delay of the POR signal.

When  $V_{OUT}$  reaches 90% of its nominal voltage, the DELAY pin current source (1  $\mu$ A) starts to charge the external capacitor. At 1.24V, POR is asserted high.

### 4.5 COMP

The MIC22601 uses an internal compensation network containing a fixed frequency zero (phase lead response) and pole (phase lag response) that allows the external compensation network to be simplified for stability. The addition of a single capacitor and resistor will add the necessary pole and zero for voltage mode loop stability using low value, low ESR ceramic capacitors.

#### 4.6 FB

The feedback pin provides the control path to control the output. A resistor divider connecting the feedback to the output is used to adjust the desired output voltage. Refer to the feedback section in the "Applications Information" for more detail.

## 4.7 POR

This is an open-drain output. A 47 k $\Omega$  resistor can be used for a pull-up to this pin. POR is asserted high when output voltage reaches 90% of nominal set voltage and after the delay set by C<sub>DELAY</sub>. POR is asserted low without delay when enable is set low or

when the output goes below the -10% threshold. For a Power Good (PG) function, the delay can be set to a minimum. This can be done by removing the DELAY capacitor.

### 4.8 SW

This is the connection to the drain of the internal P-channel MOSFET and drain of the N-channel MOSFET. This is a high frequency, high power connection. Therefore, traces should be kept as short and as wide as practical. In order to achieve the highest efficiency and reduce internal losses, connect a Schottky diode directly from this pin to ground and as close to the package as possible.

### **4.9 SGND**

Internal signal ground for all low power sections.

#### 4.10 **PGND**

Internal ground connection to the source of the internal N-channel MOSFETs.

## 5.0 APPLICATION INFORMATION

The MIC22601 is a 6A synchronous step-down regulator IC with a fixed 1 MHz, voltage mode PWM control scheme. The other features include tracking and sequencing control for controlling multiple output power systems, power-on-reset, and easy RC compensation.

## 5.1 Input Capacitor

A minimum 10  $\mu F$  ceramic capacitor is recommended on each of the PVIN pins for bypassing. X5R or X7R dielectrics are recommended for the input capacitor. Y5V dielectrics, aside from losing most of their capacitance over temperature, become resistive at high frequencies. This reduces their ability to filter out high frequency noise.

## 5.2 Output Capacitor

The MIC22601 was designed specifically for the use of ceramic output capacitors. 47  $\mu$ F can be increased to improve transient performance. Because the MIC22601 is voltage mode, the control loop relies on the inductor and output capacitor for compensation. For this reason, do not use excessively large output capacitors. The output capacitor requires either an X7R or X5R dielectric. Y5V and Z5U dielectric capacitors, aside from the undesirable effect of their wide variation in capacitance over temperature, become resistive at high frequencies. Using Y5V or Z5U capacitors can cause instability in the MIC22601.

## 5.3 Inductor Selection

Inductor selection will be determined by the following (not necessarily in the order of importance):

- Inductance

- · Rated current value

- · Size requirements

- DC resistance (DCR)

The MIC22601 is designed to use a 0.22  $\mu H$  to 4.7  $\mu H$  inductor.

Maximum current ratings of the inductor are generally given in two methods: permissible DC current and saturation current. Permissible DC current can be rated either for a 40°C temperature rise or a 10% loss in inductance. Ensure the inductor selected can handle the maximum operating current. When saturation current is specified, make sure that there is enough margin that the peak current will not saturate the inductor. The ripple can add as much as 1A to the output current level. The RMS rating should be chosen to be equal or greater than the current limit of the MIC22601 to prevent overheating in a fault condition. For best electrical performance, the inductor should be placed very close to the SW nodes of the IC. For this reason, the heat of the inductor is somewhat coupled to

the IC, which offers some level of protection if the inductor gets too hot. It is important to test all operating limits before settling on the final inductor choice.

The size requirements refer to the area and height requirements that are necessary to fit a particular design. Please refer to the inductor dimensions on their data sheet.

DC resistance is also important. While DCR is inversely proportional to size, DCR can represent a significant efficiency loss. Refer to the Efficiency Considerations section for a more detailed description.

## 5.4 EN/DLY Capacitor

EN/DLY sources 1  $\mu$ A out of the IC to allow a startup delay to be implemented. The delay time is simply the time it takes 1  $\mu$ A to charge C<sub>DLY</sub> to 1.24V. Therefore:

#### **EQUATION 5-1:**

$$t_{DLY} = \frac{1.24 \times C_{DLY}}{1.10^{-6}}$$

## 5.5 Efficiency Considerations

Efficiency is defined as the amount of useful output power, divided by the amount of power consumed.

## **EQUATION 5-2:**

$$\textit{Efficiency \%} = \left(\frac{V_{OUT} \times I_{OUT}}{V_{IN} \times I_{IN}}\right) \times 100$$

Maintaining high efficiency serves two purposes. It decreases power dissipation in the power supply, reducing the need for heat sinks and thermal design considerations and it decreases consumption of current for battery powered applications. Reduced current drawn from a battery increases the devices operating time, particularly in hand-held devices.

There are mainly two loss terms in switching converters: conduction losses and switching losses. Conduction losses are simply the power losses due to VI or I $^2$ R. For example, power is dissipated in the high side switch during the on cycle. The power loss is equal to the high-side MOSFET R $_{DS(ON)}$  multiplied by the RMS Switch Current squared ( $I_{SW}^2$ ). During the off cycle, the low-side N-Channel MOSFET conducts, also dissipating power. Similarly, the inductor's DCR and capacitor's ESR also contribute to the  $I^2$ R losses. Device operating current also reduces efficiency by the product of the quiescent (operating) current and the

supply voltage. The current required to drive the gates on and off at a constant 4 MHz frequency and the switching transitions make up the switching losses.

Although one is not required, a Schottky diode rated for 2A of continuous current, connected between SW and GND can add up to 5% to efficiency. This is achieved by preventing forward biasing of the internal MOSFET body diodes between switching transitions. The MOSFET body diode is less efficient for these short current pulses.

Figure 5-1 shows an efficiency curve. In the portion from 0A to 1A, efficiency losses are dominated by quiescent current losses, gate drive, and transition losses. In this case, lower supply voltages yield greater efficiency in that they require less current to drive the MOSFETs and have reduced input power consumption.

**FIGURE 5-1:** Efficiency 3.6V to 1.8V, L = 470 nH.

In the dashed region of 1A to 6A, efficiency loss is dominated by MOSFET  $R_{DS(ON)}$  and inductor DC losses. Higher input supply voltages will increase the Gate-to-Source threshold on the internal MOSFETs, reducing the internal  $R_{DS(ON)}$ . This improves efficiency by reducing DC losses in the device. All but the inductor losses are inherent to the device. In which case, inductor selection becomes increasingly critical in efficiency calculations. As the inductors are reduced in size, the DC resistance (DCR) can become quite significant. The DCR losses can be calculated as follows:

#### **EQUATION 5-3:**

$$L_{PD} = I_{OUT}^{2} \times DCR$$

From that, the loss in efficiency due to inductor resistance can be calculated as in Equation 5-4.

#### **EQUATION 5-4:**

$$EL = \left[1 - \left(\frac{V_{OUT} \times I_{OUT}}{(V_{OUT} \times I_{OUT}) + L_{PD}}\right)\right] \times 100$$

Where:

EL = Efficiency loss value in percent.

Efficiency loss due to DCR is minimal at light loads and gains significance as the load is increased. Inductor selection becomes a trade-off between efficiency and size in this case.

Alternatively, under lighter loads, the ripple current due to the inductance becomes a significant factor. When light load efficiencies become more critical, a larger inductor value maybe desired. Larger inductances reduce the peak-to-peak inductor ripple current, which minimizes losses.

## 5.6 Compensation

The MIC22601 has a combination of internal and external stability compensation to simplify the circuit for small, high efficiency designs. In such designs, voltage mode conversion is often the optimum solution. Voltage mode is achieved by creating an internal 4 MHz ramp signal and using the output of the error amplifier to modulate the pulse width of the switch node, maintaining output voltage regulation. With a typical gain bandwidth of 100 kHz to 200 kHz, the MIC22601 is capable of extremely fast transient responses.

The MIC22601 is designed to be stable with a typical application using a 0.22  $\mu H$  inductor and a 47  $\mu F$  ceramic (X5R) output capacitor. These values can be varied dependent on the trade off between size, cost and efficiency, keeping the LC natural frequency ideally less than 34 kHz to ensure stability can be achieved. The minimum recommended inductor value is 0.22  $\mu H$  and minimum recommended output capacitor value is 22  $\mu F$ . The trade off between changing these values is that with a larger inductor, there is a reduced peak-to-peak current which yields a greater efficiency at lighter loads. A larger output capacitor will improve transient response by providing a larger hold up reservoir of energy to the output.

The integration of one pole-zero pair within the control loop greatly simplifies compensation. The optimum values for  $C_{COMP}$  (in series with a 20 k $\Omega$  resistor) are shown in Table 5-1.

TABLE 5-1: COMPENSATION CAPACITOR SELECTION

|         | С                        |                   |                    |  |  |  |  |

|---------|--------------------------|-------------------|--------------------|--|--|--|--|

| L       | 22 μF -<br>47 μF         | 47 μF -<br>100 μF | 100 μF -<br>470 μF |  |  |  |  |

| 0.22 µH | 4.7 pF                   | 10 pF             | 15 pF              |  |  |  |  |

| 0.47 µH | 0 pF - 10 pF<br>(Note 1) | 22 pF             | 33 pF              |  |  |  |  |

| 1 μH    | 0 pF - 15 pF<br>(Note 2) | 15 pF -<br>22 pF  | 33 pF              |  |  |  |  |

| 2.2 µH  | 15 pF -<br>33 pF         | 33 pF -<br>47 pF  | 100 pF -<br>220 pF |  |  |  |  |

**Note 1:**  $V_{OUT} > 1.2V$ **2:**  $V_{OUT} > 1V$

## 5.7 Feedback

The MIC22601 provides a feedback pin to adjust the output voltage to the desired level. This pin connects internally to an error amplifier. The error amplifier then compares the voltage at the feedback to the internal 0.7V reference voltage and adjusts the output voltage to maintain regulation. The resistor divider network for a desired  $V_{\text{OUT}}$  is given by:

#### **EQUATION 5-5:**

$$R2 = \frac{R1}{\left(\frac{V_{OUT}}{V_{REE}} - 1\right)}$$

Where:

$V_{REF} = 0.7V$

$V_{OUT}$  = The desired output voltage.

A 10 k $\Omega$  or lower resistor value from the output to the feedback is recommended because large feedback resistor values increase the impedance at the feedback pin, making the feedback node more susceptible to noise pick-up. A small capacitor (50 pF to 100 pF) across the lower resistor can reduce noise pick-up by providing a low impedance path to ground.

### 5.8 PWM Operation

The MIC22601 is a voltage mode, pulse width modulation (PWM) controller. By controlling the duty cycle, a regulated DC output voltage is achieved. As load or supply voltage changes, so does the duty cycle to maintain a constant output voltage. In cases where the input supply runs into a dropout condition, the MIC22601 will run at 100% duty cycle.

The MIC22601 provides constant switching at 4 MHz with synchronous internal MOSFETs. The internal 30 m $\Omega$  MOSFETs include a high-side P-Channel MOSFET from the input supply to the switch pin and an

N-Channel MOSFET from the switch pin-to-ground. Because the low-side N-Channel MOSFET provides the current during the off cycle, a freewheeling Schottky diode from the switch node-to-ground is not required.

PWM control provides fixed-frequency operation. By maintaining a constant switching frequency, predictable fundamental and harmonic frequencies are achieved. Other methods of regulation, such as burst and skip modes, have frequency spectrums that change with load that can interfere with sensitive communication equipment.

## 5.9 Sequencing and Tracking

The MIC22601 provides additional pins to provide up/down sequencing and tracking capability for connecting multiple voltage regulators together.

#### 5.9.1 EN/DLY PIN

The EN pin contains a trimmed, 1  $\mu$ A current source that can be used with a capacitor to implement a fixed desired delay in some sequenced power systems. The threshold level for power on is 1.24V with a hysteresis of 20 mV.

#### 5.9.2 DELAY PIN

The DELAY pin also has a 1  $\mu$ A trimmed current source and a 1  $\mu$ A current sink which acts with an external capacitor to delay the operation of the Power-on-Reset (POR) output. This can be used also in sequencing outputs in a sequenced system, but with the addition of a conditional delay between supplies; allowing a first up, last down power sequence.

After Enable is driven high,  $V_{OUT}$  will start to rise (rate determined by RC capacitor). As the FB voltage goes above 90% of its nominal set voltage, Delay begins to rise as the 1  $\mu$ A source charges the external capacitor. When the threshold of 1.24V is crossed, POR is asserted high and Delay continues to charge to a voltage  $V_{DD}$ . When FB falls below 90% of nominal, POR is asserted low immediately. However, if enable is driven low, POR will fall immediately to the low state and Delay will begin to fall as the external capacitor is discharged by the 1  $\mu$ A current sink. When the threshold of  $V_{DD}-1.24V$  is crossed,  $V_{OUT}$  will begin to fall at a rate determined by the RC capacitor. As the voltage change in both cases is 1.24V, both rising and falling delays are matched at:

### **EQUATION 5-6:**

$$t_{POR} = \frac{1.24 \times C_{DLY}}{1.10^{-6}}$$

## 5.9.3 RC PIN

The RC pin provides a trimmed 1  $\mu$ A current source/sink similar to the DELAY pin for accurate ramp-up (soft-start) and ramp-down control. This allows the MIC22601 to be used in systems requiring voltage tracking or ratio-metric voltage tracking at startup.

There are two ways of using the RC pin:

- · Externally driven from a voltage source

- Externally attached capacitor sets output ramp up/down rate

In the first case, driving RC with a voltage from 0V to  $V_{REF}$  programs the output voltage between 0% and 100% of the nominal set voltage.

In the second case, the external capacitor sets the ramp up and ramp down time of the output voltage. The time is given by:

## **EQUATION 5-7:**

$$t_{RAMP} = \frac{0.7 \times C_{RC}}{1.10^{-6}}$$

Where:

$t_{RAMP}$  = The time from 0% to 100% nominal output voltage.

## 5.9.4 SEQUENCING AND TRACKING EXAMPLES

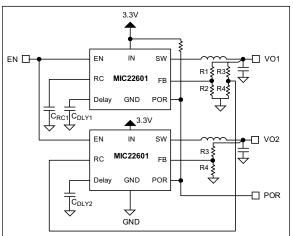

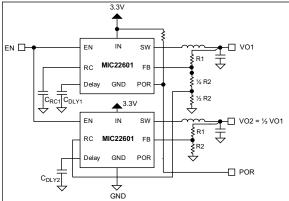

There are four distinct variations that are easily implemented using the MIC22601. The two sequencing variations are Delayed and Windowed. The two tracking variants are Normal and Ratio Metric. The following diagrams illustrate methods for connecting two MIC22601's to achieve these requirements.

## Sequencing

FIGURE 5-2: Sequencing MIC22601 Circuit.

FIGURE 5-3: Window Sequencing Example.

**FIGURE 5-4:** Delayed Sequencing Example.

## **Normal Tracking**

FIGURE 5-5: Normal Tracking Circuit.

FIGURE 5-6: Normal Tracking Example.

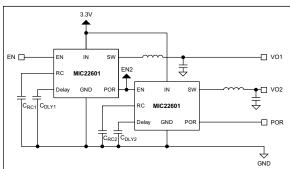

## **Ratio Metric Tracking**

#### 3.3V EN 🗅 ΕN IN sw –□ VO1 R1 **§** MIC22601 FB RC R2 \$ Delay GND POR C<sub>RC1</sub>C<sub>DLY1</sub> **♣**3.3V VO2 ↓ ΕN R3 F4 MIC22601 RC FB GND POR Delay -□ POR TC<sub>DLY2</sub> GND

FIGURE 5-7: Ratio Metric Tracking Circuit.

FIGURE 5-8: Ratio Metric Tracking Example.

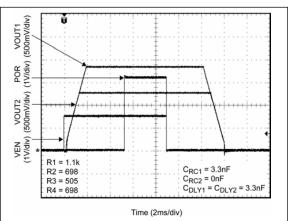

# DDR Memory $V_{DD}$ and $V_{TT}$ Tracking

FIGURE 5-9: DDR Memory Tracking Circuit.

**FIGURE 5-10:** DDR Memory Tracking Example.

An alternative method here shows an example of a  $V_{DDQ}$  &  $V_{TT}$  solution for a DDR memory power supply. Note that POR is taken from VO1 as POR2 will not go high. This is because POR is set high when FB > 0.9 x  $V_{REF}$ . In this example, FB2 is regulated to  $\frac{1}{2}V_{REF}$ .

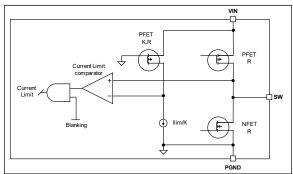

#### 5.10 Current Limit

The MIC22601 is protected against overload in two stages. The first is to limit the current in the P-channel switch; the second is by overtemperature shutdown.

Current is limited by measuring the current through the high-side MOSFET during its power stroke and immediately switching off the driver when the preset limit is exceeded.

The circuit in Figure 5-11 describes the operation of the current-limit circuit. Because the actual  $R_{\rm DS(ON)}$  of the P-Channel MOSFET varies part-to-part, over temperature and with input voltage, simple IR voltage detection is not employed. Instead, a smaller copy of the Power MOSFET (Reference FET) is fed with a constant current that is directly proportional to the factory set current limit. This sets the current limit as a current ratio and is not dependent upon the  $R_{\rm DS(ON)}$  value. Current limit is set to 10A nominal. Variations in the scale factor K between the Power PFET and the reference PFET used to generate the limit threshold account for a relatively small inaccuracy.

FIGURE 5-11: Current Limit Detail.

#### 5.11 Thermal Considerations

The MIC22601 is packaged in a 4 mm x 4 mm QFN, a package that has excellent thermal performance equaling that of the larger TSSOP packages. This maximizes heat transfer from the junction to the exposed pad (ePad) that connects to the ground plane. The size of the ground plane attached to the exposed pad determines the overall thermal resistance from the junction to the ambient air surrounding the printed circuit board. The junction temperature for a given ambient temperature can be calculated using:

### **EQUATION 5-8:**

$$T_J = T_A + P_{DISS} \times R\theta_{JA}$$

Where:

$P_{DISS}$  = The power dissipated within the QFN package and is typically 1.8W at 6A load. This has been calculated for a 0.47  $\mu H$  inductor and details can be found in Table 5-2 for reference.

$R\theta_{JA}$  = A combination of junction to case thermal resistance  $(R\theta_{JC})$  and Case-to-Ambient thermal resistance  $(R\theta_{CA}),$  since thermal resistance of the solder connection from the ePad to the PCB is negligible;  $R\theta_{CA}$  is the thermal resistance of the ground plane to ambient, so  $R\theta_{JA} = R\theta_{JC} + R\theta_{CA}.$   $T_A$  = The operating ambient temperature.

#### Example:

The Evaluation Board has two copper planes that contribute to an R $\theta_{JA}$  of approximately 25°C/W. The worst case R $\theta_{JC}$  of the QFN 4x4 is 14°C/W.

#### **EQUATION 5-9:**

$$R\theta_{JA} = R\theta_{JC} + R\theta_{CA}$$

$$R\theta_{JA} = 14^{\circ}C/W + 25^{\circ}C/W = 39^{\circ}C/W$$

To calculate the junction temperature for a 50°C ambient:

### **EQUATION 5-10:**

$$T_{J} = T_{A} + (P_{DISS} \times R\theta_{JA})$$

$$T_{J} = 50^{\circ}C + (1.8W \times 39^{\circ}C/W)$$

$$T_{J} = 120^{\circ}C$$

This is below the maximum of 125°C.

TABLE 5-2: POWER DISSIPATION FOR 6A OUTPUT

| V <sub>OUT</sub> | V <sub>IN</sub> |       |       |       |       |  |  |

|------------------|-----------------|-------|-------|-------|-------|--|--|

| at 5A            | 3V              | 3.5V  | 4V    | 4.5V  | 5V    |  |  |

| 1V               | 1.67W           | 1.71W | 1.76W | 1.81W | 1.85W |  |  |

| 1.2V             | 1.68W           | 1.72W | 1.77W | 1.81W | 1.86W |  |  |

| 1.8V             | 1.70W           | 1.74W | 1.79W | 1.74W | 1.84W |  |  |

| 2.5V             | 1.72W           | 1.76W | 1.80W | 1.85W | 1.89W |  |  |

| 3.3V             | _               | 1.78W | 1.82W | 1.86W | 1.91W |  |  |

## 6.0 PACKAGING INFORMATION

## 6.1 Package Marking Information

24-Lead QFN\*

## Example

**Legend:** XX...X Product code or customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

(e3) Pb-free JEDEC® designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (e3) can be found on the outer packaging for this package.

ullet, lacktriangle, lacktriangle Pin one index is identified by a dot, delta up, or delta down (triangle mark).

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information. Package may or may not include the corporate logo.

Underbar (\_) and/or Overbar (¯) symbol may not be to scale.

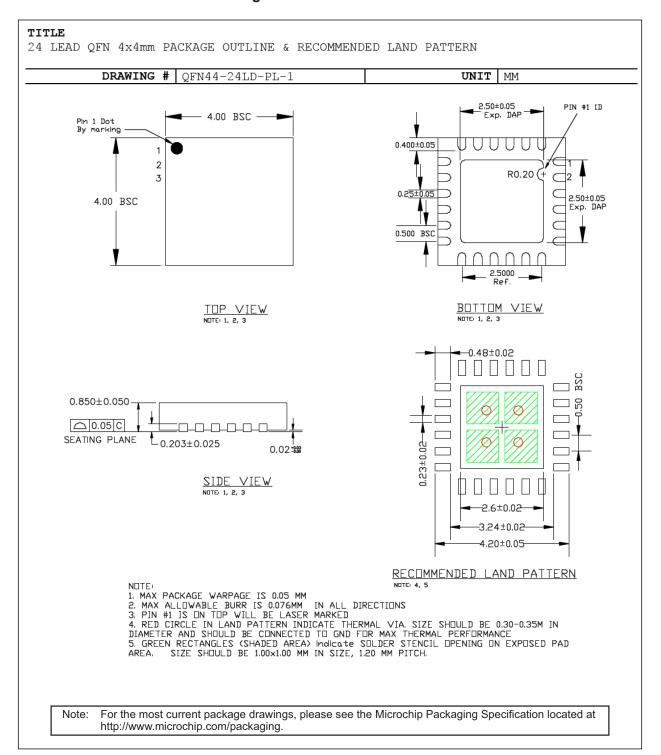

## 24-Lead QFN 4 mm x 4 mm Package Outline and Recommended Land Pattern

## APPENDIX A: REVISION HISTORY

## Revision A (January 2020)

- Converted Micrel document MIC22601 to Microchip data sheet template DS20006295A.

- · Minor grammatical text changes throughout.

- Evaluation Board Schematic, BOM, and PCB Layout sections from original data sheet moved to the part's Evaluation Board User's Guide.

# MIC22601

NOTES:

## PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, contact your local Microchip representative or sales office.

<u>Device</u> <u>X</u> <u>XX</u> -<u>XX</u> Part No. Junction Package Media Type Temp. Range MIC22601: 4 MHz, 6A Integrated Switch Synchronous Device: Buck Regulator Junction –40°C to +125°C, RoHS-Compliant Temperature Range: Package: 24-Lead 4 mm x 4 mm QFN Media Type: TR = 5,000/Reel

Examples:

a) MIC22601YML-TR: MIC22601, Adj. Output Voltage,

-40°C to +125°C Temperature Range, 24-Lead QFN,

5,000/Reel

Note 1: Tape and Reel identifier only appears in the catalog part number description. This identifier is used for ordering purposes and is not printed on the device package. Check with your Microchip Sales Office for package availability with the Tape and Reel option.

# MIC22601

NOTES:

#### Note the following details of the code protection feature on Microchip devices:

- · Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

#### **Trademarks**

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PackeTime, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TempTrackr, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, FlashTec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, Vite, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, INICnet, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2020, Microchip Technology Incorporated, All Rights Reserved.

ISBN: 978-1-5224-5476-2

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

# Worldwide Sales and Service

#### **AMERICAS**

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277

Technical Support: http://www.microchip.com/ support

Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Austin, TX** Tel: 512-257-3370

Boston

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI

Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

**Raleigh, NC** Tel: 919-844-7510

New York, NY Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110 Tel: 408-436-4270 **Canada - Toronto**

Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733

**China - Beijing** Tel: 86-10-8569-7000

**China - Chengdu** Tel: 86-28-8665-5511

**China - Chongqing** Tel: 86-23-8980-9588

**China - Dongguan** Tel: 86-769-8702-9880

**China - Guangzhou** Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

China - Nanjing Tel: 86-25-8473-2460

China - Qingdao Tel: 86-532-8502-7355

**China - Shanghai** Tel: 86-21-3326-8000

**China - Shenyang** Tel: 86-24-2334-2829

**China - Shenzhen** Tel: 86-755-8864-2200

China - Suzhou Tel: 86-186-6233-1526

**China - Wuhan** Tel: 86-27-5980-5300

China - Xian Tel: 86-29-8833-7252

China - Xiamen

Tel: 86-592-2388138

**China - Zhuhai** Tel: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631

India - Pune Tel: 91-20-4121-0141

**Japan - Osaka** Tel: 81-6-6152-7160

**Japan - Tokyo** Tel: 81-3-6880- 3770

Korea - Daegu

Tel: 82-53-744-4301 **Korea - Seoul** Tel: 82-2-554-7200

Malaysia - Kuala Lumpur Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila Tel: 63-2-634-9065

**Singapore** Tel: 65-6334-8870

**Taiwan - Hsin Chu** Tel: 886-3-577-8366

Taiwan - Kaohsiung Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600

Thailand - Bangkok Tel: 66-2-694-1351

Vietnam - Ho Chi Minh Tel: 84-28-5448-2100

#### **EUROPE**

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

Finland - Espoo Tel: 358-9-4520-820

France - Paris

Tel: 33-1-69-53-63-20

Fax: 33-1-69-30-90-79

Germany - Garching Tel: 49-8931-9700

**Germany - Haan** Tel: 49-2129-3766400

Germany - Heilbronn Tel: 49-7131-72400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Rosenheim Tel: 49-8031-354-560

Israel - Ra'anana Tel: 972-9-744-7705

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Padova Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim Tel: 47-7288-4388

**Poland - Warsaw** Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**Sweden - Gothenberg** Tel: 46-31-704-60-40

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820