# **MCP1633**

### Low-Side PWM Controller with LED Dimming Capability

#### **Features**

- High Speed Current Mode Pulse-Width Modulator (PWM) Controller

- Easy to Interface with PIC<sup>®</sup> Microcontroller for Implementing High-Performance LED Drivers

- Integrated General Purpose Operational Amplifier that can be Used for Current Sensing

- Internal Oscillator with Adjustable Frequency via External Resistor

- · External Synchronization Option for the Oscillator

- · Internal Slope Compensation Circuit

- Current Sense to V<sub>EXT</sub> Response <120 ns Typical</li>

- Internal Leading Edge Blanking Circuit for Current Sense Input

- · Programmable Current Sense Offset

- · Internal Reference Voltage Generator

- · Soft Start Capability

- Internal Push-Pull MOSFET Driver with 1A Peak Current Capability

- Internal MOSFET Driver for Dimming/Load Disconnect

- Input Voltage Range: 3V to 5.5V

- Undervoltage Lockout Circuit

- · Output Overvoltage Protection

- · Output Short Circuit Protection

- · Overtemperature Protection

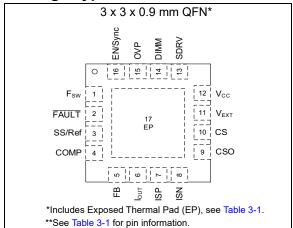

- Small 16-Pin QFN 3 x 3 mm Package

- · Passes automotive AEC-Q100 reliability testing

#### **Applications**

- · LED Drivers

- · Switch Mode Power Supplies

- · Brick DC-DC Converters

#### **General Description**

The MCP1633 High Speed PWM Controller is a pulse-width modulator developed for standalone power supply applications. The MCP1633 design is based on the MCP1632 PWM Controller but includes specific blocks for PWM LED dimming. It is suitable for use in topologies requiring a low-side MOSFET, such as Boost, Flyback, SEPIC, CUK, etc.

The MCP1633 uses Current Mode Control to provide superior bandwidth and transient response, and also cycle-by-cycle current limiting with adjustable peak offset. The MCP1633 is also capable of operating in Voltage Mode Control if required.

The switching frequency of the MCP1633 can be set by an external resistor between 200 kHz and 2.2 MHz.

The MCP1633 reference voltage is adjustable by using only one external resistor.

The MCP1633 integrates a current sense amplifier with programmable gain using external resistors.

The MCP1633 can achieve high performance LED dimming by "freezing" the compensation network and load disconnect capability.

The MCP1633 integrates a high speed comparator with a high performance error amplifier with a PWM latch to perform the high speed analog Power Supply PWM function.

Integrated Undervoltage Lockout, Overvoltage protection and Overtemperature Protection make designs using the MCP1633 robust over a range of external conditions.

### Package Type

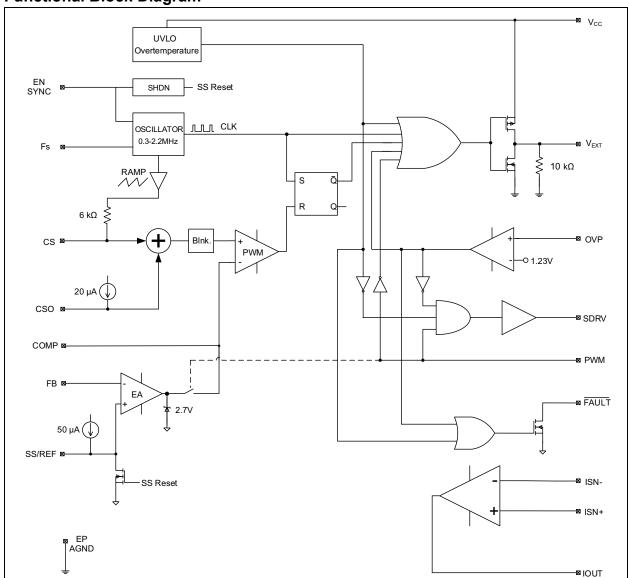

### **Functional Block Diagram**

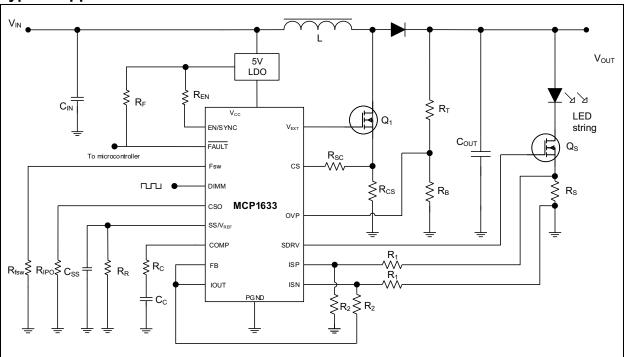

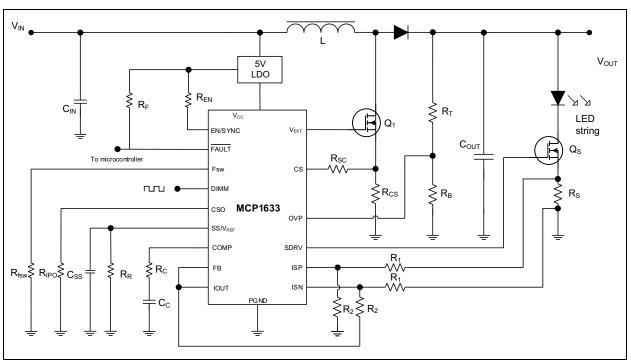

### **Typical Application for LED Driver**

#### 1.0 ELECTRICAL CHARACTERISTICS

### 1.1 Absolute Maximum Ratings†

| V <sub>CC</sub>                                 | 6V                                      |

|-------------------------------------------------|-----------------------------------------|

| Maximum Voltage on Any Pin                      | $(V_{GND} - 0.3V)$ to $(V_{IN} + 0.3V)$ |

| V <sub>EXT</sub> Short Circuit Current          | Internally Limited                      |

| Storage Temperature                             |                                         |

| Maximum Junction Temperature                    |                                         |

| Operating Junction Temperature                  | —40°C to +125°C                         |

| ESD Protection on All Pins (HMB) <sup>(1)</sup> | 2 kV                                    |

<sup>†</sup> Notice: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational sections of this specification is not intended. Exposure to maximum rating conditions for extended periods may affect device reliability.

Note 1: Devices are ESD-sensitive. Handling precautions are recommended. Human body model, 1.5 k $\Omega$  in series with 100 pF.

#### DC CHARACTERISTICS

**Electrical Specifications**: Unless otherwise noted, during characterization,  $V_{IN} = 3.3V$  to 5.5V,  $F_{SW} = 600$  kHz with  $C_{IN} = 1.0$  µF,  $T_{\Delta} = +25$ °C,  $T_{\Delta} = -40$ °C to +125°C.

| $C_{IN} = 1.0 \mu\text{F},  T_A = +25^{\circ}\text{C},  T_A = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}.$ |                                 |       |      |      |                         |                                                         |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------|---------------------------------|-------|------|------|-------------------------|---------------------------------------------------------|--|--|--|--|

| Parameters                                                                                                           | Symbol                          | Min.  | Тур. | Max. | Units                   | Conditions                                              |  |  |  |  |

| Inputs                                                                                                               |                                 |       |      |      |                         |                                                         |  |  |  |  |

| Input Operating Voltage                                                                                              | $V_{IN}$                        | 3     | _    | 5.5  | V                       |                                                         |  |  |  |  |

| Input Quiescent Current                                                                                              | I(V <sub>IN</sub> )             | _     | 5    | 5.75 | mA                      | $I_{EXT}$ = 0 mA, $V_{CC}$ = 5V,<br>$F_{SW}$ = 1200 kHz |  |  |  |  |

| Shutdown Current                                                                                                     | I <sub>IN_SHDN</sub>            | _     | _    | 1    | μA                      | EN = 0V                                                 |  |  |  |  |

| EN Input                                                                                                             |                                 |       |      |      |                         |                                                         |  |  |  |  |

| EN Input Voltage Low                                                                                                 | $EN_LOW$                        | _     | _    | 8.0  | V                       |                                                         |  |  |  |  |

| EN Input Voltage High                                                                                                | EN <sub>HIGH</sub>              | 75    | _    | _    | % of<br>V <sub>IN</sub> |                                                         |  |  |  |  |

| Oscillator                                                                                                           |                                 |       |      |      |                         |                                                         |  |  |  |  |

| Internal Oscillator Range                                                                                            | F <sub>osc</sub>                | 200   | -    | 2200 | kHz                     | Refer to Section 4.6 "Internal Oscillator" for details  |  |  |  |  |

| F <sub>SW</sub> Output Voltage                                                                                       | V <sub>RFSW</sub>               | 0     | _    | 3    | V                       |                                                         |  |  |  |  |

| External Synchronization<br>Signal Frequency Rage                                                                    | F <sub>SYNC</sub>               | 200   | 1    | 2500 | kHz                     |                                                         |  |  |  |  |

| SYNC Signal Low Voltage                                                                                              | V <sub>SYNCL</sub>              | _     | _    | 0.8  | V                       |                                                         |  |  |  |  |

| SYNC Signal High Voltage                                                                                             | V <sub>SYNCH</sub>              | 2     | _    | _    | V                       |                                                         |  |  |  |  |

| SYNC Signal Time Low                                                                                                 | T <sub>SYNC_MAX</sub>           | _     | 10   | _    | ns                      | Note 1                                                  |  |  |  |  |

| SYNC Signal Time High                                                                                                | T <sub>SYNC_MIN</sub>           | _     | 10   | _    | ns                      | Note 1                                                  |  |  |  |  |

| SYNC Signal Rise/Fall Time                                                                                           | T <sub>SYNC RISE/</sub><br>FALL | 0.001 | 1    | 10   | us                      | Note 1                                                  |  |  |  |  |

| Error Amplifier                                                                                                      |                                 |       |      |      |                         |                                                         |  |  |  |  |

| Input Voltage Offset                                                                                                 | V <sub>OS</sub>                 | -7.5  |      | 7.5  | mV                      |                                                         |  |  |  |  |

| Error Amplifier PSRR                                                                                                 | PSRR                            | 80    | _    | _    | dB                      | V <sub>IN</sub> = +5V                                   |  |  |  |  |

| Common Mode Input<br>Range                                                                                           | $V_{CM}$                        | 0     |      | 2    | V                       |                                                         |  |  |  |  |

Note 1: Determined by characterization, not production tested.

### **DC CHARACTERISTICS (CONTINUED)**

**Electrical Specifications**: Unless otherwise noted, during characterization,  $V_{IN}$  = 3.3V to 5.5V,  $F_{SW}$  = 600 kHz with  $C_{IN}$  = 1.0  $\mu$ F,  $T_{\Delta}$  = +25°C,  $T_{\Delta}$  = -40°C to +125°C.

| $C_{IN} = 1.0 \ \mu F, T_A = +25^{\circ}C, T_A = -40^{\circ}C \text{ to } +125^{\circ}C.$ |                      |              |      |      |          |                                                                |  |  |  |

|-------------------------------------------------------------------------------------------|----------------------|--------------|------|------|----------|----------------------------------------------------------------|--|--|--|

| Parameters                                                                                | Symbol               | Min.         | Тур. | Max. | Units    | Conditions                                                     |  |  |  |

| Common Mode Rejection Ratio                                                               | CMRR                 | 60           | _    | _    | dB       | V <sub>CM</sub> = 0 to 2V ( <b>Note 1</b> )                    |  |  |  |

| Transconductance                                                                          | 9 <sub>m</sub>       | 160          | 200  | 240  | μS       | V <sub>CM</sub> = 0 to 2V                                      |  |  |  |

| Output Source Current                                                                     | I <sub>OSOURCE</sub> | 13           |      |      | μA       | V <sub>CC</sub> = 5V                                           |  |  |  |

| Output Sink Current                                                                       | I <sub>OSINK</sub>   | 13           |      |      | μA       | V <sub>CC</sub> = 5V                                           |  |  |  |

| Gain Bandwidth Product                                                                    | GBWP                 | 3.5          | _    |      | MHz      | Note 1                                                         |  |  |  |

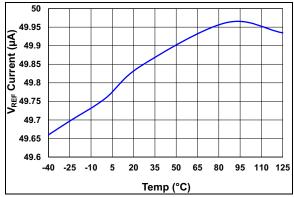

| Reference Voltage Section                                                                 |                      |              |      |      |          |                                                                |  |  |  |

| Reference Voltage Input<br>Voltage                                                        | $V_{REF}$            | 0            | _    | 3    | V        | Refer to Section 4.5 "Reference Voltage Generator" for details |  |  |  |

| Internal Constant Current<br>Generator                                                    | I <sub>REF</sub>     | 48           | 50   | 52   | μA       | Refer to Section 4.5 "Reference Voltage Generator" for details |  |  |  |

| Current Sense Input                                                                       |                      |              |      |      |          |                                                                |  |  |  |

| Maximum Input                                                                             | V <sub>CS_MAX</sub>  | 0.85         | 0.9  | 0.95 | V        |                                                                |  |  |  |

| Blanking Time                                                                             | T <sub>BLANK</sub>   | _            | 30   | _    | ns       | Note 1                                                         |  |  |  |

| Delay from CS to VEXT                                                                     | T <sub>CS_Vext</sub> | _            |      | 35   | ns       | Note 1                                                         |  |  |  |

| Current Sense Input Bias<br>Current                                                       | I <sub>CS_B</sub>    | _            | -0.1 | _    | μΑ       | Note 1                                                         |  |  |  |

| <b>Current Sense Operational</b>                                                          | Amplifier            |              |      |      |          |                                                                |  |  |  |

| Input Offset Voltage                                                                      | V <sub>OS</sub>      | -2.8         |      | 2.8  | mV       |                                                                |  |  |  |

| Operational Amplifier PSRR                                                                | PSRR                 | 60           | _    | _    | dB       | V <sub>IN</sub> = 5V                                           |  |  |  |

| Input Bias Current                                                                        | I <sub>B</sub>       | _            | 1    | _    | nA       | Note 1                                                         |  |  |  |

| Common Mode Input<br>Range                                                                | $V_{CM}$             | GND –<br>0.3 | _    | 2    | V        |                                                                |  |  |  |

| Common Mode Rejection Ratio                                                               | CMRR                 | _            | 80   | _    | dB       | Note 1                                                         |  |  |  |

| Open Loop Voltage Gain                                                                    | A <sub>VOL</sub>     | 85           |      | 150  | dB       | Note 1                                                         |  |  |  |

| Low Level Output                                                                          | Vo                   | _            | 15   | 20   | mV       |                                                                |  |  |  |

| Gain Bandwidth Product                                                                    | GBWP                 | 1.5          | 2    | _    | MHz      |                                                                |  |  |  |

| Amplifier Sink Current                                                                    | I <sub>SINK</sub>    | 5            | 10   |      | mA       |                                                                |  |  |  |

| Amplifier Source Current                                                                  | I <sub>SOURCE</sub>  | 5            | 10   | _    | mA       |                                                                |  |  |  |

| Pedestal Voltage Generator                                                                | •                    |              |      |      |          |                                                                |  |  |  |

| Internal Constant Current<br>Generator                                                    | CSO                  | 17.5         | 20   | 25   | μA       |                                                                |  |  |  |

| PWM                                                                                       |                      |              |      |      |          |                                                                |  |  |  |

| Minimum Duty Cycle                                                                        | DC <sub>MIN</sub>    |              | _    | 0    | %        |                                                                |  |  |  |

| Maximum Duty Cycle                                                                        | DC <sub>MAX</sub>    | 85           | 90   | 98   | %        |                                                                |  |  |  |

| Slope Compensation Ramp                                                                   | Generator            |              |      |      |          |                                                                |  |  |  |

| Ramp Amplitude                                                                            | V <sub>RAMP</sub>    | 8.0          | 0.9  | 1    | $V_{PP}$ |                                                                |  |  |  |

| DC Offset Low                                                                             |                      | 0.15         | 0.32 | 0.45 | V        |                                                                |  |  |  |

| DC Offset High                                                                            |                      | 1.12         | 1.22 | 1.32 | V        |                                                                |  |  |  |

| Ramp Generator Output Impedance                                                           | Z <sub>RG</sub>      | 5.5          | 6    | 6.5  | kΩ       |                                                                |  |  |  |

| Internal Driver                                                                           |                      |              |      |      |          |                                                                |  |  |  |

|                                                                                           |                      |              |      |      |          |                                                                |  |  |  |

**Note 1:** Determined by characterization, not production tested.

### **DC CHARACTERISTICS (CONTINUED)**

**Electrical Specifications**: Unless otherwise noted, during characterization,  $V_{IN}$  = 3.3V to 5.5V,  $F_{SW}$  = 600 kHz with  $C_{IN}$  = 1.0  $\mu$ F,  $T_A$  = +25°C,  $T_A$  = -40°C to +125°C.

| O <sub>IN</sub> = 1.0 μ1, 1 <sub>A</sub> = 123 C, 1 <sub>A</sub> | $C_{\text{IN}} = 1.0  \mu\text{F},  1_{\text{A}} = +25  \text{C},  1_{\text{A}} = -40  \text{C}  10 + 125  \text{C}.$ |      |      |      |          |                                                       |  |  |  |  |

|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------|------|------|----------|-------------------------------------------------------|--|--|--|--|

| Parameters                                                       | Symbol                                                                                                                | Min. | Тур. | Max. | Units    | Conditions                                            |  |  |  |  |

| R <sub>DSon</sub> P-Channel                                      | $R_{DSonP}$                                                                                                           |      | _    | 4.5  | Ω        | Typical for V <sub>IN</sub> = 5.0V                    |  |  |  |  |

| R <sub>DSon</sub> N-Channel                                      | $R_{DSonN}$                                                                                                           |      |      | 4.5  | Ω        | Typical for V <sub>IN</sub> = 5.0V                    |  |  |  |  |

| V <sub>EXT</sub> Rise Time                                       | T <sub>RISE</sub>                                                                                                     |      | 10   | _    | ns       | CL = 100 pF, V <sub>IN</sub> = 5.0V ( <b>Note 1</b> ) |  |  |  |  |

| V <sub>EXT</sub> Fall Time                                       | T <sub>FALL</sub>                                                                                                     |      | 10   | _    | ns       | CL = 100 pF, V <sub>IN</sub> = 5.0V ( <b>Note 1</b> ) |  |  |  |  |

| Input Dimming PWM                                                |                                                                                                                       |      |      |      |          |                                                       |  |  |  |  |

| Dimm Signal Low Voltage                                          | $V_{DIMM\_L}$                                                                                                         |      | _    | 8.0  | V        |                                                       |  |  |  |  |

| Dimm Signal High Voltage                                         | $V_{DIMM\_H}$                                                                                                         | 2    |      | _    | V        |                                                       |  |  |  |  |

| Series MOSFET Driver                                             |                                                                                                                       |      |      |      |          |                                                       |  |  |  |  |

| R <sub>DSon</sub> P-Channel                                      | $R_{DSonP}$                                                                                                           |      | 60   | _    | Ω        |                                                       |  |  |  |  |

| R <sub>DSon</sub> N-Channel                                      | $R_{DSonN}$                                                                                                           |      | 60   | _    | Ω        |                                                       |  |  |  |  |

| Shut-Down                                                        |                                                                                                                       |      |      |      |          |                                                       |  |  |  |  |

| Minimum Low Period for EN to Enter in Shut-Down Mode             | T <sub>MIN_EN</sub>                                                                                                   | 88   | 100  |      | us       |                                                       |  |  |  |  |

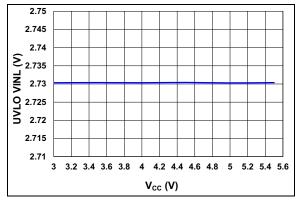

| Overvoltage Protection                                           |                                                                                                                       |      |      |      |          |                                                       |  |  |  |  |

| Overvoltage Protection Threshold                                 | $V_{OVP}$                                                                                                             | 1.19 | 1.23 | 1.3  | V        |                                                       |  |  |  |  |

| Overvoltage Protection<br>Hysteresis                             | V <sub>OVP-HYS</sub>                                                                                                  | _    | 50   | _    | mV       |                                                       |  |  |  |  |

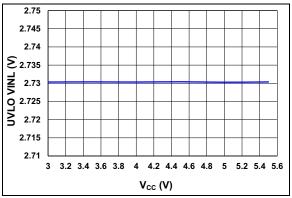

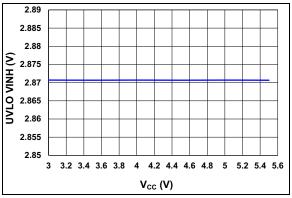

| Undervoltage Lockout                                             |                                                                                                                       |      |      |      |          |                                                       |  |  |  |  |

| Undervoltage Protection Threshold                                | UVLO                                                                                                                  | _    | 3    |      | <b>V</b> |                                                       |  |  |  |  |

| Undervoltage Protection<br>Hysteresis                            | UVLO <sub>HYS</sub>                                                                                                   | _    | 100  | _    | mV       |                                                       |  |  |  |  |

| Thermal Shutdown                                                 | Thermal Shutdown                                                                                                      |      |      |      |          |                                                       |  |  |  |  |

| Thermal Shutdown                                                 | T <sub>SHD</sub>                                                                                                      | _    | 150  | _    | °C       |                                                       |  |  |  |  |

| Thermal Shutdown<br>Hysteresis                                   | T <sub>SHD_HYS</sub>                                                                                                  | _    | 20   | _    | °C       |                                                       |  |  |  |  |

Note 1: Determined by characterization, not production tested.

#### **TEMPERATURE SPECIFICATIONS**

| Parameters                                  | Sym.           | Min. | Тур. | Max. | Units | Conditions   |  |  |

|---------------------------------------------|----------------|------|------|------|-------|--------------|--|--|

| Temperature Ranges                          |                |      |      |      |       |              |  |  |

| Operating Junction Temperature Range        | TJ             | -40  | _    | +125 | °C    | Steady State |  |  |

| Storage Temperature Range                   | T <sub>S</sub> | -65  | _    | +150 | °C    |              |  |  |

| Maximum Junction Temperature                | TJ             | _    | _    | +150 | °C    | Transient    |  |  |

| Thermal Package Resistance                  |                |      |      |      |       |              |  |  |

| Thermal Resistance<br>16L-QFN (3 mm x 3 mm) | $\theta_{JA}$  | _    | 36   | _    | °C/W  |              |  |  |

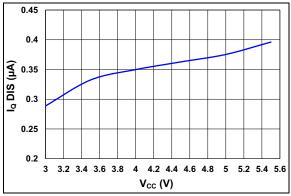

#### 2.0 TYPICAL PERFORMANCE CURVES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

**FIGURE 2-1:** Input Quiescent Disable Current vs. Input Voltage.

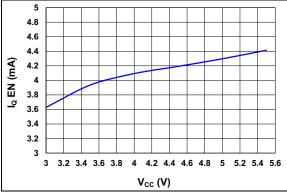

**FIGURE 2-2:** Input Quiescent Enable Current vs. Input Voltage.

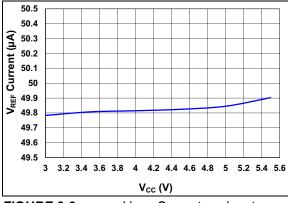

**FIGURE 2-3:** V<sub>REF</sub> Current vs. Input Voltage.

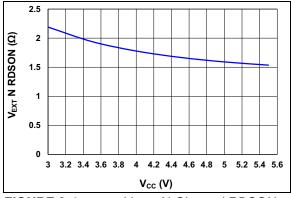

**FIGURE 2-4:**  $V_{EXT}$  N-Channel RDSON vs. Input Voltage.

**FIGURE 2-5:** V<sub>EXT</sub> P-Channel RDSON vs. Input Voltage.

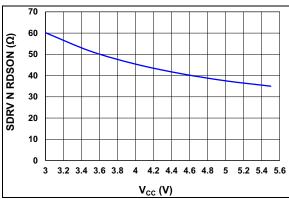

FIGURE 2-6: SRDV N-Channel RDSON vs. Input Voltage.

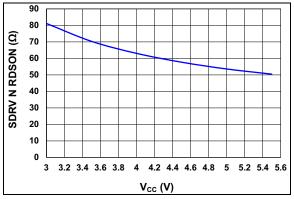

**FIGURE 2-7:** SRDV P-Channel RDSON vs. Input Voltage.

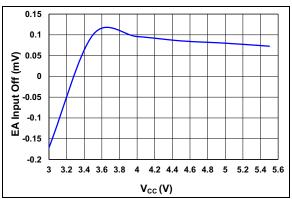

**FIGURE 2-8:** Error Amplifier Input Offset vs. Input Voltage.

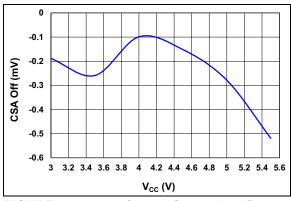

**FIGURE 2-9:** Current Sense Amplifier Offset vs. Input Voltage.

FIGURE 2-10: UVLO VINL Threshold vs. Input Voltage.

FIGURE 2-11: UVLO VINH Threshold vs. Input Voltage.

FIGURE 2-12: OVP VINL Threshold vs. Input Voltage.

**FIGURE 2-13:**  $V_{REF}$  Current vs. Temperature.

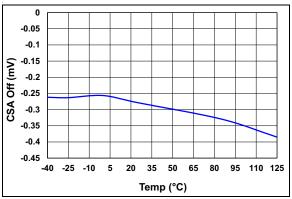

**FIGURE 2-14:** Current Sense Amplifier Offset Voltage vs. Temperature.

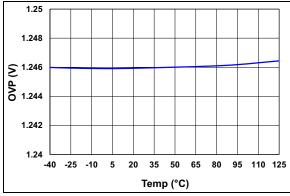

FIGURE 2-15: OVP vs. Temperature.

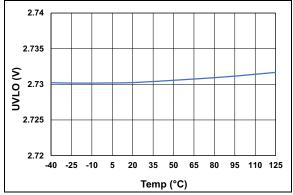

**FIGURE 2-16:** UVLO VINLO Threshold vs. Temperature.

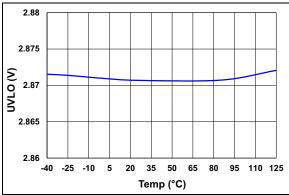

FIGURE 2-17: UVLO VINHI Threshold vs. Temperature.

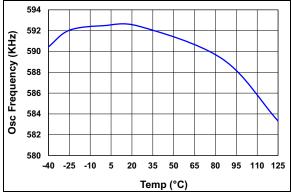

**FIGURE 2-18:** Oscillating Frequency vs. Temperature at 600 kHz.

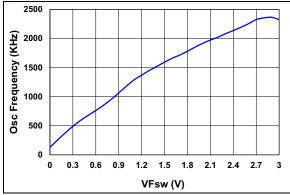

**FIGURE 2-19:** Oscillator Frequency vs.  $F_{sw}$  Pin Voltage ( $V_{CC} = 5V$ , Temperature = 25°C).

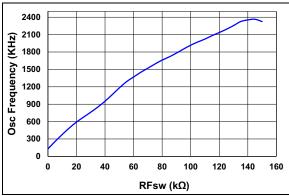

**FIGURE 2-20:** Oscillator Frequency vs.  $RF_{SW}$  ( $V_{CC}$  = 5V, Temperature = 25°C).

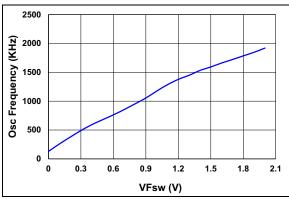

**FIGURE 2-21:** Oscillator Frequency vs.  $F_{sw}$  Pin Voltage ( $V_{CC} = 3V$ , Temperature = 25°C).

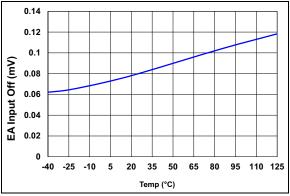

**FIGURE 2-22:** Error Amplifier Input Offset vs. Temperature.

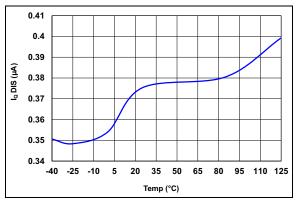

**FIGURE 2-23:** Input Quiescent Disable Current vs. Temperature.

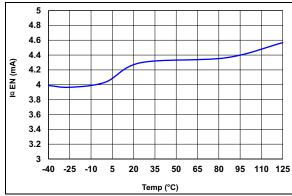

**FIGURE 2-24:** Input Quiescent Enable Current vs. Temperature.

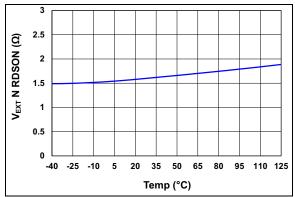

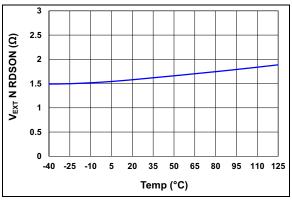

**FIGURE 2-25:**  $V_{EXT}$  N-Channel RDSON vs. Temperature.

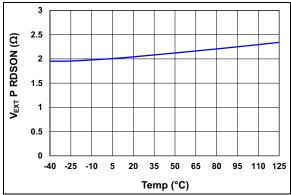

**FIGURE 2-26:**  $V_{EXT}$  P-Channel RDSON vs. Temperature.

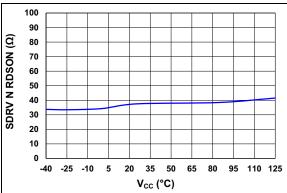

FIGURE 2-27: SRDV N-Channel RDSON vs. Temperature.

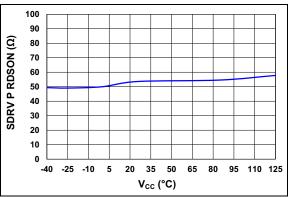

**FIGURE 2-28:** SRDV P-Channel RDSON vs. Temperature.

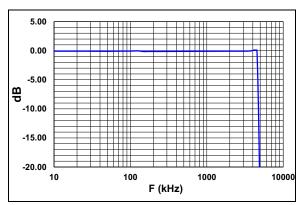

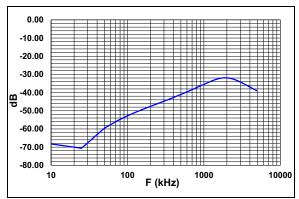

**FIGURE 2-29:** Current Sense Amplifier BW at  $V_{CC} = 5V$ .

**FIGURE 2-30:** Current Sense Amplifier CMRR at  $V_{CC} = 5V$ .

# **MCP1633**

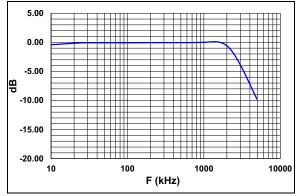

Note: Unless otherwise indicated, V<sub>IN</sub> = 5V, FOSC=600 kHZ,  $C_{IN}$ =0.1  $\mu$ F,  $T_A$ = +25°C.

FIGURE 2-31: Error Amplifier BW at

$V_{CC} = 5V$ .

#### 3.0 PIN DESCRIPTION

The descriptions of the pins are listed in Table 3-1.

TABLE 3-1: PIN FUNCTION TABLE

| Pin Number | Symbol              | Description                                         |  |  |  |

|------------|---------------------|-----------------------------------------------------|--|--|--|

| 1          | F <sub>SW</sub>     | Switching Frequency Set                             |  |  |  |

| 2          | FAULT               | Open-Drain Fault Indicator                          |  |  |  |

| 3          | SS/V <sub>REF</sub> | Soft Start/Reference Voltage Set                    |  |  |  |

| 4          | COMP                | Error Amplifier Output                              |  |  |  |

| 5          | FB                  | Inverting Error Amplifier Input                     |  |  |  |

| 6          | I <sub>OUT</sub>    | Current Sense Operational Amplifier Output          |  |  |  |

| 7          | ISP                 | Current Sense Operational Amplifier Positive Input  |  |  |  |

| 8          | ISN                 | Current Sense Operational Amplifier Negative Input  |  |  |  |

| 9          | CSO                 | Current Sense Offset                                |  |  |  |

| 10         | CS                  | Current Sense Input                                 |  |  |  |

| 11         | $V_{EXT}$           | PWM Output signal                                   |  |  |  |

| 12         | V <sub>CC</sub>     | Input Bias                                          |  |  |  |

| 13         | SDRV                | Series Dimming MOSFET Gate Driver Output            |  |  |  |

| 14         | DIMM                | PWM Dimming Input                                   |  |  |  |

| 15         | OVP                 | Overvoltage Protection Input                        |  |  |  |

| 16         | EN/Sync             | Enable or external synchronization input            |  |  |  |

| _          | EP                  | Exposed Thermal Pad, Analog Ground and Power Ground |  |  |  |

#### 3.1 Switching Frequency Set (F<sub>SW</sub>)

The switching frequency is set by an external resistor connected between the  $F_{SW}$  pin and Ground. The frequency can be adjusted between 200 kHz and 2.2 MHz.

# 3.2 Open-Drain Fault Indicator (FAULT)

The open drain output provides an indication about chip status. This output is active low and is triggered by the input undervoltage, output overvoltage and overtemperature.

# 3.3 Soft Start/Reference Voltage Set (SS/Ref)

This pin is the output of the internal Constant Current Generator (50  $\mu$ A typical). An external resistor must be connected between this pin and GND. The current flowing in this resistor will set the reference voltage. Optionally, a capacitor may also be connected between this pin and GND to set the soft start ramp behavior. This pin may be overdriven by an external voltage source, enabling the reference voltage to be controlled externally.

#### 3.4 Error Amplifier Output (COMP)

COMP is the internal error amplifier output pin. External compensation is connected from COMP to GND for control-loop stabilization.

# 3.5 Inverting Error Amplifier Input (FB)

FB is the internal error amplifier inverting input pin. The output (voltage or current) is sensed and fed back to the FB pin for regulation. Inverting or negative feedback is used.

# 3.6 Current Sense Operational Amplifier Output (I<sub>OUT</sub>)

This pin is connected to the current sense operational amplifier output. It can be connected directly to the FB pin to close the current loop or to a microcontroller to measure the output current.

#### 3.7 Current Sense Operational Amplifier Positive Input (ISP)

This pin is directly connected to the noninverting input of the current sense operational amplifier.

#### 3.8 Current Sense Operational Amplifier Negative Input (ISN)

This pin is directly connected to the inverting input of the current sense operational amplifier.

#### 3.9 Current Sense Offset (CSO)

This pin helps users to better set a peak current limit to protect the application. Internally this pin is connected to current source (20  $\mu$ A typical). By connecting a resistor between this pin and ground, the resistor generates a DC level that is added over current sense signal.

#### 3.10 Current Sense Input (CS)

This is the input for the switch current used for Peak Current Mode control. A blanking period of 30 ns (typical) for CS signal is provided to avoid leading edge spikes that can cause false PWM reset. The normal PWM duty cycle will be terminated when the voltage on the CS pin including the slope compensation ramp and DC offset (CSO) is equal to the output of the error amplifier. For Current Mode operation, the CS pin will control the PWM output on a cycle-by-cycle basis. To avoid the instability of the Peak Current Mode control when the duty cycle is higher than 50%, a slope compensation ramp generator is internally provided. This circuit will add to the CS signal an artificially generated ramp to avoid sub-harmonic oscillations. The amplitude of the slope compensation ramp is adjustable with one external resistor. If this pin is left open, the PWM Controller will operate in Voltage Mode Control. In this mode, the external switching MOSFET transistor is not protected against overcurrent conditions. Certain limitations related to the stability of the closed-loop system must be taken into account by the designer when the part operates in Voltage Mode Control.

#### 3.11 PWM Output Signal (V<sub>FXT</sub>)

$\mbox{\ensuremath{V_{EXT}}}$  is the internal MOSFET driver output pin, used to drive the external transistor.

Connect to gate of external main switching N-channel MOSFET.

#### 3.12 Input Bias (V<sub>CC</sub>)

$V_{CC}$  is the input voltage pin. Connect the input voltage source to the  $V_{CC}$  pin. For normal operation, the voltage on the  $V_{CC}$  pin should range from +3.0V to +5.5V. A bypass capacitor of at least 1  $\mu$ F should be connected between the  $V_{CC}$  pin and the GND pin. This decoupling capacitor must be located as close as possible to the controller package.

# 3.13 Series Dimming MOSFET Gate Driver Output (SDRV)

Series dimming N-channel MOSFET gate driver output. Connect to gate of external N-channel MOSFET to implement series FET PWM dimming and fault disconnect.

#### 3.14 PWM Dimming Input (DIMM)

External PWM dimming input. A direct PWM dimming command can be applied to control the LED current duty cycle and frequency. This PWM generates a signal that controls the  $V_{EXT}$  and SDRV outputs. Setting this pin to logic level low, turns off switching, disconnects the COMP pin, and sets SDRV to "0". Connect to  $V_{CC}$  via 100  $k\Omega$  resistor when not used for PWM dimming.

# 3.15 Overvoltage Protection Input (OVP)

Output voltage input. Connect a resistor divider from output voltage to GND to set output overvoltage protection. The OVP circuits turns off the MOSFET driver (V<sub>EXT</sub> pin set to "0") and the series dimming MOSFET driver (SDRV pin set to "0") when the output voltage reaches the OVP threshold.

# 3.16 Enable or External Synchronization Input (EN/Sync)

When this pin is connected to GND (logic "0") for more than 100  $\mu S$  (typical) the controller will go to DISABLE state. A logic "1" enables the normal operation of the MCP1633. When the device is disabled, the  $V_{EXT}$  output is set. This pin can also accept an external signal for synchronization from an external clock source. The user must provide a correct timing signal for synchronization to ensure consistent operation of PWM controller.

#### 3.17 Exposed Thermal Pad (AGND)

Analog ground and power ground are both connected here. This pad must be connected to PCB ground plane using multiple vias for good functionality.

#### 4.0 DETAILED DESCRIPTION

#### 4.1 Device Overview

The MCP1633 device integrates all the functions needed for designing a compact LED driver based on low-side topologies. The device uses peak current mode control technique to achieve constant output current and fast transient response. The output current level is set by the analog adjust, SS/REF, by using a simple resistor or external voltage to achieve analog dimming. PWM dimming is also supported by specialized internal block using an external PWM signal with 0 to 100%. The integrated low offset, current sense amplifier provides the flexibility due to differential type and external gain set. The output of the current sense amplifier can be used to close the loop and measure the output current. The application's safety is achieved by internal protections UVLO, OVLO and thermal shutdown turning off the converter and disconnecting the load and reporting the status via FAULT pin which is open drain indicator.

#### 4.2 PWM Circuitry

MCP1633 implements a typical Peak Current Mode control loop. The  $V_{EXT}$  output of the MCP1633 device is determined by the output level of the internal high-speed comparator and the level of the internal CLK signal. When the CLK signal level is high, the PWM output ( $V_{EXT}$ ) is forced low, limiting the maximum duty cycle to approximately 90% (typical). When the CLK signal is low, the PWM output is determined by the output level of the internal high-speed comparator. During UVLO and OVLO, the  $V_{EXT}$  pin is held in low state. During overtemperature operation, the  $V_{EXT}$  pin is high-impedance (10 kΩ to ground, typical).

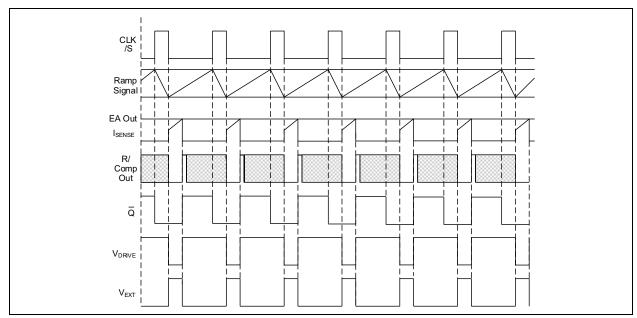

#### 4.3 Normal Cycle-by-Cycle Control

The beginning of a PWM cycle is defined by the internal CLK signal (a transition from high to low). Refer to Figure 4-1 for the detailed timing operation of the MCP1633 PWM controller. For normal operation, the state of the high-speed comparator output (R) is low and the Q output of the latch is low. On the high-to-low transition of the CLK signal, the SR inputs to the highspeed latch are both low and the Q output will remain unchanged (low). The output of the OR gate (VDRIVE) will transition from high to low, turning on the P-Channel drive transistor in the output stage of the PWM. This will change the PWM output (VEXT) from low to high, turning on the power train MOSFET and ramping current in the power train magnetic device. The sensed current in the magnetic device is fed into the CS input, shown as a ramp, and increases linearly until it reaches the same level as the divided down output of the error amplifier at the noninverting input of the high-speed comparator. The comparator output (R) changes state (low to high) and resets the PWM latch. The Q output transition from low to high turns off the V<sub>EXT</sub> drive to the external MOSFET driver, thus terminating the current conduction cycle. The CLK signal will transition from low to high while the V<sub>EXT</sub> pin remains unchanged. If the CS input pin never reaches the same level as the error amplifier output, the low-to-high transition on the CLK signal terminates the current switching cycle. This would be considered as the maximum duty cycle. In either case, while the CLK signal is high, the V<sub>EXT</sub> drive pin is low, turning off the external power train switch. The next switching cycle will start on another transition of the CLK signal from high to low.

FIGURE 4-1: PWM Timing Diagram.

#### 4.4 Error Amplifier/Comparator Current Limit Function

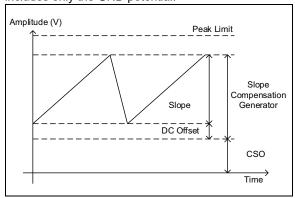

The error amplifier is of transconductance type (OTA) with external compensation network connected between the output (COMP) and the ground. The error amplifier generates an error signal proportional to the difference between the LED current sense feedback voltage and V<sub>RFF</sub> input voltage. The error amplifier output is clamped by a precision 2.7V internal voltage source. The output of the error amplifier is connected to the inverting input of the high-speed comparator. As the output load current demand increases, the error amplifier output increases too, causing the inverting input pin of the high-speed comparator to increase. Eventually, the output of the error amplifier will hit the clamp, limiting the input of the high-speed comparator to 2.7V maximum. Even if the FB input continues to decrease, calling for more current, the inverting input is limited to 2.7V. By limiting the inverting input to 2.7V, the current sense (IP) input is limited to 2.7V minus DC offset value (CSO), thus limiting the current that flows in the main switch. Limiting the maximum peak current in the switch prevents the destruction of the semiconductor device and the saturation of the inductor during overloads. To simplify the design when CS signal is too small so peak limit is far away, there is another feature called I peak offset (CSO). This DC value is added over current sense information to avoid output overloads. Refer to Figure 4-2 and Figure 4-3 for a detailed description. The error amplifier input includes only the GND potential.

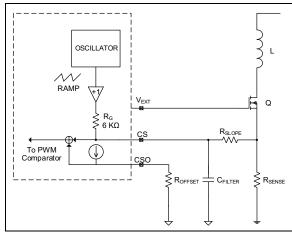

FIGURE 4-2: Slope Compensation Signal.

FIGURE 4-3: Slope Compensation Circuit.

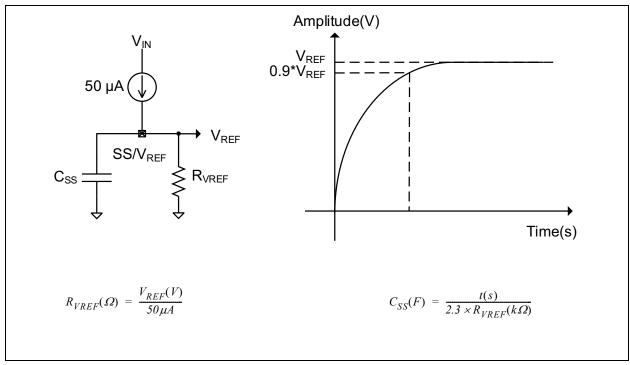

#### 4.5 Reference Voltage Generator

The internal precision constant current generator and an external resistor connected between the V<sub>REF</sub> pin and GND form the reference voltage generator. Refer to Figure 4-4 for details. Optionally, a capacitor (CSS) can be connected in parallel with RV<sub>RFF</sub> to activate the soft start function that will minimize overshoots of the output voltage during start-up. The equations in Figure 4-4 calculate the value of the resistor (RV<sub>REF</sub>) for a given reference voltage and the value of the soft start capacitor (CSS) based on the necessary time to reach 90% of the final value for V<sub>RFF</sub>. An internal circuit of the MCP1633 device will discharge the capacitor during the shutdown period. This capacitor must be of good quality, with low leakage currents, in order to avoid any errors that can affect the reference voltage. The reference voltage should not exceed 80% of the bias input voltage (V<sub>IN</sub> pin) in order to avoid any errors that affect the internal constant current generator. An external low-noise, low-impedance source can be used to overdrive the V<sub>REF</sub> pin in order to control the reference voltage. In this case, the resistor/capacitor group connected to GND is not necessary, and the soft start profile must be controlled by the external reference voltage generator.

FIGURE 4-4: Reference Voltage Generator.

#### 4.6 Internal Oscillator

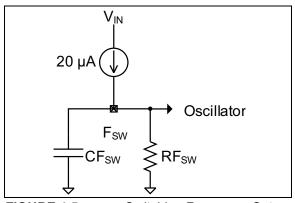

The MCP1633 PWM controller provides programmable switching frequency with an external resistor connected between the  $F_{SW}$  pin and GND. To set a desired frequency, the resistor value can be calculated with the Equation 1 below or using the graph in Figure 2-20. A small capacitor in parallel with RF $_{SW}$  is recommended.

#### **EQUATION 1: RESISTOR VALUE.**

$$RF_{SW} = 2E - 05 \times F_{SW^2} + 0.0234 \times F_{sw} - 0.026$$

FIGURE 4-5: Switching Frequency Set.

The internal oscillator can be synchronized by an external clock pulse to EN/Sync pin. It is recommended that the frequency of the external synchronization pulse is within  $\pm 20\%$  of the internal oscillator frequency programmed by the  $F_{SW}$  resistor. If the external synchronization clock is lost, then the internal oscillator takes control of the switching rate based on the  $F_{SW}$  resistor to maintain similar operating conditions.  $F_{SW}$  pin cannot be left floating.

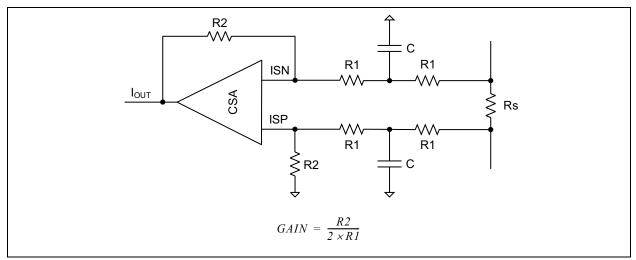

#### 4.7 Current Sense Amplifier

The internal current sense amplifier measures LED current based on the differential voltage drop between the ISP and ISN inputs over a common mode range of 0V to 5V. Inputs and output of the current sense amplifier are directly connected to pins (ISP, ISN, I<sub>OUT</sub>) to set the gain of the amplifier by external resistors providing high flexibility in designing applications. The output of current sense amplifier should be connected to FB pin to close the loop and regulate the output current. An optional low-pass filter can be used to filter the effects of output current ripple and switching spikes. Figure 4-6 shows an example of a filter.

FIGURE 4-6: Current Sense Amplifier Gain Set.

#### 4.8 PWM Dimming

MCP1633 incorporates a high-performance dimming mechanism. External PWM signal is used to modulate the output current. Internally this signal in low state disables the main driver (V<sub>EXT</sub>), disconnects the output of the error amplifier, and disconnects the load (SDRV set low) to maintain the steady state condition at the next transition. When DIMM pin is high state the driver is enabled, output of error amplifier is reconnected and SDRV pin is set high. When dimming is not required, connect the DIMM pin to the V<sub>CC</sub> pin. An internal pulldown resistor sets the input to logic-low and disables the device when the pin is floating. The SDRV pin is the output of a secondary driver which controls an NMOS transistor for dimming and is capable of sinking and sourcing up to 50 mA of peak current. To ensure that the applied dimming-pulse duration matches the effective dimming-pulse duration, it is recommended to synchronize the dimming pulses with the switching clock of the controller.

#### 4.9 Undervoltage Lockout (UVLO)

When the input voltage ( $V_{\rm IN}$ ) is lower than the UVLO threshold, the  $V_{\rm EXT}$  is held in low state. This will ensure that, if the voltage is not adequate to power the MCP1633 device, the main power supply switch will be held in off state. In order to prevent oscillations when the input voltage is near the UVLO threshold, the UVLO circuit offers 100 mV (typical) hysteresis. Typically, the MCP1633 device will not start until the input voltage at  $V_{\rm IN}$  is between 2.8V and 2.9V (typical).

#### 4.10 Overtemperature Protection

To protect the  $V_{EXT}$  output if shorted to  $V_{IN}$  or GND, the  $V_{EXT}$  output of the MCP1633 device will be high-impedance if the junction temperature is above the thermal shutdown threshold. An internal 10 k $\Omega$  pull-down

resistor is connected from  $V_{EXT}$  to ground to provide some pull-down during overtemperature conditions. The protection is set to +150°C (typical), with a hysteresis of +20°C.

#### 4.11 Overvoltage Protection

The OVP pin is a comparator used to prevent the power system from being damaged when the load is disconnected. By comparing the divided down power train output voltage with a 1.23V internal reference voltage, the MCP1633  $V_{\text{EXT}}$  output switching is interrupted and load disconnected when the output voltage is above a pre-set value. This limits the output voltage of the power train and the low comparator's hysteresis will operate as a ripple regulator.

#### 5.0 APPLICATION CIRCUITS

#### 5.1 Typical Applications

The MCP1633 PWM controller can be used for applications that require low-side MOSFET control, such as Boost, Buck-Boost, Flyback, SEPIC or CUK converters. By using an external high-side MOSFET driver (e.g., MCP14628), the MCP1633 device is able to control the buck converter. The MCP1633 PWM controller can be easily interfaced with a microcontroller in order to develop intelligent solutions for LED drivers.

Figure 5-1 depicts the typical boost converter controlled by the MCP1633. If the converter must operate with input voltages higher than 5.5V, a linear voltage regulator can be used to bias the MCP1633 controller. The Peak Current Mode control used in this case will ensure consistent performance over a wide range of operating conditions. The MOSFET is protected against overcurrent by internally limiting the maximum voltage at the output of the error amplifier of the controller. If the voltage applied on the CS pin exceeds the set threshold, the MCP1633 device will reduce the duty cycle in order to prevent overcurrent in MOSFET.

**Note:** The boost converter is not protected against the output short circuit.

FIGURE 5-1: MCP1633 Typical Boost Converter.

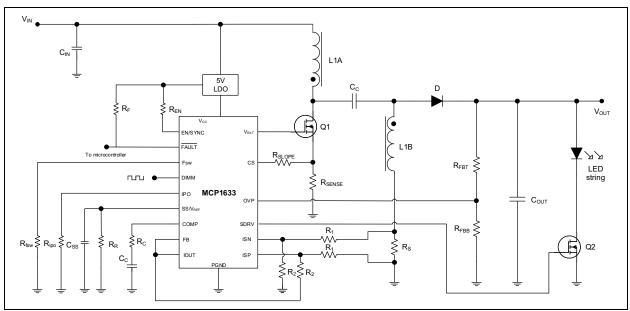

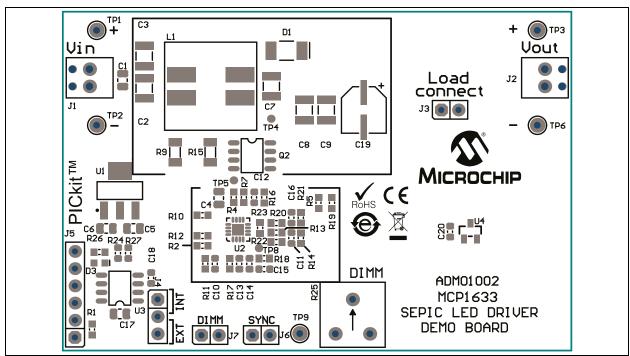

The single-ended primary inductor converter (SEPIC) used to drive an LED string is presented in Figure 5-2. This converter offers buck-boost functionality and is protected against the output short circuit. The inductors can share the same magnetic core (coupled inductors); in this case, the mutual inductance doubles the value of the inductor, reducing the ripple of the current.

FIGURE 5-2: MCP1633 Typical SEPIC Converter — Demo Board ADM01002.

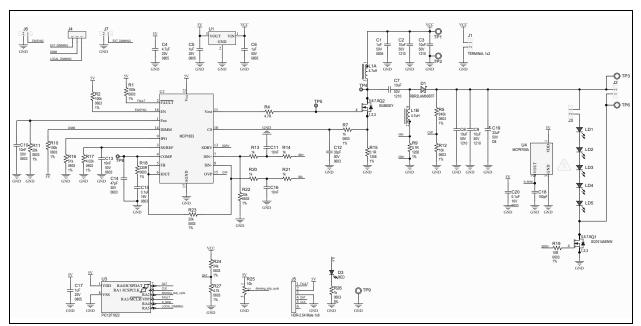

FIGURE 5-3: MCP1633 SEPIC LED Driver Schematic — Demo Board ADM01002.

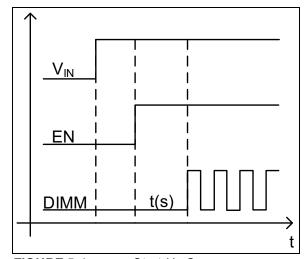

#### 5.2 Recommended Start-Up Sequence

In order to reduce the start-up stress, it is recommended to use the sequence below (Figure 5-4). Depending of the capacitor placed on the  $F_{SW}$  pin, the necessary delay for DIMM signal can be calculated with Equation 2.

# EQUATION 2: NECESSARY TIME TO REACH 90% OF THE FINAL VALUE FOR V<sub>FSW</sub>

$$t(s) = c(nf) \times r(k\Omega) \times 2.3 \times 10^{-6}$$

FIGURE 5-4: Start-Up Sequence.

#### 5.3 Layout Recommendations

Good printed circuit board layout techniques are important to any switching circuitry and switching power supplies are no different. Here are the guidelines for the PCB layout:

- The exposed pad of the MCP1633 QFN case is the only connection to the internal device ground. Connect this pad directly to the board ground plane.

- Place at least four vias in the exposed pad land to ensure good ground connection and remove heat from the device.

- Use separate grounds for power and signal paths.

Keep high current paths away from sensitive components and nodes (e.g., feedback and compensation network components).

- Route the ISP and ISN together with Kelvin connections to the current sense resistor with traces as short as possible and use noise filters.

- Use short and strong connection between V<sub>EXT</sub> and gate pin of the MOSFET.

- Locate the V<sub>REF</sub>, CSO, F<sub>SW</sub>, Comp, CSA gain components near the MCP1633 case.

- Use separate connections to close each loop directly to ground plane (V<sub>REF</sub>, CSO, F<sub>SW</sub>, Comp)

- Four-layer PCBs are highly recommended to obtain optimum results regarding noise/EMI. Use an internal layer as ground plane.

- Minimize the area of the high-current loops. Use copper planes or large traces for high-current connections in order to minimize the parasitic inductances.

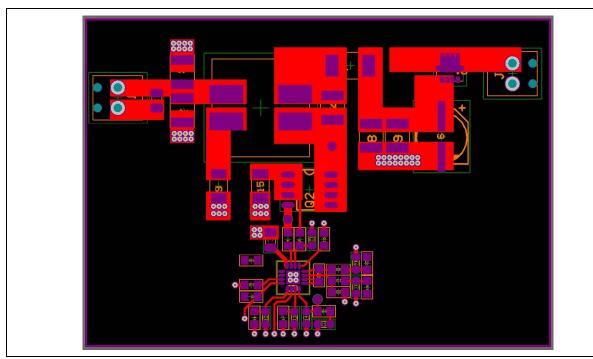

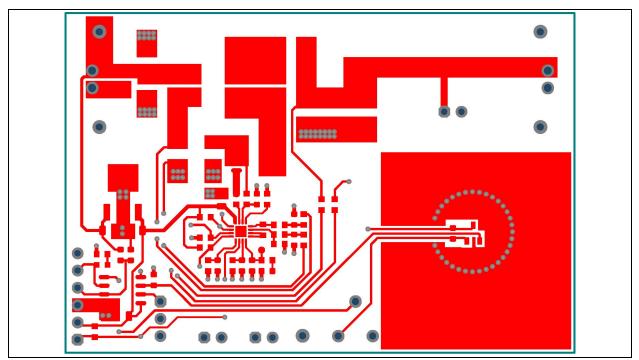

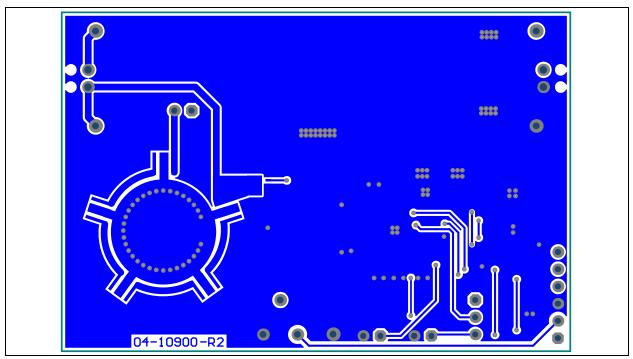

FIGURE 5-5: MCP1633 SEPIC LED Driver Demo Board ADM01002.

FIGURE 5-6: MCP1633 Demo Board ADM01002 — Top Copper.

FIGURE 5-7: MCP1633 Demo Board ADM01002 — Bottom Copper.

FIGURE 5-8: MCP1633 Demo Board ADM01002 — Top Silk.

#### 6.0 PACKAGING INFORMATION

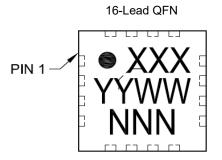

#### 6.1 Package Marking Information

Legend: XX...X Customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

By-free JEDEC® designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (e3)

can be found on the outer packaging for this package.

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

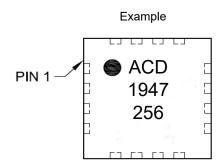

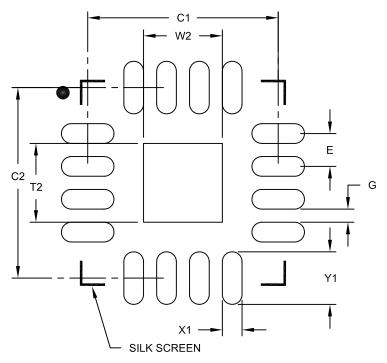

#### 16-Lead Plastic Quad Flat, No Lead Package (MG) - 3x3x0.9 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-142A Sheet 1 of 2

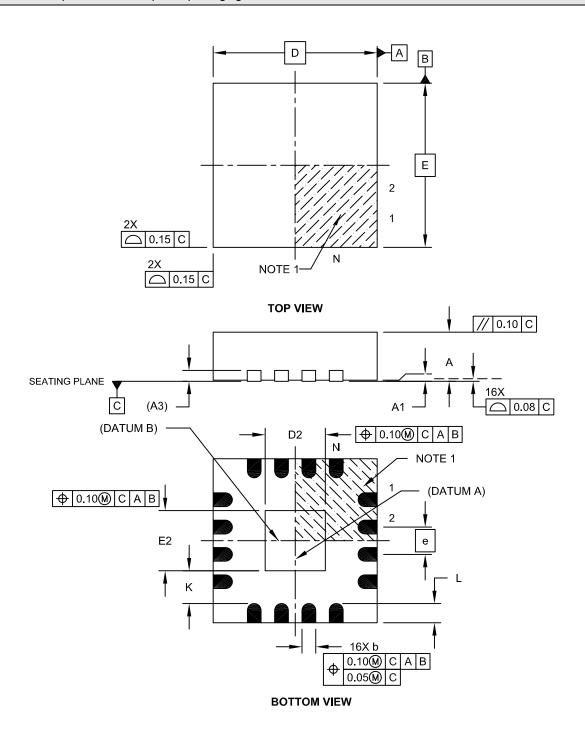

#### 16-Lead Plastic Quad Flat, No Lead Package (MG) - 3x3x0.9 mm Body [QFN]

For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units  | N              | <b>II</b> LLIMETER | S    |  |

|------------------------|--------|----------------|--------------------|------|--|

| Dimension              | Limits | MIN            | NOM                | MAX  |  |

| Number of Pins         | N      |                | 16                 |      |  |

| Pitch                  | е      |                | 0.50 BSC           |      |  |

| Overall Height         | Α      | 0.80           | 0.85               | 0.90 |  |

| Standoff               | A1     | 0.00           | 0.02               | 0.05 |  |

| Contact Thickness      | A3     | 0.20 REF       |                    |      |  |

| Overall Width          | Е      | 3.00 BSC       |                    |      |  |

| Exposed Pad Width      | E2     | 1.00 1.10 1.50 |                    |      |  |

| Overall Length         | О      | 3.00 BSC       |                    |      |  |

| Exposed Pad Length     | D2     | 1.00           | 1.10               | 1.50 |  |

| Contact Width          | р      | 0.18           | 0.25               | 0.30 |  |

| Contact Length         | L      | 0.25           | 0.35               | 0.45 |  |

| Contact-to-Exposed Pad | K      | 0.20           | -                  | -    |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-142A Sheet 2 of 2

### 16-Lead Plastic Quad Flat, No Lead Package (MG) – 3x3x0.9 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                            | MILLIMETERS |          |      |      |  |

|----------------------------|-------------|----------|------|------|--|

| Dimension                  | Limits      | MIN      | NOM  | MAX  |  |

| Contact Pitch              | Е           | 0.50 BSC |      |      |  |

| Optional Center Pad Width  | W2          |          |      | 1.20 |  |

| Optional Center Pad Length | T2          |          |      | 1.20 |  |

| Contact Pad Spacing        | C1          |          | 2.90 |      |  |

| Contact Pad Spacing        | C2          |          | 2.90 |      |  |

| Contact Pad Width (X16)    | X1          |          |      | 0.30 |  |

| Contact Pad Length (X16)   | Y1          |          |      | 0.80 |  |

| Distance Between Pads      | G           | 0.20     |      | ·    |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2142A

# **MCP1633**

NOTES:

#### APPENDIX A: REVISION HISTORY

#### Revision B (May 2021)

The following is the list of modifications:

- Added information about the automotive qualification status of the device in the Features section.

- Added note about the exposed pad in the Package Type image.

- Added Note 1 about human body model in Section 1.0, Electrical Characteristics.

- Updated Figure 5-1, Figure 5-2 and Figure 5-3 in Section 5.0, Application Circuits.

- Added Figure 5-6, Figure 5-7 and Figure 5-8 to Section 5.3, Layout Recommendations.

- Updated the Product Identification System section with automotive qualified devices.

- Corrected the device's categorization from High-Speed PWM Controller to Low-Side PWM Controller with LED Dimming Capability in the Product Identification System section.

- · Deleted page 29 (Notes page).

- Minor typographical and layout changes throughout the text.

#### **Revision A (January 2020)**

· Initial release of this document.

NOTES:

### PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.                   | [X] <sup>(1)</sup>      | <u>-X</u>                                           | <u>/XX</u> | xxx           | Ex | amples:                                          |                                                                                                                                                                                            |

|----------------------------|-------------------------|-----------------------------------------------------|------------|---------------|----|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device 1                   | Fape and Reel<br>Option | Temperature<br>Range                                | Package    | Qualification | a) | MCP1633-E/MG:                                    | Low-Side PWM Controller with<br>LED Dimming Capability,<br>Extended Temperature Range,<br>16-Lead QFN Package                                                                              |

| Device:                    |                         | 8: Low-Side PWM C<br>Capability<br>Standard Packagi |            |               | b) | MCP1633T-E/MG:                                   | Low-Side PWM Controller with<br>LED Dimming Capability,<br>Tape and Reel,<br>Extended Temperature Range,<br>16-Lead QFN Package                                                            |

| Option: Temperature Range: |                         | Tape and Reel <sup>(1)</sup> Extended: –40°C to     | o+125°C    | ,             | c) | MCP1633-E/MGVAO:                                 | Low-Side PWM Controller with<br>LED Dimming Capability,<br>Extended Temperature Range,<br>16-Lead QFN Package,<br>Automotive Qualified                                                     |

| Package:                   |                         | 16-Lead Plastic Qu<br>3 x 3 0.9 mm Body             |            | ead Package   | d) | MCP1633T-E/MGVAO:                                | Low-Side PWM Controller with<br>LED Dimming Capability,<br>Tape and Reel,<br>Extended Temperature Range,                                                                                   |

| Qualification:             |                         | Standard Qualifica<br>AEC-Q100 Autom                |            | ation         |    |                                                  | 16-Lead QFN Package,<br>Automotive Qualified                                                                                                                                               |

|                            |                         |                                                     |            |               | 1  | catalog part n<br>used for orde<br>the device pa | eel identifier only appears in the umber description. This identifier is ring purposes and is not printed on ckage. Check with your Microchip for package availability with the el option. |

# **MCP1633**

NOTES:

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specifications contained in their particular Microchip Data Sheet.

- · Microchip believes that its family of products is secure when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods being used in attempts to breach the code protection features of the Microchip devices. We believe that these methods require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Attempts to breach these code protection features, most likely, cannot be accomplished without violating Microchip's intellectual property rights.

- Microchip is willing to work with any customer who is concerned about the integrity of its code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of its code. Code protection does not

mean that we are guaranteeing the product is "unbreakable." Code protection is constantly evolving. We at Microchip are

committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection

feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or

other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication is provided for the sole purpose of designing with and using Microchip products. Information regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications.

THIS INFORMATION IS PROVIDED BY MICROCHIP "AS IS". MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION INCLUDING BUT NOT LIMITED TO ANY IMPLIED WARRANTIES OF NON-INFRINGEMENT, MERCHANTABILITY, AND FITNESS FOR A PARTICULAR PURPOSE OR WARRANTIES RELATED TO ITS CONDITION, QUALITY, OR PERFORMANCE.

IN NO EVENT WILL MICROCHIP BE LIABLE FOR ANY INDI-RECT, SPECIAL, PUNITIVE, INCIDENTAL OR CONSEQUEN-TIAL LOSS, DAMAGE, COST OR EXPENSE OF ANY KIND WHATSOEVER RELATED TO THE INFORMATION OR ITS USE, HOWEVER CAUSED, EVEN IF MICROCHIP HAS BEEN ADVISED OF THE POSSIBILITY OR THE DAMAGES ARE FORESEEABLE. TO THE FULLEST EXTENT ALLOWED BY LAW, MICROCHIP'S TOTAL LIABILITY ON ALL CLAIMS IN ANY WAY RELATED TO THE INFORMATION OR ITS USE WILL NOT EXCEED THE AMOUNT OF FEES, IF ANY, THAT YOU HAVE PAID DIRECTLY TO MICROCHIP FOR THE INFORMATION. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

### Trademarks The Microchip

The Microchip name and logo, the Microchip logo, Adaptec, AnyRate, AVR, AVR logo, AVR Freaks, BesTime, BitCloud, chipKIT, chipKIT logo, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, HELDO, IGLOO, JukeBlox, KeeLoq, Kleer, LANCheck, LinkMD, maXStylus, maXTouch, MediaLB, megaAVR, Microsemi, Microsemi logo, MOST, MOST logo, MPLAB, OptoLyzer, PackeTime, PIC, picoPower, PICSTART, PIC32 logo, PolarFire, Prochip Designer, QTouch, SAM-BA, SenGenuity, SpyNIC, SST, SST Logo, SuperFlash, Symmetricom, SyncServer, Tachyon, TempTrackr, TimeSource, tinyAVR, UNI/O, Vectron, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

APT, ClockWorks, The Embedded Control Solutions Company, EtherSynch, FlashTec, Hyper Speed Control, HyperLight Load, IntelliMOS, Libero, motorBench, mTouch, Powermite 3, Precision Edge, ProASIC, ProASIC Plus, ProASIC Plus logo, Quiet-Wire, SmartFusion, SyncWorld, Temux, TimeCesium, TimeHub, TimePictra, TimeProvider, Vite, WinPath, and ZL are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, AnyIn, AnyOut, BlueSky, BodyCom, CodeGuard, CryptoAuthentication, CryptoAutomotive, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, INICnet, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, memBrain, Mindi, MiWi, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PowerSmart, PureSilicon, QMatrix, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

The Adaptec logo, Frequency on Demand, Silicon Storage Technology, and Symmcom are registered trademarks of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2020, Microchip Technology Incorporated, All Rights Reserved.

ISBN: 978-1-5224-8309-0

For information regarding Microchip's Quality Management Systems, please visit www.microchip.com/quality.

### Worldwide Sales and Service

#### **AMERICAS**

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200

Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/ support

Web Address:

www.microchip.com

Atlanta Duluth, GA

Tel: 678-957-9614 Fax: 678-957-1455

**Austin, TX** Tel: 512-257-3370

Boston

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Dallas

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI

Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis

Noblesville, IN

Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

Raleigh, NC Tel: 919-844-7510

New York, NY Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110 Tel: 408-436-4270

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Australia - Sydney Tel: 61-2-9868-6733

**China - Beijing** Tel: 86-10-8569-7000

China - Chengdu Tel: 86-28-8665-5511

China - Chongqing Tel: 86-23-8980-9588

**China - Dongguan** Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

China - Hangzhou Tel: 86-571-8792-8115

China - Hong Kong SAR Tel: 852-2943-5100

China - Nanjing Tel: 86-25-8473-2460

China - Qingdao Tel: 86-532-8502-7355

China - Shanghai Tel: 86-21-3326-8000

**China - Shenyang** Tel: 86-24-2334-2829

**China - Shenzhen** Tel: 86-755-8864-2200

China - Suzhou

Tel: 86-186-6233-1526 China - Wuhan

Tel: 86-27-5980-5300

China - Xian Tel: 86-29-8833-7252

**China - Xiamen** Tel: 86-592-2388138

China - Zhuhai Tel: 86-756-3210040

#### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444

India - New Delhi Tel: 91-11-4160-8631

India - Pune Tel: 91-20-4121-0141

**Japan - Osaka** Tel: 81-6-6152-7160

Japan - Tokyo

Tel: 81-3-6880- 3770 Korea - Daegu

Tel: 82-53-744-4301

Korea - Seoul Tel: 82-2-554-7200

Malaysia - Kuala Lumpur Tel: 60-3-7651-7906

Malaysia - Penang Tel: 60-4-227-8870

Philippines - Manila Tel: 63-2-634-9065

**Singapore** Tel: 65-6334-8870

**Taiwan - Hsin Chu** Tel: 886-3-577-8366

Taiwan - Kaohsiung Tel: 886-7-213-7830

**Taiwan - Taipei** Tel: 886-2-2508-8600

Thailand - Bangkok Tel: 66-2-694-1351

Vietnam - Ho Chi Minh Tel: 84-28-5448-2100

#### **EUROPE**

**Austria - Wels** Tel: 43-7242-2244-39

Fax: 43-7242-2244-393

Denmark - Copenhagen

Tel: 45-4485-5910

Fax: 45-4485-2829

**Finland - Espoo** Tel: 358-9-4520-820

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Garching Tel: 49-8931-9700

**Germany - Haan** Tel: 49-2129-3766400

Germany - Heilbronn Tel: 49-7131-72400

Germany - Karlsruhe Tel: 49-721-625370

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Germany - Rosenheim Tel: 49-8031-354-560

Israel - Ra'anana Tel: 972-9-744-7705

Italy - Milan Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Padova Tel: 39-049-7625286

**Netherlands - Drunen** Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim Tel: 47-7288-4388

**Poland - Warsaw** Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**Sweden - Gothenberg** Tel: 46-31-704-60-40

**Sweden - Stockholm** Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820