# **ZD25Q16C**

# Ultra Low Power, 16M-bit Serial Multi I/O Flash Memory Datasheet

### **Performance Highlight**

- > Wide supply range from 2.3V to 3.6V for Read, Erase and Program

- > Ultra-Low Power consumption for Read, Erase and Program

- > x1, x2 and x4 Multi I/O, QPI Support

- > High reliability with 100K cycling endurance and 20-year data retention

- > Page/Sector/Block Erase

- > Fast Chip Erase time 10ms

**ZETTA Technology, Inc.**

## Contents

| 1. | OVE  | RVIEW                                                   | 4  |

|----|------|---------------------------------------------------------|----|

|    | 1.1  | Performance                                             | 4  |

|    | 1.2  | Pin Definition                                          | 5  |

| 2. | DESC | CRIPTION                                                | 5  |

|    | 2.1  | Block Diagram                                           | 5  |

|    | 2.2  | Memory Organization                                     | 6  |

| 3. | DEVI | CE OPERATION                                            | 7  |

|    | 3.1  | Mode0 and Mode3                                         | 7  |

|    | 3.2  | Status Register (SR)                                    | 9  |

|    | 3.3  | Configuration Register (CR)                             | 11 |

|    | 3.4  | Data Protection                                         | 12 |

| 4. | COM  | MAND DESCRIPTION                                        | 14 |

|    | 4.1  | Write Enable (WREN) (06H)                               | 19 |

|    | 4.2  | Write Disable (WRDI) (04H)                              | 20 |

|    | 4.3  | Write Enable for Volatile Status Register (50H)         | 21 |

|    | 4.4  | Read Status Register (RDSR) (05H, 35H)                  | 22 |

|    | 4.5  | Active Status Interrupt (ASI) (25H)                     | 23 |

|    | 4.6  | Write Status Register (WRSR) (01H or 31H)               | 23 |

|    | 4.7  | Read Data Bytes (READ) (03H)                            | 25 |

|    | 4.8  | Read Data Bytes at Higher Speed (FAST_READ) (0BH)       | 25 |

|    | 4.9  | Dual Output Fast Read (DREAD) (3BH)                     | 27 |

|    | 4.10 | Dual I/O Fast Read (2READ) (BBH)                        | 27 |

|    | 4.11 | Quad Output Fast Read (QREAD) (6BH)                     | 29 |

|    | 4.12 | Quad I/O Fast Read (4READ) (EBH)                        | 31 |

|    | 4.13 | Quad I/O Word Read (E7H)                                | 32 |

|    | 4.14 | Quad I/O Octal Word Read (E3H)                          | 34 |

|    | 4.15 | Set Read Parameters (C0H)                               | 35 |

|    | 4.16 | Burst Read with Wrap (0CH)                              |    |

|    | 4.17 | Set Burst with Wrap (77H)                               |    |

|    | 4.18 | Page Erase (PE) (81H)                                   |    |

|    | 4.19 | Sector Erase (SE) (20H)                                 |    |

|    | 4.20 | Half Block Erase (HBE) (52H)                            | 40 |

|    | 4.21 | Block Erase (BE) (D8H)                                  |    |

|    | 4.22 | Chip Erase (CE) (60H or C7H)                            |    |

|    | 4.23 | Page Program (PP) (02H)                                 |    |

|    | 4.24 | Page Write (PW) (A5H)                                   |    |

|    | 4.25 | Dual Input Page Program (DPP) (A2H)                     |    |

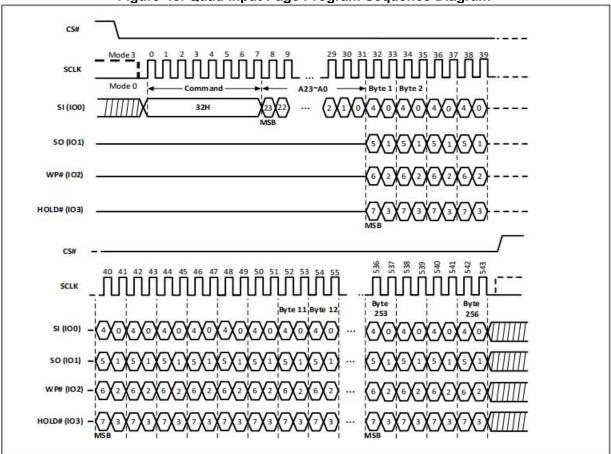

|    | 4.26 | Quad Input Page Program (QPP) (32H)                     |    |

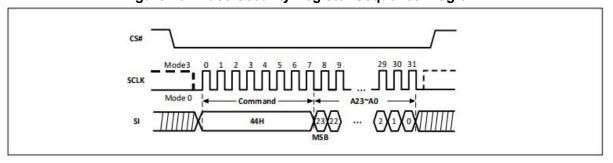

|    | 4.27 | Erase Security Register (ERSCUR) (44H)                  |    |

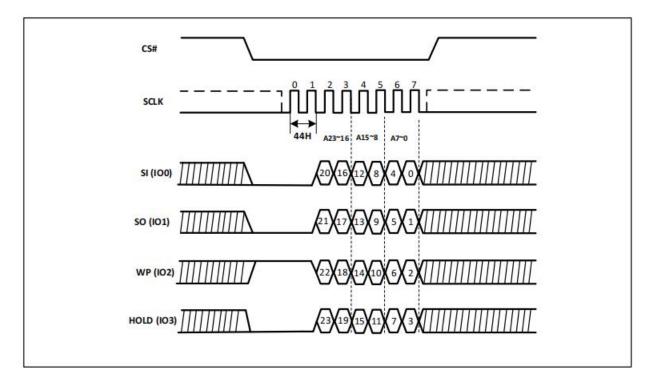

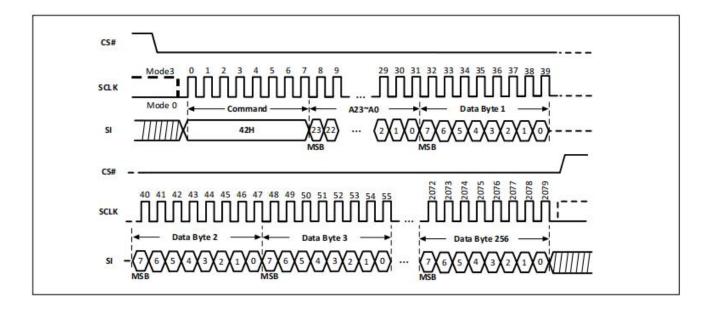

|    | 4.28 | Program Security Register (PRSCUR) (42H)                |    |

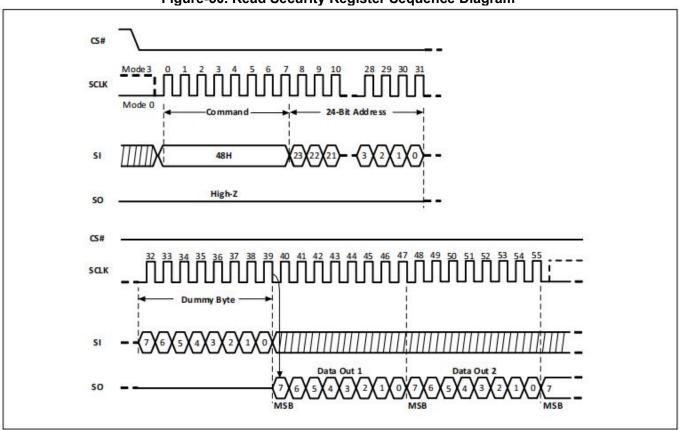

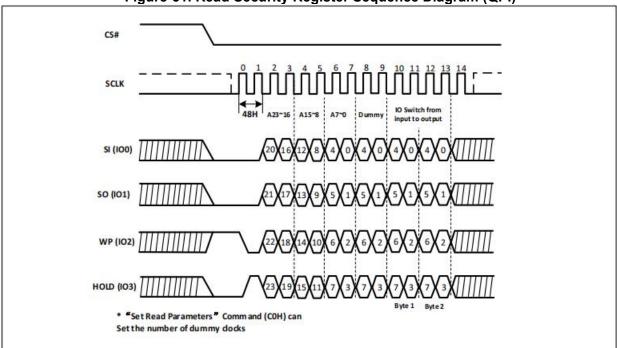

|    | 4.29 | Read Security Register (RDSCUR) (48H)                   |    |

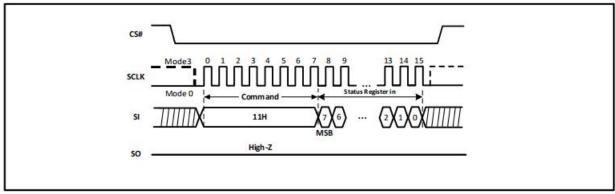

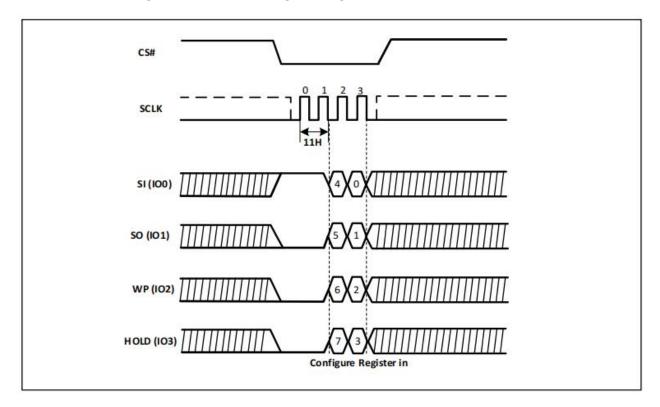

|    | 4.30 | Write Configure Register (WRCR)(11H)                    |    |

|    | 4.31 | Read Configure Register (RDCR) (45H or 15H in SPI Mode) |    |

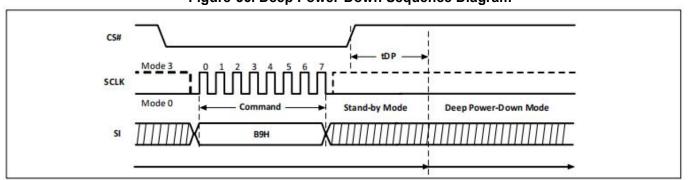

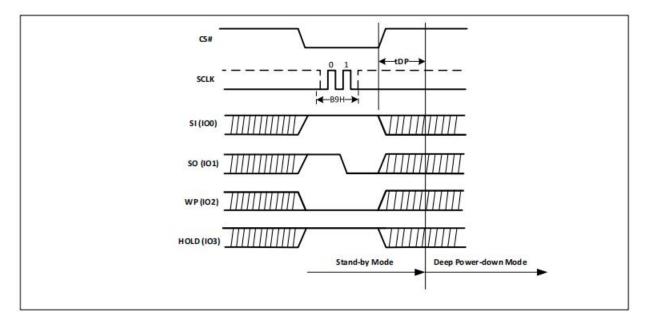

|    | 4.32 | Deep Power-Down (DP) (B9H)                              |    |

|    |      | =                                                       |    |

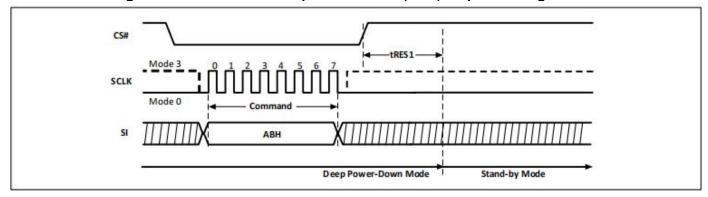

|    | 4.33 | Release form Deep Power-Down (RDP), Read Electronic Signature (RES) (ABH) | 56 |

|----|------|---------------------------------------------------------------------------|----|

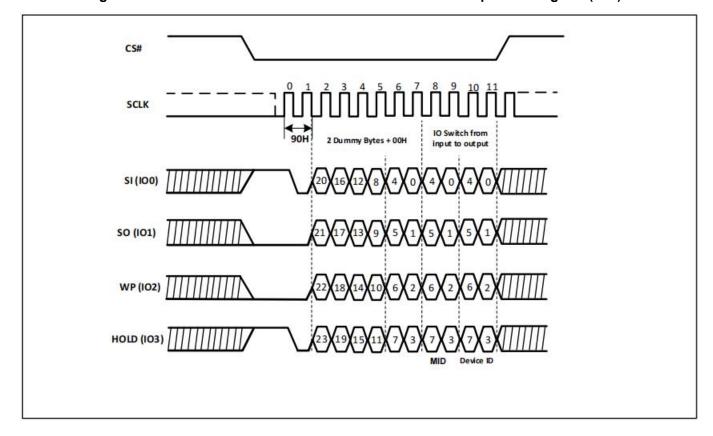

|    | 4.34 | Read Electronic Manufacturer ID & Device ID (REMS) (90H)                  | 58 |

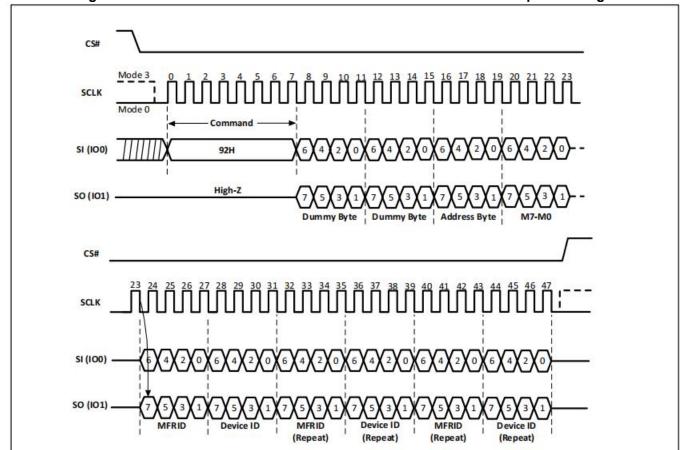

|    | 4.35 | Dual I/O Read Electronic Manufacturer ID & Device ID (DREMS) (92H)        | 60 |

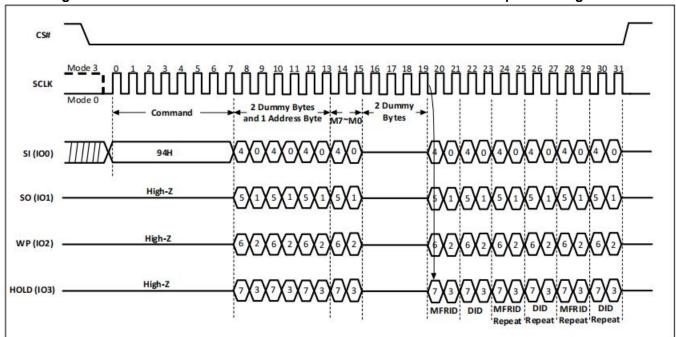

|    | 4.36 | Quad I/O Read Electronic Manufacturer ID & Device ID (QREMS) (94H)        |    |

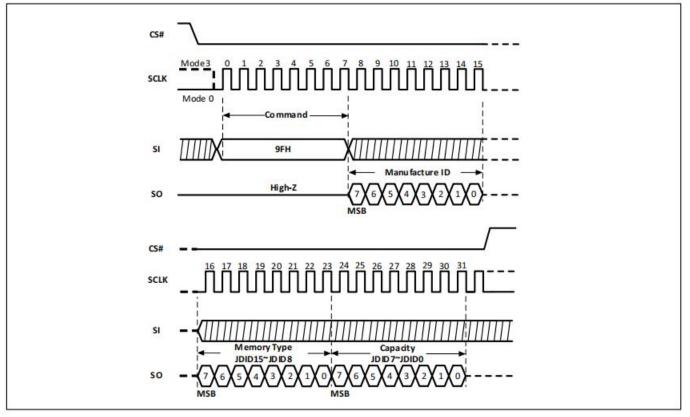

|    | 4.37 | Read Identification (RDID) (9FH)                                          | 61 |

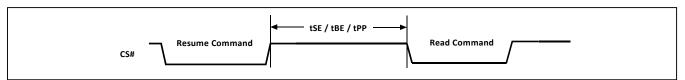

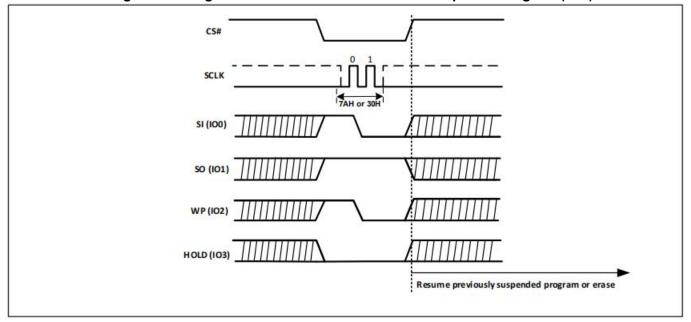

|    | 4.38 | Program/Erase Suspend/Resume (75H)                                        | 63 |

|    | 4.39 | Program Resume and Erase Resume (7AH)                                     | 65 |

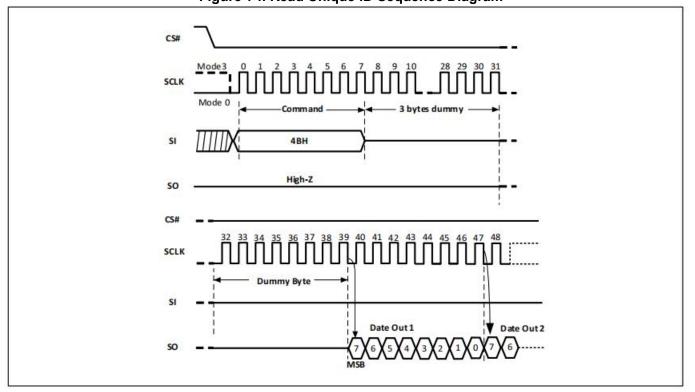

|    | 4.40 | Read Unique ID (RUID) (4BH)                                               | 66 |

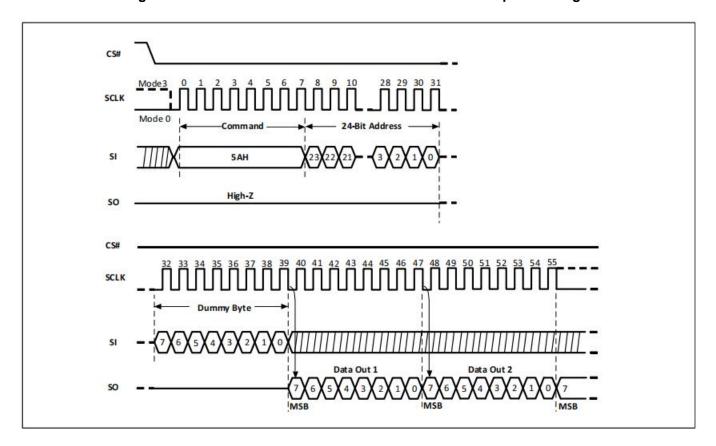

|    | 4.41 | Read SFDP Mode (RDSFDP) (5AH)                                             | 67 |

|    | 4.42 | Continuous Read Mode Reset (CRMR) (FFH)                                   | 73 |

|    | 4.43 | Enable QPI (38H)                                                          | 73 |

|    | 4.44 | Disable QPI (FFH)                                                         | 74 |

|    | 4.45 | No Operation (NOP)                                                        | 74 |

|    | 4.46 | Reset Enable (RSTEN) (66H) and Reset (RST) (99H)                          | 75 |

| 5. | ELEC | CTRICAL SPECIFICATIONS                                                    | 76 |

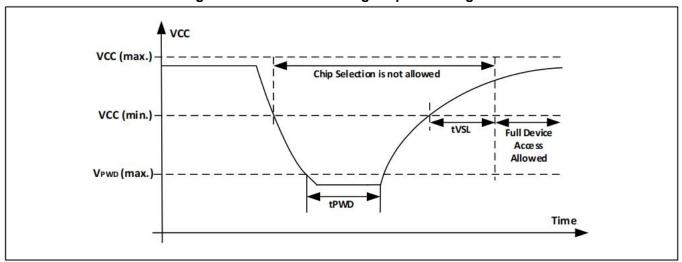

|    | 5.1  | Power-On Timing                                                           | 76 |

|    | 5.2  | Initial Delivery State                                                    | 76 |

|    | 5.3  | Absolute Maximum Ratings                                                  | 76 |

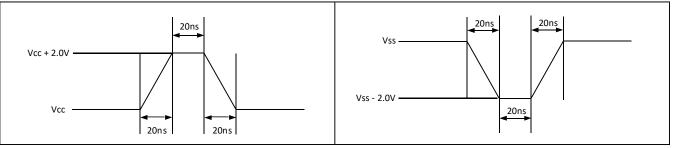

|    | 5.4  | AC Measurement Conditions                                                 | 77 |

|    | 5.5  | DC Characteristics                                                        | 77 |

|    | 5.6  | AC Characteristics                                                        | 78 |

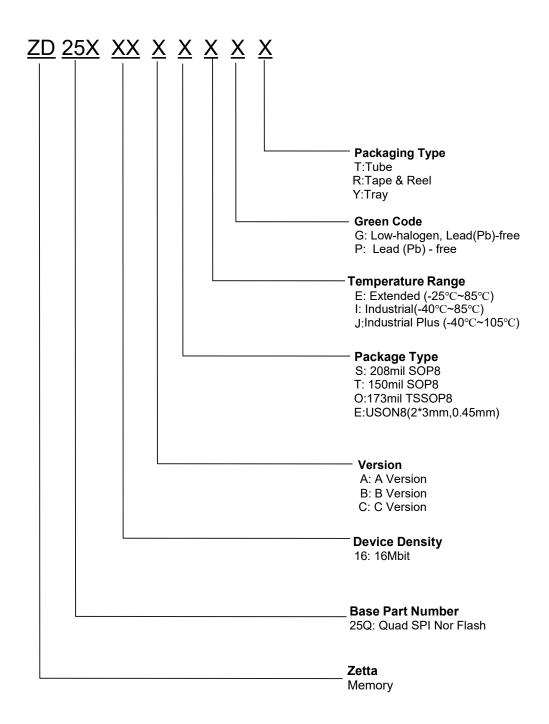

| 6. | ORD  | ERING INFORMATION                                                         | 81 |

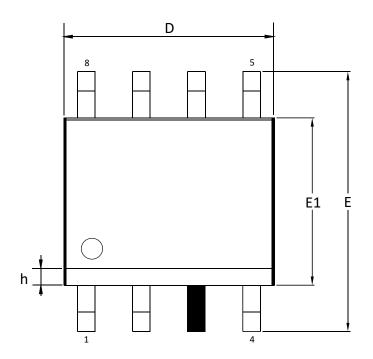

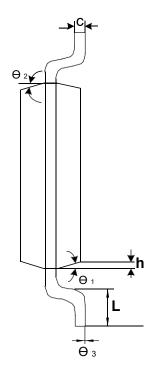

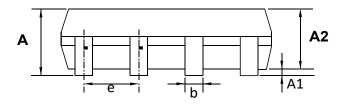

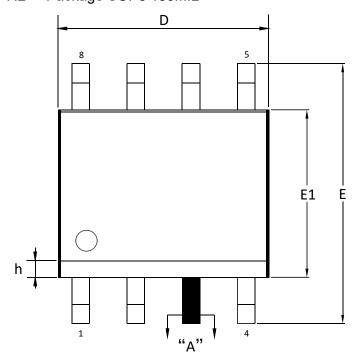

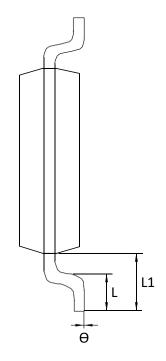

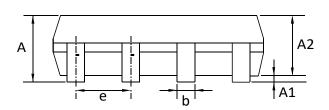

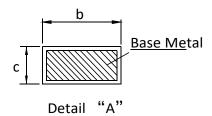

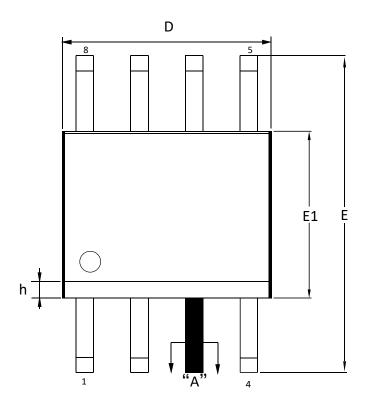

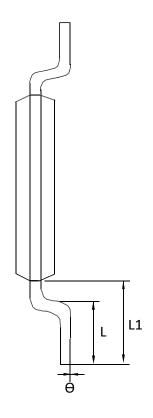

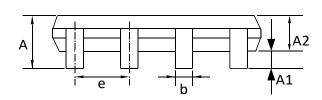

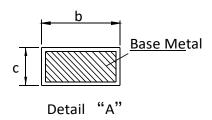

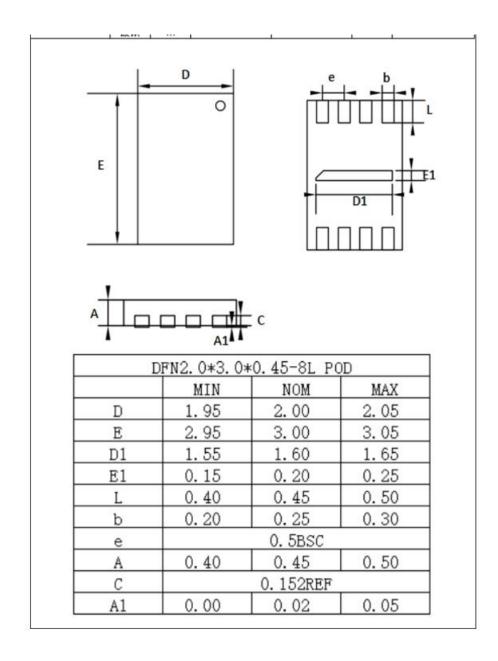

| 7. | PACI | KAGE INFORMATION                                                          | 82 |

|    | 7.1  | Package SOP8 208MIL                                                       | 82 |

|    | 7.2  | Package SOP8 150MIL                                                       | 83 |

|    | 7.3  | Package TSSOP8                                                            | 84 |

|    | 7.4  | Package USON (3x2x0.45)                                                   | 85 |

| 8. | REVI | SION HISTORY                                                              | 86 |

### 1. OVERVIEW

The ZD25Q16C (16M-Bit) serial flash supports the standard Serial Peripheral Interface (SPI), and supports the Dual/Quad SPI and QPI: Serial Clock, Chip Select, Serial Data I/O0 (SI), I/O1 (SO), I/O2 (WP#), and I/O3 (HOLD#).

The Dual I/O & Dual output data is transferred with speed of 208Mbits/s and the Quad I/O & Quad output data is transferred with speed of 416Mbits/s.

Specifically designed for use in many different systems, the device supports read, program, and erase operations with a wide supply voltage range of 2.3V to 3.6V. No separate voltage is required for programming and erasing.

### 1.1 Performance

### • Single, Dual and Quad IO mode

Standard SPI: SCLK, CS#, SI, SO Dual SPI: SCLK, CS#, IO0, IO1

Quad SPI: SCLK, CS#, IO0, IO1, IO2, IO3, QPI: SCLK, CS#, IO0, IO1, IO2, IO3

### Highest Performance Speed

- 1 IO 104MHz for fast read

- 2 IO Dual I/O Data transfer up to 208Mbits/s

- 4 IO Quad I/O Data transfer up to 416Mbits/s, QPI Mode Data transfer up to 416Mbits/s

### • Power Supply and Low Power Consumption

Single 2.3V to 3.6V supply

10μA standby current, 0.3μA deep power down current

2.5mA active read current at 33MHz, 3.0mA active program or erase current

### Flexible Architecture for Code and Data Storage

Uniform 256-byte Page Erase, Uniform 4K-byte Sector Erase

Uniform 32/64K-byte Block Erase, Program 1 to 256 byte per programmable page

Minimum 100,000 Program/Erase Cycles, More than 20-year data retention

### Fast Program and Erase Speed

2ms page program time,10ms page erase time 10ms 4K-byte sector erase time,10ms 32K/64K-byte block erase time

### Advanced Security Features

128-Bit Unique ID for each device 3\*1024-Byte Security Registers with OTP Locks Discoverable parameters (SFDP) register

### Package Options

SOP8 150MIL, SOP8 208MIL TSSOP-8, USON-8 Contact ZETTA for KGD and other options

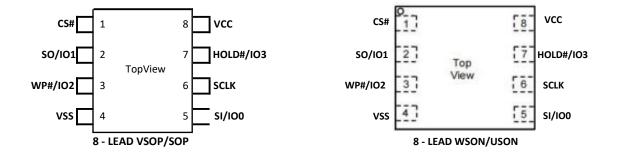

### 1.2 Pin Definition

**Table-1. Pin Definition**

| Pin No. | Pin Name    | I/O | Description                               |

|---------|-------------|-----|-------------------------------------------|

| 1       | CS#         | I   | Chip Select Input                         |

| 2       | SO (IO1)    | I/O | Data Output (Data Input Output 1)         |

| 3       | WP# (IO2)   | I/O | Write Protect Input (Data Input Output 2) |

| 4       | VSS         |     | Ground                                    |

| 5       | SI (IO0)    | I/O | Data Input (Data Input Output 0)          |

| 6       | SCLK        | I   | Serial Clock Input                        |

| 7       | HOLD# (IO3) | I/O | Hold Input (Data Input Output 3)          |

| 8       | VCC         |     | Power Supply                              |

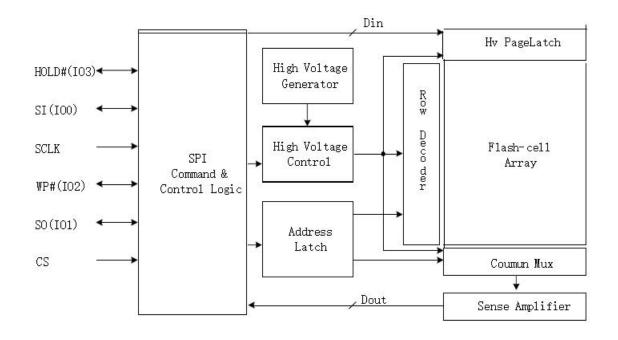

### 2. DESCRIPTION

### 2.1 BLOCK DIAGRAM

5

### 2.2 MEMORY ORGANIZATION

Table-2. ZD25Q16C Array Organization

| Each device has | Each block has | Each sector has | Each page has |         |

|-----------------|----------------|-----------------|---------------|---------|

| 2M              | 64/32K         | 4K              | 256           | Bytes   |

| 8K              | 256/128        | 16              | -             | Pages   |

| 512             | 16/8           | -               | -             | Sectors |

| 32/64           | -              | -               | -             | Blocks  |

Table-3. ZD25Q16C Uniform Block Sector Architecture

| Block | Sector | Addre   | ss range |

|-------|--------|---------|----------|

|       | 511    | 1FF000H | 1FFFFFH  |

| 31    | •••••  |         | •••••    |

|       | 496    | 1F0000H | 1F0FFFH  |

|       | 495    | 1EF000H | 1EFFFFH  |

| 30    | •••••  |         | •••••    |

|       | 480    | 1E0000H | 1E0FFFH  |

|       | *****  |         | •••••    |

|       | *****  |         | •••••    |

|       | •••••  |         | •••••    |

|       | •••••  |         | •••••    |

|       | *****  |         | •••••    |

|       | •••••  |         | •••••    |

|       | 47     | 02F000H | 02FFFFH  |

| 2     | •••••  |         | •••••    |

|       | 32     | 020000H | 020FFFH  |

|       | 31     | 01F000H | 01FFFFH  |

| 1     | •••••  |         | •••••    |

|       | 16     | 010000H | 010FFFH  |

|       | 15     | 00F000H | 00FFFFH  |

| 0     | •••••  |         |          |

|       | 0      | 000000H | 000FFFH  |

### 3. DEVICE OPERATION

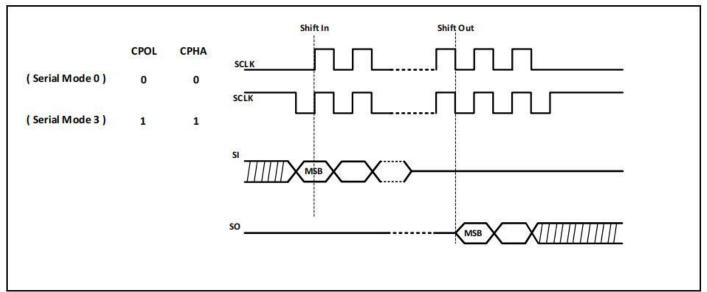

### 3.1 Mode0 and Mode3

- 1. Before a command is issued, the status register should be checked to ensure the device is ready for the intended operation.

- 2. When an incorrect command is input, the device enters standby mode and remains in standby mode until the next CS# falling edge. In standby mode, the SO pin of the device is in High-Z.

- 3. When the correct command is input, the device enters active mode and remains in active mode until the next rising edge of CS#.

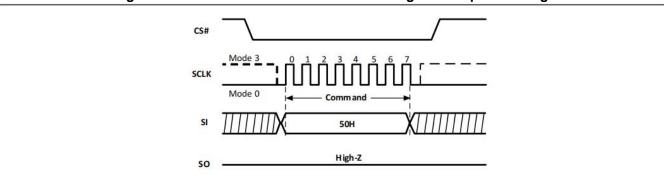

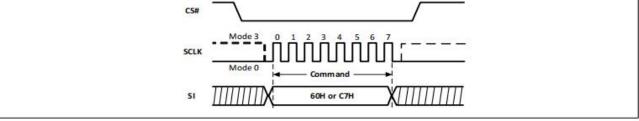

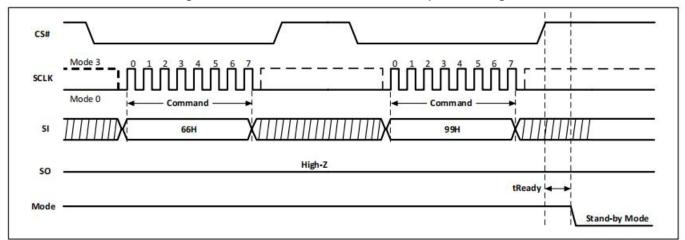

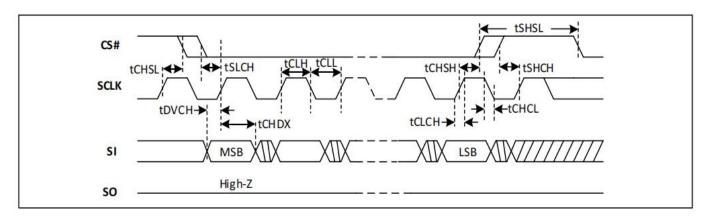

- 4. For standard single data rate serial mode, input data is latched on the rising edge of Serial Clock (SCLK) and data is shifted out on the falling edge of SCLK. The difference between Serial mode 0 and mode 3 is shown in Figure-1.

Figure-1. Serial Modes Supported (for Normal Serial Mode)

#### Standard SPI

The ZD25Q16C features a serial peripheral interface on 4 signals: Serial Clock (SCLK), Chip Select (CS#), Serial Data Input (SI) and Serial Data Output (SO). Both SPI bus mode 0 and 3 are supported. Input data is latched on the rising edge of SCLK and is data shifted out on the falling edge of SCLK.

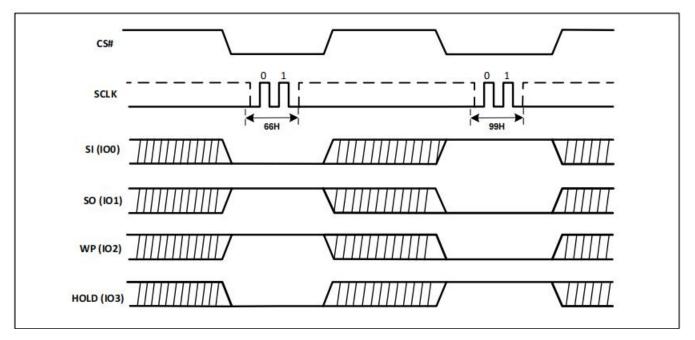

### **Dual SPI**

The ZD25Q16C supports Dual SPI operation when using the "Dual Output Fast Read" (3BH), "Dual I/O Fast Read" (BBH), "Dual I/O Read Manufacture ID & Device ID" (92H) and "Dual Input Page Program" (A2H) commands. These commands allow data to be transferred to or from the device at twice the rate of the standard SPI. When using the Dual SPI command, the SI and SO pins become bidirectional I/O pins: IO0 and IO1.

#### **Quad SPI**

The ZD25Q16C supports Quad SPI operation when using the "Quad Output Fast Read" (6BH), "Quad I/O Fast Read" (EBH/E7H/E3H), "Quad I/O Read Manufacture ID/Device ID" (94H) and "Quad Input Page Program" (32H) commands. These commands allow data to be transferred to or from the device at four times the rate of the standard SPI. When using the Quad SPI command, the SI, SO, WP# and HOLD# pins become bidirectional I/O pins: IO0, IO1, IO2 and IO3, respectively. Quad SPI commands require the non-volatile Quad Enable bit (QE) in Status Register to be set.

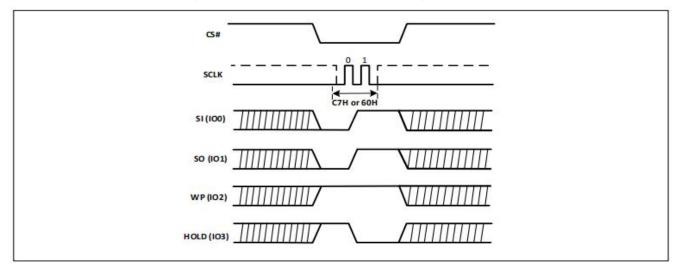

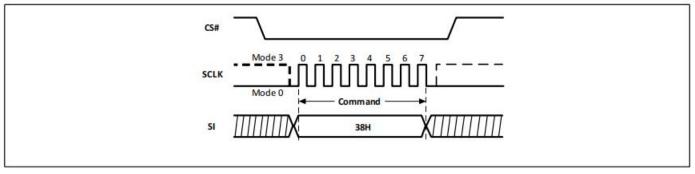

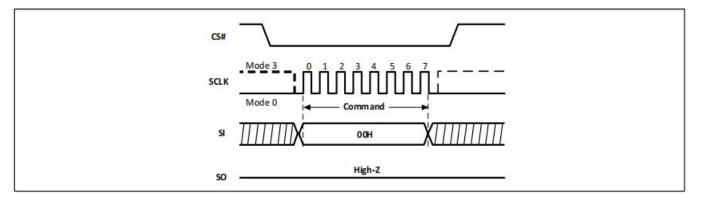

#### **QPI Mode**

The ZD25Q16C supports Quad Peripheral Interface (QPI) operations only when the device is switched from Standard/Dual/Quad SPI mode to QPI mode using the "Enable the QPI (38H)" command. The QPI mode utilizes all four IO pins to input the command code. Standard/Dual/Quad SPI mode and QPI mode are exclusive. Only one mode can be active at any given times. "Enable the QPI (38H)" and "Disable the QPI(FFH)" commands are used to switch between these two modes. Upon power-up and after software reset using "Reset (99H)" command, the default state of the device is Standard/Dual/Quad SPI mode. The QPI mode requires the non-volatile Quad Enable bit (QE) in Status Register to be set.

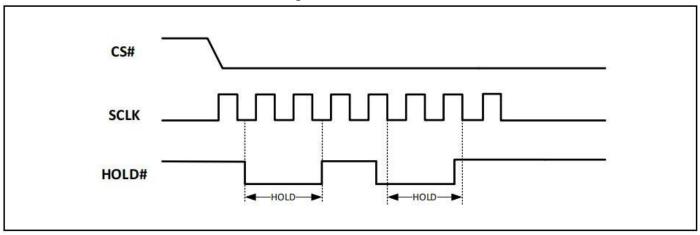

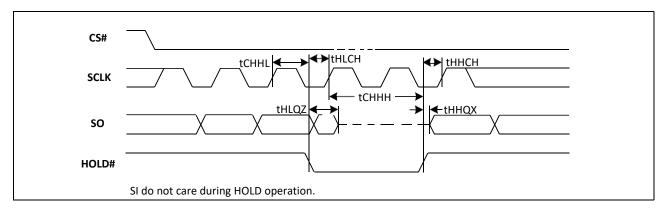

#### Hold

Driving the HOLD# pin low will pause any serial communications with the device. The HOLD feature will not stop the following operations if already in progress when the HOLD# pin goes low: status register write, program, or erase.

The operation of HOLD requires Chip Select (CS#) to remain low and begins on the falling edge of HOLD# pin signal while the Serial Clock (SCLK) signal is low (if the Serial Clock signal is not low, the HOLD operation will not start until the Serial Clock signal is low). The HOLD condition ends on the rising edge of HOLD# pin signal while the Serial Clock (SCLK) signal is low (if the Serial Clock signal is not low, the HOLD operation will not end until the Serial Clock is low).

Figure-2. Hold Condition

During the HOLD operation, the Serial Data Output (SO) is in a high impedance state when the HOLD# pin goes low and will remain in a high impedance state until the HOLD# pin goes high. The Serial Data Input (SI) is ignored (don't care) if both the Serial Clock (SCLK) and HOLD# pin go low and will remain in this state until the SCLK goes low and the HOLD# pin goes high. If Chip Select (CS#) is driven high during the HOLD operation, it will reset the internal logic of the device. To re-start communication with chip, the HOLD# must be driven high and CS# must be at a logic low.

Note: The HOLD feature is disabled in Quad I/O and QPI mode.

### 3.2 Status Register (SR)

Table-4. Status Register

| S15 | S14 | S13 | S12 | S11 | S10     | S9 | S8   |

|-----|-----|-----|-----|-----|---------|----|------|

| sus | СМР | LB3 | LB2 | LB1 | EP_FAIL | QE | SRP1 |

| <b>S</b> 7 | S6  | <b>S</b> 5 | <b>S4</b> | S3  | S2  | <b>S</b> 1 | S0  |

|------------|-----|------------|-----------|-----|-----|------------|-----|

| SRP0       | BP4 | BP3        | BP2       | BP1 | BP0 | WEL        | WIP |

The status and control bits of the Status Register are as follows:

#### WIP bit

The Write in Progress (WIP) bit indicates whether the device is busy executing a program/erase/write status register operation. When the Write in Progress (WIP) bit is set to 1, a program/erase/write status register operation is in progress. When the Write in Progress (WIP) bit is set to 0, the device does not have a program/erase/write status register operation in progress.

### **WEL** bit

The Write Enable Latch (WEL) bit indicates the status of the internal Write Enable Latch. When set to 1, the internal Write Enable Latch is set, when set to 0 the internal Write Enable Latch is reset, and no Write Status Register, Program or Erase command is accepted.

### BP4, BP3, BP2, BP1, BP0 bits

The Block Protect (BP4, BP3, BP2, BP1, and BP0) bits are non-volatile. They define the size of the area software protected against Program and Erase commands. These bits are written with the Write Status Register (01H) command. When the Block Protect (BP4, BP3, BP2, BP1, BP0) bits are set to the target value, the relevant memory area (as defined in Table-7.X) becomes protected against Page Program (02H), Page Erase (81H), Sector Erase (20H), Half Block Erase (52H) and Block Erase (D8H) commands. The Chip Erase (60H or C7H) command is executed, only if the Block Protect bits are set to "None protected". The Block Protect bits can be written if the Hardware Protection Mode has not been set.

### SRP1, SRP0 bits

The Status Register Protect (SRP1 and SRP0) bits are non-volatile Read/Write bits in the status register. The SRP bits control the method of write protection: software protection, hardware protection, power supply lock-down or one-time programmable protection.

| SRP1 | SRP0 | #WP | Status Register                 | Description                                                                                            |  |  |  |  |

|------|------|-----|---------------------------------|--------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0    | 0    | х   | Software Protected              | The Status Register can be written to after a Write Enable command, WEL=1. (Default)                   |  |  |  |  |

| 0    | 1    | 0   | Hardware Protected              | WP#=0, the Status Register is locked and cannot be wr to.                                              |  |  |  |  |

| 0    | 1    | 1   | Hardware Unprotected            | WP#=1, the Status Register is unlocked and can be written to after a Write Enable command, WEL=1.      |  |  |  |  |

| 1    | 0    | х   | Power Supply<br>Lock-Down (1)   | Status Register is protected and cannot be written to again until the next Power-Down, Power-Up cycle. |  |  |  |  |

| 1    | 1    | х   | One Time Program <sup>(2)</sup> | Status Register is permanently protected and cannot be written to.                                     |  |  |  |  |

Table-5. Status Register Protection Bits

#### Notes:

- 1. When SRP1, SRP0= (1, 0), a Power-Down, Power-Up cycle will change SRP1, SRP0 to (0, 0) state.

- 2. This feature is available on special order. Please contact ZETTA for details.

### QE bit

The Quad Enable (QE) bit is a non-volatile Read/Write bit in the Status Register that allows Quad operation. When the QE bit is set to 0 (Default) the device is set to Standard SPI operation and both WP# and HOLD# pins are enabled. When the QE bit is set to 1, the Quad IO2 and IO3 pins are enabled and the WP# pin function is not available since this pin is used for IO2. (Set the QE bit to 0 to avoid short issue if the WP# or HOLD# pin is tied directly to the power supply or ground.)

### **EP\_FAIL** bit

The Erase/Program Fail bit is a read only bit which shows the status of the last Program/Erase operation. The bit will be set to "1" if the program/erase operation failed or interrupted by reset or the program/erase region was protected. It will be automatically cleared to "0" if the next program/erase operation succeeds. Please note that it will not interrupt or stop any operation in the flash memory.

#### LB3, LB2, LB1 bits

The LB3, LB2, LB1 bits are non-volatile One Time Program (OTP) bits in Status Register (S13-S11) that provide the write protect control and status for the Security Registers. The default state of LB3-LB1 is 0, with the security registers unprotected. The LB3-LB1 bits can be set to 1 individually using the Write Register (01H or 31H) command. The LB3-LB1 bits are One Time Programmable, once setting to 1, the corresponding Security Registers will become read-only permanently.

#### **CMP** bit

The CMP bit is a non-volatile Read/Write bit in the Status Register (S14). It is used in conjunction with the BP4-BP0 bits to provide more flexibility for the memory array protection. Please see the Table-7.X for protect area details. The default setting is CMP=0.

### SUS bit

The SUS bit is read only bit in the status register (S15) that is set to 1 after executing a Program/Erase Suspend (75H or B0H) command. The SUS bit is cleared to 0 by the Program/Erase Resume (7AH or 30H)

command, the Software Reset (66H+99H) command as well as a power-down, power-up cycle.

### 3.3 Configuration Register (CR)

Table 6. Status Register

| C7       | C6           | C5           | C4       | C3       | C2       | C1       | C0           |

|----------|--------------|--------------|----------|----------|----------|----------|--------------|

| Reserved | DRV1         | DRV0         | QP       | Reserved | Reserved | Reserved | DC           |

|          | Non-volatile | Non-volatile | Volatile |          |          |          | Non-volatile |

#### QP bit

The Quad Page (QP) bit is a volatile Read/Write bit in the Configure Register that allows Quad Page operation. When the QP bit is set to 0 (Default) the page size is 256bytes. When the QP pin is set to 1, the page size is 1024bytes.

This bit controls the page programming buffer address wrap point. Legacy SPI devices generally have used a 256 Byte page programming buffer and defined that if data is loaded into the buffer beyond the 255 Byte locations, the address at which additional bytes are loaded would be wrapped to address zero of the buffer. The ZD25Q16C provides a 1024Byte page programming buffer that can increase programming performance. For legacy software compatibility, this configuration bit provides the option to continue the wrapping behavior at the 256 Byte boundary or to enable full use of the available 1024Byte buffer by not wrapping the load address at the 256 Byte boundary.

When the QP pin is set to 1, the page erase instruction(81h) will erase the data of the chosen Quad Page to be "1".

#### DRV1 & DRV0 bit

The DRV1 & DRV0 bits are non-volatile Read/Write bits which are used to determine the output driver strength for the Read operations.

| DRV1,DRV0    | Drive Strength |

|--------------|----------------|

| 0,0          | 80%            |

| 0,1          | 40%            |

| 1,0          | 100%           |

| 1,1(default) | 60%            |

### DC bit

The Dummy Configuration (DC) bit is non-volatile, which selects the number of dummy cycles between the end of address and the start of read data output. Dummy cycles provide additional latency that is needed to complete the initial read access of the flash array before data can be returned to the host system. Some read commands require additional dummy cycles as the SCLK frequency increases.

The following dummy cycle tables provide different dummy cycle settings that are configured

| Command | DC bit      | Numbers of Dummy Cycles | Freq.(MHz) |

|---------|-------------|-------------------------|------------|

| BBH     | 0 (default) | 4                       | 66         |

| DDN     | 1           | 8                       | 86         |

| EDII    | 0 (default) | 6                       | 66         |

| EBH     | 1           | 10                      | 86         |

### 3.4 Data Protection

During power transition, there may be some false system level signals which result in inadvertent erasure or programming. The device is designed to protect itself from these accidental write cycles.

The state machine will be reset to standby mode automatically during power up. In addition, the control register architecture of the device ensures that the memory contents can only be changed after specific command sequences have completed successfully.

In the following, there are several features to protect the system from the accidental write cycles during VCC power-up and power-down or from system noise.

- Valid command length checking: The command length will be checked whether it is at byte base and completed on byte boundary.

- Write Enable (06H) command: WREN command is required to set the Write Enable Latch bit (WEL) before

issuing other commands to change data.

- Software Protection Mode: The Block Protect (BP4, BP3, BP2, BP1, and BP0) bits define the section of the memory array that can be read but not changed.

- Hardware Protection Mode: WP# going low to protect the CMP, BP0~BP4 bits and SRP0~1 bits.

- Deep Power-Down Mode: By entering deep power down mode, the flash device is ignores all commands until the Release from Deep Power-Down Mode (B9H) command.

Table-7.1 ZD25Q16C Protected Area Size (CMP bit=0)

|     |     | Status bi | it  |     | Memory Content |                 |         |             |

|-----|-----|-----------|-----|-----|----------------|-----------------|---------|-------------|

| BP4 | BP3 | BP2       | BP1 | BP0 | Blocks         | Addresses       | Density | Portion     |

| Х   | Х   | 0         | 0   | 0   | NONE           | NONE            | NONE    | NONE        |

| 0   | 0   | 0         | 0   | 1   | 31             | 1F0000H-1FFFFFH | 64KB    | Upper 1/32  |

| 0   | 0   | 0         | 1   | 0   | 30 and 31      | 1E0000H-1FFFFFH | 128KB   | Upper 1/16  |

| 0   | 0   | 0         | 1   | 1   | 28 to 31       | 1C0000H-1FFFFFH | 256KB   | Upper 1/8   |

| 0   | 0   | 1         | 0   | 0   | 24 to 31       | 180000H-1FFFFFH | 512KB   | Upper 1/4   |

| 0   | 0   | 1         | 0   | 1   | 16 to 31       | 100000H-1FFFFFH | 1MB     | Upper 1/2   |

| 0   | 1   | 0         | 0   | 1   | 0              | 000000H-00FFFFH | 64KB    | Lower 1/32  |

| 0   | 1   | 0         | 1   | 0   | 0 and 1        | 000000H-01FFFFH | 128KB   | Lower 1/16  |

| 0   | 1   | 0         | 1   | 1   | 0 to 3         | 000000H-03FFFFH | 256KB   | Lower 1/8   |

| 0   | 1   | 1         | 0   | 0   | 0 to 7         | 000000H-07FFFFH | 512KB   | Lower 1/4   |

| 0   | 1   | 1         | 0   | 1   | 0 to 15        | 000000H-0FFFFFH | 1MB     | Lower 1/2   |

| Х   | Х   | 1         | 1   | Х   | 0 to 31        | 000000H-1FFFFFH | 2MB     | ALL         |

| 1   | 0   | 0         | 0   | 1   | 31             | 1FF000H-1FFFFFH | 4KB     | Upper 1/512 |

| 1   | 0   | 0         | 1   | 0   | 31             | 1FE000H-1FFFFFH | 8KB     | Upper 1/256 |

| 1   | 0   | 0         | 1   | 1   | 31             | 1FC000H-1FFFFFH | 16KB    | Upper 1/128 |

| 1   | 0   | 1         | 0   | Х   | 31             | 1F8000H-1FFFFFH | 32KB    | Upper 1/64  |

| 1   | 1   | 0         | 0   | 1   | 0              | 000000H-000FFFH | 4KB     | Lower 1/512 |

| 1   | 1   | 0         | 1   | 0   | 0              | 000000H-001FFFH | 8KB     | Lower 1/256 |

| 1   | 1   | 0         | 1   | 1   | 0              | 000000H-003FFFH | 16KB    | Lower 1/128 |

| 1   | 1   | 1         | 0   | Х   | 0              | 000000H-007FFFH | 32KB    | Lower 1/64  |

Table-7.2 ZD25Q16C Protected Area Size (CMP bit=1)

| Status bit |     |     |     |     | Memory Content |                                  |               |               |  |

|------------|-----|-----|-----|-----|----------------|----------------------------------|---------------|---------------|--|

| BP4        | BP3 | BP2 | BP1 | BP0 | Blocks         | Blocks Addresses Density Portion |               |               |  |

| х          | х   | 0   | 0   | 0   | 0 to 31        | 000000H-1FFFFFH                  | 2MB           | ALL           |  |

| 0          | 0   | 0   | 0   | 1   | 0 to 30        | 000000H-1EFFFFH                  | 1984KB        | Lower 31/32   |  |

| 0          | 0   | 0   | 1   | 0   | 0 to 29        | 000000H-1DFFFFH                  | 1920KB        | Lower 15/16   |  |

| 0          | 0   | 0   | 1   | 1   | 0 to 27        | 000000H-1BFFFFH                  | 1792KB        | Lower 7/8     |  |

| 0          | 0   | 1   | 0   | 0   | 0 to 23        | 000000H-17FFFFH                  | 1536KB        | Lower 3/4     |  |

| 0          | 0   | 1   | 0   | 1   | 0 to 15        | 000000H-0FFFFFH                  | 1MB           | Lower 1/2     |  |

| 0          | 1   | 0   | 0   | 1   | 1 to 31        | 010000H-1FFFFFH                  | 1984KB        | Upper 31/32   |  |

| 0          | 1   | 0   | 1   | 0   | 2 to 31        | 020000H-1FFFFFH                  | 1920KB        | Upper 15/16   |  |

| 0          | 1   | 0   | 1   | 1   | 4 to 31        | 040000H-1FFFFFH                  | 1792KB        | Upper 7/8     |  |

| 0          | 1   | 1   | 0   | 0   | 8 to 31        | 080000H-1FFFFFH                  | 1536KB        | Upper 3/4     |  |

| 0          | 1   | 1   | 0   | 1   | 16 to 31       | 100000H-1FFFFFH                  | 1MB Upper 1/2 |               |  |

| х          | х   | 1   | 1   | х   | NONE           | NONE                             | NONE NONE     |               |  |

| 1          | 0   | 0   | 0   | 1   | 0 to 31        | 000000H-1FEFFFH                  | 2044KB        | Lower 511/512 |  |

| 1          | 0   | 0   | 1   | 0   | 0 to 31        | 000000H-1FDFFFH                  | 2040KB        | Lower 255/256 |  |

| 1          | 0   | 0   | 1   | 1   | 0 to 31        | 000000H-1FBFFFH                  | 2032KB        | Lower 127/128 |  |

| 1          | 0   | 1   | 0   | х   | 0 to 31        | 000000H-1F7FFFH 2016KB Lowe      |               | Lower 63/64   |  |

| 1          | 1   | 0   | 0   | 1   | 0 to 31        | 001000H-1FFFFFH                  | 2044KB        | Upper 511/512 |  |

| 1          | 1   | 0   | 1   | 0   | 0 to 31        | 002000H-1FFFFFH                  | 2040KB        | Upper 255/256 |  |

| 1          | 1   | 0   | 1   | 1   | 0 to 31        | 004000H-1FFFFFH                  | 2032KB        | Upper 127/128 |  |

| 1          | 1   | 1   | 0   | х   | 0 to 31        | 008000H-1FFFFFH                  | 2016KB        | Upper 63/64   |  |

### Notes:

- 1. X=don't care

- 2. If any erase or program command specifies a memory that contains protected data portion, this command will be ignored.

### 4. COMMAND DESCRIPTION

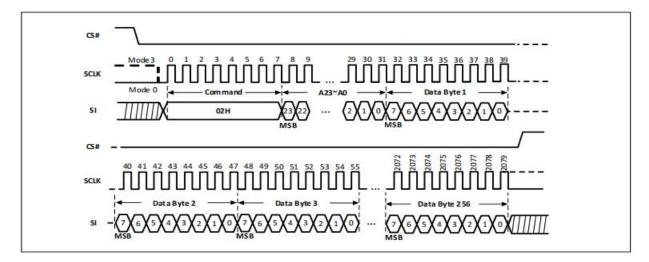

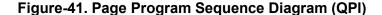

All commands, addresses and data are shifted in and out of the device, beginning with the most significant bit on the first rising edge of SCLK after CS# is driven low. Then, the one-byte command code must be shifted into the device starting with the most significant bit on SI. Each bit is latched on the rising edge of SCLK.

The commands supported by ZD25Q16C are listed inTable-8. Every command sequence starts with a one-byte command code. Depending on the command, it might be followed by address or data bytes, or by both or none. CS# must be driven high after the last bit of the command sequence has been completed. For the commands of Read, Fast Read, Read Status Register, Release from Deep Power- Down, and Read Device ID, the shifted-in command sequence is followed by a data-out sequence. All read commands can be completed after any bit of the data-out sequence is shifted out, and then CS# must be driven high to return to deselected status.

For the Page Program, Sector Erase, Half Block Erase, Block Erase, Chip Erase, Write Status Register, Write Enable, Write Disable or Deep Power-Down commands, CS# must be driven high exactly at a byte boundary, otherwise the command is rejected, and is not executed. That means CS# must be driven high when the number of clock pulses after CS# being driven low is an exact multiple of eight. For Page Program, if CS# is driven high at any time the input byte is not a full byte, nothing will happen and WEL will not be reset.

Table-8. Commands (Standard/Dual/Quad SPI)

|                           |        | DIO 01 001 |         | (      |         |         |         |         |         |

|---------------------------|--------|------------|---------|--------|---------|---------|---------|---------|---------|

| Command Name              | Byte 1 | Byte 2     | Byte 3  | Byte 4 | Byte 5  | Byte 6  | Byte 7  | Byte 8  | Byte 9  |

| Write Enable              | 06H    |            |         |        |         |         |         |         |         |

| Write Disable             | 04H    |            |         |        |         |         |         |         |         |

| Volatitle SR Write Enable | 50H    |            |         |        |         |         |         |         |         |

| Read Status Register-1    | 05H    | (S7-S0)    | (cont.) |        |         |         |         |         |         |

| Read Status Register-2    | 35H    | (S15-S8)   | (cont.) |        |         |         |         |         |         |

| Read Configure Register   | 45/15H | (S7-S0)    | (cont.) |        |         |         |         |         |         |

| Write Status Register-1   | 01H    | S7-S0      |         |        |         |         |         |         |         |

| Write Status Register-1&2 | 01H    | S7-S0      | S15-S8  |        |         |         |         |         |         |

| Write Status Register-2   | 31H    | S15-S8     |         |        |         |         |         |         |         |

| Write Configure Register  | 11H    | S7-S0      |         |        |         |         |         |         |         |

| Read Data                 | 03H    | A23-A16    | A15-A8  | A7-A0  | (D7-D0) | (cont.) |         |         |         |

| Fast Read                 | 0BH    | A23-A16    | A15-A8  | A7-A0  | dummy   | (D7-D0) | (cont.) |         |         |

| Dual Output Fast Read     | 3BH    | A23-A16    | A15-A8  | A7-A0  | dummy   | (D7-D0) | (cont.) |         |         |

| Quad Output Fast Read     | 6BH    | A23-A16    | A15-A8  | A7-A0  | dummy   | (D7-D0) | (cont.) |         |         |

| Read Word Quad I/O        | E7H    | A23-A16    | A15-A8  | A7-A0  | M7-M0   | dummy   | (D7-D0) | (cont.) |         |

| Read Octal Word Quad I/O  | E3H    | A23-A16    | A15-A8  | A7-A0  | M7-M0   | (D7-D0) | (cont.) |         |         |

| Dual I/O Fast Read        | ввн    | A23-A16    | A15-A8  | A7-A0  | M7-M0   | (D7-D0) | (cont.) |         |         |

| Active Status Interrupt   | 25H    |            |         |        |         |         |         |         |         |

| Quad I/O Fast Read        | EBH    | A23-A16    | A15-A8  | A7-A0  | M7-M0   | dummy   | dummy   | (D7-D0) | (cont.) |

### Commands (Standard/Dual/Quad SPI)

| Command Name                                    | Byte 1  | Byte 2          | Byte 3         | Byte 4        | Byte 5          | Byte 6          | Byte 7        | Byte8           | Byte 9        | Byte 10 |

|-------------------------------------------------|---------|-----------------|----------------|---------------|-----------------|-----------------|---------------|-----------------|---------------|---------|

| Set Burst with Wrap                             | 77H     | dummy           | dummy          | dummy         | W7-W0           |                 |               |                 |               |         |

| Page Program                                    | 02H     | A23-A16         | A15-A8         | A7-A0         | D7-D0           | Next Byte       |               |                 |               |         |

| Page Write                                      | A5H     | A23-A16         | A15-A8         | A7-A0         | D7-D0           | Next Byte       |               |                 |               |         |

| Dual-IN Page Program                            | A2H     | A23-A16         | A15-A8         | A7-A0         | D7-D0           | Next Byte       |               |                 |               |         |

| Quad Page Program                               | 32H     | A23-A16         | A15-A8         | A7-A0         | D7-D0           | Next Byte       |               |                 |               |         |

| Page Erase                                      | 81H     | A23-A16         | A15-A8         | A7-A0         |                 |                 |               |                 |               |         |

| Sector Erase                                    | 20H     | A23-A16         | A15-A8         | A7-A0         |                 |                 |               |                 |               |         |

| Block Erase (32K)                               | 52H     | A23-A16         | A15-A8         | A7-A0         |                 |                 |               |                 |               |         |

| Block Erase (64K)                               | D8H     | A23-A16         | A15-A8         | A7-A0         |                 |                 |               |                 |               |         |

| Chip Erase                                      | C7/60H  |                 |                |               |                 |                 |               |                 |               |         |

| Read Manufacturer/Device                        | 90H     | dummy           | dummy          | A7-A0         | (MID7-<br>MID0) | (ID7-ID0)       | (cont.)       |                 |               |         |

| Dual I/O Read<br>Manufacturer/Device ID         | 92H     | dummy           | dummy          | A7-A0         | M7-M0           | (MID7-<br>MID0) | (ID7-<br>ID0) | (cont.)         |               |         |

| Quad I/O Read<br>Manufacturer/Device ID         | 94H     | dummy           | dummy          | A7-A0         | M7-M0           | dummy           | dummy         | (MID7-<br>MID0) | (ID7-<br>ID0) | (cont.) |

| Read Identification                             | 9FH     | (MID7-<br>MID0) | (ID15-<br>ID8) | (ID7-<br>ID0) | (cont.)         |                 |               |                 |               |         |

| Read Unique ID                                  | 4BH     | dummy           | dummy          | dummy         | dummy           | (UID7-<br>UID0) | (cont.)       |                 |               |         |

| Erase Security Registers                        | 44H     | A23-A16         | A15-A8         | A7-A0         |                 |                 |               |                 |               |         |

| Program Security Registers                      | 42H     | A23-A16         | A15-A8         | A7-A0         | D7-D0           | Next Byte       |               |                 |               |         |

| Read Security Registers                         | 48H     | A23-A16         | A15-A8         | A7-A0         | dummy           | (D7-D0)         | (cont.)       |                 |               |         |

| Enable Reset                                    | 66H     |                 |                |               |                 |                 |               |                 |               |         |

| Reset                                           | 99H     |                 |                |               |                 |                 |               |                 |               |         |

| Program/Erase Suspend                           | 75H/B0H |                 |                |               |                 |                 |               |                 |               |         |

| Program/Erase Resume                            | 7AH/30H |                 |                |               |                 |                 |               |                 |               |         |

| Deep Power-Down                                 | В9Н     |                 |                |               |                 |                 |               |                 |               |         |

| Release From Deep<br>Power-Down                 | АВН     |                 |                |               |                 |                 |               |                 |               |         |

| Release From Deep Power-Down and Read Device ID | АВН     | dummy           | dummy          | dummy         | (ID7-<br>ID0)   | (cont.)         |               |                 |               |         |

| Read Serial Flash Discoverable Parameter        | 5AH     | A23-A16         | A15-A8         | A7-A0         | dummy           | (D7-D0)         | (cont.)       |                 |               |         |

| Enable QPI                                      | 38H     |                 |                |               |                 |                 |               |                 |               |         |

### Command set (QPI)

| Command Name                                   | Byte 1 | Byte 2    | Byte 3   | Byte 4  | Byte 5      | Byte 6    | Byte 7  | Byte 8  |

|------------------------------------------------|--------|-----------|----------|---------|-------------|-----------|---------|---------|

| Clock Number                                   | (0,1)  | (2,3)     | (4,5)    | (6,7)   | (8,9)       | (10,11)   | (12,13) | (14,15) |

| Write Enable                                   | 06H    |           |          |         |             |           |         |         |

| Write Disable                                  | 04H    |           |          |         |             |           |         |         |

| Read Config Register bit                       | 45/15H | (S7-S0)   | (cont.)  |         |             |           |         |         |

| Read Status Register-1                         | 05H    | (S7-S0)   | (cont.)  |         |             |           |         |         |

| Read Status Register-2                         | 35H    | (S15-S8)  | (cont.)  |         |             |           |         |         |

| Write Status Register-1                        | 01H    | S7-S0     |          |         |             |           |         |         |

| Write Status Register-1&2                      | 01H    | S7-S0     | S15-S8   |         |             |           |         |         |

| Write Status Register-2                        | 31H    | S15-S8    |          |         |             |           |         |         |

| Write Configure Register                       | 11H    | S7-S0     |          |         |             |           |         |         |

| Volatile SR Write Enable                       | 50H    |           |          |         |             |           |         |         |

| Fast Read                                      | 0BH    | A23-A16   | A15-A8   | A7-A0   | dummy       | dummy     | (D7-D0) | (cont.) |

| Quad I/O Fast Read                             | EBH    | A23-A16   | A15-A8   | A7-A0   | M7-M0       | dummy     | (D7-D0) | (cont.) |

| Page Program                                   | 02H    | A23-A16   | A15-A8   | A7-A0   | D7-D0       | Next Byte |         |         |

| Page Write                                     | A5H    | A23-A16   | A15-A8   | A7-A0   | D7-D0       | Next Byte |         |         |

| Page Erase                                     | 81H    | A23-A16   | A15-A8   | A7-A0   |             |           |         |         |

| Sector Erase                                   | 20H    | A23-A16   | A15-A8   | A7-A0   |             |           |         |         |

| Block Erase (32K)                              | 52H    | A23-A16   | A15-A8   | A7-A0   |             |           |         |         |

| Block Erase (64K)                              | D8H    | A23-A16   | A15-A8   | A7-A0   |             |           |         |         |

| Chip Erase                                     | C7/60H |           |          |         |             |           |         |         |

| Set Read Parameters                            | C0H    | P7-P0     |          |         |             |           |         |         |

| Manufacturer/Device ID                         | 90H    | dummy     | dummy    | 00H     | (MID7-MID0) | (ID7-ID0) | (cont.) |         |

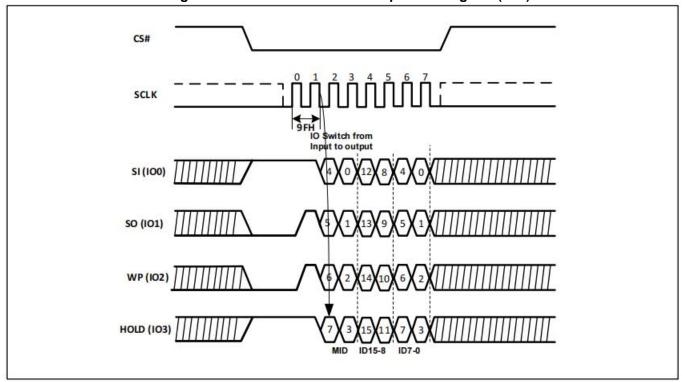

| Read Identification                            | 9FH    | MID7-MID0 | ID15-ID8 | ID7-ID0 | (cont.)     |           |         |         |

| Erase Security Registers                       | 44H    | A23-A16   | A15-A8   | A7-A0   |             |           |         |         |

| Program Security Registers                     | 42H    | A23-A16   | A15-A8   | A7-A0   | (D7-D0)     | Next Byte |         |         |

| Read Security Registers                        | 48H    | A23-A16   | A15-A8   | A7-A0   | dummy       | dummy     | (D7-D0) | (cont.) |

| Enable Reset                                   | 66H    |           |          |         |             |           |         |         |

| Reset                                          | 99H    |           |          |         |             |           |         |         |

| Burst Read with Wrap                           | 0CH    | A23-A16   | A15-A8   | A7-A0   | dummy       | dummy     | (D7-D0) | (cont.) |

| Program/Erase Suspend                          | 75H    |           |          |         |             |           |         |         |

| Program/Erase Resume                           | 7AH    |           |          |         |             |           |         |         |

| Deep Power-Down                                | В9Н    |           |          |         |             |           |         |         |

| Release from Deep Power-Down Release From Deep | ABH    |           |          |         |             |           |         |         |

| Power-Down, And Read Device ID                 | ABH    | dummy     | dummy    | dummy   | (ID7-ID0)   | (cont.)   |         |         |

| Disable QPI                                    | FFH    |           |          |         |             |           |         |         |

| Read Serial Flash Discoverable Parameter       | 5AH    | A23-A16   | A15-A8   | A7-A0   | dummy       | dummy     | (D7-D0) | (cont.) |

#### Notes:

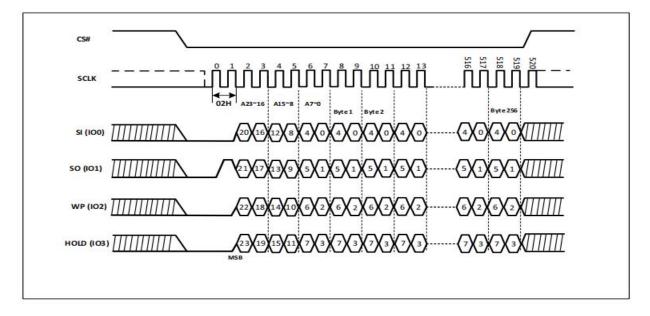

### 1. Dual Output data

IO0 = (D6, D4, D2, D0)

IO1 = (D7, D5, D3, D1)

### 2. Dual Input Address

IO0 = A22, A20, A18, A16, A14, A12, A10, A8, A6, A4, A2, A0, M6, M4, M2, M0

IO1 = A23, A21, A19, A17, A15, A13, A11, A9, A7, A5, A3, A1, M7, M5, M3, M1

### 3. Quad Output Data

IO0 = (D4, D0, ....)

IO1 = (D5, D1, ....)

IO2 = (D6, D2, ....)

IO3 = (D7, D3,....)

### 4. Quad Input Address

IO0 = A20, A16, A12, A8, A4, A0, M4, M0

IO1 = A21, A17, A13, A9, A5, A1, M5, M1

IO2 = A22, A18, A14, A10, A6, A2, M6, M2

IO3 = A23, A19, A15, A11, A7, A3, M7, M3

### 5. Fast Read Quad I/O Dummy Bits and Data

IO0 = (x, x, x, x, D4, D0,...)

IO1 = (x, x, x, x, D5, D1,...)

IO2 = (x, x, x, x, D6, D2,...)

IO3 = (x, x, x, x, D7, D3,...)

### 6. Word Read Quad I/O Data

IO0 = (x, x, D4, D0,...)

IO1 = (x, x, D5, D1,...)

IO2 = (x, x, D6, D2,...)

IO3 = (x, x, D7, D3,...)

### 7. Security Registers Address:

Security Register1: A23-A16=00H, A15-A8=04H, A7-A0= Byte Address;

Security Register2: A23-A16=00H, A15-A8=08H, A7-A0= Byte Address;

Security Register3: A23-A16=00H, A15-A8=0CH, A7-A0= Byte Address;

### 8. Dummy bits and Wrap Bits

IO0 = (x, x, x, x, x, x, W4, x)

IO1 = (x, x, x, x, x, x, W5, x)

102 = (x, x, x, x, x, x, W6, x)

IO3 = (x, x, x, x, x, x, x, x)

9. Address, Continuous Read Mode bits, Dummy bits, Manufacture ID and Device ID

IO0 = (A20, A16, A12, A8, A4, A0, M4, M0, x, x, x, x, MID4, MID0, DID4, DID0, ...)

IO1 = (A21, A17, A13, A9, A5, A1, M5, M1, x, x, x, x, MID5, MID1, DID5, DID1, ...)

IO2 = (A22, A18, A14, A10, A6, A2, M6, M2, x, x, x, x, MID6, MID2, DID6, DID2, ...)

IO3 = (A23, A19, A15, A11, A7, A3, M7, M3, x, x, x, x, MID7, MID3, DID7, DID3, ...)

10. QPI Command, Address, Data input/output format:

CLK #0 1 2 3 4 5 6 7 8 9 10 11

IO0= C4, C0, A20, A16, A12, A8, A4, A0, D4, D0, D4, D0

IO1= C5, C1, A21, A17, A13, A9, A5, A1, D5, D1, D5, D1

IO2= C6, C2, A22, A18, A14, A10, A6, A2, D6, D2, D6, D2

IO3= C7, C3, A23, A19, A15, A11, A7, A3, D7, D3, D7, D3

11. A0 must be 0 for Word Read 4xI/O. A0-A3 must be 0 for Octal Word Read.

### **Tables of ID Definition:**

### Table-9 ZD25Q16C

| Operation Code | MID7-MID0 | ID15-ID8 | ID7-ID0 |

|----------------|-----------|----------|---------|

| 9FH            | ВА        | 60       | 15      |

| 90H/92H/94H    | ВА        |          | 14      |

| ABH            |           |          | 14      |

18

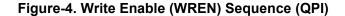

### 4.1 Write Enable (WREN) (06H)

The Write Enable (06H) command sets the Write Enable Latch (WEL) bit. The WEL bit must be set prior to every Page Program, Page Erase, Sector Erase, Half Block Erase, Block Erase, Chip Erase, Write Status Register and Erase/Program Security Register command. The WREN command is entered by driving Chip Select (CS#) Low, sending the command code, and then driving CS# High.

Figure-3. Write Enable Sequence Diagram

SO

High-Z

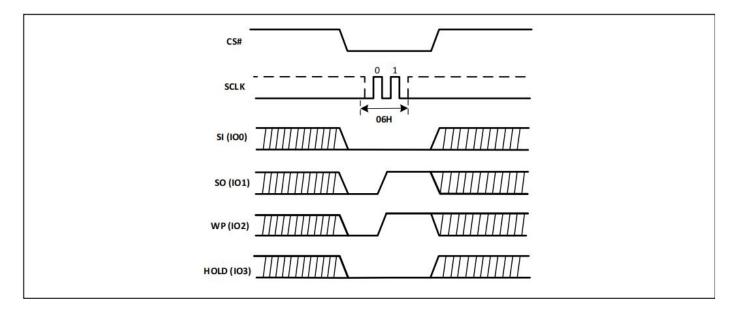

### 4.2 Write Disable (WRDI) (04H)

The Write Disable (04H) command resets the Write Enable Latch (WEL) bit in the Status Register to 0. The WRDI command is entered by driving Chip Select (CS#) low, shifting the command code "04h" into the SI pin and then driving CS# high. Note that the WEL bit is automatically reset after Power-up and upon completion of the Write Status Register, Page Program, Page Erase, Sector Erase, Half Block Erase, Block Erase, Chip Erase, Erase/Program Security Register and Reset commands.

Figure-5. Write Disable Sequence Diagram

### 4.3 Write Enable for Volatile Status Register (50H)

The non-volatile Status Register bits can also be written to as volatile bits. During power up reset, the non-volatile Status Register bits are copied to a volatile version of the Status Register that is used during device operation. This provides more flexibility to change the system configuration and memory protection schemes quickly without waiting for the typical non-volatile bit write cycles or affecting the endurance of the Status Register non-volatile bits.

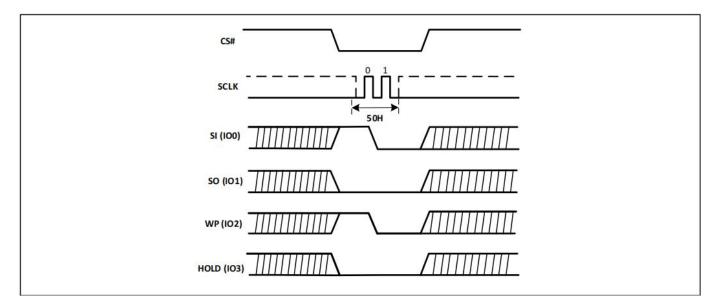

To write the volatile version of the Status Register bits, the Write Enable for Volatile Status Register (50H) command must be issued and immediately followed by the Write Status Register (01H/11H/31H) command. Write Enable for Volatile Status Register command (Figure-7) will not set the Write Enable Latch (WEL) bit, it is only valid for the next Write Status Register command, to change the volatile Status Register bit values.

Figure-7. Write Enable for Volatile Status Register Sequence Diagram

Figure-8. Write Enable for Volatile Status Register Sequence Diagram (QPI)

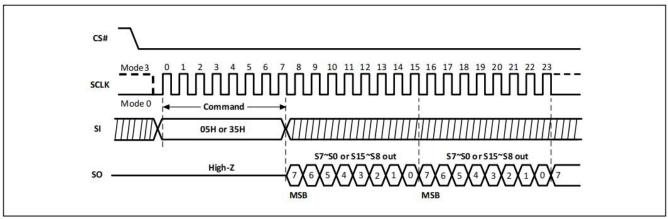

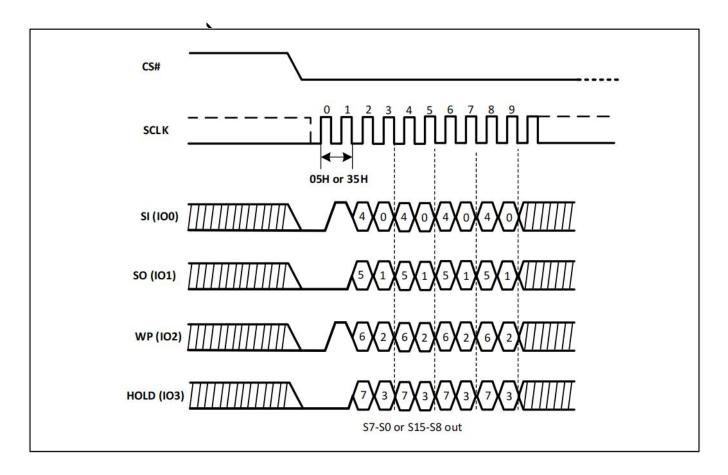

### 4.4 Read Status Register (RDSR) (05H, 35H)

The Read Status Register (05H or 35H) command allows the Status Register to be read. The Status Register may be read at any time, even while a Program, Erase or Write Status Register cycle is in progress. When one of these cycles is in progress, it is recommended to check the Write In Progress (WIP) bit before sending a new command to the device. It is also possible to read the Status Register continuously. For command code "05H", the SO will output Status Register bits S7~S0. And for command code "35H", the SO will output Status Register bits S15~S8.

The sequence of issuing RDSR instruction is: CS# goes low→ sending RDSR instruction code→ Status Register data out on SO.

Figure-9. Read Status Register Sequence Diagram

Figure-10. Read Status Register Sequence Diagram (QPI)

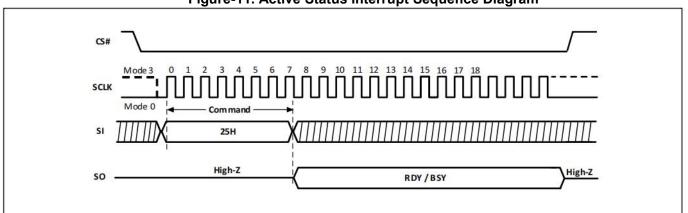

### 4.5 Active Status Interrupt (ASI) (25H)

The Active Status Interrupt (25h) command provides an alternative method to read the Write In Progress (WIP) bit. The SO pin outputs the WIP bit continuously with the ASI command. The SO pin can be connected to an interrupt line of the host controller, and the host controller remains in sleep mode until the SO pin indicates that the device is ready for the next command.

The WIP bit can be read at any time, including while an internally self-timed program or erase operation is in progress. To enable the ASI command, the CS# pin must first be asserted and the opcode of 25h must be clocked into the device.

The value of WIP is then output on the SO pin and is continuously updated by the device for as long as the CS# pin remains asserted. Additional clocks on the SCLK pin are not required. If the WIP bit changes from 1 to 0 while the CS# pin is asserted, the SO pin will change from 1 to 0 when the program/erase operation is completed. (The WIP bit cannot change from 0 to 1 during an operation, so if the SO pin already is 0, it will not change.)

Deserting the CS# pin will terminate the ASI operation and put the SO pin into a high-impedance state. The CS# pin can be deserted at any time and does not require that a full byte of data be read.

The sequence of issuing ASI command is: CS# goes low -> send Active Status Interrupt (25H) command code -> Write In Progress (WIP) data out on SO.

Figure-11. Active Status Interrupt Sequence Diagram

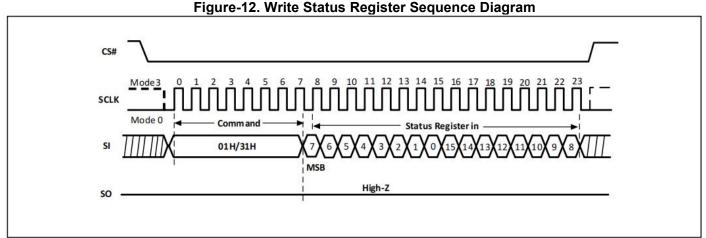

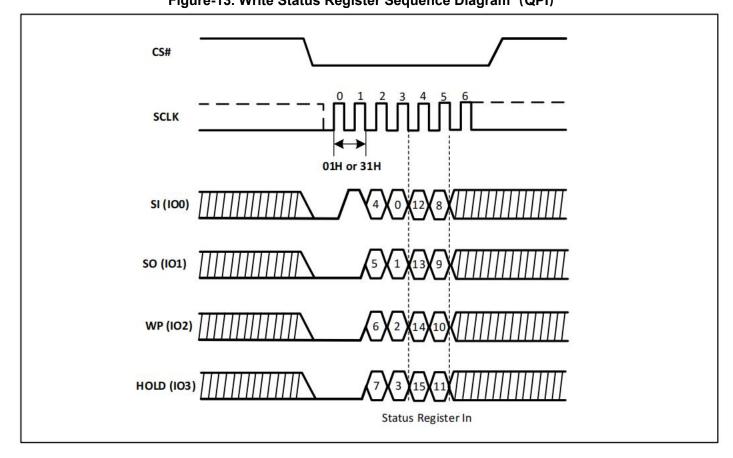

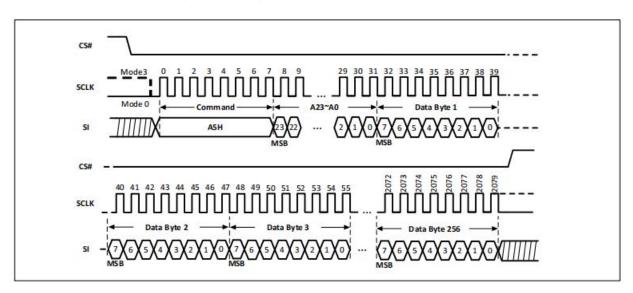

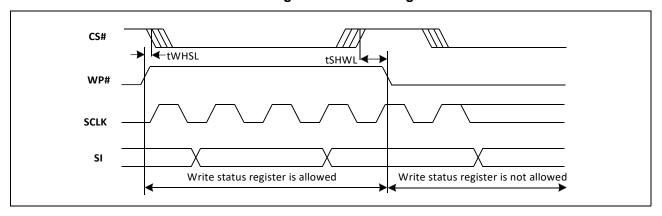

### 4.6 Write Status Register (WRSR) (01H or 31H)

WRSR can write 8bits or 16bits data. The Write Status Register (01H for one byte or two bytes, 31H for one byte only) command allows new values to be written to the Status Register. Command 01H is used to write S7~S0 (one byte) or S15~S0(two bytes). Command 31H is used to write S15~S8. Before the command can be accepted, a Write Enable (06H) command must previously have been executed. After the Write Enable command has been decoded and executed, the device sets the Write Enable Latch (WEL).

The WRSR command is entered by driving Chip Select (CS#) Low, followed by the command code and the data byte on Data Input (SI).

The WRSR command has no effect on S15, S10, S1 and S0 of the Status Register. CS# must be driven high after the sixteenth bit or eighth bit of the data byte has been latched in. If not, the WRSR command is not executed. As soon as CS# is driven High, the self-timed Write Status Register cycle (whose duration is tW) is initiated. While the Write Status Register cycle is in progress, the Status Register may still be read to check the value of the Write In Progress (WIP) bit. The WIP bit is 1 during the self-timed Write Status Register cycle and is 0 when it is completed. When the cycle is completed, the WEL bit is reset.

The WRSR command allows the user to change the values of the Block Protect (BP4, BP3, BP2, BP1,

BP0) bits. The WRSR command also allows the user to set or reset the Status Register Protect (SRP1 and SRP0) bits in accordance with the Write Protect (WP#) signal. The Status Register Protect (SRP1 and SRP0) bits and WP# signal allow the device to be put in the Hardware Protection Mode. The WRSR command is not executed once the Hardware Protection Mode is entered.

CS# must go high exactly at the 8bit or 16bit data boundary; otherwise the command will be rejected and not executed. The self-timed Write Status Register cycle time (tW) is initiated as soon as CS# goes high. The WIP bit still can be checked during the Write Status Register cycle is in progress. The WIP is set to 1 during tW and is reset to 0 along with the WEL bit when Write Status Register Cycle is completed.

Figure-13. Write Status Register Sequence Diagram (QPI)

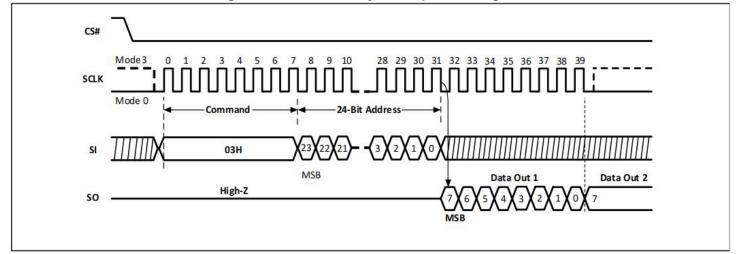

### 4.7 Read Data Bytes (READ) (03H)

The device is first selected by driving Chip Select (CS#) Low. The command code for the Read Data Bytes (03H) command is followed by a 3-byte address (A23-A0), with each bit latched-in on the rising edge of Serial Clock (SCLK). Then the memory contents, at that address, is shifted out on Data Output (SO), with each bit shifted out at a maximum frequency fR on the falling edge of SCLK.

The command sequence is shown in Figure-14. The first byte addressed can be at any location. The address is automatically incremented to the next higher address after each byte of data is shifted out. The whole memory can, therefore, be read with a single READ command. When the highest address is reached, the address counter rolls over to 000000h, allowing the read sequence to be continued indefinitely.

The READ command is terminated by driving CS# High. CS# can be driven High at any time during data output. Any READ command to the memory array, while an Erase, Program or Write cycle is in progress, is rejected without having any effects on the cycle that is in progress.

Figure-14. Read Data Bytes Sequence Diagram

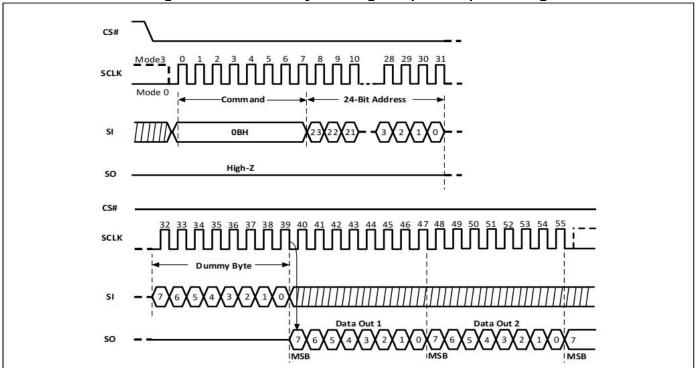

### 4.8 Read Data Bytes at Higher Speed (FAST\_READ) (0BH)

The device is first selected by driving Chip Select (CS#) Low. The command code for the Read Data Bytes at Higher Speed (0BH) command is followed by a 3-byte address (A23-A0) and a dummy byte, each bit being latched-in on the rising edge of Serial Clock (SCLK). Then the memory contents, at that address, is shifted out on Data Output (SO), with each bit shifted out at a maximum frequency fC on the falling edge of SCLK.

The command sequence is shown in Figure-15. The first byte addressed can be at any location. The address is automatically incremented to the next higher address after each byte of data is shifted out. The whole memory can, therefore, be read with a single FAST\_READ command. When the highest address is reached, the address counter rolls over to 000000h, allowing the read sequence to be continued indefinitely.

The FAST\_READ command is terminated by driving CS# High. CS# can be driven High at any time during data output. Any FAST\_READ command, while an Erase, Program or Write cycle is in progress, is rejected without having any effects on the cycle that is in progress.

Figure-15. Read Data Bytes at Higher Speed Sequence Diagram

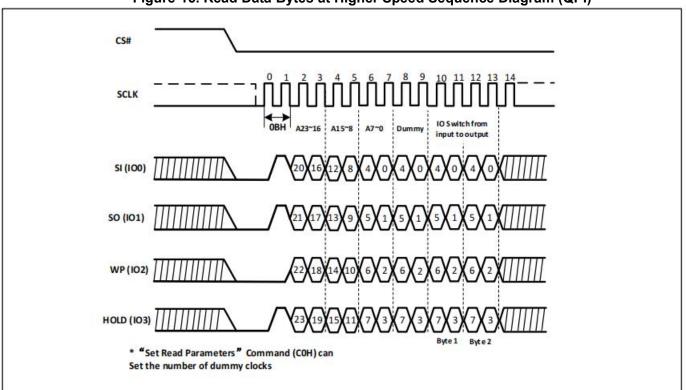

### Read Data Bytes at Higher Speed in QPI mode

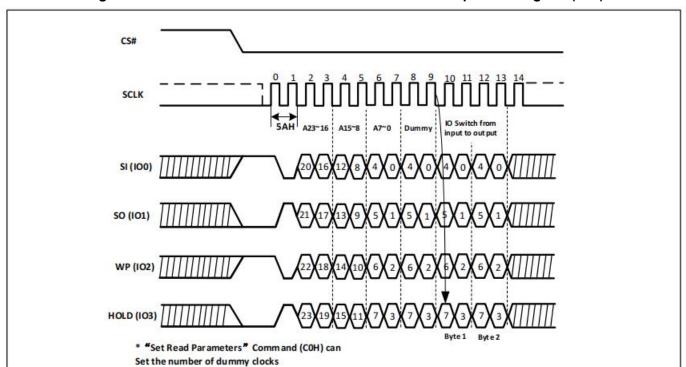

The Fast Read command is also supported in QPI mode. In QPI mode, the number of Dummy Cycles is configured by the "Set Read Parameters (C0H)" command to accommodate a wide range application with different needs for either maximum Fast Read frequency or minimum data access latency. Depending on the Read Parameter Bits P[5:4] setting, the number of Dummy Cycles can be configured as either 4/6/8.

Figure-16. Read Data Bytes at Higher Speed Sequence Diagram (QPI)

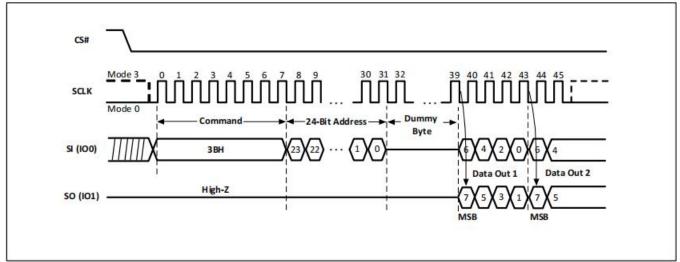

### 4.9 Dual Output Fast Read (DREAD) (3BH)

The Dual Output Fast Read (3BH) is similar to the standard Fast Read (0BH) command except that data is output on two pins, SI (IO0) and SO (IO1), instead of just SO. This allows data to be transferred from the ZD25Q16C at twice the rate of standard SPI devices. The DREAD command is ideal for quickly downloading code from the flash to RAM upon power-up or for applications that cache code-segments to RAM for execution. Like the Fast Read command, the DREAD command can operate at the highest possible frequency of fT. This is accomplished by adding eight "Dummy Cycles after the 24-bit address as shown in Figure-17. The Dummy Cycles allow the device's internal circuits the time required for setting up the initial address. The input data during the Dummy Cycle is "don't care". However, the SI pin should be in a high-impedance state prior to

the falling edge of SLCK for the first data out.

Figure-17. Dual Output Fast Read Sequence Diagram

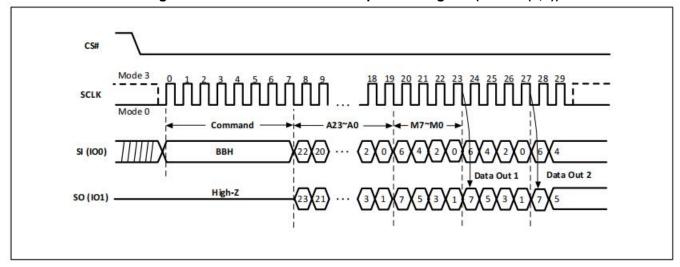

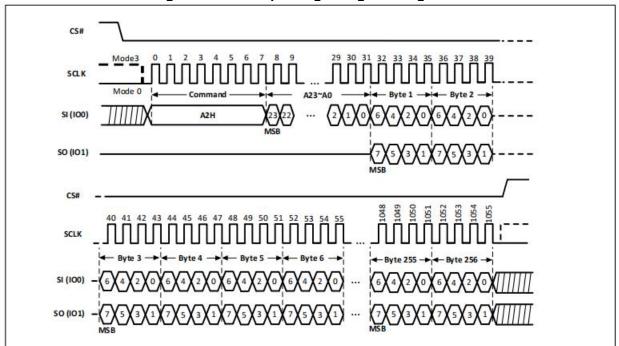

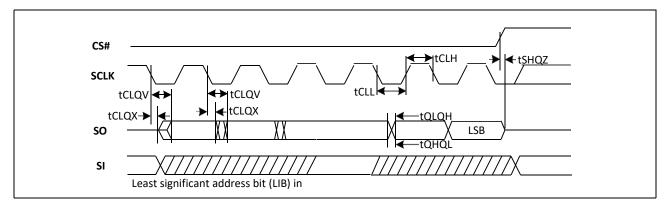

### 4.10 Dual I/O Fast Read (2READ) (BBH)

The Dual I/O Fast Read (BBH) command allows for improved random access while maintaining two IO pins, SI (IO0) and SO (IO1). It is similar to the Dual Output Fast Read (3BH) command but with the ability to input the address bits (A23-0) two bits per clock. This reduced command overhead may allow for code execution (XIP) directly from the Dual SPI in some applications.

The 2READ command enables double throughput of Serial Flash in read mode. The address is latched on rising edge of SCLK, and two bits of data (interleave 2 I/O pins) are shifted out on the falling edge of SCLK at a maximum frequency fT. The first address can be at any location. The address is automatically increased to the next higher address after each byte data is shifted out, so the whole memory can be read out with a single 2READ command. The address counter rolls over to 0 when the highest address has been reached. The 2READ command is shown in Figure-18.

Figure-18. Dual I/O Fast Read Sequence Diagram (M5-4 ≠ (1,0))

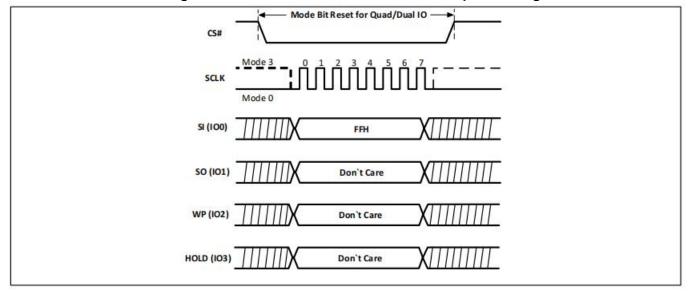

### Dual I/O Fast Read with "Continuous Read Mode" (BBH)

The Dual I/O Fast Read (BBH) command supports Dual I/O Fast Read with "Continuous Read Mode" which can further reduce command overhead by setting the "Continuous Read Mode" bits (M7-0) after the input 3-byte address (A23-A0). If the "Continuous Read Mode" bits (M5-4) = (1, 0), then the next Dual I/O Fast Read command (after CS# is raised and then lowered) does not require the BBH command code.

If the "Continuous Read Mode" bits (M5-4) do not equal (1, 0), the next command requires the first BBH command code, thus returning to normal operation. A "Continuous Read Mode" Reset command can be used to reset (M5-4) before issuing a normal command.

Figure-19. Dual I/O Fast Read with "Continuous Read Mode" Sequence Diagram (M5-4 = (1,0))

**Note**: Dual I/O Fast Read with "Continuous Read Mode", if (M5-4)=(1,0). If not using "Continuous Read Mode" recommend setting (M5-4)≠(1,0).

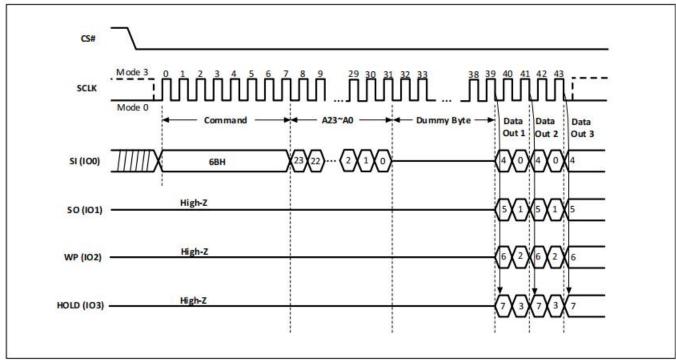

### 4.11 Quad Output Fast Read (QREAD) (6BH)

The Quad Output Fast Read (6BH) command is similar to the Dual Output Fast Read (3BH) command except that data is output on four pins, IO0, IO1, IO2, and IO3. A Quad Enable (QE) of Status Register-2 must be executed before the device will accept the QREAD Command. (The QE bit must equal "1"). The QREAD Command allows data to be transferred at four times the rate of standard SPI devices.

The QREAD command can operate at a higher frequency than the traditional Read Data command. This is accomplished by adding eight "dummy" Cycles after the 24-bit address as shown in Figure-20. The Dummy Cycles allow the device's internal circuits the time required for setting up the initial address. The input data during the Dummy Cycles is "don't care." However, the IO pins should be in a high-impedance state prior to the falling edge of SCLK for the first data out.

Figure-20. Quad Output Fast Read Sequence Diagram

### Quad I/O Fast Read with "Continuous Read Mode" (EBH)

The Quad I/O Fast Read (EBH) command supports Quad I/O Fast Read with "Continuous Read Mode" which can further reduce command overhead by setting the "Continuous Read Mode" bits (M7-0) after the input 3-byte address (A23-A0). If the "Continuous Read Mode" bits (M5-4) = (1, 0), then the next Quad I/O Fast Read (EBH) command (after CS# is raised and then lowered) does not require the EBH command code.

If the "Continuous Read Mode" bits (M5-4) do not equal (1, 0), the next command requires the first EBH command code, thus returning to normal operation. A "Continuous Read Mode" Reset command can be used to reset (M5-4) before issuing a normal command.

Figure-21. Quad I/O Fast Read with "Continuous Read Mode" Sequence Diagram (M5-4 = (1,0))

**Note**: Quad I/O Fast Read with "Continuous Read Mode", if (M5-4)=(1,0). If not using "Continuous Read Mode" recommend setting (M5-4) $\neq$ (1,0).

### Quad I/O in QPI mode

The Quad I/O Fast Read command is also supported in QPI mode. In QPI mode, the number of Dummy Cycles is configured by the "Set Read Parameters (C0H)" command to accommodate a wide range application with different needs for either maximum Fast Read frequency or minimum data access latency. Depending on the Read Parameter Bits P[5:4] setting, the number of Dummy Cycles can be configured as either 4/6/8. In QPI mode, the "Continuous Read Mode" bits M7-M0 are also considered as Dummy Cycles. "Continuous Read Mode" feature is also available in QPI mode for Quad I/O Fast Read command. "Wrap Around" feature is not available in QPI mode for Quad I/O Fast Read command. To perform a read operation with fixed data length wrap around in QPI mode, a dedicated "Burst Read with Wrap" (0CH) command must be used.

Figure-22. Quad I/O Read in QPI Mode Sequence (M5-4 ≠ (1,0))

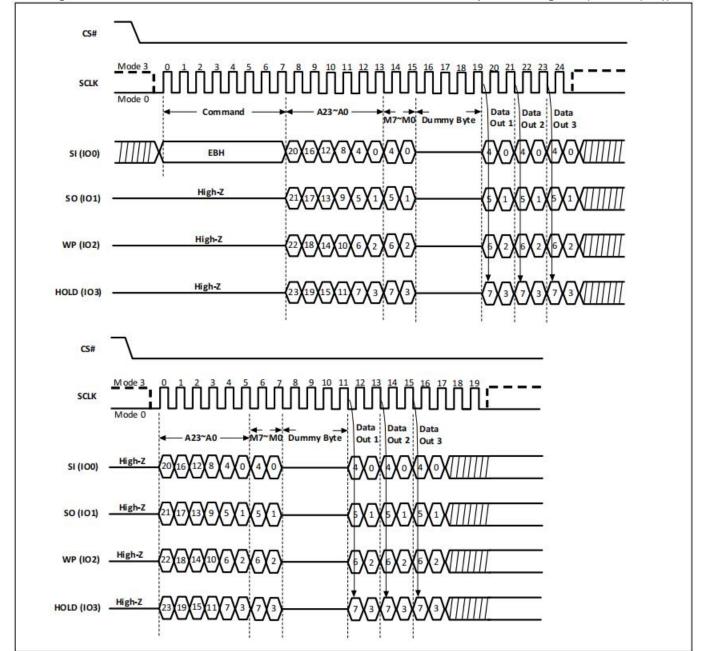

### 4.12 Quad I/O Fast Read (4READ) (EBH)

The Quad I/O Fast Read (EBH) command is similar to the Dual I/O Fast Read (BBH) command except that address and data bits are input and output through four pins, SI (IO0), SO (IO1), WP (IO2) and HOLD (IO3). Six Dummy Cycles are required prior to the data output. A Quad Enable (QE) of Status Register-2 must be executed before the device will accept the 4READ Command. (The QE bit must equal "1"). The Quad I/O dramatically reduces command overhead allowing faster random access for code execution (XIP) directly from the Quad SPI.

The 4READ command enables quad throughput of Serial Flash in read mode. The address is latched on rising edge of SCLK, and data four bits of data (interleave on 4 I/O pins) shift out on the falling edge of SCLK at a maximum frequency fQ. The first address can be any location. The address is automatically increased to the next higher address after each byte data is shifted out, so the whole memory can be read out with a single 4READ command. The address counter rolls over to 0 when the highest address has been reached. Once writing 4READ command, the following address / dummy / data out will transfer 4-bits per clock cycle instead of the previous 1-bit.

The sequence of issuing 4READ command is: CS# goes low -> send Quad I/O Fast Read (EBH) command -> 24-bit address interleave on IO3, IO2, IO1 and IO0 -> 2+4 dummy cycles -> data out interleave on IO3, IO2, IO1 and IO0 -> end 4READ operation by driving CS# high at any time during data out, as shown in Figure-23.

Another sequence of issuing 4READ command especially useful in random access is: CS# goes low -> send Quad I/O Fast Read (EBH) command -> 24-bit address interleave on IO3, IO2, IO1 and IO0 -> "Continuous Read Mode" byte M[7:0] -> 4 dummy cycles -> data out until CS# goes high -> CS# goes low (reduce 4READ command) -> 24-bit random access address.

In the Continuous Read Mode, the "Continuous Read Mode" bits M[5:4] = (1,0) can make this mode continue and reduce the next 4READ command. Once  $M[5:4] \neq (1,0)$  and after CS# is raised and then lowered, the system then will escape from the enhanced performance mode and return to normal operation. A "Continuous Read Mode" Reset command can be used to reset (M5-4) before issuing normal commands. While Program/Erase/Write Status Register cycle is in progress, the 4READ command is rejected without any impact

on the Program/Erase/Write Status Register operation.

Figure-23. Quad I/O Fast Read Sequence Diagram (M5-4 ≠ (1,0))

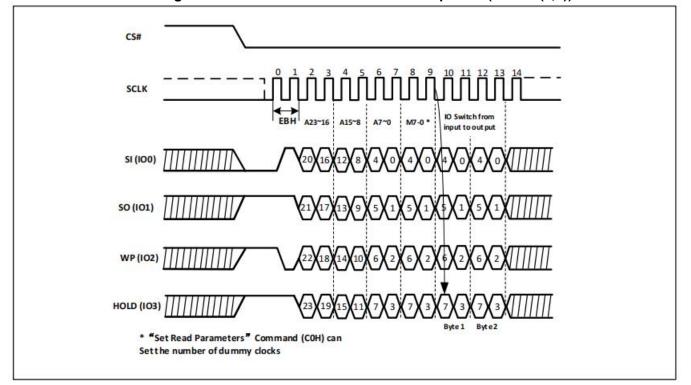

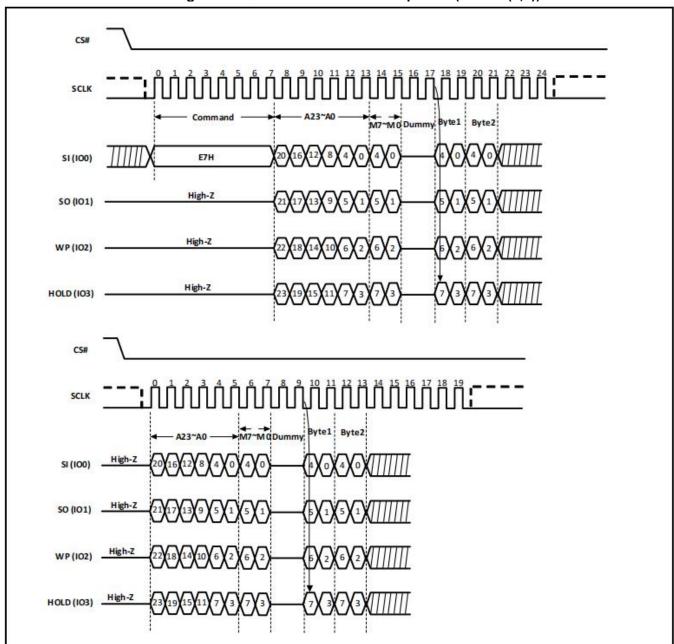

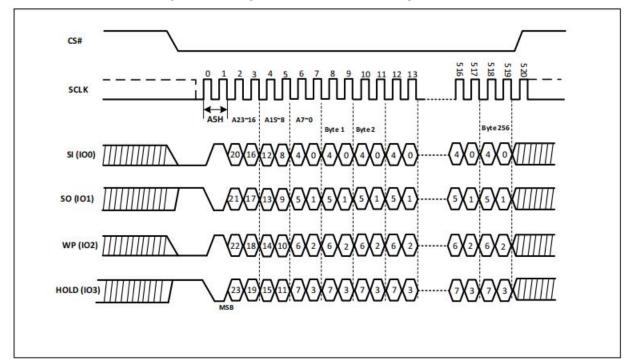

### 4.13 Quad I/O Word Read (E7H)

The Quad I/O Word Read command is similar to the Quad I/O Read command except that the lowest address bit (A0) must equal 0 and only 2-Dummy Cycle. The first byte addressed can be at any location. The address is automatically incremented to the next higher address after each byte of data is shifted out. The Quad Enable bit (QE) of Status Register (S9) must be set to enable for the Quad I/O Word read command.

Figure-24. Quad I/O Word Read Sequence (M5-4 ≠ (1,0))

#### Quad I/O Word Read with "Continuous Read Mode"

The Quad I/O Word Read command can further reduce command overhead through setting the "Continuous Read Mode" bits (M7-0) after the input 3-byte address (A23-A0). If the "Continuous Read Mode" bits (M5-4) = (1, 0), then the next Quad I/O Word Read command (after CS# is raised and then lowered) does not require the E7H command code. If the "Continuous Read Mode" bits (M5-4) do not equal to (1, 0), the next command requires the first E7H command code, thus returning to normal operation. A "Continuous Read Mode" Reset command can be used to reset (M5-4) before issuing normal command.

Figure-25. Quad I/O Word Read Sequence (M5-4 = (1,0))

### Quad I/O Word Read with "8/16/32/64-Byte Wrap Around" in Standard SPI mode

The Quad I/O Word Read command can be used to access a specific portion within a page by issuing "Set Burst with Wrap" (77H) commands prior to E7H. The "Set Burst with Wrap" (77H) command can either enable or disable the "Wrap Around" feature for the following E7H commands. When "Wrap Around" is enabled, the data being accessed can be limited to either an8/16/32/64-byte section of a 256-byte page. The output data starts at the initial address specified in the command, once it reaches the ending boundary of the 8/16/32/64-byte section, the output will wrap around the beginning boundary automatically until CS# is pulled high to terminate the command.

The Burst with Wrap feature allows applications that use cache to quickly fetch a critical address and then fill the cache afterwards within a fixed length (8/16/32/64-byte) of data without issuing multiple read commands. The "Set Burst with Wrap" command allows three "Wrap Bits" W6-W4 to be set. The W4 bit is used to enable or disable the "Wrap Around" operation while W6-W5 is used to specify the length of the wrap around section within a page.

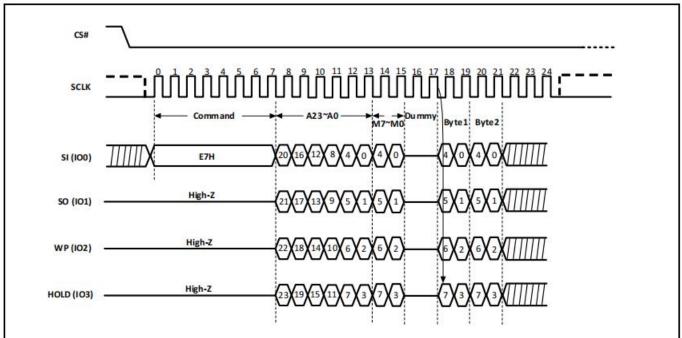

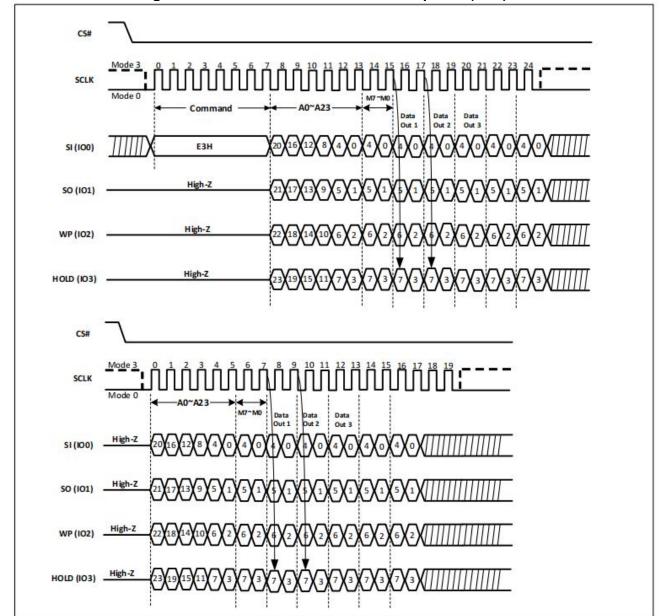

### 4.14 Quad I/O Octal Word Read (E3H)

The Quad IO Octal Word Read (E3h) instruction is similar to the Quad IO Read (EBH) instruction except that the lower four Address bits (A0, A1, A2, A3) must equal 0. As a result, the Dummy Cycles are not required, which further reduces the instruction overhead allowing even faster random access for code execution (XIP). The Quad Enable bit (QE) of Status Register-2 must be set to enable the Octal Word Read Quad I/O Instruction.

### Quad IO Octal Word Read with "Continuous Read Mode"

The Quad IO Octal Word Read instruction can further reduce instruction overhead through setting the "Continuous Read Mode" bits (M7-0) after the input Address bits (A23-0). The upper nibble of the (M7-4) controls the length of the next Octal Word Read Quad I/O instruction through the inclusion or exclusion of the first byte instruction code. The lower nibble bits of the (M3-0) are don't care ("x"). However, the IO pins should be high-impedance prior to the falling edge of the first data out clock.

If the "Continuous Read Mode" bits M5-4 = (1,0), then the next Fast Read Quad I/O instruction (after CS# is raised and then lowered) does not require the E3h instruction code, as shown in Figure 26. This reduces the instruction sequence by eight clocks and allows the Read address to be immediately entered after CS# is asserted low. If the "Continuous Read Mode" bits M5-4 do not equal to (1,0), the next instruction (after CS# is raised and then lowered) requires the first byte instruction code, thus returning to normal operation. It is recommended to input FFH on IO0 for the next instruction (8 clocks), to ensure M4 = 1 and return the device to normal operation.

Figure 26. Quad I/O Octal Word Read Sequence(E3H)

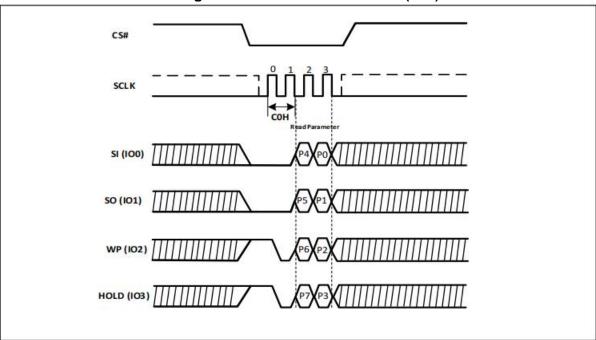

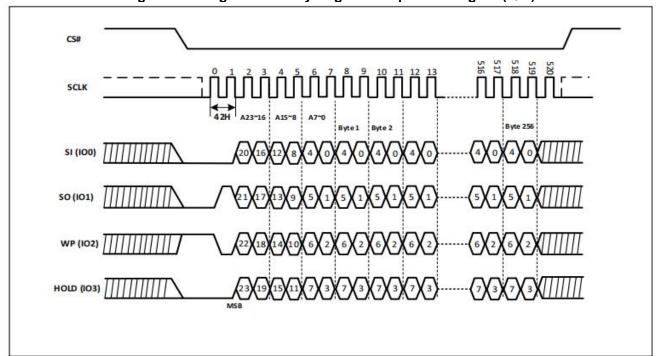

### 4.15 Set Read Parameters (C0H)

In QPI mode the "Set Read Parameters (C0H)" command can be used to configure the number of Dummy Cycles for "Fast Read (0BH)", "Quad I/O Fast Read (EBH)", "Read Security Register (48H)", "Read SFDP Mode (5AH)" and "Burst Read with Wrap (0CH)" command, and to configure the number of bytes of "Wrap Length" for the "Burst Read with Wrap (0CH)" command. The "Wrap Length" is set by W5-6 bit in the "Set Burst with Wrap (77H)" command. This setting will remain unchanged when the device is switched from Standard SPI mode to QPI mode.

| P5-P4 | Dummy Cycles | Maximum Read Freq. | P1-P0 | Wrap Length |

|-------|--------------|--------------------|-------|-------------|

| 0,0   | 10           | 86MHz              | 0,0   | 8-byte      |

| 0,1   | 4            | 66MHz              | 0,1   | 16-byte     |

| 1,0   | 6            | 66MHz              | 1,0   | 32-byte     |

| 1,1   | 8            | 86MHz              | 1,1   | 64-byte     |

Figure 27. Set Read Parameters (QPI)

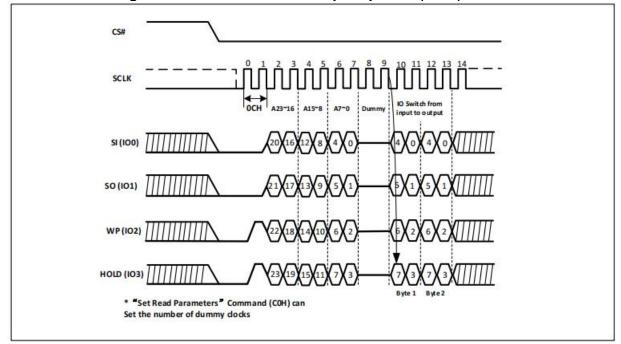

### 4.16 Burst Read with Wrap (0CH)

The "Burst Read with Wrap (0CH)" command provides an alternative way to perform the read operation with "Wrap Around" in QPI mode. This command is similar to the "Fast Read (0BH)" command in QPI mode, except the addressing of the read operation will "Wrap Around" to the beginning boundary of the "Wrap Around" once the ending boundary is reached. The "Wrap Length" and the number of Dummy Cycles can be configured by the "Set Read Parameters (C0H)" command.

Figure 28. Burst Read with Wrap Sequence (QPI)

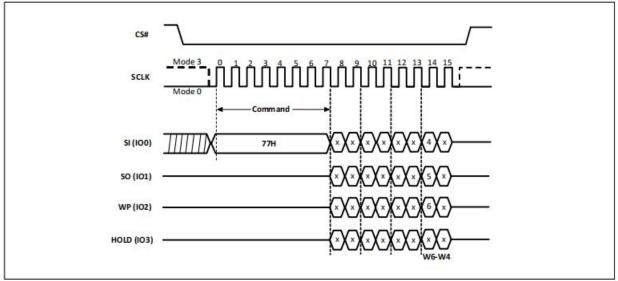

### 4.17 Set Burst with Wrap (77H)

The Set Burst with Wrap (77h) command is used in conjunction with Quad I/O Fast Read (EBH/E7H) command to access a fixed length of 8/16/32/64-byte section within a 256-byte page, in standard SPI mode.

The Set Burst with Wrap command sequence: CS# goes low -> Send Set Burst with Wrap (77h) command -> Send 24 dummy bits-> Send 8 bits "Wrap bits" -> CS# goes high.

If the W6-W4 bits are set by the Set Burst with Wrap command, all the following Quad I/O Fast Read commands will use the W6-W4 setting to access the 8/16/32/64-byte section within any page. To exit the "Wrap Around" function and return to normal read operation, another Set Burst with Wrap command should be issued to set W4=1.

|       | W4=0      |         | W4=1 (d | default) |  |

|-------|-----------|---------|---------|----------|--|

| W6,W5 | Wrap Wrap |         | Wrap    | Wrap     |  |

|       | Around    | Length  | Around  | Length   |  |

| 0,0   | Yes       | 8-byte  | No      | N/A      |  |

| 0,1   | Yes       | 16-byte | No      | N/A      |  |

| 1,0   | Yes       | 32-byte | No      | N/A      |  |

| 1,1   | Yes       | 64-byte | No      | N/A      |  |

Table-10. Burst Length and Wrap

Figure-29. Set Burst with Wrap Sequence Diagram

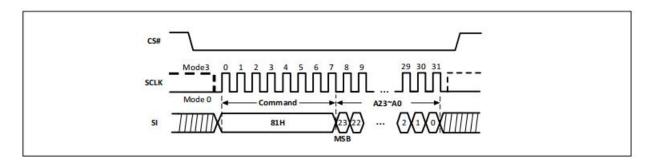

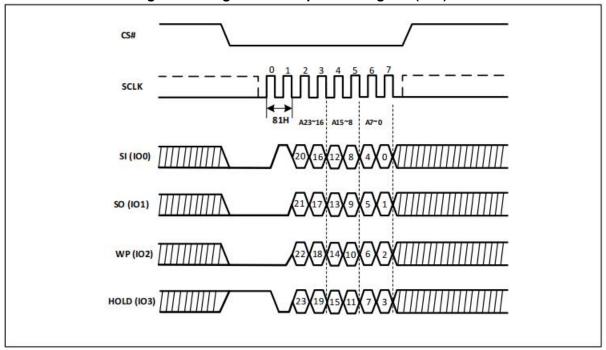

### 4.18 Page Erase (PE) (81H)

The Page Erase (81H) command sets all bits to 1 (FFH) inside the chosen page. Before it can be accepted, a Write Enable (06H) command must have previously been executed. After the Write Enable command has been decoded, the device sets the Write Enable Latch (WEL).

The PE command is entered by driving Chip Select (CS#) Low, followed by the command code, and three address bytes on Data Input (SI). Any address inside the page is a valid address for the PE command. CS# must be driven Low for the entire duration of the sequence.

The command sequence is shown in Figure-30. The CS# must go high exactly at the byte boundary (after the least significant bit of the third address byte is latched-in); otherwise, the command will be rejected and not executed. As soon as CS# is driven High, the self-timed Page Erase cycle (with duration tPE) is initiated. While the Page Erase cycle is in progress, the Status Register may be read to check the value of the Write In Progress (WIP) bit. The WIP bit is 1 during the self-timed Page Erase cycle and is 0 when it is completed. At some unspecified time before the cycle is completed, the WEL bit is reset.

A PE command may be applied only to a page which is not protected by the Block Protect (BP4, BP3, BP2, BP1, BP0) bits.

Figure-30. Page Erase Sequence Diagram

Figure-31. Page Erase Sequence Diagram (QPI)

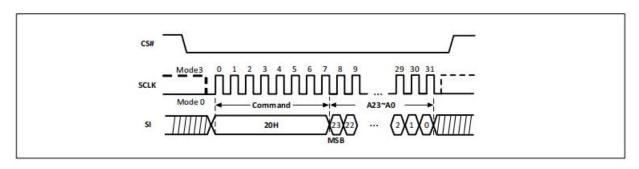

### 4.19 Sector Erase (SE) (20H)

The Sector Erase (20H) command sets all bits to 1 (FFH) inside the chosen sector. Before it can be accepted, a Write Enable (06H) command must have previously been executed. After the Write Enable command has been decoded, the device sets the Write Enable Latch (WEL).

The SE command is entered by driving Chip Select (CS#) Low, followed by the command code, and three address bytes on Data Input (SI). Any address inside the sector is a valid address for the SE command. CS# must be driven Low for the entire duration of the sequence.

The command sequence is shown in Figure-32. The CS# must go high exactly at the byte boundary (after the least significant bit of the third address byte is latched-in); otherwise, the command will be rejected and not executed. As soon as CS# is driven High, the self-timed Sector Erase cycle (with duration tSE) is initiated. While the Sector Erase cycle is in progress, the Status Register may be read to check the value of the Write In Progress (WIP) bit. The WIP bit is 1 during the self-timed Sector Erase cycle and is 0 when it is completed. At some unspecified time before the cycle is completed, the WEL bit is reset.

A SE command may be applied only to a sector which is not protected by the Block Protect (BP4, BP3, BP2, BP1, BP0) bits.

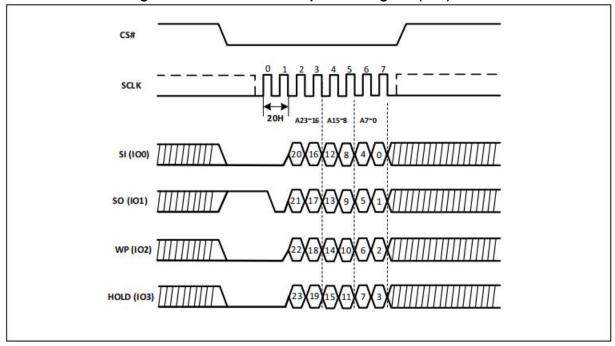

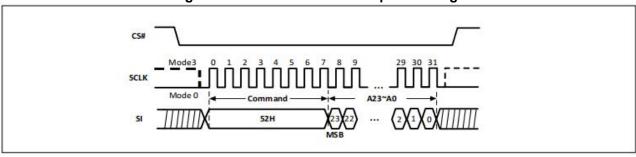

Figure-32. Sector Erase Sequence Diagram

Figure-33. Sector Erase Sequence Diagram (QPI)

The self-timed Sector Erase Cycle time (tSE) is initiated as soon as Chip Select (CS#) goes high. The Write in progress (WIP) bit still can be check out during the Sector Erase cycle is in progress. The WIP sets 1 during the tSE timing, and sets 0 when Sector Erase Cycle is completed, and the Write Enable Latch (WEL) bit is reset. If the sector is protected by BP4, BP3, BP2, BP1, BP0 bits, the Sector Erase (SE) instruction will not be executed on the sector

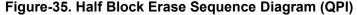

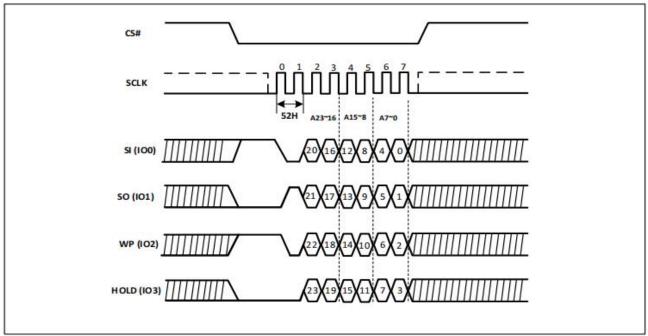

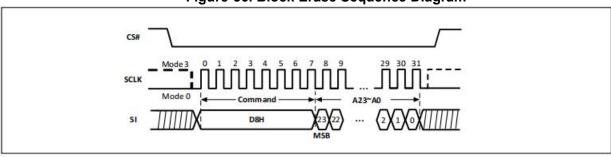

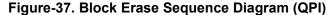

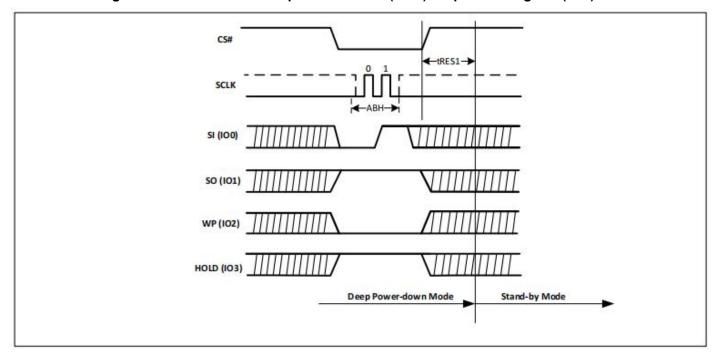

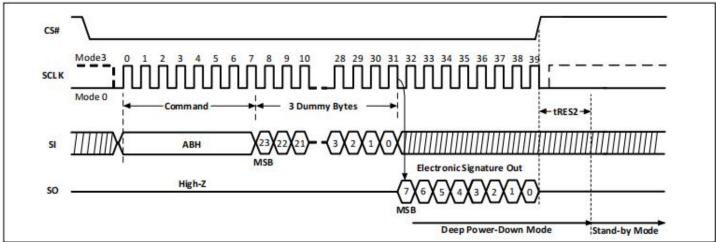

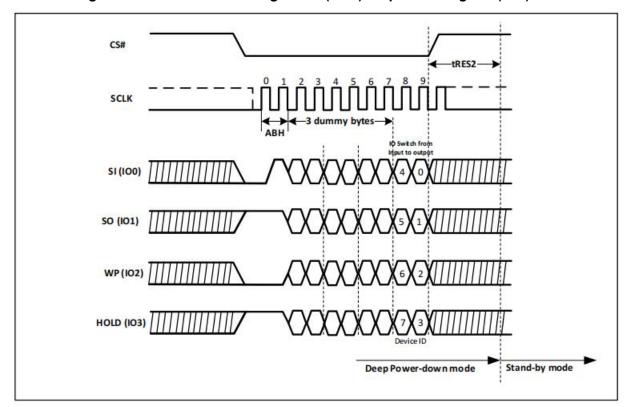

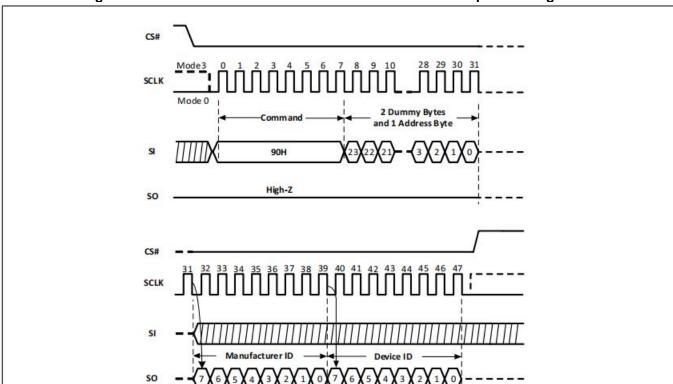

#### 4.20 Half Block Erase (HBE) (52H)