# 6- or 10-Output, 5-Synthesizer Clock Generators

#### Features

#### Highlights

- Any-to-any frequency conversion

- Five output frequency synthesizers

- Inputs: crystal or CMOS input clock

- · Outputs: up to 10 differential, up to 20 CMOS

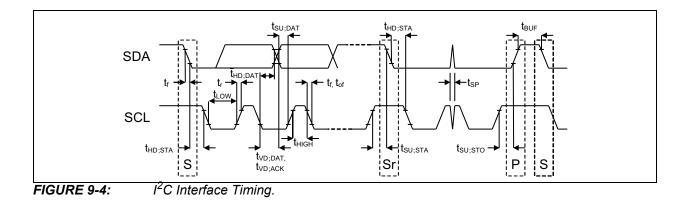

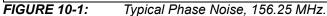

- Output jitter 100 fs<sub>RMS</sub> typical for 156.25 MHz 12 kHz to 20 MHz

- Core power consumption <0.9W

#### Input Clocks

- · Crystal: 24-60 MHz

- OSCB: CMOS 10-400 MHz

#### **Output Clocks**

- Any frequency 0.5 Hz to 750 MHz

- Each OUTP/N pair can be LVDS, LVPECL, 2xC-MOS, Low-V<sub>CM</sub>, or programmable differential

- In 2xCMOS mode, the P and N pins can be different frequencies (e.g. 125 MHz and 25 MHz)

- VDD per output pair, CMOS voltages 1.8V to 3.3V

- Per-synth phase adjustment, 1 ps resolution

- · Per-output duty cycle adjustment

- Precise output alignment circuitry and per-output phase adjustment

- Per-output enable/disable and glitchless start/stop (stop high or low)

#### **General Features**

- Automatic self-configuration at power-up from internal Flash memory, 7 configurations

- Numerically controlled oscillator behavior in each synthesizer

- Easy-to-configure design requires no external VCXO or loop filter components

- 5 GPIO pins with many possible behaviors, each OUT can be GPO

- SPI or I<sup>2</sup>C processor Interface

- 1.8V and 3.3V core VDD voltages

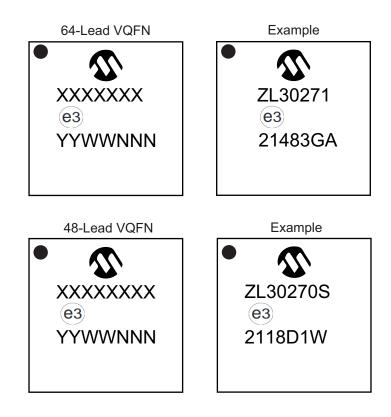

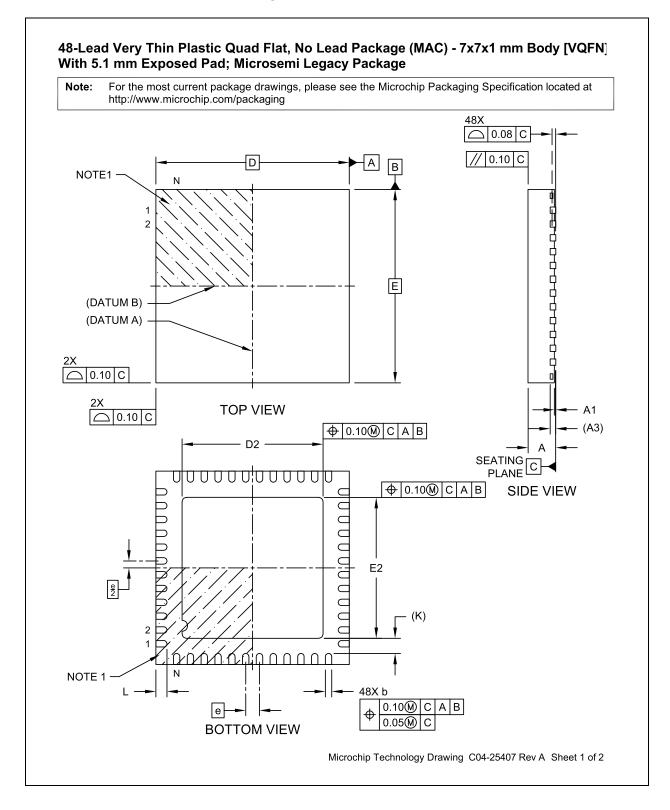

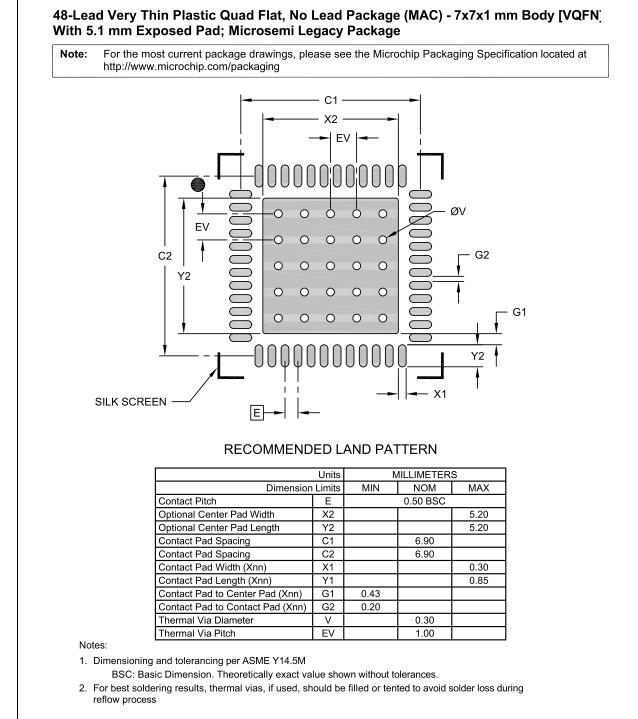

- 48-Lead 7 mm x 7 mm VQFN Package (ZL30270)

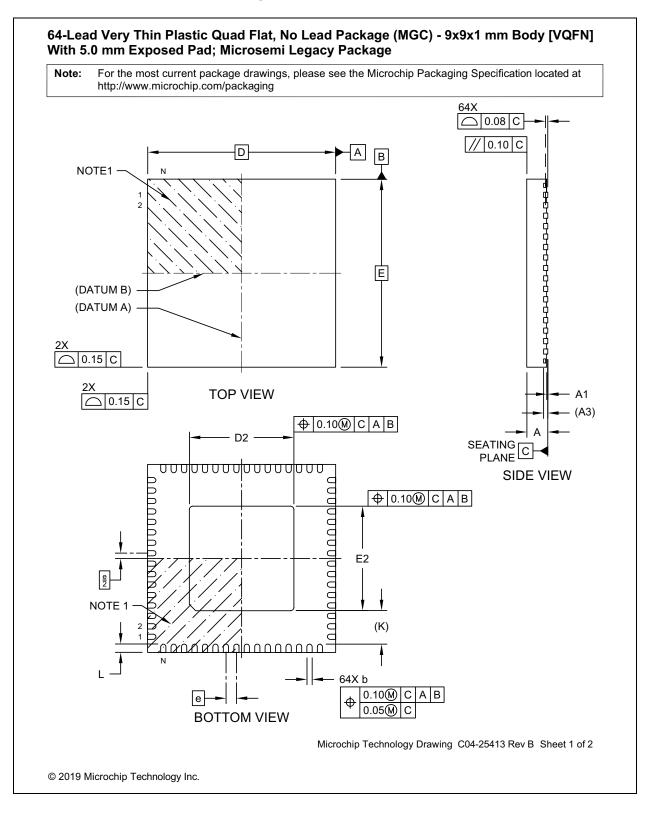

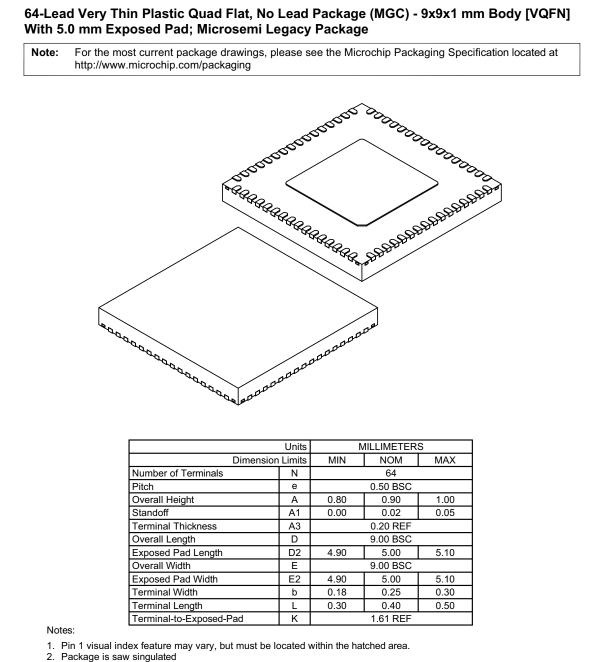

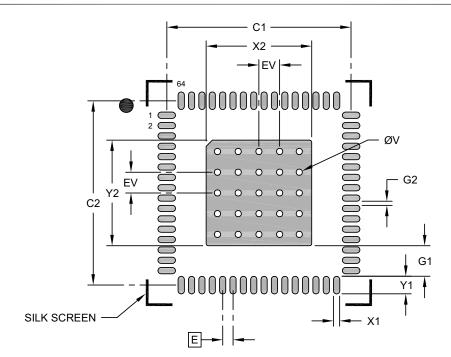

- 64-Lead 9 mm x 9 mm VQFN Package (ZL30271)

- · Easy-to-use evaluation/programming software

#### Applications

• Frequency conversion and frequency synthesis in a wide variety of equipment types

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include -literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

# TABLE OF CONTENTS

| 1.0 Block Diagram                                                                               | 5  |

|-------------------------------------------------------------------------------------------------|----|

| 2.0 Detailed Features                                                                           | 5  |

| 2.1 General                                                                                     | 5  |

| 2.2 Synthesizer Features                                                                        | 5  |

| 2.3 Output Clock Features                                                                       | 5  |

| 2.4 General Features                                                                            | 6  |

| 2.5 Evaluation Software                                                                         | 6  |

| 3.0 Pin Diagrams                                                                                | 7  |

| 4.0 Pin Descriptions                                                                            |    |

| 5.0 Functional Description                                                                      |    |

| •                                                                                               |    |

| 5.1 Output Frequency Synthesizers<br>5.1.1 Synthesizer Enable                                   |    |

| 5.1.2 Synthesizer Nominal Frequency                                                             |    |

| 5.1.3 Synthesizer Frequency Offset and NCO Behavior                                             |    |

| 5.1.4 Spread-Spectrum Modulation                                                                |    |

| 5.1.5 Synthesizer Phase Adjustment                                                              |    |

| 5.2 Output Clocks                                                                               |    |

| 5.2.1 Output Enable, Signal Format, Voltage and Interfacing                                     |    |

| 5.2.2 Output Frequency Configuration                                                            |    |

| 5.2.3 Output Phase Alignment and Phase Adjustment                                               |    |

| 5.2.4 Output Duty Cycle/Pulse Width Adjustment                                                  |    |

| 5.2.5 Output Clock Start/Stop and Squelch<br>5.2.6 Output Clock Pins as General-Purpose Outputs |    |

|                                                                                                 |    |

| 5.3 Crystal or Input Clock<br>5.3.1 External Oscillator                                         |    |

| 5.3.2 External Crystal                                                                          |    |

| 5.3.3 Input Clock Frequency Selection                                                           |    |

| 5.4 Power Supplies                                                                              |    |

| 5.4.1 Power Up/Down Sequence                                                                    |    |

| 5.4.2 Power Supply Filtering                                                                    |    |

| 5.4.3 Power Calculator                                                                          |    |

| 5.5 Reset and Configuration Pins                                                                |    |

| 6.0 Configuration and Control                                                                   |    |

| 6.1 Pre-Configured Default Values on Power-Up                                                   |    |

| 6.2 Configuration Sequence                                                                      |    |

| 6.3 GPIO Configuration                                                                          |    |

| 7.0 Host Interface                                                                              |    |

| 7.0 Host interface                                                                              |    |

| 7.1 Serial Peripheral Interface<br>7.1.1 Least Significant Bit (LSb) First Transmission Mode    |    |

| 7.1.2 Most Significant Bit (MSb) First Transmission Mode                                        |    |

| 7.1.3 SPI Burst Mode Operation                                                                  |    |

| 7.1.4 Interfacing to a 1.8V, 2.5V, or 3.3V SPI Bus                                              | 21 |

| 7.2 I2C Interface                                                                               |    |

| 8.0 Register Map                                                                                |    |

| 8.1 Multi-Byte Register Values                                                                  |    |

| 8.1.1 Time Between Two Write Accesses to the Same Register                                      |    |

| 8.1.2 Time After Change to APLL Related Configuration                                           |    |

| 8.2 Register Map List Summary                                                                   |    |

| 8.2 Register Map List Summary                                                                   |    |

| 9.0 Electrical Characteristics                                                                  |    |

| 10.0 Performance Characteristics                                                                |    |

|                                                                                                 |    |

| 11.0 Package and Thermal Information                                                            |    |

| 12.0 Package Outline                                                                            | 73 |

| 12.1 Package Marking Information | 73 |

|----------------------------------|----|

| 13.0 Acronyms and Abbreviations  | 80 |

# List of Figures

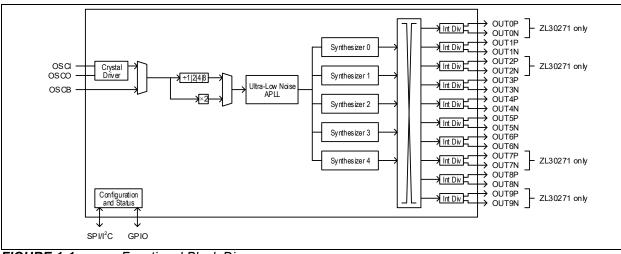

| FIGURE 1-1: Functional Block Diagram.                                        | 5  |

|------------------------------------------------------------------------------|----|

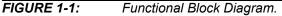

| FIGURE 3-1: 64-Lead 9 mm x 9 mm VQFN (0.5 mm pitch) for ZL30271              | 7  |

| FIGURE 3-2: 48-Lead 7 mm x 7 mm VQFN (0.5 mm pitch) for ZL30270              | 8  |

| FIGURE 5-1: Output Signal External Component Examples.                       | 14 |

| FIGURE 5-2: Crystal Equivalent Circuit/Recommended Crystal Circuit.          |    |

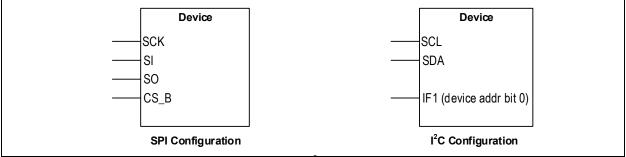

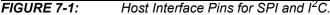

| FIGURE 7-1: Host Interface Pins for SPI and I2C.                             |    |

| FIGURE 7-2: Serial Peripheral Interface Functional Waveform - LSB First Mode |    |

| FIGURE 7-3: Serial Peripheral Interface Functional Waveform - MSB First Mode |    |

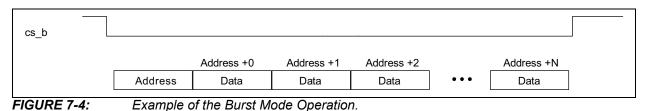

| FIGURE 7-4: Example of the Burst Mode Operation.                             | 21 |

| FIGURE 7-5: I2C Data Write Protocol.                                         | 21 |

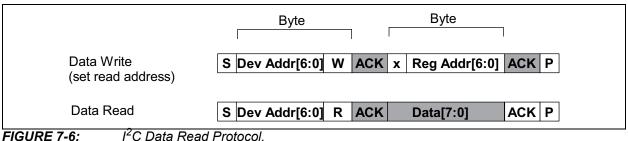

| FIGURE 7-6: I2C Data Read Protocol.                                          |    |

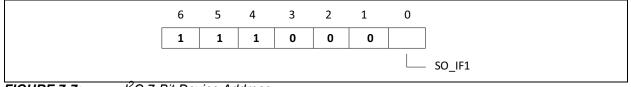

| FIGURE 7-7: I2C 7-Bit Device Address.                                        | 21 |

| FIGURE 7-8: I2C Data Write Burst Mode.                                       |    |

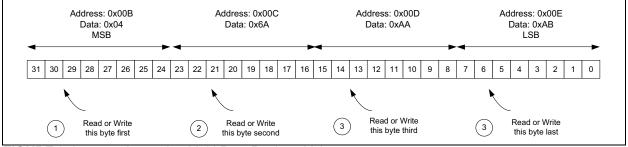

| FIGURE 8-1: Accessing Multi-Byte Register Value.                             |    |

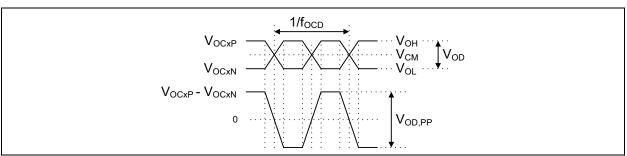

| FIGURE 9-1: Electrical Characteristics: Differential Clock Outputs.          | 64 |

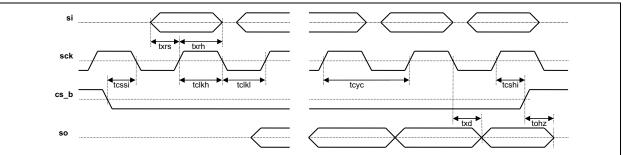

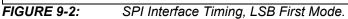

| FIGURE 9-2: SPI Interface Timing, LSB First Mode                             |    |

| FIGURE 9-3: SPI Interface Timing, MSB First Mode.                            |    |

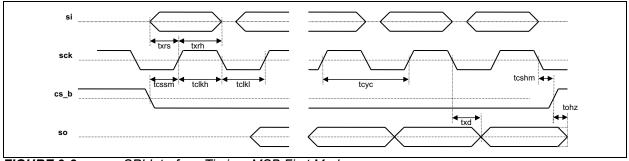

| FIGURE 9-4: I2C Interface Timing.                                            |    |

| FIGURE 10-1: Typical Phase Noise, 156.25 MHz.                                | 71 |

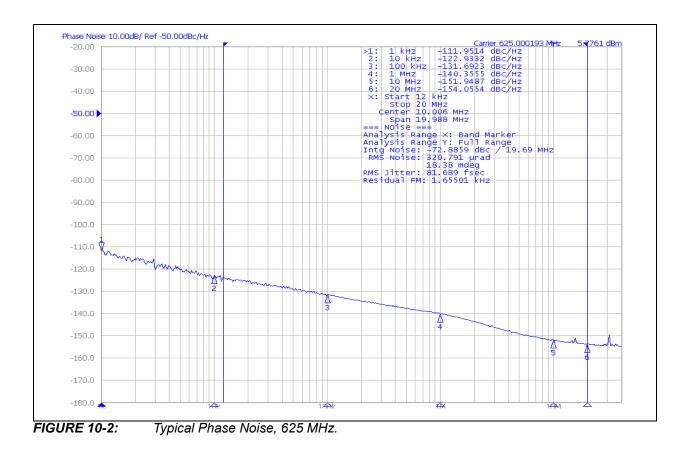

| FIGURE 10-2: Typical Phase Noise, 625 MHz.                                   | 71 |

# **List of Tables**

| TABLE 4-1: Pin Descriptions                                                   |    |

|-------------------------------------------------------------------------------|----|

| TABLE 5-1: Crystal Selection Parameters                                       | 17 |

| TABLE 7-1: Serial Interface Selection                                         | 19 |

| TABLE 8-1: Top-Level Register Map                                             | 24 |

| TABLE 9-1: Absolute Maximum Ratings                                           | 62 |

| TABLE 9-2: Recommended DC Operating Conditions                                | 62 |

| TABLE 9-3: Electrical Characteristics: Supply Currents                        | 61 |

| TABLE 9-4: Electrical Characteristics: OSCB Clock Input                       | 63 |

| TABLE 9-5: Electrical Characteristics: Other Inputs and I/O (Bidirectional)   | 64 |

| TABLE 9-6: Electrical Characteristics: OUTP/N LVDS Clock Outputs              | 65 |

| TABLE 9-7: Electrical Characteristics: OUTP/N LVPECL Clock Outputs            | 65 |

| TABLE 9-8: Electrical Characteristics: OUTP/N Low-Vcm clock outputs           |    |

| TABLE 9-9: Electrical Characteristics: OUTP/N CMOS Clock Outputs              | 66 |

| TABLE 9-10: Electrical Characteristics: Other Outputs and I/O (Bidirectional) | 67 |

| TABLE 9-11: Electrical Characteristics: Output-to-Output Timing               | 67 |

| TABLE 9-12: Electrical Characteristics: SPI Interface Timing                  | 68 |

| TABLE 9-13: Electrical Characteristics: I2C Interface Timing                  | 66 |

| TABLE 10-1: Output Clock Jitter Generation – OUTxP/N Differential             |    |

| TABLE 11-1: 9x9 QFN Package Thermal Properties                                |    |

| TABLE 11-2: 7x7 QFN Package Thermal Properties                                | 72 |

## 1.0 BLOCK DIAGRAM

# 2.0 DETAILED FEATURES

#### 2.1 General

- · Operates from a single crystal resonator or clock oscillator

- ≥48 MHz for lowest jitter

- 9.72 MHz to 400 MHz total frequency range

- Configurable via SPI or I<sup>2</sup>C interface

- · Internal nonvolatile memory

- Factory-configurable power-on configuration

- Multiple time writeable/re-writeable

- Default settings can be overridden using SPI/I<sup>2</sup>C

# 2.2 Synthesizer Features

- · Five next-generation low-jitter, low-power, any-frequency synthesizers

- · A total of five output frequency families

- Any-to-any frequency conversion with 0 ppm error

- Easy-to-configure, completely encapsulated design requires no external VCXO or loop filter components

- Jitter suitable for OC-192, STM-64, and 1G, 10G, 40G, 100G, and 400G Ethernet jitter requirements

# 2.3 Output Clock Features

- ZL30270: Up to 12 single-ended outputs, up to 6 differential outputs, from any synthesizer

- ZL30271: Up to 20 single-ended outputs, up to 10 differential outputs, from any synthesizer

- · Each output can be one differential output or two CMOS outputs

- Output clocks can be any frequency from 0.5 Hz to 750 MHz (250 MHz max for CMOS)

- Output jitter 100 fs<sub>RMS</sub> typical for 156.25 MHz and many other frequencies (12 kHz to 20 MHz)

- In CMOS mode, the OUTxN frequency can be an integer divisor of the OUTxP frequency (Example 1: OUT3P 125 MHz, OUT3N 25 MHz. Example 2: OUT2P 25 MHz, OUT2N 1 Hz)

- · Outputs directly interface (DC-coupled) with LVDS, LVPECL, HCSL, and CMOS components

- · Supported telecom frequencies include PDH, SDH, Synchronous Ethernet, OTN

- · Can produce clock frequencies for microprocessors, ASICs, FPGAs, and other components

- Can produce PCIe Gen 1 to 5 clocks

- · Sophisticated output-to-output phase alignment

- Per-synthesizer phase adjustment, 1 ps resolution

- · Per-output phase adjustment to accommodate trace delays or compensate for system routing paths

- Per-output duty cycle/pulse width configuration

- · Per-output enable/disable

- Per-output glitchless start/stop (stop high or low)

- · Each OUT pin can be a GPO (general-purpose output)

#### 2.4 General Features

- · Automatic self-configuration at power-up from internal Flash memory

- · Generates output SYNC signals: 1PPS (IEEE 1588), 2 kHz or 8 kHz (SONET/SDH), or other frequency

- · JESD204B clocking: clock and SYSREF signal generation with skew adjustment

- Numerically controlled oscillator (NCO) behavior allows system software to steer synthesizer frequency with resolution better than 0.005 ppt

- · Spread-spectrum modulation available in each synthesizer (PCIe compliant)

- · Five general-purpose I/O pins each with many possible status and control options

- SPI or I<sup>2</sup>C serial microprocessor interface

#### 2.5 Evaluation Software

- Simple, intuitive Windows-based graphical user interface

- · Supports all device features and register fields

- · Makes lab evaluation of the device quick and easy

- · Generates configuration scripts

- · Works with or without an evaluation board

## 3.0 PIN DIAGRAMS

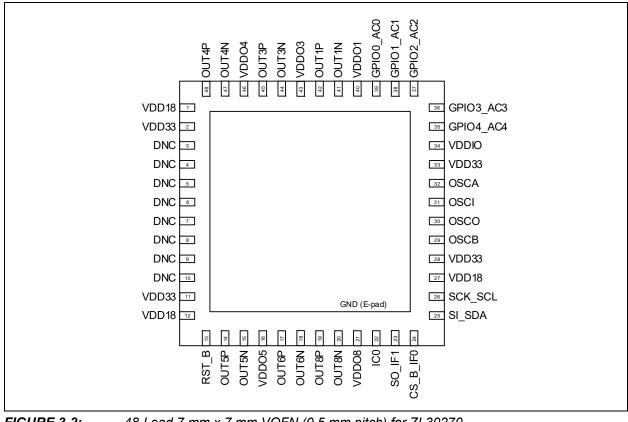

FIGURE 3-1: 64-Lead 9 mm x 9 mm VQFN (0.5 mm pitch) for ZL30271.

FIGURE 3-2:

48-Lead 7 mm x 7 mm VQFN (0.5 mm pitch) for ZL30270.

# 4.0 PIN DESCRIPTIONS

All device inputs and outputs are LVCMOS unless described otherwise. The Type column uses the following symbols: I – input,  $I_{PU}$  – input with internal pull-up resistor,  $I_{OPD}$  – input/output with internal pull-down resistor, O – output, A – analog, P – power supply pin. All GPIO and SPI/I<sup>2</sup>C interface pins have Schmitt-trigger inputs and have output drivers that can be disabled (high impedance).

| 7x7 Pin<br>Number | 9x9 Pin<br>Number | Pin Name | Туре            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                    |   |       |  |

|-------------------|-------------------|----------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|---|-------|--|

| Output C          | locks             |          |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                    |   |       |  |

| _                 | 52                | OUTOP    |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                    |   |       |  |

| —                 | 51                | OUTON    |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                    |   |       |  |

| 42                | 55                | OUT1P    |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                    |   |       |  |

| 41                | 54                | OUT1N    |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                    |   |       |  |

| —                 | 58                | OUT2P    |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                    |   |       |  |

| _                 | 57                | OUT2N    |                 | Outputs Claska                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                    |   |       |  |

| 45                | 61                | OUT3P    |                 | Outputs Clocks<br>LVDS, LVPECL, programmable differential, Low-V <sub>CM</sub> differential (HCSL-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                    |   |       |  |

| 44                | 60                | OUT3N    |                 | like) or 1 or 2 CMOS. Programmable frequency and drive strength. Pro-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                    |   |       |  |

| 48                | 64                | OUT4P    |                 | grammable common-mode voltage and signal amplitude in programmable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                    |   |       |  |

| 47                | 63                | OUT4N    | 0               | differential mode. See Figure 5-1 for example external interface circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                    |   |       |  |

| 14                | 17                | OUT5P    |                 | See Table 9-6, Table 9-7, and Table 9-8 for electrical specifications for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                    |   |       |  |

| 15                | 18                | OUT5N    | -               | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | LVDS, LVPECL, and Low-V <sub>CM</sub> signal format, respectively. |   |       |  |

| 17                | 20                | OUT6P    |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | I                                                                  |   |       |  |

| 18                | 21                | OUT6N    |                 | See Table 9-9 for electrical specifications for interfacing to CMOS inputs on<br>neighboring devices.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                    |   |       |  |

| _                 | 23                | OUT7P    |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                    |   |       |  |

|                   | 24                | OUT7N    | -               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                    | 1 | OUT7N |  |

| 19                | 26                | OUT8P    |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                    |   |       |  |

| 20                | 27                | OUT8N    |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                    |   |       |  |

| _                 | 29                | OUT9P    |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                    |   |       |  |

| _                 | 30                | OUT9N    |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                    |   |       |  |

| Control a         | nd Status         |          |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                    |   |       |  |

| 13                | 16                | RST_B    | I <sub>PU</sub> | <b>Power-on Reset.</b> A logic low at this input resets the device. To ensure proper operation, the device must be reset <u>after</u> power-up by <u>driving</u> the RST_B pin low. The RST_B pin should be held low for at least 2 ms. This pin has an internal 85 k $\Omega$ pull-up to VDD33 (not VDDIO). Device registers can be accessed either 500 ms after RST_B goes high or after bit 7 in register at address 0x00 goes high. Note that the supply rail for RST_B is VDD33 not VDDIO. When the host interface is I <sup>2</sup> C, Microchip recommends RST_B be wired to a general-purpose output pin on an FPGA, microcontroller or other software-controlled component. |                                                                    |   |       |  |

#### TABLE 4-1: PIN DESCRIPTIONS

| 7x7 Pin<br>Number | 9x9 Pin<br>Number | Pin Name             | Туре             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------|-------------------|----------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 39                | 49                | GPIO0_AC<br>0        |                  | General Purpose I/O / Auto-Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 38                | 48                | GPIO1_AC<br>1        |                  | General-Purpose I/O: These are general-purpose pins with many possible uses, including:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 37                | 47                | GPIO2_AC<br>2        |                  | <ul> <li>Status indicators</li> <li>Interrupt Output: indicates changes of device status prompting system</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 36                | 46                | GPIO3_AC<br>3        |                  | software to read the interrupt service registers (ISR).<br>These pins have internal pull-down resistors (80 k $\Omega$ typical). Each pull-<br>down can be disabled by a register field. If not used, GPIO can be left                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 35                | 45                | GPIO4_AC<br>4        | IO <sub>PD</sub> | unconnected.<br>Auto-Configuration: On the rising edge of RST_B GPIO3_AC3 and<br>GPIO4_AC4 must be 0 for normal operation, and GPIO0_AC0 to<br>GPIO2_AC2 behave as auto-configuration pins to specify a custom config-<br>uration stored in internal Flash.<br>000 = configuration 0<br>001 = configuration 1<br>010 = configuration 2<br>011 = configuration 3<br>100 = configuration 4<br>101 = configuration 5<br>110 = configuration 6<br>111 = factory default state (no configuration)<br>If the specified configuration is empty in internal flash then the device pow-<br>ers up in factory default state.<br>When the host interface is I <sup>2</sup> C, Microchip recommends GPIO3 be wired to<br>a 1 k $\Omega$ resistor to ground and to a general-purpose output pin on an FPGA,<br>microcontroller or other software-controlled component. |

| Host Inte         | rface (SPI        | or I <sup>2</sup> C) |                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 26                | 36                | SCK_SCL              | I/O              | <b>SPI Clock/I<sup>2</sup>C Clock</b><br><i>SPI Clock:</i> An external SPI controller must provide the SPI clock signal on SCK.<br>$I^2C$ <i>Clock:</i> An external I <sup>2</sup> C controller must provide the I <sup>2</sup> C clock signal on the SCL pin. This pin should be externally pulled high by 1 k $\Omega$ to 5 k $\Omega$ resistor. See the I <sup>2</sup> C bus specification for sizing guidance for this resistor, referred to as RP in that specification.<br>This pin has an internal pull-up (typical 85 k $\Omega$ ) to VDDIO.                                                                                                                                                                                                                                                                                                      |

| 25                | 35                | SI_SDA               | I/O              | <b>SPI Data In/I<sup>2</sup>C Data</b><br><i>SPI Data In:</i> An external SPI controller sends commands, addresses and data to the device on SI.<br><i>I<sup>2</sup>C Data:</i> SDA is the bidirectional data line between the device and an external I <sup>2</sup> C controller. This pin should be externally pulled high by 1 kΩ to 5 kΩ resistor. See the I <sup>2</sup> C bus specification for sizing guidance for this resistor, referred to as RP in that specification.<br>This pin has an internal pull-up (typical 85 kΩ) to VDDIO.                                                                                                                                                                                                                                                                                                           |

| 23                | 33                | SO_IF1               | I/O              | <b>SPI Data Out/Interface Mode 1</b><br><i>SPI Data Out:</i> After reset this pin is SO. The device outputs data to an external SPI controller on SO during SPI read transactions.<br><i>Interface Mode:</i> On the rising edge of RST_B this pin behaves as IF1. In I <sup>2</sup> C interface mode IF1 specifies bit 0 of the I <sup>2</sup> C device address. In SPI interface mode IF1 is ignored. The interface mode is set by the CS_B_IF0 pin state on the rising edge of RST_B. See Section 7.0, "Host Interface".                                                                                                                                                                                                                                                                                                                                |

#### TABLE 4-1:PIN DESCRIPTIONS (CONTINUED)

| 7x7 Pin<br>Number | 9x9 Pin<br>Number | Pin Name | Туре            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------|-------------------|----------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24                | 34                | CS_B_IF0 | I <sub>PU</sub> | SPI Chip Select (Active Low)/Interface Mode 0<br>SPI Chip Select: After reset this pin is CS_B. An external SPI controller<br>must assert (low) CS_B to access device registers. CS_B should not be<br>allowed to float.<br>Interface Mode: On the rising edge of RST_B this pin behaves as IF0:<br>0=I <sup>2</sup> C, 1=SPI.<br>This pin has an internal pull-up (typical 85 kΩ) to VDDIO.                                                                                          |

| Crystal o         | r Input Cl        | ock      | r               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 31                | 41                | OSCI     | A-I             | Crystal Pins (Jitter Reference)                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 30                | 40                | osco     | A-O             | <i>Crystal:</i> An on-chip crystal driver circuit is designed to work with an external crystal connected to the OSCI and OSCO pins. See Section 5.3.2 for crystal characteristics and recommended external components. <i>Input Clock:</i> Wire OSCI to a 1 k $\Omega$ resistor to ground. Leave OSCO unconnected.                                                                                                                                                                    |

| 32                | 42                | OSCA     | Ρ               | <b>Crystal Oscillator Guard Pin</b><br>This pin is internally connected to crystal driver circuit ground.<br><i>Crystal:</i> Wire OSCA to a top-layer ring around the external crystal and a<br>layer-2 island under the ring, the crystal and the OSCA, OSCI, OSCO, and<br>OSCB pins. Void all other PCB layers under the layer-2 island. See<br>Section 5.3.2 for details.<br><i>Input Clock:</i> Leave OSCA unconnected.                                                           |

| 29                | 39                | OSCB     | A-I             | <b>System Clock Input (Jitter Reference)</b><br><i>Crystal:</i> When a crystal is connected to the OSCI and OSCO pins, wire<br>OSCB to the ring and layer-2 island that are connected to OSCA.<br><i>Input Clock:</i> An external single-ended local oscillator or clock signal can be<br>connected to the OSCB pin. This is a design alternative instead of a crystal<br>connected to OSCI and OSCO. Only one crystal or clock signal should be<br>wired to the OSC* pins at a time. |

| Miscellar         | neous             |          | -               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 22                | 32                | IC0      | A-I/O           | Internal Connection. Leave unconnected. Do not attach to any routing.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Power ar          | nd Ground         |          |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1                 | 1                 |          |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| —                 | 2                 | VDD18    | Р               | Core Power Supply. 1.8V ±5%.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 12                | 15                | VDD10    | Г               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 27                | 37                |          |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 2                 | 3                 |          |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 11                | 14                | VDD33    | Р               | Core Power Supply. 3.3V ±5%.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 28                | 38                | VDD00    | 1               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 33                | 43                |          |                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 34                | 44                | VDDIO    | Ρ               | <b>Digital I/O Supply.</b> 1.8V±5% to VDD33.<br>Supply pin for SPI/I <sup>2</sup> C and GPIO[4:0] pins.                                                                                                                                                                                                                                                                                                                                                                               |

|                   | 50                | VDDO0    | Р               | OUT0P/N Power Supply. 1.8V±5% to VDD33.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 40                | 53                | VDDO1    | Р               | OUT1P/N Power Supply. 1.8V±5% to VDD33.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| -                 | 56                | VDDO2    | Р               | OUT2P/N Power Supply. 1.8V±5% to VDD33.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 43                | 59                | VDDO3    | Р               | OUT3P/N Power Supply. 1.8V±5% to VDD33.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 46                | 62                | VDDO4    | Р               | OUT4P/N Power Supply. 1.8V±5% to VDD33.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 16                | 19                | VDDO5    | Р               | OUT5P/N Power Supply. 1.8V±5% to VDD33.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| _                 | 22                | VDDO6    | Р               | OUT6P/N Power Supply. 1.8V±5% to VDD33.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

TABLE 4-1: PIN DESCRIPTIONS (CONTINUED)

| 7x7 Pin<br>Number    | 9x9 Pin<br>Number               | Pin Name | Туре | Description                                                                   |  |

|----------------------|---------------------------------|----------|------|-------------------------------------------------------------------------------|--|

| —                    | 25                              | VDD07    | Р    | OUT7P/N Power Supply. 1.8V±5% to VDD33.                                       |  |

| 21                   | 28                              | VDDO8    | Р    | OUT8P/N Power Supply. 1.8V±5% to VDD33.                                       |  |

| —                    | 31                              | VDDO9    | Р    | OUT9P/N Power Supply. 1.8V±5% to VDD33.                                       |  |

| —                    | —                               | NC       | _    | Not connected Not internally connected.                                       |  |

| 3,4,5,6,<br>7,8,9.10 | 4,5,6,7,8<br>,9,10,11,<br>12,13 | DNC      | _    | <b>Do Not Connect.</b> Do not wire anything to these pins. Leave unconnected. |  |

| E-pad                | E-pad                           | VSS      | Р    | Ground. 0 volts.                                                              |  |

#### TABLE 4-1: PIN DESCRIPTIONS (CONTINUED)

## 5.0 FUNCTIONAL DESCRIPTION

#### 5.1 Output Frequency Synthesizers

#### 5.1.1 SYNTHESIZER ENABLE

A synthesizer is enabled by setting synth\_ctrl\_x::en=1.

#### 5.1.2 SYNTHESIZER NOMINAL FREQUENCY

The synthesizers can each generate any clock frequency from just above the APLL frequency divided by 64 up to APLL frequency divided by 16. For a typical case of APLL frequency being 12.0 GHz, this range is from just above 187.5 MHz up to and including 750 MHz.

The frequency for a synthesizer is programmed as B \* K \* M / N Hz where B, M, and N are 16-bit registers and K is a 32-bit register. The synth\_freq\_base, synth\_freq\_mult, synth\_freq\_m and synth\_freq\_n mailbox registers specify B, K, M, and N respectively.

#### 5.1.3 SYNTHESIZER FREQUENCY OFFSET AND NCO BEHAVIOR

The frequency offset of a synthesizer can be adjusted with resolution of  $2^{-48}$  (~0.0000035 ppb or 3.5E–15) in the synth\_df\_offset\_manual\_x register. The adjustment affects all outputs configured to follow the synthesizer. This register can be written as fast as once every 600 µs.

#### 5.1.4 SPREAD-SPECTRUM MODULATION

For applications that require 100 MHz PCI Express clocks, the device can perform spread spectrum modulation (SSM) in any synthesizer. In SSM the frequency of the output clock is continually varied over a narrow frequency range to spread the energy of the signal and thereby reduce EMI. Spread-spectrum is enabled by setting synth\_c-trl\_x::spread\_spectrum\_en=1.

For center-spread applications, the frequency modulation is triangle-wave center-spread up to ±5% deviation from the center frequency with modulation rate configurable from 10 kHz to 100 kHz. (Values outside of these ranges are often achievable as well.)

For down-spread applications, such as PCI Express Refclk, the frequency modulation is triangle-wave down-spread of up to -10% deviation from the nominal frequency with modulation rate configurable from 10 kHz to 100 kHz. (Values outside of these ranges are often achievable as well.)

#### 5.1.5 SYNTHESIZER PHASE ADJUSTMENT

The phase of a synthesizer when enabled is set by the synth\_phase\_compensation mailbox register with 1 ps step size.

#### 5.2 Output Clocks

The device has ten OUTxP/N output clock signal pairs that each can be internally connected to any synthesizer. Each output pair has individual enable, signal format, divider, pulse width, and start/stop controls. In CMOS mode, each signal pair can become two CMOS outputs, allowing the device to have up to 20 output clock signals. Also in CMOS mode, the OUTxN pin can have an additional divider that allows the OUTxN frequency to be an integer divisor of the OUTxP frequency (example: OUT3P 125 MHz and OUT3N 25 MHz). The outputs can be aligned relative to each other and the phases of output signals can be adjusted dynamically with fine resolution.

#### 5.2.1 OUTPUT ENABLE, SIGNAL FORMAT, VOLTAGE AND INTERFACING

To use an output, the output driver must be enabled in output\_mode::signal\_format and the per-output divider must be enabled by setting output\_ctrl\_x::en. The per-output dividers include the per-output phase adjustment/alignment circuitry and start/stop logic.

Each output pair can be disabled or configured as LVDS, LVPECL, programmable differential, Low-V<sub>CM</sub> (HCSL-like), or one or two CMOS outputs. When an output is disabled, it is high impedance, and the output driver is in a low-power state. In CMOS mode, the OUTxN pin can be disabled, in-phase, or inverted vs. the OUTxP pin. Also the OUTxP pin can be disabled while the OUTxN pin is enabled. The clock to the output driver can inverted by setting output\_mode::polarity. The CMOS output driver can be set to any of four drive strengths in the output\_driver\_level::drive mailbox register field.

When the output driver is in LVDS mode.  $V_{OD}$  is forced to 400 mV.  $V_{CM}$  can be configured in output\_driver\_config::vcm mailbox register field, but the default value is typically used to get  $V_{CM}$ =1.2V for LVDS.

When the output driver is in programmable differential mode the output swing ( $V_{OD}$ ) can be configured in the output\_driver\_level::vod mailbox register field to any value from 300 mV to 900 mV in 100 mV steps, and the common-mode voltage can be configured to any voltage from 1.0V to 2.1V in 0.1V steps in the output\_driver\_level::vcm mailbox register field. Together these fields allow the output signal to be customized to meet the requirements of the clock receiver and minimize the need for external components. By default, programmable differential mode provides 800 mV LVPECL signal swing with a 1.2V common mode voltage. This gives a signal that can be AC-coupled to receivers that are LVPECL or that require a larger signal swing than LVDS. The output driver can also be configured for LVPECL output with standard 2.0V common-mode voltage.

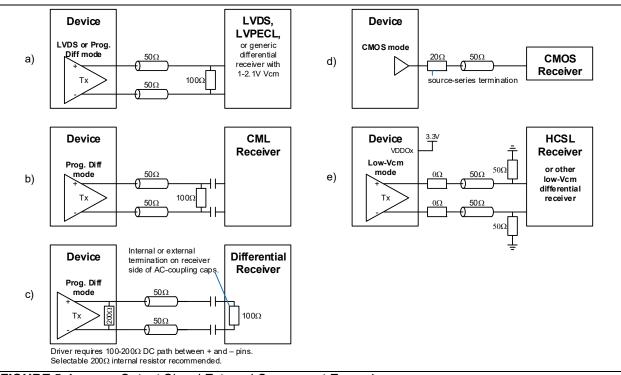

In both LVDS mode and programmable differential mode, the output driver requires a DC path between OUTxP and OUTxN for proper operation. This DC path is often a 100 $\Omega$  termination resistor placed as close as possible to the receiver inputs to terminate the differential signal as shown in Figure 5-1 parts a) and b). If the receiver requires a common-mode voltage that cannot be matched by the output driver then the POS and NEG signals can be AC-coupled to the receiver after the 100 $\Omega$  resistor as shown in Figure 5-1 part b). For the case where the receiver already has a 100 $\Omega$  termination resistor and AC-coupling is required, a resistor can be placed between OUTxP and OUTxN as close as possible to the device to provide the required DC path as shown in Figure 5-1 part c). This resistor can be 100 $\Omega$  for double-termination of the signal or it can be up to 200 $\Omega$ , in which case the signal is single-terminated by the 100 $\Omega$  resistor at the receiver is larger than the double-termination case. The device provides an optional internal 200 $\Omega$  that can be enabled by setting output\_driver\_config::rbias=1.

When the output driver is in Low-V<sub>CM</sub> mode the output format is HCSL-like with electrical specs as shown in Table 9-8.

Each output has its own power supply pin, VDDO0 through VDDO9, to allow CMOS signal swing from 1.8V to 3.3V for glueless interfacing to neighboring components.

Note that LVDS and LVPECL signal formats must have a VDDOx power supply of 2.5V or 3.3V.

FIGURE 5-1: Output Signal External Component Examples.

#### 5.2.2 OUTPUT FREQUENCY CONFIGURATION

The frequency of each output is determined by the configuration of the source synthesizer and the output divider. Each OUTxP/N pair can be connected to any synthesizer using output\_ctrl\_x::synth\_sel. The output divider (output\_div mailbox register) can produce signals with 50% duty cycle for all divider values including odd numbers. The maximum input frequency for the output divider is 750 MHz.

Because each output pair has its own independent divider, the device can output families of related frequencies that have a synthesizer divider frequency as a common multiple. For example, for Ethernet clocks, a 625 MHz clock from a synthesizer can be divided by four for one output to get 156.25 MHz, divided by five for another output to get 125 MHz, and divided by 25 for another output to get 25 MHz. Similarly, for SDH/SONET clocks, a 622.08 MHz clock can be divided by 4 to get 155.52 MHz, by 8 to get 77.76 MHz, by 16 to get 38.88 MHz or by 32 to get 19.44 MHz.

#### Two Different Frequencies in 2xCMOS Mode

When an output is in 2xCMOS mode it can be configured, using the 1100 and 1111 decodes of output\_mode::signal\_format, for N-pin divide mode. In this mode, an additional divider allows the OUTxN frequency to be an integer divide of the OUTxP frequency. Examples of where this can be useful:

- 125 MHz on OUTxP and 25 MHz on OUTxN for Ethernet applications

- 77.76 MHz on OUTxP and 19.44 MHz on OUTxN for SONET/SDH applications

- 25 MHz on OUTxP and 1 Hz (i.e. 1PPS) on OUTxN for telecom applications with IEEE1588 timing

- In N-pin divide mode, the output\_esync\_period register specifies the additional divide value.

Note that the per-output divider must be configured to divide by 2 or more in N-pin divide mode.

#### 5.2.3 OUTPUT PHASE ALIGNMENT AND PHASE ADJUSTMENT

The device automatically maintains alignment of enabled outputs. The default behavior is rising-edge alignment of all outputs. The phase of an output signal can be shifted by 180° by inverting the polarity (output\_mode::polarity). In addition, the phase of an output signal can be shifted using the output\_phase\_compensation register with a step size equal to ½ of the source synthesizer clock period. For example, if the synthesizer is 625 MHz then one synthesizer period is 1.6 ns and the smallest phase adjustment is 0.8 ns.

In addition to the per-output controls mentioned above, the phase of all outputs derived from the same synthesizer can be controlled with 1 ps resolution. See Section 5.1.5 for details.

#### 5.2.4 OUTPUT DUTY CYCLE/PULSE WIDTH ADJUSTMENT

The duty cycle of the output clock can be modified using the output\_width mailbox register. For normal polarity outputs, the pulse is high and the signal is low the remainder of the cycle. For inverse polarity outputs, the pulse is low and the signal is high the remainder of the cycle.

When an OUTxP/N pair is configured for two different frequencies using N-pin divide mode, the OUTxN duty cycle can be modified using the output\_esync\_width mailbox register.

#### 5.2.5 OUTPUT CLOCK START/STOP AND SQUELCH

#### 5.2.5.1 Output Start/Stop

Output clocks can be stopped high or low or high-impedance. One use for this behavior is to ensure "glitchless" output clock operation while the output is reconfigured or phase aligned with some other signal.

Each output has an output\_ctrl\_x register with bits to control this behavior. When bit stop\_high=1 and the stop bit is asserted, the output clock is stopped after the next rising edge of the output clock. When stop\_high=0 and the stop bit is asserted, the output clock is stopped after the next falling edge of the output clock. When the output is stopped, the output driver goes high-impedance if bit stop\_hz=1. Internally the clock signal continues to toggle while the output is stopped. When the stop signal is deasserted, the output clock resumes on the opposite edge that it stopped on. Low-speed output clocks can take long intervals before being stopped after the stop signal goes active. For example, a 1 Hz output could take up to 1 second to stop.

When the output polarity is inverted the output stops on the opposite polarity that is specified by the stop mode field.

The output divider must be dividing by 2 or more (output\_div mailbox register  $\geq$  2) to use start/stop behavior because divider set to 1 bypasses the start-stop circuits.

Note that when the OUTxP/N pair is configured for two frequencies using N-pin divide mode the start-stop logic controls both OUTxP and OUTxN simultaneously. This is glitchless (no short high or low times) for the OUTxP signal, but the lower-frequency OUTxN signal can have high time or low time as short as one OUTxP cycle.

#### 5.2.6 OUTPUT CLOCK PINS AS GENERAL-PURPOSE OUTPUTS

When an output pair is configured for a CMOS signal format, the OUTxP pin and the OUTxN pin each can be individually configured as a general-purpose output with similar behaviors to the GPIO pins (see Section 6.3). Setting output\_g-po\_en::out\_p=1 configures the OUTxP pin as a GPO. Setting output\_gpo\_en::out\_n=1 configures the OUTxN pin as a

GPO. Note that the pin must be enabled in the output\_mode::signal\_format register field to be a GPO. For example if signal\_format="0101 – One CMOS, OCxP Enabled, OCxN High impedance" then OCxN is disabled even when output\_gpo\_en::out\_n=1. When an output is configured as a GPO, its behavior can be output-high, output-low, or status as specified by the output\_gpo\_config\_out\_p or output\_gpo\_config\_out\_n register. When an output is a *status* GPO it can be configured to follow an internal status bit specified by output\_gpo\_select\_out\_p or output\_gpo\_select\_out\_n.

# 5.3 Crystal or Input Clock

All output clocks are generated from a crystal wired to the OSCI and OSCO pins or from an oscillator wired to the OSCB pin. For a list of reference oscillators, refer to ZLAN-442.

#### 5.3.1 EXTERNAL OSCILLATOR

When using a clock oscillator as the device's clock source, connect the oscillator's output clock to the OSCB pin and set xo\_config::xtal\_en=0.

The jitter on output clock signals depends on the phase noise and frequency of the oscillator. For the device to operate with the lowest possible output jitter, the external oscillator should have the following characteristics:

- Phase Jitter: less than 0.1 ps<sub>RMS</sub> over the 12 kHz to 5 MHz integration band

- · Frequency: The higher the better, all else being equal

Several vendors offer XO products with the required jitter. Three good choices from Vectron are the 114.285 MHz VCC1-9004-114M285, the 49.152 MHz VCC1-1545-49M152, and the 48 MHz Vectron VCC1-9003-48M0000. Each of these is a standard VCC1 XO but with a max jitter specification of 0.1 ps<sub>RMS</sub> over the 12 kHz to 5 MHz integration band.

#### 5.3.2 EXTERNAL CRYSTAL

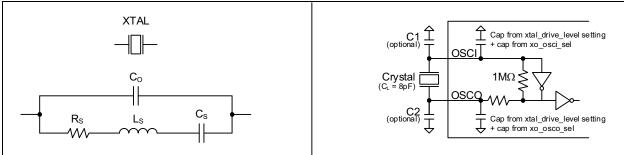

The on-chip crystal driver circuit is designed to work with a <u>fundamental mode, AT-cut</u> crystal resonator. See Table 5-1 for recommended crystal specifications. To enable the crystal driver, set xo\_config::xtal\_en=1.

FIGURE 5-2: Crystal Equivalent Circuit/Recommended Crystal Circuit.

See Figure 5-2 for the crystal equivalent circuit and the recommended external component connections. The driver circuit design includes configurable internal load capacitors. For an 8 pF crystal the total capacitance on each of OSCI and OSCO should be 2 x 8 pF = 16 pF. To achieve these loads without external capacitors, first an appropriate crystal drive level should be set in xo\_amp\_sel::xtal\_drive\_level. This sets baseline internal capacitance numbers for OSCI and OSCO as described in the xtal\_drive\_level description. Then register field xo\_osci\_sel should be set to 16 pF minus the baseline internal OSCI capacitance minus the actual external OSCI board trace capacitance. Register field xo\_osco\_sel should be set in a similar manner for OSCO load capacitance. Crystals with nominal load capacitance other than 8 pF usually can be supported with only internal load capacitance. If the xo\_osci\_sel and xo\_osco\_sel fields do not have sufficient range for the application, capacitance can be increased by using external capa C1 and C2.