# HX65HVD17xx Fault-Protected RS-485 Transceivers With Extended Common-Mode Range

# **Description**

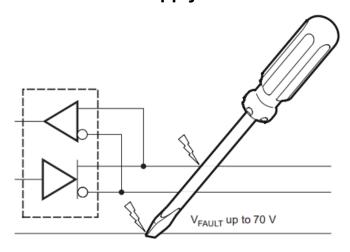

These devices are designed to survive overvoltage faults such as direct shorts to power supplies, mis-wiring faults, connector failures, cable crushes, and tool mis-applications. They are also robust to ESD events, with high levels of protection to human-body model specifications.

These devices combine a differential driver and a differential receiver, which operate from a single power supply. In the HVD1785, HVD1786, and HVD1787, the driver differential outputs and the receiver differential inputs are connected internally to orm a bus port suitable for half-duplex (two-wire bus) communication. In the HVD1793, the driver differential outputs and the receiver differential inputs are separate pins, to form a bus port suitable for full-duplex (four-wire bus) communication. These ports feature a wide common-mode voltage range, making the devices suitable for multipoint applications over long cable runs. These devices are characterized from  $-40^{\circ}\text{C}$  to  $105^{\circ}\text{C}$ .

#### **Features**

- Bus-Pin Fault Protection to:

- > ±70 V ('HVD1785, 86, 91, 92)

- > ±30 V ('HVD1787, 93)

- Common-Mode Voltage Range (–20V to 25V)More Than Doubles TIA/EIA 485 Requirement

- Bus I/O Protection

- ±16 kV JEDE C HBM Protection

- Reduced Unit Load for Up to 256 Nodes

- Failsafe Receiver for Open-Circuit, Short-Circuit and Idle-Bus Conditions

- Low Power Consumption

- Low Standby Supply Current, 1 μA Typical

- ICC 5 mA Quiescent During Operation

- Power-Up, Power-Down Glitch-Free Operation

## **Applications**

Designed for RS-485 and RS-422 Networks

# **Ordering Information**

| DEVICE             | Package Type          | MARKING     | Packing | Packing Qty  |

|--------------------|-----------------------|-------------|---------|--------------|

| HX65HVD1785EIPG    | DIP8                  | HX65HVD1785 | TUBE    | 2000pcs/Box  |

| HX65HVD1786EIPG    | DIP8                  | HX65HVD1786 | TUBE    | 2000pcs/Box  |

| HX65HVD1787EIPG    | DIP8                  | HX65HVD1787 | TUBE    | 2000pcs/Box  |

| HX65HVD1785EIDRG   | SOP8                  | HX65HVD1785 | REEL    | 2500pcs/Reel |

| HX65HVD1786EIDRG   | SOP8                  | HX65HVD1786 | REEL    | 2500pcs/Reel |

| HX65HVD1787EIDRG   | SOP8                  | HX65HVD1787 | REEL    | 2500pcs/Reel |

| HX65HVD1785EIDGKRG | MSOP8                 | HX65HVD1785 | REEL    | 3000pcs/Reel |

| HX65HVD1786EIDGKRG | MSOP8                 | HX65HVD1786 | REEL    | 3000pcs/Reel |

| HX65HVD1787EIDGKRG | MSOP8                 | HX65HVD1787 | REEL    | 3000pcs/Reel |

| HX65HVD1791EIDRRG  | SOP14                 | HX65HVD1791 | REEL    | 2500pcs/Reel |

| HX65HVD1792EIDRG   | SOP14                 | HX65HVD1792 | REEL    | 2500pcs/Reel |

| HX65HVD1793EIDRG   | SOP14                 | HX65HVD1793 | REEL    | 2500pcs/Reel |

| HX65HVD1791EIPWRG  | TSSOP14               | HX65HVD1791 | REEL    | 2500pcs/Reel |

| HX65HVD1792EIPWRG  | 1792EIPWRG TSSOP14 HX |             | REEL    | 2500pcs/Reel |

| HX65HVD1793EIPWRG  | TSSOP14               | HX65HVD1793 | REEL    | 2500pcs/Reel |

# **Example of Bus Short to Power Supply**

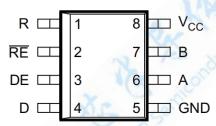

# **Pin Configuration and Functions**

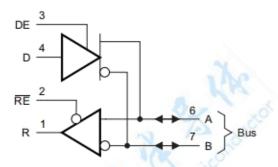

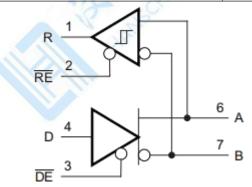

## SOP8/MSOP8/DIP8

# **Pin Functions (HX65HVD1785, HX65HVD1786, HX65HVD1787)**

| PIN  |     | TYPE               | DESCRIPTION                                          |

|------|-----|--------------------|------------------------------------------------------|

| NAME | NO. | ITPE               | DESCRIPTION                                          |

| Α    | 6   | Bus input/output   | Driver output or receiver input (complementary to B) |

| В    | 7   | Bus input/output   | Driver output or receiver input (complementary to A) |

| D    | 4   | Digital input      | Driver data input                                    |

| DE   | 3   | Digital input      | Driver enable, active high                           |

| GND  | 5   | Referencepotential | Local device ground                                  |

| R    | 1   | Digital output     | Receive data output                                  |

| RE   | 2   | Digital input      | Receiver enable, active low                          |

| VCC  | 8   | Supply             | 4.5-V-to-5.5-V supply                                |

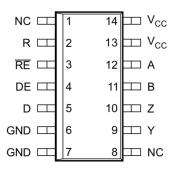

# **Pin Configuration and Functions**

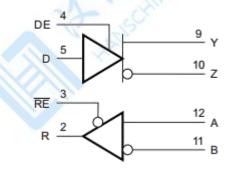

#### SOP14/TSSOP14

NC - No internal connection

Pins 6 and 7 are connected together internally.

Pins 13 and 14 are connected together internally.

# **Pin Functions (HX65HVD1791, HX65HVD1792, HX65HVD1793)**

| Р    | IN     | TYPE               | DESCRIPTION                         |

|------|--------|--------------------|-------------------------------------|

| NAME | NO.    | ITPE               | DESCRIPTION                         |

| Α    | 12     | Bus input          | Receiver input (complementary to B) |

| В    | 11     | Bus input          | Receiver input (complementary to A) |

| Υ    | 9      | Bus output         | Driver output (complementary to Z)  |

| Z    | 10     | Bus output         | Driver output (complementary to Y)  |

| D    | 5      | Digital input      | Driver data input                   |

| DE   | 4      | Digital input      | Driver enable, active high          |

| GND  | 6, 7   | Referencepotential | Local device ground                 |

| R    | 2      | Digital output     | Receive data output                 |

| RE   | 3      | Digital input      | Receiver enable, active low         |

| VCC  | 13, 14 | Supply             | 4.5-V to 5.5-V supply               |

| NC   | 1, 8   | No connect         | No connect; should be left floating |

# **Absolute Maximum Ratings**

|                                     |                         |           | MIN  | MAX            | UNIT |

|-------------------------------------|-------------------------|-----------|------|----------------|------|

| VCC Supply voltage                  | -0.5                    | 7         | V    |                |      |

|                                     | HVD1785, 86, 91, 92, 93 | A, B pins | -70  | 70             | V    |

| Voltage at bus pins                 | HVD1787                 | A, B pins | -70  | 30             | V    |

|                                     | HVD1793                 | Y, Z pins | -70  | 30             | V    |

| Input voltage at any logic pin      |                         |           | -0.3 | $V_{CC} + 0.3$ | V    |

| Transient overvoltage pulse thro    | ıgh 100 Ω per TIA-485   |           | -100 | 100            | V    |

| Receiver output current             | Receiver output current |           |      |                | mA   |

| T <sub>J</sub> Junction temperature |                         | 170       | °C   |                |      |

| Tstg Storage temperature            |                         |           |      | °C             |      |

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These

are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated

under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for

extended periods may affect device reliability.

## **ESD Ratings**

|                                            |                                                                                |                       | VALUE  | UNIT |

|--------------------------------------------|--------------------------------------------------------------------------------|-----------------------|--------|------|

|                                            | Human body model (HBM), per ANSI/ESDA/JEDEC                                    | Bus terminals and GND | ±16000 |      |

|                                            | JS-001 <sup>(1)</sup> , JEDEC Standard 22, Test Method A114                    |                       | ±4000  |      |

| V <sub>(ESD)</sub> Electrostatic discharge | Charged-device model (CDM), per JEDEC specificat Standard 22, Test Method C101 | ±2000                 | V      |      |

| a.e.e., a.e. ge                            | Machine Model, JEDEC Standard 22, Test Method A115                             |                       |        |      |

|                                            | IEC 60749-26 ESD (human-body model)                                            | Bus terminals and GND | ±16000 |      |

- (1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

- (2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

# **Recommended Operating Conditions**

|                |                                                                                                 |                                                                 | MIN | NOM | MAX | UNIT |

|----------------|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----|-----|-----|------|

| VCC            | Supply voltage                                                                                  | ge                                                              | 4.5 | 5   | 5.5 | ٧    |

| Vı             | Input voltage                                                                                   | at any bus terminal (separately or common mode) <sup>(1)</sup>  | -20 |     | 25  | V    |

| VIH            | High-level in                                                                                   | put voltage (driver, driver enable, and receiver enable inputs) | 2   |     | VCC | V    |

| VIL            | Low-level inp                                                                                   | out voltage (driver, driver enable, and receiver enable inputs) | 0   |     | 8.0 | V    |

| VID            | Differential ir                                                                                 | nput voltage                                                    | -25 |     | 25  | ٧    |

|                | Output current, driver                                                                          |                                                                 |     |     | 60  | mA   |

| I <sub>O</sub> | Output current, receiver                                                                        |                                                                 |     |     | 8   | mA   |

| R∟             | Differential lo                                                                                 | pad resistance                                                  | 54  | 60  |     | Ω    |

| CL             | Differential lo                                                                                 | pad capacitance                                                 |     | 50  |     | pF   |

|                | Ciara alia a                                                                                    | HVD1785, HVD1791                                                |     | 115 |     | kbps |

| 1/t∪ı          | Signaling<br>rate                                                                               | HVD1786, HVD1792                                                |     | 1   |     | Mena |

|                | HVD1787, HVD1793                                                                                |                                                                 |     | 10  |     | Mbps |

| T <sub>A</sub> | T <sub>A</sub> Operating free-air temperature (see application section for thermal information) |                                                                 |     |     | 105 | °C   |

| TJ             | Junction temperature                                                                            |                                                                 |     |     | 150 | °C   |

<sup>(1)</sup> By convention, the least positive (most negative) limit is designated as minimum in this data sheet.

## **Thermal Information**

|                                                 | THERMAL METRIC(1)                               | HX65H\<br>HX65H\<br>HX65H | •        | HX65HVD1791,<br>HX65HVD1792,<br>HX65HVD1793 | UNIT |

|-------------------------------------------------|-------------------------------------------------|---------------------------|----------|---------------------------------------------|------|

|                                                 |                                                 | D (SOIC)                  | P (PDIP) | D (SOIC)                                    |      |

|                                                 |                                                 | 8 PINS                    | 8 PINS   | 14 PINS                                     |      |

| R <sub>0</sub> JA                               | Junction-to-ambient thermal resistance          | 138                       | 59       | 95                                          | °C/W |

| R <sub>θ</sub> JA (low-K)                       | Junction-to-case (top) thermal resistance       | 242                       | 128      | 168                                         | °C/W |

| RθJC(top)                                       | Junction-to-board thermal resistance            | 61                        | 61       | 44                                          | °C/W |

| RθJB Junction-to-top characterization parameter |                                                 | 62                        | 39       | 40                                          | °C/W |

| ΨJT                                             | JT Junction-to-board characterization parameter |                           | 17.6     | 8.2                                         | °C/W |

| ΨЈВ                                             | Junction-to-case (bottom) thermal resistance    | 33.4                      | 28.3     | 25                                          | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

# **Electrical Characteristics**

over recommended operating conditions (unless otherwise noted)

|                        | PARAMETER                                                                        | TEST CONDI                                                            | TIONS                                                                                                                      | MIN  | TYP                   | MAX | UNIT |

|------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------|-----------------------|-----|------|

|                        |                                                                                  | RS-485 with common-mode load,                                         | T <sub>A</sub> ≤ 85°C                                                                                                      |      | 1.5                   |     |      |

| $ V_{OD} $             | Driver differential output voltage magnitude                                     | V <sub>CC</sub> > 4.75 V,<br>see Figure 5                             | T <sub>A</sub> ≤ 105°C                                                                                                     |      | 1.4                   |     |      |

|                        |                                                                                  | R <sub>L</sub> = 54 $\Omega$ , 4.75 V ≤                               |                                                                                                                            | 1.5  |                       | 2   | V    |

|                        |                                                                                  | R <sub>L</sub> = 100 Ω, 4.75 V ≤                                      |                                                                                                                            | 2    | 2.5                   |     |      |

| $\Delta  V_{OD} $      | Change in magnitude of driver differential outputvoltage                         | R <sub>L</sub> = 54 Ω                                                 |                                                                                                                            | -0.2 | 0                     | 0.2 | V    |

| Voc(ss<br>)            | Steady-state common-mode output voltage                                          |                                                                       |                                                                                                                            | 1    | V <sub>CC</sub> /2    | 3   | V    |

| $\Delta V_{\text{OC}}$ | Change in differential driver output common-<br>mode voltage                     |                                                                       |                                                                                                                            | -100 | 0                     | 100 | mV   |

| VOC(PP<br>)            | Peak-to-peak driver common-mode output voltage                                   | Center of two 27-Ω losee Figure 6                                     | oad resistors,                                                                                                             |      | 500                   |     | mV   |

| COD                    | Differential output capacitance                                                  |                                                                       |                                                                                                                            |      | 23                    |     | pF   |

| VIT+                   | Positive-going receiver differential input voltagethreshold                      |                                                                       | be                                                                                                                         |      | -100                  | -10 | mV   |

| VIT-                   | Negative-going receiver differential input voltage threshold                     | V = 20 V to 25 V                                                      | , and                                                                                                                      | -200 | -150                  |     | mV   |

| VHYS                   | Receiver differential input voltage threshold hysteresis ( $V_{IT+} - V_{IT-}$ ) | $V_{CM} = -20 \text{ V to } 25 \text{ V}$                             | Adule                                                                                                                      | 30   | 50                    |     | mV   |

| Voн                    | Receiver high-level output voltage                                               | I <sub>OH</sub> = –8 mA                                               |                                                                                                                            | 2.4  | V <sub>CC</sub> - 0.3 |     | V    |

| VOH                    | 43.                                                                              | $I_{OH} = -400 \mu A$                                                 |                                                                                                                            |      | 4                     |     |      |

| VOL                    | - 1                                                                              | I <sub>OL</sub> = 8 mA                                                | T <sub>A</sub> ≤ 85°C                                                                                                      |      | 0.2                   | 0.4 |      |

|                        | Receiver low-level output voltage                                                | 101 0 1117 1                                                          | T <sub>A</sub> ≤ 105°C                                                                                                     |      | 0.2                   | 0.5 | V    |

| l <sub>l</sub>         | Driver input, driver enable, and receiver enableinput current                    | YAL                                                                   |                                                                                                                            | -100 |                       | 100 | μΑ   |

| loz                    | Receiver output high-impedance current                                           | $V_0 = 0 \text{ V or } V_{CC}, \overline{RE}$                         | at V <sub>CC</sub>                                                                                                         | -1   |                       | 1   | μA   |

| los                    | Driver short-circuit output current                                              |                                                                       | II                                                                                                                         | -250 |                       | 250 | mA   |

| l <sub>i</sub>         | Bus input current (disabled driver)                                              | V <sub>CC</sub> = 4.5 to 5.5 V or<br>V <sub>CC</sub> = 0 V, DE at 0 V |                                                                                                                            | -100 | 75<br>–40             | 125 | μA   |

|                        |                                                                                  | 100 0 1, 2 2 410 1                                                    | 87 V <sub>I</sub> = 12 V                                                                                                   |      | 500                   |     | F 1  |

|                        |                                                                                  |                                                                       | 93 V <sub>I</sub> = -7 V                                                                                                   |      | -400                  |     |      |

|                        |                                                                                  | Driver and receiver enabled                                           | $\begin{aligned} \text{DE} &= \text{V}_{\text{CC}}, \\ \text{RE} &= \text{GND}, \\ \text{no load} \end{aligned}$           |      | 4                     | 6   |      |

| ICC                    |                                                                                  | Driver enabled, receiver disabled                                     | $\begin{aligned} \text{DE} &= \text{V}_{\text{CC}}, \\ \text{RE} &= \text{V}_{\text{CC}}, \\ \text{no load} \end{aligned}$ |      | 3                     | 5   | mA   |

|                        | Supply current (quiescent)                                                       | Driver disabled, receiver enabled                                     | DE = GND,<br>RE = GND,<br>no load                                                                                          |      | 2                     | 4   |      |

|                        |                                                                                  | Driver and receiver disabled                                          | DE = GND,<br>D = open<br>RE = V <sub>cc</sub> ,<br>no load                                                                 |      | 0.5<br>5              |     | μА   |

|                        |                                                                                  | See Typical Characte                                                  |                                                                                                                            |      |                       |     |      |

## **Thermal Considerations**

| PARAMETER                                             |        | TEST CONDITIONS                                                                                                                                                           | VALUE | UNIT |

|-------------------------------------------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|

|                                                       | 85, 91 | $V_{CC}$ = 5.5 V, $T_J$ = 150°C, $R_L$ = 300 $\Omega$ , $C_L$ = 50 pF (driver), $C_L$ = 15 pF (receiver) 5-V supply, unterminated <sup>(1)</sup>                          | 290   |      |

|                                                       | 85, 91 | V = = 5 5 V T = 150°C D = 100 O C = 50 pF (driver)                                                                                                                        |       |      |

| P <sub>D</sub> Power                                  | 86     | $V_{CC}$ = 5.5 V, $T_J$ = 150°C, $R_L$ = 100 $\Omega$ , $C_L$ = 50 pF (driver), $C_L$ = 15 pF (receiver) 5-V supply, RS-422 load <sup>(1)</sup>                           |       | \A/  |

| dissipation                                           | 87     |                                                                                                                                                                           |       | mW   |

|                                                       | 85, 91 | V - 5 5 V T - 450°C D - 54 C C - 50 mF (dminor)                                                                                                                           |       |      |

|                                                       | 86     | $V_{CC} = 5.5 \text{ V}, T_J = 150^{\circ}\text{C}, R_L = 54 \Omega, C_L = 50 \text{ pF (driver)}, C_L = 15 \text{ pF (receiver)}$ 5-V supply, RS-485 load <sup>(1)</sup> |       |      |

|                                                       | 87     |                                                                                                                                                                           |       |      |

| T <sub>SD</sub> Thermal-shutdown junction temperature |        |                                                                                                                                                                           | 170   | °C   |

<sup>(1)</sup> Driver and receiver enabled, 50% duty cycle square-wave signal at signaling rate: HVD1785, 1791 at 115 kbps, HVD1786 at 1 Mbps, HVD1787 at 10 Mbps)

# **Switching Characteristics**

over recommended operating conditions (unless otherwise noted)

|                                 | PARAMETER                                              | TEST COND                                         | ITIONS                   | MIN  | TYP      | MAX | UNIT |

|---------------------------------|--------------------------------------------------------|---------------------------------------------------|--------------------------|------|----------|-----|------|

|                                 | DRIVER (                                               | HVD1785 AND HVD1                                  | 1791)                    |      |          |     |      |

| t <sub>r</sub> , t <sub>f</sub> | Driver differential output rise/fall time              | QN                                                | 101                      | 0.4  | 1.7      | 2.6 | μs   |

| tPHL,tPLH                       | Driver propagation delay                               | $R_L = 54 \Omega$ , $C_L = 50$                    | pF,                      |      | 0.8<br>2 |     | μs   |

| t<br>SK(P)                      | Driver differential output pulse skew,  tPHL - tPLH    | see Figure 7                                      | Co.                      |      | 20       | 250 | ns   |

| tphz, tplz                      | Driver disable time                                    | 13 Ill Se                                         | 0 5                      |      | 0.1<br>5 |     | μs   |

| tPZH, tPZL                      | Driver enable time                                     | Receiver enabled                                  |                          |      | 0.2      | 40  | μs   |

| DDIVED (U                       | VD1786 AND HVD1792)                                    | Receiver disabled                                 |                          |      | 3        | 12  |      |

| t <sub>r</sub> , t <sub>f</sub> | Driver differential output rise/fall time              |                                                   |                          | 50   |          | 300 | ns   |

| tPHL, tPLH                      | Driver differential output riserial time               | $R_L$ = 54 $\Omega$ , $C_L$ = 50 pF, see Figure 7 |                          | - 30 | 200      | 300 | ns   |

| tSK(P)                          | Driver differential output pulse skew,  tpHL - tpLH    |                                                   |                          |      | 25       |     | ns   |

| tPHZ, tPLZ                      | Driver disable time                                    |                                                   | 0 5: 0                   |      | 3        |     | μs   |

|                                 |                                                        | Receiver enabled                                  | See Figure 8 andFigure 9 |      | 300      |     | ns   |

| tpzh, tpzl                      | Driver enable time                                     | Receiver disabled                                 | andrigule 9              |      | 10       |     | μs   |

|                                 |                                                        | Receiver enabled                                  | VCM > VCC                |      | 500      |     | ns   |

| DRIVER (H                       | VD1787 AND HVD1793)                                    |                                                   |                          |      |          |     |      |

| $t_r$ , $t_f$                   | Driver differential output rise/fall time              |                                                   |                          | 3    |          | 30  | ns   |

| tPHL, tPLH                      | Driver propagation delay                               | $R_L = 54 \Omega, C_L = 50$                       | nF                       |      | 50       |     | ns   |

| <sup>t</sup> SK(P)              | Driver differential output pulse skew,<br> tPHL - tPLH | see Figure 7                                      |                          |      | 10       |     | ns   |

| tPHZ, tPLZ                      | Driver disable time                                    |                                                   |                          |      | 3        |     | μs   |

|                                 |                                                        | Receiver enabled                                  | See Figure 8 andFigure 9 |      | 300      |     | ns   |

| tPZH, tPZL                      | Driver enable time                                     | Receiver disabled                                 | andrigule 9              |      | 9        |     | μs   |

| ı                               |                                                        | Receiver enabled                                  | VCM > VCC                |      | 500      |     | ns   |

# **Switching Characteristics (continued)**

over recommended operating conditions (unless otherwise noted)

|                                 | PARAMETER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | TEST CON                                | DITIONS        | MIN | TYP | MAX | UNIT |  |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------|-----|-----|-----|------|--|

|                                 | RECEIVER (ALL DEV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ICES UNLESS OTH                         | IERWISE NOTED  | ))  |     |     |      |  |

| t <sub>r</sub> , t <sub>f</sub> | Receiver output rise/fall time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                         |                | 4   |     | 15  | ns   |  |

| tPHL, tPLH                      | tout tout of the second of the |                                         | 85, 86, 91, 92 | 10  | 0   | 200 | no   |  |

| PAL, PLA                        | Receiver propagation delay time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | $C_L = 15 \text{ pF},$<br>see Figure 10 | 87, 93         | 70  |     |     | ns   |  |

| tSK(P)                          | Receiver output pulse skew,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | see Figure 10                           | 85, 86, 91, 92 | 6   | i   | 20  | no   |  |

| ISK(F)                          | tPHL – tPLH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                         | 87, 93         |     | 5   |     | ns   |  |

| tPLZ, tPHZ                      | Receiver disable time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Driver enabled, se                      | ee Figure 11   | 1:  | 5   | 100 | ns   |  |

| tPZL(1),                        | Driver er                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                         | ee Figure 11   | 80  | 0   | 300 | ns   |  |

| tPZH(1)                         | Receiver enable time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                         |                |     |     |     |      |  |

| tPZL(2),                        | IVECEIVEL CHADIC IIIIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Driver disabled, see Figure 12          |                | 3   |     | 9   | μs   |  |

| tPZH(2)                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |                |     |     |     |      |  |

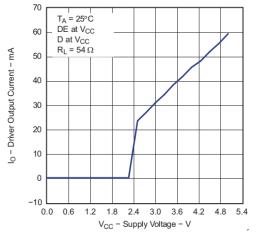

# **Typical Characteristics**

Figure 1. Driver Output Current vs Supply Voltage

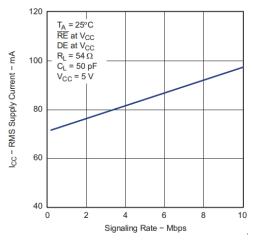

Figure 2. HVD1787 RMS Supply Current vs Signaling Rate

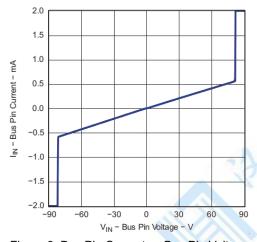

Figure 3. Bus Pin Current vs Bus Pin Voltage

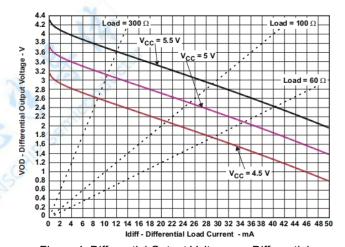

Figure 4. Differential Output Voltage vs. Differential Load Current

#### **Parameter Measurement Information**

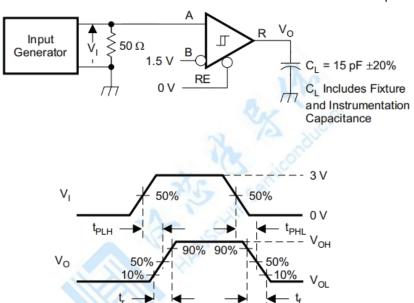

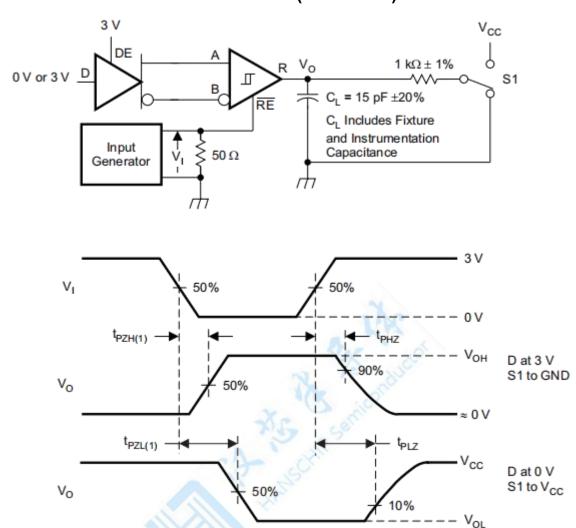

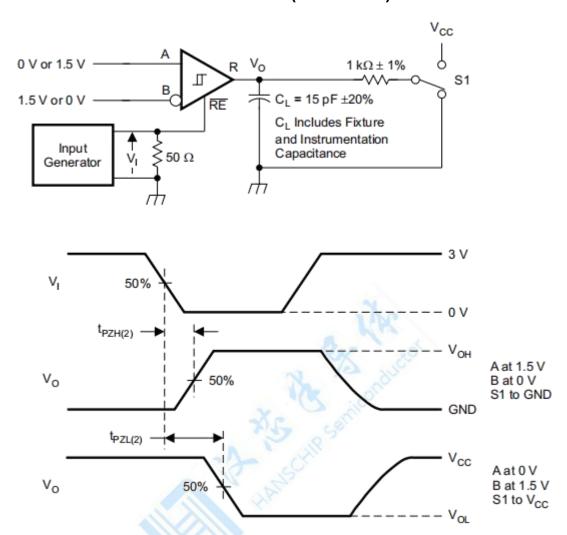

Input generator rate is 100 kbps, 50% duty cycle, rise and fall times less than 6 nsec, output impedance 50 Ω.

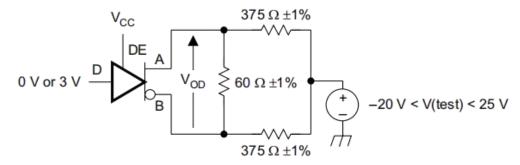

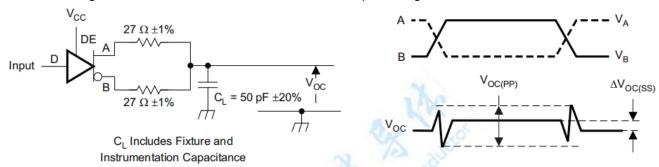

Figure 5. Measurement of Driver Differential Output Voltage With Common-Mode Load

Figure 6. Measurement of Driver Differential and Common-Mode Output With RS-485 Load

Figure 7. Measurement of Driver Differential Output Rise and Fall Times and Propagation Delays

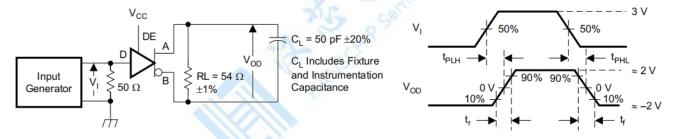

NOTE: D at 3 V to test non-inverting output, D at 0 V to test inverting output.

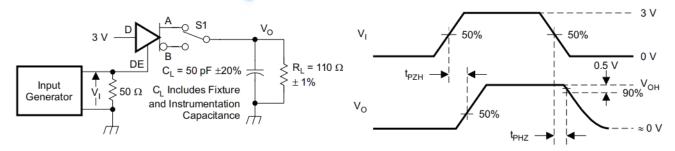

Figure 8. Measurement of Driver Enable and Disable Times With Active High Output and Pulldown Load

# **Parameter Measurement Information (continued)**

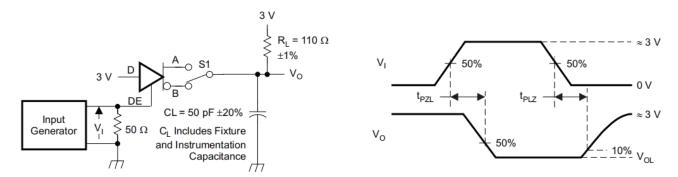

NOTE: D at 0 V to test non-inverting output, D at 3 V to test inverting output.

Figure 9. Measurement of Driver Enable and Disable Times With Active-Low Output and Pullup Load

Figure 10. Measurement of Receiver Output Rise and Fall Times and Propagation Delays

# **Parameter Measurement Information (continued)**

Figure 11. Measurement of Receiver Enable/Disable Times With Driver Enabled

# **Parameter Measurement Information (continued)**

Figure 12. Measurement of Receiver Enable Times With Driver Disabled

## **Detailed Description**

#### Overview

The HX65HVD17xx family of RS-485 transceivers are designed to operate up to 115 kbps (HVD1785 and HVD1791), 1 Mbps (HVD1786 and HVD1792), or 10 Mbps (HVD1787 or HVD1793) and to withstand DC overvoltage faults on the bus interface pins. This helps to protect the devices against damages resulting from direct shorts to power supplies, cable mis-wirings, connector failures, or other common faults.

The HX65HVD178x devices are half-duplex, and thus have the transmitter and receiver bus interfaces connected together internally. The HX65HVD179x family leaves these two interfaces separate, allowing for full-duplex communication. The low receiver loading allows for up to 256 nodes to share a common RS-485 bus. The devices feature a wide common-mode range as well as fail-safe receivers, which ensure a stable logic-level output during bus open, short, or idle conditions.

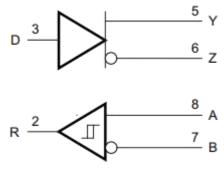

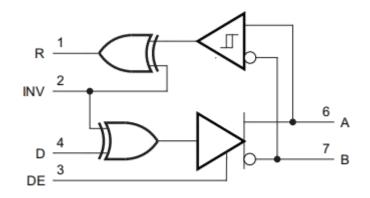

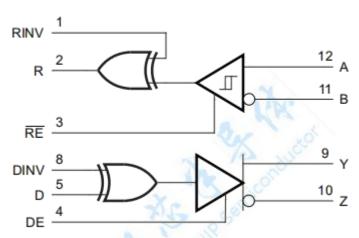

## **Functional Block Diagram**

Figure 13. Half-Duplex Transceiver Logic Diagram (Positive Logic)

Figure 14. Full Duplex Transceiver

# **Feature Description**

#### **Hot-Plugging**

These devices are designed to operate in hot swap or hot pluggable applications. Key features for hot-pluggable applications are power-up, power-down glitch free operation, default disabled input/output pins, and receiver failsafe. As shown in Figure 1, an internal Power-On Reset circuit keeps the driver outputs in a high-impedance state until the supply voltage has reached a level at which the device will reliably operate. This ensures that no spurious transitions (glitches) will occur on the bus pin outputs as the power supply turns on or turns off.

As shown in Device Functional Modes, the ENABLE inputs have the feature of default disable on both the driver enable and receiver enable. This ensures that the device will neither drive the bus nor report data on the R pin until the associated controller actively drives the enable pins.

## **Feature Description (continued)**

#### **Receiver Failsafe**

The differential receiver is failsafe to invalid bus states caused by:

- open bus conditions such as a disconnected connector,

- shorted bus conditions such as cable damage shorting the twisted-pair together,

- or idle bus conditions that occur when no driver on the bus is actively driving.

In any of these cases, the differential receiver outputs a failsafe logic High state, so that the output of the receiver is not indeterminate.

In the HVD17xx family of RS-485 devices, receiver failsafe is accomplished by offsetting the receiver thresholds so that the "input indeterminate" range does not include zero volts differential. In order to comply with the RS-422 and RS-485 standards, the receiver output must output a High when the differential input VID is more positive than 200 mV, and must output a Low when the VID is more negative than -200 mV. The HVD17xx receiver parameters which determine the failsafe performance are VIT+ and VIT- and VHYS. In the Electrical Characteristics table, VIT- has a typical value of -150 mV and a minimum (most negative) value of -200 mV, so differential signals more negative than -200 mV will always cause a Low receiver output. Similarly, differential signals more positive than 200 mV will always cause a High receiver output, because the typical value of VIT+ is -100mV, and VIT+ is never more positive than -10 mV under any conditions of temperature, supply voltage, or common-mode offset.

When the differential input signal is close to zero, it will still be above the VIT+ threshold, and the receiver output will be High. Only when the differential input is more negative than VIT- will the receiver output transition to a Low state. So, the noise immunity of the receiver inputs during a bus fault condition includes the receiver hysteresis value VHYS (the separation between VIT+ and VIT-) as well as the value of VIT+.

For the HVD17xx devices, the typical noise immunity is typically about 150 mV, which is the negative noise level needed to exceed the VIT– threshold (VIT- TYP = -150 mV). In the worst case, the failsafe noise immunity is never less than 40 mV, which is set by the maximum positive threshold (VIT+ TYP = -150 mV) plus the minimum hysteresis voltage (VHYS TYP = -150 mV).

#### 70-V Fault-Protection

The HX65HVD17xx family of RS-485 devices is designed to survive bus pin faults up to ±70V. The devices designed for fast signaling rate (10 Mbps) will not survive a bus pin fault with a direct short to voltages above 30V when:

- 1. the device is powered on AND

- 2a. the driver is enabled (DE=HIGH) AND D=HIGH AND the bus fault is applied to the A pin OR

- 2b. the driver is enabled (DE=HIGH) AND D=LOW AND the bus fault is applied to the B pin

Under other conditions, the device will survive shorts to bus pin faults up to 70V. Table 1 summarizes the conditions under which the device may be damaged, and the conditions under which the device will not be damaged.

# **Feature Description (continued)**

Table 1. Device Conditions

| POWER | DE | D | Α                           | В                           | RESULTS          |

|-------|----|---|-----------------------------|-----------------------------|------------------|

| OFF   | X  | X | -70V < V <sub>A</sub> < 70V | -70V < V <sub>B</sub> < 70V | Device survives  |

| ON    | LO | Х | -70V < V <sub>A</sub> < 70V | -70V < V <sub>B</sub> < 70V | Device survives  |

| ON    | HI | L | -70V < V <sub>A</sub> < 70V | -70V < V <sub>B</sub> < 30V | Device survives  |

| ON    | HI | L | -70V < V <sub>A</sub> < 70V | 30V < V <sub>B</sub>        | Damage may occur |

| ON    | HI | Н | -70V < V <sub>A</sub> < 30V | -70V < V <sub>B</sub> < 30V | Device survives  |

| ON    | HI | Н | 30V < V <sub>A</sub>        | -70V < V <sub>B</sub> < 30V | Damage may occur |

## **Additional Options**

The HX65HVD17xx family also has options for J1708 applications, for always-enabled full-duplex versions (industry-standard 65LBC179 footprint) and for inverting-polarity versions, which allow users to correct a reversal of the bus wires without re-wiring.

Table 2. HX65HVD17xx Options for J1708 Applications

| PART NUMBER                               | HX65HVD17xx |        |      |  |  |  |  |

|-------------------------------------------|-------------|--------|------|--|--|--|--|

| FOOTPRINT/FUNCTION                        | SLOW        | MEDIUM | FAST |  |  |  |  |

| Half-duplex (176 pinout)                  | 85          | 86     | 87   |  |  |  |  |

| Full-duplex no enables (179 pinout)       | 88          | 89     | 90   |  |  |  |  |

| Full-duplex with enables (180 pinout)     | 91          | 92     | 93   |  |  |  |  |

| Half-duplex with cable invert             | 94          | 95     | 96   |  |  |  |  |

| Full-duplex with cable invert and enables | 97          | 98     | 99   |  |  |  |  |

| J1708                                     | 08          | 09     | 10   |  |  |  |  |

Figure 15. HX65HVD1708E Transceiver for J1708 Applications

Figure 16. HX65HVD17xx Always-Enabled Driver Receiver

Figure 17. HX65HVD17xx Options With Inverting Feature to Correct for Miswired Cables

# **Device Functional Modes**

Table 3. Driver Function Table

| INPUT | ENABLE | OUTP | UTS |                                    |

|-------|--------|------|-----|------------------------------------|

| D     | DE     | Α    | В   |                                    |

| Н     | Н      | Н    | L   | Actively drive bus high            |

| L     | Н      | L    | Н   | Actively drive bus low             |

| X     | L      | Z    | Z   | Driver disabled                    |

| X     | OPEN   | Z    | Z   | Driver disabled by default         |

| OPEN  | Н      | Н    | L   | Actively drive bus high by default |

Table 4. Receiver Function Table

| DIFFERENTIAL INPUT                 | ENABLE | OUTPUT |                              |

|------------------------------------|--------|--------|------------------------------|

| $V_{ID} = V_A - V_B$               | RE     | R      |                              |

| V <sub>IT+</sub> < V <sub>ID</sub> | L      | Н      | Receive valid bus high       |

| VIT- < VID < VIT+                  | L      | ?      | Indeterminate bus state      |

| VID < VIT-                         | L      | L      | Receive valid bus low        |

| X                                  | Н      | Z      | Receiver disabled            |

| X                                  | OPEN   | Z      | Receiver disabled by default |

| Open-circuit bus                   | L      | Н      | Fail-safe high output        |

| Short-circuit bus                  | L      | Н      | Fail-safe high output        |

| Idle (terminated) bus              | Ĺ      | Н      | Fail-safe high output        |

## **Application Information**

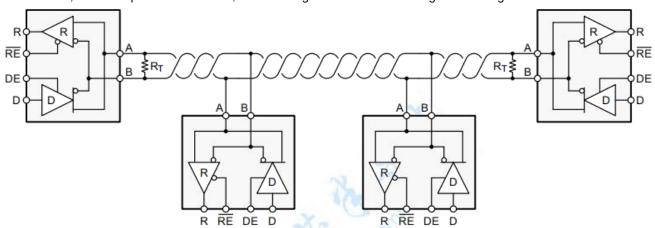

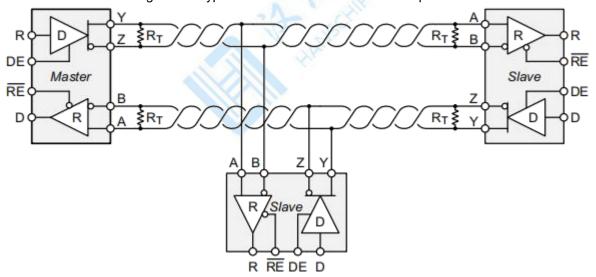

The HX65HVD17xx family consists of both half-duplex and full-duplex transceivers that can be used for asynchronous data communication. Half-duplex implementations require one signaling pair (two wires), while full- duplex implementations require two signaling pairs (four wires). The driver and receiver enable pins of the HX65HVD17xx family allow for control over the direction of data flow. Since it is common for multiple transceivers to share a common communications bus, care should be taken at the system level to ensure that only one driver is enabled at a time. This avoids bus contention, a fault condition in which multiple drivers attempt to send data at the same time.

## **Typical Application**

An RS-485 bus consists of multiple transceivers connecting in parallel to a bus cable. To eliminate line reflections, each cable end is terminated with a termination resistor, RT, whose value matches the characteristic impedance, Z0, of the cable. This method, known as parallel termination, allows for higher data rates over longer cable length.

Figure 18. Typical RS-485 Network With Half-duplex Transceivers

Figure 19. Typical RS-485 Network With Full-duplex Transceivers

# **Typical Application (continued)**

#### **Design Requirements**

RS-485 is a robust electrical standard suitable for long-distance networking that may be used in a wide range of applications with varying requirements, such as distance, data rate, and number of nodes.

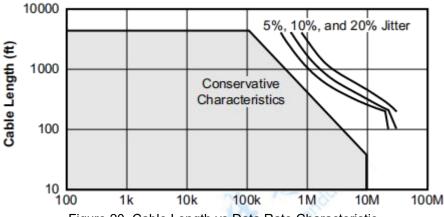

#### **Data Rate and Bus Length**

There is an inverse relationship between data rate and cable length, which means the higher the data rate, the short the cable length; and conversely, the lower the data rate, the longer the cable length. While most RS-485 systems use data rates between 10 kbps and 100 kbps, some applications require data rates up to 250 kbps at distances of 4000 feet and longer. Longer distances are possible by allowing for small signal jitter of up to 5 or 10%.

Figure 20. Cable Length vs Data Rate Characteristic

Even higher data rates are achievable (for example, 10 Mbps for the HX65HVD1787 and HX65HVD1793) in cases where the interconnect is short enough (or has suitably low attenuation at signal frequencies) to not degrade the data.

#### Stub Length

When connecting a node to the bus, the distance between the transceiver inputs and the cable trunk, known as the stub, should be as short as possible. Stubs present a non-terminated piece of bus line which can introduce reflections as the length of the stub increases. As a general guideline, the electrical length, or round-trip delay, of a stub should be less than one-tenth of the rise time of the driver, thus giving a maximum physical stub length as shown in Equation 1.

$$L_{stub} \le 0.1 \times t_r \times V \times c$$

#### where

- tr is the 10/90 rise time of the driver

- c is the speed of light (3 × 108 m/s)

- v is the signal velocity of the cable or trace as a factor of c

#### Receiver Failsafe

The differential receiver of the HX65HVD17xx family is failsafe to invalid bus states caused by:

- Open bus conditions, such as a disconnected connector

- Shorted bus conditions, such as cable damage shorting the twisted-pair together

- Idle bus conditions that occur when no driver on the bus is actively driving

n any of these cases, the differential receiver will output a failsafe logic high state so that the output of the receiver is not indeterminate.

# **Typical Application (continued)**

Receiver failsafe is accomplished by offsetting the receiver thresholds such that the "input indeterminate" range does not include zero volts differential. In order to comply with the RS-422 and RS-485 standards, the receiver output must output a high when the differential input VID is more positive than +200 mV, and must output a low when VID is more negative than -200 mV. The receiver parameters which determine the failsafe performance are VIT(+) and VIT(-). As shown in the Electrical Characteristics table, differential signals more negative than -200 mV will always cause a low receiver output, and differential signals more positive than +200 mV will always cause a high receiver output.

When the differential input signal is close to zero, it is still above the maximum VIT(+) threshold of -10 mV, and the receiver output will be high.

#### **Detailed Design Procedure**

Although the HX65HVD17xx family is internally protected against human-body-model ESD strikes up to 16 kV, additional protection against higher-energy transients can be provided at the application level by implementing external protection devices.

#### **Application Curve**

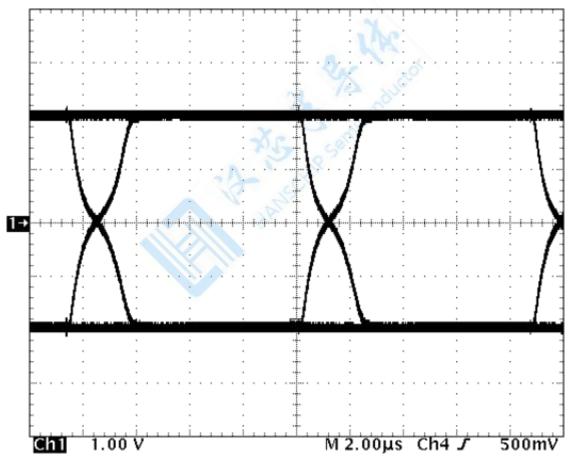

Figure 21. HX65HVD1785 Differential Output at 115 kbps

# **Physical Dimensions**

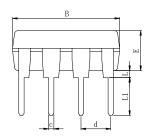

DIP8

| Dimensions In Millimeters(DIP8) |      |      |      |      |      |      |      |      |      |      |          |

|---------------------------------|------|------|------|------|------|------|------|------|------|------|----------|

| Symbol:                         | Α    | В    | D    | D1   | E    | L    | L1   | а    | b    | С    | р        |

| Min:                            | 6.10 | 9.00 | 8.40 | 7.42 | 3.10 | 0.50 | 3.00 | 1.50 | 0.85 | 0.40 | 2.54 BSC |

| Max:                            | 6.68 | 9.50 | 9.00 | 7.82 | 3.55 | 0.70 | 3.60 | 1.55 | 0.90 | 0.50 | 2.54 BSC |

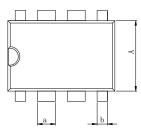

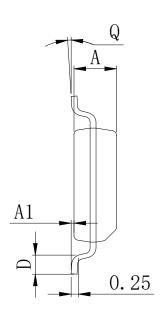

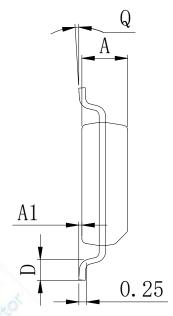

SOP8 (150mil)

| Dimensions In Millimeters(SOP8) |      |      |      |      |      |      |    |      |          |  |

|---------------------------------|------|------|------|------|------|------|----|------|----------|--|

| Symbol:                         | Α    | A1   | В    | С    | C1   | D    | Q  | а    | b        |  |

| Min:                            | 1.35 | 0.05 | 4.90 | 5.80 | 3.80 | 0.40 | 0° | 0.35 | 1 27 DCC |  |

| Max:                            | 1.55 | 0.20 | 5.10 | 6.20 | 4.00 | 0.80 | 8° | 0.45 | 1.27 BSC |  |

# **Physical Dimensions**

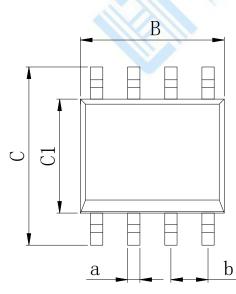

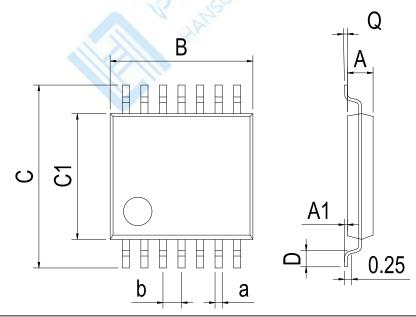

# SOP14

| Dimensions In Millimeters(SOP14) |      |      |      |      |      |      |    |      |          |  |  |

|----------------------------------|------|------|------|------|------|------|----|------|----------|--|--|

| Symbol:                          | Α    | A1   | В    | С    | C1   | D    | Q  | а    | Ф        |  |  |

| Min:                             | 1.35 | 0.05 | 8.55 | 5.80 | 3.80 | 0.40 | 0° | 0.35 | 1 27 DSC |  |  |

| Max:                             | 1.55 | 0.20 | 8.75 | 6.20 | 4.00 | 0.80 | 8° | 0.45 | 1.27 BSC |  |  |

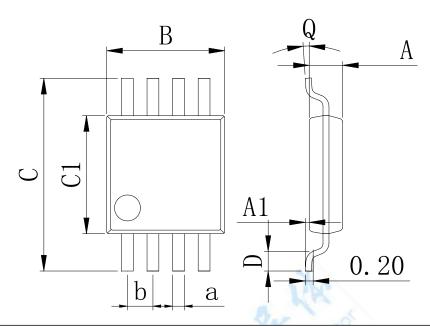

TSSOP14

| Dimensions In Millimeters(TSSOP14) |      |      |      |      |      |      |    |      |          |  |  |

|------------------------------------|------|------|------|------|------|------|----|------|----------|--|--|

| Symbol:                            | Α    | A1   | В    | С    | C1   | D    | Q  | а    | b        |  |  |

| Min:                               | 0.85 | 0.05 | 4.90 | 6.20 | 4.30 | 0.40 | 0° | 0.20 | 0.65 BSC |  |  |

| Max:                               | 0.95 | 0.20 | 5.10 | 6.60 | 4.50 | 0.80 | 8° | 0.25 |          |  |  |

# **Physical Dimensions**

## MSOP8

| Dimensions In Millimeters(MSOP8) |      |      |      |      |      |      |    |      |          |  |  |

|----------------------------------|------|------|------|------|------|------|----|------|----------|--|--|

| Symbol:                          | A    | A1   | В    | С    | C1   | D    | Q  | а    | b        |  |  |

| Min:                             | 0.80 | 0.05 | 2.90 | 4.75 | 2.90 | 0.35 | 0° | 0.25 | 0.65 BSC |  |  |

| Max:                             | 0.90 | 0.20 | 3.10 | 5.05 | 3.10 | 0.75 | 8° | 0.35 | 0.00 BSC |  |  |

#### **IMPORTANT STATEMENT:**

Shenzhen Hanschip semiconductor co.,ltd. reserves the right to change the products and services provided without notice. Customers should obtain the latest relevant information before ordering, and verify the timeliness and accuracy of this information.

Customers are responsible for complying with safety standards and taking safety measures when using our products for system design and machine manufacturing to avoid potential risks that may result in personal injury or property damage.

Our products are not licensed for applications in life support, military, aerospace, etc., so we do not bear the consequences of the application of these products in these fields.

Our documentation is only permitted to be copied without any tampering with the content, so we do not accept any responsibility or liability for the altered documents.