users. A8D12C1BB012A

# FORESEE® Shit C'

# 1.Gbit SLC NAND Flash

**Datasheet**

LM-00003

Rev 1.3

2022-07-25 10:02

LONGSYS ELECTRONICS RESERVES THE RIGHT TO CHANGE PRODUCTS, INFORMATION AND SPECIFICATIONS WITHOUT NOTICE.

Products and specifications discussed herein are for reference purposes only. All information discussed herein is provided on an "AS IS" basis, without warranties of any kind. All brand names, trademarks and registered trademarks belong to their respective

This document and all information discussed herein remain the sole and exclusive property of Longsys Electronics. No license of any patent, copyright, mask work, trademark or any other intellectual property right is granted by one party to the other party under this document, by implication, estoppel or other-wise.

For updates or additional information about Longsys products, contact your nearest Longsys office.

© 2020 Shenzhen Longsys Electronics Co., Ltd. All rights reserved.

### **Revision History**

| Rev. | Date       | Changes                                                 | 19At! |

|------|------------|---------------------------------------------------------|-------|

| 1.0  | 2020/01/28 | Initial release                                         | 10    |

| 1.1  | 2021/10/12 | Revise descriptions in 10.1, 10.4, 10.6.2, 10.6.3, 12.5 |       |

| 1.2  | 2021/11/22 | Revise descriptions in 4, 14.1, 14.2                    |       |

| 1.3  | 2021/12/3  | Add Chap 15                                             |       |

受控

2022-07-25 10:02

users. A8D12C1BB012A

2022-07-25 10:02

users.

2022-07-25 10:02

D12C1BB0124FB5

Everything for Memory

30124FB5

### **Content**

| Content                                | 6<br>8<br>9<br>10<br>11 |

|----------------------------------------|-------------------------|

| Product List                           | 6<br>8<br>9<br>10<br>11 |

| Product List                           | 6<br>8<br>9<br>10<br>11 |

| Product List                           | 6<br>8<br>9<br>10<br>11 |

| 4 Package Types and Pin Configurations | 7<br>9<br>10<br>11      |

|                                        | 8<br>9<br>10<br>11      |

| F. Din Descriptions                    | 9<br>10<br>11           |

| •                                      | 10<br>11<br>12          |

| 6 Block Diagram                        | 11<br>12                |

| 7 Array Organization and Mapping       | 11<br>12                |

|                                        | 12                      |

| 8 Mode Selection                       |                         |

| 9 Command Set                          |                         |

| 10 Device Operation                    | 13                      |

| 10.1 Reset (FFh)                       | 13                      |

| 10.2 Read Operation                    | 13                      |

| 10.2.1 Page Read (00h-30h)             | 13                      |

| 10.2.2 Pandom Data Outnut (05h 50h)    | 1/                      |

| 10.2.2 Random Data Output (0511-L011)  | 15                      |

| 10.2.4 Read ID (90n)                   | 16                      |

| 10.2.5 Read Parameter Page (ECh)       | 17                      |

| 10.2.6 Read Unique ID (EDH)            | 20                      |

| 10.3 Program Operation                 |                         |

| 10.3.1 Page Program (80h-10h)          | 21                      |

| 10.3.2 Random Data Input (85h)         | 21                      |

| 10.4 Copy Back Operation               | 22                      |

| 10.4.1 Copy Back Read (00h-35h)        |                         |

| 10.4.2 Copy Back Program (85h-10h)     | 22                      |

| 10.5 Block Erase (60h-D0h)             | 23                      |

| 10.6 Feature Operation                 | 24                      |

| 10.6.1 Feature Register                | 24                      |

| 10.6.2 Get Feature (EEh)               | 24                      |

| 10.6.3 Set Feature (EFh)               | 25                      |

| 10.7 OTP Operation                     | 26                      |

| 10.7.1 OTP Read / Program Operation    | 26                      |

| 10.7.2 OTP Lock Operation              | 26                      |

| 10.8 Block Protection                  | 27                      |

| \ \ 10.9 Write Protect                 | 28                      |

# **FORESEE**®

| 11 S | oftware Algorithm                      | 31      |

|------|----------------------------------------|---------|

| 11.1 | I Initial Invalid Block(s)             | 31      |

| 11.2 | 2 Identifying Initial Invalid Block(s) | 31      |

| 11.3 | B Error in Operation                   | 32      |

| 11.4 |                                        | 32\245  |

| 11.5 | System Interface Using CE# Don't-Care  |         |

| 12 E | System Interface Using CE# Don't-Care  | 35      |

| 12.1 | 1 Absolute Maximum Ratings             | 35      |

| 12.2 |                                        | 35      |

| 12.3 | Power-up Timing                        | 35      |

| 12.4 | 4 Pin Capacitance                      | 36      |

| 12.5 | 5 DC Electrical Characteristics        | 36      |

| 12.6 | 6 AC Measurement Conditions            | 37      |

| 12.7 |                                        |         |

| 12.8 | Read / Program / Erase Characteristics | 38      |

| 13 T | iming Diagram                          | 39      |

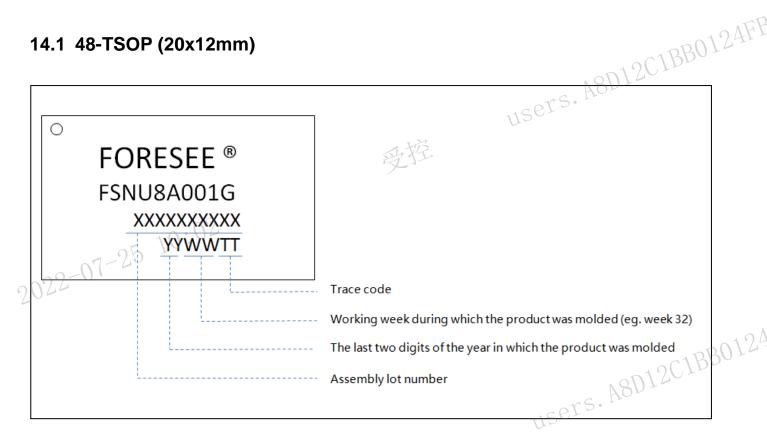

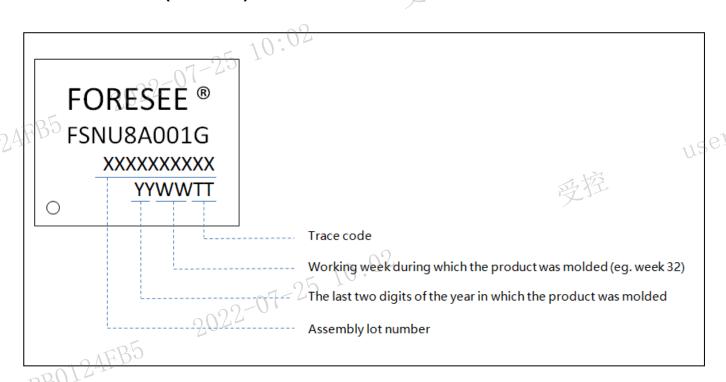

| 14 P | art Marking Scheme                     | 48      |

| 14.1 | 1 48-TSOP (20x12mm)                    | 48      |

| 14.2 | 2 63-TFBGA (11x9mm)                    |         |

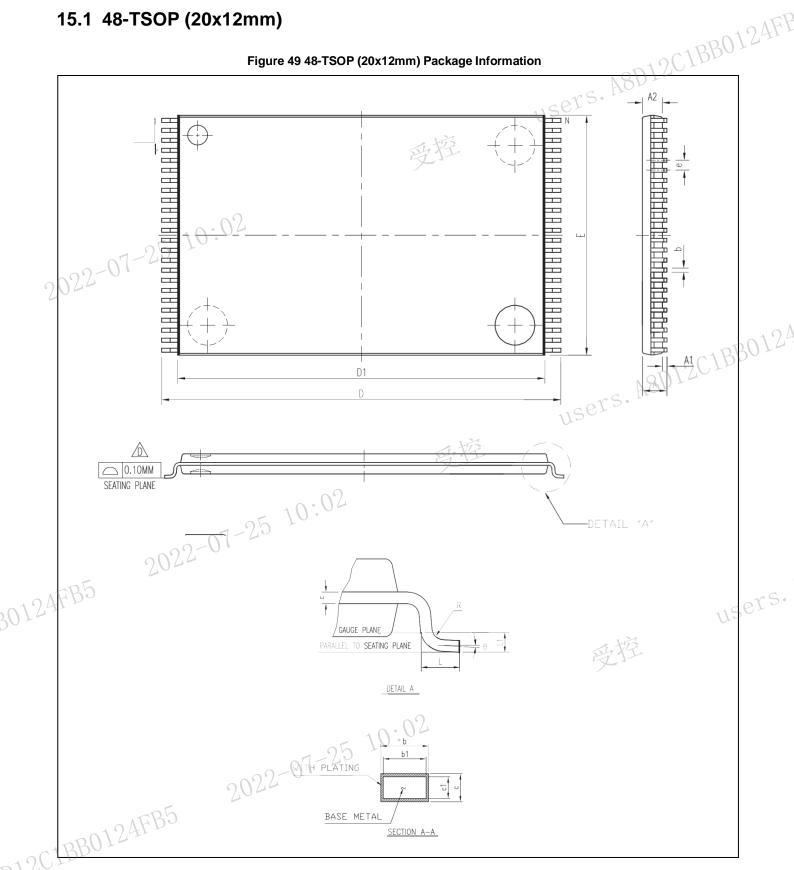

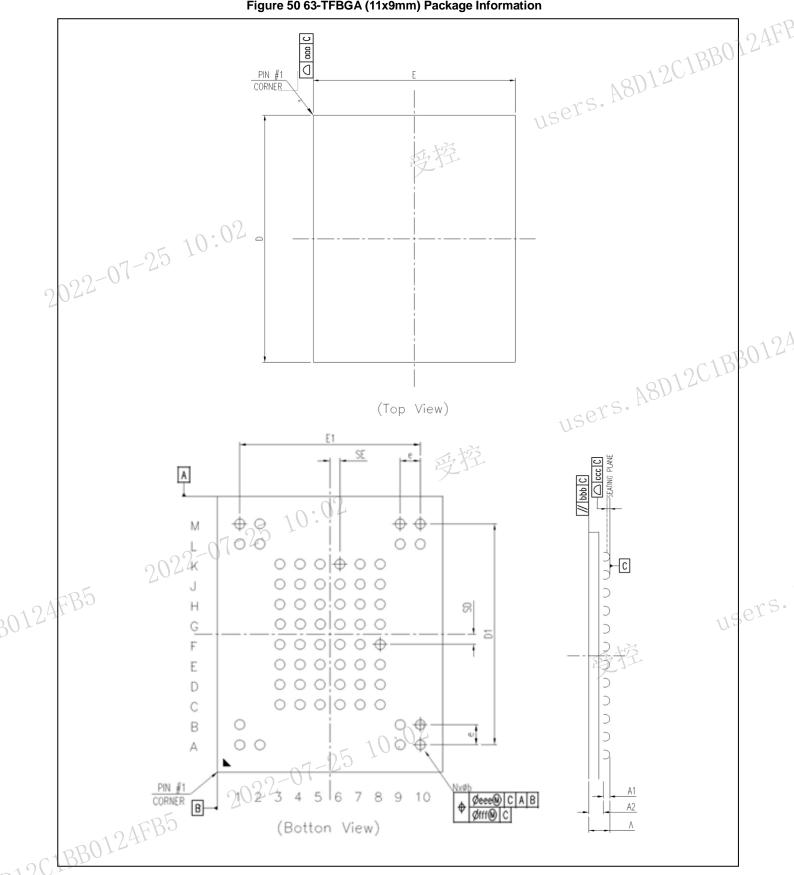

| 15 P | ackaging Information                   | 49      |

| 15.1 | 1 48-TSOP (20x12mm)                    | U.S. 49 |

| 15.2 | 2 63-TFBGA (11x9mm)                    | 51      |

2022-07-25 10:02

users.

2022-07-25 10:02

D12C1BB0124FB5

30124FB5

### **General Description** 1

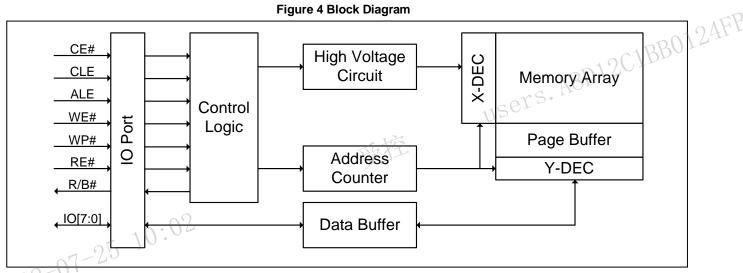

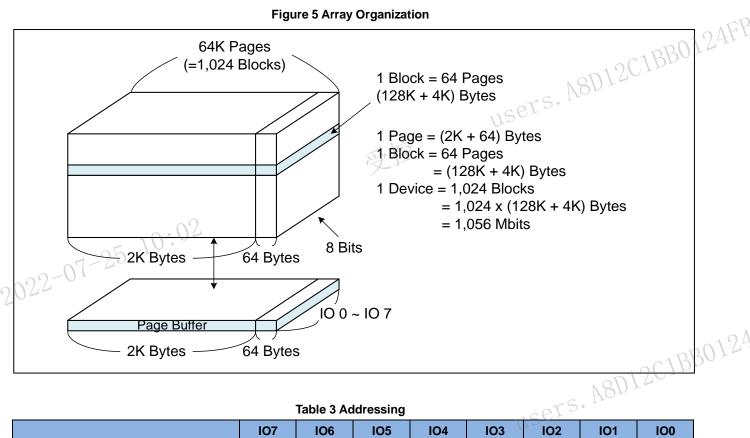

The FSNU8A001G is a 1G-bit (128Mx8bit) NAND Flash Memory with spare 32M-bit. The device on a single 1.8V VCC. A program operation can be performed in typical 350µs on the (2K+64) Byte page and an erase operation can be performed in typical 2ms on a (128K+4K) Byte block. Data in the page buffer can be read out at 25ns cycle time per Byte. The FSNU8A001G is an optimum solution for large nonvolatile storage applications such as solid state file storage and other portable applications requiring non-volatility.

The FSNU8A001G supports the standard NAND flash memory interface using the multiplexed 8-bit bus to transfer data, addresses, and command instructions. The five control signals, CLE, ALE, CE#, RE# and WE# handle the bus interface protocol. Also, the device has two other signal pins, the WP# and the R/B# for monitoring the device status.

### **Features**

### **Voltage Supply**

- VCC: 1.7V ~ 1.95V

### **Organization**

- Memory Cell Array: (128M + 4M) Byte

- Page Size: (2k + 64) Byte

- Block Size: 64 pages, (128k + 4k) Byte

- Plane Size: 1,024 Blocks

### High Performance

- Random Read: 25µs Sequential Read: 25ns

- Page Program Time: 350µs (Typ.)

- Block Erase Time: 2ms (Typ.)

### **Low Power**

- Standby: 10µA (Typ.)

- Read: 10mA (Typ.)

2022-07-25 10:0 - Program/Erase: 15mA (Typ.)

### **Advanced Features**

- .cut A8D12C1BB012A - Hardware WP# write protect

- Software block protect

- Unique ID

- One 2kB parameter page

- Sixty-two 2kB OTP Pages

- Promised golden block0

### **High Reliability**

- Endurance: typical 100k cycles (1)

- Data Retention: 10 years (1)

### **Package**

- 48-TSOP

- 63-TFBGA (11x9mm)

### Note:

(1) Endurance and Data Retention specification is based on

1bit / 528Byte ECC

users.

### 3 Product List

**Table 1 Product List**

| Part Number    | Density | I/O Type | Voltage Range | Package     | Temp. Range   | Packing |

|----------------|---------|----------|---------------|-------------|---------------|---------|

| FSNU8A001G-TWT | 1Gb     | x8       | 1.7V ~ 1.95V  | 48-TSOP     | -40°C ~ 85°C  | Tray    |

| FSNU8A001G-TAT | 1Gb     | х8       | 1.7V ~ 1.95V  | 48-TSOP     | -40°C ~ 105°C | Tray    |

| FSNU8A001G-BWT | 1Gb     | x8       | 1.7V ~ 1.95V  | 63-TFBGA    | -40°C ~ 85°C  | Tray    |

| FSNU8A001G-BAT | 1Gb     | x8       | 1.7V ~ 1.95V  | 63-TFBGA US | -40°C ~ 105°C | Tray    |

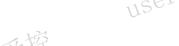

Figure 1 Marketing Part Numbering Chart

2022-07-25 10:02

**运**控

user

### **Package Types and Pin Configurations**

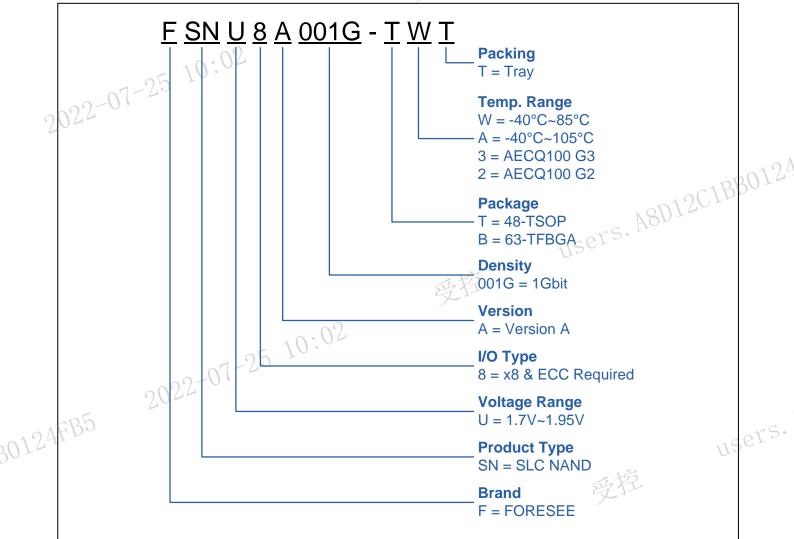

Figure 2 Pin Configuration 48-TSOP

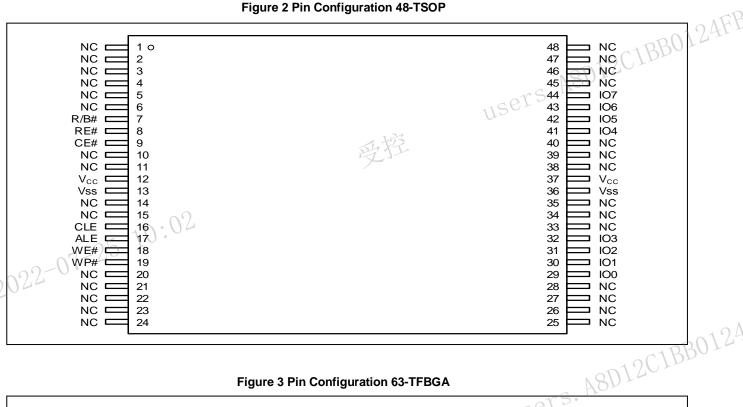

Figure 3 Pin Configuration 63-TFBGA

Everything for Memory 7/52 Longsys Copyright

### **Pin Descriptions** 5

**Table 2 Pin Description**

|           | Table 2 Pin Description                                                                                                        |

|-----------|--------------------------------------------------------------------------------------------------------------------------------|

| Pin Name  | Pin Functions Pin Functions                                                                                                    |

|           | Chip Enable                                                                                                                    |

| CE#       | The CE# input is the device selection control. When the device is in the Busy state, CE# high is ignored, and the              |

|           | device does not return to standby mode in program or erase operation.                                                          |

|           | Read Enable                                                                                                                    |

| RE#       | The RE# input is the serial data-out control, and when active drives the data onto the I/O bus. Data is valid t <sub>REA</sub> |

|           | after the falling edge of RE# which also increments the internal column address counter by one.                                |

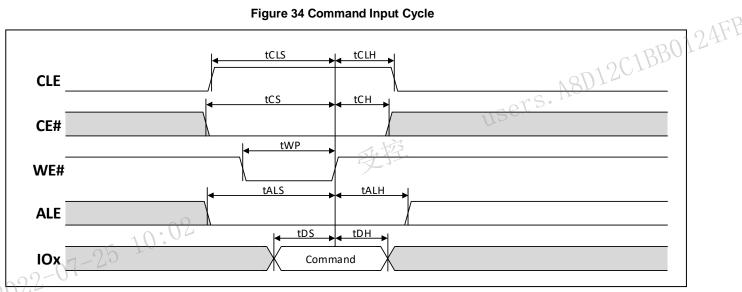

|           | Write Enable                                                                                                                   |

| WE#       | The WE# input controls writes to the I/O port. Commands, address and data are latched on the rising edge of                    |

| - 07      | the WE# pulse.                                                                                                                 |

| 022       | Command Latch Enable                                                                                                           |

| CLE       | The CLE input controls the activating path for commands sent to the command register. Commands are                             |

|           | latched on the rising edge of WE# with CLE high.                                                                               |

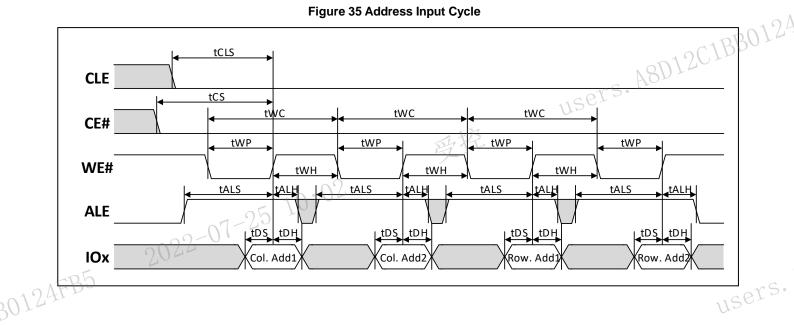

|           | Address Latch Enable                                                                                                           |

| ALE       | The ALE input controls the activating path for address sent to the address registers. Addresses are latched on                 |

|           | the rising edge of WE# with ALE high.                                                                                          |

|           | Write Protect                                                                                                                  |

| WP#       | The WP# input can be used to prevent the inadvertent program / erase to the device. All program / erase                        |

|           | operations are disabled when WP# is active low.                                                                                |

|           | Ready / Busy Output                                                                                                            |

| D/D#      | The R/B# output indicates the status of the device operation. When low, it indicates that a program, erase or                  |

| R/B#      | random read operation is in process and returns to high state upon completion. It is an open drain output and                  |

|           | does not float to high-z condition when the chip is deselected or when outputs are disabled.                                   |

|           | Data Inputs / Outputs                                                                                                          |

| 107 - 100 | The IO pins are used to input command, address and data and to output data during read operations. The IO                      |

| EBO       | pins float to high-z when the chip is deselected or when the outputs are disabled.                                             |

| VSS       | Ground                                                                                                                         |

2022-07-25 10:02

D12C1BB0124FB5 Everything for Memory

user

### **Block Diagram**

Figure 4 Block Diagram

2022-07-25 10:02

users.

users. A8D12C1BB012A

2022-07-25 10:02

D12C1BB0124FB5

30124FB5

9/52 Everything for Memory Longsys Copyright

### **Array Organization and Mapping**

Figure 5 Array Organization

**Table 3 Addressing**

|                |           | 107   | 106 | 105 | 104 | 103 | 102 | IO1 | 100 |

|----------------|-----------|-------|-----|-----|-----|-----|-----|-----|-----|

| Column Address | 1st cycle | A7    | A6  | A5  | A4  | A3  | A2  | A1  | A0  |

|                | 2nd cycle | L     | L   | L'Z | L   | A11 | A10 | A9  | A8  |

| Row Address    | 3rd cycle | A19   | A18 | A17 | A16 | A15 | A14 | A13 | A12 |

|                | 4th cycle | \ A27 | A26 | A25 | A24 | A23 | A22 | A21 | A20 |

10/52

### Note

- (1) L: A low condition, which must be held during the address cycle to insure correct processing.

- (2) A17~A12 are page addresses, A27~A18 are block addresses.

users.

2022-07-25 10:02

Longsys Copyright

D12C1BB0124FB5 Everything for Memory

### **Mode Selection**

### **Table 4 Mode Selection**

|        |                          | Table | 4 Mode Selec | ction  |       |      |                      |        |

|--------|--------------------------|-------|--------------|--------|-------|------|----------------------|--------|

|        | Mode                     |       | ALE          | CE#    | WE#   | RE#  | WP#                  | (2At 1 |

| Read   | Command Input            | Н     | L            | L      |       | Н    | 0018BU               | 10     |

| Reau   | Address Input (4 cycles) | L     | Н            | L      |       | 401  | X                    |        |

| Write  | Command Input            | Н     | L            | L      | LF    | s. H | Н                    |        |

| vviite | Address Input (4 cycles) | L     | Н            | L      | T. A. | Н    | Н                    |        |

|        | Data Input               |       | L            | With L |       | Н    | Н                    |        |

|        | Data Output              | L     | L发           | 17 L   | Н     | 7    | Х                    |        |

| D      | uring Read (Busy)        | Х     | Х            | Х      | Х     | Н    | Х                    |        |

| Dur    | ring Program (Busy)      | Х     | Х            | Х      | Х     | Х    | Н                    |        |

| Di     | During Erase (Busy)      |       | Х            | Х      | Х     | Х    | Н                    |        |

|        | Write Protect            |       | Х            | Х      | Х     | Х    | L                    |        |

| 02-0   | Stand-by                 | Х     | Х            | Н      | Х     | Х    | 0V / V <sub>CC</sub> | ]      |

Note

30124FB5

2022-07-25 10:02

users.

2022-07-25 10:02

D12C1BB0124FB5

11 / 52 Everything for Memory Longsys Copyright

<sup>(1) &</sup>quot;H" indicates a HIGH input level, "L" indicates a LOW input level, and "X" can be  $V_{IL}$  or  $V_{IH}$ . users. A8D12C1BB012A

### **Command Set**

**Table 5 Command Table**

|                                                                                        | Table 5 Command       | Table                                                 |                       | 1     |

|----------------------------------------------------------------------------------------|-----------------------|-------------------------------------------------------|-----------------------|-------|

| Command                                                                                | 1 <sup>st</sup> Cycle | 2 <sup>nd</sup> Cycle                                 | Acceptable While Busy | (24F) |

| Reset                                                                                  | FFh                   | -                                                     | Yes 1880              | 10    |

| Page Read                                                                              | 00h                   | 30h                                                   | 1801201               |       |

| Random Data Output                                                                     | 05h                   | E0h                                                   | S. Aus                |       |

| Read Status                                                                            | 70h                   | - 11563                                               | Yes                   |       |

| Read ID                                                                                | 90h                   | -                                                     |                       |       |

| Read Parameter Page                                                                    | ECh                   | <u> </u>                                              |                       |       |

| Read Unique ID                                                                         | EDh                   | -                                                     |                       |       |

| Page Program                                                                           | 80h                   | 10h                                                   |                       |       |

| Random Data Input                                                                      | 85h                   | -                                                     |                       |       |

| Copy Back Read                                                                         | 00h                   | 35h                                                   |                       |       |

| Copy Back Program                                                                      | 85h                   | 10h                                                   |                       |       |

| Block Erase                                                                            | 60h                   | D0h                                                   |                       |       |

| Get Feature                                                                            | EEh                   | -                                                     |                       |       |

| Set Feature                                                                            | EFh                   | -                                                     |                       | -194  |

| Note  (1) Random Data Input and Random Data  (2) Any commands not in the above table a | •                     | be used within a page. If and are prohibited as input | s. ASD12C1B           | B012  |

30124FB5

2022-07-25 10:02

users.

2022-07-25 10:02

D12C1BB0124FB5

12 / 52 Everything for Memory Longsys Copyright

### **Device Operation**

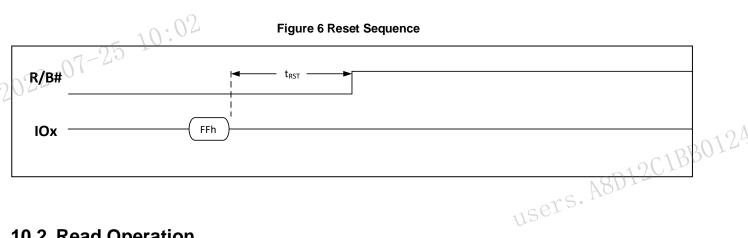

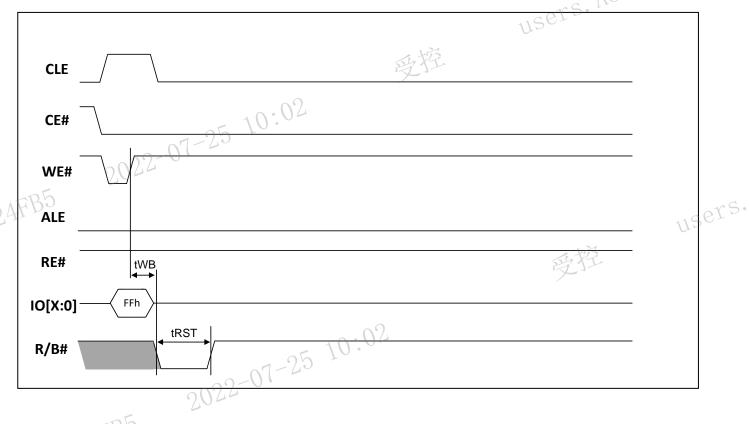

### 10.1 Reset (FFh)

,0124FB The device offers a reset operation, executed by writing FFh to the command register. When the device is in busy state during random read, program or erase mode, the reset operation will abort these operations. The contents of memory cells being altered are no longer valid, as the data will be partially programmed or erased. The command register is cleared to wait for the next command, and the Status Register is cleared to value C0h when WP# is high. If the device is already in Ready state, a new reset command will be accepted by the command register, and the device is reset instantly, but the R/B# pin will not change to low.

Figure 6 Reset Sequence

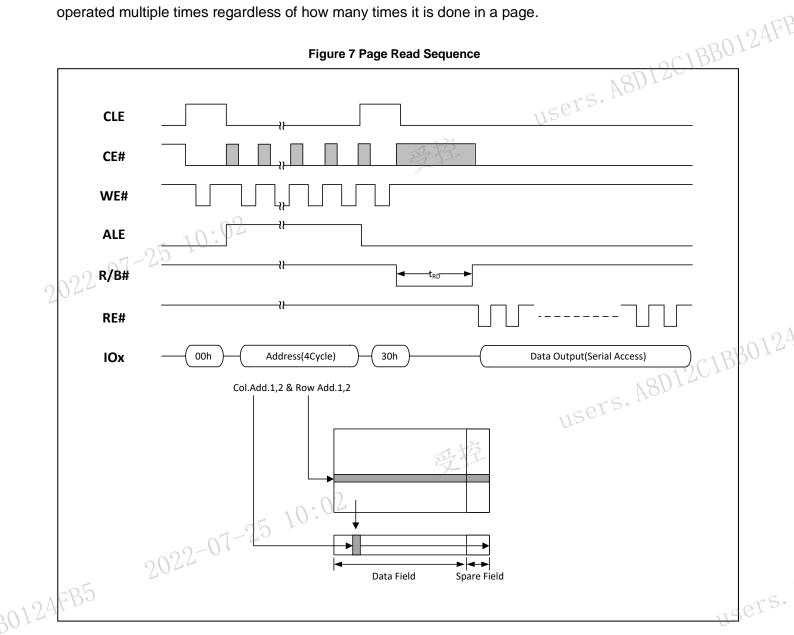

### 10.2 Read Operation

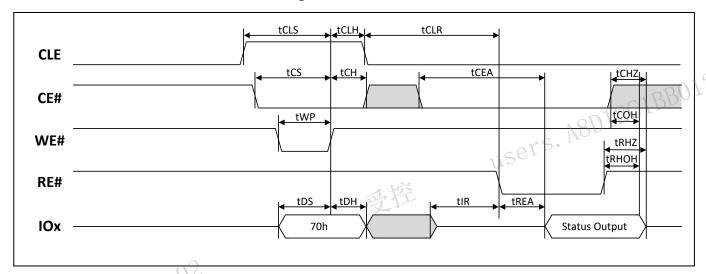

### 10.2.1 Page Read (00h-30h)

The FSNU8A001G array is accessed in page of 2,112 bytes. When the device powers on, 00h command is latched to command register. Therefore, system only issues four address cycles and 30h command for initial read from the device. This operation can also be entered by writing 00h command to the command register, and then write four address cycles, followed by writing 30h command. After writing 30h command, the data is transferred from NAND array to page buffer during t<sub>R</sub>.

Data transfer progress can be done by monitoring the status of the R/B# signal output. R/B# signal will be LOW during data transfer. Also, there is an alternate method by using the Read Status command. If the Read Status command is issued during read operation, the Page Read command must be re-issued to read out the data from page buffer.

Once the data in a page is loaded into the page buffer, R/B# signal goes high, and the data can be read from Page buffer by toggling RE#. Read is sequential from initial column address to the end of the page.

If the host side uses a sequential access time (t<sub>RC</sub>) of less than 30ns, the data can be latched on the next falling edge of RE# as the waveform of EDO mode.

The device may output random data in a page instead of the consecutive sequential data by writing Random Data Output command. The column address of next data, which is going to be out, may be changed to the address which follows random data output command. Random data output can be operated multiple times regardless of how many times it is done in a page.

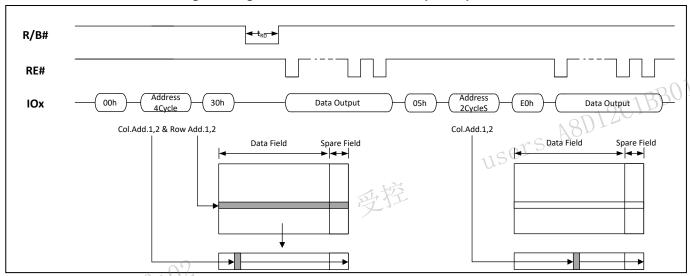

Figure 7 Page Read Sequence

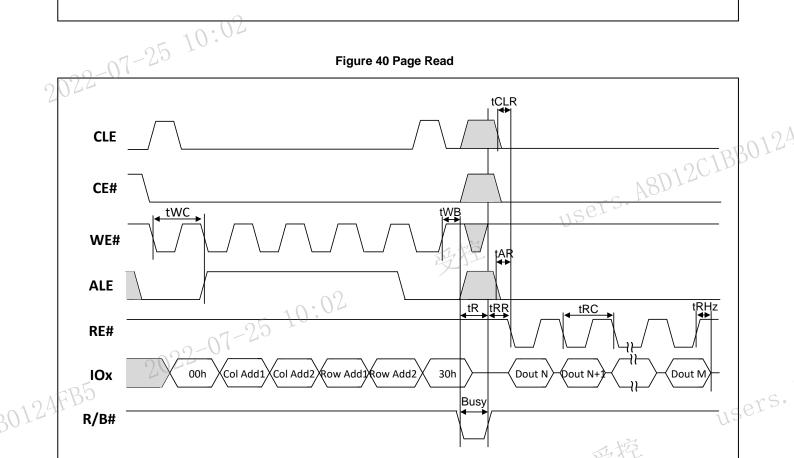

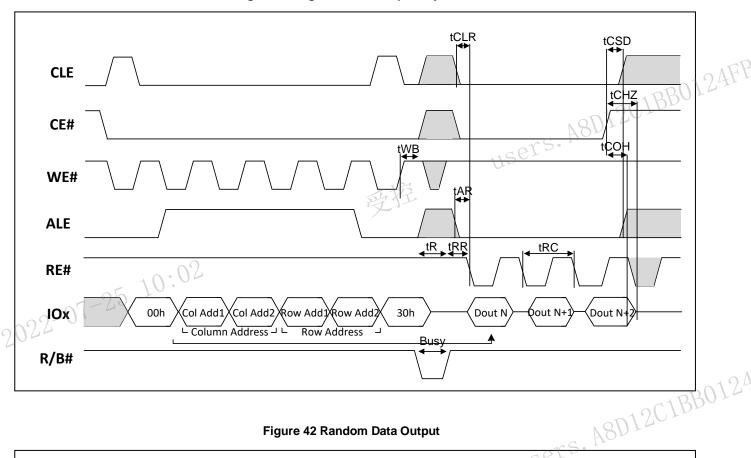

### 10.2.2 Random Data Output (05h-E0h)

D12CIBB0124FB5

The Random Data Output command allows the selection of random column addresses to read out data from a single or multiple of addresses. The use of the Random Data Output command is available after the Page Read (00h-30h) sequence by writing the 05h command following by the two cycle column address and then the E0h command. Toggling RE# will output data sequentially. The Random Data Output command can be issued multiple times, but limited to the current loaded page.

Everything for Memory 14/52 Longsys Copyright

Figure 8 Page Read with Random Data Output Sequence

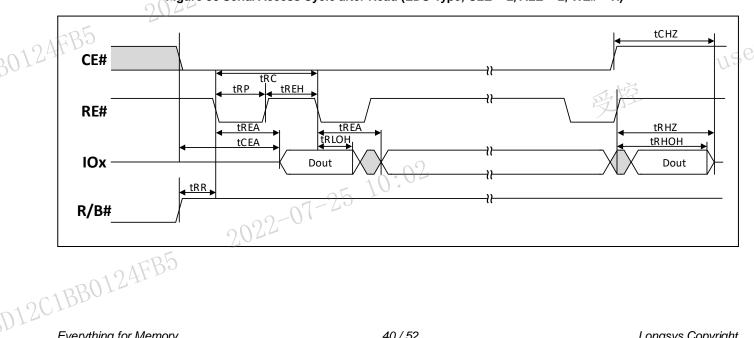

### 10.2.3 Read Status (70h)

The device contains a Status Register which may be read to find out whether program or erase operation is completed, and whether the program or erase operation is completed successfully. After writing 70h command to the command register, a read cycle outputs the content of the Status Register to the I/O pins on the falling edge of CE# or RE#, whichever occurs last. This two line control allows the system to poll the progress of each device in multiple memory connections even when R/B pins are common-wired. RE# or CE# does not need to be toggled for updated status. Refer to Table 6 for specific Status Register definitions.

The command register remains in Read Status mode until another command is issued. Therefore, if the status register is read during a random read cycle, the Page Read command should be given before starting read cycles.

30124FB5 users. **CLE** tCEA tCHZ CE# tWP ţCOḤ WE# tRHZ tRHOH RE# tREA Status Output **IOx**

Figure 9 Read Status Sequence

Everything for Memory 15/52 Longsys Copyright

| Table 6 | <b>Status</b> | Register | Definition |

|---------|---------------|----------|------------|

|---------|---------------|----------|------------|

| SR Bits | Page Program  | Block Erase   | Read          | Definition                     |  |  |  |  |

|---------|---------------|---------------|---------------|--------------------------------|--|--|--|--|

| IO 0    | Pass / Fail   | Pass / Fail   | Not use       | 0 = Pass, 1 = Fail             |  |  |  |  |

| IO 1    | Not use       | Not use       | Not use       | Don't -care                    |  |  |  |  |

| IO 2    | Not use       | Not use       | Not use       | Don't -care                    |  |  |  |  |

| IO 3    | Not use       | Not use       | Not use       | Don't -care                    |  |  |  |  |

| IO 4    | Not use       | Not use       | Not use       | Don't -care                    |  |  |  |  |

| IO 5    | Not Use       | Not Use       | Not Use       | Don't -care                    |  |  |  |  |

| IO 6    | Ready / Busy  | Ready / Busy  | Ready/Busy    | 0 = Busy, 1 = Ready            |  |  |  |  |

| IO 7    | Write Protect | Write Protect | Write Protect | 0 = Protected, 1 = Unprotected |  |  |  |  |

|         |               |               |               |                                |  |  |  |  |

Note

(1) IOs defined 'Not use' are recommended to be masked out when Read Status is being executed.

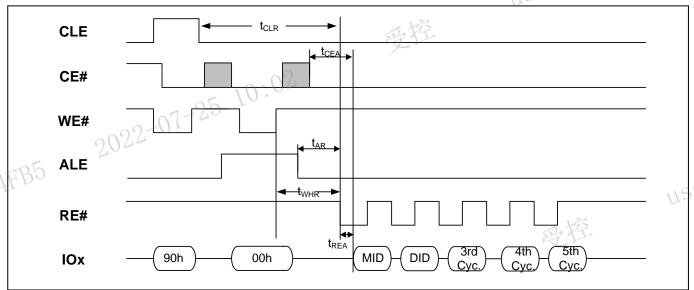

## 10.2.4 Read ID (90h).

Read ID command is comprised of two modes determined by the input address, device (00h) or ONFI (20h) identification information. To enter the Read ID mode, write 90h command following by a 00h address cycle, then toggle RE# for 5 single byte cycles. The pre-programmed code includes the Manufacturer ID, Device ID, and Product-Specific Information (See Table 8). If the Read ID command is followed by 20h address, the output code includes 4 single byte cycles of ONFI identifying information. The device remains in the Read ID mode until the next valid command is issued.

Figure 10 Read ID Sequence

Table 7 Device and ONFI identification information

| Addres        | s       | 1 <sup>st</sup> Byte/Cycle | 2 <sup>nd</sup> Byte/Cycle | 3 <sup>rd</sup> Byte/Cycle | 4 <sup>th</sup> Byte/Cycle | 5 <sup>th</sup> Byte/Cycle |

|---------------|---------|----------------------------|----------------------------|----------------------------|----------------------------|----------------------------|

| 00h           |         | CDh 22                     | A1h                        | 00h                        | 95h                        | 40h                        |

| Oon           | 00h     | Manufacturer ID            | Device ID                  | 0011                       | 9311                       | 4011                       |

| 20h           | Th De   | 4Fh                        | 4Eh                        | 46h                        | 49h                        | -                          |

| 12C1BB01      |         |                            |                            |                            |                            |                            |

| Frankhina for | r Mamar |                            | 16                         | / 50                       |                            | Langerya Convisio          |

### **Table 8 Product-Specific Information**

| Terms                                 | Description       | 107 | 106  | 105 | 104 | 103 | 102 | IO1 | 100  |  |

|---------------------------------------|-------------------|-----|------|-----|-----|-----|-----|-----|------|--|

| 3 <sup>rd</sup> Byte                  |                   |     | 00h  |     |     |     |     |     |      |  |

| Cache Program                         | 0 = Not supported | 0   |      |     |     |     |     |     |      |  |

| Multiple die operation                | 0 = Not supported |     | 0    |     |     |     |     |     | 20   |  |

| Simultaneously Programmed page number | 00 = 1            |     |      | 0   | 0   |     | 181 | 12C | BBC  |  |

| Cell type                             | 00 = SLC          |     |      |     |     | 0,5 | 0   |     |      |  |

| Die number per CE                     | 00 = 1            |     |      |     | U   | 50  |     | 0   | 0    |  |

| 4 <sup>th</sup> Byte                  |                   |     | 1.4% | 1   | 9   | 5h  |     |     |      |  |

| Sequential access min                 | 10 = 25ns         | 1   | 支小   |     |     | 0   |     |     |      |  |

| Organization                          | 0 = x8            |     | 0    |     |     |     |     |     |      |  |

| Block size (without spare)            | 01 = 128kB        |     |      | 0   | 1   |     |     |     |      |  |

| Spare size per 512B                   | 1 = 16            |     |      |     |     |     | 1   |     |      |  |

| Page size                             | 01 = 2kB          |     |      |     |     |     |     | 0   | 1    |  |

| 5 <sup>th</sup> Byte                  |                   | 40h |      |     |     |     |     |     |      |  |

| Internal ECC                          | 0 = Not supported | 0   |      |     |     |     |     |     |      |  |

| Plane size                            | 100 = 1Gb         |     | 1    | 0   | 0   |     |     |     |      |  |

| Plane number per CE                   | 00 = 1            |     |      |     |     | 0   | 0   |     |      |  |

| ECC requirement                       | 00 = 1bit / 528B  |     |      |     |     |     |     | 0   | - OP |  |

| 10.2.5 Read Parameter Page (ECh)      |                   |     |      |     |     |     |     |     |      |  |

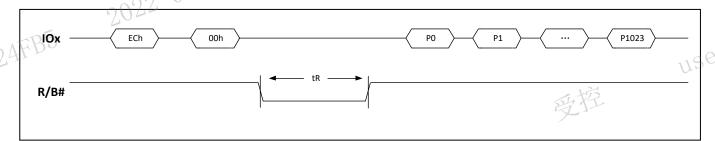

### 10.2.5 Read Parameter Page (ECh)

Read Parameter Page can read out the device's parameter data structure, such as, manufacturer information, device organization, timing parameters, key features, and other pertinent device parameters. The data structure is stored with at least three copies in the device's parameter page. The Random Data Output command is supported during data output.

Figure 11 Read Parameter Page Sequence

**Table 9 Parameter Definition**

|           |             | 711.5                                             |                   |

|-----------|-------------|---------------------------------------------------|-------------------|

| Byte      | Number      | Descriptions                                      | Values            |

| (         | 0~3         | Parameter Page Signature, "ONFI" ASCII characters | 4Fh 4Eh 46h 49h   |

| 4         | 4~5         | Revision Number                                   | 02h 00h           |

| 12C1BB0   | 124FB       |                                                   |                   |

| Everythin | na for Memo | rv 17/52                                          | Longsys Copyright |

| Byte Number           | Descriptions                                         | Values                     |  |  |  |

|-----------------------|------------------------------------------------------|----------------------------|--|--|--|

|                       | Feature Supported                                    |                            |  |  |  |

|                       | b6-b15 reserved (0)                                  |                            |  |  |  |

|                       | b5 1 = supports source synchronous                   |                            |  |  |  |

| 6.7                   | b4 1 = supports odd to even page Copyback            | 40k 00k                    |  |  |  |

| 6~7                   | b3 1 = supports interleaved operations               | 10h 00h                    |  |  |  |

|                       | b2 1 = supports non-sequential page programming      | 1801201                    |  |  |  |

|                       | b1 1 = supports multiple LUN operations              | ers. Aor                   |  |  |  |

|                       | b0 1 = supports 16-bit data bus width                | 10h 00h  USers. A8D12CIBBC |  |  |  |

|                       | Optional Command Supported                           |                            |  |  |  |

|                       | b6-b15 reserved (0)                                  |                            |  |  |  |

|                       | b5 1 = supports Read Unique ID                       |                            |  |  |  |

| 0.0                   | b4 1 = supports Copy-back                            | 0.41 0.01                  |  |  |  |

| 8~9                   | b3 1 = supports Read Status Enhanced                 | 34h 00h                    |  |  |  |

|                       | b2 1 = supports Get Features and Set Features        |                            |  |  |  |

| 07-20                 | b1 1 = supports Read Cache commands                  |                            |  |  |  |

| 022-01                | b0 1 = supports Page Cache Program command           |                            |  |  |  |

| 10~31                 | Reserved (0)                                         | all 00h                    |  |  |  |

|                       |                                                      | 46h 4Fh 52h 45h            |  |  |  |

| 32~43                 | Device manufacturer , 12 ASCII characters            | 53h 45h 45h 20h            |  |  |  |

|                       |                                                      | 20h 20h 20h 20h            |  |  |  |

|                       |                                                      | 46h 53h 4Eh 55h            |  |  |  |

|                       |                                                      | 38h 41h 30h 30h            |  |  |  |

| 44-63                 | Device Model, 20 ASCII characters                    | 31h 47h 20h 20h            |  |  |  |

|                       | 20h 20h 20h 20h                                      |                            |  |  |  |

|                       | 7                                                    | 20h 20h 20h 20h            |  |  |  |

| 64                    | JEDEC MID                                            | CDh                        |  |  |  |

| 65-66                 | Date Code 1000                                       | 00h 00h                    |  |  |  |

| 67-79                 | Reserved (0)                                         | all 00h                    |  |  |  |

| 80-83                 | Number of Data Bytes per Page                        | 00h 08h 00h 00h            |  |  |  |

| 84-85                 | Number of Spare Bytes per Page                       | 40h 00h                    |  |  |  |

| FB <sup>3</sup> 86-89 | Number of Data Bytes per Partial Page                | 00h 02h 00h 00h            |  |  |  |

| 90-91                 | Number of Spare Bytes per Partial Page               | 10h 00h                    |  |  |  |

| 92-95                 | Number of Pages per Block                            | 40h 00h 00h 00h            |  |  |  |

| 96-99                 | Number of Block per Logic Unit                       | 00h 04h 00h 00h            |  |  |  |

| 100                   | Number of Logic Units                                | 01h                        |  |  |  |

|                       | Number of Address Bytes                              |                            |  |  |  |

| 101                   | b4-b7 column address cycles                          | 22h                        |  |  |  |

|                       | b4-b7 column address cycles b0-b3 row address cycles |                            |  |  |  |

| 102                   | Number of Bits per Cell                              | 01h                        |  |  |  |

| 103-104               | Bad Blocks Maximum per Logic Unit                    | 14h 00h                    |  |  |  |

| 105-106               | Block Endurance                                      | 01h 05h                    |  |  |  |

| - A A - D             |                                                      |                            |  |  |  |

| 107                   | Guaranteed Valid Blocks at Beginning of Target       | 01h                        |  |  |  |

| 108-109               | Block Endurance for Guaranteed Valid Blocks          | 01h 03h                    |  |  |  |

4.47

| Byte Number | Descriptions                                           | Values                |

|-------------|--------------------------------------------------------|-----------------------|

| 110         | Number of Programs per Page                            | 04h                   |

|             | Partial Programming Attributes                         |                       |

|             | b5-b7 reserved (0)                                     |                       |

| 444         | b4 1 = partial page layout is partial page data        | 006                   |

| 111         | followed by partial page spare                         | 00h                   |

|             | b1-b3 reserved (0)                                     | (8D12011              |

|             | b0 1 = partial page programming has constraints        | ooh online ABD12C1BB0 |

| 112         | Number of ECC Bits Correctability                      | 01h).S                |

|             | Number of Interleaved Address Bits                     |                       |

| 113         | b4-b7 reserved (0)                                     | 00h                   |

|             | b0-b3 number of interleaved address bits               |                       |

|             | Interleaved Operation Attributes                       |                       |

|             | b4-b7 reserved (0)                                     |                       |

| 05          | b3 address restrictions for program cache              |                       |

| 114 - 2     | b2 1 = program cache supported                         | 00h                   |

| 114, -25    | b1 1 = no block address restrictions                   |                       |

|             | b0 overlapped / concurrent interleaving support        |                       |

| 115-127     | Reserved (0)                                           | all 00h               |

| 128         | I/O Pin Capacitance, Maximum                           | 08h                   |

|             | Asynchronous Timing Mode Support                       | users. A8D12C1B       |

|             | b6-b15 reserved (0)                                    | A8012                 |

|             | b5 1 = supports timing mode 5                          | users.                |

| 400 400     | b4 1 = supports timing mode 4                          | 451 001               |

| 129-130     | b3 1 = supports timing mode 3                          | 1Fh 00h               |

|             | b2 1 = supports timing mode 2                          |                       |

|             | b1 1 = supports timing mode 1                          |                       |

|             | b0 1 = supports timing mode 0, shall be 1              |                       |

|             | Asynchronous Program Cache Timing Mode Support         |                       |

| 00          | b6-b15 reserved (0)                                    |                       |

| 4           | b5 1 = supports timing mode 5                          |                       |

| FBO         | b4 1 = supports timing mode 4                          | 201-201-              |

| 131-132     | b3 1 = supports timing mode 3                          | 00h 00h               |

|             | b2 1 = supports timing mode 2                          |                       |

|             | b1 1 = supports timing mode 1                          | 受红                    |

|             | b0 1 = supports timing mode 0, shall be 1              |                       |

| 133-134     | t <sub>PROG</sub> Maximum Page Program Time (us)       | BCh 02h               |

| 135-136     | t <sub>BER</sub> Maximum Block Erase Time (us)         | 10h 27h               |

| 137-138     | t <sub>R</sub> Maximum Page read Time (us)             | 19h 00h               |

| 139~140     | t <sub>CCS</sub> Minimum Change Column Setup Time (ns) | 3Ch 00h               |

| 141-163     | Reserved (0)                                           | all 00h               |

| 164-165     | Vendor Specific Revision Number                        | 00h 00h               |

| 166-253     | Vendor Specific                                        | all 00h               |

| 254-255     | Integrity CRC                                          | 20h 47h               |

| L           | U 7 * *                                                |                       |

英控

Everything for Memory 19 / 52 Longsys Copyright

use

| Byte Number | Descriptions                         | Values |

|-------------|--------------------------------------|--------|

| 256-511     | Value of Bytes 0-255                 |        |

| 512-767     | Value of Bytes 0-255                 |        |

| 768+        | Additional Redundant Parameter Pages |        |

### Note:

(1) The Integrity CRC (Cycling Redundancy Check) field is used to verify that the contents of the parameters page were transferred correctly to the host. Please refer to ONFI 1.0 specifications for details. The CRC shall be calculated using the users. following 16-bit generator polynomial: G(X) = X16 + X15 + X2 + 1

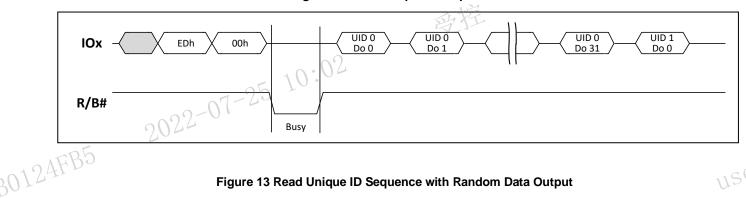

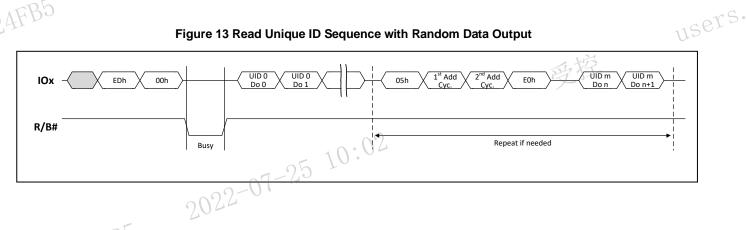

### 10.2.6 Read Unique ID (EDH)

The unique ID is 32-byte and with 16 copies for back-up purpose. After writing the Unique ID read command and following the one address byte (00h), the host may read out the unique ID data. The host need to XOR the 1st 16-byte unique data and the 2nd 16-byte complement data to get the result, if the result is FFh, the unique ID data is correct; otherwise, host need to repeat the XOR with the next copy of Unique ID data.

Once sending the EDh command, the NAND device will remain in the Unique ID read mode until next valid command is sent. The Random Data Output command is supported during data output.

The Read Status command can be used to check the completion. To continue the read operation, a following read command (00h) to re-enable the data out is peoperate. users. A81

Figure 12 Read Unique ID Sequence

Figure 13 Read Unique ID Sequence with Random Data Output

Longsys Copyright

D12CIBBO124FB5 Everything for Memory

20/52

### **10.3 Program Operation**

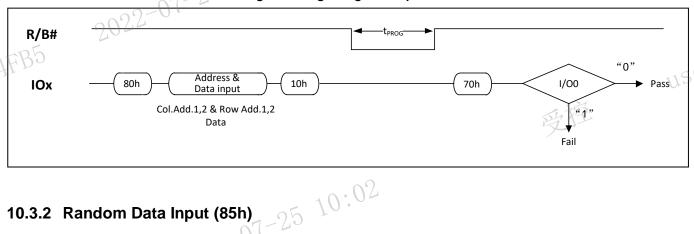

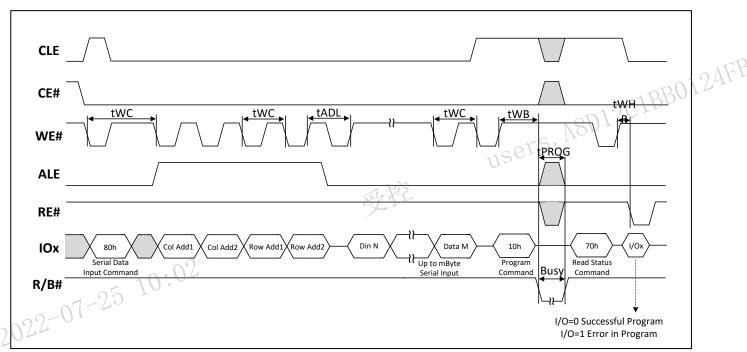

### 10.3.1 Page Program (80h-10h)

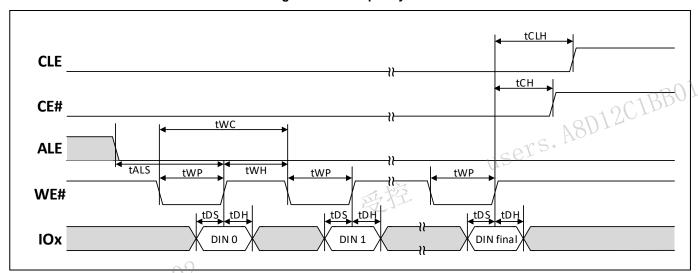

The device is programmed basically on a page basis, but it does allow multiple partial page programming of a word or consecutive bytes up to 2,112 in a single page program cycle. The number of consecutive partial page programming operation within the same page without an intervening erase operation must NOT exceed 4 times for a single page. The addressing should be done in sequential order in a block.

A page program cycle consist of a serial data loading period in which up to 2,112-bytes of data may be loaded into the page buffer, followed by a non-volatile programming period where the loaded data is programmed into the appropriate cell.

The serial data loading period begins by inputting the 80h command, followed by the four cycle address inputs and then serial data loading. The words other than those to be programmed do not need to be loaded. The 10h command initiates the programming process. Writing 10h alone without previously entering the serial data will not initiate the programming process.

The internal write state controller automatically exe-cutes the algorithms and timings necessary for program and verify, thereby freeing the system controller for other tasks. Once the program process starts, the Read Status command may be entered to read the status register. The system controller can detect the completion of a program cycle by monitoring the R/B# output, or the Status bit (IO6) of the Status Register. Only the Read Status command and Reset command are valid while programming is in progress. When the Page Program is complete, the Write Status bit (IO 0) may be checked (See Figure 14). The internal write verify detects only errors for "1"s that are not successfully programmed to "0"s. The command register remains in Read Status command mode until another valid command is written to the command register.

Figure 14 Page Program Sequence

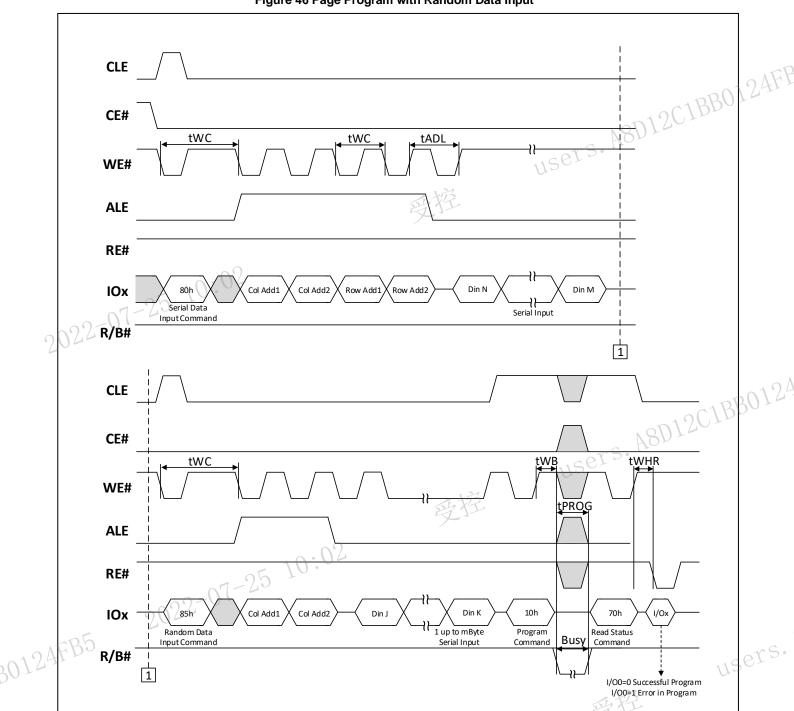

### 10.3.2 Random Data Input (85h)

After the Page Program 80h command execution of the initial data has been loaded into the page buffer, if the need for additional writing of data is required, using the Random Data Input command can perform this function to a new column address prior to the 10h command. The Random Data Input may be operated multiple times regardless of how many times it is done in a page.

R/B#

IOx

80h

Address & Data input

Col.Add.1,2 & Row Add.1,2

Data

Data

Data

Data

Data

Data

Data

Data

Data

Figure 15 Page Program with Random Data Input Seguence

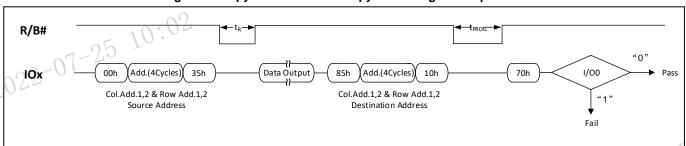

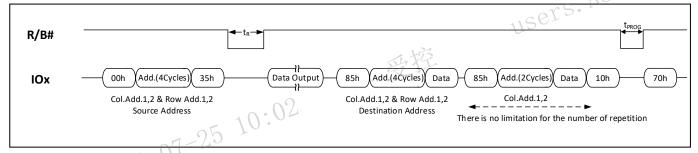

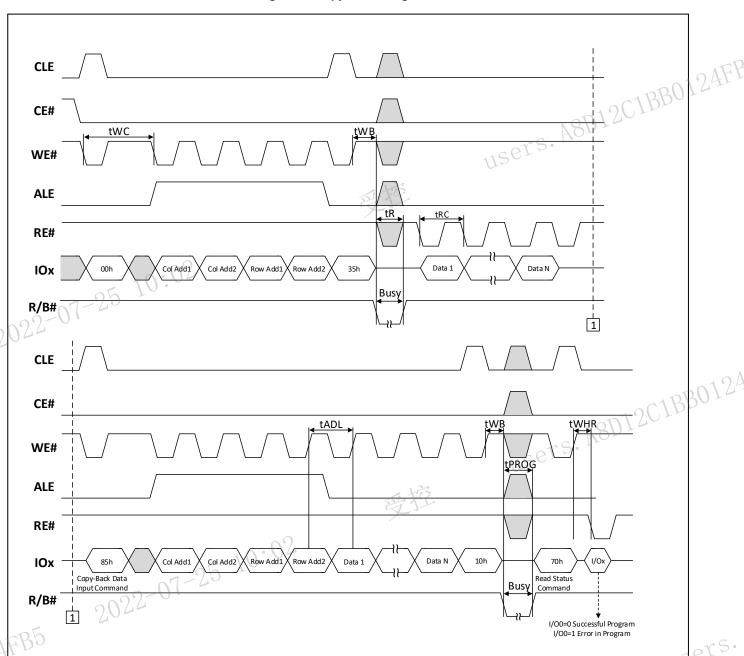

### 10.4 Copy Back Operation

Copy Back operations can quickly and efficiently rewrite data stored in one page. The benefit is especially obvious when a portion of a block is updated and the rest of the block also needs to be copied to the newly assigned free block. The operations require two sequential command sets. Issue a Copy Back Read command first, then the Copy Back Program command.

Since Copy Back operations do not use external memory and the data of source page might include a bit errors, a competent ECC scheme should be developed to check the data before programming data to a new destination page.

Note: Copy Back Operation can only be used to copy even page to even page or to copy odd page to odd page.

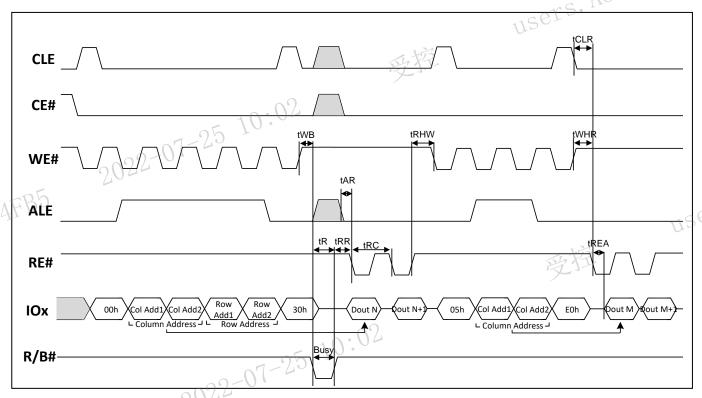

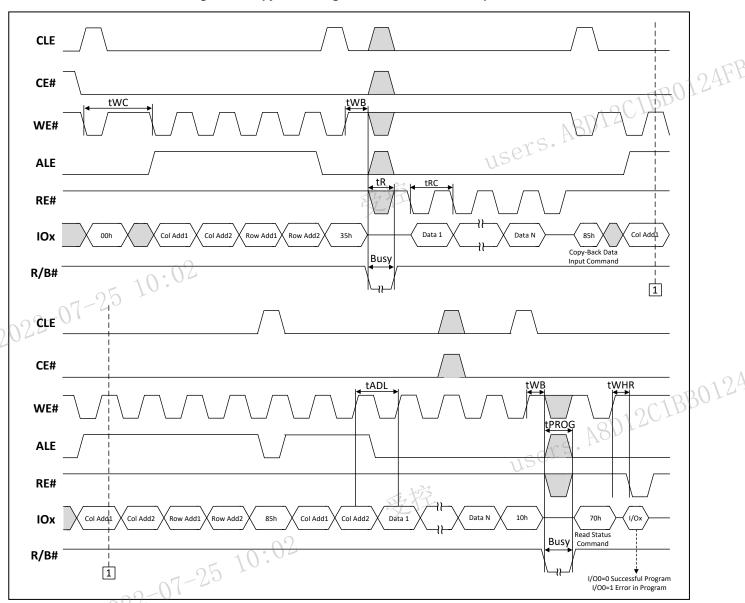

### 10.4.1 Copy Back Read (00h-35h)

The Copy Back Read command is used together with the Copy Back Program command. To start execution, 00h command is written to the command register, followed by the four cycles of the source page address. To start the transfer of the selected page data from the memory array to the page buffer, write the 35h command to the command register.

After execution of the Copy Back Read command sequence and R/B# returns to HIGH marking the completion of the operation, the transferred data from the source page into the page buffer may be read out by toggling RE#. Data is output sequentially from the column address that was originally specified with the Copy Back Read command (See **Figure 16**).

The Random Data Output commands can be issued multiple times without any limitation after Copy Back Read command has been executed.

### 10.4.2 Copy Back Program (85h-10h)

After the Copy Back Read command operation has been completed and R/B# goes HIGH, the Copy Back Program command can be written to the Command Register.

在校

Everything for Memory 22 / 52 Longsys Copyright

The operation is initiated by issuing 85h command with destination page address. Actual programming operation begins after 10h command is issued. Once the program process starts, the Read Status command may be entered to read the status register. The system controller can detect the completion of a program cycle by monitoring the R/B# output, or the Status bit (IO6) of the Status Register. When the copy back program is complete, the Write Status Bit (IO0) may be checked (See **Figure 16**). The command register remains in Read Status command mode until another valid command is written to the command register.

During copy-back program, data modification is possible using Random Data Input command with multiple times (see **Figure 17**).

Figure 16 Copy Back Read and Copy Back Program Sequence

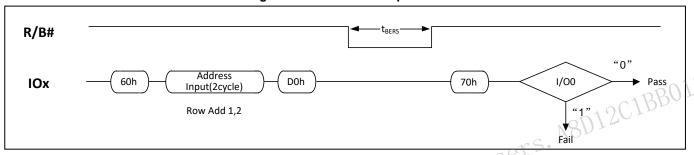

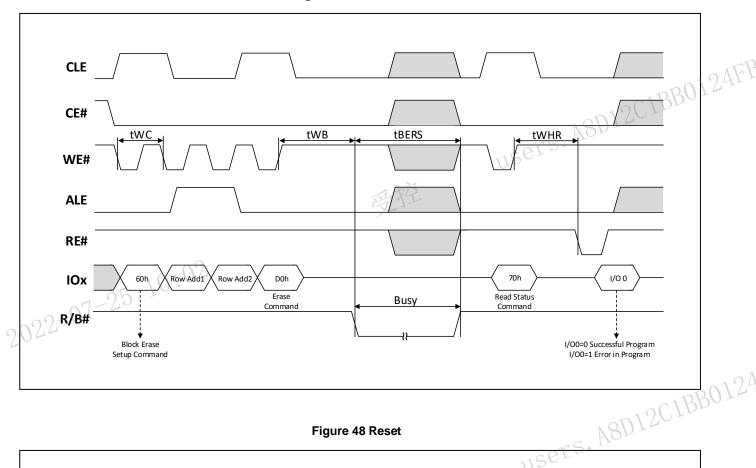

### 10.5 Block Erase (60h-D0h)

The erase operation is done on a block basis. Block address loading is accomplished in two cycles initiated by 60h command. Only address A18 to A27 is valid while A12 to A17 is ignored. The D0h command following the block address loading initiates the internal erasing process. This two-step sequence of setup followed by execution command ensures that memory contents are not accidentally erased due to external noise conditions.

At the rising edge of WE# after the erase confirm command input, the internal write controller handles erase and erase-verify. The system controller can detect the completion of an erase cycle by monitoring the R/B# output, or the Status bit (IO6) of the Status Register. When the block erase operation is complete, the Write Status Bit (IO0) may be checked.

红花

user

### Figure 18 Block Erase Sequence

### **10.6 Feature Operation**

The Feature Set operation is to change the default power-on feature sets by using the Set Feature and Get Feature command and writing the specific parameter data (P1-P4) on the specific feature addresses. The NAND device may remain the current feature set until next power cycle since the feature set data is volatile. However, the Reset command cannot reset the current feature set.

### 10.6.1 Feature Register

**Table 10 Feature Register**

| Table 10 Feature Register |         |           |              |              |     |        |         |     | 012 |     |                                                                                     |         |  |  |  |  |  |

|---------------------------|---------|-----------|--------------|--------------|-----|--------|---------|-----|-----|-----|-------------------------------------------------------------------------------------|---------|--|--|--|--|--|

| Feature<br>Register       | Address | Parameter | 107          | 106          | 105 | 104    | 103     | 102 | IO1 | 100 | Description                                                                         | )0 -    |  |  |  |  |  |

|                           |         |           | 0            | 0            | 0   | 0      | 0       | 0   | 0   | 0 1 | Normal Mode, default value after power cycle.                                       |         |  |  |  |  |  |

|                           |         | P1        | 0            | 0            | 0   | 0      | 0       | 挖   | 0   | 1   | OTP Operation Mode. See 10.7.1 for detail information                               |         |  |  |  |  |  |

| Operation<br>Mode         | 90h     |           | 0 (          | .02          | 0   | 0      | 0       | 0   | 1   | 1   | OTP Lock Mode. See 10.7.2 for detail information                                    |         |  |  |  |  |  |

|                           |         |           |              |              |     |        | P2-20   | 1   |     |     | Reserv                                                                              | ved (0) |  |  |  |  |  |

|                           |         | P3        | Reserved (0) |              |     |        |         |     |     |     |                                                                                     |         |  |  |  |  |  |

|                           |         | P4        |              | Reserved (0) |     |        |         |     |     |     |                                                                                     |         |  |  |  |  |  |

| Block<br>Protection       | A0h     | P1        | R            | BP3          | BP2 | BP1    | BP0     | ТВ  | 0   | SP  | Default value after power cycle is 00000000 (00h).  See 10.8 for detail information | ers     |  |  |  |  |  |

|                           |         | P2        |              | ı            | I.  | Reserv | ved (0) | I.  | I.  |     |                                                                                     |         |  |  |  |  |  |

|                           |         | P3        |              |              |     | Reserv | ved (0) |     |     |     |                                                                                     |         |  |  |  |  |  |

|                           |         | P4        |              | Reserved (0) |     |        |         |     |     |     |                                                                                     |         |  |  |  |  |  |

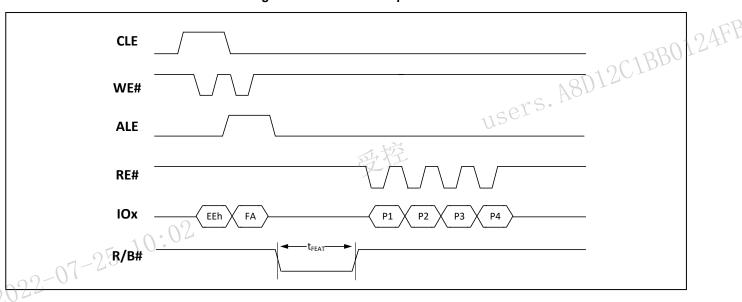

10.6.2 Get Feature (EEh) The Get Feature command is to read feature parameter. After sending the Get Feature command and following register address, the host may read out the P1-P4 sub-feature parameter data. Once sending the EEh command, the NAND device will remain in the Get Feature mode until next valid command is

sent.

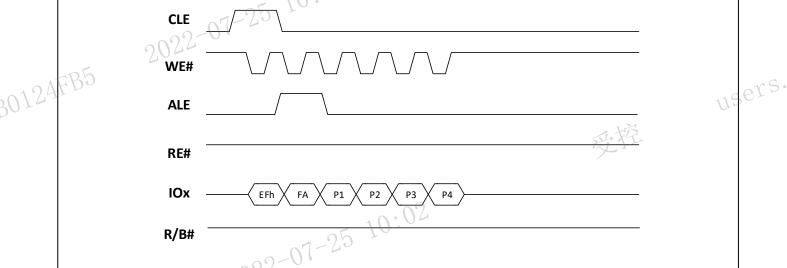

### 10.6.3 Set Feature (EFh)

The Set Feature command is to change the power-on default feature set. After sending the Set Feature command and following register address and then input the P1-P4 parameter data to change the feature set. Once sending the EFh command, the NAND device will remain in the Set Feature mode until next valid command is sent. The Set Feature command is completed instantly, and the R/B# pin will not change to low.

**CLE**

Figure 20 Set Feature Sequence

D12CIBB0124FB5 25/52 Everything for Memory Longsys Copyright

### 10.7 OTP Operation

The OTP area has 62 pages (62 x 2,112-byte). It is a non-erasable and one-time programmable area, which is default to "1" and allows whole page or partial page program to be "0". Once the OTP protection mode is set, the OTP area becomes read-only and cannot be programmed again.

The OTP operation is operated by the Set Feature / Get Feature operation to access the OTP Operation Mode and OTP Lock Mode.

To check the NAND device is ready or busy in the OTP operation mode, either checking the R/B# or using the Read Status command to check the status.

To exit the OTP operation or protect mode, it can be done by writing 00h to P1 at feature address 90h.

### 10.7.1 OTP Read / Program Operation

To enter the OTP Operation Mode, it is by using the Set Feature command and followed by the feature address 90h and then input the 01h to P1 and 00h to P2-P4 of sub-Feature Parameter data (see Table 10 Feature Register).

After enter the OTP Operation Mode, the OTP area can be read or programmed like non-OTP area. The users. address of OTP is located on the 02h-3Fh of page address.

### 10.7.2 OTP Lock Operation

To prevent the further OTP data to be changed, the OTP lock operation is necessary. To enter the OTP Lock Mode, it can be done by using the Set Feature command and followed by the feature address 90h and then input the 03h to P1 and 00h to P2-P4 of sub-Feature Parameter data (see Table 10 Feature Register). And then the normal Page Program command with the address 00h before the 10h command is required.

The OTP lock operation is operated on the whole OTP area instead of individual OTP page. Once the OTP protection mode is set, the OTP area can NOT be programmed or unprotected again.

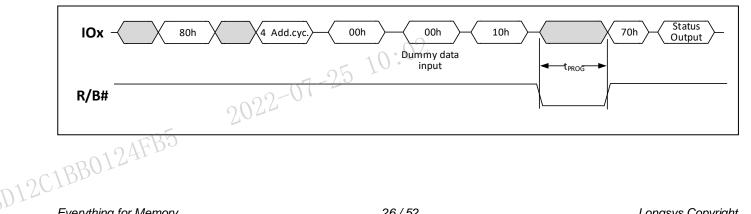

Figure 21 OTP Lock Operation Sequence

### 10.8 Block Protection

The block protect operation can protect the whole chip or selected blocks from erasing or programming. When program or erase attempt at a protected block is happened, the R/B# keeps low for the time of t<sub>PBSY</sub>, and the Status Read command may get the 41h result.

At power-on, all the blocks are default to be un-protected. The Set Feature command with feature address A0h followed by the destined protection bits with data "1" is necessary to protect those selected blocks. After the selected blocks are protected, those protected blocks can be un-protected again by reset Block Protection Bit to "0" if required.

The "solid-protection" feature can be set by writing the Set Feature command with feature address A0h and the "SP" solid protection bit as "1" (see Table 10 Feature Register), after that, the selected block is solid-protected and cannot be up-protected until next power cycle.

**Table 11 Block Protection Bits**

| COIIC | solid protected and calmot be up protected until next power cycle. |     |     |     |                |                       |           |             |      |

|-------|--------------------------------------------------------------------|-----|-----|-----|----------------|-----------------------|-----------|-------------|------|

|       | 0-07                                                               | -25 | )   |     | Table 11       | Block Protection Bits |           |             |      |

| 204   | H DDG                                                              | DDG | DD4 | DDO | Protected      | Protected Page        | Protected | Protected   |      |

| ТВ    | BP3                                                                | BP2 | BP1 | BP0 | Block(s)       | Address PA[15:0]      | Density   | Portion     |      |

| Х     | 0                                                                  | 0   | 0   | 0   | NONE           | NONE                  | NONE      | NONE        | 0121 |

| 0     | 0                                                                  | 0   | 0   | 1   | 1022 & 1023    | FF80h - FFFFh         | 256KB     | Upper 1/512 | 8017 |

| 0     | 0                                                                  | 0   | 1   | 0   | 1020 thru 1023 | FF00h - FFFFh         | 512KB     | Upper 1/256 |      |

| 0     | 0                                                                  | 0   | 1   | 1   | 1016 thru 1023 | FE00h - FFFFh         | 1MB ~S    | Upper 1/128 |      |

| 0     | 0                                                                  | 1   | 0   | 0   | 1008 thru 1023 | FC00h - FFFFh         | 2MB       | Upper 1/64  |      |

| 0     | 0                                                                  | 1   | 0   | 1   | 992 thru 1023  | F800h - FFFFh         | 4MB       | Upper 1/32  |      |

| 0     | 0                                                                  | 1   | 1   | 0   | 960 thru 1023  | F000h - FFFFh         | 8MB       | Upper 1/16  |      |

| 0     | 0                                                                  | 1   | 1   | 1   | 896 thru 1023  | E000h - FFFFh         | 16MB      | Upper 1/8   |      |

| 0     | 1                                                                  | 0   | 0   | 0   | 768 thru 1023  | C000h - FFFFh         | 32MB      | Upper 1/4   |      |

| 0     | 1                                                                  | 0   | 0   | 1   | 512 thru 1023  | 8000h - FFFFh         | 64MB      | Upper 1/2   |      |

| 1     | 0                                                                  | 0   | 00- | 01  | 0 & 1          | 0000h – 007Fh         | 256KB     | Lower 1/512 |      |

| 1     | 0                                                                  | 0   | 1   | 0   | 0 thru 3       | 0000h - 00FFh         | 512KB     | Lower 1/256 |      |

| 153   | 0                                                                  | 0   | 1   | 1   | 0 thru 7       | 0000h - 01FFh         | 1MB       | Lower 1/128 | 105. |

| 1     | 0                                                                  | 1   | 0   | 0   | 0 thru 15      | 0000h - 03FFh         | 2MB       | Lower 1/64  | ers. |

| 1     | 0                                                                  | 1   | 0   | 1   | 0 thru 31      | 0000h - 07FFh         | 4MB       | Lower 1/32  |      |

| 1     | 0                                                                  | 1   | 1   | 0   | 0 thru 63      | 0000h - 0FFFh         | 8MB       | Lower 1/16  |      |

| 1     | 0                                                                  | 1   | 1   | 1   | 0 thru 127     | 0000h - 1FFFh         | 16MB      | Lower 1/8   |      |

| 1     | 1                                                                  | 0   | 0   | 0   | 0 thru 255     | 0000h - 3FFFh         | 32MB      | Lower 1/4   |      |

| 1     | 1                                                                  | 0   | 0   | 1   | 0 thru 511     | 0000h - 7FFFh         | 64MB      | Lower 1/2   |      |

| Х     | 1                                                                  | 0   | 1   | Х   | 0 thru 1023    | 0000h - FFFFh         | 128MB     | ALL         |      |

| Х     | 1                                                                  | 1   | Х   | Х   | 0 thru 1023    | 0000h - FFFFh         | 128MB     | ALL         |      |

D12CIBB0124FB5

### **10.9 Write Protect**

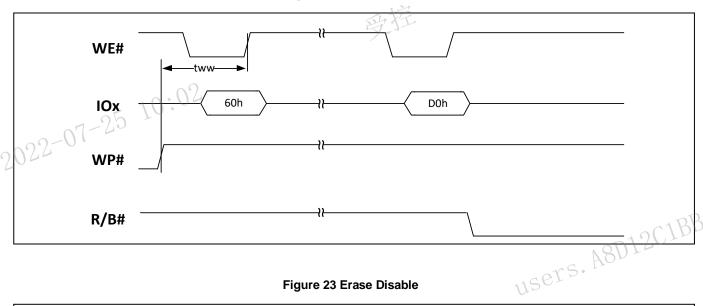

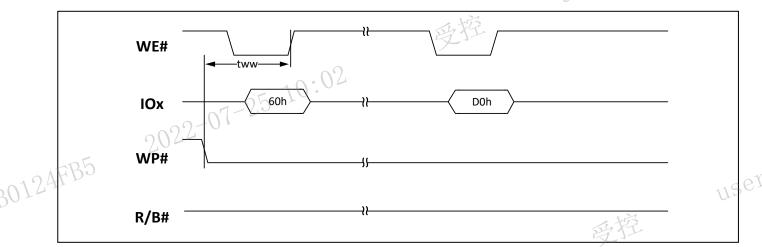

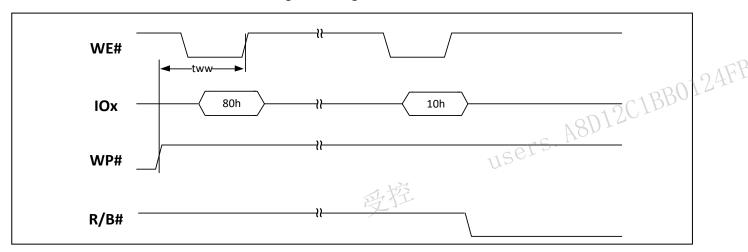

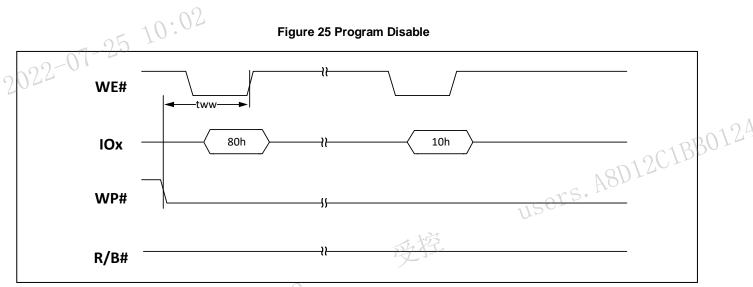

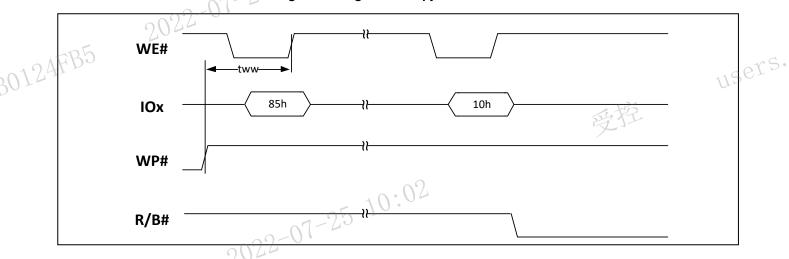

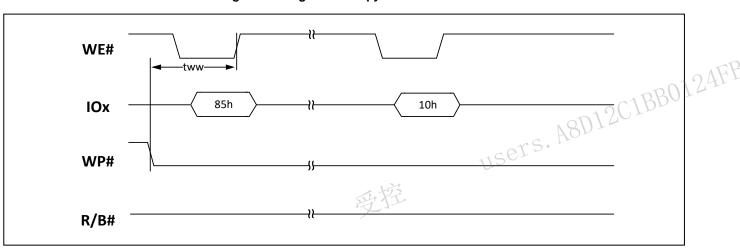

WP# pin can enable or disable program and erase commands preventing or allowing program and erase operations. Figure 22 to Figure 27 shows the enabling or disabling timing with WP# setup time (tww) that is from rising or falling edge of WP# to latch the first commands. After first command is latched, WP# pin must not toggle until the command operation is complete and the device is in the ready state. (Status users. A81 Register Bit6 (IO6) equal 1).

Figure 22 Erase Enable

Figure 23 Erase Disable

2022-07-25 10:02

D12CIBB0124FB5 Everything for Memory 28/52 Longsys Copyright

Figure 24 Program Enable

Figure 25 Program Disable

Figure 26 Program for Copy-Back Enable

D12C1BB0124FB5 29/52 Everything for Memory Longsys Copyright

### Figure 27 Program for Copy-Back Disable

2022-07-25 10:02

users. A8D12C1BB012A

受控

2022-07-25 10:02

users.

受控

2022-07-25 10:02

D12C1BB0124FB5

30124FB5

Everything for Memory 30 / 52 Longsys Copyright

USET

### **Software Algorithm**

### 11.1 Initial Invalid Block(s)

30124FB Initial invalid blocks are defined as blocks that contain one or more initial invalid bits whose reliability is not guaranteed. Devices with initial invalid block(s) have the same quality level as devices with all valid blocks and have the same electrical characteristics. An initial invalid block(s) does not affect the performance of valid block(s). The system design must be able to mask out the initial invalid block(s) via address mapping. The 1st block, which is placed on 00h block address, is guaranteed to be a valid block at the time of shipment.

**Table 12 Valid Block Number**

| Parameter          | Symbol          | Min  | Max  | Unit   |

|--------------------|-----------------|------|------|--------|

| Valid block number | N <sub>VB</sub> | 1004 | 1024 | Blocks |

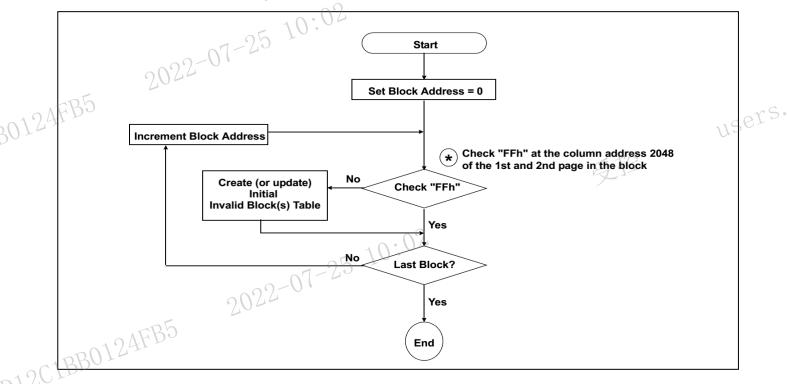

### 11.2 Identifying Initial Invalid Block(s)

All device locations are erased (FFh) except locations where the initial invalid block(s) information is written prior to shipping. All initial invalid blocks are marked with non-FFh at the first byte of spare area on the 1st or 2nd page. Since the initial invalid block information is also erasable in most cases, it is impossible to recover the information once it has been erased. Therefore, the system must be able to recognize the initial invalid block(s) based on the original initial invalid block information and create the initial invalid block table via the suggested flow (Figure 28). Any intentional erasure of the original initial invalid block information is prohibited.

Figure 28 Flow to Create Initial Invalid Block Table

31/52 Everything for Memory Longsys Copyright

### 11.3 Error in Operation

Within its life time, additional invalid blocks may develop with NAND Flash memory. The following possible failure modes should be considered to implement a highly reliable system. In the case of status read failure after erase or program, block replacement should be done. Because program status fail during a page program does not affect the data of the other pages in the same block, block replacement can be executed with a page-sized buffer by finding an erased empty block and reprogramming the current target data and copying the rest of the replaced block. In case of Read, ECC must be employed. To improve the efficiency of memory space, it is recommended that the read or verification failure due to single bit error be reclaimed by ECC without any block replacement. The said additional block failure rate does not include those reclaimed blocks.

**Table 13 Failure Modes**

| Operation | Detection and recommended procedure           |  |  |  |  |  |

|-----------|-----------------------------------------------|--|--|--|--|--|

| Erase     | Status read after erase → Block Replacement   |  |  |  |  |  |

| Program   | Status read after program → Block Replacement |  |  |  |  |  |

| Read      | Verify ECC → ECC correction                   |  |  |  |  |  |

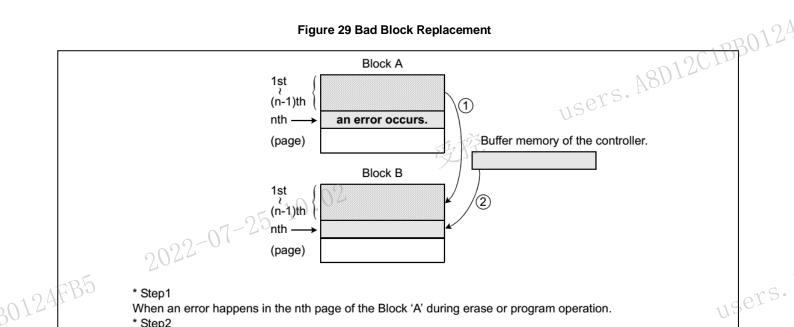

**Figure 29 Bad Block Replacement**

\* Step1

When an error happens in the nth page of the Block 'A' during erase or program operation.

Copy the data in the 1st ~ (n-1)th page to the same location of another free block. (Block 'B')

\* Step3

Then, copy the nth page data of the Block 'A' in the buffer memory to the nth page of the Block 'B'.

\* Step4

Do not erase or program to Block 'A' by creating an 'invalid block' table or other appropriate scheme.

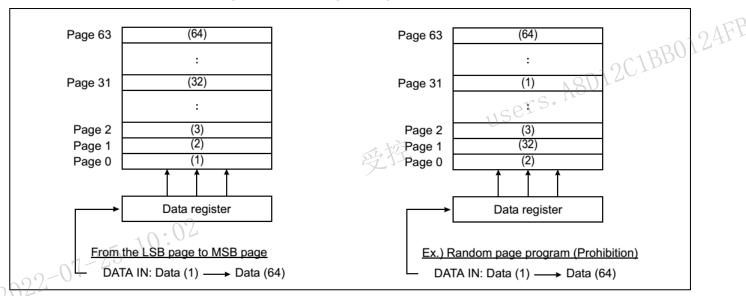

### 11.4 Addressing for Program Operation

Within a block, the pages must be programmed consecutively from the LSB(least significant bit) page of the block to the MSB(most significant bit) pages of the block. The LSB page is defined as the start page among the pages to be programmed, does not need to be page 0 in the block. Random page address

32 / 52

programming is prohibited.

Figure 30 Addressing for Program Operation

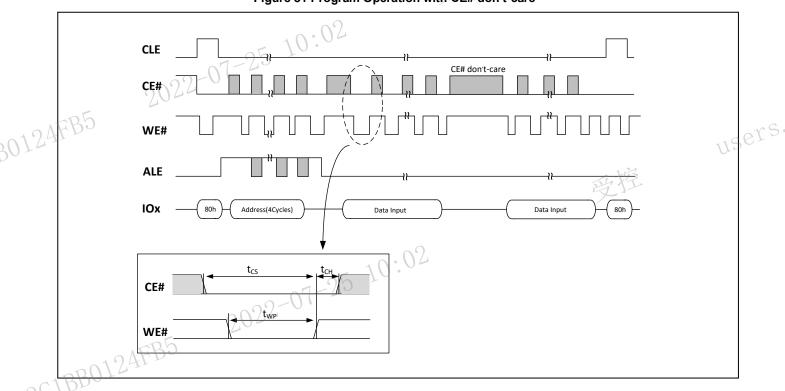

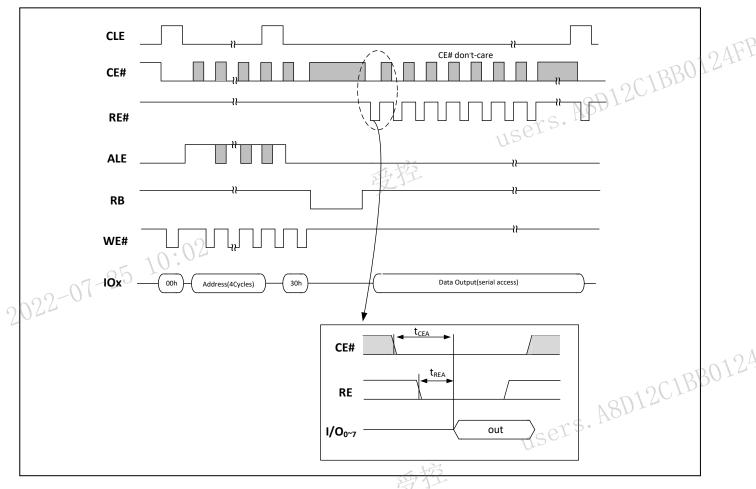

### 11.5 System Interface Using CE# Don't-Care

For an easier system interface, CE# may be inactive during the data-loading or serial access as shown below. The internal 2,112 byte data registers are utilized as separate buffers for this operation and the system design gets more flexible. In addition, for voice or audio applications which use slow cycle time on the order of  $\mu$ -seconds, de-activating CE# during the data-loading and serial access would provide significant savings in power consumption.

Figure 31 Program Operation with CE# don't-care

兵党

Longsys Copyright

115

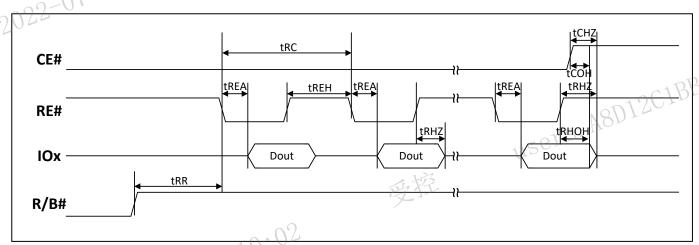

Figure 32 Read Operation with CE# don't-care

2022-07-25 10:02

30124FB5

users.

受控

2022-07-25 10:02

D12C1BB0124FB5

Everything for Memory 34/52 Longsys Copyright

### **Electrical Characteristics**

### 12.1 Absolute Maximum Ratings

Table 14 Absolute Maximum Rating

| 2.1 Absolute Maximum Ratings       |                   |                              | C1BB01 |

|------------------------------------|-------------------|------------------------------|--------|

| Table 14 Absolute M                | aximum Rating     | 219                          | CIRPO  |

| Parameters                         | Symbol            | Range                        | Unit   |

| Supply Voltage                     | Vcc               | -0.6 to +2.5                 | V      |

| Voltage Applied to Any Pin         | V <sub>IO</sub>   | -0.6 to V <sub>CC</sub> +0.4 | V      |

| Temperature under Bias             | T <sub>BIAS</sub> | -40 to +125                  | °C     |

| Storage Temperature                | T <sub>STG</sub>  | -65 to +150                  | °C     |

| Short circuit output current, I/Os | los               | 5                            | mA     |

### Note:

- (1) Minimum DC voltage is -0.6V on input/output pins. During transitions, this level may undershoot to -2.0V for periods <30ns.Maximum DC voltage on input/output pins is VCC+0.3V which, during transitions, may overshoot to VCC+2.0V for periods <20ns.

- (2) Permanent device damage may occur if ABSOLUTE MAXIMUM RATINGS are exceeded. Functional operation should be users. A8D12C1BB012A restricted to the conditions as detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### 12.2 Operating Ranges

**Table 15 Operating Ranges**

| Parameters          | Symbol | Conditions      | Min | Max  | Unit |

|---------------------|--------|-----------------|-----|------|------|

| Supply Voltage      | Vcc    |                 | 1.7 | 1.95 | V    |

| Ambient Temperature | 10:00  | Industrial      | -40 | +85  | °C   |

| Ambient Temperature | ) M    | Industrial plus | -40 | +105 | °C   |

### 12.3 Power-up Timing

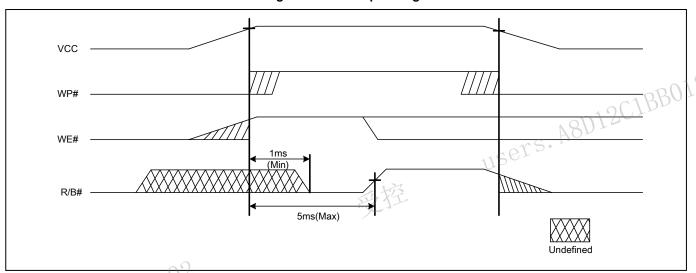

users. The device is designed to offer protection from any involuntary program/erase during power-transitions. An internal voltage detector disables all functions whenever V<sub>CC</sub> is below about 1.1V. WP# pin provides hardware protection and is recommended to be kept at V<sub>IL</sub> during power-up and power down. A recovery time of minimum 1ms is required before internal circuit gets ready for any command sequences as 2022-07-25 10:02 shown in Figure 33.

### Figure 33 Power-up Timing

### 12.4 Pin Capacitance

**Table 16 Pin Capacitance**

| Parameters                                                         | Symbol          | Min | Max  | Unit  |

|--------------------------------------------------------------------|-----------------|-----|------|-------|

| Input / Output Capacitance                                         | C <sub>IO</sub> |     | 8    | pF D1 |

| Input Capacitance                                                  | C <sub>IN</sub> |     | 8    | 2 pF  |

| Note:                                                              |                 |     | Y8n: |       |

| (1) Test conditions: TA=25°C, F=1MHz, $V_{IN}$ =0V, $V_{CC}$ =1.8V |                 | 115 | ers. |       |

| (2) These parameters are characterized only.                       |                 | OLD |      |       |

### Note:

- (1) Test conditions: TA=25°C, F=1MHz, V<sub>IN</sub>=0V, V<sub>CC</sub>=1.8V

- (2) These parameters are characterized only.

### 12.5 DC Electrical Characteristics

**Table 17 DC Electrical Characteristics**

| Donomotoro O d                     | 7-20                  | Conditions                                                                     |                      | SPEC <sup>(1)</sup> | Unit                 |    |      |

|------------------------------------|-----------------------|--------------------------------------------------------------------------------|----------------------|---------------------|----------------------|----|------|

| Parameters 22                      | <b>○</b> Symbol       | Conditions                                                                     | Min                  | Тур                 | Тур Мах              |    |      |

| Standby Current(CMOS)              | I <sub>SB</sub>       | CE# = $V_{CC}$ - 0.2V, All Input Pin = 0V/ $V_{CC}$ , IO7 - IO0 = 0V/ $V_{CC}$ |                      | 10                  | 50                   | μA | ers. |

| Page Read Current                  | I <sub>CC1</sub>      |                                                                                |                      | 10                  | 25                   | mA |      |

| Program Current                    | I <sub>CC2</sub>      |                                                                                |                      | 15,                 | 25                   | mA |      |

| Erase Current                      | I <sub>CC3</sub>      |                                                                                |                      | 15                  | 25                   | mA |      |

| Input Leakage Current              | ILI                   | $V_{IN} = 0$ to $V_{CC}(max)$                                                  |                      |                     | ±10                  | μA |      |

| Output Leakage Current             | I <sub>LO</sub>       | V <sub>OUT</sub> = 0 to V <sub>CC</sub> (max)                                  |                      |                     | ±10                  | μA |      |

| Output Low Current (R/B#)          | I <sub>OL(R/B#)</sub> | V <sub>OL</sub> = 0.2V                                                         | 3                    | 4                   |                      | mA |      |

| Input Low Voltage                  | V <sub>IL</sub>       | 7.5                                                                            | -0.3                 |                     | 0.2V <sub>CC</sub>   | V  |      |

| Input High Voltage V <sub>IH</sub> |                       | -0.1                                                                           | 0.8V <sub>CC</sub>   |                     | V <sub>CC</sub> +0.3 | V  |      |

| Output Low Voltage                 |                       | I <sub>OL</sub> = 100μA                                                        |                      |                     | 0.2                  | V  |      |

| Output High Voltage                | V <sub>OH</sub>       | Ι <sub>ΟΗ</sub> = -100μΑ                                                       | V <sub>CC</sub> -0.2 |                     |                      | V  |      |

Note:

<sup>(1)</sup> Applicable over recommended operating range from: T<sub>A</sub> = -40°C to +85°C, VCC= 1.7V to 1.95V, unless otherwise noted.

### 12.6 AC Measurement Conditions

**Table 18 AC Measurement Conditions**

| Table 18 AC Measuren             | nent Condition  | ns                   |       | 01   |

|----------------------------------|-----------------|----------------------|-------|------|

| Parameters                       | Symbol          | Min                  | Max   | Unit |

| Load Capacitance                 | C <sub>L</sub>  |                      | 30    | pF   |

| Input Rise Time                  | t <sub>R</sub>  | - 01                 | S . 5 | ns   |

| Input Fall Time                  | t <sub>F</sub>  | use                  | 5     | ns   |

| Input Pulse Voltages             | V <sub>IN</sub> | 0 to V <sub>CC</sub> |       | V    |

| Input Timing Reference Voltages  | 之1N             | 0.5V <sub>CC</sub>   |       | V    |

| Output Timing Reference Voltages | OUT             | 0.5V <sub>CC</sub>   |       | V    |

# 12.7 AC Electrical Characteristics

Table 19 AC Electrical Characteristics for Command, Address and Data Input

| 10000 10710 = 10000 0100 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 0100000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 0100000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 0100000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 0100000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 0100000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 0100000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000 01000000 |                                 |     |       |       |      |