## High-Efficiency Boost/SEPIC DC/DC Controller

### **General Description**

The VP3481 is a versatile controller designed for use in Boost, SEPIC and power converter and topologies that needs an external low-side N-MOSFET acting as primary switch. Besides cycleby-cycle current limiting, current mode control scheme also makes it wide bandwidth and good transient response. The current limit can be programmed simply with an external resistor.

The switching frequency can be set in any value between 100kHz and 1MHz with a resistor or any external clock source. The VP3481 can be operated at high switching frequency to save the solution board size. While entering shutdown mode, the VP3481 only sinks 5µA and it allows power supply sequencing. It has built-in protection circuits such as thermal shutdown, under-voltage lockout, short circuit protection, and overvoltage protection. Internal soft-start circuitry reduces the **Applications** inrush current at start-up.

VP3481 is available in small MSOP-10 and DFN3X3-10 green package.

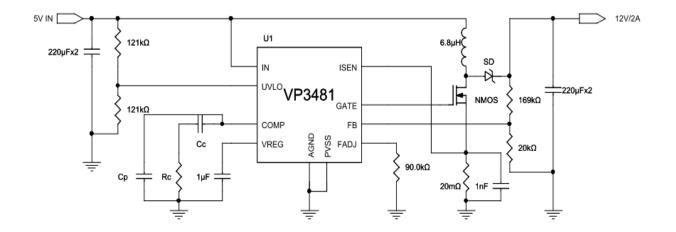

## Typical Application

#### **Features**

- VP3481MSG10-A in MSOP10 package is AEC-Q100 Qualified and Manufactured on an Automotive Grade Flow

- Wide Input Voltage from 2.97V to 40V

- Reference Voltage with ±3.0% Accuracy

- Adjustable 100kHz~1MHz Clock Frequency

- 10µA Shutdown Current

- 1A Peak Current Limit Using Internal Driver

- Current Mode Operation

- Internal 4/2Ω MOSFET Switch

- External RC Compensation

- Internal Soft-Start

- High Efficiency at Light Loads

- Current Limit and Over Temperature Protection

- Adjustable Input UVLO Threshold Voltage

- MSOP-10 and TDFN3x3 Green Package with

- Portable Speakers

- Offline Power Supply

- **Battery Powered Device**

- Set-Top Box

- Photovoltaic Inverters

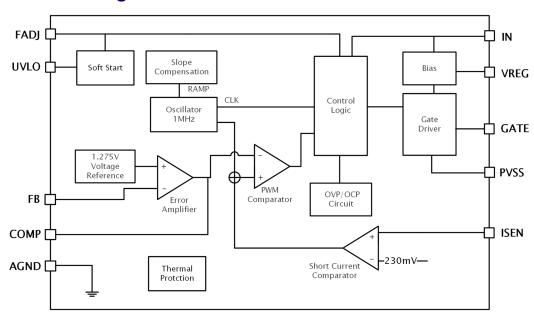

## **Functional Block Diagram**

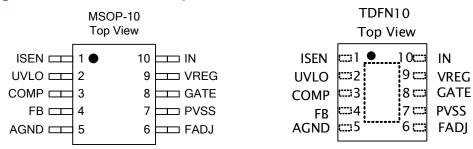

## **Pin Assignments And Descriptions**

| Pin No. | Pin  | I/O/P | Function Description                                                                                                                                                                                                                                                                                                                                       |

|---------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | ISEN | Р     | Current Sense. Use an external resistor in series with ground to measure the voltage drop.                                                                                                                                                                                                                                                                 |

| 2       | UVLO | I     | Under Voltage Lockout. Use a proper ratio resistor divider network to determine the voltage input to allow switching and the hysteresis to disable switching.                                                                                                                                                                                              |

| 3       | COMP | I     | Compensation. Use a RC/C network to do proper loop compensation.                                                                                                                                                                                                                                                                                           |

| 4       | FB   | 1     | Output Feedback. Connect the external resistor divider network from output to this pin to sense output voltage. The FB pin voltage is regulated to internal 1.275V reference voltage.                                                                                                                                                                      |

| 5       | AGND | Р     | Analog Ground. Connect to exposed pad.                                                                                                                                                                                                                                                                                                                     |

| 6       | FADJ | ı     | Frequency Adjust/Synchronization/Shutdown. A resistor connected from this pin to ground simply sets the oscillator frequency. An external clock signal at this pin will synchronize the controller to the clock. Pull on this pin for $\geq$ 30 $\mu$ s will turn the device off and the device will then very few current about $5\mu$ A from the supply. |

| 7       | PVSS | I     | Power Ground. Connect to exposed pad.                                                                                                                                                                                                                                                                                                                      |

| 8       | GATE | 0     | Gate Drive. Connect this terminal to the gate pin of the external MOSFET.                                                                                                                                                                                                                                                                                  |

| 9       | VREG | 0     | Drive Supply Voltage. A bypass capacitor must be connected from this pin to ground. Do not bias this pin with external power source.                                                                                                                                                                                                                       |

| 10      | IN   | I     | Power Supply Input.                                                                                                                                                                                                                                                                                                                                        |

## **Absolutely Maximum Ratings**

Over operating free-air temperature range, unless otherwise specified (\* 1)

| Symbol                                     | Parameter                                 | Limit      | Unit |

|--------------------------------------------|-------------------------------------------|------------|------|

| V <sub>IN</sub>                            | Supply voltage range                      | -0.3 to 42 | V    |

| V <sub>LV</sub> (COMP/UVLO/FB/             | Low voltage range                         | -0.3 to 6  | V    |

| FADJ/GATE)                                 | Low voltage range                         | -0.3 to 0  | , v  |

| V <sub>CC</sub> (VREG)                     | Regulator output pin range                | -0.3 to 5  | V    |

| V <sub>ISEN</sub>                          | V <sub>ISEN</sub> Current sense pin range |            | V    |

| T <sub>JMAX</sub>                          | junction temperature MAX                  | 150        | ۰C   |

| T <sub>STG</sub> Storage temperature range |                                           | -65 to 150 | ۰C   |

| Electrostatic discharge                    | lectrostatic discharge Human body model   |            | kV   |

| Electrostatic discharge Machine model      |                                           | 200        | V    |

<sup>(\*1):</sup> Stress beyond those listed at "absolute maximum rating" table may cause permanent damage to the device. These are stress rating ONLY. For functional operation are strongly recommend follow up "recommended operation conditions" table.

## **Recommended Operating Conditions**

| Symbol           | Parameter                 | Specifi | Unit |       |

|------------------|---------------------------|---------|------|-------|

| Symbol           | raiametei                 | Min     | Max  | Oilit |

| V <sub>IN</sub>  | Supply voltage            | 2.97    | 40   | V     |

| f <sub>osc</sub> | Switching Frequency range | 0.1     | 1    | MHz   |

| Тյ               | Operating Junction range  | -40     | 125  | ۰C    |

### **Thermal Information**

|                       | Thermal Metric Parameter                    | VP3481MSG10 | LM3481DNG10 | Unit    |  |

|-----------------------|---------------------------------------------|-------------|-------------|---------|--|

|                       | mema metric rarameter                       | MSOP        | TDFN        |         |  |

| $\theta_{JC(top)}$    | Thermal resistance (Junction to Case (top)) | 46          | 54          | °C/W    |  |

| $\theta_{JA}$         | Thermal resistance (Junction to Air)        | 147         | 49          | °C/W    |  |

| $\theta_{	extsf{JB}}$ | Thermal resistance (Junction to Board)      | 81          | 21          | °C/W    |  |

| Ψյт                   | Junction-to-top characterization parameter  | 3           | 2           | °C/W    |  |

| Ψјв                   | Junction-to-board characterization parame-  | 77          | 21          | °C/W    |  |

| $\Psi_{jR}$           | ter                                         | , ,         | ۷ ا         | - C/ VV |  |

### **Electrical Characteristics**

$V_{\text{IN}}{=}\,12\text{V},\,R_{\text{FADJ}}{=}\,150\text{k}\Omega,\,T_{\text{J}}{=}\,25^{\circ}\!\text{C},\,\text{unless otherwise specified}$  (\* 1)

| Symbol                   | Parameter                                 | Test Condition                                         |                                                                         | Specification |          |       | Unit        |

|--------------------------|-------------------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------|---------------|----------|-------|-------------|

| Syllibol                 | Parameter                                 |                                                        | rest Condition                                                          |               | Тур      | Max   | Offic       |

|                          |                                           | $V_{COMP} =$                                           | =1.4V, 3V <v<sub>IN&lt;40V</v<sub>                                      |               | 1.275    |       | V           |

| $V_{FB}$                 | Feedback voltage                          |                                                        | $V_{COMP}=1.4V, 3V < V_{IN} < 40V, -40^{\circ}C < T_{J} < 125^{\circ}C$ |               |          | 1.313 | ٧           |

|                          |                                           |                                                        | $V_{IN} = 12V$                                                          |               | 10       |       |             |

| $I_Q$                    | Quiescent current in shutdown             | $V_{FADJ}=3V$                                          | V <sub>IN</sub> =12V,<br>-40°C <t<sub>J&lt;125°C</t<sub>                |               |          | 15    |             |

| IQ                       | mode                                      | V FADJ — J V                                           | V <sub>IN</sub> =5V                                                     |               | 5        |       | μA          |

|                          |                                           |                                                        | $V_{IN}=5V$ ,<br>-40°C< $T_J$ <125°C                                    |               |          | 10    |             |

| $V_{\text{UVLO}}$        | Under voltage lockout                     | Vu                                                     | <sub>JVLO</sub> Ramp down                                               | 1.345         |          | 1.517 | V           |

| I <sub>UVLO</sub>        | UVLO source current                       |                                                        | Enabled                                                                 |               | 4.5      |       | μΑ          |

| $V_{\text{UVLOSD}}$      | UVLO Shutdown voltage                     |                                                        |                                                                         | 0.55          | 0.7      | 0.82  | ٧           |

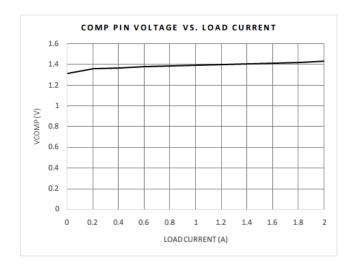

| $V_{COMP}$               | COMP pin voltage                          |                                                        | V <sub>FB</sub> =1.275V                                                 |               | 1        |       | V           |

| D                        | High-side switch R <sub>DS(ON)</sub> (*1) | V <sub>IN</sub> =5V, I <sub>GATE</sub> =0.2A           |                                                                         |               | 4        |       | Ω           |

| $R_{DS(ON)}$             | Low-side switch R <sub>DS(ON)</sub> (*1)  | V <sub>IN</sub>                                        | V <sub>IN</sub> =5V, I <sub>GATE</sub> =0.2A                            |               | 2        |       | 22          |

| A <sub>VOL</sub>         | Error amplifier voltage gain              | V <sub>COMP</sub>                                      | $V_{COMP}=1.4V$ , $I_{EAO}=100\mu A$                                    |               | 60       |       | V/V         |

| <b>9</b> м               | Error amplifier trans-<br>conductance     | V <sub>COMP</sub> =1.4V                                |                                                                         |               | 430      |       | μ℧          |

| $V_{GATE}$               | Maximum GATE driving swing                | $V_{IN} < 5.8V$                                        |                                                                         |               | $V_{IN}$ |       | V           |

| <b>V</b> GATE            | Maximum GATE unving swing                 | V <sub>IN</sub> ≥5.8V                                  |                                                                         |               | 5.2      |       |             |

| $f_{OSC}$                | Oscillation frequency                     | $R_{FADJ} = 150 k\Omega$                               |                                                                         |               | 0.146    |       | MHz         |

| TOSC                     | Osemation requeitey                       | $R_{FADJ}=150$                                         | 0kΩ , −40℃ <t<sub>J&lt;125℃</t<sub>                                     | 0.125         |          | 0.2   | 141112      |

| $D_{MAX}$                | Maximum duty cycle                        |                                                        | $R_{FADJ} = 150k\Omega$                                                 |               | 85       |       | %           |

| $\Delta V_{\text{LINE}}$ | Voltage line regulation                   |                                                        | $3V < V_{IN} < 40V$                                                     |               | 0.02     |       | %/V         |

| $\Delta V_{\text{LOAD}}$ | Voltage load regulation                   | I <sub>EAO</sub> Source/Sink                           |                                                                         |               | ±0.5     |       | %/ <b>A</b> |

| t <sub>MIN(ON)</sub>     | Minimum on-time                           | _                                                      |                                                                         |               |          | 571   | nS          |

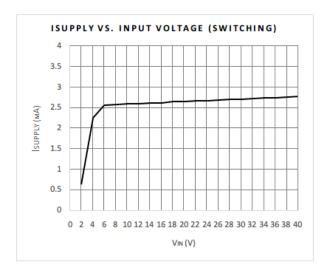

| I <sub>SUPPLY</sub>      | Supply Current                            | $R_{FADJ} = 150k\Omega$                                |                                                                         |               | 3.3      |       | mA<br>mV    |

| -301121                  |                                           | $R_{FADJ}=150$                                         | $R_{FADJ} = 150 k\Omega$ , $-40^{\circ}C < T_{J} < 125^{\circ}C$        |               |          | 5     |             |

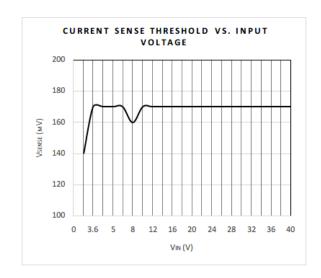

| $V_{SENSE}$              | Current sense threshold volt-             | V <sub>IN</sub> =12V                                   |                                                                         |               | 160      | 265   |             |

| -                        | age                                       | $V_{IN} = 12V$ , $-40^{\circ}C < T_{J} < 125^{\circ}C$ |                                                                         | 120           | 266      | 200   |             |

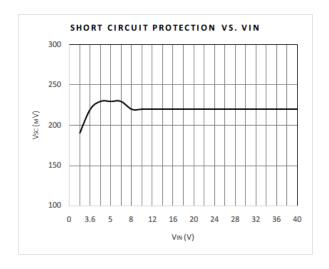

| $V_{SC}$                 | Overload current limit sense              |                                                        |                                                                         | 200           | 250      | mV    |             |

| \ <u>'</u>               | voltage                                   | V <sub>IN</sub> = 1 2                                  | V , -40℃ <t<sub>J&lt;125℃</t<sub>                                       | 160           | 00       | 350   | na\/        |

| $V_{SL}$                 | Internal compensation ramp                |                                                        |                                                                         |               | 90       |       | mV          |

## **Electrical Characteristics (cont.)**

$V_{IN}{=}\,1\,2V,\,R_{FADJ}{=}\,1\,50k\Omega,\,T_{J}{=}\,25^{\circ}\!C,\,unless$  otherwise specified (\* 1)

| Symbol                | Parameter                                | Test Condition                                                                     | Specification |      |      | Unit       |  |

|-----------------------|------------------------------------------|------------------------------------------------------------------------------------|---------------|------|------|------------|--|

| Syllibol              | raidilletei                              | rest Condition                                                                     | Min           | Тур  | Max  | Onic       |  |

| $V_{\text{OVP}}$      | Output overvoltage protection            | $V_{COMP}=1.4V$                                                                    | 26            | 85   | 135  | mV         |  |

| V <sub>OVP(HYS)</sub> | Output overvoltage protection hysteresis | V <sub>COMP</sub> =1.4V                                                            | 28            | 70   | 106  | mV         |  |

|                       |                                          | Source, $V_{COMP} = 1.4V$ , $V_{FB} = 0V$                                          |               | 650  |      |            |  |

| I <sub>EAO</sub>      | Error amplifier output current           | Source, $V_{COMP} = 1.4V$ , $V_{FB} = 0V$<br>$-40^{\circ}C < T_J < 125^{\circ}C$   | 470           |      | 950  |            |  |

| IEAO                  | (Source/Sink)                            | $Sink,V_{COMP}=1.4V,V_{FB}=1.4V$                                                   |               | 57   |      | μA         |  |

|                       |                                          | Sink, $V_{COMP} = 1.4V$ , $V_{FB} = 1.4V$<br>$-40^{\circ}C < T_{J} < 125^{\circ}C$ | 30            |      | 105  |            |  |

|                       |                                          | Upper Limit: V <sub>FB</sub> =0V, COMP pin floating                                |               | 2.65 |      |            |  |

| V <sub>EAO</sub>      | Error amplifier output voltage           | Upper Limit: $V_{FB}$ =0V, COMP pin floating -40°C <t<sub>J&lt;125°C</t<sub>       | 2.4           |      | 2.95 |            |  |

|                       |                                          | Lower Limit: V <sub>FB</sub> =1.4V                                                 |               | 0.65 |      |            |  |

|                       |                                          | Lower Limit: V <sub>FB</sub> =1.4V<br>−40°C <t<sub>J&lt;125°C</t<sub>              | 0.32          |      | 0.9  |            |  |

|                       |                                          | Output=High Level (SD)                                                             |               | 1.26 |      |            |  |

| $V_{SD}$              | Shutdown signal threshold on             | Output=High Level (SD), $-40^{\circ}\text{C} < \text{T}_{J} < 125^{\circ}\text{C}$ |               |      | 1.4  | V          |  |

| <b>▼</b> 2D           | FADJ pin (*2)                            | Output=Low Level (EN)                                                              |               | 0.63 |      | V          |  |

|                       |                                          | Output=Low Level (EN),<br>−40°C <t<sub>J&lt;125°C</t<sub>                          |               |      | 0.4  |            |  |

| t <sub>SS</sub>       | Soft start delay                         | $V_{FB} = 1.2V$ , COMP pin floating                                                | 8.7           | 15   | 21.3 | mS         |  |

| t <sub>R</sub>        | GATE pin rising time                     | $Cgs = 3000pF$ , $V_{GATE} = 0V$ to $3V$                                           |               | 18   |      | nS         |  |

| t <sub>F</sub>        | GATE pin falling time                    | $Cgs = 3000pF, V_{GATE} = 3V to 0V$                                                |               | 12   |      | nS         |  |

| I <sub>SD</sub>       | Shutdown pin current FADJ pin            | $V_{SD} = 0V$                                                                      |               | 10   |      | μΑ         |  |

| T <sub>SD</sub>       | Thermal shutdown                         |                                                                                    |               | 175  |      | °C         |  |

| $T_{SD(HYS)}$         | Thermal shutdown hysteresis              |                                                                                    |               | 10   |      | $^{\circ}$ |  |

<sup>(\*1):</sup> Stress beyond those listed at "absolute maximum rating" table may cause permanent damage to the device. These are stress rating ONLY. For functional operation are strongly recommend follow up "recommended operation conditions" table.

<sup>(\*2)</sup> The FADJ pin should be pulled to VIN through a resistor to turn the regulator off. The voltage on the FADJ pin must be above the maximum limit for Output = High Level to keep the regulator off and must be below the limit for Output = Low Level to keep the regulator on.

### **Functional Descriptions**

The VP3481 employs the current-mode, adjustable frequency pulse-width modulation (PWM) architecture. It operates at adjustable switching frequency under medium to high load current conditions.

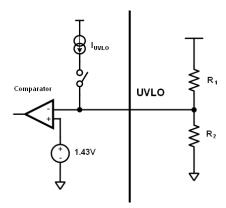

#### Overvoltage and UVLO Protection

The VP3481 uses FB pin to detect overvoltage occurrence. The overvoltage protection should be triggered at the voltage rises to  $V_{FB}+V_{OVP}$ . When OVP occurs only the MOSFET will be turned off, the output voltage will drop. VP3481 will switch when the voltage on FB pin is less then  $(V_{OVP}+V_{FB}-V_{OVP(HYS)})$ .

The VP3481 provides UVLO pin to program enable and disable thresholds. The voltage on UVLO pin would be compared with internal reference 1.43V. Figure 1 shows how the UVLO detection works.

Figure 1. UVLO Pin Configuration

The R1/R2 network programs the enable threshold voltage  $V_{EN}$ . When the VP3481 is enabled the  $I_{UVLO}$  will source 4.5 $\mu$ A current flows the  $R_2$  which causes a hysteresis. Hence the disable threshold,  $V_{SH}$ , is lower then the enable threshold  $V_{EN}$ .

$$R_{2} = \frac{1.43V}{I_{UVLO}} \times \left(1 + \frac{1.43V - V_{SH}}{V_{EN} - 1.43V}\right)$$

$$R_{1} = R_{2} \times \left(\frac{V_{EN}}{1.43V} - 1\right)$$

Select appropriate value of  $V_{EN}$ ,  $V_{SH}$  and use above two equations to determine the value of  $R_1$  and  $R_2$ .

#### Bias Voltage

VP3481 generates the internal bias voltage from IN input voltage if it does not exceeds 6V. When VIN is higher then 6V the VP3481 will use internal regulation to bias the chip. To improve the stability of the bias, an external capacitor of  $0.47\mu F\sim4.7\mu F$  is strongly recommended to add on VREG terminal.

In any case, do not add external voltage on VREG pin or the chip would be damaged.

#### Frequency Adjust

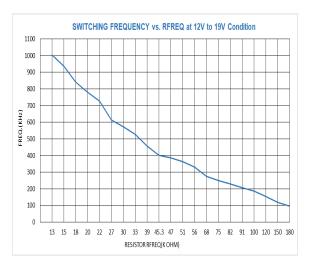

The switching frequency can be adjusted from 100kHz to 1MHz by a external resistor in series with FADJ terminal and ground. The following equation is used to calculate resistor value.

a. When Fs < 300KHz the calculate as below,

$$R_{FADJ} \cong \frac{17 \times 10^3}{f_s} + 8.7$$

b. When Fs > 300KHz the calculate as below,

$$R_{FADJ} \cong \frac{21 \times 10^3}{f_s} - 7.2$$

Where  $f_S$  is in kHz and  $R_{FADJ}$  is in k $\Omega$ .

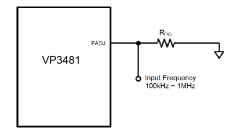

#### **Clock Synchronization**

VP3481 is able to be synchronized to an external clock by connecting to the FADJ terminal with  $R_{\text{FADJ}}$  in series with ground as shown in figure 2.

Figure 2. Clock Synchronization

### **Functional Descriptions (cont.)**

#### Shutdown

The FADJ pin can be used as a shutdown pin. If the high signal pulls up this pin, VP3481 will stop the switching and then enter the shutdown state. In this state, VP3481 consumes only 5µA typically.

The use of shutdown control in frequency adjustment mode is quite simple. Connects the FADJ pin to ground will force the VP3481 runs at specified frequency and pulls this pin high will shutdown the IC. In both frequency and synchronization mode, pulls FADJ pin high lasting then 30us will also force the VP3481 enter the shutdown state.

**Slope Compensation**

VP3481 employs current mode control scheme. It has many advantages such as cycle-by-cycle current limit for the switch and easier to parallel power stages because automatic current sharing. The compensation ramp is already added in VP3481 and the slope of the default compensation ramp could satisfy most applications.

#### Overvoltage Protection

The VP3481 has overvoltage protection for the output. OVP occurrence is detected by sensing feedback (FB) pin. When the voltage at FB pin is over  $V_{FB}+V_{OVP}$ , overvoltage protection is triggered and the drive pin and the GATE pin will be tied-low.

Once the voltage at FB pin is lower then  $V_{FB}+(V_{OVP}-V_{OVP(HYS)})$ , the VP3481 will begin to switch again. Be aware that the error amplifier is still in operation during OVP event.

#### **Short Circuit Protection**

The ISEN pin is used to sense the over-current

occurrence. If the difference between ISEN pin and ground is greater then 230mV, the current limit will be activated. The comparator will decrease the switching frequency by the factor of 8 and maintains this condition until the over-current (short) event is removed.

### **Application Information**

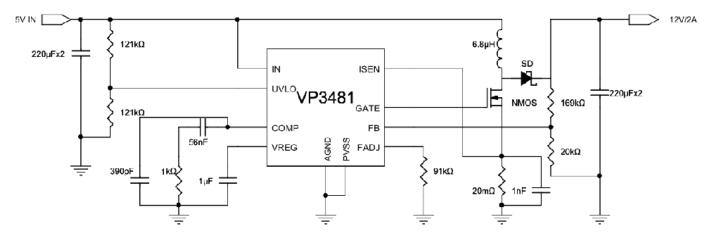

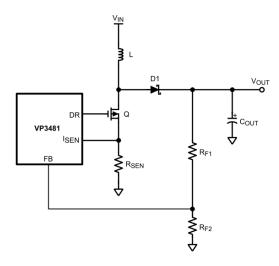

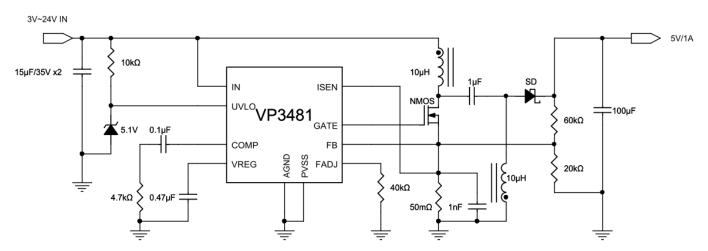

Figure 3 VP3481 Typical Boost Application

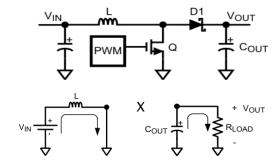

The most common topology for the VP3481 is the boost or step-up topology. The boost converter converts a low input voltage into a higher output voltage. The basic configuration for a boost regulator is shown in Figure 4. In continuous conduction mode (when the inductor current never reaches zero at steady state), the boost regulator operates in two cycles. In the first cycle of operation, MOSFET Q is turned on and energy is stored in the inductor. During this cycle, diode D1 is reverse biased and load current is supplied by the output capacitor, Cout. In the second cycle, MOSFET Q is off and the diode is forward biased. The energy stored in the inductor is transferred to the load and output capacitor. The ratio of these two cycles determines the output voltage. The output voltage is defined as:

$$V_{OUT} = \frac{V_{IN}}{1 - D}$$

(ignoring the voltage drop across the MOSFET and the diode), or

$$V_{OUT} + V_{D1} - V_{Q} = \frac{V_{IN} - V_{Q}}{1 - D}$$

where D is the duty cycle of the switch, VD1 is the forward voltage drop of the diode, and VQ is the drop across the MOSFET when it is on. The following sections describe selection of components for a boost converter.

A. First Cycle of Operation

B. Second Cycle of Operation

Figure 4. Simplified Boost Converter Diagram

#### **Power Inductor Selection**

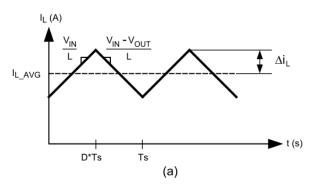

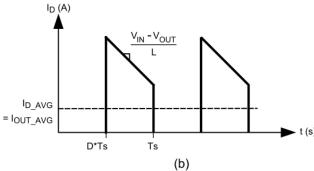

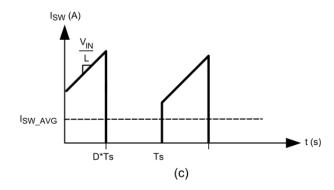

The inductor is one of the two energy storage elements in a boost converter. Figure 5 shows how the inductor current varies during a switching cycle. The current through an inductor is quantified as:

$$V_L(t) = L \frac{di_L(t)}{dt}$$

Figure 5. (a) Inductor Current (b) Diode Current (c) Switch Current

If VL(t) is constant, diL(t)/dt must be constant. Hence, for a given input voltage and output voltage, the current in the inductor changes at a constant rate.

The important quantities in determining a proper inductance value are IL (the average inductor current) and  $\Delta$ iL (the inductor current ripple difference between the peak inductor current and the average inductor current). If  $\Delta$ iL is larger than IL , the inductor current drops to zero for a portion of the

cycle and the converter operates in discontinuous conduction mode. If  $\Delta iL$  is smaller than IL, the inductor current stays above zero and the converter operates in continuous conduction mode. All the analysis in this data sheet assumes operation in continuous conduction mode. To operate in continuous conduction mode, the following conditions must be met:

(1)

$$I_L > \Delta i_L$$

(2)

$$\frac{I_{OUT}}{1-D} > \frac{DV_{IN}}{2f_SL}$$

(3)

$$L > \frac{D(1-D)V_{IN}}{2I_{OUT}f_S}$$

Choose the minimum lout to determine the minimum L. A common choice is to set (2 x  $\Delta i_L$ ) to 30% of  $I_L$ . Choosing an appropriate core size for the inductor involves calculating the average and peak currents expected through the inductor. In a boost converter,

$$(4) \quad I_L = \frac{I_{OUT}}{1 - D}$$

(5)

$$I_{L_{-}PEAK} = I_{L}(\max) + \Delta i_{L}(\max)$$

(6)

$$\Delta i L = \frac{DV_{IN}}{2 \times L \times fs}$$

A core size with ratings higher than these values should be chosen. If the core is not properly rated, saturation will dramatically reduce overall efficiency.

The VP3481 can be set to switch at very high frequencies. When the switching frequency is high, the converter can operate with very small inductor values. With a small inductor value, the peak inductor current can be extremely higher than the output currents, especially under light load conditions.

The VP3481 senses the peak current through the Evaluate RSEN at the maximum and minimum VIN switch. The peak current through the switch is the values and choose the smallest RSEN calculated. same as the peak current calculated above.

### Programming the Output Voltage and Output Current

The output voltage can be programmed using a resistor divider between the output and the feedback pins, as shown in Figure 6. The resistors are selected such that the voltage at the feedback pin is 1.275V. RF1 and RF2 can be selected using the equation,

$$Vout = 1.275(1 + \frac{R_{F1}}{R_{F2}})$$

A 100pF capacitor may be connected between the feedback and ground pins to reduce noise.

The maximum amount of current that can be delivered at the output can be controlled by the sense resistor, RSEN. Current limit occurs when the voltage that is generated across the sense resistor equals the current sense threshold voltage, Vsense. Limits for VSENSE have been specified in the Electrical Characteristics section. This can be expressed as:

$$\boldsymbol{I}_{\mathit{SW(pexk)}} \times \boldsymbol{R}_{\mathit{SEN}} = \boldsymbol{V}_{\mathit{SENSE}} - \boldsymbol{D} \times \boldsymbol{V}_{\mathit{SL}}$$

The peak current through the switch is equal to the peak inductor current.

$$I_{SW(pexk)} = I_L(\max) + \Delta i_L$$

Therefore for a boost converter,

$$I_{SW(pexk)} = \frac{I_{OUT(max)}}{(1-D)} + \frac{(D \times V_{IN})}{(2 \times f_s \times L)}$$

Combining the two equations yields an expression for RSEN,

$$R_{SEN} = \frac{V_{SENSE} - (D \times V_{SL})}{\left[\frac{I_{OUT(\text{max})}}{(1-D)} + \frac{(D \times V_{IN})}{(2 \times f_S \times L)}\right]}$$

Figure 6. Adjusting the Output Voltage

#### **Power Diode Selection**

Observation of the boost converter circuit shows that the average current through the diode is the average load current, and the peak current through the diode is the peak current through the inductor. The diode should be rated to handle more than the inductor peak current. The peak diode current can be calculated using the formula:

$$I_{D(Peak)} = [I_{OUT}/(1-D)] + \Delta i_L$$

lout is the output current and  $\Delta i L$  has been defined in Figure 5. The peak reverse voltage for a boost converter is equal to the regulator output voltage. The diode must be capable of handling this peak reverse voltage. To improve efficiency, a low forward drop Schottky diode is recommended.

#### **Power MOSFET Selection**

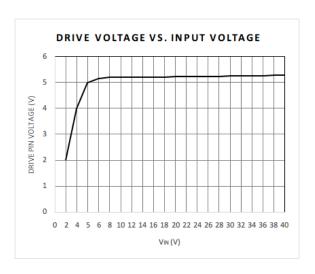

The drive pin, DR, of the VP3481 must be connected to the gate of an external MOSFET. In a boost topology, the drain of the external N-Channel MOSFET is connected to the inductor and the source is connected to the ground. The drive pin voltage, VDR, depends on the input voltage. In most applications, a logic level MOSFET can be used. For very low input voltages, a sub-logic level MOSFET should be used.

The selected MOSFET directly controls the efficiency. The critical parameters for selection of a MOSFET are:

- Minimum threshold voltage, VTH(MIN)

- On-resistance, RDS(ON)

- · Total gate charge, Qg

- · Reverse transfer capacitance, CRSS

- Maximum drain to source voltage, VDS(MAX)

The off-state voltage of the MOSFET is approximately equal to the output voltage. VDS(MAX) of the MOSFET must be greater than the output voltage. The power losses in the MOSFET can be catego-

rized into conduction losses and ac switching or transition losses.  $R_{DS(ON)}$  is needed to estimate the conduction losses. The conduction loss,  $P_{COND}$ , is the  $I^2R$  loss across the MOSFET. The maximum conduction loss is given by:

$$P_{COND(MAX)} = \left(\frac{I_{OUT(\max)}}{1 - D_{MAX}}\right)^2 \times D_{MAX} \times R_{DS(ON)}$$

where DMAX is the maximum duty cycle.

$$D_{\mathit{MAX}} = \left(1 - \frac{V_{\mathit{IN}(\mathit{MIN})}}{V_{\mathit{OUT}}}\right)$$

At high switching frequencies the switching losses may be the largest portion of the total losses.

The switching losses are very difficult to calculate due to changing parasitics of a given MOSFET in operation. Often, the individual MOSFET datasheet does not give enough information to yield a useful result. As below equation give a rough idea how the switching losses are calculated:

$$P_{SW} = \frac{I_{L \max} \times V_{out}}{2} \times f_{SW} \times (t_{LH} + t_{HL})$$

$$t_{LH} = \left(Qgd + \frac{Qgs}{2}\right) \times \frac{R_{Gate}}{V_{DR} - Vgs_{th}}$$

#### **Input Capacitor Selection**

Due to the presence of an inductor at the input of a boost converter, the input current waveform is continuous and triangular, as shown in Figure 5. The inductor ensures that the input capacitor sees fairly low ripple currents. However, as the input capacitor gets smaller, the input ripple goes up. The rms current in the input capacitor is given by:

$$I_{CIN(RMS)} = \Delta i_L / \sqrt{3} = \left( \frac{(V_{OUT} - V_{IN}) \times V_{IN}}{\sqrt{12} \times V_{OUT} \times L \times f_S} \right)$$

The input capacitor should be capable of handling the rms current. Although the input capacitor is not as critical in a boost application, low values

can cause impedance interactions. Therefore a good quality capacitor should be chosen in the range of  $100 \, \text{uF}$  to  $200 \, \text{uF}$ . If a value lower than  $100 \, \text{uF}$  is used, then problems with impedance interactions or switching noise can affect the VP3481. To improve performance, especially with Vin below 8 V, it is recommended to use a  $20 \, \Omega$  resistor at the input to provide a RC filter. This resistor is placed in series with the Vin pin with only a bypass capacitor attached to the Vin pin directly (see Figure 7). A  $0.1 \, \text{uF}$  or  $1 \, \text{uF}$  ceramic capacitor is necessary in this configuration. The bulk input capacitor and inductor will connect on the other side of the resistor with the input power supply.

Figure 7 Reducing IC Input Noise

#### **Output Capacitor Selection**

The output capacitor in a boost converter provides all the output current when the inductor is charging. As a result it sees very large ripple currents. The output capacitor should be capable of handling the maximum rms current. The rms current in the output capacitor is:

$$I_{CIN(RMS)} = \sqrt{(1-D)\left[I_{OUT^2} \frac{D}{(1-D)^2} + \frac{\Delta i_L^2}{3}\right]}$$

Where

$$\Delta i_L = \frac{DV_{IN}}{2 \times L \times f_s}$$

and D, the duty cycle is equal to (Vout  $-\ VIN\ )/VOUT.$

The ESR and ESL of the output capacitor directly control the output ripple. Use capacitors with low ESR and ESL at the output for high efficiency and low ripple voltage. Surface mount tantalums, surface mount polymer electrolytic and polymer tantalum, Sanyo- OSCON, or multi-layer ceramic capacitors are recommended at the output.

#### **Driver Supply Capacitor Selection**

A good quality ceramic bypass capacitor must be connected from the Vcc pin to the PGND pin for proper operation. This capacitor supplies the transient current required by the internal MOSFET driver, as well as filtering the internal supply voltage for the controller. A value of between 0.47uF and 4.7uF is recommended.

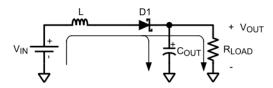

Figure 8 VP3481 Typical SEPIC Application

VP3481 can also be used in SEPIC application because of it controls low-side of NMOSFET. Figure 8 shows the VP3481 typical SEPIC application. This configuration allows the input voltage higher or lower then output voltage. For both stepping-up and stepping-down configuration, two inductors are needed. The two inductors can be individual inductor or two windings of a coupled transformer. For reducing input ripple it is better to use the coupled windings of transformers for both inductors.

The advantage of SEPIC structure over a boost converter is input and output isolation. The input and the output of pure boost converter is always connected through an inductor unless external switch is added. For SEPIC structure, a capacitor isolates the input from the output and provides protection against shorted or malfunctioning load. Hence, the SEPIC is useful for replacing boost circuits when true shutdown is required. This means that the output voltage falls to 0V when the switch is turned off. In pure boost converter, the output can only fall to the input voltage minus a diode drop and never turn off the output.

To properly pick up the components for the application, the following parameters need to be exam-

ined: Input voltage range, output voltage, output current range and the switching frequency. These four main parameters will affect the operating characteristic of the application.

#### **MOSFET Selection**

Four parameters will dominate the selection of the MOSFET: minimum threshold voltage  $V_{TH(MIN)}$ , the On–resistance  $R_{DS(ON)}$ , the total gate charge Qg, the reverse transfer capacitance Css and the maximum drain to source voltage  $V_{DS(MAX)}$ .

The peak switch voltage in SEPIC application is:

$$V_{SW(PEAK)} = V_{IN} + V_{OUT} + V_{DIODE}$$

Hence the VDS(MAX) of MOSFET shell be:

$$V_{DS(MAX)} > V_{SW(PEAK)}$$

The peak switch current is determined by:

$$I_{SW(PEAK)} = I_{L1(AVG)} + I_{OUT} + \frac{\Delta I_{L1} + \Delta I_{L2}}{2}$$

Where  $\Delta I_{L1}$  and  $\Delta I_{L2}$  are the peak-to-peak ripple currents of the inductors respectively.

The RMS current through the switch is given by:

$$I_{SW(RMS)} = \sqrt{\left[I_{SW(PEAK)}^2 - I_{SW(PEAK)}(\Delta I_{L1} + \Delta I_{L2}) + \frac{(\Delta I_{L1} + \Delta I_{L2})^2}{3}\right]^D}$$

#### **Power Diode Selection**

The diode must be selected to handle the peak current and the peak reverse voltage. In SEPIC application, the diode peak current is the same as the switch peak current. The off-state voltage or peak reverse voltage of the diode is  $V_{\text{IN}}+V_{\text{OUT}}$ . Similar to the boost converter, the average diode current is equal to the output current. In order to improve the efficiency, schottky diodes are recommended.

### **Inductor Selection**

The inductors shall be chosen carefully to satisfy constant current mode requires calculations of the following parameters:

Inductor average current:

$$I_{L1(AVG)} = \frac{D \times I_{OUT}}{1 - D}$$

$$I_{L2(AVG)} = I_{OUT}$$

Peak-to-peak ripple current:

$$\Delta I_{L1} = \frac{D \times (V_{IN} - V_Q)}{f_{S \times L_1}}$$

$$\Delta I_{L2} = \frac{D \times (V_{IN} - V_Q)}{f_{S \times L2}}$$

Maintaining the condition  $I_L > \Delta I_L/2$  to ensure continuous conduction mode yields the following minimum values for  $L_1$  and  $L_2$ :

$$L_1 > \frac{(1-D) \times (V_{IN} - V_Q)}{f_S \times I_{OUT} \times 2}$$

$$L_2 > \frac{D \times (V_{IN} - V_Q)}{f_S \times I_{OUT} \times 2}$$

Peak current in the inductor, to ensure the inductor does not saturate:

$$I_{L1(PK)} = \frac{D \times I_{OUT}}{1 - D} + \frac{\Delta I_{L1}}{2}$$

$$I_{L2(PK)} = I_{OUT} + \frac{\Delta I_{L2}}{2}$$

I<sub>L1(PK)</sub> must be lower than the maximum current rat-

ing set by the current sense resistor.

The value of L1 can be increased above the minimum recommended value to reduce input ripple and output ripple. However, once  $\Delta I_{L1}$  is less than 20% of  $I_{L1(AVG)}$ , the benefit to output ripple is minimal.

By increasing the value of L2 above the minimum recommendation,  $\Delta I_{L2}$  can be reduced, which in turn will reduce the output ripple voltage:

$$\Delta V_{OUT} = \left(\frac{I_{OUT}}{1 - D} + \frac{\Delta I_{L2}}{2}\right) \times ESR$$

where ESR is the equivalent series resistance of the output capacitor.

If L1 and L2 are wound on the same core, then L1=L2=L. All the equations above will hold true if the inductance is replaced by 2L.

#### Input Capacitor Selection

Like boost structure, SEPIC has an inductor at the input. The inductor ensures that the input capacitor sees fairly low ripple currents and the capacitor should be capable of handling the input RMS current. In SEPIC application, lower values can cause impedance interactions. Therefore a good quality capacitor such as polymer tantalum, OScon or multilayer ceramic capacitors is recommended in the range from 100 µF to 200 µF.

To improve the performance especially when  $V_{\text{IN}}$  is under 8V, the input RC low pass filter could be added. Refer the input capacitor selection in boost controller application for details.

#### **Output Capacitor Selection**

The output capacitors directly affect the output ripple. Use capacitors with low ESR and ESL at the

output for higher efficiency and lower ripple voltage. Surface mount tantalums, surface mount polymer electrolytic and polymer tantalum, OS-Con, or multi-layer ceramic capacitors are recommended at the output for low ripple.

#### **Resistor Selection**

The peak current through the MOSFET,  $I_{SW(PEAK)}$ , can be adjusted using the current sense resistor,  $R_{SEN}$ , to limit at certain output current.  $R_{SEN}$  can be selected using the following equation:

$$R_{SEN} = \frac{V_{SENSE} - D \times (V_{SL} + \Delta V_{SL})}{I_{SW(PEAK)}}$$

#### **Isolation Capacitor Selection**

The isolation capacitor Cs , depends on the rms current. The rms current of the SEPIC capacitor is given by:

$$I_{CSRMS} = \sqrt{I_{SWRMS}^2 + (I_{L1PK}^2 - I_{L1PK} \Delta I_{L1} + \Delta I_{L1}^2)(1 - D)}$$

The isolation capacitor must be rated for a large ACrms current relative to the output power. This property makes the SEPIC much better suited to lower power applications where the rms current through the capacitor is small (relative to capacitor technology). The voltage rating of the isolation capacitor must be greater than the maximum input voltage. Tantalum capacitors are the best choice for SMT, having high rms current ratings relative to size. Ceramic capacitors could be used, but the low C values will tend to cause larger changes in voltage across the capacitor due to the large currents, and high C value ceramics are expensive. Electrolytics work well for through hole applications where the size required to meet the rms current rating can be accommodated. There is an energy balance between C S and L1, which can be used to determine the value of the capacitor. The basicenergy balance equation is:

$$\frac{1}{2}C_{S}\Delta V_{S}^{2} = \frac{1}{2}(L1)\Delta I_{L1}^{2}$$

Where

$$\Delta V_{S} = (\frac{V_{OUT}}{V_{OUT} + V_{IN} - V_{Q} + V_{DIODE}}) \times \frac{I_{OUT}}{f_{S}C_{S}}$$

is the ripple voltage across the isolation capacitor, and

$$\Delta I_{L1} = \frac{(V_{IN} - V_Q) \times D}{(L1)f_S}$$

is the ripple current through the inductor L1. The energy balance equation can be solved to provide a minimum value for Cs:

$$C_S \ge L1 \frac{I_{OUT}^2}{(V_{IN} - V_O)^2}$$

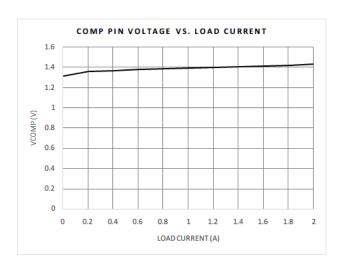

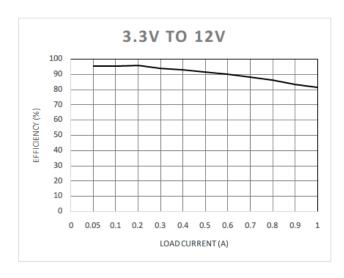

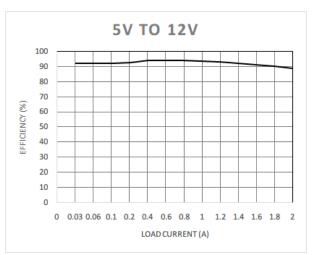

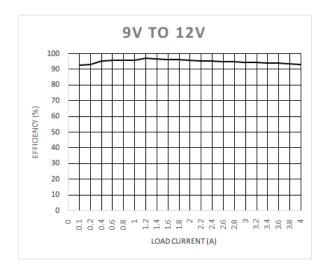

## **Typical Characteristic**

## **Typical Characteristic (cont.)**

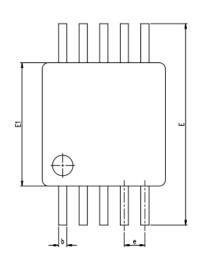

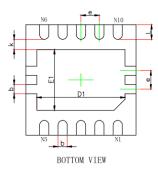

# **Package Information**

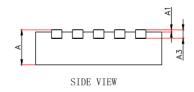

### MSOP10

| SYMBOL | DIMENSION IN MM |      |      | DIMENSION IN INCH |        |       |

|--------|-----------------|------|------|-------------------|--------|-------|

| SIMBOL | MIN.            | NOM. | MAX. | MIN.              | NOM.   | MAX.  |

| Α      | 0.81            | 1.02 | 1.10 | 0.032             | 0.040  | 0.043 |

| A1     | 0.05            |      | 0.15 | 0.002             |        | 0.006 |

| A2     | 0.75            | 0.86 | 0.95 | 0.030             | 0.034  | 0.037 |

| b      | 0.17            | 0.20 | 0.27 | 0.007             | 0.008  | 0.011 |

| С      | 0.13            | 0.15 | 0.23 | 0.005             | 0.006  | 0.009 |

| D      | 2.90            | 3.00 | 3.10 | 0.114             | 0.118  | 0.122 |

| E      | 4.75            | 4.90 | 5.05 | 0.187             | 0.193  | 0.199 |

| E1     | 2.90            | 3.00 | 3.10 | 0.114             | 0.118  | 0.122 |

| е      | 0.50 BASIC      |      |      | 0.0               | 20 BAS | IC    |

| L      | 0.40            | 0.55 | 0.70 | 0.016             | 0.022  | 0.028 |

| θ      | 0,              | 3°   | 6*   | 0,                | 3*     | 6*    |

| JEDEC  |                 |      |      |                   |        |       |

"NOTES: DIMENSION " D " DOES NOT INCLUDE MOLD FLASH,

TIE BAR BURRS AND GATE BURRS

MOLD FLASH, TIE BAR BURRS AND GATE BURRS SHALL NOT

EXCEED 0.005 INCH (0.12 MM) PER END DIMENSION " E1 "

DOES NOT INCLUDE INTERLEAD FLASH.

INTERLEAD FLASH SHALL NOT EXCEED 0.010 INCH (0.25 MM)

PER SIDE.

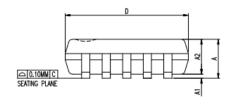

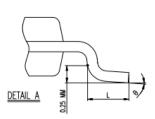

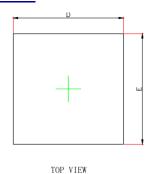

### TDFN10

| Symbol | Dimensions I | n Millimeters | Dimensions In Inches |             |  |

|--------|--------------|---------------|----------------------|-------------|--|

| Symbol | Min.         | Max.          | Min.                 | Max.        |  |

| Α      | 0.700/0.800  | 0.800/0.900   | 0.028/0.031          | 0.031/0.035 |  |

| A1     | 0.000        | 0.050         | 0.000                | 0.002       |  |

| A3     | 0.203        | REF.          | 0.008                | REF.        |  |

| D      | 2.924        | 3.076         | 0.115                | 0.121       |  |

| E      | 2.924        | 3.076         | 0.115                | 0.121       |  |

| D1     | 2.300        | 2.500         | 0.091                | 0.098       |  |

| E1     | 1.550        | 1.750         | 0.061                | 0.069       |  |

| k      | 0.200MIN.    |               | 0.008                | BMIN.       |  |

| b      | 0.200        | 0.300         | 0.008                | 0.012       |  |

| е      | 0.500        | TYP.          | 0.020                | TYP.        |  |

| L      | 0.324        | 0.476         | 0.013                | 0.019       |  |

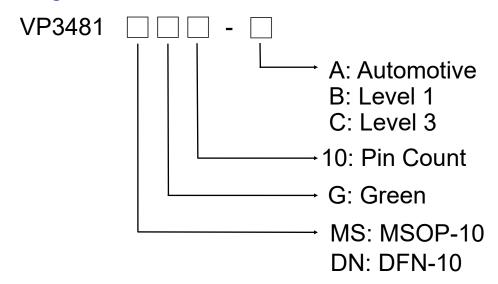

### **Ordering Information**

| Part No.      | Q`ty/Reel | MSL Peak Temp. | Op Temp.(°C ) |

|---------------|-----------|----------------|---------------|

| VP3481MSG10-A | 2,500     | Level 1 (G1)   | -40 to +125   |

| VP3481MSG10-B | 2,500     | Level 1        | -40 to +125   |

| VP3481MSG10-C | 2,500     | Level 3        | -40 to +85    |

| VP3481DNG10-B | 2,500     | Level 1        | -40 to +125   |

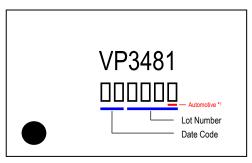

## **Marking Information**

\*1 Automotive Specifications Marking will show "-"

### **Contact Information**

### Viva Electronics Incorporated

10F-1, No. 32, Gaotie 2nd Rd., Zhubei City, Hsinchu County, Taiwan, R.O.C.

Tel: 886-3-6579508 Fax: 886-3-6579509

WWW: http://www.viva-elec.com.tw Sales: sales@viva-elec.com.tw FAE Support: fae@viva-elec.com.tw

#### **IMPORTANT NOTICE**

Viva Electronics Incorporated reserves the right to make changes without further notice to any products or specifications herein. Viva Electronics Incorporated does not assume any responsibility for use of any its products for any particular purpose, nor does Viva Electronics Incorporated assume any liability arising out of the application or use of any its products or circuits. Viva Electronics Incorporated does not convey any license under its patent rights or other rights nor the rights of others.