# **Parallel NOR Flash Automotive Memory**

## MT28FW01GABA1xPC-0AAT, MT28FW01GABA1xJS-0AAT

## Features

- Single-level cell (SLC) process technology

- Supply voltage

- V<sub>CC</sub> = 2.7–3.6V (program, erase, read)

- V<sub>CCQ</sub> = 1.65 V<sub>CC</sub> (I/O buffers)

- Asynchronous random/page read

- Page size: 16 words

- Page access: 20ns ( $V_{CC} = V_{CCQ} = 2.7-3.6V$ )

- Random access: 105ns ( $V_{CC} = V_{CCQ} = 2.7-3.6V$ )

- Random access: 110ns ( $V_{CCQ} = 1.65 V_{CC}$ )

- Buffer program (512-word program buffer)

- 2.0 MB/s (TYP) when using full buffer program

- 2.5 MB/s (TYP) when using accelerated buffer program (V<sub>HH</sub>)

- Word program: 25us per word (TYP)

- Block erase (128KB): 0.2s (TYP)

- Memory organization

- Uniform blocks: 128KB or 64KW each

- x16 data bus

- Program/erase suspend and resume capability

- Read from another block during a PROGRAM SUSPEND operation

- Read or program another block during an ERASE SUSPEND operation

- Unlock bypass, block erase, chip erase, and write to buffer capability

- BLANK CHECK operation to verify an erased block

- CYCLIC REDUNDANCY CHECK (CRC) operation to verify a program pattern

- V<sub>PP</sub>/WP# protection

- Protects first or last block regardless of block protection settings

- Software protection

- Volatile protection

- Nonvolatile protection

- Password protection

- Extended memory block

- 512-word block for permanent, secure identification

- Programmed or locked at the factory or by the customer

- JESD47-compliant

- 100,000 (minimum) ERASE cycles per block

- Data retention: 20 years (TYP)

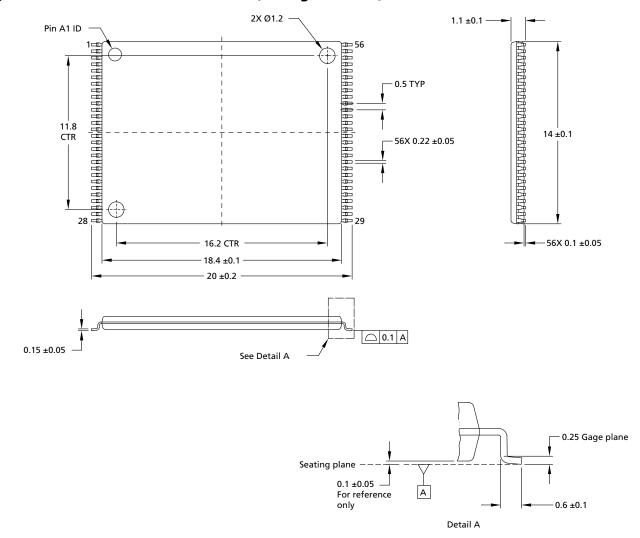

- Package

- 56-pin TSOP, 14mm x 20mm (JS)

- 64-ball LBGA, 13mm x 11mm (PC)

- RoHS-compliant, halogen-free packaging

- Automotive operating temperature

- Ambient: -40°C to 105°C

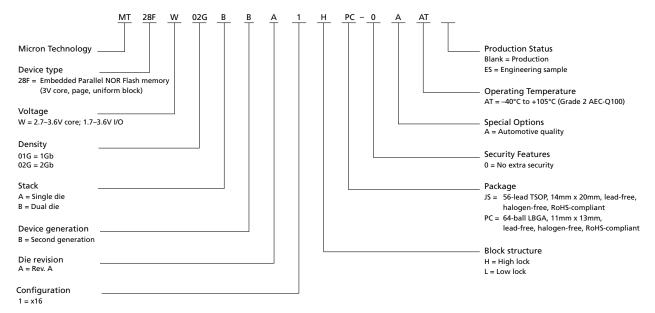

## **Part Numbering Information**

For available options, such as packages or high/low protection, or for further information, contact your Micron sales representative. Part numbers can be verified at www.micron.com. Feature and specification comparison by device type is available at www.micron.com/products. Contact the factory for devices not found.

#### **Figure 1: Part Number Chart**

## Contents

| Important Notes and Warnings                       |    |

|----------------------------------------------------|----|

| General Description                                | 8  |

| Automatic Power Savings Feature                    | 8  |

| Signal Assignments                                 | 10 |

| Signal Descriptions                                |    |

| Memory Organization                                | 14 |

| Memory Configuration                               | 14 |

| Memory Map                                         | 14 |

| Bus Operations                                     | 15 |

| Read                                               | 15 |

| Write                                              | 15 |

| Standby                                            | 15 |

| Output Disable                                     |    |

| Reset                                              |    |

| Registers                                          |    |

| Data Polling Register                              |    |

| Read Status Register                               |    |

| Clear Status Register                              |    |

| Lock Register                                      |    |

| Standard Command Definitions – Address-Data Cycles |    |

| READ and AUTO SELECT Operations                    |    |

| READ/RESET Command                                 |    |

| READ CFI Command                                   |    |

| AUTO SELECT Command                                |    |

| Read Electronic Signature                          |    |

| Cyclic Redundancy Check Operation                  |    |

| CYCLIC REDUNDANCY CHECK Command                    |    |

| Cyclic Redundancy Check Operation Command Sequence |    |

| Bypass Operations                                  | 33 |

| UNLOCK BYPASS Command                              |    |

| UNLOCK BYPASS RESET Command                        |    |

| Program Operations                                 |    |

| PROGRAM Command                                    |    |

| UNLOCK BYPASS PROGRAM Command                      |    |

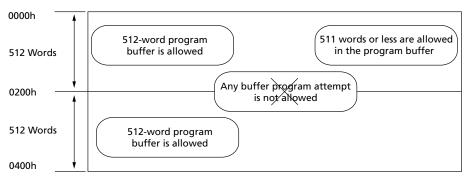

| WRITE TO BUFFER PROGRAM Command                    |    |

| UNLOCK BYPASS WRITE TO BUFFER PROGRAM Command      |    |

| WRITE TO BUFFER PROGRAM CONFIRM Command            |    |

| BUFFERED PROGRAM ABORT AND RESET Command           |    |

| PROGRAM SUSPEND Command                            |    |

| PROGRAM SOSPEND Command                            |    |

| ACCELERATED BUFFERED PROGRAM Operations            |    |

| Erase Operations                                   |    |

| CHIP ERASE Command                                 |    |

| UNLOCK BYPASS CHIP ERASE Command                   |    |

|                                                    |    |

| BLOCK ERASE Command                                |    |

| UNLOCK BYPASS BLOCK ERASE Command                  |    |

| ERASE SUSPEND Command                              |    |

| ERASE RESUME Command                               | 41 |

| ACCELERATED CHIP ERASE Operations                  |    |

| BLANK CHECK Operation                              | 41 |

### 1Gb: x16, 3V, MT28FW, Automotive Parallel NOR Features

| Device Protection                                          | 43 |

|------------------------------------------------------------|----|

| Hardware Protection                                        | 43 |

| Software Protection                                        | 43 |

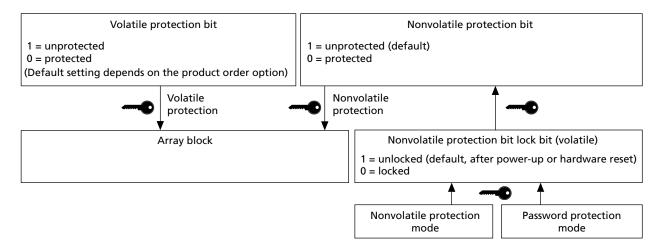

| Volatile Protection Mode                                   |    |

| Nonvolatile Protection Mode                                | 44 |

| Password Protection Mode                                   |    |

| Block Protection Command Definitions – Address-Data Cycles | 47 |

| Protection Operations                                      |    |

| LOCK REGISTER Commands                                     | 50 |

| PASSWORD PROTECTION Commands                               | 50 |

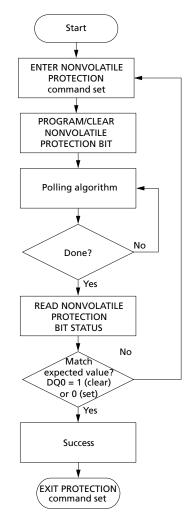

| NONVOLATILE PROTECTION Commands                            | 50 |

| NONVOLATILE PROTECTION BIT LOCK BIT Commands               | 51 |

| VOLATILE PROTECTION Commands                               | 52 |

| EXTENDED MEMORY BLOCK Commands                             | 52 |

| EXIT PROTECTION Command                                    | 53 |

| Common Flash Interface                                     | 54 |

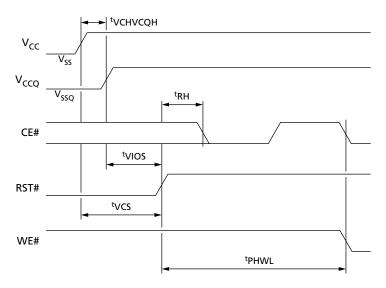

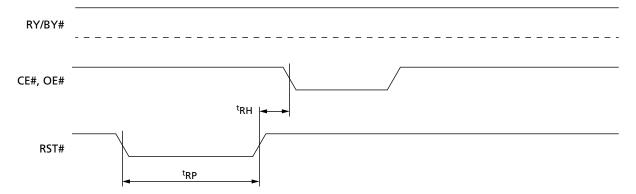

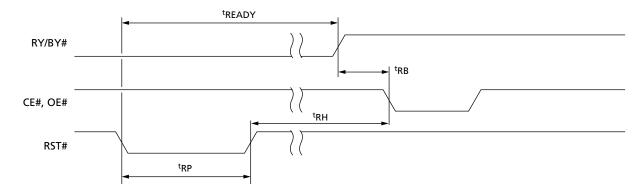

| Power-Up and Reset Characteristics                         | 59 |

| Absolute Ratings and Operating Conditions                  | 61 |

| DC Characteristics                                         |    |

| Read AC Characteristics                                    | 65 |

| Write AC Characteristics                                   | 67 |

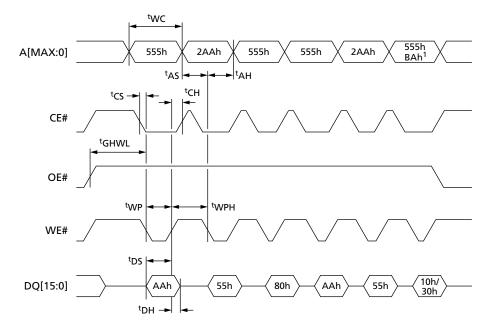

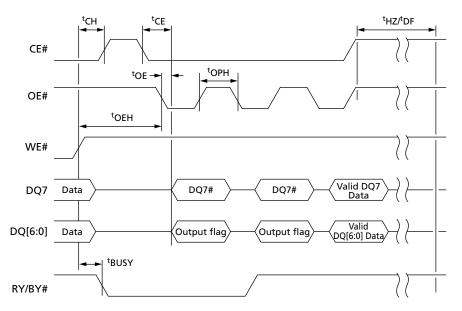

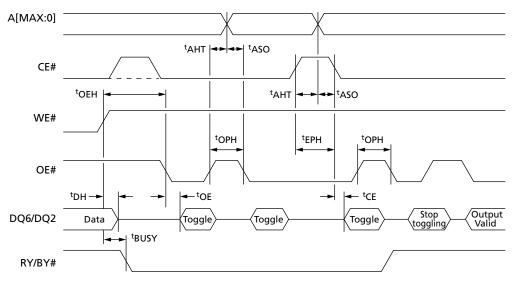

| Data Polling/Toggle AC Characteristics                     | 72 |

| Program/Erase Characteristics                              | 74 |

| Package Dimensions                                         | 75 |

| Revision History                                           | 77 |

| Rev. H –05/18                                              | 77 |

| Rev. G – 11/16                                             | 77 |

| Rev. F – 6/16                                              | 77 |

| Rev. E – 9/15                                              | 77 |

| Rev. D – 01/15                                             | 77 |

| Rev. C – 12/14                                             | 77 |

| Rev. B – 07/14                                             | 77 |

| Rev. A – 05/14                                             | 77 |

|                                                            |    |

## **List of Figures**

| Figure 1:  | Part Number Chart                                        | . 2 |

|------------|----------------------------------------------------------|-----|

| Figure 2:  | Logic Diagram                                            | . 9 |

| Figure 3:  | 56-Pin TSOP (Top View)                                   | 10  |

| Figure 4:  | 64-Ball LBGA (Top View – Balls Down)                     | 11  |

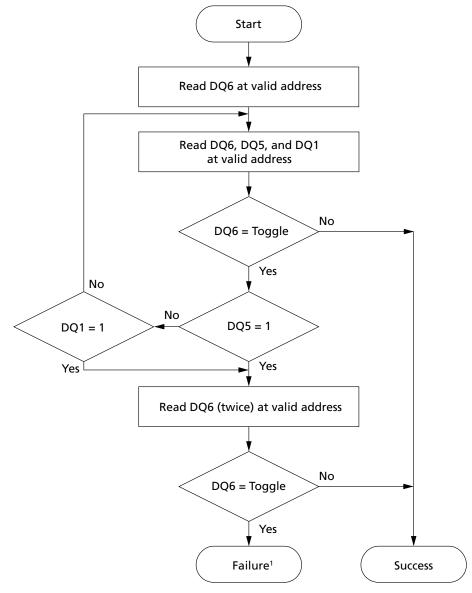

| Figure 5:  | Data Polling Flowchart                                   | 19  |

| Figure 6:  | Toggle Bit Flowchart                                     | 20  |

| Figure 7:  | Data Polling/Toggle Bit Flowchart                        | 21  |

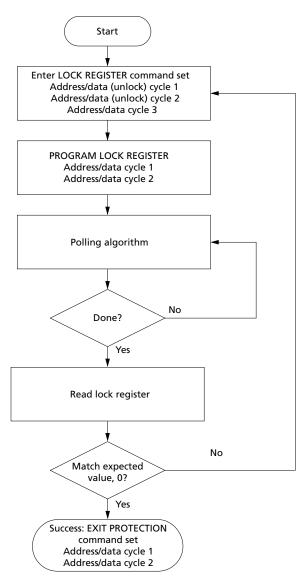

| Figure 8:  | Lock Register Program Flowchart                          | 25  |

|            | Boundary Condition of Program Buffer Size                |     |

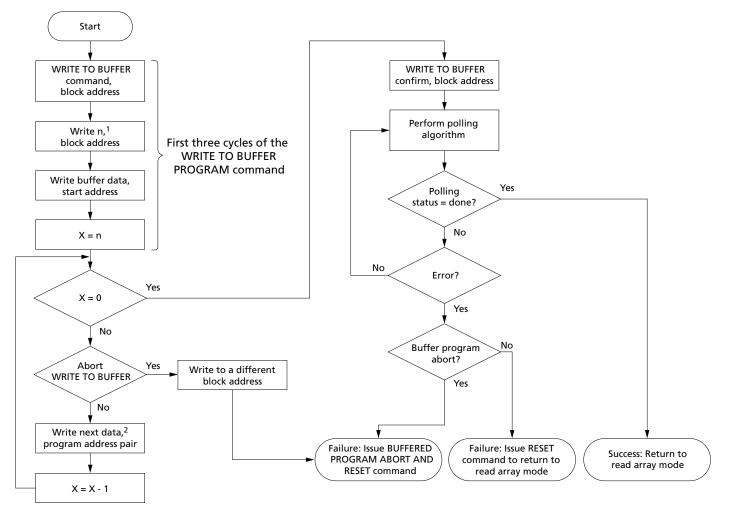

| Figure 10: | WRITE TO BUFFER PROGRAM Flowchart                        | 36  |

| Figure 11: | Software Protection Scheme                               | 45  |

| Figure 12: | Set/Clear Nonvolatile Protection Bit Algorithm Flowchart | 51  |

|            | Power-Up Timing                                          |     |

|            | Reset AC Timing – No PROGRAM/ERASE Operation in Progress |     |

|            | Reset AC Timing During PROGRAM/ERASE Operation           |     |

|            | AC Measurement Load Circuit                              |     |

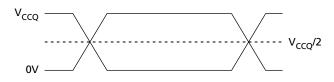

| Figure 17: | AC Measurement I/O Waveform                              | 62  |

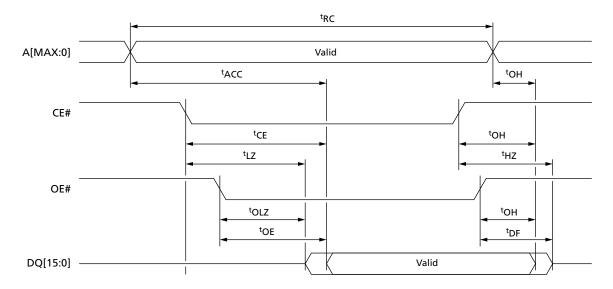

| Figure 18: | Random Read AC Timing                                    | 66  |

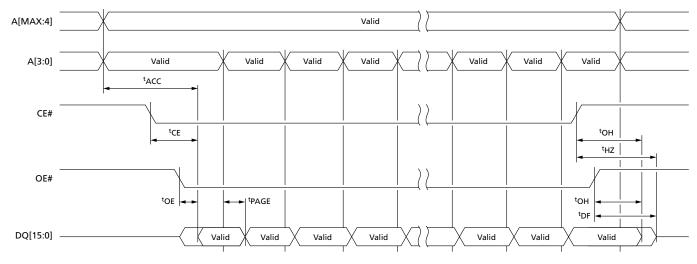

| Figure 19: | Page Read AC Timing                                      | 66  |

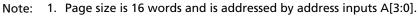

| Figure 20: | WE#-Controlled Program AC Timing                         | 68  |

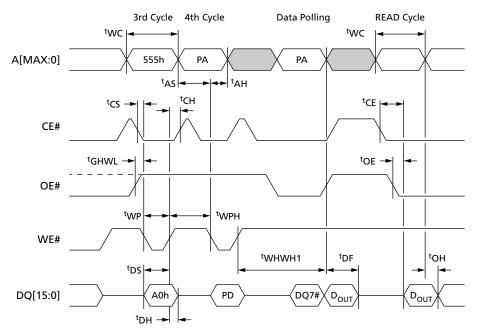

| Figure 21: | CE#-Controlled Program AC Timing                         | 70  |

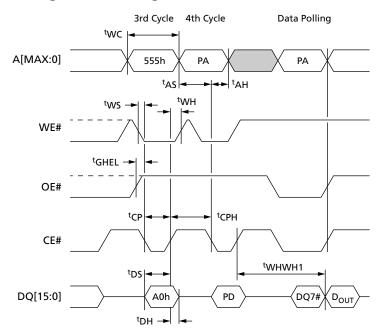

|            | Chip/Block Erase AC Timing                               |     |

| Figure 23: | Accelerated Program AC Timing                            | 71  |

|            | Data Polling AC Timing                                   |     |

| Figure 25: | Toggle/Alternative Toggle Bit Polling AC Timing          | 73  |

|            | 56-Pin TSOP – 14mm x 20mm (Package Code: JS)             |     |

| Figure 27: | 64-Ball LBGA – 11mm x 13mm (Package Code: PC)            | 76  |

## **List of Tables**

| 2  |

|----|

| 4  |

| 5  |

| 7  |

| 8  |

| 22 |

| 24 |

| 26 |

| 29 |

| 29 |

| 80 |

| 32 |

| 88 |

| 1  |

| 3  |

| 6  |

| 7  |

| 52 |

| 54 |

| 54 |

| 55 |

| 55 |

| 6  |

| 59 |

| 60 |

| 51 |

| 51 |

| 62 |

| 53 |

| 64 |

| 65 |

| 65 |

| 67 |

| 59 |

| 2  |

| '4 |

|    |

## **Important Notes and Warnings**

Micron Technology, Inc. ("Micron") reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions. This document supersedes and replaces all information supplied prior to the publication hereof. You may not rely on any information set forth in this document if you obtain the product described herein from any unauthorized distributor or other source not authorized by Micron.

Automotive Applications. Products are not designed or intended for use in automotive applications unless specifically designated by Micron as automotive-grade by their respective data sheets. Distributor and customer/distributor shall assume the sole risk and liability for and shall indemnify and hold Micron harmless against all claims, costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of product liability, personal injury, death, or property damage resulting directly or indirectly from any use of non-automotive-grade products in automotive applications. Customer/distributor shall ensure that the terms and conditions of sale between customer/distributor and any customer of distributor/customer (1) state that Micron products are not designed or intended for use in automotive applications unless specifically designated by Micron as automotive-grade by their respective data sheets and (2) require such customer of distributor/customer to indemnify and hold Micron harmless against all claims, costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of product liability, personal injury, death, or property damage resulting from any use of non-automotive-grade by their respective data sheets and (2) require such customer of distributor/customer to indemnify and hold Micron harmless against all claims, costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of product liability, personal injury, death, or property damage resulting from any use of non-automotive-grade products in automotive applications.

**Critical Applications.** Products are not authorized for use in applications in which failure of the Micron component could result, directly or indirectly in death, personal injury, or severe property or environmental damage ("Critical Applications"). Customer must protect against death, personal injury, and severe property and environmental damage by incorporating safety design measures into customer's applications to ensure that failure of the Micron component will not result in such harms. Should customer or distributor purchase, use, or sell any Micron component for any critical application, customer and distributor shall indemnify and hold harmless Micron and its subsidiaries, subcontractors, and affiliates and the directors, officers, and employees of each against all claims, costs, damages, and expenses and reasonable attorneys' fees arising out of, directly or indirectly, any claim of product liability, personal injury, or death arising in any way out of such critical application, whether or not Micron or its subsidiaries, subcontractors, or affiliates were negligent in the design, manufacture, or warning of the Micron product.

**Customer Responsibility.** Customers are responsible for the design, manufacture, and operation of their systems, applications, and products using Micron products. ALL SEMICONDUCTOR PRODUCTS HAVE INHERENT FAIL-URE RATES AND LIMITED USEFUL LIVES. IT IS THE CUSTOMER'S SOLE RESPONSIBILITY TO DETERMINE WHETHER THE MICRON PRODUCT IS SUITABLE AND FIT FOR THE CUSTOMER'S SYSTEM, APPLICATION, OR PRODUCT. Customers must ensure that adequate design, manufacturing, and operating safeguards are included in customer's applications and products to eliminate the risk that personal injury, death, or severe property or environmental damages will result from failure of any semiconductor component.

Limited Warranty. In no event shall Micron be liable for any indirect, incidental, punitive, special or consequential damages (including without limitation lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort, warranty, breach of contract or other legal theory, unless explicitly stated in a written agreement executed by Micron's duly authorized representative.

## **General Description**

The device is an asynchronous, uniform block, parallel NOR Flash memory device. READ, ERASE, and PROGRAM operations are performed using a single low-voltage supply. Upon power-up, the device defaults to read array mode.

The main memory array is divided into uniform blocks that can be erased independently so that valid data can be preserved while old data is purged. PROGRAM and ERASE commands are written to the command interface of the memory. An on-chip program/ erase controller simplifies the process of programming or erasing the memory by taking care of all special operations required to update the memory contents. The end of a PROGRAM or ERASE operation can be detected and any error condition can be identified. The command set required to control the device is consistent with JEDEC standards.

CE#, OE#, and WE# control the bus operation of the device and enable a simple connection to most microprocessors, often without additional logic.

The device supports asynchronous random read and page read from all blocks of the array. It also features an internal program buffer that improves throughput by programming 512 words via one command sequence. A 512-word extended memory block overlaps addresses with array block 0. Users can program this additional space and then protect it to permanently secure the contents. The device also features different levels of hardware and software protection to secure blocks from unwanted modification.

### **Automatic Power Savings Feature**

The automatic power savings feature provides low power operation during reads.

After data is read from the memory array and the address lines are quiescent, the automatic power savings feature reduces device current to a low value of  $I_{CCAPS}$ .

During automatic power savings mode, average current is measured over 5ms time interval 5µs after the following events happen:

- No internal read, program or erase activity occurring

- RST# is deasserted and CE# is asserted

- All other signals are quiescent and at  $V_{SS}\, or \, V_{CCQ}$

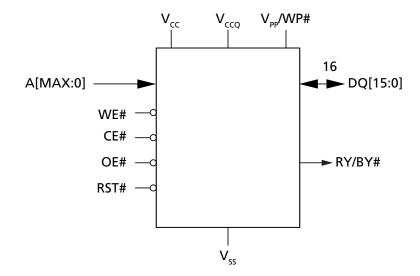

### Figure 2: Logic Diagram

## **Signal Assignments**

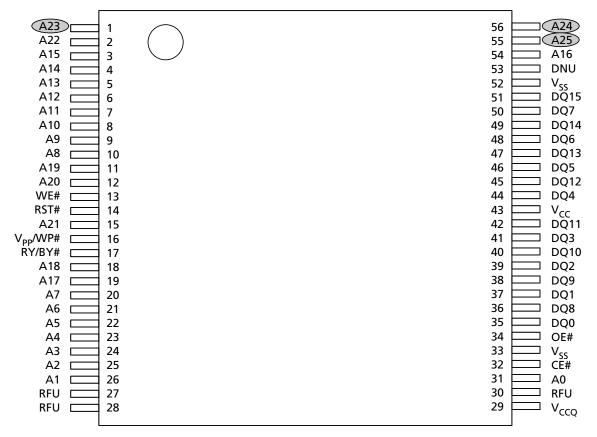

#### Figure 3: 56-Pin TSOP (Top View)

Notes: 1. A23 is valid for 256Mb and above; otherwise, it is RFU.

- 2. A24 is valid for 512Mb and above; otherwise, it is RFU.

- 3. A25 is valid for 1Gb and above; otherwise, it is RFU.

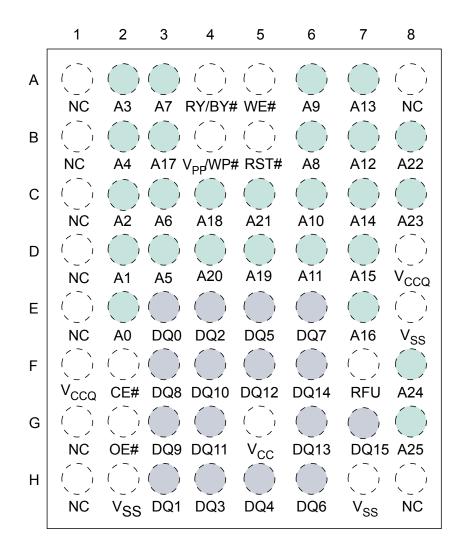

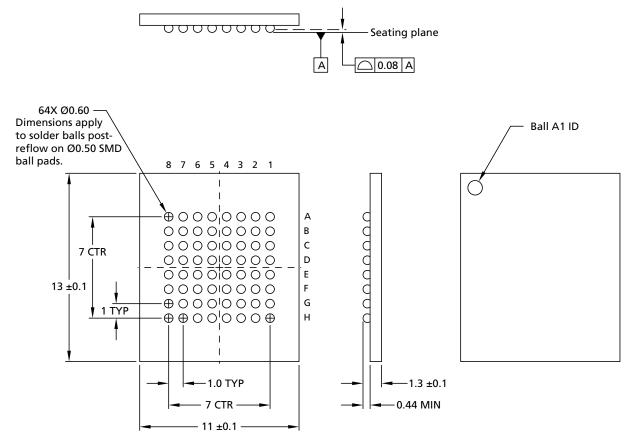

#### Figure 4: 64-Ball LBGA (Top View – Balls Down)

- 2. A24 is valid for 512Mb and above; otherwise, it is RFU.

- 3. A25 is valid for 1Gb and above; otherwise, it is RFU.

## **Signal Descriptions**

The signal description table below is a comprehensive list of signals for this device family. All signals listed may not be supported on this device. See Signal Assignments for information specific to this device.

#### **Table 1: Signal Descriptions**

| Name                 | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A[MAX:0]             | Input  | <b>Address:</b> Selects the cells in the array to access during READ operations. During WRITE operations, they control the commands sent to the command interface of the program/erase controller.                                                                                                                                                                                                                                                                                                                                                                                           |

| CE#                  | Input  | <b>Chip enable:</b> Activates the device, enabling READ and WRITE operations to be performed. When CE# is HIGH, the device goes to standby and data outputs are High-Z.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| OE#                  | Input  | <b>Output enable:</b> Active LOW input. OE# LOW enables the data output buffers during READ cycles. When OE# is HIGH, data outputs are High-Z.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| WE#                  | Input  | Write enable: Controls WRITE operations to the device. Address is latched on the falling edge of WE# and data is latched on the rising edge.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| V <sub>PP</sub> /WP# | Input  | <b>V<sub>PP</sub>/Write Protect:</b> Provides WRITE PROTECT function and V <sub>HH</sub> function. These functions protect the lowest or highest block and enable the device to enter unlock bypass mode, respectively. (Refer to Hardware Protection and Bypass Operations for details.)                                                                                                                                                                                                                                                                                                    |

| RST#                 | Input  | <b>Reset:</b> Applies a hardware reset to the device control logic and places it in standby, which is achieved by holding RST# LOW for at least <sup>t</sup> PLPH. After RST# goes HIGH, the device is ready for READ and WRITE operations (after <sup>t</sup> PHEL or <sup>t</sup> PHWL, whichever occurs last).                                                                                                                                                                                                                                                                            |

| DQ[15:0]             | I/O    | <b>Data I/O:</b> Outputs the data stored at the selected address during a READ operation. During WRITE operations, they represent the commands sent to the command interface of the internal state machine.                                                                                                                                                                                                                                                                                                                                                                                  |

| RY/BY#               | Output | <b>Ready busy:</b> Open-drain output that can be used to identify when the device is performing a PROGRAM or ERASE operation. During PROGRAM or ERASE operations, RY/BY# is LOW, and is High-Z during read mode, auto select mode, and erase suspend mode. The use of an open-drain output enables the RY/BY# pins from several devices to be connected to a single pull-up resistor to V <sub>CCQ</sub> . A low value will then indicate that one (or more) of the devices is (are) busy. A 10K Ohm or bigger resistor is recommended as pull-up resistor to achieve 0.1V V <sub>OL</sub> . |

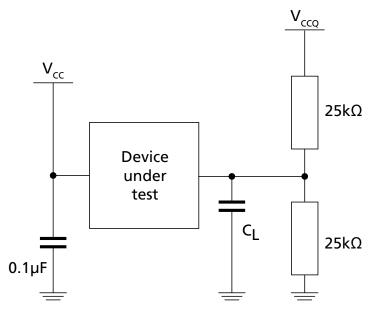

| V <sub>cc</sub>      | Supply | <b>Supply voltage:</b> Provides the power supply for READ, PROGRAM, and ERASE operations.<br>The device is disabled when $V_{CC} \leq V_{LKO}$ . If the program/erase controller is programming or erasing during this time, then the operation aborts and the contents being altered will be invalid.<br>A 0.1µF and 0.01µF capacitor should be connected between $V_{CC}$ and $V_{SS}$ to decouple the current surges from the power supply. The PCB track widths must be sufficient to carry the currents required during PROGRAM and ERASE operations (see DC Characteristics).          |

| V <sub>CCQ</sub>     | Supply | <b>I/O supply voltage:</b> Provides the power supply to the I/O pins and enables all outputs to be powered independently from V <sub>CC</sub> .<br>A 0.1µF and 0.01µF capacitor should be connected between V <sub>CCQ</sub> and V <sub>SS</sub> to decouple the current surges from the power supply.                                                                                                                                                                                                                                                                                       |

| V <sub>SS</sub>      | Supply | Ground: All V <sub>SS</sub> pins must be connected to the system ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

#### **Table 1: Signal Descriptions (Continued)**

| Name | Туре | Description                                                                                                                                                                                                                           |

|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RFU  | —    | <b>Reserved for future use:</b> Reserved by Micron for future device functionality and enhance-<br>ment. Recommend that these be left floating. May be connected internally, but external con-<br>nections will not affect operation. |

| DNU  | _    | <b>Do not use:</b> Do not connect to any other signal, or power supply; must be left floating.                                                                                                                                        |

| NC   | —    | No connect: No internal connection; can be driven or floated.                                                                                                                                                                         |

## **Memory Organization**

## **Memory Configuration**

The main memory array is divided into 128KB or 64KW uniform blocks.

### **Memory Map**

### Table 2: Blocks[1023:0]

|       | Address Range |           |  |  |  |

|-------|---------------|-----------|--|--|--|

| Block | Start         | End       |  |  |  |

| 1023  | 3FF 0000h     | 3FF FFFFh |  |  |  |

| :     | :             | :         |  |  |  |

| 511   | 1FF 0000h     | 1FF FFFFh |  |  |  |

| :     | :             | :         |  |  |  |

| 255   | 0FF 0000h     | 0FF FFFFh |  |  |  |

| :     | :             | :         |  |  |  |

| 127   | 07F 0000h     | 07F FFFFh |  |  |  |

| :     | :             | :         |  |  |  |

| 63    | 03F 0000h     | 03F FFFFh |  |  |  |

| :     | :             | :         |  |  |  |

| 0     | 000 0000h     | 000 FFFFh |  |  |  |

Note: 1. 1Gb device = Blocks 0–1023.

## **Bus Operations**

### **Table 3: Bus Operations**

#### Notes 1 and 2 apply to entire table

| Operation         | CE# | OE# | WE# | RST# | V <sub>PP</sub> /WP# | A[MAX:0]        | DQ[15:0]                |

|-------------------|-----|-----|-----|------|----------------------|-----------------|-------------------------|

| READ              | L   | L   | Н   | Н    | Х                    | Address         | Data output             |

| WRITE             | L   | Н   | L   | Н    | H <sup>3</sup>       | Command address | Data input <sup>4</sup> |

| STANDBY           | Н   | Х   | Х   | Н    | Х                    | Х               | High-Z                  |

| OUTPUT<br>DISABLE | L   | Н   | Н   | Н    | х                    | Х               | High-Z                  |

| RESET             | Х   | Х   | Х   | L    | Х                    | Х               | High-Z                  |

Notes: 1. Typical glitches of less than 3ns on CE#, OE#, and WE# are ignored by the device and do not affect bus operations.

- 2. H = Logic level HIGH ( $V_{IH}$ ); L = Logic level LOW ( $V_{IL}$ ); X = HIGH or LOW.

- 3. If WP# is LOW, then the highest or the lowest block remains protected, depending on line item.

- 4. Data input is required when issuing a command sequence or when performing data polling or block protection.

#### Read

Bus READ operations read from the memory cells, registers, extended memory block, or CFI space. To accelerate the READ operation, the memory array can be read in page mode where data is internally read and stored in a page buffer.

Page size is 16 words and is addressed by address inputs A[3:0]. The extended memory blocks and CFI area support page read mode.

A valid bus READ operation involves setting the desired address on the address inputs, taking CE# and OE# LOW, and holding WE# HIGH. The data I/Os will output the value. If CE# goes HIGH and returns LOW for a subsequent access, a random read access is performed and <sup>t</sup>ACC or <sup>t</sup>CE is required. (See AC Characteristics for details about when the output becomes valid.)

#### Write

Bus WRITE operations write to the command interface. A valid bus WRITE operation begins by setting the desired address on the address inputs. The address inputs are latched by the command interface on the falling edge of CE# or WE#, whichever occurs last. The data I/Os are latched by the command interface on the rising edge of CE# or WE#, whichever occurs first. OE# must remain HIGH during the entire bus WRITE operation (See AC Characteristics for timing requirement details).

### Standby

Driving CE# HIGH in read mode causes the device to enter standby and data I/Os to be High-Z (See DC Characteristics).

### 1Gb: x16, 3V, MT28FW, Automotive Parallel NOR Bus Operations

During PROGRAM or ERASE operations, the device will continue to use the program/ erase supply current ( $I_{CC3}$ ) until the operation completes. The device cannot be placed into standby mode during a PROGRAM/ERASE operation.

## **Output Disable**

Data I/Os are High-Z when OE# is HIGH.

#### Reset

During reset mode the device is deselected and the outputs are High-Z. The device is in reset mode when RST# is LOW. The power consumption is reduced to the standby level, independently from CE#, OE#, or WE# inputs.

When RST# is HIGH, a time of <sup>t</sup>PHEL is required before a READ operation can access the device, and a delay of <sup>t</sup>PHWL is required before a write sequence can be initiated. After this wake-up interval, normal operation is restored, the device defaults to read array mode, and the data polling register is reset.

If RST# is driven LOW during a PROGRAM/ERASE operation or any other operation that requires writing to the device, the operation will abort within <sup>t</sup>PLRH, and memory contents at the aborted block or address are no longer valid.

## Registers

The device features two methods for monitoring internal status during modify operations: data polling status and read status register. Users must not mix the two methods. Only one method at a time must be used to monitor internal operations.

## **Data Polling Register**

The device automatically enters data polling status mode upon command issuance. The data polling status information uses the following to indicate information: DQ1, DQ2, DQ3, DQ5, DQ6, and DQ7; DQ[15:8] are reserved and will output 00h.

### **Table 4: Data Polling Register Bit Definitions**

| Note | 1 | applies | to | entire  | table |

|------|---|---------|----|---------|-------|

| NOLC |   | upplies | ιU | CITCITC | tubic |

| Bit | Name                             | Settings                                           | Description                                                                                                                                                                                                                                                                                                              | Notes   |

|-----|----------------------------------|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| DQ7 | Data polling<br>bit              | 0 or 1, depending on operations                    | Monitors whether the program/erase controller has successful-<br>ly completed its operation, or has responded to an ERASE SUS-<br>PEND operation.                                                                                                                                                                        | 2, 4    |

| DQ6 | Toggle bit                       | Toggles: 0 to 1; 1 to 0;<br>and so on              | Monitors whether the program, erase, or blank check control-<br>ler has successfully completed its operations, or has responded<br>to an ERASE SUSPEND operation. During a PROGRAM/ERASE/<br>BLANK CHECK operation, DQ6 toggles from 0 to 1, 1 to 0, and<br>so on, with each successive READ operation from any address. | 3, 4, 5 |

| DQ5 | Error bit                        | 0 = Success<br>1 = Failure                         | Identifies errors detected by the program/erase controller. DQ5<br>is set to 1 when a PROGRAM, BLOCK ERASE, or CHIP ERASE op-<br>eration fails to write the correct data to the memory, or when<br>a BLANK CHECK or CRC operation fails.                                                                                 | 4, 6    |

| DQ3 | Erase timer<br>bit               | 0 = Erase not in progress<br>1 = Erase in progress | Identifies the start of program/erase controller operation dur-<br>ing a BLOCK ERASE command. Before the program/erase con-<br>troller starts, this bit set to 0.                                                                                                                                                        | 4       |

| DQ2 | Alternative<br>toggle bit        | Toggles: 0 to 1; 1 to 0;<br>and so on              | During CHIP ERASE, BLOCK ERASE, and ERASE SUSPEND opera-<br>tions, DQ2 toggles from 0 to 1, 1 to 0, and so on, with each<br>successive READ operation from addresses within the blocks<br>being erased.                                                                                                                  | 3, 4    |

| DQ1 | Buffered<br>program<br>abort bit | 1 = Abort                                          | Indicates a BUFFER PROGRAM, BLANK CHECK, or CRC opera-<br>tion abort. The BUFFERED PROGRAM ABORT and RESET com-<br>mand must be issued to return the device to read mode (see<br>WRITE TO BUFFER PROGRAM command).                                                                                                       |         |

Notes: 1. The data polling register can be read during PROGRAM, ERASE, or ERASE SUSPEND operations; the READ operation outputs data on DQ[7:0].

2. For a PROGRAM operation in progress, DQ7 outputs the complement of the bit being programmed. For a READ operation from the address previously programmed successfully, DQ7 outputs existing DQ7 data. For a READ operation from addresses with blocks to be erased while an ERASE SUSPEND operation is in progress, DQ7 outputs 0; upon successful completion of the ERASE SUSPEND operation, DQ7 outputs 1. For an ERASE operation in progress, DQ7 outputs 0; upon ERASE operation's successful completion, DQ7 outputs 1. During a BUFFER PROGRAM operation, the data polling bit is valid only for the last word being programmed in the write buffer.

- 3. After successful completion of a PROGRAM, ERASE, or BLANK CHECK operation, the device returns to read mode.

- 4. During erase suspend mode, READ operations to addresses within blocks not being erased output memory array data as if in read mode. A protected block is treated the same as a block not being erased. See the Toggle Flowchart for more information.

- 5. During erase suspend mode, DQ6 toggles when addressing a cell within a block being erased. The toggling stops when the program/erase controller has suspended the ERASE operation. See the Toggle Flowchart for more information.

- 6. When DQ5 is set to 1, a READ/RESET (F0h) command must be issued before any subsequent command.

#### **Table 5: Operations and Corresponding Bit Settings**

| Operation                          | Address                       | DQ7                                          | DQ6       | DQ5 | DQ3 | DQ2       | DQ1 | RY/BY# | Notes |

|------------------------------------|-------------------------------|----------------------------------------------|-----------|-----|-----|-----------|-----|--------|-------|

| PROGRAM                            | Any address                   | DQ7#                                         | Toggle    | 0   | _   | _         | 0   | 0      | 2     |

| CRC range of<br>blocks             | Any address                   | 1                                            | Toggle    | 0   | _   | -         | 0   | 0      |       |

| CRC chip                           | Any address                   | DQ7#                                         | Toggle    | 0   | _   | -         | 0   | 0      | 4     |

| CHIP ERASE                         | Any address                   | 0                                            | Toggle    | 0   | 1   | Toggle    | _   | 0      |       |

| BLANK CHECK                        | Blank-checking<br>block       | 0                                            | Toggle    | 0   | 1   | Toggle    | -   | 0      |       |

|                                    | Non-blank-check-<br>ing block | 0                                            | Toggle    | 0   | 1   | No toggle | -   | 0      |       |

| BLOCK ERASE                        | Erasing block                 | 0                                            | Toggle    | 0   | 1   | Toggle    | -   | 0      |       |

|                                    | Non-erasing block             | 0                                            | Toggle    | 0   | 1   | No toggle | _   | 0      |       |

| PROGRAM<br>SUSPEND                 | Programming<br>block          | Invalid operation                            |           |     |     |           |     | High-Z |       |

|                                    | Nonprogramming<br>block       | Outputs memory array data as if in read mode |           |     |     |           |     | High-Z |       |

| ERASE                              | Erasing block                 | 1                                            | No Toggle | 0   | -   | Toggle    | -   | High-Z |       |

| SUSPEND                            | Non-erasing block             | Outputs memory array data as if in read mode |           |     |     |           |     |        |       |

| PROGRAM during                     | Erasing block                 | DQ7#                                         | Toggle    | 0   | -   | Toggle    | -   | 0      | 2     |

| ERASE SUSPEND                      | Non-erasing block             | DQ7#                                         | Toggle    | 0   | -   | No Toggle | -   | 0      | 2     |

| BUFFERED<br>PROGRAM ABORT          | Any address                   | DQ7#                                         | Toggle    | 0   | _   | -         | 1   | High-Z |       |

| PROGRAM Error                      | Any address                   | DQ7#                                         | Toggle    | 1   | -   | -         | -   | High-Z | 2     |

| ERASE Error                        | Any address                   | 0                                            | Toggle    | 1   | 1   | Toggle    | _   | High-Z |       |

| BLANK CHECK Er- Any address<br>ror |                               | 0                                            | Toggle    | 1   | 1   | Toggle    | -   | High-Z |       |

| CRC range of<br>blocks error       | Any address                   | 1                                            | Toggle    | 1   | _   | -         | -   | High-Z |       |

| CRC chip error                     | Any address                   | DQ7#                                         | Toggle    | 1   | -   | -         | _   | High-Z | 4     |

Note 1 applies to entire table

Notes: 1. Unspecified data bits should be ignored.

2. DQ7# for buffer program is related to the last address location loaded.

3. DQ7# is the reverse DQ7 of the last word or byte loaded before CRC chip confirm command cycle.

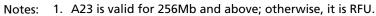

#### **Figure 5: Data Polling Flowchart**

- Notes: 1. Valid address is the last address being programmed or an address within the block being erased.

- 2. Failure results: DQ5 = 1 indicates an operation error. A READ/RESET (F0h) command must be issued before any subsequent command.

- 3. Failure results: DQ1 = 1 indicates a WRITE TO BUFFER PROGRAM ABORT operation. A full three-cycle RESET (AAh/55h/F0h) command sequence must be used to reset the aborted device.

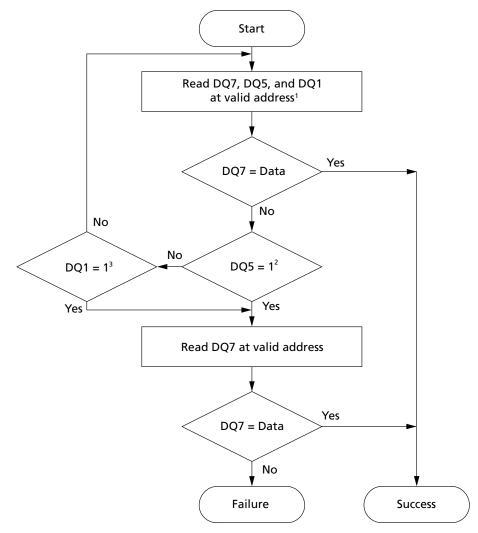

### Figure 6: Toggle Bit Flowchart

Note: 1. Failure results: DQ5 = 1 indicates an operation error; DQ1 = 1 indicates a WRITE TO BUF-FER PROGRAM ABORT operation.

## **Read Status Register**

The device's status register displays PROGRAM, ERASE, and BLANK CHECK operations status. A device's status can be read after writing the READ STATUS REGISTER command (70h). When the READ STATUS REGISTER command is issued, the current status is captured by the register and the device is in read status register mode. The first read access in the status register mode exits the mode and returns to the output state when the READ STATUS REGISTER command was issued. No other command should be sent before reading the status register to exit the status register mode.

The status register bits are output on DQ[7:0], while DQ[15:8] outputs are 00h.

#### **Table 6: Status Register Definitions**

| Bit      | Name                                           | Settings                                                                        | Description                                                                                                                                                                             |

|----------|------------------------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SR[15:8] | -                                              | Reserved                                                                        | Reserved for future use. Will always be set to 0.                                                                                                                                       |

| SR7      | Device program/<br>erase/blank check<br>status | 0 = Busy<br>1 = Ready                                                           | Indicates erase, program, or blank check completion in the de-<br>vice. SR[6:1] are invalid; SR7 = 0.                                                                                   |

| SR6      | Erase suspend status                           | 0 = Erase in progress/<br>complete<br>1 = Erase suspended                       | Indicates whether the device is erase suspended. After issuing an ERASE SUSPEND command, SR7 and SR6 are set to 1. SR6 remains set until the device receives an ERASE RESUME command.   |

| SR5      | Erase/blank check<br>status                    | 0 = Erase/blank<br>check successful<br>1 = Erase/blank<br>check error           | Set to 1 if an attempted erase or blank check failed.                                                                                                                                   |

| SR4      | Program status                                 | 0 = Program success<br>1 = Program error                                        | Indicates whether the program failed or the buffer program has aborted.                                                                                                                 |

| SR3      | Writer buffer abort<br>status                  | 0 = Program not<br>aborted<br>1 = Program aborted<br>during buffer pro-<br>gram | Indicates whether the buffer program has aborted.                                                                                                                                       |

| SR2      | Program suspend<br>status                      | 0 = Program in pro-<br>gress/complete<br>1 = Program suspen-<br>ded             | Indicates whether the device is program suspended. After receiv-<br>ing a PROGRAM SUSPEND command, SR7 and SR2 are set to 1,<br>and remain set at 1 until a RESUME command is received. |

| SR1      | Device protect status                          | 0 = Unlocked<br>1 = Aborted erase/<br>program attempt on<br>a locked block      | Indicates whether program or erase was attempted on a locked<br>block. If an ERASE or PROGRAM operation is attempted on a<br>locked block, SR1 is set to 1 and the operation aborts.    |

| SR0      | -                                              | Reserved                                                                        | Reserved for future use. Will always be set to 0.                                                                                                                                       |

## **Clear Status Register**

The status register content can be cleared by CLEAR STATUS REGISTER command (71h). The CLEAR STATUS REGISTER command clears the status register bits SR[6:1]. SR7 remains at 0, which indicates the device is busy.

However, for buffer program abort only, the CLEAR STATUS REGISTER command would change also SR7 to 1, which reverts the device to main array read mode. The status register can also be cleared by using RESET Command (F0h).

## **Lock Register**

### **Table 7: Lock Register Bit Definitions**

Note 1 applies to entire table

| Bit      | Name                                            | Settings                                                                                                                                                                  | Description                                                                                                                                                                                                                                      | Notes |

|----------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| DQ[15:9] | -                                               | Default value = 1                                                                                                                                                         | DQ[15:9] are reserved and are set to a default value of 1.                                                                                                                                                                                       |       |

| DQ8      | -                                               | Default value = 0                                                                                                                                                         | DQ8 is reserved and is set to a default value of 0.                                                                                                                                                                                              |       |

| DQ[7:3]  | -                                               | Default value =1                                                                                                                                                          | DQ[7:3] are reserved and are set to a default value of 1.                                                                                                                                                                                        |       |

| DQ2      |                                                 | 0 = Password protec-<br>tion mode enabled<br>1 = Password protec-<br>tion mode disabled<br>(default)                                                                      | Places the device permanently in password protection mode.                                                                                                                                                                                       | 2     |

| DQ1      | Nonvolatile<br>protection<br>mode lock bit      | 0 = Nonvolatile pro-<br>tection mode enabled<br>with password protec-<br>tion mode perma-<br>nently disabled<br>1 = Nonvolatile pro-<br>tection mode enabled<br>(default) | Places the device in nonvolatile protection mode, with pass-<br>word protection mode permanently disabled. When shipped<br>from the factory, the device will operate in nonvolatile pro-<br>tection mode, and the memory blocks are unprotected. | 2     |

| DQ0      | Extended<br>memory<br>block protec-<br>tion bit | 0 = Protected<br>1 = Unprotected (de-<br>fault)                                                                                                                           | If the device is shipped with the extended memory block un-<br>locked, the block can be protected by setting this bit to 0. The<br>extended memory block protection status can be read in auto<br>select mode by issuing an AUTO SELECT command. |       |

Notes: 1. The lock register is a 16-bit, one-time programmable register. DQ[15:3] are reserved.

2. The password protection mode lock bit and nonvolatile protection mode lock bit cannot both be programmed to 0. Any attempt to program one while the other is programmed causes the operation to abort, and the device returns to read mode. The device is shipped from the factory with the default setting.

- Notes: 1. Each lock register bit can be programmed only once.

- 2. See the Block Protection Command Definitions table for address-data cycle details.

- 3. DQ5 and DQ1 are ignored in this algorithm flow.

## Standard Command Definitions – Address-Data Cycles

#### Table 8: Standard Command Definitions – Address-Data Cycles

Note 1 applies to entire table

|                                                   |       |       | Address and Data Cycles |    |     |    |        |        |     |    |     |    |         |

|---------------------------------------------------|-------|-------|-------------------------|----|-----|----|--------|--------|-----|----|-----|----|---------|

| Command and                                       | 1st   |       | 2n                      | d  | 3r  | d  | 4th    |        | 5th |    | 6th |    | 1       |

| Code/Subcode                                      | Α     | D     | Α                       | D  | Α   | D  | Α      | D      | Α   | D  | A   | D  | Notes   |

| <b>READ and AUTO SELECT</b>                       | Opera | tions |                         |    |     |    |        |        |     |    |     |    |         |

| READ/RESET (F0h)                                  | 555   | AA    | 2AA                     | 55 | Х   | F0 |        |        |     |    |     |    | 2       |

| READ CFI (98h)                                    | 555   | 98    |                         |    |     |    |        |        |     |    |     |    |         |

| EXIT READ CFI (F0h)                               | Х     | F0    |                         |    |     |    |        |        |     |    |     |    |         |

| AUTO SELECT (90h)                                 | 555   | AA    | 2AA                     | 55 | 555 | 90 | Note 3 | Note 3 |     |    |     |    | 4, 5    |

| EXIT AUTO SELECT (F0h)                            | Х     | F0    |                         |    |     |    |        |        |     |    |     |    |         |

| READ STATUS (70h)                                 | 555   | 70    |                         |    |     |    |        |        |     |    |     |    |         |

| CLEAR STATUS (71h)                                | 555   | 71    |                         |    |     |    |        |        |     |    |     |    |         |

| BYPASS Operations                                 |       |       |                         |    |     |    |        |        |     |    |     |    |         |

| UNLOCK BYPASS (20h)                               | 555   | AA    | 2AA                     | 55 | 555 | 20 |        |        |     |    |     |    |         |

| UNLOCK BYPASS                                     | Х     | 90    | Х                       | 00 |     |    |        |        |     |    |     |    |         |

| RESET (90h/00h)                                   |       |       |                         |    |     |    |        |        |     |    |     |    |         |

| <b>PROGRAM</b> Operations                         |       | 1     |                         |    |     |    | i -    |        |     |    |     |    |         |

| PROGRAM (A0h)                                     | 555   | AA    | 2AA                     | 55 | 555 | A0 | PA     | PD     |     |    |     |    |         |

| UNLOCK BYPASS<br>PROGRAM (A0h)                    | Х     | A0    | PA                      | PD |     |    |        |        |     |    |     |    | 6       |

| WRITE TO BUFFER<br>PROGRAM (25h)                  | 555   | AA    | 2AA                     | 55 | BAd | 25 | BAd    | N      | PA  | PD |     |    | 7, 8, 9 |

| UNLOCK BYPASS<br>WRITE TO BUFFER<br>PROGRAM (25h) | BAd   | 25    | BAd                     | N  | PA  | PD |        |        |     |    |     |    | 6       |

| WRITE TO BUFFER<br>PROGRAM CONFIRM<br>(29h)       | BAd   | 29    |                         | 1  |     |    |        |        |     |    |     |    | 7       |

| BUFFERED PROGRAM<br>ABORT and RESET (F0h)         | 555   | AA    | 2AA                     | 55 | 555 | F0 |        |        |     |    |     |    |         |

| PROGRAM SUSPEND<br>(B0h)                          | Х     | B0    |                         |    |     |    |        |        |     |    |     |    |         |

| PROGRAM RESUME (30h)                              | Х     | 30    |                         |    |     |    |        |        |     |    |     |    |         |

| PROGRAM SUSPEND<br>(51h)                          | Х     | 51    |                         |    |     |    |        |        |     |    |     |    |         |

| PROGRAM RESUME (50h)                              | Х     | 50    |                         |    |     |    |        |        |     |    |     |    |         |

| ERASE Operations                                  |       |       |                         |    |     |    |        |        |     |    |     |    |         |

| CHIP ERASE (80/10h)                               | 555   | AA    | 2AA                     | 55 | 555 | 80 | 555    | AA     | 2AA | 55 | 555 | 10 |         |

| UNLOCK BYPASS<br>CHIP ERASE (80/10h)              | Х     | 80    | Х                       | 10 |     |    |        |        |     |    |     |    | 6       |

#### Table 8: Standard Command Definitions – Address-Data Cycles (Continued)

Note 1 applies to entire table

|                                       |     | Address and Data Cycles |     |    |     |    |     |    |     |    |     |    |       |

|---------------------------------------|-----|-------------------------|-----|----|-----|----|-----|----|-----|----|-----|----|-------|

| Command and                           | 1st |                         | 2nd |    | 3rd |    | 4th |    | 5th |    | 6th |    |       |

| Code/Subcode                          | Α   | D                       | Α   | D  | Α   | D  | Α   | D  | A   | D  | Α   | D  | Notes |

| BLOCK ERASE (80/30h)                  | 555 | AA                      | 2AA | 55 | 555 | 80 | 555 | AA | 2AA | 55 | BAd | 30 |       |

| UNLOCK BYPASS<br>BLOCK ERASE (80/30h) | Х   | 80                      | BAd | 30 |     |    |     |    |     |    | •   |    | 6     |

| ERASE SUSPEND (B0h)                   | Х   | B0                      |     |    |     |    |     |    |     |    |     |    |       |

| ERASE RESUME (30h)                    | Х   | 30                      |     |    |     |    |     |    |     |    |     |    |       |

| BLANK CHECK Operations                |     |                         |     |    |     |    |     |    |     |    |     |    |       |

| BLANK CHECK                           | 555 | 33                      |     |    |     |    |     |    |     |    |     |    |       |

- Notes: 1. A = Address; D = Data; X = "Don't Care"; BAd = Any address in the block; N = Number of words to be programmed; PA = Program address; PD = Program data; Gray shading = Not applicable. All values in the table are hexadecimal. Some commands require both a command code and subcode.

- 2. A full three-cycle RESET command sequence must be used to reset the device in the event of a buffered program abort error (DQ1 = 1).

- 3. These cells represent READ cycles (versus WRITE cycles for the others).

- 4. AUTO SELECT enables the device to read the manufacturer code, device code, block protection status, and extended memory block protection indicator.

- 5. AUTO SELECT addresses and data are specified in the Electronic Signature table and the Extended Memory Block Protection table.

- 6. For any UNLOCK BYPASS ERASE/PROGRAM command, the first two UNLOCK cycles are unnecessary.

- 7. BAd must be the same as the address loaded during the WRITE TO BUFFER PROGRAM 3rd and 4th cycles.

- WRITE TO BUFFER PROGRAM operation: maximum cycles = 517. UNLOCK BYPASS WRITE TO BUFFER PROGRAM operation: maximum cycles = 515. WRITE TO BUFFER PROGRAM operation: N + 1 = words to be programmed; maximum buffer size = 512 words.

- 9. A[MAX:9] address pins should remain unchanged while A[8:0] pins are used to select a word within the N+1 word page.

## **READ and AUTO SELECT Operations**

### **READ/RESET Command**

The READ/RESET (F0h) command returns the device to read mode and resets the errors in the data polling register. One or three bus WRITE operations can be used to issue the READ/RESET command. Note: A full three-cycle RESET command sequence must be used to reset the device in the event of a buffered program abort error (DQ1 = 1).

Once a PROGRAM, ERASE, or SUSPEND operation begins, RESET commands are ignored until the operation is complete. Read/reset serves primarily to return the device to read mode from a failed PROGRAM or ERASE operation. Read/reset may cause a return to read mode from undefined states that might result from invalid command sequences. A hardware reset may be required to return to normal operation from some undefined states.

To exit the unlock bypass mode, the system must issue a two-cycle UNLOCK BYPASS RESET command sequence. A READ/RESET command will not exit unlock bypass mode.

## **READ CFI Command**

The READ CFI (98h) command puts the device in read CFI mode and is only valid when the device is in read array or auto select mode. One bus WRITE cycle is required to issue the command.

Once in read CFI mode, bus READ operations will output data from the CFI memory area (Refer to the Common Flash Interface for details).

Read CFI mode is exited by performing a READ/RESET command (F0h). The device returns to read mode unless it entered read CFI mode after an ERASE SUSPEND or PRO-GRAM SUSPEND command, in which case it returns to erase or program suspend mode.

### **AUTO SELECT Command**

At power-up or after a hardware reset, the device is in read mode. It can then be put in auto select mode by issuing an AUTO SELECT (90h) command. Auto select mode enables the following device information to be read:

- Electronic signature, which includes manufacturer and device code information as shown in the Electronic Signature table.

- Block protection, which includes the block protection status and extended memory block protection indicator, as shown in the Block Protection table.

Electronic signature or block protection information is read by executing a READ operation with control signals and addresses set, as shown in the Read Electronic Signature table or the Block Protection table, respectively. In addition, this device information can be read or set by issuing an AUTO SELECT command.

Auto select mode can be used by the programming equipment to automatically match a device with the application code to be programmed.

Three consecutive bus WRITE operations are required to issue an AUTO SELECT command. The device remains in auto select mode until a READ/RESET or READ CFI command is issued.

### 1Gb: x16, 3V, MT28FW, Automotive Parallel NOR READ and AUTO SELECT Operations

The device cannot enter auto select mode when a PROGRAM or ERASE operation is in progress (RY/BY# LOW). However, auto select mode can be entered if the PROGRAM or ERASE operation has been suspended by issuing a PROGRAM SUSPEND or ERASE SUSPEND command.

Auto select mode is exited by performing a READ/RESET command (F0h). The device returns to read mode unless it entered auto select mode after an ERASE SUSPEND or PROGRAM SUSPEND command, in which case it returns to erase or program suspend mode.

#### **Table 9: Block Protection**

Note 1 applies to entire table

|                                                                                       |           |     |     | L A        | ddress li | nput |    | Data Input/Output  |

|---------------------------------------------------------------------------------------|-----------|-----|-----|------------|-----------|------|----|--------------------|

| READ Cycle                                                                            | CE#       | OE# | WE# | A[MAX:16]  | A[15:2]   | A1   | A0 | DQ[15:0]           |

| 128-bit (0x0~0x7) Factory-Programmable Extended Memory Protection Indicator (Bit DQ7) |           |     |     |            |           |      |    |                    |

| Low lock                                                                              | L         | L   | Н   | L          | L         | Н    | Н  | 0009h <sup>2</sup> |

|                                                                                       |           |     |     |            |           |      |    | 0089h <sup>3</sup> |

| High lock                                                                             | L         | L   | Н   | L          | L         | Н    | Н  | 0019h <sup>2</sup> |

|                                                                                       |           |     |     |            |           |      |    | 0099h <sup>3</sup> |

| Block protection                                                                      | on status |     |     |            |           |      |    |                    |

| Protected                                                                             | L         | L   | Н   | Block base | L         | Н    | L  | 0001h              |

| Unprotected                                                                           | L         | L   | Н   | address    | L         | Н    | L  | 0000h              |

Notes: 1. H = Logic level HIGH ( $V_{IH}$ ); L = Logic level LOW ( $V_{IL}$ ); X = HIGH or LOW.

- 2. Customer-lockable (default).

- 3. Micron prelocked.

## **Read Electronic Signature**

#### Table 10: Read Electronic Signature – 1Gb

Note 1 applies to entire table

|                   |     |     |     | A        | ddress | Input |    |    | Data Input/<br>Output |

|-------------------|-----|-----|-----|----------|--------|-------|----|----|-----------------------|

| READ Cycle        | CE# | OE# | WE# | A[MAX:4] | A3     | A2    | A1 | A0 | DQ[15:0]              |

| Manufacturer code | L   | L   | Н   | L        | L      | L     | L  | L  | 0089h                 |

| Device code 1     | L   | L   | Н   | L        | L      | L     | L  | Н  | 227Eh                 |

| Device code 2     | L   | L   | Н   | L        | Н      | Н     | Н  | L  | 2228h                 |

| Device code 3     | L   | L   | Н   | L        | Н      | Н     | Н  | Н  | 2201h                 |

Note: 1. H = Logic level HIGH ( $V_{IH}$ ); L = Logic level LOW ( $V_{IL}$ ); X = HIGH or LOW.

## **Cyclic Redundancy Check Operation**

## **CYCLIC REDUNDANCY CHECK Command**

The CYCLIC REDUNDANCY CHECK (CRC) command is a nonsecure hash function designed to detect accidental changes to raw data. Typically, it is used in digital networks and storage devices such as hard disk drives. A CRC-enabled device calculates a short, fixed-length binary sequence known as the CRC code (or CRC). The device CRC operation will generate the CRC result of the whole device or of an address range specified by the operation. Then the CRC result is compared with the expected CRC data provided in the sequence. Finally, the device indicates a pass or fail through the data polling register. If the CRC fails, corrective action is possible, such as re-verifying with a normal READ mode or rewriting the array data.

CRC is a higher performance alternative to reading data directly to verify recently programmed data, or as a way to periodically check the data integrity of a large block of data against a stored CRC reference over the life of the product.

CRC helps improve test efficiency for programmer or burn-in stress tests. No system hardware changes are required to enable CRC.

The CRC-64 operation follows the ECMA standard; the generating polynomial is:

$G(x) = x^{64} + x^{62} + x^{57} + x^{55} + x^{54} + x^{53} + x^{52} + x^{47} + x^{46} + x^{45} + x^{40} + x^{39} + x^{38} + x^{37} + x^{35} + x^{33}$

$+ x^{32} + x^{31} + x^{29} + x^{27} + x^{24} + x^{23} + x^{22} + x^{21} + x^{19} + x^{17} + x^{13} + x^{12} + x^{10} + x^9 + x^7 + x^4 + x + 1$

**Note:** The data stream sequence is from LSB to MSB and the default initial CRC value is all zeros.

The CRC command sequences are shown in the tables below, for an entire die or for a selected range, respectively.

## **Cyclic Redundancy Check Operation Command Sequence**

#### Table 11: Command Sequence – Range of Blocks

| Address | DQ[15:0] | Description                         | Notes |

|---------|----------|-------------------------------------|-------|

| 0000555 | 00AAh    | UI unlock cycle 1                   |       |

| 00002AA | 0055h    | UI unlock cycle 2                   |       |

| 0000000 | 00EBh    | Extended function interface command |       |

| 0000000 | 0027h    | CRC sub-op code                     |       |

| 0000000 | 000Ah    | N-1 data count                      |       |

| 0000000 | FFFEh    | CRC operation option data           |       |

| 0000001 | Data     | 1st word of 64-bit expected CRC     |       |

| 0000002 | Data     | 2nd word of 64-bit expected CRC     |       |

| 0000003 | Data     | 3rd word of 64-bit expected CRC     |       |

| 0000004 | Data     | 4th word of 64-bit expected CRC     |       |

Note 1 and 2 apply to entire table

#### Table 11: Command Sequence – Range of Blocks (Continued)

Note 1 and 2 apply to entire table.

| Address | DQ[15:0]                         | Description                                          | Notes |

|---------|----------------------------------|------------------------------------------------------|-------|

| 0000005 | DQ15 = A14                       | Byte address to start                                | 3     |

|         | DQ14 = A13                       |                                                      |       |

|         |                                  |                                                      |       |

|         | DQ2 = A1                         |                                                      |       |

|         | DQ1 = A0                         |                                                      |       |

|         | DQ0 = set to zero                |                                                      |       |

| 0000006 | A <sub>30</sub> -A <sub>15</sub> | Byte address to start                                | 3     |

| 000007  | Reserved                         | Default as 0000h                                     |       |

| 000008  | DQ15 = A14                       | Byte address to stop                                 | 3     |

|         | DQ14 = A13                       |                                                      |       |

|         |                                  |                                                      |       |

|         | DQ2 = A1                         |                                                      |       |

|         | DQ1 = A0                         |                                                      |       |

|         | DQ0 = set to zero                |                                                      |       |

| 0000009 | A <sub>30</sub> -A <sub>15</sub> | Byte address to stop                                 | 3     |

| 000000A | Reserved                         | Default as 0000h                                     |       |

| 0000000 | 0029h                            | Confirm command                                      |       |

| 0000000 | Read                             | Continue data polling to wait for device to be ready |       |

Notes: 1. If the CRC check fails, a check error is generated by setting DQ5 = 1.

- 2. This is a byte-aligned operation.

- 3. The stop address must be bigger than the start address; otherwise, the algorithm will take no action.

## 1Gb: x16, 3V, MT28FW, Automotive Parallel NOR Cyclic Redundancy Check Operation

#### **Table 12: Command Sequence – Entire Chip**

| Address | DQ[15:0] | Description                                          |

|---------|----------|------------------------------------------------------|

| 0000555 | 00AAh    | UI unlock cycle 1                                    |

| 00002AA | 0055h    | UI unlock cycle 2                                    |

| 0000000 | 00EBh    | Extended function interface command                  |

| 0000000 | 0027h    | CRC sub-op code                                      |

| 0000000 | 0004h    | N-1 data count                                       |

| 0000000 | FFFFh    | CRC operation option data                            |

| 0000001 | Data     | 1st word of 64-bit expected CRC                      |

| 0000002 | Data     | 2nd word of 64-bit expected CRC                      |

| 0000003 | Data     | 3rd word of 64-bit expected CRC                      |

| 0000004 | Data     | 4th word of 64-bit expected CRC                      |

| 0000000 | 0029h    | Confirm command                                      |

| 0000000 | Read     | Continue data polling to wait for device to be ready |

Note: 1. Applies to entire table: If the CRC check fails, a check error is generated by setting DQ5 = 1.

## **Bypass Operations**

## **UNLOCK BYPASS Command**

The UNLOCK BYPASS (20h) command is used to place the device in unlock bypass mode. Three bus WRITE operations are required to issue the UNLOCK BYPASS command.

When the device enters unlock bypass mode, the two initial UNLOCK cycles required for a standard PROGRAM or ERASE operation are not needed, thus enabling faster total program or erase time.

The UNLOCK BYPASS command is used in conjunction with UNLOCK BYPASS PRO-GRAM or UNLOCK BYPASS ERASE commands to program or erase the device faster than with standard PROGRAM or ERASE commands. Using these commands can save considerable time when the cycle time to the device is long. When in unlock bypass mode, only the following commands are valid:

- The UNLOCK BYPASS PROGRAM command can be issued to program addresses within the device.

- The UNLOCK BYPASS BLOCK ERASE command can then be issued to erase one or more memory blocks.

- The UNLOCK BYPASS CHIP ERASE command can be issued to erase the whole memory array.

- The UNLOCK BYPASS WRITE TO BUFFER PROGRAM and UNLOCK BYPASS EN-HANCED WRITE TO BUFFER PROGRAM commands can be issued to speed up the programming operation.

- The UNLOCK BYPASS RESET command can be issued to return the device to read mode.

In unlock bypass mode, the device can be read as if in read mode.

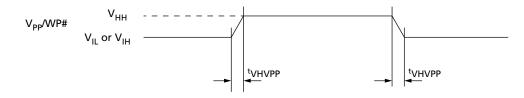

In addition to the UNLOCK BYPASS command, when  $V_{PP}/WP\#$  is raised to  $V_{HH}$ , the device automatically enters unlock bypass mode. When  $V_{PP}/WP\#$  returns to  $V_{IH}$  or  $V_{IL}$ , the device is no longer in unlock bypass mode, and normal operation resumes. The transitions from  $V_{IH}$  to  $V_{HH}$  and from  $V_{HH}$  to  $V_{IH}$  must be slower than <sup>t</sup>VHVPP. (See the Accelerated Program, Data Polling/Toggle AC Characteristics.)

**Note:** Micron recommends entering and exiting unlock bypass mode using the ENTER UNLOCK BYPASS and UNLOCK BYPASS RESET commands rather than raising  $V_{PP}$ /WP# to  $V_{HH}$ .  $V_{PP}$ /WP# should never be raised to  $V_{PPH}$  from any mode except read mode; otherwise, the device may be left in an indeterminate state.  $V_{PP}$ /WP# should not remain at  $V_{HH}$  for than 80 hours cumulative.

## **UNLOCK BYPASS RESET Command**

The UNLOCK BYPASS RESET (90/00h) command is used to return to read/reset mode from unlock bypass mode. Two bus WRITE operations are required to issue the UN-LOCK BYPASS RESET command. The READ/RESET command does not exit from unlock bypass mode.

## **Program Operations**

## **PROGRAM Command**

The PROGRAM (A0h) command can be used to program a value to one address in the memory array. The command requires four bus WRITE operations, and the final WRITE operation latches the address and data in the internal state machine and starts the program/erase controller. After programming has started, bus READ operations output the data polling register content.

Programming can be suspended and then resumed by issuing a PROGRAM SUSPEND command and a PROGRAM RESUME command, respectively.

If the address falls in a protected block, the PROGRAM command is ignored, and the data remains unchanged. The data polling register is not read, and no error condition is given.

After the PROGRAM operation has completed, the device returns to read mode, unless an error has occurred. When an error occurs, bus READ operations to the device continue to output the data polling register. A READ/RESET command must be issued to reset the error condition and return the device to read mode.

The PROGRAM command cannot change a bit set to 0 back to 1, and an attempt to do so is masked during a PROGRAM operation. Instead, an ERASE command must be used to set all bits in one memory block or in the entire memory from 0 to 1.

The PROGRAM operation is aborted by performing a hardware reset or by powering down the device. In this case, data integrity cannot be ensured, and it is recommended that the words or bytes that were aborted be reprogrammed.

### UNLOCK BYPASS PROGRAM Command