# **Automotive SPI Communication Interface (ASCI)**

## **General Description**

The MAX17841B ASCI combines an SPI port with a universal asynchronous receiver transmitter (UART) specially designed to interface with Maxim battery management devices.

The UART can be configured to automatically performManchesterencoding/decoding, message framing, parity, wake-up, and keep-alive signaling as required for Maxim's battery management UART protocol.

The UART has programmable baud rates of 0.5Mbps, 1Mbps, or 2Mbps and supports either single-ended or differential signaling. For host efficiency, the UART contains a 28-byte transmit buffer and a 62-byte receive buffer with host-configurable interrupt events.

## **Applications**

- Battery Management Systems (BMS)

- Electric and Hybrid Vehicles (EV/HEV)

- Energy Storage Systems (ESS)

### **Benefits and Features**

- Supports Maxim's Battery Management UART Protocol

- SPI Interface Up to 4MHz

- UART Baud Rate Programmable Up to 2Mbps

- 3.3V or 5V Operation

- Ultra-Low Quiescent Current

- Transmit and Receive Buffers with Programmable Interrupts Allow for Queuing of UART Messages

- Manchester Encoder and Decoder Reduces Host Controller Burden

- Operating Temperature Range from -40°C to +105°C (AEC-Q100 Type 2)

- Supports ASIL Requirements

Ordering Information appears at end of data sheet.

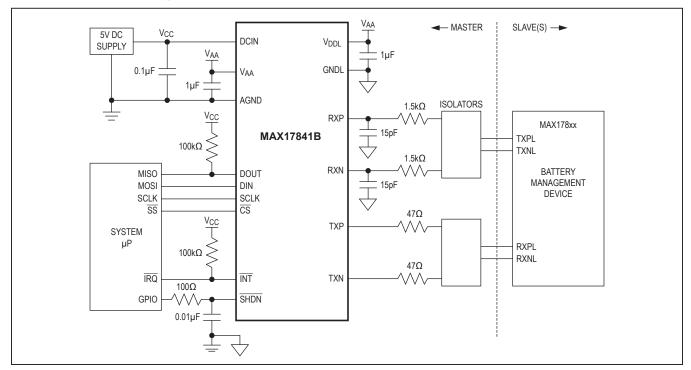

## **Simplified Operating Circuit**

## **Absolute Maximum Ratings**

| DCIN to AGND               | 0.3V to +6V                        |

|----------------------------|------------------------------------|

| V <sub>AA</sub> to AGND    | 0.3V to +4V                        |

| V <sub>DDL</sub> to GNDL   | 0.3V to +4V                        |

| AGND to GNDL               | 0.3V to +0.3V                      |

| TXP, TXN to GNDL           | 0.3V to (V <sub>DDI</sub> + 0.3V)  |

| DOUT to GNDL               | 0.3V to (V <sub>DCIN</sub> + 0.3V) |

| CTG to AGND                |                                    |

| SHDN to AGND               | 0.3V to (V <sub>DCIN</sub> + 0.3V) |

| CS, DIN, SCLK, INT to GNDL | 0.3V to +6V                        |

| RXP, RXN to GNDL           | 30V to +30V                        |

Soldering Lead Temperature for 10s.....+300°C

Note 1: Average power for time period  $\tau$  where  $\tau$  is the time constant (in  $\mu$ s) of the transient diode current during a hot-plug event. For, example, if  $\tau$  is 330 $\mu$ s, the maximum average power is 0.793W. Peak current must never exceed 2A. Actual average power during hot-plug must be calculated from the diode current waveform for the application circuit and compared to the maximum rating.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **Electrical Characteristics**

$(V_{DCIN} = 5V, V_{AA} = V_{DDL} = 3.3V, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted, where  $T_{MIN} = -40$ °C and  $T_{MAX} = +105$ °C. Typical values are at  $T_A = +25$ °C. Operation is with the recommended application circuit.)

| PARAMETER                         | SYMBOL               | C                                                                                                                     | ONDITIONS                                                         | MIN  | TYP  | MAX                   | UNITS |

|-----------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|------|------|-----------------------|-------|

| POWER REQUIREMENTS                |                      |                                                                                                                       |                                                                   | •    |      |                       |       |

| Supply Voltage                    | \/                   | V <sub>DCIN</sub> = V <sub>AA</sub> =                                                                                 | $V_{DCIN} = V_{AA} = V_{DDL} = 3.3V$ nominal                      |      | 3.3  | 3.5                   | V     |

| Supply Voltage                    | V <sub>DCIN</sub>    | V <sub>DCIN</sub> = 5V no                                                                                             | minal; V <sub>AA</sub> = V <sub>DDL</sub>                         | 4.5  | 5.0  | 5.5                   | V     |

|                                   |                      | \/                                                                                                                    | $V_{DCIN} = V_{AA} = 3.3V$                                        |      | 4    | 10                    |       |

|                                   | ISHUTDOWN            | $V_{\overline{SHDN}} = 0V$                                                                                            | V <sub>DCIN</sub> = 5V                                            |      | 1    | 10                    | μA    |

| Supply Current                    | ISTANDBY             | SHDN high, f <sub>SC</sub>                                                                                            | CLK = 0, f <sub>UART</sub> = 0                                    | 1.0  | 2.3  | 5.0                   |       |

| одруу санон                       | IACTIVE              | Continuous SPI writes at 4MHz, 50pF<br>TXP load, 50pF TXN load, f <sub>UART</sub> =<br>2Mbps, Transmit Preambles mode |                                                                   | 1.0  | 4    | 6                     | mA    |

| REGULATOR                         |                      |                                                                                                                       |                                                                   | ,    |      |                       |       |

| Output Voltage                    | V <sub>AA</sub>      |                                                                                                                       | 0mA < I <sub>VAA</sub> < 10mA,<br>4.5V < V <sub>DCIN</sub> < 5.5V |      | 3.30 | 3.46                  | V     |

| Short-Circuit Current             | I <sub>AASC</sub>    | V <sub>AA</sub> = AGND                                                                                                |                                                                   | 13.0 | 26.0 | 120.0                 | mA    |

| DOD Three-bald                    | VAARESET             | V <sub>AA</sub> falling                                                                                               |                                                                   | 2.8  | 2.9  | 3.0                   | V     |

| POR Threshold                     | V <sub>AAVALID</sub> | V <sub>AA</sub> rising                                                                                                |                                                                   | 2.9  | 3.0  | 3.1                   | V     |

| POR Hysteresis                    | VAAHYS               |                                                                                                                       |                                                                   |      | 40.0 | 100                   | mV    |

| LOGIC INPUTS (SHDN, CS, DI        | N, SCLK)             |                                                                                                                       |                                                                   |      |      |                       |       |

| Pulldown Resistance (CS)          | RCS                  | V <sub>CS</sub> = 5V                                                                                                  |                                                                   | 5.5  | 12   | 28.8                  | ΜΩ    |

| Pulldown Resistance (SHDN)        | R <sub>SHDN</sub>    | V <sub>SHDN</sub> = 5V                                                                                                |                                                                   | 0.75 | 1.5  | 3.0                   | ΜΩ    |

| Input Leakage Current (DIN, SCLK) | I <sub>LKG</sub>     | V <sub>DIN</sub> , V <sub>SCLK</sub> = 0V                                                                             |                                                                   | -1.0 |      | +1.0                  | μA    |

| Input Low Threshold               | V <sub>IL</sub>      |                                                                                                                       |                                                                   |      | 0.   | 3 x V <sub>DCIN</sub> | V     |

| Input High Threshold              | V <sub>IH</sub>      | 0.7 x V <sub>DCIN</sub>                                                                                               |                                                                   |      | V    |                       |       |

## **Electrical Characteristics (continued)**

$(V_{DCIN} = 5V, V_{AA} = V_{DDL} = 3.3V, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted, where  $T_{MIN} = -40$ °C and  $T_{MAX} = +105$ °C. Typical values are at  $T_A = +25$ °C. Operation is with the recommended application circuit.)

| PARAMETER                                  | SYMBOL                | CONDITIONS                                          | MIN                                 | TYP                 | MAX                             | UNITS |

|--------------------------------------------|-----------------------|-----------------------------------------------------|-------------------------------------|---------------------|---------------------------------|-------|

| LOGIC OUTPUTS (DOUT, INT)                  |                       |                                                     |                                     |                     |                                 |       |

| Output Leakage Current                     | I <sub>LKG</sub>      | V <sub>DOUT</sub> = 0 and 5V, V <sub>INT</sub> = 5V | -1.0                                |                     | +1.0                            | μA    |

| Output Low Voltage                         | V <sub>OL</sub>       | I <sub>OL</sub> = -2mA                              |                                     |                     | V <sub>GNDL</sub> + 0.4         | V     |

| Output High Voltage (DOUT)                 | V <sub>OH</sub>       | I <sub>OH</sub> = 2mA                               | V <sub>DCIN</sub><br>- 0.4          |                     |                                 | V     |

| POWER AND GROUND FAULT                     | DETECTION             |                                                     | ,                                   |                     |                                 |       |

| Open Detection Voltage (V <sub>DDL</sub> ) | V <sub>VDDLALRT</sub> | V <sub>AA</sub> = 3.3V                              | 2.8                                 | 3.0                 |                                 | V     |

| Open Detection Voltage (GNDL)              | V <sub>GNDLALRT</sub> | V <sub>AGND</sub> = 0V                              |                                     | 0.13                | 0.25                            | V     |

| Open Detection Voltage (AGND)              | V <sub>AGNDALRT</sub> | V <sub>GNDL</sub> = 0V                              |                                     | 0.13                | 0.25                            | V     |

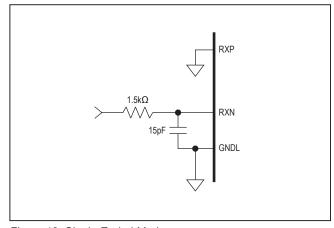

| UART INPUTS (RXP, RXN)                     |                       |                                                     | ·                                   |                     |                                 |       |

| RXP Input Voltage                          | V <sub>RXP</sub>      |                                                     | V <sub>GNDL</sub><br>- 28           |                     | V <sub>GNDL</sub><br>+ 28       | V     |

| RXN Input Voltage                          | V <sub>RXN</sub>      |                                                     | V <sub>GNDL</sub><br>- 28           |                     | V <sub>GNDL</sub><br>+ 28       | V     |

| Differential Input High Threshold          | V <sub>TH</sub>       | (Note 2)                                            | V <sub>DDL</sub> /2<br>-<br>400mV   | V <sub>DDL</sub> /2 | V <sub>DDL</sub> /2 +<br>400mV  | V     |

| Differential Input Zero-Crossing Threshold | V <sub>ZC</sub>       | (Note 2)                                            | -400                                | 0                   | +400                            | mV    |

| Differential Input Low Threshold           | V <sub>TL</sub>       | (Note 2)                                            | -V <sub>DDL</sub> /<br>2 -<br>400mV | -V <sub>DDL</sub> / | -V <sub>DDL</sub> /2<br>+ 400mV | V     |

| Differential Input Hysteresis              | V <sub>HYST</sub>     | (Note 2)                                            | 25                                  | 75                  | 150                             | mV    |

| Common-Mode Voltage Bias                   | V <sub>CM</sub>       |                                                     | V <sub>DDL</sub> /3<br>- 0.1        | V <sub>DDL</sub> /3 | V <sub>DDL</sub> /3<br>+ 0.1    | V     |

| Input Capacitance                          | C <sub>IN</sub>       |                                                     |                                     | 2                   |                                 | pF    |

| Leakage Current                            | I <sub>LKG</sub>      |                                                     | -30                                 |                     | +30                             | μA    |

| Input Resistance to V <sub>CM</sub>        | R <sub>RXIN</sub>     |                                                     |                                     | 1.1                 |                                 | ΜΩ    |

| UART OUTPUTS (TXP, TXN)                    |                       |                                                     |                                     |                     |                                 |       |

| Output Low Voltage                         | V <sub>OL</sub>       | I <sub>OL</sub> = -20mA                             |                                     |                     | V <sub>GNDL</sub> + 0.4         | V     |

| Output High Voltage                        | V <sub>OH</sub>       | I <sub>OH</sub> = 20mA                              | V <sub>DDL</sub> - 0.4              |                     |                                 | V     |

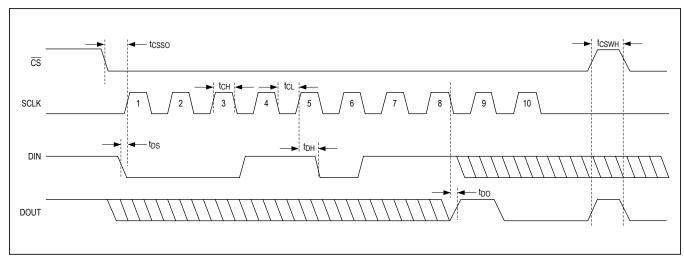

| SPI TIMING                                 |                       | ,                                                   | 1                                   |                     |                                 |       |

| SCLK Frequency                             | f <sub>SCLK</sub>     |                                                     |                                     |                     | 4                               | MHz   |

| CS to SCLK Setup Time                      | tcss                  |                                                     | 250                                 |                     |                                 | ns    |

| CS High Pulse Width                        | tcswh                 |                                                     | 200                                 |                     |                                 | ns    |

| SCLK High Time                             | t <sub>CH</sub>       |                                                     | 100                                 |                     |                                 | ns    |

| SCLK Low Time                              | t <sub>CL</sub>       |                                                     | 100                                 |                     |                                 | ns    |

## **Electrical Characteristics (continued)**

$(V_{DCIN} = 5V, V_{AA} = V_{DDL} = 3.3V, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted, where  $T_{MIN} = -40$ °C and  $T_{MAX} = +105$ °C. Typical values are at  $T_A = +25$ °C. Operation is with the recommended application circuit.)

| PARAMETER                                                 | SYMBOL                  | CONDITIONS                  | MIN                  | TYP   | MAX                  | UNITS              |

|-----------------------------------------------------------|-------------------------|-----------------------------|----------------------|-------|----------------------|--------------------|

| SCLK Fall to DOUT Valid                                   | t <sub>DO</sub>         |                             |                      |       | 30                   | ns                 |

| DIN to SCLK Setup Time                                    | t <sub>DS</sub>         |                             | 10                   |       |                      | ns                 |

| DIN to SCLK Hold Time                                     | t <sub>DH</sub>         |                             | 30                   |       |                      | ns                 |

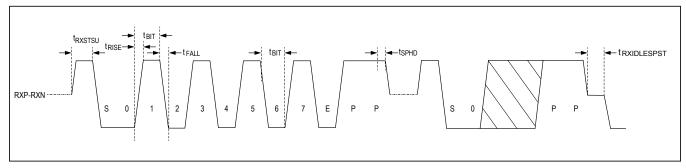

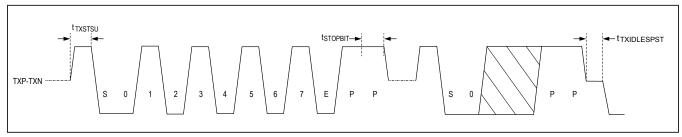

| UART TIMING                                               |                         |                             |                      |       |                      |                    |

| Dit Davied Franch for Consul                              |                         | f <sub>UART</sub> = 2Mbps   |                      | 8     |                      |                    |

| Bit Period Except for Second STOP Bit (Notes 3, 4)        | t <sub>BIT</sub>        | f <sub>UART</sub> = 1Mbps   |                      | 16    |                      | 1/f <sub>OSC</sub> |

| Creation Distriction Creation                             |                         | f <sub>UART</sub> = 0.5Mbps |                      | 32    |                      |                    |

|                                                           |                         | f <sub>UART</sub> = 2Mbps   |                      | 9     |                      |                    |

| Second STOP Bit Period (Notes 3, 4)                       | tSTOPBIT                | f <sub>UART</sub> = 1Mbps   |                      | 18    |                      | 1/f <sub>OSC</sub> |

| (140103 0, 4)                                             |                         | f <sub>UART</sub> = 0.5Mbps |                      | 36    |                      |                    |

|                                                           |                         | f <sub>UART</sub> = 2Mbps   | 0                    |       | 8                    |                    |

| Rx Idle to START Setup Time (Notes 3, 4)                  | t <sub>RXSTSU</sub>     | f <sub>UART</sub> = 1Mbps   | 0                    |       | 16                   | 1/f <sub>OSC</sub> |

| (110165 3, 4)                                             |                         | f <sub>UART</sub> = 0.5Mbps | 0                    |       | 32                   |                    |

|                                                           |                         | f <sub>UART</sub> = 2Mbps   |                      | 8     |                      |                    |

| Tx Idle to START Setup Time (Notes 3, 4)                  | ttxstsu                 | f <sub>UART</sub> = 1Mbps   |                      | 16    |                      | 1/f <sub>OSC</sub> |

|                                                           |                         | f <sub>UART</sub> = 0.5Mbps |                      | 32    |                      |                    |

| STOP Hold Time to Idle<br>(Notes 3, 4)                    | <sup>t</sup> SPHD       |                             |                      |       | 4                    | 1/f <sub>OSC</sub> |

|                                                           |                         | f <sub>UART</sub> = 2Mbps   | 8                    |       |                      |                    |

| Rx Minimum Idle Time (STOP Bit to START Bit) (Notes 3, 4) | t <sub>RXIDLESPST</sub> | f <sub>UART</sub> = 1Mbps   | 16                   |       |                      | 1/f <sub>OSC</sub> |

| bit to START bit) (Notes 5, 4)                            |                         | f <sub>UART</sub> = 0.5Mbps | 32                   |       |                      |                    |

| Tx Minimum Idle Time (Notes 3, 4)                         | t <sub>TXIDLESPST</sub> |                             | 10                   |       |                      | 1/f <sub>OSC</sub> |

|                                                           |                         | f <sub>UART</sub> = 2Mbps   |                      |       | 4                    |                    |

| Rx Fall Time (Notes 3–5)                                  | tFALL                   | f <sub>UART</sub> = 1Mbps   |                      |       | 8                    | 1/f <sub>OSC</sub> |

|                                                           |                         | f <sub>UART</sub> = 0.5Mbps |                      |       | 16                   |                    |

|                                                           |                         | f <sub>UART</sub> = 2Mbps   |                      |       | 4                    |                    |

| Rx Rise Time (Notes 3–5)                                  | t <sub>RISE</sub>       | f <sub>UART</sub> = 1Mbps   |                      |       | 8                    | 1/f <sub>OSC</sub> |

| . ,                                                       |                         | f <sub>UART</sub> = 0.5Mbps |                      |       | 16                   |                    |

| Startup Time (SHDN High to RXP Valid)                     | tSTARTUP                | -                           |                      | 800   | 2000                 | μs                 |

| Oscillator Frequency                                      | fosc                    |                             | 15.68                | 16.00 | 16.32                | MHz                |

| UART MESSAGE TIMING                                       | ·                       |                             |                      |       |                      |                    |

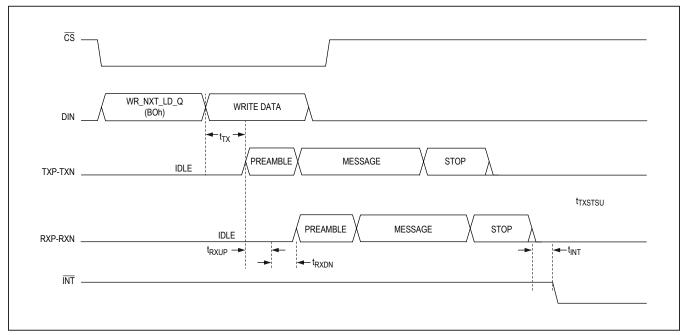

| SPI Command to Tx Valid Delay (Note 6)                    | t <sub>TX</sub>         |                             | 4 x t <sub>BIT</sub> |       | 5 x t <sub>BIT</sub> |                    |

## **Electrical Characteristics (continued)**

$(V_{DCIN} = 5V, V_{AA} = V_{DDL} = 3.3V, T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted, where  $T_{MIN} = -40$ °C and  $T_{MAX} = +105$ °C. Typical values are at  $T_A = +25$ °C. Operation is with the recommended application circuit.)

| PARAMETER                                                               | SYMBOL             | CONDITIONS | MIN | TYP | MAX                                                      | UNITS |

|-------------------------------------------------------------------------|--------------------|------------|-----|-----|----------------------------------------------------------|-------|

| Tx Valid to Rx Valid Up Stack Delay (Note 7)                            | t <sub>RXUP</sub>  |            |     |     | n x<br>t <sub>PROP</sub>                                 |       |

| Tx Valid to Rx Valid Down Stack Delay (Note 7)                          | t <sub>RXDN</sub>  |            |     |     | n x<br>t <sub>PROP</sub>                                 |       |

| End of STOP Character to RX_Stop_INT Flag True (Note 8)                 | t <sub>INT</sub>   |            |     |     | 2 x t <sub>BIT</sub>                                     |       |

| SPI START to UART Slave<br>Device Register Write Delay<br>(Notes 9, 10) | <sup>t</sup> REGWR |            |     | 130 | fsclk +<br>0 x t <sub>BIT</sub> +<br>x t <sub>PROP</sub> |       |

- Note 2: Differential signal (V<sub>RXP</sub> V<sub>RXN</sub>) where V<sub>RXP</sub>, V<sub>RXN</sub> do not exceed a common-mode voltage range of ±25V.

- Note 3: All parameters measured based on differential signal.

- Note 4: Guaranteed by design and not production tested.

- Note 5: Fall time measured 90% to 10%, rise time measured 10% to 90%.

- Note 6: Measured from falling edge of 8th SCLK cycle of the WR NXT LD Q SPI command byte (B0h).

- Note 7: tpROP is the maximum propagation delay through a slave device in a given direction. Refer to the UART slave device data sheet for the actual delay. The number of UART slave devices is denoted by n.

- Note 8: Measured from end of 12th bit of stop character.

- Note 9: Parameter t<sub>REGWR</sub> is the minimum amount of time needed to write a register in the nth slave device of the daisy-chain. It is measured from the start of the SPI transaction WR\_NXT\_LD\_Q (B0h) that initiates transmission of a WRITEALL message to when the nth device receives a valid WRITEALL message. For example, for 4MHz SPI frequency, 2Mbps UART baud rate, n = 10 and t<sub>PROP</sub> = 3 x t<sub>BIT</sub>, t<sub>REGWR</sub> = 2µs + 65µs + 15µs = 82µs.

- Note 10:Computation of t<sub>REGWR</sub> consists of three terms: 1) duration of the SPI transaction, 2) partial duration of the UART message, and 3) propagation delay of the UART message. The first term equals the number of bits in the SPI transaction (8) x the SPI bit time (1 / f<sub>SCLK</sub>). The second term equals the time from the start of the WRITEALL message to the first STOP bit of the last PEC nibble. The last PEC nibble is the 11th character in the message. With each character lasting 12 UART bit times, there are 11 x 12 = 132 bit times from the start of the message to the end of the last PEC nibble. Since the write occurs just before the two STOP bits of the 11th character, the term is actually 130 x t<sub>BIT</sub>. The third term is the propagation delay required for the WRITEALL message to get to the nth device.

Figure 1. SPI Timing Diagram (Example of Reading Register 0x1B with Data 80h and Transaction Terminated Prematurely)

Figure 2. Receive UART Timing

Figure 3. Transmit UART Timing

Figure 4. UART Message Timing

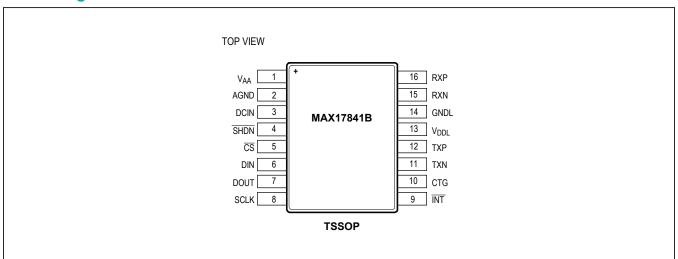

# **Pin Configuration**

# **Pin Description**

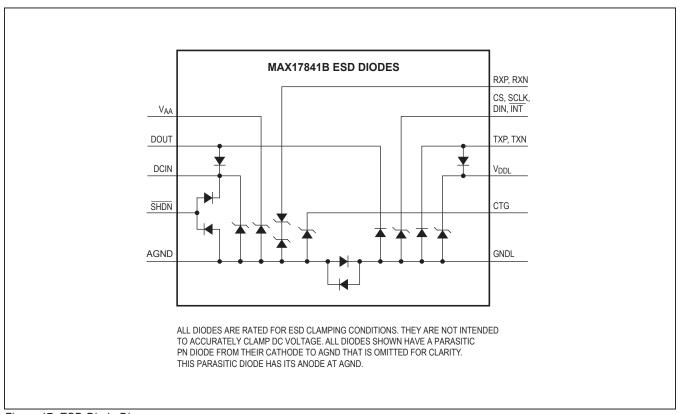

| PIN | NAME            | FUNCTION | DESCRIPTION                                                                                                                                                                                                                    |

|-----|-----------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | V <sub>AA</sub> | Power    | Power Output for LDO Regulator (5V Mode Only) and Supply for Oscillator. For 5V mode, connect to V <sub>DDL</sub> . For 3.3V mode, connect this pin to 3.3V supply. Decouple per application circuit.                          |

| 2   | AGND            | Ground   | Analog Ground. Connect to the power supply ground.                                                                                                                                                                             |

| 3   | DCIN            | Power    | Power Input for LDO Regulator and SPI Port. For 5V mode, connect to 5V supply. For 3.3V mode, connect this pin to 3.3V supply. Decouple per application circuit.                                                               |

| 4   | SHDN            | Input    | Active-Low Shutdown Input. Connect to host GPIO. Assert to place device in shutdown mode. In this mode, the regulator is disabled and the device is reset. This pin has a $1.5 \text{M}\Omega$ internal pulldown. 5V tolerant. |

| 5   | <del>CS</del>   | Input    | Active-Low SPI Chip-Select Input. Connect to the Slave_Select output of the SPI master. Assert to enable the SPI port. This pin has a 12MΩ internal resistor to ground. 5V tolerant.                                           |

| 6   | DIN             | Input    | SPI Data Input. Connect to DOUT/MOSI output of SPI master. 5V tolerant.                                                                                                                                                        |

| 7   | DOUT            | Output   | SPI Data Output. Connect to DIN/MISO input of SPI master. This output is three-stated when $\overline{CS}$ is deasserted. When $\overline{CS}$ is asserted, this pin is driven between DCIN and AGND supplies.                 |

| 8   | SCLK            | Input    | SPI Clock Input. Connect to SCLK output of SPI master. 5V tolerant.                                                                                                                                                            |

| 9   | ĪNT             | Output   | Active-Low, Open-Drain Interrupt Output. Connect a pullup resistor to this pin per application requirements. This pin is asserted if any interrupt flag is set.                                                                |

| 10  | CTG             | Ground   | Reserved for factory use. Connect to AGND.                                                                                                                                                                                     |

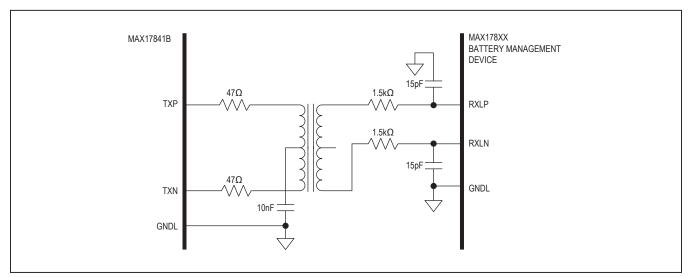

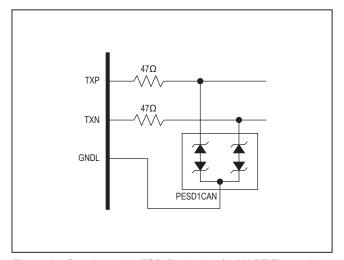

| 11  | TXN             | Output   | UART Transmitter Negative Output. Connect to Rx port negative input circuit of UART slave device per application circuit. This pin is driven between the V <sub>DDL</sub> and GNDL supplies.                                   |

| 12  | TXP             | Output   | UART Transmitter Positive Output. Connect to Rx port positive input circuit of UART slave device per application circuit. This pin is driven between the V <sub>DDL</sub> and GNDL supplies.                                   |

| 13  | $V_{DDL}$       | Power    | 3.3V Digital and UART Port Power. Connect to V <sub>AA</sub> . Decouple per application circuit.                                                                                                                               |

| 14  | GNDL            | Ground   | Digital and UART Port Ground. Connect to AGND.                                                                                                                                                                                 |

| PIN | NAME | FUNCTION | DESCRIPTION                                                                                                    |

|-----|------|----------|----------------------------------------------------------------------------------------------------------------|

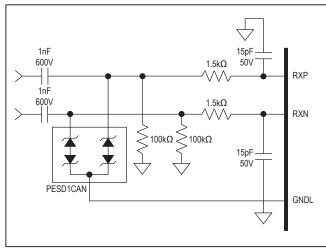

| 15  | RXN  | Output   | UART Receiver Negative Input. Connect to Tx port negative output of UART slave device per application circuit. |

| 16  | RXP  | Output   | UART Receiver Positive Input. Connect to Tx port positive output of UART slave device per application circuit. |

## **Detailed Description**

The MAX17841B allows any host controller with an SPI port to communicate with one or more battery management slave devices that use Maxim's battery management UART protocol.

**Table 1. Internal Power Distribution**

| BLOCK                      | SUPPLY    |

|----------------------------|-----------|

| Oscillator                 | $V_{AA}$  |

| SPI Port and LDO Regulator | DCIN      |

| Digital, UART, and Control | $V_{DDL}$ |

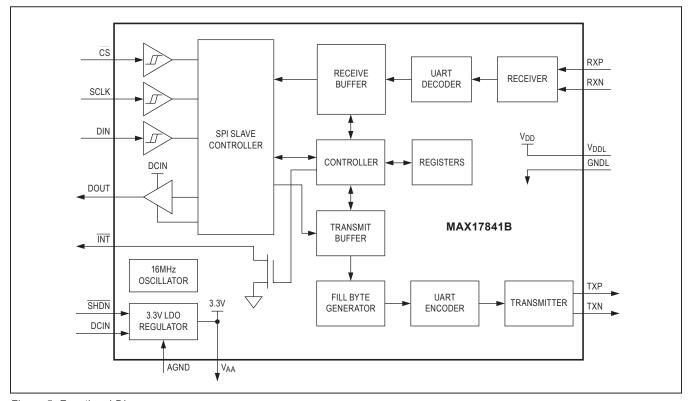

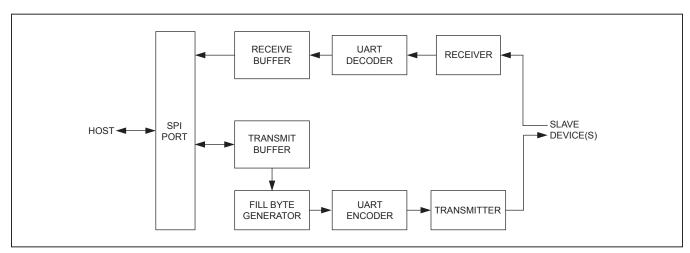

Together with the host controller, the ASCI is the master for communications with the slave devices. <u>Figure 5</u> shows the functional block diagram. <u>Table 1</u> shows how power is distributed inside the device.

### Serial Peripheral Interface (SPI)

The SPI port is a synchronous data link that the host uses to read and write the ASCI registers and the UART communication buffers.

#### **SPI Transactions**

An SPI transaction is initiated when the host drives the  $\overline{\text{CS}}$  pin low. The host always transmits data most-significant bit (MSB) first to the ASCI. After the first byte, it can termi-

Figure 5. Functional Diagram

nate the transaction (single-byte transaction), continue to clock data out (write transaction), or start clocking data in (read transaction). However, it does not send and receive data at the same time (half-duplex operation).

### **Register Transactions**

For register transactions, the host first sends a single-byte register address. Register addresses are either read-only (odd addresses) or write-only (even addresses). For a read transaction, the second byte is the read data sent by the ASCI to the host. For a write transaction, the second byte is the write data sent by the host to the ASCI. Multiple data bytes are allowed as long as  $\overline{\text{CS}}$  remains active-low—the ASCI automatically selects the next read-only register address (for reads) or the next write-only address (for writes). The SPI transaction is terminated when the host drives  $\overline{\text{CS}}$  high.

#### **Buffer Transactions**

Buffer transactions can consist of only a command byte, a command byte followed by one or more read bytes, or a command byte followed by one or more write bytes. All allowed transactions are specified in Table 9.

#### **SPI Timing**

The ASCI is only compatible with SPI mode 0 (CPOL = 0/CPHA = 0). In this mode, data is always driven on the falling edge of SCLK and is always sampled on the rising edge of SCLK.

For reads, the ASCI starts driving DOUT on the first falling edge of SCLK immediately after the ASCI samples the least-significant bit (LSB) of the command/address byte. DIN is a "don't care" while reading. Reads attempted beyond the address space return zero.

For writes, registers are written on the falling edge of SCLK, after the last bit is sampled. However, if  $\overline{\text{CS}}$  goes high before the last bit's falling edge of SCLK, that register is not written.

**Table 2. SPI Communication Summary**

| PARAMETER               | VALUE                                  |

|-------------------------|----------------------------------------|

| Communication Mode      | Half-duplex                            |

| Maximum Clock Frequency | 4MHz                                   |

| Bit Order               | Most-significant bit first             |

| Clock Polarity (CPOL)   | 0 (leading clock edge is rising edge)  |

| Clock Phase (CPHA)      | 0 (data sampled on leading clock edge) |

#### **UART Interface**

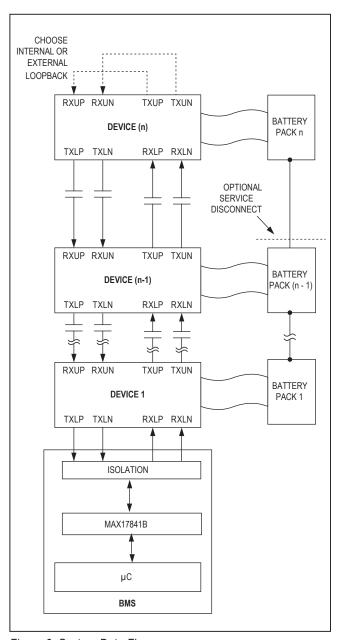

Slave devices that use Maxim's battery management UART protocol can be connected in daisy-chain fashion to manage a multiple battery-cell stack. In a BMS, or Battery Management System, the BMS controller is the host for all slave devices and initiates all communication. The data flow always starts from the host, goes up the daisy-chain and back down to the host as represented in Figure 6.

Figure 6. System Data Flow

### **Battery Management UART Protocol**

The ASCI uses a UART protocol specifically designed for Maxim battery management devices. This protocol uses the following features to maximize the integrity of the communications:

- All transmitted data are Manchester-encoded where each data bit is transmitted twice with the second bit inverted (G.E. Thomas convention).

- Every transmitted character contains 12 bits that include a START bit, a parity bit, and two STOP bits.

- Each message contains a CRC-8 packet errorchecking (PEC) byte

- Each message is framed by a preamble character and stop character.

- Each received message contains a data-check byte for verifying the integrity of the transmission.

The protocol is also designed to minimize power consumption by allowing slave devices to shut down if the data link is idle for a specified period of time. To prevent the unintentional shutdown of slave devices, the host should enable the ASCI's Keep-Alive mode to periodically transmit stop characters. The time period between stop characters is configurable by the host.

#### **UART Messages**

A message is defined as a sequence of UART characters. The message starts with a preamble character, followed by data characters, and ending with a stop character.

Each character consists of the following 12 bits:

- One START bit

- Eight data bits (LSB first)

- One parity bit (even)

- Two STOP bits

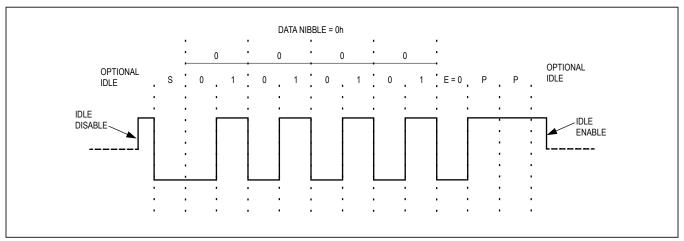

Each data byte is transmitted and received as two separate characters, one 12-bit character for each 4-bit data nibble. Each Manchester-encoded nibble actually requires eight data bits: four true bits and four inverted bits.

In its default configuration, when the ASCI transmits a message, it automatically performs the following functions:

- Frames the message with the required preamble character at the beginning of the message.

- Manchester encodes each data nibble and transmits each encoded nibble with the required START, parity, and STOP bits.

- Transmits the message at the configured baud rate of 0.5Mbps, 1Mbps, or 2Mbps.

- Frames the message with the required stop character at the end of the message.

These automatic functions can be disabled by enabling the following special transmit modes:

- Transmit No Preamble mode (eliminates preamble characters)

- Transmit No Stop mode (eliminates stop characters)

- Transmit Raw Data mode (transmits data with no Manchester encoding)

- Receive Raw Data mode (receives data as not Manchester encoded)

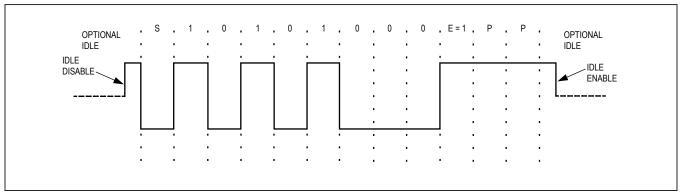

#### **Preamble Character**

The preamble is a framing character that the UART generates to signal the beginning of a message. It is transmitted as an unencoded 15h, but is still a DC-balanced character. If any bit(s) other than the STOP bits deviate from the unique preamble sequence, the character is not interpreted as a valid preamble, but rather as a data character.

Figure 7. UART Timing for a Preamble

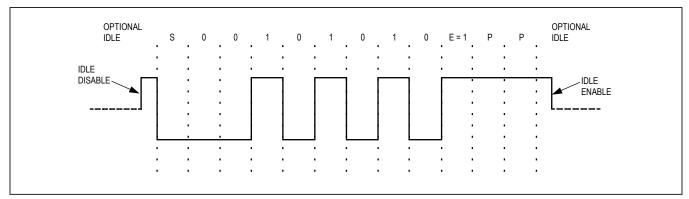

Figure 8. UART Timing for a Stop Character

Figure 9. UART Timing for a Manchester-Encoded Data Nibble 0h

#### **Stop Character**

The stop character is a framing character that the UART generates to signal the end of a message. It is transmitted as an unencoded 54h, but it is still a DC-balanced character.

#### **Manchester Encoding**

Each data byte is transmitted as two separate nibbles (four bits) that are Manchester-encoded. For each data bit, the first bit represents the information and the second bit is its complement. The parity is even so its value should always result in an even number of high bits. Since the data is Manchester-encoded and there are two STOP bits, the parity bit for data characters (but not framing characters) should always be zero.

## Automotive SPI Communication Interface (ASCI)

#### **Data Types**

Maxim's battery management UART protocol supports several different data types as described in <u>Table 3</u>. The ASCI does not interpret the significance of any of these data types. It is up to the host to both compose the data being transmitted and interpret the data being received. For example, the host must compute the proper PEC value for each transmitted message and must verify the PEC value on each received message.

#### **Assigning Slave Device Addresses**

The battery management UART protocol requires that the host assign a unique and contiguous address between 0 and 31 to each UART slave device so that the host can address each slave device individually as desired. The host performs this assignment by specifying a seed address in the HELLOALL command sequence. As the command propagates up the daisy-chain, each slave device assigns its own address. The HELLOALL sequence returns a value from which the host can determine the number of devices in the daisy-chain as well as the device addresses.

**Table 3. Message Data Types**

| DATA TYPE     | DESCRIPTION                                                                                                                                                                                                                                                                                                                         |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Command       | Defines the type of message, either a write command or a read command.                                                                                                                                                                                                                                                              |

| Address       | Register address to be read or written.                                                                                                                                                                                                                                                                                             |

| Data          | Register data being read or written.                                                                                                                                                                                                                                                                                                |

| PEC           | CRC-8 packet error-checking byte; sent and returned with every message.                                                                                                                                                                                                                                                             |

| Data-Check    | Error status provided by the slave devices; returned only on reads.                                                                                                                                                                                                                                                                 |

| Alive-Counter | Used to verify the number of devices responding to a transmitted message. This byte is optional but is recommended for error-checking purposes.                                                                                                                                                                                     |

| Fill          | Bytes with values C2h or D3h transmitted as a part of read commands so that the total number of bytes sent equals the number of bytes received. However, these bytes are not returned to receiver with their original values; instead each slave device replaces the fill bytes with the register data being requested by the host. |

#### **Table 4. Common Commands**

| COMMAND BYTE | VALUE | DESCRIPTION                                                        |  |

|--------------|-------|--------------------------------------------------------------------|--|

| HELLOALL     | 57h   | Assigns a unique device address to each device in the daisy-chain. |  |

| WRITEALL     | 02h   | Writes a specific register in all devices.                         |  |

| READALL      | 03h   | Reads a specific register from all devices.                        |  |

### **UART Operation**

The UART is the subsystem that transmits messages to the UART slave devices and receives them back. The host uses SPI buffer transactions to store unencoded outgoing messages in the transmit buffer and also to read decoded incoming messages out of the receive buffer as shown in Figure 10. Table 5 shows the size and organization of the UART buffers.

#### **UART Interrupts**

There are 12 different UART events that can cause an interrupt (refer to the <u>Register Table</u> for details). For each event, there is a status bit, an enable bit, and a flag bit. The status bit is the real-time status of the event and can only be set or cleared by the UART. The enable bit determines

whether or not the event causes an interrupt. Interrupt flags (except the POR\_Flag) are edge-triggered in that they are set only when the interrupt enable bit is true and the corresponding status bit transitions from a logic-zero state to logic-one state. Interrupt flags can only be cleared by the host.

If the flag enable is set when its corresponding status bit is true, the flag is not set until the status bit transitions from a logic-zero state to a logic-one state. If the flag is cleared when the corresponding status bit is true, the flag does not set again until the status bit transitions from a logic-zero state to a logic-one state.

When any flag is true, the UART asserts the  $\overline{\text{INT}}$  pin. All flags must be cleared for the  $\overline{\text{INT}}$  pin to be deasserted. The only exception is the POR\_Flag, which has no effect on  $\overline{\text{INT}}$ .

Figure 10. UART Data Flow

#### **Table 5. UART Buffers**

| PARAMETER        | TRANSMIT BUFFER | RECEIVE BUFFER |

|------------------|-----------------|----------------|

| Organization     | 4 x 7 bytes     | 1 x 62 bytes   |

| Size             | 28 bytes        | 62 bytes       |

| Message Capacity | 4 messages      | Variable       |

| Host Access      | Read and Write  | Read Only      |

## **Table 6. UART Operational Modes**

| MODE                             | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Shutdown                         | Asserting SHDN resets all ASCI registers and buffer data to their default state, stops sending and receiving UART communication, and disables the 3.3V regulator.                                                                                                                                                                                                                                                                  |

| Transmit<br>Preambles            | Transmits preambles continuously (no idle state). Used to wake up the UART slave devices and initialize the UART baud rate of each slave device. This mode takes precedence over all transmit modes except Transmit Pause mode.                                                                                                                                                                                                    |

| Keep-Alive                       | Periodically sends a stop character to prevent UART slave devices from shutting down during periods of no communication (idle state). The idle time in between the periodic stop characters is programmable from zero to 10.24ms through the Keep-Alive [3:0] configuration. The default setting is infinite (mode disabled). The Transmit Pause, Transmit Preambles, and the Transmit Queue modes take precedence over this mode. |

| Transmit Queue<br>(default mode) | Starts transmission of the message loaded in the transmit queue if 1) there is sufficient space in the receive buffer for the message (RX_Full_Status is false) or 2) the limitations on message length are removed (TX_Unlimited is set). Default is enabled.                                                                                                                                                                     |

| Transmit Unlimited               | In this mode, the transmit queue automatically limits the message length to 255 bytes instead of the default 62-byte limit, and the message transmission is permitted even if the message length is greater than the available write space in the receive buffer.                                                                                                                                                                  |

| Transmit Pause                   | Places the transmitter into idle state once the UART has finished transmitting the current byte, however, the TX_Busy_Status and TX_Idle_Status bits remain unchanged. Transmission resumes when this bit is cleared. This mode takes precedence over all other transmit modes.                                                                                                                                                    |

| Transmit Odd<br>Parity           | Transmits characters with odd parity. Since the battery management UART protocol uses even parity, this mode can be used to test the system's ability to detect parity errors. Even parity is default.                                                                                                                                                                                                                             |

| Transmit No Stop                 | Transmits messages without a stop character. By sending subsequent messages with the No Preamble bit, a framed message of indefinite length can be constructed. The TX_Unlimited bit must be set for messages greater than 62 bytes.                                                                                                                                                                                               |

| Transmit No<br>Preamble          | Transmits messages without a preamble. By first sending a message in which the TX_No_Stop bit is set, and then sending messages with this bit set, a framed message of indefinite length can be constructed. However, if the preceding message was terminated with a stop character (end of frame), then the data sent in this mode is unframed (without preamble) and is not stored in the receive buffer.                        |

| Transmit Raw Data                | Disables Manchester encoding of transmitted data. In this mode, each data byte is transmitted as one character (instead of two characters).                                                                                                                                                                                                                                                                                        |

| Receive Raw Data                 | Disables Manchester decoding of the received data. In this mode, there is one data byte stored for every character received (instead of every two received).                                                                                                                                                                                                                                                                       |

#### **Transmit Buffer**

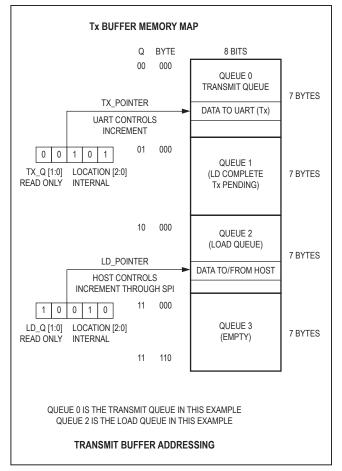

The transmit buffer memory map is shown below. It consists of four fixed-length queues, which the host uses to store outgoing messages. At any time, one of the queues is designated as the load queue (the queue being loaded) and one of the queues is designated as the transmit queue (the queue being unloaded). The load queue is selected by the two-bit register LD\_Q and the transmit queue is selected by the two-bit register TX\_Q. Each queue consists of seven bytes.

#### **Transmit Buffer Queues**

In each queue, location 0 is reserved for the message length and the remaining six locations are for specific message data. The default state of each queue is as shown in Table 7.

#### Clearing the Transmit Buffer

During UART initialization, it is recommended that the host reset the transmit buffer by issuing the CLR\_TX\_BUF SPI transaction (20h). This resets the transmit buffer as follows:

- TX\_Q [1:0] = 00b

- LD Q [1:0] = 00b

- Data in transmit buffer (28 bytes) is reset to default state per Table 7.

#### **Message Length**

Before composing any message, the host should compute the message's length (in bytes, not characters) based on both the type of command (read or write) and the device count. The message length should include any required fill bytes (but not preamble and stop characters). The host writes the message length into location 0 of the load queue, but if the specified message length is greater than 62d, only 62d (3Eh) is actually written. If the TX\_Unlimited = 1, then the maximum message length written is increased to 255d (FFh), but the host must service the receive buffer accordingly to avoid any possible overflow.

Figure 11. Transmit Buffer Memory Map

If the specified message length is greater than 6 bytes, the UART automatically appends alternating fill bytes (D3h, C2h) as required by the battery management UART protocol during the latter portion of the message transmission.

**Table 7. Queue Memory Map**

| LOCATION | DESCRIPTION                  | DEFAULT | MAXIMUM DEFAULT PERMITTED |                  |     |

|----------|------------------------------|---------|---------------------------|------------------|-----|

| LOCATION | DESCRIPTION                  | VALUE   | TX_UNLIMITED = 0          | TX_UNLIMITED = 1 |     |

| 0        | Message length               | 00h     | 3Eh                       | FFh              |     |

| 1        |                              | D3h     |                           |                  |     |

| 2        |                              | C2h     |                           |                  |     |

| 3        | Data bytes and/or fill bytes | -       | D3h                       | FF!-             | FFL |

| 4        |                              |         | C2h                       | FFh              | FFh |

| 5        |                              | D3h     |                           |                  |     |

| 6        |                              | C2h     |                           |                  |     |

#### Writing the Load Queue

A message, not including fill bytes, consists of three (3) to six (6) bytes. The HELLOALL sequence, for example, is three bytes: 57h, 00h, 00h (first address set to zero). Since no fill bytes are required, the total message length is 3 bytes. Therefore, the host should write the load queue with the following data in Table 8.

The host can write the load queue starting at any location within the queue by using appropriate SPI commands listed in SPI transaction <u>Table 9</u>. However, if the host attempts to write beyond location 6 of the queue, the additional data is ignored.

The UART never attempts to transmit the queue selected by LD\_Q because the host may be in the process of loading it or, even if it has finished loading, may need to verify (read) the contents of the load queue by using the RD\_LD\_Q transaction (C1h). The host can then select the next queue in sequence for loading by performing the WR\_NXT\_LD\_Q transaction (B0h), which increments the LD\_Q value. It is only when this increment occurs that the UART starts transmitting the data in the previously loaded queue. For both LD\_Q[1:0] and TX\_Q[1:0], values of 3h increment to 0h.

Table 8. Example of Queue Loaded with Message HELLOALL

| LOCATION | VALUE | DESCRIPTION    |

|----------|-------|----------------|

| 0        | 03h   | Message length |

| 1        | 57h   | Command byte   |

| 2        | 00h   | Address byte   |

| 3        | 00h   | Data byte      |

| 4 C2h    |       | Not written    |

| 5 D3h    |       | Not written    |

| 6        | C2h   | Not written    |

#### Filling the Transmit Buffer

The host can load all available queues until LD\_Q = TX\_Q - 1. In this state, the transmit buffer is full (TX\_Full\_Status true). In this condition, the host cannot start loading the transmit queue because the UART may still be unloading/transmitting data. If the transmit buffer is full and the host attempts to perform a WR\_NXT\_LD\_Q transaction and thus attempts to load the transmit queue, the increment does not occur and an overflow condition is indicated (TX\_Overflow\_Status true). The only time the host can write the transmit queue is when the transmit buffer is

empty (TX\_Q = LD\_Q), which is the default state. This state can also occur when the UART finishes sending the last loaded message and thus creates an empty transmit buffer.

#### Message Transmission

Whenever LD\_Q = TX\_Q, the transmit buffer is considered empty (TX\_Empty\_Status is true) because either the host has not yet finished loading the selected queue or the host has written but not yet verified the queue. However, once the host is finished servicing the queue, it performs a WR\_NXT\_LD\_Q transaction to select the next queue. Once this occurs, the transmit buffer is no longer considered empty because LD\_Q  $\neq$  TX\_Q.

The UART unloads/transmits the transmit queue if the following conditions are met:

- The UART is in Transmit\_Queue mode (TX\_Queue bit is set)

- The transmit buffer has at least one loaded queue (TX Empty Status is false)

- There is sufficient space in the receive buffer for the message (RX\_Space\_ ≥ Message Length)

Note: The limitation on available space in the receive buffer can be removed by setting the TX Unlimited bit.

Once the transmit conditions are met, the UART automatically starts unloading the transmit queue until the entire message, including any required fill bytes, has been transmitted. After the transmission is complete, the contents of the transmit queue are reset to their default values and the queue is once again available to the host for loading.

#### **Receive Buffer**

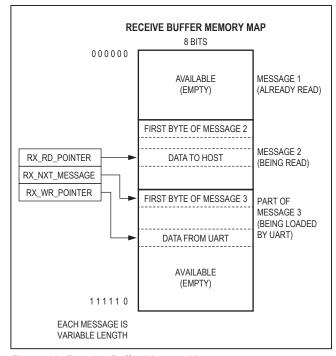

The receive buffer is a 62-byte circular buffer that the host can read with the SPI, but can only be loaded by the UART as it receives data. It utilizes three pointers as shown in the receive buffer memory map (Figure 12).

- RX\_RD\_POINTER: Read pointer or buffer location to be read by host (default 00h, read-only)

- RX\_WR\_POINTER: Write pointer or buffer location to be written by UART (default 01h, read-only)

- RX\_NXT\_MSG\_POINTER: Buffer location that is start of next unread message (default 00h, read-only)

In the default state, where the read pointer is one less than the write pointer, the receive buffer is considered empty (RX\_Empty\_Status is true). Any receive buffer data read in this condition will be zero.

### Clearing the Receive Buffer

During UART initialization, it is recommended that the host clear the receive buffer by issuing the CLR\_RX\_BUF SPI transaction (E0h). This resets the receive buffer as follows:

RX\_RD\_Pointer: 00hRX\_WR\_Pointer: 01h

RX\_NXT\_MSG\_POINTER: 00h

• Data in receive buffer (62 bytes) is cleared to 00h

If the receive buffer is cleared during Transmit Preambles mode, the state of the buffer cannot be guaranteed. Therefore, after disabling the Transmit Preambles mode, the host should wait until all transmitted preambles have been received before clearing the buffer. Since the first keep-alive stop character received after the last preamble results in a null message, the host can simply wait until the buffer is no longer empty (RX\_Empty\_Status = 0) before clearing the buffer.

The RX Clear Buffer command acts an an asynchronous reset not only for the RX Buffer, but also for the UART receiver logic. When the UART receiver logic is reset, it must resynchronize to the incoming UART signal before bytes can be properly processed. This is accomplished by receiving either a preamble byte or an idle state lasting at least one UART byte period. The preamble used to resynchronize the data stream should not be the same preamble that is at the beginning of the next transmitted message. The application should make sure that one of these conditions is met following an RX buffer clear prior to sending the next message from the MAX17841B.

### **Receiving Messages**

UART messages are framed with the preamble and stop characters. If the UART receiver decodes a valid preamble, it prepares to receive a message but it does not store the preamble in the receive buffer. Once data is received, the buffer is no longer empty (RX\_Empty\_Status = 0) and the UART sequentially stores decoded data bytes in the receive buffer until either a stop character or another preamble is received. When the stop character is received at the end of a message, the UART stores it in the receive buffer as a null byte (00h) and sets the RX\_Stop\_Status bit. The RX\_Stop\_Status bit is subsequently cleared when all unread messages have been read (buffer empty) or the next preamble is detected. The host can set the RX\_Stop\_INT\_Enable bit and monitor the interrupt line to determine when to service the receive buffer.

When the host services the receive buffer, three bits in the RX Byte register indicate specific information about the

Figure 12. Receive Buffer Memory Map

byte being read (the byte addressed by RX\_RD\_Pointer), which is useful for error checking:

- First\_Byte bit: Indicates that the byte is the first data byte in a message (the corresponding character was preceded by preamble character).

- Byte\_Error bit: Indicates that the byte may contain an error (the corresponding character contained a Manchester and/or parity error). This bit drives the RX\_Error interrupt.

- Last\_Byte bit: Indicates that the byte is the last byte in a message (the corresponding character was a stop character and was stored as a null byte).

#### **Message Exceptions**

If a message is not framed with a valid preamble, then the UART ignores the data and does not store it.

If a message is not framed with a stop character, then the preamble of the next message serves to delineate between the two messages. However, the first message has no stop character stored.

If the UART receives a preamble followed by a stop character it stores a null message in the receive buffer consisting of a single null byte (00h). This occurs when a keep-alive stop character is received after Transmit Preambles mode is disabled. In this use case, the receive

## Automotive SPI Communication Interface (ASCI)

buffer is not empty. The host should dispense of the null message by either clearing the receive buffer or by simply reading the null message and discarding it.

A receive buffer overflow occurs when the UART receives data but there is no more space to store it. This could potentially occur if TX\_Unlimited was set or if there was sufficient latency in the daisy-chain. The UART cannot overtake the read pointer and overwrite the data being

read so the last address that can be written is the one just behind the read pointer. If more data is received after the last address is written, the UART simply overwrites the last address and then sets the RX\_Overflow\_Status bit. The RX\_Overflow\_Status bit is cleared when the receive buffer is read, thereby creating more write space. To detect any overflow, the status must be checked before servicing the receive buffer. After servicing the receive buffer, the status

**Table 9. SPI Transactions**

| ADDRESS                       |                      | N                      | IAME                                                                                          | DESCRIPTION                                                                                                                                                                                                |  |

|-------------------------------|----------------------|------------------------|-----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0x01 to 0x1B and 0x95 to 0x9B |                      | See the Register Table |                                                                                               | Reads or writes the specified ASCI register                                                                                                                                                                |  |

| <b>BUFFER TRAN</b>            | SACTIONS             |                        |                                                                                               |                                                                                                                                                                                                            |  |

| COMMAND                       | START LOCAT          | ION                    |                                                                                               | DESCRIPTION                                                                                                                                                                                                |  |

| 0x20                          | _                    |                        | CLR_TX_BUF Command: Resets the transmit buffer to its default state and clears TX_Q and LD_Q. |                                                                                                                                                                                                            |  |

| 0x91                          | RX_RD_<br>Pointer    |                        | Pointer. Autom                                                                                | nmand: Reads the receive buffer starting at the address RX_RD_<br>natically increments the read pointer after the byte is read but does<br>the read pointer into the next message.                         |  |

| 0x93                          | RX_NXT_MS<br>Pointer | G_                     | NXT_MSG_P                                                                                     | G Command: Reads the receive buffer starting at the address RX_<br>binter (oldest unread message). Automatically increments the read<br>byte is read but does not increment the read pointer into the next |  |

| 0xB0                          | LD_Q Locatio         | n 0                    |                                                                                               |                                                                                                                                                                                                            |  |

| 0xB2                          | LD_Q Locatio         | n 1                    | WR_NXT_LD_Q Command: Increments LD_Q, then writes the transmit buffer                         |                                                                                                                                                                                                            |  |

| 0xB4                          | LD_Q Locatio         | n 2                    |                                                                                               | he increment occurs whether the host loads the data or not. The                                                                                                                                            |  |

| 0xB6                          | LD_Q Locatio         | n 3                    | command byte defines the first location to be written (locations 0 to 6). For                 |                                                                                                                                                                                                            |  |

| 0xB8                          | LD_Q Location 4      |                        | example, 0xB0 starts writing at location 0 and continues through location 6. Writes           |                                                                                                                                                                                                            |  |

| 0xBA                          | LD_Q Location 5      |                        | beyond location 6 have no effect.                                                             |                                                                                                                                                                                                            |  |

| 0xBC                          | LD_Q Location 6      |                        |                                                                                               |                                                                                                                                                                                                            |  |

| 0xC0                          | LD_Q Location 0      |                        |                                                                                               |                                                                                                                                                                                                            |  |

| 0xC2                          | LD_Q Locatio         | n 1                    |                                                                                               |                                                                                                                                                                                                            |  |

| 0xC4                          | LD_Q Locatio         | n 2                    |                                                                                               | ommand: Writes the transmit buffer load queue. The command byte                                                                                                                                            |  |

| 0xC6                          | LD_Q Locatio         | n 3                    |                                                                                               | st byte written (locations 0 to 6). For example, 0xC0 starts writing nd continues through location 6. Writes beyond location 6 have no                                                                     |  |

| 0xC8                          | LD_Q Locatio         | n 4                    | effect.                                                                                       | nd continues through location of writes beyond location o have no                                                                                                                                          |  |

| 0xCA                          | LD_Q Locatio         | n 5                    | 0001.                                                                                         |                                                                                                                                                                                                            |  |

| 0xCC                          | LD_Q Locatio         | n 6                    |                                                                                               |                                                                                                                                                                                                            |  |

| 0xC1                          | LD_Q Locatio         | n 0                    |                                                                                               |                                                                                                                                                                                                            |  |

| 0xC3                          | LD_Q Locatio         | n 1                    |                                                                                               |                                                                                                                                                                                                            |  |

| 0xC5                          | LD_Q Locatio         | n 2                    |                                                                                               | ommand: Reads transmit buffer load queue. The command byte                                                                                                                                                 |  |

| 0xC7                          | LD_Q Locatio         | n 3                    |                                                                                               | st byte read (locations 0 to 6). For example, 0xC1 starts reading                                                                                                                                          |  |

| 0xC9                          | LD_Q Location 4      |                        | at location 0 and continues through location 6. Reading beyond location 6 read zeros.         |                                                                                                                                                                                                            |  |

| 0xCB                          | LD_Q Locatio         | n 5                    | .=                                                                                            |                                                                                                                                                                                                            |  |

| 0xCD                          | LD_Q Locatio         | n 6                    |                                                                                               |                                                                                                                                                                                                            |  |

| 0xE0                          | _                    |                        |                                                                                               | Command: Resets the receive buffer and the receive buffer eir default state.                                                                                                                               |  |

should be checked again for data errors (e.g., parity errors) prior to initiating transmission of the next message.

If multiple messages are received without being read, then an overflow can occur and the UART sets the RX\_ Overflow\_Status bit. This occurs when the write pointer has incremented until it is one less than the read pointer, at which point the UART no longer increments it. In this case, the last data byte is overwritten.

#### Reading Messages

The host can use two different SPI transactions to read the receive buffer:

- RD\_RX\_BUF (91h): Starts reading at the current read pointer location

- RD\_NXT\_MSG (93h): Starts reading at the start of the next unread message

During any read transaction, the host may continue reading data until the end of the message, after which the data read will be 00h. The host cannot continue reading into the next message, if there is one.

During any read transaction, the UART increments the read pointer after the data byte is read so that if the SPI transaction is prematurely terminated in the middle of the byte, then the same location is resent on the next RD\_MSG SPI transaction. This allows the host to stop a read and restart it without losing data. Each byte in the buffer is cleared after it is read and is eventually available to the UART for storing incoming data.

## **Applications Information**

### **Transaction Sequence for UART Initialization**

In the example shown in <u>Table 10</u>, the host <u>initializes</u> communication with two UART slave devices. <u>SHDN</u> must be deasserted first. Transactions to poll RX\_STATUS register are repeated until the poll is successful or times out.

It is recommended that all writes to configuration registers be verified by reading back the register data. Transmit buffer data can be verified by reading the buffer contents or by reading the transmitted data in the receive buffer.

# Transaction Sequence for UART Write and Read