# Ultra Series<sup>™</sup> Crystal Oscillator (VCXO) Si569 Data Sheet

Pin Assignments

SCL (Top View 6 VDD

5 CLK-

8 4 CLK+

# Ultra Low Jitter I2C Programmable VCXO (100 fs), 0.2 to 3000 MHz

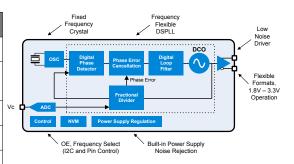

The Si569 Ultra Series<sup>™</sup> voltage-controlled crystal oscillator utilizes Skyworks Solutions' advanced 4<sup>th</sup> generation DSPLL® technology to provide an ultra-low jitter, low phase noise clock at any output frequency. The device is user-programmed via simple I2C commands to provide any frequency from 0.2 to 3000 MHz with <1 ppb resolution and maintains exceptionally low jitter for both integer and fractional frequencies across its operating range. On-chip power supply filtering provides industry-leading power supply noise rejection, simplifying the task of generating low jitter clocks in noisy systems that use switched-mode power supplies. Unlike a traditional XO, where a different crystal is required for each output frequency, the Si569 uses one simple crystal and a DSPLL IC-based approach to provide the desired output frequency. The Si569 is factory-configurable for a wide variety of user specifications, including startup frequency, I2C address, output format, and OE pin location/polarity. Specific configurations are factory-programmed at time of shipment, eliminating long lead times associated with custom oscillators.

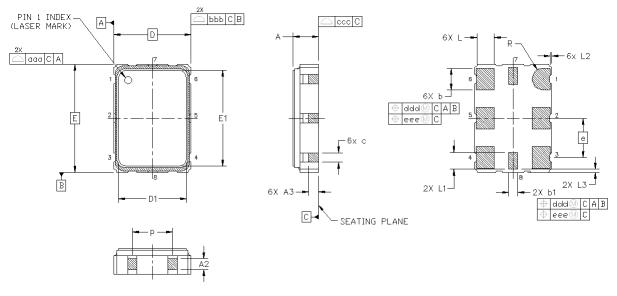

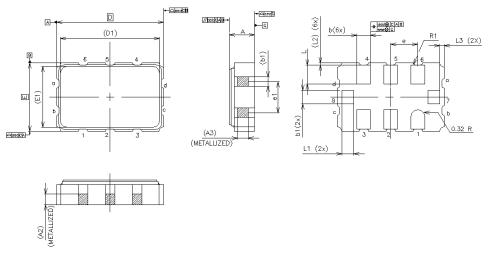

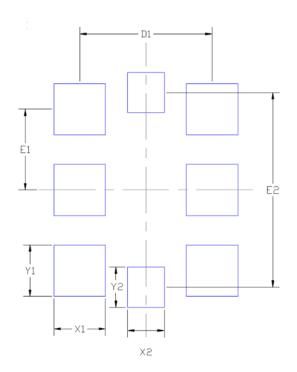

5 x 7 mm and 3.2 x 5 mm 2.5 x 3.2 mm

VC

3

OE/FS 2

| Pin # | Descriptions                                                                |

|-------|-----------------------------------------------------------------------------|

| 1     | VC = Voltage Control Pin                                                    |

| 2     | Selectable via ordering option<br>OE = Output enable; FS = Frequency Select |

| 3     | GND = Ground                                                                |

| 4     | CLK+ = Clock output                                                         |

| 5     | CLK- = Complementary clock output. Not used for CMOS.                       |

| 6     | VDD = Power supply                                                          |

| 7     | SDA = I2C Serial Data                                                       |

| 8     | SCL = I2C Serial Clock                                                      |

#### KEY FEATURES

- I2C programmable to any frequency from 0.2 to 3000 MHz with < 1 ppb resolution

- Ultra low jitter: 100 fs RMS Typ (12 kHz 20 MHz)

- Configure up to 2 pin-selectable startup frequencies

- I2C interface supports 100 kbps, 400 kbps, and 1 Mbps (Fast Mode Plus)

- Excellent PSNR and supply noise immunity: -80 dBc Typ

- Programmable Kv (ppm/V) simplifies development

- 3.3 V, 2.5 V and 1.8 V  $V_{\text{DD}}$  supply operation from the same part number

- LVPECL, LVDS, CML, HCSL, CMOS, and Dual CMOS output options

- 2.5x3.2, 3.2x5, 5x7 mm package options

- · Samples available with 1-2 week lead times

#### APPLICATIONS

- 100G/200G/400G OTN, coherent optics, PAM4

- 3G-SDI/12G-SDI/24G-SDI broadcast video

- · Servers, switches, storage, search acceleration

- FPGA/ASIC clocking

1

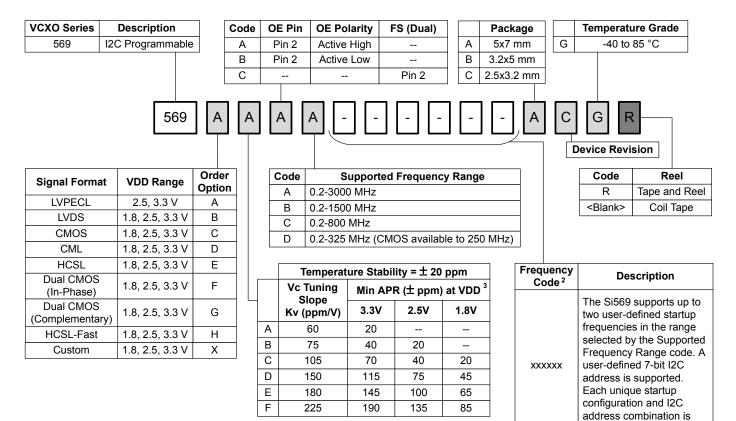

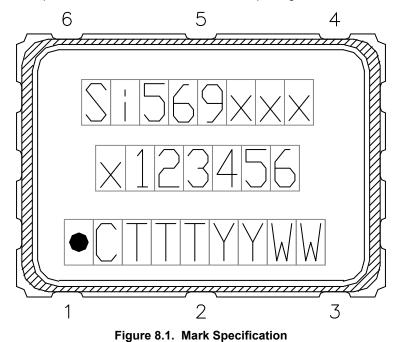

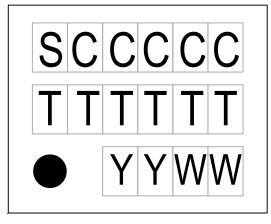

### 1. Ordering Guide

The Si569 XO supports a variety of options including startup frequency, output format, and control voltage tuning slope, as shown in the chart below. Specific device configurations are programmed into the part at time of shipment, and samples are available in 1-2 weeks. Skyworks Solutions provides an online part number configuration utility to simplify this process. Refer to https://www.skywork-sinc.com/en/Products/Timing-Oscillators to access this tool and for further ordering instructions.

#### Notes:

1. Contact Skyworks for non-standard configurations.

2. Create custom part numbers at https://www.skyworksinc.com/en/Products/Timing-Oscillators.

3. Min Absolute Pull Range (APR) includes temp stability, initial accuracy, load pulling, VDD variation, and 20 year aging at 70 °C.

a. For best jitter and phase noise performance, always choose the smallest Kv that meets the application's minimum APR requirements. Unlike SAW-based solutions which require higher Kv values to account for their higher temperature dependence, the Si56x series provides lower Kv options to minimize noise coupling and jitter in real-world PLL designs.

assigned a 6-digit code.

2

- b. Absolute Pull Range (APR) is the ability of a VCXO to track a signal over the product lifetime. A VCXO with an APR of ±20 ppm is able to lock to a clock with a ±20 ppm stability over 20 years over all operating conditions.

- c. APR (±) = (0.5 x VDD x tuning slope) (initial accuracy + temp stability + load pulling + VDD variation + aging).

- d. Minimum APR values noted above include absolute worst case values for all parameters.

- e. See application note, "AN266: VCXO Tuning Slope (Kv), Stability, and Absolute Pull Range (APR)" for more information.

#### 1.1 Technical Support

| Oscillator Phase Noise Lookup Utility | https://www.skyworksinc.com/tools/oscillator-phase-noise |

|---------------------------------------|----------------------------------------------------------|

| Quality and Reliability               | https://www.skyworksinc.com/quality                      |

| Development Kits                      | https://www.skyworksinc.com/en/Products/Timing           |

### 2. Electrical Specifications

#### Table 2.1. Electrical Specifications

$V_{DD}$  = 1.8 V, 2.5 or 3.3 V  $\pm$  5%,  $T_A$  = –40 to 85 °C

| Parameter                          | Symbol                         | Test Condition/Comment                                                                      | Min                    | Тур | Max                    | Unit            |

|------------------------------------|--------------------------------|---------------------------------------------------------------------------------------------|------------------------|-----|------------------------|-----------------|

| Temperature Range                  | T <sub>A</sub>                 |                                                                                             | -40                    | —   | 85                     | °C              |

| Frequency Range                    | F <sub>CLK</sub>               | LVPECL, LVDS, CML                                                                           | 0.2                    |     | 3000                   | MHz             |

|                                    |                                | HCSL                                                                                        | 0.2                    |     | 400                    | MHz             |

|                                    |                                | CMOS, Dual CMOS                                                                             | 0.2                    |     | 250                    | MHz             |

| Supply Voltage                     | V <sub>DD</sub>                | 3.3 V                                                                                       | 3.135                  | 3.3 | 3.465                  | V               |

|                                    |                                | 2.5 V                                                                                       | 2.375                  | 2.5 | 2.625                  | V               |

|                                    |                                | 1.8 V                                                                                       | 1.71                   | 1.8 | 1.89                   | V               |

| Supply Current                     | I <sub>DD</sub>                | LVPECL (output enabled)                                                                     | _                      | 120 | 170                    | mA              |

|                                    |                                | LVDS/CML (output enabled)                                                                   | _                      | 100 | 140                    | mA              |

|                                    |                                | HCSL (output enabled)                                                                       | _                      | 95  | 140                    | mA              |

|                                    |                                | HCSL-Fast (output enabled)                                                                  | _                      | 103 | 152                    | mA              |

|                                    |                                | CMOS (output enabled)                                                                       | _                      | 95  | 145                    | mA              |

|                                    |                                | Dual CMOS (output enabled)                                                                  | _                      | 105 | 155                    | mA              |

|                                    |                                | Tristate Hi-Z (output disabled)                                                             | _                      | 83  |                        | mA              |

| Temperature Stability <sup>1</sup> |                                | -40 to 85 °C                                                                                | -20                    |     | 20                     | ppm             |

| Rise/Fall Time                     | T <sub>R</sub> /T <sub>F</sub> | LVPECL/LVDS/CML                                                                             | _                      |     | 350                    | ps              |

| (20% to 80% V <sub>PP</sub> )      |                                | CMOS / Dual CMOS<br>(C <sub>L</sub> = 5 pF)                                                 | —                      | 0.5 | 1.5                    | ns              |

|                                    |                                | HCSL, F <sub>CLK</sub> >50 MHz                                                              | _                      |     | 450                    | ps              |

|                                    |                                | HCSL-Fast, F <sub>CLK</sub> >50 MHz                                                         | _                      |     | 275                    | ps              |

| Duty Cycle                         | D <sub>C</sub>                 | All formats                                                                                 | 45                     |     | 55                     | %               |

| Output Enable (OE)                 | V <sub>IH</sub>                |                                                                                             | 0.7 × V <sub>DD</sub>  |     |                        | V               |

| Frequency Select (FS) <sup>2</sup> | V <sub>IL</sub>                |                                                                                             | _                      |     | 0.3 × V <sub>DD</sub>  | V               |

|                                    | T <sub>D</sub>                 | Output Disable Time, F <sub>CLK</sub> >10 MHz                                               | _                      |     | 3                      | μs              |

|                                    | T <sub>E</sub>                 | Output Enable Time, F <sub>CLK</sub> >10 MHz                                                | _                      |     | 20                     | μs              |

|                                    | T <sub>FS</sub>                | Settling Time after FS Change                                                               | _                      |     | 10                     | ms              |

| Powerup Time                       | tosc                           | Time from 0.9 × V <sub>DD</sub> until output fre-<br>quency (F <sub>CLK</sub> ) within spec | -                      |     | 10                     | ms              |

| Powerup VDD Ramp Rate              | V <sub>RAMP</sub>              | Fastest V <sub>DD</sub> ramp rate allowed on startup                                        | -                      | —   | 100                    | V/ms            |

| LVPECL Output Option <sup>3</sup>  | V <sub>OC</sub>                | Mid-level                                                                                   | V <sub>DD</sub> – 1.42 |     | V <sub>DD</sub> – 1.25 | V               |

|                                    | Vo                             | Swing (diff, F <sub>CLK</sub> ≤ 1.5 GHz)                                                    | 1.1                    |     | 1.9                    | V <sub>PP</sub> |

|                                    |                                | Swing (diff, F <sub>CLK</sub> > 1.5 GHz) <sup>6</sup>                                       | 0.55                   |     | 1.7                    | V <sub>PP</sub> |

3

#### Si569 Data Sheet • Electrical Specifications

| Parameter                            | Symbol          | Test Condition/Comment                                | Min                  | Тур  | Max                    | Unit            |

|--------------------------------------|-----------------|-------------------------------------------------------|----------------------|------|------------------------|-----------------|

| LVDS Output Option <sup>4</sup>      | V <sub>OC</sub> | Mid-level (2.5 V, 3.3 V VDD)                          | 1.125                | 1.20 | 1.275                  | V               |

|                                      |                 | Mid-level (1.8 V VDD)                                 | 0.8                  | 0.9  | 1.0                    | V               |

|                                      | V <sub>O</sub>  | Swing (diff, F <sub>CLK</sub> ≤ 1.4 GHz)              | 0.6                  | 0.7  | 0.9                    | V <sub>PP</sub> |

|                                      |                 | Swing (diff, F <sub>CLK</sub> > 1.4 GHz) <sup>6</sup> | 0.25                 | 0.5  | 0.8                    | V <sub>PP</sub> |

|                                      |                 | Swing (diff, $F_{CLK} \le 1.6 \text{ GHz})^7$         | 0.6                  | 0.8  | 1.0                    | V <sub>PP</sub> |

| HCSL Output Option <sup>5</sup>      | V <sub>OH</sub> | Output voltage high                                   | 660                  | 800  | 850                    | mV              |

| HCSL-Fast Output Option <sup>5</sup> | V <sub>OL</sub> | Output voltage low                                    | -150                 | 0    | 150                    | mV              |

|                                      | V <sub>C</sub>  | Crossing voltage                                      | 250                  | 410  | 550                    | mV              |

| CML Output Option (AC-Coupled)       | Vo              | Swing (diff, F <sub>CLK</sub> ≤ 1.5 GHz)              | 0.6                  | 0.8  | 1.0                    | V <sub>PP</sub> |

|                                      |                 | Swing (diff, F <sub>CLK</sub> > 1.5 GHz) <sup>6</sup> | 0.3                  | 0.55 | 0.9                    | $V_{PP}$        |

| CMOS Output Option                   | V <sub>OH</sub> | I <sub>OH</sub> = 8/6/4 mA for 3.3/2.5/1.8V VDD       | $0.85 \times V_{DD}$ | —    | —                      | V               |

|                                      | V <sub>OL</sub> | I <sub>OL</sub> = 8/6/4 mA for 3.3/2.5/1.8V VDD       | _                    | —    | 0.15 × V <sub>DD</sub> | V               |

#### Notes:

1. Min APR includes ±20 ppm temperature stability, initial accuracy, load pulling, VDD variation, and aging for 20 yrs at 70 °C.

2. OE includes a 50 k $\Omega$  pull-up to VDD for OE active high, or includes a 50 k $\Omega$  pull-down to GND for OE active low. FS pin includes a 50 k $\Omega$  pull-up to VDD.

3.  $R_{term}$  = 50  $\Omega$  to  $V_{DD}$  – 2.0 V (see Figure 4.1). Additional DC current from the output driver will flow through the 50  $\Omega$  resistors, resulting in a shift in common mode voltage. The measurements in this table have accounted for this.

4.  $R_{term}$  = 100  $\Omega$  (differential) (see Figure 4.2).

5.  $R_{term}$  = 50  $\Omega$  to GND (see Figure 4.2).

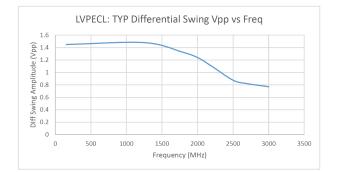

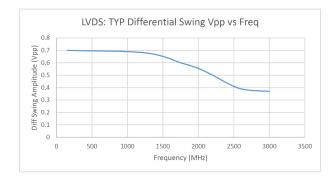

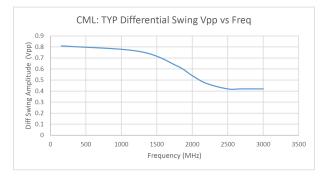

6. Refer to the figure below for Typical Clock Output Swing Amplitudes vs Frequency.

7. High drive LVDS swing is supported when following the method shown in section 5.8 Configuring High Drive LVDS Swing.

Figure 2.1. Typical Clock Output Swing Amplitudes vs. Frequency

#### Table 2.2. I2C Characteristics

### $V_{DD}$ = 1.8, 2.5, or 3.3 V $\pm$ 5%, $T_A$ = –40 to 85 °C

| Symbol           | Test Condition/Comment                | Min                                                                                                             | Тур                                                                                                                                                                                           | Max                                                                                                                                                                                                                                | Unit                                                                                                                                                                                                                                                                                                                                                  |

|------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>IH</sub>  |                                       | 0.70 x<br>V <sub>DD</sub>                                                                                       | _                                                                                                                                                                                             | _                                                                                                                                                                                                                                  | V                                                                                                                                                                                                                                                                                                                                                     |

| V <sub>IL</sub>  |                                       | _                                                                                                               | _                                                                                                                                                                                             | 0.30 x<br>V <sub>DD</sub>                                                                                                                                                                                                          | V                                                                                                                                                                                                                                                                                                                                                     |

| M <sub>RES</sub> |                                       | _                                                                                                               | 0.026                                                                                                                                                                                         | _                                                                                                                                                                                                                                  | ppb                                                                                                                                                                                                                                                                                                                                                   |

|                  | From center frequency                 | -950                                                                                                            | —                                                                                                                                                                                             | +950                                                                                                                                                                                                                               | ppm                                                                                                                                                                                                                                                                                                                                                   |

|                  | < ±950 ppm from center fre-<br>quency |                                                                                                                 | —                                                                                                                                                                                             | 100                                                                                                                                                                                                                                | μs                                                                                                                                                                                                                                                                                                                                                    |

|                  | > ±950 ppm from center fre-<br>quency | _                                                                                                               | _                                                                                                                                                                                             | 40                                                                                                                                                                                                                                 | ms                                                                                                                                                                                                                                                                                                                                                    |

|                  | V <sub>IH</sub><br>V <sub>IL</sub>    | V <sub>IH</sub> V <sub>IL</sub> M <sub>RES</sub> From center frequency         < ±950 ppm from center frequency | $V_{IH}$ $0.70 \times V_{DD}$ $V_{IL}$ $M_{RES}$ $M_{RES}$ $<$ From center frequency $<$ +950 ppm from center frequency $<$ +950 ppm from center frequency $<$ +950 ppm from center frequency | $V_{IH}$ $0.70 \times V_{DD}$ $V_{IL}$ $M_{RES}$ 0.026           From center frequency         -950 $< \pm 950$ ppm from center frequency         -950 $< \pm 950$ ppm from center frequency $> \pm 950$ ppm from center frequency | $V_{IH}$ $0.70 \times V_{DD}$ $V_{IL}$ $0.30 \times V_{DD}$ $0.30 \times V_{DD}$ $M_{RES}$ $0.026$ $M_{RES}$ $0.026$ $V_{LD}$ 100 $V_{LD}$ > $\pm 950$ ppm from center fre- |

### Table 2.3. V<sub>C</sub> Control Voltage Input

### $V_{DD}$ = 1.8, 2.5 or 3.3 V $\pm$ 5%, $T_A$ = –40 to 85 °C

| Parameter                                                 | Symbol         | Test Condition                  | Min          | Тур                    | Max          | Unit  |

|-----------------------------------------------------------|----------------|---------------------------------|--------------|------------------------|--------------|-------|

| Control Voltage Range                                     | V <sub>C</sub> |                                 | 0.1 x<br>VDD | VDD/2                  | 0.9 x<br>VDD | V     |

| Control Voltage Tuning Slope<br>(Vc = 10% VDD to 90% VDD) | Kv             | Positive slope, ordering option | 60, 75,      | 105, 150, <sup>2</sup> | 180, 225     | ppm/V |

| Kv Variation                                              | Kv_var         |                                 | _            | _                      | ±10          | %     |

| Control Voltage Linearity                                 | LVC            | Best Straight Line fit          | -1.5         | ±0.5                   | +1.5         | %     |

| Modulation Bandwidth                                      | BW             |                                 | _            | 10                     | _            | kHz   |

| Vc Input Impedance                                        | ZVC            |                                 | 500          | _                      | _            | kΩ    |

#### Table 2.4. Clock Output Phase Jitter and PSNR

### $V_{DD}$ = 1.8 V, 2.5 or 3.3 V $\pm$ 5%, $T_A$ = –40 to 85 °C

| Parameter                                                                    | Symbol | Test Condition/Comment              | Min | Тур | Max | Unit |

|------------------------------------------------------------------------------|--------|-------------------------------------|-----|-----|-----|------|

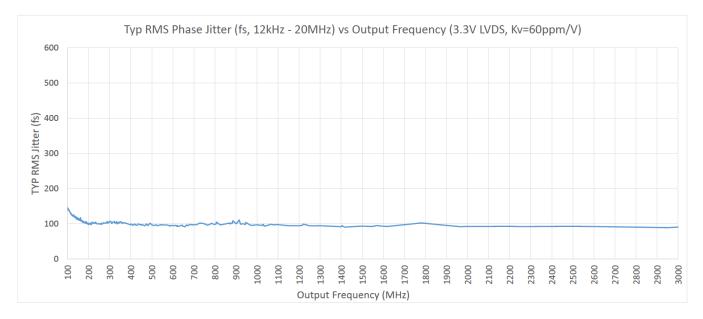

| Phase Jitter (RMS, 12 kHz - 20 MHz) <sup>1</sup>                             | φJ     | Kv = 60 ppm/V                       | _   | 100 | 150 | fs   |

| All Differential Formats, $F_{CLK} \ge 200 \text{ MHz}$                      |        | Kv = 75 ppm/V                       | _   | 103 | _   | fs   |

|                                                                              |        | Kv = 105 ppm/V                      | _   | 110 | _   | fs   |

|                                                                              |        | Kv = 150 ppm/V                      | _   | 123 | _   | fs   |

|                                                                              |        | Kv = 180 ppm/V                      | _   | 132 | _   | fs   |

|                                                                              |        | Kv = 225 ppm/V                      | _   | 150 | _   | fs   |

| Phase Jitter (RMS, 12 kHz - 20 MHz) <sup>1</sup>                             | φJ     | Kv = 60 ppm/V                       | _   | 115 | 180 | fs   |

| All Diff Formats, 100 MHz ≤ F <sub>CLK</sub> < 200 MHz                       |        | Kv = 75 ppm/V                       | _   | 118 |     | fs   |

|                                                                              |        | Kv = 105 ppm/V                      | _   | 125 |     | fs   |

|                                                                              |        | Kv = 150 ppm/V                      | _   | 138 | _   | fs   |

|                                                                              |        | Kv = 180 ppm/V                      | _   | 147 |     | fs   |

|                                                                              |        | Kv = 225 ppm/V                      | _   | 165 |     | fs   |

| Phase Jitter (RMS, 12 kHz - 20 MHz) <sup>1</sup>                             | Γφ     | Kv = 60 ppm/V                       | _   | 110 | 130 | fs   |

| LVDS, F <sub>CLK</sub> = 156.25 MHz                                          |        | Kv = 75 ppm/V                       | _   | 113 | _   | fs   |

|                                                                              |        | Kv = 105 ppm/V                      | _   | 120 | _   | fs   |

|                                                                              |        | Kv = 150 ppm/V                      | _   | 133 | _   | fs   |

|                                                                              |        | Kv = 180 ppm/V                      | _   | 142 | _   | fs   |

|                                                                              |        | Kv = 225 ppm/V                      | _   | 160 | _   | fs   |

| Phase Jitter (RMS, 12 kHz - 20 MHz) <sup>1</sup><br>CMOS / Dual CMOS Formats | φJ     | 10 MHz ≤ F <sub>CLK</sub> < 250 MHz | _   | 200 | _   | fs   |

| Spurs Induced by External Power Supply                                       | PSNR   | 100 kHz sine wave                   |     | -83 |     | dBc  |

| Noise, 50 mVpp Ripple. LVDS 156.25 MHz<br>Output                             |        | 200 kHz sine wave                   |     | -83 |     |      |

|                                                                              |        | 500 kHz sine wave                   |     | -82 |     |      |

|                                                                              |        | 1 MHz sine wave                     |     | -85 |     | 1    |

6

| Offset Frequency (f) | 156.25 MHz LVDS      | 200 MHz LVDS      | 644.53125 MHz LVDS      | Unit   |

|----------------------|----------------------|-------------------|-------------------------|--------|

| 100 Hz               | -73                  | -71               | -60                     |        |

| 1 kHz                | -102                 | -102              | -93                     |        |

| 10 kHz               | -130                 | -128              | -118                    |        |

| 100 kHz              | -141                 | –139              | –129                    | dBc/Hz |

| 1 MHz                | –150                 | -148              | –138                    |        |

| 10 MHz               | –159                 | -160              | –153                    |        |

| 20 MHz               | -160                 | -162              | -154                    |        |

| Offset Frequency (f) | 156.25 MHz<br>LVPECL | 200 MHz<br>LVPECL | 644.53125 MHz<br>LVPECL | Unit   |

| 100 Hz               | -72                  | -71               | -60                     |        |

| 1 kHz                | -103                 | -101              | -92                     |        |

| 10 kHz               | -130                 | –127              | -117                    |        |

| 100 kHz              | -142                 | –139              | –129                    | dBc/Hz |

| 1 MHz                | -150                 | -148              | –138                    |        |

| 10 MHz               | -160                 | -162              | -154                    |        |

| 20 MHz               | -161                 | -162              | -156                    |        |

#### Table 2.5. 3.2 x 5 mm Clock Output Phase Noise (Typical)

Phase jitter measured with Agilent E5052 using a differential-to-single ended converter (balun or buffer). Measurements collected for >700 commonly used frequencies. Phase noise plots for specific frequencies are available using our free, online Oscillator Phase Noise Lookup Tool at https://www.skyworksinc.com/-/media/Skyworks/SL/documents/public/user-guides/ug298-si5xxuc-evb-ug.pdf.

#### Table 2.6. Environmental Compliance and Package Information

| Parameter                                                 | Test Condition                                          |  |  |  |

|-----------------------------------------------------------|---------------------------------------------------------|--|--|--|

| Mechanical Shock                                          | MIL-STD-883, Method 2002                                |  |  |  |

| Mechanical Vibration                                      | MIL-STD-883, Method 2007                                |  |  |  |

| Solderability                                             | MIL-STD-883, Method 2003                                |  |  |  |

| Gross and Fine Leak                                       | MIL-STD-883, Method 1014                                |  |  |  |

| Resistance to Solder Heat                                 | MIL-STD-883, Method 2036                                |  |  |  |

| Moisture Sensitivity Level (MSL): 3.2 x 5, 5 x 7 packages | 1                                                       |  |  |  |

| Moisture Sensitivity Level (MSL): 2.5 x 3.2 package       | 2                                                       |  |  |  |

| Contact Pads: 3.2x5, 5x7 packages                         | Au/Ni (0.3 - 1.0 μm / 1.27 - 8.89 μm)                   |  |  |  |

| Contact Pads: 2.5x3.2 packages                            | Au/Pd/Ni (0.03 - 0.12 μm / 0.1 - 0.2 μm / 3.0 - 8.0 μm) |  |  |  |

| M. (.                                                     |                                                         |  |  |  |

Note:

For additional product information not listed in the data sheet (e.g. RoHS Certifications, MDDS data, qualification data, REACH Declarations, ECCN codes, etc.), refer to our "Corporate Request For Information" portal found here: www.skyworksinc.com/quality.

### Table 2.7. Thermal Conditions<sup>1</sup>

#### Max Junction Temperature = 125° C

| Package                                | Parameter                                | Symbol          | Test Condition   | Value | Unit |

|----------------------------------------|------------------------------------------|-----------------|------------------|-------|------|

|                                        | Thermal Resistance Junction to Ambient   | Θ <sub>JA</sub> | Still Air, 85 °C | 72    | °C/W |

| 2.5 x 3.2 mm<br>8-pin DFN <sup>2</sup> | Thermal Parameter Junction to Board      | Ψ <sub>JB</sub> | Still Air, 85 °C | 38    | °C/W |

|                                        | Thermal Parameter Junction to Top Center | $\Psi_{JT}$     | Still Air, 85 °C | 15    | °C/W |

|                                        | Thermal Resistance Junction to Ambient   | Θ <sub>JA</sub> | Still Air, 85 °C | 55    | °C/W |

| 3.2 × 5 mm<br>8-pin CLCC               | Thermal Parameter Junction to Board      | Ψ <sub>JB</sub> | Still Air, 85 °C | 20    | °C/W |

| ·                                      | Thermal Parameter Junction to Top Center | $\Psi_{JT}$     | Still Air, 85 °C | 20    | °C/W |

|                                        | Thermal Resistance Junction to Ambient   | Θ <sub>JA</sub> | Still Air, 85 °C | 53    | °C/W |

| 5 × 7 mm<br>8-pin CLCC                 | Thermal Parameter Junction to Board      | Ψ <sub>JB</sub> | Still Air, 85 °C | 26    | °C/W |

| ·                                      | Thermal Parameter Junction to Top Center | $\Psi_{JT}$     | Still Air, 85 °C | 26    | °C/W |

#### Note:

1. Based on PCB Dimensions: 4.5" x 7", PCB Thickness: 1.6 mm, Number of Cu Layers: 4.

2. For best 2.5x3.2mm thermal performance, use 2 GND vias as shown in the Si5xxUC-EVB eval board layout

8

### Table 2.8. Absolute Maximum Ratings<sup>1</sup>

| Parameter                                     | Symbol            | Rating                        | Unit |

|-----------------------------------------------|-------------------|-------------------------------|------|

| Maximum Operating Temp.                       | T <sub>AMAX</sub> | 95                            | °C   |

| Storage Temperature                           | T <sub>S</sub>    | -55 to 125                    | °C   |

| Supply Voltage                                | V <sub>DD</sub>   | -0.5 to 3.8                   | °C   |

| Input Voltage                                 | V <sub>IN</sub>   | –0.5 to V <sub>DD</sub> + 0.3 | V    |

| ESD HBM (JESD22-A114)                         | НВМ               | 2.0                           | kV   |

| Solder Temperature <sup>2</sup>               | T <sub>PEAK</sub> | 260                           | °C   |

| Solder Time at T <sub>PEAK</sub> <sup>2</sup> | T <sub>P</sub>    | 20–40                         | sec  |

Notes:

1. Stresses beyond those listed in this table may cause permanent damage to the device. Functional operation specification compliance is not implied at these conditions. Exposure to maximum rating conditions for extended periods may affect device reliability.

2. The device is compliant with JEDEC J-STD-020.

Si569 Data Sheet • Dual CMOS Buffer

### 3. Dual CMOS Buffer

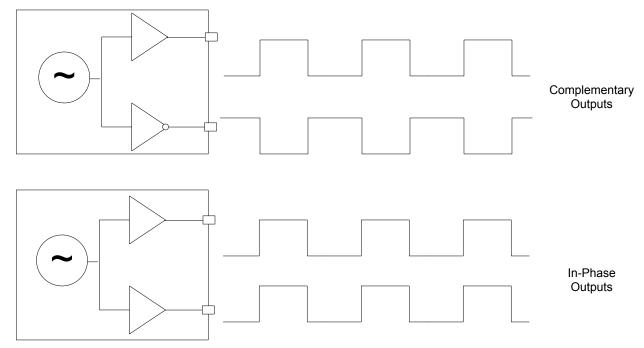

Dual CMOS output format ordering options support either complementary or in-phase signals for two identical frequency outputs. This feature enables replacement of multiple VCXOs with a single Si569 device.

Figure 3.1. Integrated 1:2 CMOS Buffer Supports Complementary or In-Phase Outputs

### 4. Recommended Output Terminations

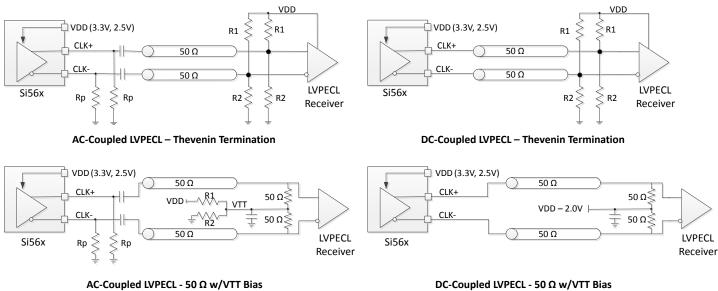

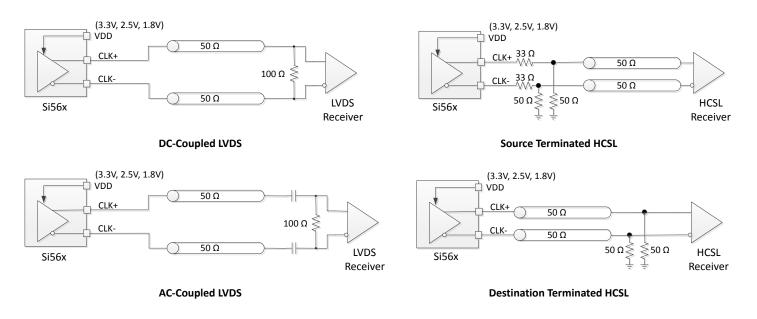

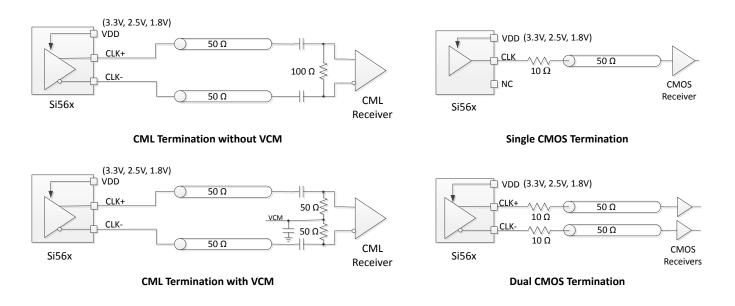

The output drivers support both AC-coupled and DC-coupled terminations as shown in figures below.

AC-Coupled LVPECL - 50 Ω w/VTT Bias

| AC-Coupled LVPECL<br>Termination Resistor Values |        |       |       | DC-Coupled LVPECL mination Resistor Va |       |        |  |

|--------------------------------------------------|--------|-------|-------|----------------------------------------|-------|--------|--|

| VDD                                              | R1     | R2    | Rp    | VDD R1 R2                              |       |        |  |

| 3.3 V                                            | 82.5 Ω | 127 Ω | 130 Ω | 3.3 V                                  | 127 Ω | 82.5 Ω |  |

| 2.5 V                                            | 62.5 Ω | 250 Ω | 90 Ω  | 2.5 V                                  | 250 Ω | 62.5 Ω |  |

Figure 4.3. CML and CMOS Output Terminations

### 5. Configuring Si569 via I2C

The Si569 VCXO device contains a fixed frequency crystal and frequency synthesis IC using Skyworks patented DSPLL<sup>TM</sup> technology, all enclosed in a standard hermetically sealed voltage controlled crystal oscillator (VCXO) package. The internal crystal provides the reference frequency used by the DSPLL frequency synthesis IC. The center output frequency of the Si569 voltage controlled oscillator is set via I2C register settings in the DSPLL frequency synthesis IC. The output frequency is then pulled higher or lower by applying a voltage above or below VDD/2 to the VC pin. The amount of output frequency change per volt is based on a programmed ppm/V (Kv) register setting. DSPLL technology provides unmatched frequency flexibility with superior output jitter/phase noise performance and part per trillion frequency accuracy. This section describes how to calculate the required Si569 register values used to set device output frequency and Kv gain, and how to load these values into the Si569 device.

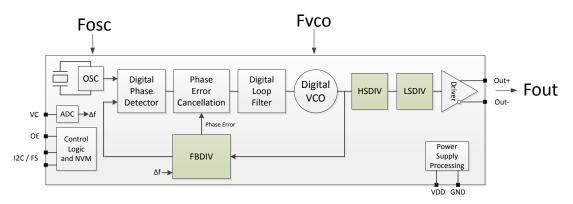

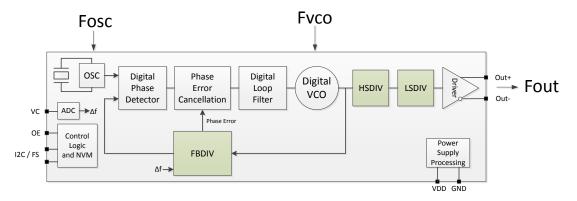

Figure 5.1. Si569 Block Diagram

The figure above is a simplified high-level block diagram of the Si569 VCXO device. The output frequency is set by a combination of three divider blocks highlighted in the above block diagram.

- 1. FBDIV DSPLL<sup>TM</sup> Feedback Divider used to set Digital VCO frequency

- 2. HSDIV High-Speed Output Divider

- 3. LSDIV Low-Speed Output Divider

The final device output frequency (Fout) is based on the digital VCO frequency (Fvco) divided by the product of the HSDIV and LSDIV divider values. The digital VCO frequency is based on the crystal reference frequency (OSC) multiplied by the feedback divider setting (FBDIV). The FBDIV value is set via I2C registers and is modulated depending on the voltage on the Vc pin. The amount of digital VCO frequency variation for a given Vc voltage in ppm/V depends on the Kv register setting. The limits of each of these internal blocks (digital VCO and dividers) determines the valid operating frequency range of the device.

The FBDIV divider is a fractional fixed-point divider with a total length of 43 bits consisting of an 11-bit integer field (FBINT) and a 32 bit fractional field (FBFRAC) where total FBDIV = [FBINT].[FBFRAC] with an implied decimal point as shown. This bit format is known as an 11.32 fixed point format where the integer portion is 11 bits and fractional portion is 32 bits, for a total of 43 bits.

The HSDIV divider is an integer divider, 11 bits in length, containing a binary divider value. One noteworthy feature of the HSDIV divider is a special duty cycle correction circuit that allows **odd** divide ratios of lower divider values (4-33 only) with 50% duty cycle output. This feature is useful when LSDIV divide ratio is set to 1.

The LSDIV divider performs power-of-2 divides ranging from divide by 1 ( $2^0$ ) to divide by 32 ( $2^5$ ). The register controlling the LSDIV divider is 3 bits in length, holding the power-of-2 divide ratio (divider exponent). For example, if the LSDIV register = 3 the LSDIV divide ratio is  $2^3 = 8$ . Note that LSDIV has a maximum value of 32 and therefore LSDIV register settings of 5, 6 or 7 will all result in the maximum divide-by-32 LSDIV operation.

The tables below summarize the divider limits for LSDIV, HSDIV, FBDIV. These limits and restrictions **must** be observed when deriving divider register values as will be explained in later sections.

#### Table 5.1. Si569 Divider Range Limits

| Divider                            | Upper Limit     | Lower Limit |

|------------------------------------|-----------------|-------------|

| HSDIV[10:0] (unsigned)             | 2046            | 4           |

| LSDIV[2:0] <sup>1</sup> (unsigned) | 32 (2^5)        | 1 (2^0)     |

| FBDIV[42:0] hex (unsigned)         | 7FDFFFFFFF      | 03C0000000  |

| FBDIV[42:0] int.frac (unsigned)    | 2045.9999999976 | 60.0        |

### Table 5.2. Additional LSDIV and HSDIV Divider Restrictions

| LSDIV          | Divide Ratio | HSDIV Value Restrictions               |

|----------------|--------------|----------------------------------------|

| Register Value |              |                                        |

| 0              | 1            |                                        |

| 1              | 2            |                                        |

| 2              | 4            |                                        |

| 3              | 8            | 5-33 even or odd values <sup>1</sup> , |

| 4              | 16           | 34-2046 even values only               |

| 5              | 32           |                                        |

| 6              | 32           |                                        |

| 7              | 32           |                                        |

| Note:          | 1            |                                        |

1. HSDIV can implement low value (5-33) **odd** divide ratios while providing a 50% duty cycle output due to special duty cycle correction circuit.

Note that all divider values (FBDIV, HSDIV, LSDIV) are unsigned and contain only positive values.

The Si569 high-performance VCXO family has four different speed grade offerings, each covering a specific frequency range. The table below outlines the output frequency range coverage by each speed grade, the corresponding min and max VCO frequency for that speed grade, and the nominal crystal frequency. The information in the table below is needed when calculating divider settings for a given device, speed grade, and output frequency.

| Table 5.3. | Si569 Speed Grades, | <b>Crystal Frequency</b> , | and VCO Range Limits |

|------------|---------------------|----------------------------|----------------------|

|------------|---------------------|----------------------------|----------------------|

| Device | Speed Grade | Xtal freq (MHz) | Min Output Freq<br>(MHz) | Max Output<br>Freq (MHz) | Min Fvco (GHz) | Max Fvco (GHz) |

|--------|-------------|-----------------|--------------------------|--------------------------|----------------|----------------|

| Si569  | A           | 152.6           | 0.2                      | 3000                     | 10.8           | 13.122222022   |

|        | В           | 152.6           | 0.2                      | 1500                     | 10.8           | 12.511886114   |

|        | С           | 152.6           | 0.2                      | 800                      | 10.8           | 12.206718160   |

|        | D           | 152.6           | 0.2                      | 325                      | 10.8           | 12.206718160   |

Si569 Data Sheet • Configuring Si569 via I2C

### 5.1 Output Frequency and Kv Gain Calibration Equations

The basic equations used to derive the output frequency are given below and can be inferred from the device block diagram in Figure 5.2 Si569 Frequency Definition Block Diagram on page 15. Equation 1 is the relationship between the output frequency (Fout), and the VCO frequency (Fvco) and total output divider ratio (HSDIV \* LSDIV). Equation 2 is the relationship between the VCO frequency (Fvco), the fixed crystal oscillator frequency (Fosc), and the feedback divider (FBDIV). Equation 2 also includes frequency adjustment ( $\Delta$ f) using the input control voltage (Vc) and the ppm/V control voltage gain (Kv).

Fout = Fvco / (HSDIV x LSDIV)

#### Equation 1

#### Fvco = (Fosc x FBDIV) x (1 + $\Delta$ f) (offset freq in ppm)

#### **Equation 2a**

Fvco = (Fosc x FBDIV) x (1 + [(Vc - VDD/2) \* Kv])

#### **Equation 2b**

Figure 5.2. Si569 Frequency Definition Block Diagram

Equation 3a is a rearranged Equation 1 to solve for the total output divider (HSDIV \*LSDIV) given Fout and Fvco. Equation 3b is rearranged again solving for Fvco given Fout and (HSDIV \* LSDIV).

(HSDIV x LSDIV) = Fvco / Fout

#### **Equation 3a**

Fvco = Fout x (HSDIV x LSDIV)

#### **Equation 3b**

Equation 4a is a rearranged Equation 2b to now solve for FBDIV given Fvco, Vc, VDD, Kv, and Fosc. Equation 4b simplifies Equation 4a to determine the FBDIV value for the center output frequency when Vc = VDD/2.

FBDIV = (Fvco / Fosc) / [1 + (Vc - VDD/2) \* Kv]

#### **Equation 4a**

FBDIV = Fvco / Fosc for Vc = VDD/2 (center frequency)

#### **Equation 4b**

Equations 3a, 3b, 4a, and 4b will be used in the process of deriving the required divider values to provide a desired center output frequency (Fout). The basic process is outlined in the next section.

Whenever the Fvco frequency is modified from the factory default, it is necessary to re-calibrate Kv gain. This is because the Vc ADC input sampling rate is tied to Fvco and is factory calibrated to 80 MHz based on the factory Fvco setting. Whenever Fvco is modified to change the output center frequency, the Vc ADC sampling rate is also changed so the full-scale Kv gain must be re-calculated.

#### CADC\_FSGAIN = round (128 \* nominal Vc ADC sampling rate / new Vc ADC sampling rate)

#### **Equation 5a**

#### CADC\_FSGAIN = round (128 \* 80e6 / (Fvco / NFXDIV / 8))

#### **Equation 5b**

Equations 5a and 5b are used along with the table below to re-calculate the Kv full scale gain. This process is also outlined in the next section.

#### Table 5.4. Si569 NFXDIV Values for Different FBDIV Integer Values

| FBDIV Min | FBDIV Max | NFXDIV Value |

|-----------|-----------|--------------|

| _         | 71.999999 | 16           |

| 72.000000 | 78.999999 | 18           |

| 79.000000 | 85.999999 | 20           |

| 86.000000 | —         | 22           |

#### 5.2 General Process Steps for Divider Calculations and Kv Gain Calibration

- 1. Estimate a theoretical total output divider value (HSDIV \* LSDIV) based on desired Fout while targeting the minimum valid Fvco frequency using Equation 3a and Table 5.3 Si569 Speed Grades, Crystal Frequency, and VCO Range Limits on page 14. Use floating point calculations for this step.

- Result: Floating point value of total output divider (HSDIV \* LSDIV) for Fvco minimum.

- 2. Derive a valid LSDIV divider value based on LSDIV and HSDIV divider limitations. Use the lowest possible integer value for LSDIV. For example, if the floating point output divider (HSDIV \* LSDIV) for Fvco minimum = 8.22, use LSDIV = 1 and HSDIV = 8.22 versus LSDIV = 2 and HSDIV = 4.11.

- Result: Valid integer LSDIV value.

- 3. Using the LSDIV value from #2 above, find the nearest valid **integer** HSDIV divider value resulting in Fvco being **equal to or greater than Fvco min**, observing all HSDIV limitations. Use Equations 3a/3b as necessary.

- · Result: Valid integer HSDIV value.

- 4. With valid integer HSDIV and LSDIV values, calculate the target Fvco center frequency with Equation. 3b. (Fvco must remain in the valid range per Table 5.3 Si569 Speed Grades, Crystal Frequency, and VCO Range Limits on page 14.)

- Result: Valid Fvco frequency.

- 5. With the derived valid Fvco frequency, use Equation 4b to calculate the required FBDIV based on the device specific Fosc frequency from Table 5.3 Si569 Speed Grades, Crystal Frequency, and VCO Range Limits on page 14. Assume Vc = VDD/2 to calculate an FBDIV value for the center Fout frequency.

- Result: Valid fractional FBDIV value

- 6. At this point all FBDIV, HSDIV and LSDIV values required to generate the desired center output frequency have been calculated. These three divider values must be now be appropriately formatted to fit the register format expected by the device. This is described in a later section.

- · Result: Valid register values for FBDIV, HSDIV, LSDIV

- 7. To re-calibrate Kv gain, first determine the integer portion of the new FBDIV value in step #5 above using truncation (not rounding) and then use that value to select the correct NFXDIV value using Table 5.4 Si569 NFXDIV Values for Different FBDIV Integer Values on page 16.

- Result: Valid NFXDIV value

- 8. To complete Kv gain calibration, calculate the new Kv gain calibration value (CADC\_FSGAIN) using Equation 5b. This Kv gain calibration value must be appropriately formatted to fit the register format expected by the device. This is described in a later section.

- · Result: Valid CADC FSGAIN value

#### 5.3 Example: Deriving Si569 Divider Settings for 156.75 MHz Output

The general process of deriving divider values for a specific output frequency is outlined in the previous section and now will be used in this example. To reiterate, all calculations must be done while observing divider limits and valid VCO frequency range limits for your device. In this example, the device is Si569 and with a desired output frequency of 156.75 MHz, the speed grade required will be "D" or better. (One important note: All divider and register settings derived for any speed grade will work without modification for all **faster** speed grades on the same base part number device.)

## Example VB code that implements the following divider calculation process is given in 5.10 Si569 Frequency Planner VB Code and can be used for implementing any supported output frequency.

**Step 1:** Find the valid theoretical lower limit of the total output divider (HSDIV\*LSDIV) based on the desired output frequency and lowest valid VCO frequency. This will bias the divider solution to the lowest possible VCO frequency since this will provide the best performance solution.

Given the valid Si569 VCO range is 10.8000 GHz to 13.1222 GHz, the minimum theoretical values for (HSDIV \* LSDIV) for the example 156.75 MHz output frequency are given in Equation 3:

Minimum (HSDIV\*LSDIV) = (10.8000 GHz / 156.75 MHz) = 68.89952...

**Step 2:** Find valid LSDIV divisor value given minimum (HSDIV\*LSDIV) from step 1. For best performance, preference should be given to implementation of the total output divider (HSDIV\*LSDIV) using HSDIV with LSDIV divide ratio = 1, if possible. Use LSDIV divide ratios > 1 only if HSDIV alone cannot implement the required output divider. Since the total (HSDIV\*LSDIV) value of 68.8995... is less than the HSDIV maximum divider value of 2046, the LSDIV divide **ratio** value will be 1, which corresponds to a LSDIV register setting of 0, since the LSDIV divider can only be a power of 2 value (see Table 5.2 Additional LSDIV and HSDIV Divider Restrictions on page 14 for valid LSDIV settings).

#### LSDIV divide ratio = $\underline{1}$ , therefore **LSDIV register value = \underline{0}**

**Step 3:** Find HSDIV divisor value. Given LSDIV = 1, HSDIV must implement 68.8995... or greater. Since HSDIV is an integer divider, the next greatest integer is 69. But, checking valid HSDIV values when LSDIV divide ratio = 1, we see 69 is NOT valid since it is greater than 33 and an odd value. This means the next greater integer value must be used, which is 70 (now even value). Note that 68 would **not** be valid since 68 is less than 68.8995... and would result in a VCO frequency below the lower VCO frequency limit.

#### HSDIV divide ratio = $\underline{70}$ , which gives **HSDIV register value = \underline{70} decimal (or hex value = \underline{0x46})**

**Step 4:** Calculate a valid VCO frequency and corresponding floating point FBDIV value. Given the calculated output divider value (HSDIV\*LSDIV) = 70, the VCO frequency must be set to (156.75 MHz \* 70) = **10.9725 GHz**. Note that 10.9725 GHz is indeed within the valid VCO frequency range per Table 5.3 Si569 Speed Grades, Crystal Frequency, and VCO Range Limits on page 14.

#### Fvco = 10.9725 GHz

**Step 5:** Calculate the FBDIV value necessary to provide a 10.9725 GHz Fvco using a 152.6 MHz crystal as reference (Si569 device). The floating point FBDIV value required to attain 10.9725 GHz with a 152.6 MHz crystal reference can be calculated as follows:

#### FBDIV (float) = 10.9725 GHz / 152.6 MHz = 71.9036697247707

**Step 6:** Format each divider value into the required register format. LSDIV and HSDIV are simply binary values and can be directly used. FBDIV must first be put into 11.32 fixed point format. Converting the floating point FBDIV value into the 11.32 fixed point hex value required by the Si569 is done as follows:

Integer value = 71 decimal. Convert 71 to 11 bit hex = 0x047. This is FBINT.

**Fractional** value = 0.9036697247707. Multiply fractional value by  $2^{32} = 3881231914.2752$ . Now extract only the **integer** part of the result which is 3881231914. Convert 3881231914 to 32 bit hex =  $0 \times E756E62A$ . This is FBFRAC.

The resulting 11.32 fixed point hex number is therefore:

#### FBDIV = FBINT.FBFRAC = 0x047E756E62A

At this point we have calculated all the required divider values. The table below summarizes the resulting divider values for implementing a 156.75 MHz output clock on the Si569.

| Divider Register | Decimal Value    | Hex Value     | Reg Length (bits) |

|------------------|------------------|---------------|-------------------|

| LSDIV            | 0                | 0x0           | 3                 |

| HSDIV            | 70               | 0x046         | 11                |

| FBDIV            | 71.9036697247707 | 0x047E756E62A | 43 (11+32)        |

#### Table 5.5. Divider Register Values for Si569 Configured for 156.75 MHz Output Clock

#### 5.4 Example: Deriving Si569 Kv Gain Settings for 156.75 MHz Output

Whenever the Fvco frequency is modified from the factory default it is necessary to re-calibrate Kv gain.

Step 1: Find the Fvco and FBDIV values from the new configuration to be used for Equation 5b.

#### Fvco = 10.9725 GHz

#### FBDIV (float) = 10.9725 GHz / 152.6 MHz = 71.9036697247707

Step 2: Use the integer portion of FBDIV to find the correct value for NFXDIV using Table 5.4 Si569 NFXDIV Values for Different FBDIV Integer Values on page 16. Do not round up the integer portion of FBDIV, instead truncate FBDIV down via the floor function.

FBDIV (int) = floor (10.9725 GHz / 152.6 MHz) = floor (71.9036697247707) = <u>71</u>

#### Excerpt from Table 5.4 Si569 NFXDIV Values for Different FBDIV Integer Values on page 16:

| FBDIV Min | FBDIV Max | NFXDIV Value |

|-----------|-----------|--------------|

| _         | 71.999999 | <u>16</u>    |

| 72.000000 | 78.999999 | 18           |

Step 3: Calculate the new CADC\_FSGAIN calibration value using Fvco, FBDIV (int) and NFXDIV.

CADC\_FSGAIN = round (128 \* 80e6 / (Fvco / NFXDIV / 8))

CADC\_FSGAIN = round (128 \* 80e6 / (10.9725e9 / 16 / 8))

CADC\_FSGAIN = round (119.455) = <u>119</u> = <u>0x77</u>

### 5.5 Mapping Divider Settings into Register Values

For the previous 156.75 MHz example, the divider value to register mapping is shown in the table below. Note that Register 24 is a packed register and contains bits from both LSDIV and HSDIV registers as follows: LSDIV[2:0] maps into Reg24[6:4] and HSDIV[10:8] maps into Reg24[2:0]. Note that bits Reg24[7] and Reg24[3] are not used and indicated with 'x' in the RegName field below. See also the Register Map Reference section for specific bit positioning within registers.

#### Table 5.6. Si569 Divider Register Values for 156.75 MHz Output Clock Configuration

| Register (Decimal) | Hex Value | Reg Name                   |

|--------------------|-----------|----------------------------|

| 23                 | 46        | HSDIV[7:0]                 |

| 24                 | 00        | x:LSDIV[2:0]:x:HSDIV[10:8] |

|                    |           |                            |

| 26                 | 2A        | FBDIV[7:0]                 |

| 27                 | E6        | FBDIV[15:8]                |

| 28                 | 56        | FBDIV[23:16]               |

| 29                 | E7        | FBDIV[31:24]               |

| 30                 | 47        | FBDIV[39:32]               |

| 31                 | 00        | FBDIV[42:40]               |

| 35                 | 77        | CADC_FSGAIN[7:0]           |

#### 5.6 I2C Register Write Procedure to Set Output Frequency

After the frequency setting registers (Reg 23-Reg31) are calculated, there is a procedure that must be followed involving other specific control registers for the device to properly use the new frequency setting registers. Simply writing Reg23-Reg31 is not enough. The following procedure must be performed as shown to properly configure the Si569 for the desired output frequency. In other words, all the following register writes must be done, and **in the exact sequence shown**.

This programming sequence consists of three distinct phases.

- 1. Writing to specific registers to get the device ready to be updated.

- 2. Writing the calculated frequency (divider) settings for the desired output frequency.

- 3. Writing to specific registers necessary to start-up the device after divider registers have been updated. The new output frequency will appear on output.

The divider values shown in the table below are for the previously described Si569 example for an output frequency of 156.75 MHz (for other frequencies, replace the divider values in registers 23-31 with values specific to your frequency requirements).

#### Table 5.7. Si569 Register Write Sequence to Set Output Frequency

| Register (decimal) | Write Data (hex) | Description                                                | Purpose                     |

|--------------------|------------------|------------------------------------------------------------|-----------------------------|

| 255                | 0x00             | Set page register to point to page 0                       | Get Device Ready for Update |

| 69                 | 0x00             | Disable FCAL override (to allow FCAL for this Freq Update) |                             |

| 17                 | 0x00             | Synchronously disable output                               |                             |

| 23                 | 0x46             | HSDIV[7:0]                                                 |                             |

| 24                 | 0x00             | LSDIV[2:0]:HSDIV[10:8]                                     |                             |

| 26                 | 0x2A             | FBDIV[7:0]                                                 |                             |

| 27                 | 0xE6             | FBDIV[15:8]                                                | Lindete Dividere            |

| 28                 | 0x56             | FBDIV[23:16]                                               | Update Dividers             |

| 29                 | 0xE7             | FBDIV[31:24]                                               |                             |

| 30                 | 0x47             | FBDIV[39:32]                                               |                             |

| 31                 | 0x00             | FBDIV[42:40]                                               |                             |

| 35                 | 0x77             | CADC_FSGAIN[7:0]                                           | Update Kv Gain              |

| 7                  | 0x08             | Start FCAL using new divider values                        | Startup Device              |

| -                  | —                | Internal FCAL VCO calibration<br>(30 ms delay)             |                             |

| 17                 | 0x01             | Synchronously enable output                                |                             |

#### 5.7 Digitally Controlled Oscillator – ADPLL: Small, Fast Frequency Changes

The Si569 can make small, fast frequency adjustments over a range of +/- 950 ppm (parts-per-million) around the device output frequency (set as described in previous sections). This mode is typically used in applications requiring a digitally controlled oscillator (DCO) for digital PLL or other types of frequency control loops. We refer to this type of application as an all-digital PLL or ADPLL.

For ADPLL applications and superior ADPLL performance, Skyworks recommends the Si548 I2C oscillator. The Si548 is a 6-pin device that features lower jitter than the Si569 while I2C lines are active, due to the different physical location of the SDA/SCL pins on the package.

The ADPLL mode uses a single 24 bit register, ADPLL\_DELTA\_M[23:0], to add an offset to the VCO frequency to affect the small frequency change. This offset is added in a synchronous fashion to prevent frequency discontinuities and can be updated as fast as the max I2C bus speed of 1 MHz will allow. The frequency offset can be positive or negative over a range of -950 ppm to +950 ppm with 0.0001164 ppm resolution.

The equation for this frequency change is simply,

#### ADPLL DELTA M[23:0] = $\triangle$ FoutPPM / 0.0001164

Where  $\Delta$  Fout<sub>PPM</sub> is the desired ppm change in output frequency, ADPLL\_DELTA\_M[23:0] is a two's complement 24 bit value, and 0.0001164 is a constant per-bit ppm value. The 24 bit ADPLL\_DELTA\_M[23:0] value is written into three sequential 8 bit registers in LSByte to MSByte order via I2C. Upon writing the MSByte, the frequency change takes effect. Below is an example VB to implement this feature. (Note that writing ADPLL\_DELTA\_M[23:0] = 0x000 will result in no frequency offset and return to the nominal output frequency.)

VB Code example for ADPLL (small frequency change) calculation and operation:

```

nAddr = Device I2C address

PPM_Delta = desired PPM frequency shift

Function Set_ADPLL(ByVal nAddr As UInteger, ByVal PPM_Delta As Double) As Integer

Dim ADPLL_PPM_StepSize As Double = 0.0001164

Dim ADPLL_Delta_M As Integer

Dim Reg231 As UInteger = 0

Dim Reg232 As UInteger = 0

Dim Reg233 As UInteger = 0

Dim ReturnCode As Integer = 0 '1=OK, -1 PPM requested is out of bounds

If (PPM_Delta <= 950 And PPM_Delta >= -950) Then

ADPLL_Delta_M = (PPM_Delta / ADPLL_PPM_StepSize)

Reg231 = (ADPLL_Delta_M And &HFF)

Reg232 = (ADPLL_Delta_M >> 8) And &HFF

Reg233 = (ADPLL_Delta_M >> 16) And &HFF

I2C_Write(nAddr, 0, 231, Reg231) 'write "Reg231" value to register 231 at nAddr, page 0 (LSByte)

I2C_Write(nAddr, 0, 232, Reg232) 'write "Reg232" value to register 232 at nAddr, page 0

'write "Reg233" value to register 233 at nAddr, page 0

I2C_Write(nAddr, 0, 233, Reg233)

(MSByte)

ReturnCode = 1

Else

ReturnCode = -1

End If

Return (ReturnCode)

End Function

```

#### 5.8 Configuring High Drive LVDS Swing

The Si569 LVDS clock output swing can be increased 100 mV via I2C to have the same swing as AC-coupled CML. This is done by programming the three registers as shown in the table below.

| Register Address (dec) | Output Drive          | LVDS (dec) | High Drive LVDS / CML (dec) |

|------------------------|-----------------------|------------|-----------------------------|

| 16 [5:0]               | OD_DRV_TRIM_V3P3[5:0] | 17         | 20                          |

| 125 [5:0]              | OD_DRV_TRIM_V2P5[5:0] | 20         | 23                          |

| 126 [5:0]              | OD_DRV_TRIM_V1P8[5:0] | 22         | 25                          |

#### Table 5.8. LVDS and CML Output Drive Settings

#### 5.9 Register Map Reference

| Register  |                   |                                                                                             |                   | Regist            | ter Bit           |           |             |        | Туре | Reset |

|-----------|-------------------|---------------------------------------------------------------------------------------------|-------------------|-------------------|-------------------|-----------|-------------|--------|------|-------|

| (decimal) | 7                 | 6                                                                                           | 5                 | 4                 | 3                 | 2         | 1           | 0      |      | Value |

| 0         |                   | DEVICE_TYPE[7:0]                                                                            |                   |                   |                   |           |             |        | R    | 0x45  |

| 7         | RESET             | RESET <reserved> = 3'b000     MS_ICAL     <reserved> = 3'b000       2</reserved></reserved> |                   |                   |                   |           |             | 'b000  | R/W  | 0x00  |

| 17        |                   |                                                                                             |                   | <unused></unused> |                   |           |             | ODC_OE | R/W  | 0x01  |

| 23        |                   |                                                                                             |                   | HSDI              | <b>V</b> [7:0]    |           |             |        | R/W  | 0x54  |

| 24        | <unused></unused> |                                                                                             | LSDIV[2:0]        |                   | <unused></unused> |           | HSDIV[10:8  | ]      | R/W  | 0x00  |

| 26        |                   | FBDIV[7:0]                                                                                  |                   |                   |                   |           |             | R/W    | 0x00 |       |

| 27        |                   | FBDIV[15:8]                                                                                 |                   |                   |                   |           | R/W         | 0x00   |      |       |

| 28        |                   | FBDIV[23:16]                                                                                |                   |                   |                   |           |             | R/W    | 0x00 |       |

| 29        |                   | FBDIV[31:24]                                                                                |                   |                   |                   |           |             | R/W    | 0x00 |       |

| 30        |                   |                                                                                             |                   | FBDIV             | [39:32]           |           |             |        | R/W  | 0x64  |

| 31        |                   |                                                                                             | <unused></unused> |                   |                   | I         | FBDIV[42:40 | )]     | R/W  | 0x00  |

| 32        |                   | <unused></unused>                                                                           |                   |                   | К                 | V_VCXO[4: | 0]          |        | R/W  | 0x06  |

| 35        |                   |                                                                                             |                   | CADC_FS           | GAIN[7:0]         |           |             |        | R/W  | 0x80  |

| 69        | FCAL_OVR          | FCAL_OVR <reserved> = 7'b0000001</reserved>                                                 |                   |                   |                   |           | R/W         | 0x01   |      |       |

| 231       |                   | ADPLL_DELTA_M[7:0]                                                                          |                   |                   |                   |           |             | R/W    | 0x00 |       |

| 232       |                   | ADPLL_DELTA_M[15:8]                                                                         |                   |                   |                   |           |             | R/W    | 0x00 |       |

| 233       |                   |                                                                                             | ŀ                 | ADPLL_DEL         | TA_M[23:16]       |           |             |        | R/W  | 0x00  |

| 255       |                   | <                                                                                           | Reserved>         | = 6'b00000        | )                 |           | PAG         | E[1:0] | R/W  | 0x00  |

### Table 5.9. Register Map Reference Summary

### Table 5.10. Register Bit Field Summary

| Register Bit Field Name | Bit Field (#bits) | Register | Description                                                                                                                                                                                                          |

|-------------------------|-------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DEVICE_TYPE[7:0]        | 8                 | 0        | Read only value of 69 (dec) which represents the device type (Si569)                                                                                                                                                 |

| RESET                   | 1                 | 7        | Set to 1 to reset device. Self clearing.                                                                                                                                                                             |

| MS_ICAL2                | 1                 | 7        | Set to 1 to initiate FCAL. Self clearing.                                                                                                                                                                            |

| ODC_OE                  | 1                 | 17       | Set to 0 to disable the output clock, and<br>remove output enable/disable control from<br>the external OE or OEB pin.<br>Set to 1 to return enable/disable control<br>back to the OE or OEB pin.                     |

| HSDIV[10:0]             | 11                | 23-24    | HSDIV is High-speed output divider value<br>in unsigned 11-bit binary format. Valid di-<br>vide values are from 5 to 2046, with values<br>of 5-33 even or odd, and values 34-2046<br>restricted to even values only. |

| Register Bit Field Name | Bit Field (#bits) | Register | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------------------|-------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LSDIV[2:0]              | 3                 | 24       | LSDIV sets a power-of-2 output divider.<br>Values of 0,1,2,3,4,5,6,7 result in divide ra-<br>tio of 1,2,4,8,16,32,32,32 respectively. Note<br>that a value of 0 (divide-by-1) essentially<br>bypasses this divider.                                                                                                                                                                                                                                                                                                                                                                                                            |

| FBDIV[42:0]             | 43                | 26-31    | The main DSPLL system feedback divide<br>(FBDIV) value for Si56x. This 43 bit value<br>is composed of an unsigned 11-bit integer<br>value (FBDIV[42:32]) concatenated with a<br>32-bit fractional value (FBDIV[31:0]), for an<br>11.32 fixed point binary format. The valid<br>range of the 11-bit integer part is from 60 to<br>2045.                                                                                                                                                                                                                                                                                         |

| KV_VCXO[4:0]            | 5                 | 32       | Sets Vc voltage control gain Kv (ppm/V).<br>Multiply the register value in decimal by 7.5<br>to get the actual Kv in ppm/V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CADC_FSGAIN[7:0]        | 8                 | 35       | Full-scale Kv gain parameter. Used to set<br>the (ppm/V) full-scale of the Vc input de-<br>pending on the programmed VCO frequen-<br>cy.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |