## HT8837C 1A 低电压 H 桥驱动器

- 1 特性

- 独立的 H 桥电机

- 驱动直流电机或其他负载

- 低 MOSFET 导通电阻: HS + LS 1 Ω

- 1A 最大驱动电流

- 工作电源电压范围: 0V 至 11V

- •标准脉宽调制 (PWM) 接口 (IN1/IN2)

- 低功耗休眠模式,休眠电流最大值仅为 120nA nSLEEP 引脚

- 小型封装尺寸

- 8 晶圆级小外形无引线 (WSON)(带外露散热焊盘)

- 2.0mm × 2.0mm

- 保护特性

- VCC 欠压闭锁 (UVLO)

- 过流保护 (OCP)

- 热关断 (TSD)

- 2 应用范围

- 摄像机

- 数字单镜头反光 (DSLR) 镜头

- 消费类产品

- 玩具

- 机器人技术

- 医疗设备

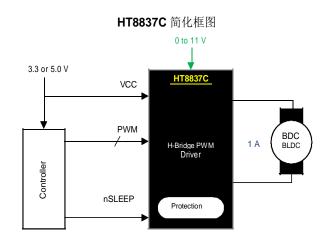

HT8837C器件提供了一套集成型电机驱动器解决方案,主要面向照相机、消费类产品、玩具以及其他低电压和电池供电类运动控制应用。此器件能够驱动一个直流电机或其他诸如螺线管的器件。输出驱动器模块由 配置为 H 桥的 N 沟道功率 MOSFET 组成,用以驱动

电且为 F 你的 N 內通功率 MOSFET 组成,用以驱动 电机绕组。一个内部电荷泵被用来生成所需的栅极驱动 电压。

HT8837C 器件可以提供高达 1A 的输出电流。该器件的电机电源电压为 0 至 11V,其控制逻辑工作电源 轨为 1.8V 至 5V。

HT8837C器件有一个 PWM (IN/IN) 输入接口。 此外,还提供用于过流保护、短路保护、欠压闭锁和过 热保护的内部关断功能。

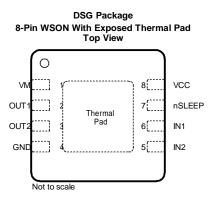

## 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN       |               | TYPE | DESCRIPTION                                                                                                                                                                                               |  |

|-----------|---------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME      | NAME NO. TYPE |      | DESCRIPTION                                                                                                                                                                                               |  |

| POWER AND | GROUND        |      |                                                                                                                                                                                                           |  |

| GND       | 4             | PWR  | Device ground<br>This pin must be connected to the PCB ground.                                                                                                                                            |  |

| VCC       | 8             | PWR  | Logic power supply<br>Bypass this pin to the GND pin with a 0.1-µF ceramic capacitor rated for VCC.                                                                                                       |  |

| VM        | 1             | PWR  | Motor power supply<br>Bypass this pin to the GND pin with a 0.1-µF ceramic capacitor rated for VM.                                                                                                        |  |

| CONTROL   |               |      |                                                                                                                                                                                                           |  |

| IN1       | 6             | I    | IN1 input                                                                                                                                                                                                 |  |

| IN2       | 5             | Ι    | IN2 input                                                                                                                                                                                                 |  |

| nSLEEP    | 7             | I    | Sleep mode input<br>When this pin is in logic low, the device enters low-power sleep mode. The device operates<br>normally when this pin is logic high. The pin has an internal pulldown resistor to GND. |  |

| OUTPUT    |               |      |                                                                                                                                                                                                           |  |

| OUT1      | 2             | 0    | Motor output                                                                                                                                                                                              |  |

| OUT2      | 3             | 0    | Connect this pin to the motor winding.                                                                                                                                                                    |  |

## **6** Specifications

## 6.1 Absolute Maximum Ratings

Over operating free-air temperature range (unless otherwise noted)<sup>(1)(2)</sup>

|                                            |                  | MIN       | MAX       | UNIT |

|--------------------------------------------|------------------|-----------|-----------|------|

| Motor power-supply voltage                 | VM               | -0.3      | 12        | V    |

| Logic power-supply voltage                 | ° cc             | -0.3      | 7         | V    |

| Control pin voltage                        | IN1, IN2, nSLEEP | -0.5      | 7         | V    |

| Peak drive current OUT1, OUT2              |                  | Internall | y limited | А    |

| Operating virtual junction temperature, TJ |                  | -40       | 150       | °C   |

| Storage temperature, T <sub>Stg</sub>      |                  | -60       | 150       | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltage values are with respect to network ground pin.

## 6.2 ESD Ratings

|       |               |                                                                                | VALUE | UNIT |

|-------|---------------|--------------------------------------------------------------------------------|-------|------|

| V     | Electrostatic | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±4000 |      |

| (ESD) | discharge     | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±1000 | V    |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 6.3 Recommended Operating Conditions

Over operating free-air temperature range (unless otherwise noted)

|         |                                  | MIN | MAX | UNIT |

|---------|----------------------------------|-----|-----|------|

| V<br>VM | Motor power-supply voltage       | 0   | 11  | V    |

| v<br>cc | Logic power-supply voltage       | 1.8 | 7   | V    |

| OUT     | Motor peak current               | 0   | 1   | А    |

| PWM     | Externally applied PWM frequency | 0   | 250 | kHz  |

| LOGIC   | Logic level input voltage        | 0   | 5.5 | V    |

| TA      | Operating ambient temperature    | -40 | 85  | °C   |

## 6.4 Thermal Information

over operating free-air temperature range (unless otherwise noted)

|               |                                              | HT8837C    |      |

|---------------|----------------------------------------------|------------|------|

|               | THERMAL METRIC <sup>(1)</sup>                | DSG (WSON) | UNIT |

|               |                                              | 8 PINS     |      |

| R<br>0JA      | Junction-to-ambient thermal resistance       | 60.9       | °C/W |

| κ<br>θJC(top) | Junction-to-case (top) thermal resistance    | 71.4       | °C/W |

| θΒ            | Junction-to-board thermal resistance         | 32.2       | °C/W |

| Ψ<br>Л        | Junction-to-top characterization parameter   | 1.6        | °C/W |

| Ψ<br>JB       | Junction-to-board characterization parameter | 32.8       | °C/W |

| κ<br>θJC(bot) | Junction-to-case (bottom) thermal resistance | 9.8        | °C/W |

## 6.5 Electrical Characteristics

$T_A = 25^{\circ}C$ , over recommended operating conditions unless otherwise noted

|                 | PARAMETER                                 | TEST CONDITIONS                                                                                   | MIN       | TYP      | МАХ      | UNIT |

|-----------------|-------------------------------------------|---------------------------------------------------------------------------------------------------|-----------|----------|----------|------|

| POWER           | SUPPLIES (VM, V <sub>CC</sub> )           |                                                                                                   |           |          |          |      |

| V<br>VM         | VM operating voltage                      |                                                                                                   | 0         |          | 11       | V    |

| I               |                                           | VVM = 5 V; VCC = 3 V;<br>No PWM                                                                   |           | 40       | 100      | μΑ   |

| VM              | VM operating supply current               | V <sub>VM</sub> = 5 V; V <sub>CC</sub> = 3 V;<br>50 kHz PWM                                       |           | 0.8      | 1.5      | mA   |

| <b> </b><br>VMQ | VM sleep mode supply current              | V <sub>VM</sub> = 5 V; V <sub>CC</sub> = 3 V;<br>nSLEEP = 0                                       |           | 30       | 95       | nA   |

| v<br>cc         | V <sub>CC</sub> operating voltage         |                                                                                                   | 1.8       |          | 7        | V    |

| 1               |                                           | V <sub>VM</sub> = 5 V; V <sub>CC</sub> = 3 V;<br>No PWM                                           |           | 300      | 500      | μA   |

| VCC             | V <sub>CC</sub> operating supply current  | V <sub>VM</sub> = 5 V; V <sub>CC</sub> = 3 V;<br>50 kHz PWM                                       |           | 0.7      | 1.5      | mA   |

| VCCQ            | V <sub>CC</sub> sleep mode supply current | $V_{VM} = 5 V; V_{CC} = 3 V;$<br>nSLEEP = 0                                                       |           | 5        | 25       | nA   |

| CONTRO          | DL INPUTS (IN1/PH, IN2/EN, nSLEE          | P)                                                                                                |           |          |          |      |

| °⊾              | Input logic-low voltage                   |                                                                                                   |           | 0.       | 25 × VCC | V    |

| • ін            | Input logic-high voltage                  |                                                                                                   | 0.5 × VCC |          |          | V    |

| V<br>HYS        | Input logic hysteresis                    |                                                                                                   | 0.        | 08 × VCC |          | V    |

| I<br>IL         | Input logic-low current                   | V <sub>INx</sub> = 0 V                                                                            | -5        |          | 5        | μA   |

| н               | Input logic-high current                  | V <sub>INx</sub> = 3.3 V                                                                          |           |          | 50       | μA   |

| PD              | Pulldown resistance                       |                                                                                                   |           | 100      |          | kΩ   |

|                 | DRIVER OUTPUTS (OUT1, OUT2)               |                                                                                                   |           |          |          |      |

| R<br>DS(ON)     | HS + LS FET on-resistance                 | V <sub>VM</sub> = 5 V; V <sub>CC</sub> = 3.3 V;<br>I <sub>O</sub> = 200 mA; T <sub>J</sub> = 25°C |           | 1000     |          | mΩ   |

| OFF             | Off-state leakage current                 |                                                                                                   | -200      |          | 200      | nA   |

| PROTEC          | CTION CIRCUITS                            |                                                                                                   |           |          |          |      |

| V               |                                           | V <sub>CC</sub> falling                                                                           |           |          | 1.7      | V    |

| UVLO            | V <sub>CC</sub> undervoltage lockout      | V <sub>CC</sub> rising                                                                            |           |          | 1.8      | V    |

| OCP             | Overcurrent protection trip level         |                                                                                                   | 1.2       |          |          | А    |

| DEG             | Overcurrent deglitch time                 |                                                                                                   |           | 1        |          | μS   |

| RETRY           | Overcurrent retry time                    |                                                                                                   |           | 1        |          | ms   |

| T(1)            | Thermal shutdown temperature              | Die temperature T                                                                                 | 150       | 160      | 180      | °C   |

(1) Not tested in production; limits are based on characterization data

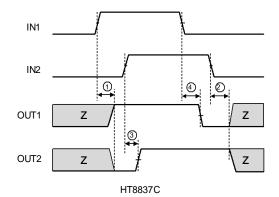

## 6.6 Timing Requirements

$T_{\text{A}} = 25^{\circ}\text{C}, \, \text{V}_{\text{VM}} = 5 \, \text{V}, \, \text{V}_{\text{CC}} = 3 \, \text{V}, \, \text{RL} = 20 \, \Omega$

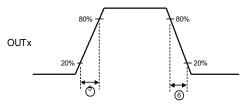

| NO. |           |                                                  |            | MIN | MAX | UNIT |

|-----|-----------|--------------------------------------------------|------------|-----|-----|------|

| 1   | t7        | Output enable time                               |            |     | 300 | ns   |

| 2   | t8        | Output disable time                              |            |     | 300 | ns   |

| 3   | tg        | Delay time, INx high to OUTx high                | - See 图 1. |     | 160 | ns   |

| 4   | 10        | Delay time, INx low to OUTx low                  | See 🛐 1.   |     | 160 | ns   |

| 5   | 11        | Output rise time                                 |            | 20  | 188 | ns   |

| 6   | נ<br>12   | Output fall time                                 |            | 20  | 188 | ns   |

| _   | ι<br>wake | ake Wake time, nSLEEP rising edge to part active |            |     | 30  | μS   |

图 1. Input and Output Timing for HT8837C

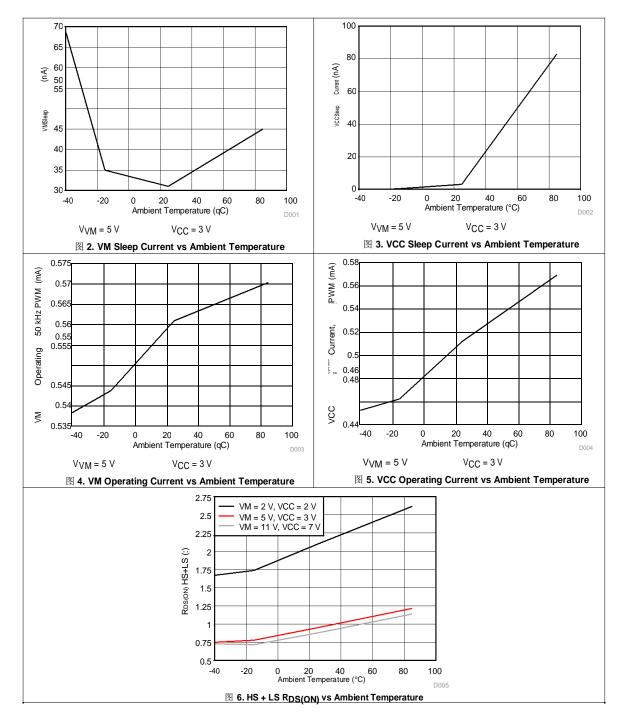

## 6.7 Typical Characteristics

Plots generated using characterization data.

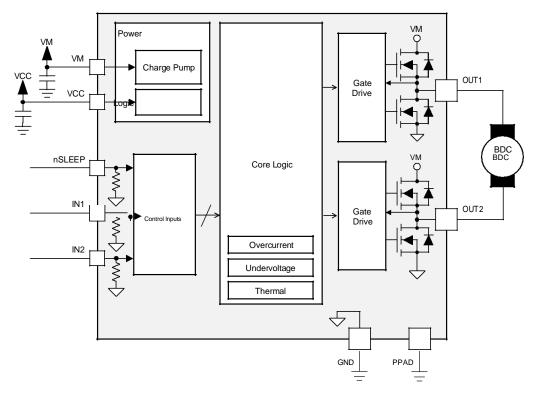

## 7 Detailed Description

## 7.1 Overview

The HT8837C device is an H-bridge driver that can drive one DC motor or other devices like solenoids. The outputs are controlled using a PWM interface (IN1/IN2).

A low-power sleep mode is included, which can be enabled using the nSLEEP pin.

This device greatly reduces the component count of motor driver systems by integrating the necessary driver FETs and FET control circuitry into a single device. In addition, the HT8837C device adds protection features beyond traditional discrete implementations: undervoltage lockout, overcurrent protection, and thermal shutdown.

## 7.2 Functional Block Diagram

## 7.3 Feature Description

#### 7.3.1 Bridge Control

The HT8837C device is controlled using a PWM input interface, also called an IN/IN interface. Each output is controlled by a corresponding input pin.

表 1 shows the logic for the HT8837C device.

| nSLEEP | IN1 | IN2 | OUT1 | OUT2 | FUNCTION (DC MOTOR) |

|--------|-----|-----|------|------|---------------------|

| 0      | Х   | Х   | Z    | Z    | Coast               |

| 1      | 0   | 0   | Z    | Z    | Coast               |

| 1      | 0   | 1   | L    | Н    | Reverse             |

| 1      | 1   | 0   | н    | L    | Forward             |

| 1      | 1   | 1   | L    | L    | Brake               |

#### 表 1. HT8837C Device Logic

#### 7.3.2 Sleep Mode

If the nSLEEP pin is brought to a logic-low state, the HT8837C device enters a low-power sleep mode. In this state, all unnecessary internal circuitry is powered down.

#### 7.3.3 Power Supplies and Input Pins

The input pins can be driven within the recommended operating conditions with or without the VCC, VM, or both power supplies present. No leakage current path exists to the supply. Each input pin has a weak pulldown resistor (approximately  $100 \text{ k}\Omega$ ) to ground.

The VCC and VM supplies can be applied and removed in any order. When the VCC supply is removed, the device enters a low-power state and draws very little current from the VM supply. The VCC and VM pins can be connected together if the supply voltage is between 1.8 and 7 V.

The VM voltage supply does not have any undervoltage-lockout protection (UVLO). As long as  $V_{CC} > 1.8$  V, the internal device logic remains active which means that the VM pin voltage can drop to 0 V, however, the load may not be sufficiently driven at low VM voltages.

#### 7.3.4 Protection Circuits

The HT8837C is fully protected against VCC undervoltage, overcurrent, and overtemperature events.

VCC undervoltage lockout If at any time the voltage on the VCC pin falls below the undervoltage lockout threshold voltage, all FETs in the H-bridge are disabled. Operation resumes when the VCC pin voltage rises above the UVLO threshold.

Overcurrent protection (OCP) An analog current-limit circuit on each FET limits the current through the FET by removing the gate drive. If this analog current limit persists for longer than t<sub>DEG</sub>, all FETs in the H-bridge are disabled. Operation resumes automatically after t<sub>RETRY</sub> has elapsed. Overcurrent conditions are detected on both the high-side and low-side devices. A short to the VM pin, GND, or from the OUT1 pin to theOUT2 pin results in an overcurrent condition.

**Thermal shutdown (TSD)** If the die temperature exceeds safe limits, all FETs in the H-bridge are disabled. After the die temperature falls to a safe level, operation automatically resumes.

| FAULT                   | CONDITION                      | H-BRIDGE                            | RECOVERY       |

|-------------------------|--------------------------------|-------------------------------------|----------------|

| VCC undervoltage (UVLO) | VCC < 1.7 V                    | Disabled                            | VCC > 1.8 V    |

| Overcurrent (OCP)       | I <sub>OUT</sub> > 1.2 A (MIN) | Disabled (retries<br>automatically) | tRETRY elapses |

| Thermal Shutdown (TSD)  | T <sub>J</sub> > 150°C (MIN)   | Disabled (retries<br>automatically) | TJ < 150°C     |

#### 表 2. Fault Behavior

## 7.4 Device Functional Modes

The HT8837C device is active unless the nSLEEP pin is brought logic low. In sleep mode the H-bridge FETs are disabled Hi-Z. The HT8837C device is brought out of sleep mode automatically if nSLEEP is brought logic high. The H-bridge outputs are disabled during undervoltage lockout, overcurrent, and overtemperature fault conditions.

|                   | 2                       |                                  |

|-------------------|-------------------------|----------------------------------|

| MODE              | CONDITION               | H-BRIDGE                         |

| Operating         | nSLEEP pin = 1          | Operating                        |

| Sleep mode        | nSLEEP pin = 0          | Disabled                         |

| Fault encountered | Any fault condition met | Disabled (retries automatically) |

| 表 3. Operation Modes | 表 3 | . Operation | Modes |

|----------------------|-----|-------------|-------|

|----------------------|-----|-------------|-------|

## 8 Application and Implementation

注

Information in the following applications sections is not part of the TI component specification, and TI does not warrant its accuracy or completeness. TI's customers are responsible for determining suitability of components for their purposes. Customers should validate and test their design implementation to confirm system functionality.

#### 8.1 Application Information

The HT8837C device is device is used to drive one DC motor or other devices like solenoids. The following design procedure can be used to configure the HT8837C device.

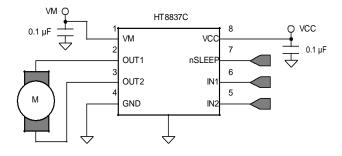

#### 8.2 Typical Application

#### 图 7. Schematic of HT8837C Application

#### 8.2.1 Design Requirements

$\pm$  4 lists the required parameters for a typical usage case.

| DESIGN PARAMETER     | REFERENCE | EXAMPLE VALUE |  |  |  |

|----------------------|-----------|---------------|--|--|--|

| Motor supply voltage | VM        | 9 V           |  |  |  |

| Logic supply voltage | VCC       | 3.3 V         |  |  |  |

| Target RMS current   | OUT       | 0.8 A         |  |  |  |

#### 表 4. System Design Requirements

#### 8.2.2 Detailed Design Procedure

#### 8.2.2.1 Motor Voltage

The appropriate motor voltage depends on the ratings of the motor selected and the desired RPM. A higher voltage spins a brushed dc motor faster with the same PWM duty cycle applied to the power FETs. A higher voltage also increases the rate of current change through the inductive motor windings.

#### 8.2.2.2 Low-Power Operation

When entering sleep mode, TI recommends setting all inputs as a logic low to minimize system power.

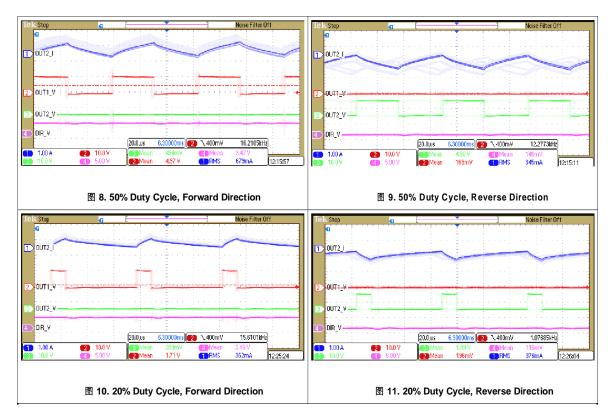

## 8.2.3 Application Curves

## 9 Power Supply Recommendations

#### 9.1 Bulk Capacitance

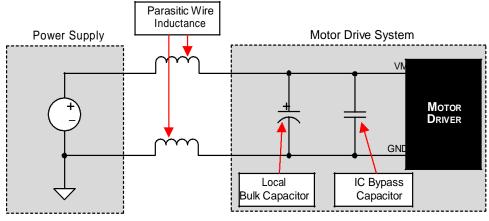

Having appropriate local bulk capacitance is an important factor in motor-drive system design. It is generally beneficial to have more bulk capacitance, while the disadvantages are increased cost and physical size.

The amount of local capacitance needed depends on a variety of factors, including:

- The highest current required by the motor system

- · The power-supply capacitance and ability to source current

- The amount of parasitic inductance between the power supply and motor system

- The acceptable voltage ripple

- The type of motor used (brushed dc, brushless dc, stepper)

- The motor braking method

The inductance between the power supply and motor drive system limits the rate at which current can change from the power supply. If the local bulk capacitance is too small, the system responds to excessive current demands or dumps from the motor with a change in voltage. When adequate bulk capacitance is used, the motor voltage remains stable and high current can be quickly supplied.

The data sheet generally provides a recommended value, but system-level testing is required to determine the appropriate size of bulk capacitor.

## Bulk Capacitance (接下页)

图 12. Example Setup of Motor Drive System With External Power Supply

The voltage rating for bulk capacitors should be higher than the operating voltage, to provide margin for cases when the motor transfers energy to the supply

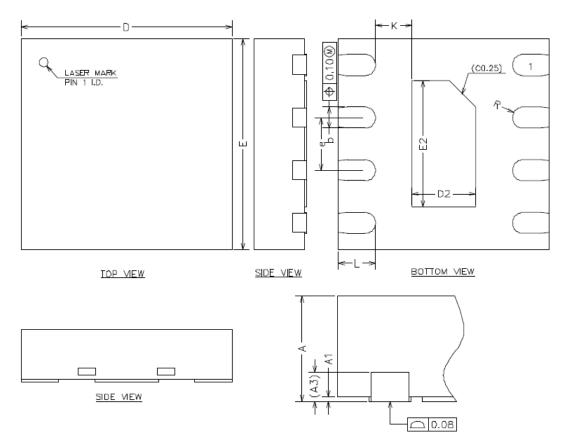

# DFN8 2\*2

## COMMON DIMENSIONS (UNITS OF MEASURE=MILLIMETER)

| SYMBOL | MIN     | NQM  | MAX  |

|--------|---------|------|------|

| A      | 0.70    | 0.75 | 0.80 |

| A1     | 0       | 0.02 | 0.05 |

| A3     | 0.20REF |      |      |

| b      | 0.15    | 0.20 | 0.25 |

| D      | 1,90    | 2.00 | 2.10 |

| E      | 1.90    | 2,00 | 2.10 |

| D2     | 0.5D    | 0.60 | 0.7D |

| E2     | 1.10    | 1.20 | 1.30 |

| €      | 0.40    | 0.5D | D.60 |

| K      | 0.20    | _    | _    |

| L      | 0.3D    | 0,35 | D.40 |

| R      | 0.09    | _    | _    |