# 2.4MHz 3A Step-Down Converter with I<sup>2</sup>C Interface

### **General Description**

The RT5738 is a step-down switching voltage regulator that delivers a digitally programmable output from an input voltage supply of 2.5V to 5.5V. The output voltage is programmed through an  $I^2C$  interface capable of operating up to 3.4MHz.

Using a proprietary architecture with synchronous rectification, the RT5738 is capable of delivering 3A continuous at over 80% efficiency, maintaining that efficiency at load currents as low as 10mA. The regulator operates at a nominal fixed frequency of 2.4MHz, which reduces the value of the external components. Additional output capacitance can be added to improve regulation during load transients without affecting stability.

At moderate and light loads, Pulse Frequency Modulation (PFM) is used to operate in Power-Save Mode with a typical quiescent current of 40µA at room temperature. Even with such a low quiescent current, the part exhibits excellent transient response during large load swings. At higher loads, the system automatically switches to fixed-frequency control, operating at 2.4MHz. In Shutdown Mode, the supply current is typically 0.1µA, excellent in reducing power consumption. PFM Mode can be disabled if fixed frequency is desired. The RT5738 is available in a small WL-CSP-15B 1.31x2.02 (BSC)

### Features

- 0.3V to 1.85V Programmable Slew Rate for Voltage Transitions

- Steady 2.4MHz Switching Frequency

- Best-in-Class Load Transient

- Continuous Output Current Capability : 3A

- 2.5V to 5.5V Input Voltage Range

- Digitally Programmable Output Voltage

- I<sup>2</sup>C-Compatible Interface Up to 3.4Mbps

- PFM Mode for High Efficiency in Light Load

- Quiescent Current in PFM Mode : 45µA (Typical)

- Input Under-Voltage Lockout (UVLO)

- Thermal Shutdown and Overload Protection

- 15-Ball WL-CSP Package

# Applications

- Application, Graphic, and DSP Processors

ARM<sup>™</sup>, Tegra<sup>™</sup>, OMAP<sup>™</sup>, NovaThor<sup>™</sup>, ARMADA<sup>™</sup>, Krait<sup>™</sup>, etc.

- Hard Disk Drives, LPDDR3, LPDDR4

- Tablets, Netbooks, Ultra-Mobile PCs

- Smart Phones

- Gaming Devices

### **Marking Information**

For marking information, contact our sales representative directly or through a Richtek distributor located in your area.

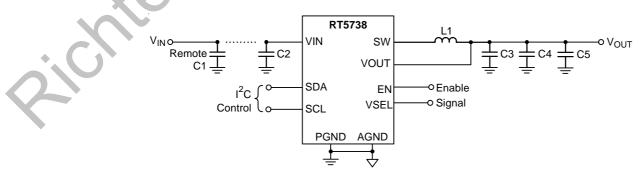

# **Simplified Application Circuit**

## **Ordering Information**

#### RT5738 🖵 🖵

Package Type

WSC : WL-CSP-15B 1.31x2.02 (BSC)

Power-Up Defaults (VSEL0/VSEL1)

A : 0.4V/0.6V B : 1.125V/1.125V C : 0.65V/0.7V

Note :

Richtek products are :

- RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- Suitable for use in SnPb or Pb-free soldering processes.

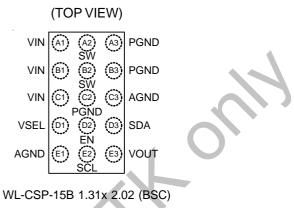

### Pin Configuration

| <b></b>    |          |                                                                                                                                                                                                                                                                                                                       |

|------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No.    | Pin Name | Pin Function                                                                                                                                                                                                                                                                                                          |

| A1, B1, C1 | VIN      | Power input voltage. Connect to the input power source. Connect to $C_{IN}$ with minimal path.                                                                                                                                                                                                                        |

| A2, B2     | SW       | Switching node. Connect to the inductor.                                                                                                                                                                                                                                                                              |

| A3, B3, C2 | PGND     | Power ground. The low-side MOSFET is referenced to this pin. $C_{\rm IN}$ and $C_{\rm OUT}$ should be returned with a minimal path to these pins.                                                                                                                                                                     |

| C3, E1     | AGND     | Analog ground. All signals are referenced to this pin. Avoid routing high dV/dt AC currents through this pin.                                                                                                                                                                                                         |

| D1         | VSEL     | Voltage select. When this pin is LOW, VOUT is set by the VSEL0 register. When this pin is HIGH, VOUT is set by the VSEL1 register. Polarity of pin in conjunction with the MODE bits in the Control register 02h, will select Forced PWM or Auto PFM/PWM mode of operation. VSEL0 = Auto PFM, and VSEL1 = Forced PWM. |

| D2         | EN       | Enable. The device is in Shutdown Mode when this pin is LOW. Device keeps register content when EN pin is LOW.                                                                                                                                                                                                        |

| D3         | SDA      | l <sup>2</sup> C serial data.                                                                                                                                                                                                                                                                                         |

| E2         | SCL      | I <sup>2</sup> C serial clock.                                                                                                                                                                                                                                                                                        |

| E3         | VOUT     | VOUT. Output voltage sense through this pin. Connect to output capacitor.                                                                                                                                                                                                                                             |

### **Functional Pin Description**

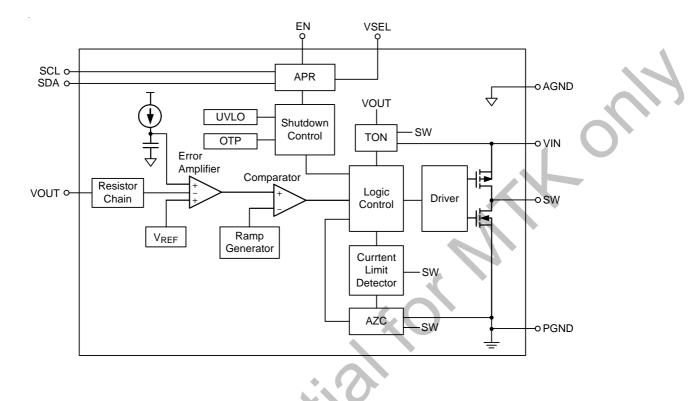

## **Functional Block Diagram**

# Operation

The RT5738 is a low voltage synchronous step-down converter that can support input voltage ranging from 2.5V to 5.5V and the output current can be up to 3A. The RT5738 uses ACOT<sup>™</sup> mode control. To achieve good stability with low-ESR ceramic capacitors, the ACOT uses a virtual inductor current ramp generated inside the IC. This internal ramp signal replaces the ESR ramp normally provided by the output capacitor's ESR. The ramp signal and other internal compensations are optimized for low-ESR ceramic output capacitors.

In steady-state operation, the feedback voltage, with the virtual inductor current ramp added, is compared to the reference voltage. When the combined signal is less than the reference, the on-time one-shot is triggered, as long as the minimum off-time one-shot is clear and the measured inductor current (through the synchronous rectifier) is below the current limit. The on-time one-shot turns on the high-side switch and the inductor current ramps up linearly. After the on-time, the high-side switch is turned off and the synchronous rectifier is turned on and the inductor current ramps down linearly. At the same

time, the minimum off-time one-shot is triggered to prevent another immediate on-time during the noisy switching time and allow the feedback voltage and current sense signals to settle. The minimum off-time is kept short so that rapidly-repeated on-times can raise the inductor current quickly when needed.

#### **PWM Frequency and Adaptive on Time Control**

The on-time can be roughly estimated by the equation :

$$T_{ON} = \frac{V_{OUT}}{V_{IN}} \times \frac{1}{f_{SW}}$$

where  $f_{SW}$  is nominal 2.4MHz

#### Auto-Zero Current Detector

The auto-zero current detector circuit senses the SW waveform to adjust the zero current threshold voltage. When the current of low side MOSFET decrease to the zero current threshold. The low-side MOSFET turns off to prevent negative inductor current. In this way, the zero current threshold can adjust for different condition to get better efficiency.

# **RT5738**

## **Under-voltage Protection (UVLO)**

The UVLO continuously monitors the voltage of VIN to make sure the device works properly. When the VCC is high enough to reach the high threshold voltage of UVLO. The step down converter softly start or pre-bias to its regulated output voltage. When the VIN decreases to its low threshold (350mV hysteresis), the device will shut down.

#### **Power GOOD**

When the output voltage is higher than PGOOD rising threshold, the PGOOD flag is High.

#### **Over-Current Protection (OCP)**

The RT5738 senses the current signal when low side MOSFET turns on and uses a valley current limiting circuit. As a result, the OCP set point is the OCP DC

limit minus half of the ripple current. The OCP is cycleby-cycle limit. If the OCP occurs, the converter holds off the next on pulse until inductor current drops below the OCP limit. If the OCP keeps and the load current is larger than the current provided by the converter over 16 consecutive times, the output voltage drops and the converter latches off before entering Hiccup mode. Latch off time is 1.7ms or 50ms by factory configuration.

#### Soft-Start

An internal current source charges an internal capacitor to build the soft-start ramp voltage. The typical soft start time can be programming by I<sup>2</sup>C.

#### **Over-Temperature Protection (OTP)**

The RT5738 has over temperature protection. When the device triggers the OTP, the device shuts down.

# Absolute Maximum Ratings (Note 1)

| Supply Input Voltage, VIN                      | 0.3V to 7V                       |   |

|------------------------------------------------|----------------------------------|---|

| Other I/O Pin Voltages                         | 0.3V to (V <sub>IN</sub> + 0.3V) | ) |

| • Power Dissipation, $P_D @ T_A = 25^{\circ}C$ |                                  |   |

| WL-CSP-15B 1.31x2.02 (BSC)                     | 2W                               |   |

| Package Thermal Resistance (Note 3)            |                                  |   |

| WL-CSP-15B 1.31x2.02 (BSC), θ <sub>JA</sub>    | 49.8°C/W                         |   |

| Junction Temperature                           | 150°C                            |   |

| Lead Temperature (Soldering, 10 sec.)          | 260°C                            |   |

| Storage Temperature Range                      | 65°C to 150°C                    |   |

| ESD Susceptibility (Note 4)                    |                                  |   |

| HBM (Human Body Model)                         | 2kV                              |   |

| MM (Machine Model)                             | 200V                             |   |

|                                                |                                  |   |

# Recommended Operating Conditions (Note 5)

| • Supply Input Voltage, V <sub>IN</sub> | <br>2.5V to 5.5V   |

|-----------------------------------------|--------------------|

| • Output Current, IOUT                  | <br>0A to 3A       |

| Junction Temperature Range              | <br>–40°C to 125°C |

| Ambient Temperature Range               | <br>–40°C to 85°C  |

### **Electrical Characteristics**

(V<sub>IN</sub> = 3.6V,  $T_A = -40^{\circ}$ C to 85°C, unless otherwise specified)

| Parar                       | neter          | Symbol                 | Test Conditions                                                                                         | Min | Тур  | Max  | Unit |

|-----------------------------|----------------|------------------------|---------------------------------------------------------------------------------------------------------|-----|------|------|------|

| Operating quie<br>PWM       | escent current | IQ_PWM                 | I <sub>LOAD</sub> = 0, MODE Bit = 1 (Forced PWM)                                                        |     | 15   | -    | mA   |

| Operating quie              | escent current | IQ_PFM                 | ILOAD = 0                                                                                               |     | 45   |      | μA   |

| H/W Shutdowr<br>Current     | n Supply       | ISHDN_H/W              | EN = GND                                                                                                |     | 0.1  | 3    | μA   |

| S/W Shutdowr<br>Current     | n Supply       | ISHDN_S/W              | $\label{eq:entropy} \begin{array}{l} EN = VIN, \ BUCK\_ENx = 0, \\ 2.5V \leq VIN \leq 5.5V \end{array}$ |     | 2    | 12   | μΑ   |

| Under-Voltage<br>Threshold  | Lockout        | Vuvlo                  | VIN Rising                                                                                              |     | 2.32 | 2.45 | V    |

| Under-Voltage<br>Hysteresis | Lockout        | Δνυνίο                 |                                                                                                         |     | 350  | -    | mV   |

| RDS(ON) of P-N              | NOSFET         | RDS(ON)_P              | $V_{IN} = 5V$                                                                                           |     | 30   | -    | mΩ   |

| RDS(ON) of N-M              | MOSFET         | R <sub>DS(ON)</sub> _L | $V_{IN} = 5V$                                                                                           |     | 17   |      | mΩ   |

|                             | Logic-High     | VIH                    | $2.5~V \leq V_{IN} \leq 5.5~V$                                                                          | 1.1 |      |      | V    |

| Input Voltage               | Logic-Low      | VIL                    | $2.5~V \leq V_{IN} \leq 5.5~V$                                                                          |     |      | 0.4  | v    |

| Input Bias Cur              | rent           | l <sub>IN</sub>        | Input Tied to GND or VIN                                                                                |     | 0.01 | 1    | μA   |

| Parameter                      | Symbol             | Test Conditions                                                                                                                                           | Min  | Тур  | Max  | Unit |

|--------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|

| VOUT DC Accuracy               |                    | $2.5 V \le V_{IN} \le 5.5 V$ , VOUT from<br>Minimum to Maximum, $V_{OUT} = 0.4V$ ,<br>Auto PFM/PWM (Note 5)                                               | -3   |      | 3    | %    |

| VOOT DE Accuracy               |                    | $\begin{array}{l} 2.5V \leq V_{IN} \leq 5.5V, \mbox{ VOUT from Minimum} \\ \mbox{to Maximum,} \\ V_{OUT} = 0.4V, \mbox{ Forced PWM (Note 5)} \end{array}$ | -1.5 |      | 1.5  | %    |

| Load Regulation                | $\Delta V_{LOAD}$  | I <sub>OUT(DC)</sub> = 1 to 3A                                                                                                                            |      | 0.1  |      | %/A  |

| Line Regulation                | ΔVLINE             | $\begin{array}{l} 2.5V \leq VIN \leq 5.5V, \\ I_{OUT(DC)} = 1.5A \end{array} \end{array} \label{eq:IOUT}$                                                 |      | 0.2  |      | %/V  |

| Transient load Response        | ACLOAD             | $I_{LOAD}$ Step 0.01 A to 1.5 A,<br>tr = tf = 500ns, $V_{OUT}$ = 1.125 V (Note 5)                                                                         |      | ±45  | -    | mV   |

| Line Transient                 | VLINE              | $V_{IN} = 3V$ to 3.6V, tr = tf = 10µs,<br>IOUT = 100mA, Forced PWM mode<br>(Note 5)                                                                       |      | ±40  |      | mV   |

| P-MOSFET Peak Current<br>Limit | I <sub>LIM_P</sub> | *                                                                                                                                                         | 5    | 5.5  | 6    | А    |

| Valley Current Limit           |                    | $\zeta$                                                                                                                                                   | 3.5  | 4    | 4.5  | А    |

| Thermal Shutdown               | T <sub>SD</sub>    |                                                                                                                                                           |      | 150  |      | °C   |

| Thermal Shutdown<br>Hysteresis | ΔTSD               |                                                                                                                                                           |      | 30   |      | °C   |

| Input OVP Shutdown             | VSDHD_OVPrth       | Rising Threshold                                                                                                                                          |      | 6.15 |      | V    |

| Input OVP Shutdown             | VSDHD_OVPfth       | Falling Threshold                                                                                                                                         | 5.5  | 5.73 |      | V    |

| Switching Frequency            | fsw                | Vout = 1.2V (Note 5)                                                                                                                                      | 2100 | 2400 | 2700 | kHz  |

| Minimum Off-Time               | A                  | X                                                                                                                                                         |      | 170  |      | ns   |

| Resolution                     | Ċ                  |                                                                                                                                                           |      | 8    |      | bits |

| Differential Nonlinearity      |                    |                                                                                                                                                           |      |      | 0.5  | LSB  |

**Note 1.** Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

Note 2.  $\theta_{JA}$  is measured under natural convection (still air) at  $T_A = 25^{\circ}C$  with the component mounted on a high effectivethermal-conductivity four-layer test board on a JEDEC 51-7 thermal measurement standard.

Note 3. Devices are ESD sensitive. Handling precaution is recommended.

Note 4. The device is not guaranteed to function outside its operating conditions.

Note 5. Guarantee by design.

Preliminary

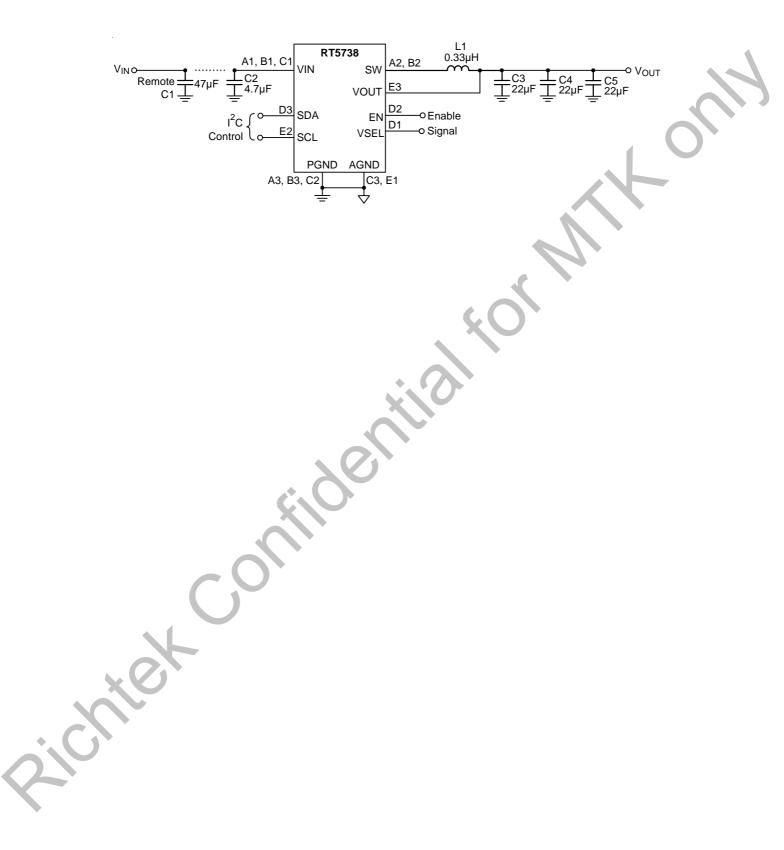

# **Typical Application Circuit**

# **Application Information**

#### I<sup>2</sup>C Interface

The RT5738A I<sup>2</sup>C slave address = 7'b1010000 for 0.4V/0.6V setting The RT5738B I<sup>2</sup>C slave address = 7'b1010111 for 1.125V/1.125V setting The RT5738C I<sup>2</sup>C slave address = 7'b1010010 for 0.65V/0.7V setting

#### I<sup>2</sup>C Register Map

| Address  | -    | Register   |        |         |        |          | <b>-</b> <i>t</i> - | <b>-</b> <i>t</i> - |                |                 |

|----------|------|------------|--------|---------|--------|----------|---------------------|---------------------|----------------|-----------------|

| Name     |      | ddress     | Bit7   | Bit6    | Bit5   | Bit4     | Bit3                | Bit2                | Bit1           | Bit0            |

|          |      | Meaning    |        |         |        |          | VSEL0               |                     |                |                 |

| NSEL0    | 0x00 | Default    | 0      | 0       | 0      | 0        | 0                   | 0                   | 0              | 0               |

|          |      | Read/Write | R/W    | R/W     | R/W    | R/W      | R/W                 | R/W                 | R/W            | R/W             |

|          |      | Meaning    |        |         |        |          | VSEL1               |                     | •              |                 |

| NSEL1    | 0x01 | Default    | 0      | 0       | 0      | 0        | 0                   | 0                   | 0              | 0               |

|          |      | Read/Write | R/W    | R/W     | R/W    | R/W      | R/W                 | R/W                 | R/W            | R/W             |

|          |      | Meaning    | DISCHG |         | UP_SF  | R[2:0]   | Reserved            | SW_RESET            | MODE_<br>VSEL1 | MODE_<br>VSEL0  |

| CONTROL1 | 0x02 | Default    | 0      | 0       | 0      | 1        | 0                   | 0                   | 1              | 0               |

|          |      | Read/Write | R/W    | R/W     | R/W    | R/W      | R                   | R/W                 | R/W            | R/W             |

|          |      | Meaning    | VEN    | IDOR_   | ID     | Reserved |                     | DIE                 | _ID            |                 |

| ID1      | 0x03 | Default    | 0      | 0       | 0      | 0        | 0                   | 0                   | 0              | 0               |

|          |      | Read/Write | R      | R       | R      | R        | R                   | R                   | R              | R               |

|          |      | Meaning    |        | Res     | served |          |                     | DIE_                | REV            |                 |

| ID2      | 0x04 | Default    | 0      | 0       | 0      | 0        | 0                   | 0                   | 0              | 0               |

|          |      | Read/Write | R      | R       | R      | R        | R                   | R                   | R              | R               |

|          |      | Meaning    | PGOOD  | UVLO    | OVP    | POS      | NEG                 | RESET_<br>STAT      | ОТ             | BUCK_<br>STATUS |

| MONITOR  | 0x05 | Default    | 0      | 0       | 0      | 0        | 0                   | 0                   | 0              | 1               |

|          |      | Read/Write | R      | R       | R      | R        | R                   | R                   | R              | R               |

|          |      | Meaning    | DN_    | _SR[2:0 | 0]     | Reserved | SS_S                | SR[1:0]             | EN_<br>VSEL1   | EN_VSEL0        |

| CONTROL2 | 0x06 | Default    | 0      | 0       | 1      | 0        | 0                   | 0                   | 0              | 0               |

|          |      | Read/Write | R/W    | R/W     | R/W    | R        | R/W                 | R/W                 | R/W            | R/W             |

|          |      | Meaning    | Reser  | ved     |        |          | EN                  | _DLY[5:0]           |                | -               |

| CONTROL3 | 0x07 | Default    | 0      | 0       | 0      | 0        | 0                   | 0                   | 0              | 0               |

|          |      | Read/Write | R      | R       | R/W    | R/W      | R/W                 | R/W                 | R/W            | R/W             |

|          |      | Meaning    | Reser  | ved     |        |          | DIS                 | _DLY[5:0]           |                |                 |

| CONTROL4 | 0x08 | Default    | 0      | 0       | 0      | 0        | 0                   | 0                   | 0              | 0               |

|          |      | Read/Write | R      | R       | R/W    | R/W      | R/W                 | R/W                 | R/W            | R/W             |

Copyright ©2016 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

DS5738-P02\_MTK August 2016

| Register<br>Name |       | Register<br>Address | b[7]<br>(MSB)                                                           | b[6]                       | b[5]                                               | b[4]             | b[3]  | b[2]  | b[1] | b[0]<br>(LSB) |  |  |  |  |  |

|------------------|-------|---------------------|-------------------------------------------------------------------------|----------------------------|----------------------------------------------------|------------------|-------|-------|------|---------------|--|--|--|--|--|

|                  |       | Meaning             |                                                                         |                            |                                                    |                  | VSEL0 |       |      |               |  |  |  |  |  |

| NSEL0            | 0x00  | Default             | 0                                                                       | 0                          | 0                                                  | 0                | 0     | 0     | 0    | 0             |  |  |  |  |  |

|                  |       | Read/Write          | R/W                                                                     | R/W                        | R/W                                                | R/W              | R/W   | R/W   | R/W  | R/W           |  |  |  |  |  |

|                  | VSEL0 |                     | VID Table<br>SEL[7:0] =<br><br>SEL[7:0] =<br><br>SEL[7:0] =<br>5mV step | = 1111<br>= 1100<br>= 0000 | 1111 :<br>1000 :<br>000 : 0                        | Vout = 1<br>0.3V |       | o1.85 | 1    | 0             |  |  |  |  |  |

| Register<br>Name |       | Register<br>Address | b[7]<br>(MSB)                                                           | b[6]                       | b[5]                                               | b[4]             | b[3]  | b[2]  | b[1] | b[0]<br>(LSB) |  |  |  |  |  |

|                  |       | Meaning             |                                                                         |                            |                                                    |                  | VSEL1 |       |      |               |  |  |  |  |  |

| NSEL1            | 0x01  | Default             | 0                                                                       | 0                          | 0                                                  | 0                | 0     | 0     | 0    | 0             |  |  |  |  |  |

|                  |       | Read/Write          | R/W                                                                     | R/W                        | R/W                                                | R/W              | R/W   | R/W   | R/W  | R/W           |  |  |  |  |  |

| ·                | VSEL1 |                     | VID Table<br>SEL[7:0] =<br><br>SEL[7:0] =<br><br>SEL[7:0] =             | = 1111<br>= 1100<br>= 0000 | 1111 :<br>100 0:<br>000 : 0                        | Vout = ^<br>0.3V | I.3V  | )     |      |               |  |  |  |  |  |

|                  |       |                     | 5mV step                                                                | for 0.3                    | 5mV step for 0.3 to 1.3, 10mV step for 1.3 to 1.85 |                  |       |       |      |               |  |  |  |  |  |

| Register<br>Name |        | Register<br>Address | b[7]<br>(MSB)                                                                                                                                | b[6]                                                                      | b[5]                                                    | b[4]   | b[3]     | b[2]         | b[1]           | b[0]<br>(LSB)  |  |

|------------------|--------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------|--------|----------|--------------|----------------|----------------|--|

|                  | 0.00   | Meaning             | DISCHG                                                                                                                                       | C                                                                         | P_SR[                                                   | 2:0]   | Reserved | SW_<br>RESET | MODE_<br>VSEL1 | MODE_<br>VSEL0 |  |

| CONTROL1         | 0x02   | Default             | 0                                                                                                                                            | 0                                                                         | 0                                                       | 1      | 0        | 0            | 1              | 0              |  |

|                  |        | Read/Write          | R/W                                                                                                                                          | R/W                                                                       | R/W                                                     | R/W    | R/W      | R/W          | R/W            | R/W            |  |

|                  |        |                     | 0 : Discha                                                                                                                                   | rge pa                                                                    | th disa                                                 | bled   |          |              |                |                |  |

|                  | ISCHO  |                     | 1 : Discha                                                                                                                                   | rge pa                                                                    | th enal                                                 | oled   |          |              |                |                |  |

| UP               | _SR[2  | :0]                 | DVS Spee<br>000 = 24n<br>001 = 12n<br>010 = 6m <sup>1</sup><br>011 = 3m <sup>1</sup><br>100 = 1.5n<br>101 = 0.73<br>110 = 0.33<br>111 = 0.13 | nV step<br>NV step/<br>V step/<br>NV step/<br>mV ste<br>5mV st<br>75mV st | o/μs<br>o/μs<br>/μs<br>/μs<br>ep/μs<br>ep/μs<br>step/μs | ï      |          |              |                |                |  |

|                  | eserve |                     | Reserved                                                                                                                                     |                                                                           |                                                         |        |          |              |                |                |  |

| SW               | _RES   | El                  | write 1 to                                                                                                                                   | reset, a                                                                  | always                                                  | read 0 |          |              |                |                |  |

| MOE              | DE_VS  | EL1                 | 0 : Auto<br>1 : Continuous mode                                                                                                              |                                                                           |                                                         |        |          |              |                |                |  |

|                  |        |                     | 0 : Auto                                                                                                                                     |                                                                           |                                                         |        |          |              |                |                |  |

| MOL              | DE_VS  | ELU                 | 1 : Contin                                                                                                                                   | uous n                                                                    | node                                                    |        |          |              |                |                |  |

# **RT5738**

# Preliminary

| Register<br>Name |         | egister<br>ddress | b[7]<br>(MSB) | b[6]    | b[5] | b[4]     | b[3]        | b[3] b[2] |   | b[0]<br>(LSB) |

|------------------|---------|-------------------|---------------|---------|------|----------|-------------|-----------|---|---------------|

|                  |         | Meaning           | VEND          | OR_ID[2 | 2:0] | Reserved | DIE_ID[3:0] |           |   |               |

| ID1              | 0x03    | Default           | 0             | 0       | 0    | 0        | 0           | 0         | 0 | 0             |

|                  |         | Read/Write        | R             | R       | R    | R        | R           | R         | R | R             |

| VEN              | DOR_I   | D[2:0]            | Vendor_II     | D       |      |          |             |           |   |               |

| DI               | IE_ID[3 | 3:0]              | DIE_ID        |         |      |          |             |           |   |               |

| Register<br>Name |       | legister<br>Address | b[7]<br>(MSB) | b[6] | b[5]  | b[4] | b[3] | b[2]  | b[1]     | b[0]<br>(LSB) |

|------------------|-------|---------------------|---------------|------|-------|------|------|-------|----------|---------------|

|                  |       | Meaning             |               | Rese | erved |      |      | DIE_R | REV[3:0] |               |

| ID2              | 0x04  | Default             | 0             | 0    | 0     | 0    | 0    | 0     | 0        | 0             |

|                  |       | Read/Write          | R             | R    | R     | R    | R    | R     | R        | R             |

| DIE              | E_REV | [3:0]               | Revision_     | ID   |       |      |      |       |          |               |

|                  |       |                     |               |      |       |      |      |       |          |               |

| Register<br>Name |       | egister<br>ddress | b[7]<br>(MSB)                                              | b[6]     | b[5]     | b[4]          | b[3]          | b[2]           | b[1] | b[0]<br>(LSB)   |  |  |

|------------------|-------|-------------------|------------------------------------------------------------|----------|----------|---------------|---------------|----------------|------|-----------------|--|--|

|                  |       | Meaning           | PGOOD                                                      | UVLO     | OVP      | POS           | NEG           | RESET_<br>STAT | ОТ   | BUCK_<br>STATUS |  |  |

| MONITOR          | 0x05  | Default           | 0                                                          | 0        | 0        | 0             | 0             | 0              | 0    | 1               |  |  |

|                  |       | Read/Write        | R                                                          | R        | R        | R             | R             | R              | R    | R               |  |  |

| l                | PGOO  | D                 | 1 : Buck is enabled and soft-start is completed.           |          |          |               |               |                |      |                 |  |  |

|                  | UVLO  |                   | 1 : Signifi                                                | es the V | IN is le | ss than the l | JVLO three    | shold.         |      |                 |  |  |

|                  | OVP   |                   | 1 : Signifi                                                | es the V | IN is gr | eater than th | ne OVP thr    | eshold.        |      |                 |  |  |

|                  | POS   |                   | 1 : Signifies a positive voltage transition is in progress |          |          |               |               |                |      |                 |  |  |

|                  | NEG   |                   | 1 : Signifi                                                | es a neg | ative v  | oltage transi | tion is in pi | ogress         |      |                 |  |  |

| RE               | SET_S | ТАТ               | 1 : Indicates that a register reset was performed.         |          |          |               |               |                |      |                 |  |  |

|                  | ОТ    |                   | 1 : Signifies the thermal shutdown is active.              |          |          |               |               |                |      |                 |  |  |

| BUC              | K_STA | ATUS              | 1 : Buck e                                                 | enabled; | 0 : buc  | k disabled.   |               |                |      |                 |  |  |

|                  | e     |                   |                                                            |          |          |               |               |                |      |                 |  |  |

| Register<br>Name | Regis | ster Address | b[7]<br>(MSB)                                                             | b[6]                                                                                                                                                                                                                     | b[5] | b[4] | b[3] | b[2] | b[1] | b[0]<br>(LSB) |  |  |  |

|------------------|-------|--------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|---------------|--|--|--|

|                  |       | Meaning      | DN                                                                        | DN_SR[2:0] Reserved SS_SR[1:0] EN_ EN_<br>VSEL1 VSEL0                                                                                                                                                                    |      |      |      |      |      |               |  |  |  |

| CONTROL2         | 0x06  | Default      | 0                                                                         | 1                                                                                                                                                                                                                        | 1    | 0    | 0    | 0    | 0    | 0             |  |  |  |

|                  |       | Read/Write   | R/W                                                                       | R/W                                                                                                                                                                                                                      | R/W  | R    | R/W  | R/W  |      |               |  |  |  |

| DN               | _SR[2 | :0]          | 000 = 2<br>001 = 1<br>010 = 6<br>011 = 3<br>100 = 1<br>101 = 0<br>110 = 0 | DVS Speed for DN DVS      000 = 24mV step/μs      001 = 12mV step/μs      010 = 6mV step/μs      011 = 3mV step/μs      00 = 1.5mV step/μs      01 = 0.75mV step/μs      10 = 0.375mV step/μs      11 = 0.1875mV step/μs |      |      |      |      |      |               |  |  |  |

| SS               | _SR[1 | :0]          | 00=10m<br>01=5m\<br>10=2.5m                                               | DVS Speed for SOFT START DVS<br>D0=10mV step/µs<br>D1=5mV step/µs<br>10=2.5mV step/µs<br>11=1.25mV step/µs                                                                                                               |      |      |      |      |      |               |  |  |  |

| EN               | LVSEI | _1           | 0 : DISA<br>1 : ENA                                                       |                                                                                                                                                                                                                          |      |      |      |      |      |               |  |  |  |

| EN               | LVSEI | _0           | 0 : DISA<br>1 : ENA                                                       |                                                                                                                                                                                                                          |      | × 0  |      |      |      |               |  |  |  |

| Register<br>Name | Register Address |            | b[7]<br>(MSB) | b[6]    | b[5]        | b[4]                     | b[3]        | b[2]   | b[1] | b[0]<br>(LSB) |  |

|------------------|------------------|------------|---------------|---------|-------------|--------------------------|-------------|--------|------|---------------|--|

| CONTROL3         | 0x07             | Meaning    | Reserved      |         | EN_DLY[5:0] |                          |             |        |      |               |  |

|                  |                  | Default    | 0             | 0       | 0           | 0                        | 0           | 0      | 0    | 0             |  |

|                  |                  | Read/Write | R             | R       | R/W         | R/W                      | R/W         | R/W    | R/W  | R/W           |  |

| Reserved Re      |                  |            | Reserve       | ed bits |             |                          |             |        |      |               |  |

|                  |                  |            |               |         |             | bling (ms)<br>11b = 63ms | s (steps of | f 1ms) |      |               |  |

$\smile$

|   | Register<br>Name | Sedister Address |            | b[7]<br>(MSB)                                                                    | b[6]    | b[5]         | b[4] | b[3] | b[2] | b[1] | b[0]<br>(LSB) |

|---|------------------|------------------|------------|----------------------------------------------------------------------------------|---------|--------------|------|------|------|------|---------------|

|   | ×                | S                | Meaning    | Reser                                                                            | ved     | DIS_DLY[5:0] |      |      |      |      |               |

|   | CONTROL4         | 0x08             | Default    | 0                                                                                | 0       | 0            | 0    | 0    | 0    | 0    | 0             |

|   |                  |                  | Read/Write | R                                                                                | R       | R/W          | R/W  | R/W  | R/W  | R/W  | R/W           |

|   | Reserved         |                  |            | Reserve                                                                          | ed bits |              |      |      |      |      |               |

| 2 | DIS_DLY[5:0]     |                  |            | Delay applied upon disable (ms)<br>000000b = 0ms - 111111b = 63ms (steps of 1ms) |         |              |      |      |      |      |               |

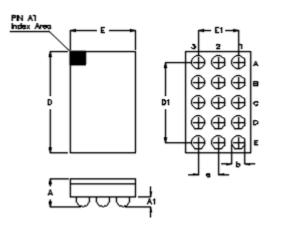

# **Outline Dimension**

| Symbol | Dimensions I | n Millimeters | Dimensions In Inches |       |  |  |

|--------|--------------|---------------|----------------------|-------|--|--|

| Symbol | Min.         | Max.          | Min.                 | Max.  |  |  |

| А      | 0.500 0.600  |               | 0.020                | 0.024 |  |  |

| A1     | 0.170        | 0.230         | 0.007                | 0.009 |  |  |

| b      | 0.240        | 0.300         | 0.009                | 0.012 |  |  |

| D      | 1.980        | 2.060         | 0.078                | 0.081 |  |  |

| D1     | 1.6          | 600           | 0.063                |       |  |  |

| E      | 1.270        | 1.350         | 0.050                | 0.053 |  |  |

| E1     | 0.8          | 300           | 0.031                |       |  |  |

| е      | 0.4          | 100           | 0.016                |       |  |  |

15B WL-CSP 1.31x2.02 Package (BSC)

## **Footprint Information**

|                          |                  |      | 1       |             |         | 6         | 14 |

|--------------------------|------------------|------|---------|-------------|---------|-----------|----|

| Package                  | Number of<br>Pin | Туре | Footpri | nt Dimensic | on (mm) | Tolerance |    |

|                          |                  |      | е       | А           | В       |           |    |

| WL-CSP1.31*2.02-15(BSC)  | 15               | NSMD | 0.400   | 0.240       | 0.340   | ±0.025    |    |

| WE-COT 1.51 2.02-15(DOC) |                  | SMD  |         | 0.270       | 0.240   |           |    |

|                          | <u> </u>         |      | ~       | 0           |         |           |    |

### Richtek Technology Corporation

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C. Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

### **Datasheet Revision History**

| P00 | 2016/5/3 |                                                                                                        | First Edition |  |

|-----|----------|--------------------------------------------------------------------------------------------------------|---------------|--|

| P01 | 2016/6/8 | I <sup>2</sup> C Interface                                                                             | Modify        |  |

| P02 | 2016/8/4 | Features<br>Ordering Information<br>Electrical Characteristics<br>Note 2<br>I <sup>2</sup> C Interface | Modify        |  |

Copyright ©2016 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.