## **Summary**

Atmel's SAM4L series is a member of a family of Flash microcontrollers based on the high performance 32-bit ARM Cortex-M4 RISC processor running at frequencies up to 48MHz.

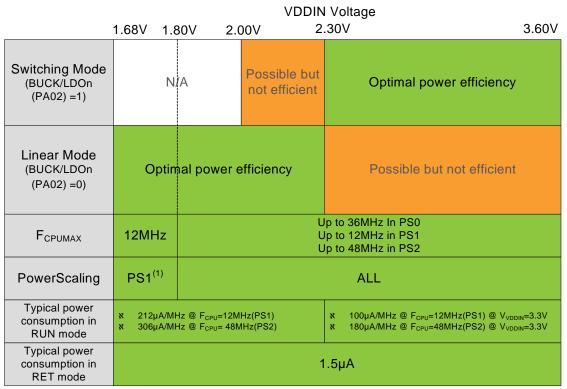

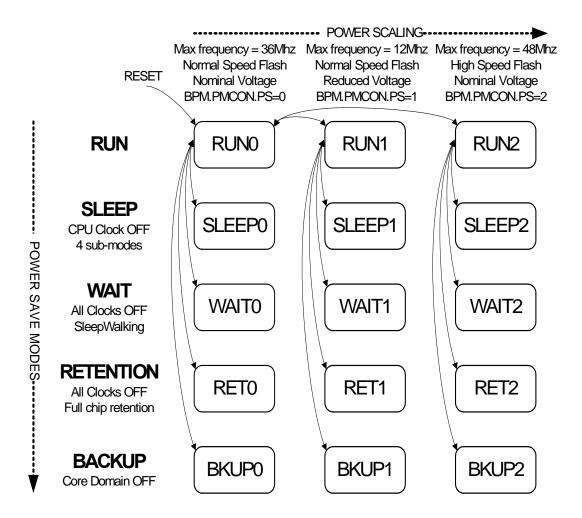

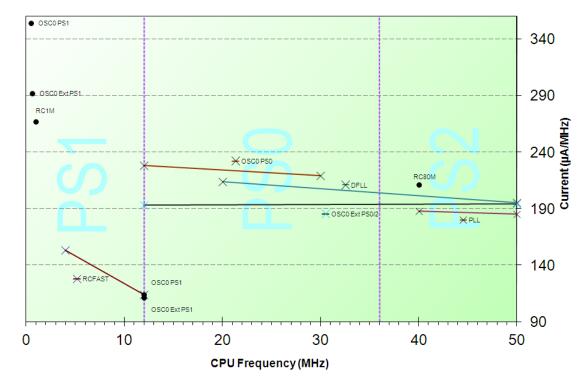

The SAM4L series embeds state-of-the-art picoPower technology for ultra-low power consumption. Combined power control techniques are used to bring active current consumption down to  $90\mu\text{A/MHz}$ . The device allows a wide range of options between functionality and power consumption, giving the user the ability to reach the lowest possible power consumption with the feature set required for the application. The WAIT and RETENTION modes provide full logic and RAM retention, associated with fast wake-up capability (<1.5 $\mu$ s) and a very low consumption of, respectively, 3  $\mu$ A and 1.5  $\mu$ A. In addition, WAIT mode supports SleepWalking features. In BACKUP mode, CPU, peripherals and RAM are powered off and, while consuming less than 0.9 $\mu$ A with external interrupt wake-up supported.

The SAM4L series offers a wide range of peripherals such as segment LCD controller, embedded hardware capacitive touch (QTouch), USB device & embedded host, 128-bit AES and audio interfaces in addition to high speed serial peripherals such as USART, SPI and I<sup>2</sup>C. Additionally the Peripheral Event System and SleepWalking allows the peripherals to communicate directly with each other and make intelligent decisions and decide to wake-up the system on a qualified events on a peripheral level; such as I<sup>2</sup>C address match or and ADC threshold.

### **Features**

- Core

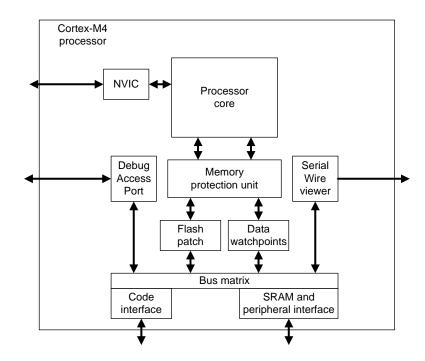

- ARM<sup>®</sup> Cortex<sup>™</sup>-M4 running at up to 48MHz

- Memory Protection Unit (MPU)

- Thumb<sup>®</sup>-2 instruction set

- picoPower® Technology for Ultra-low Power Consumption

- Active mode downto 90µA/MHz with configurable voltage scaling

- High performance and efficiency: 28 coremark/mA

- Wait mode downto 3µA with fast wake-up time (<1.5µs) supporting SleepWalking

- Full RAM and Logic Retention mode downto 1.5μA with fast wake-up time (<1.5μs)

- Ultra low power Backup mode with/without RTC downto 1,5/0.9µA

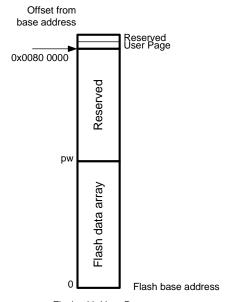

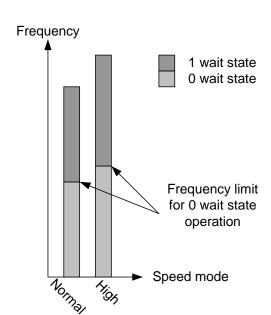

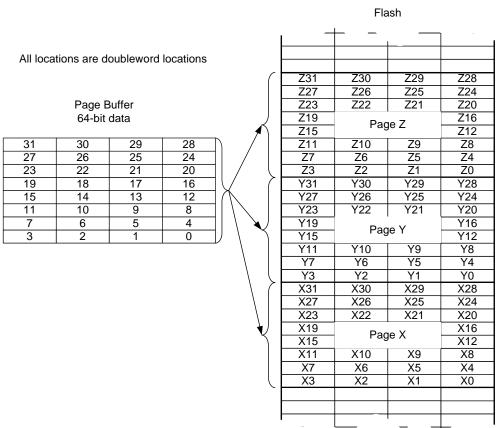

- Memories

- From 128 to 512Kbytes embedded Flash, 64-bit wide access,

- 0 wait-state capability up to 24MHz

- up to 64Kbytes embedded SRAM

- System Functions

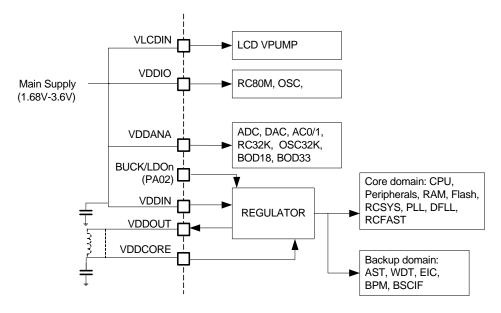

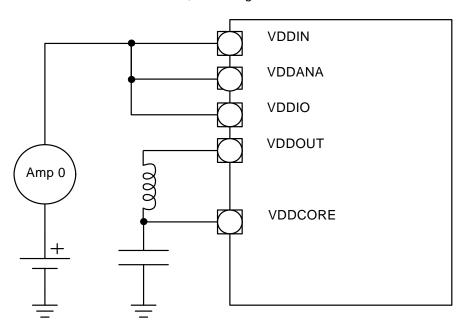

- Embedded voltage linear and switching regulator for single supply operation

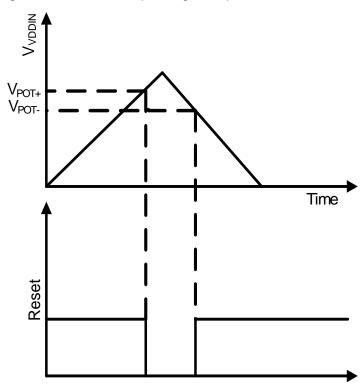

- Two Power-on-Reset and Two Brown-out Detectors (BOD)

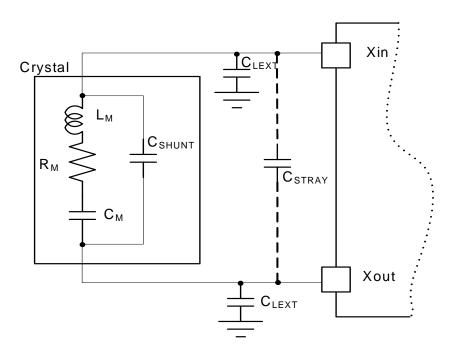

- Quartz or ceramic resonator oscillators: 0.6 to 30MHz main power with Failure

Detection and low power 32.768 kHz for RTC or device clock

- High precision 4/8/12MHz factory trimmed internal RC oscillator

- Slow Clock Internal RC oscillator as permanent low-power mode device clock

- High speed 80MHz internal RC oscillator

- Low power 32kHz internal RC oscillator

# ATSAM ARM-based Flash MCU

## **SAM4L Series**

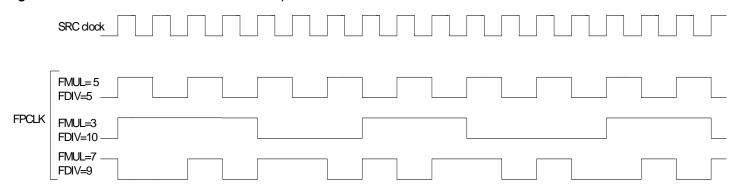

- PLL up to 240MHz for device clock and for USB

- Digital Frequency Locked Loop (DFLL) with wide input range

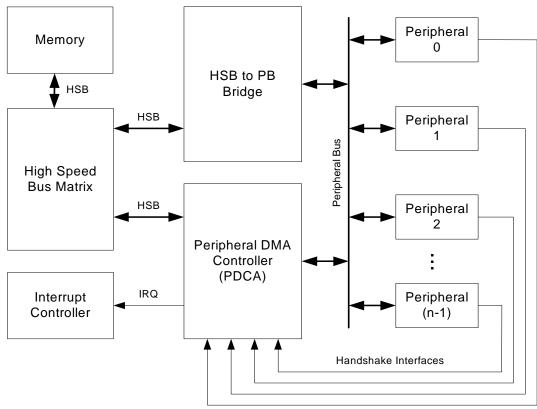

- Up to 16 peripheral DMA (PDCA) channels

#### Peripherals

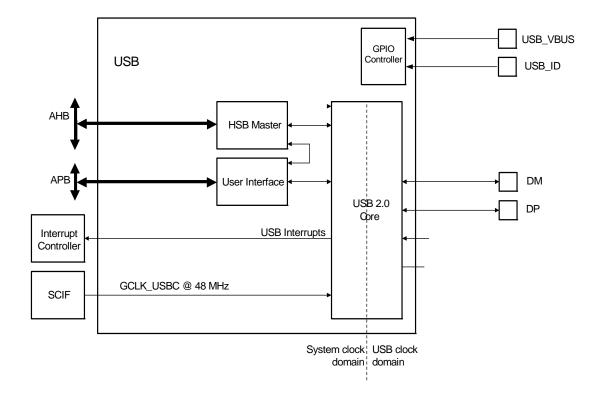

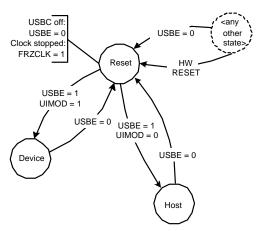

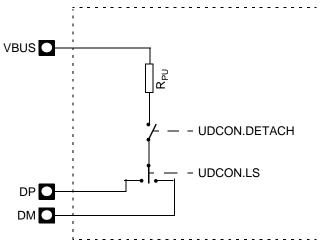

- USB 2.0 Device and Embedded Host: 12 Mbps, up to 8 bidirectional Endpoints and Multi-packet Ping-pong Mode. On-Chip Transceiver

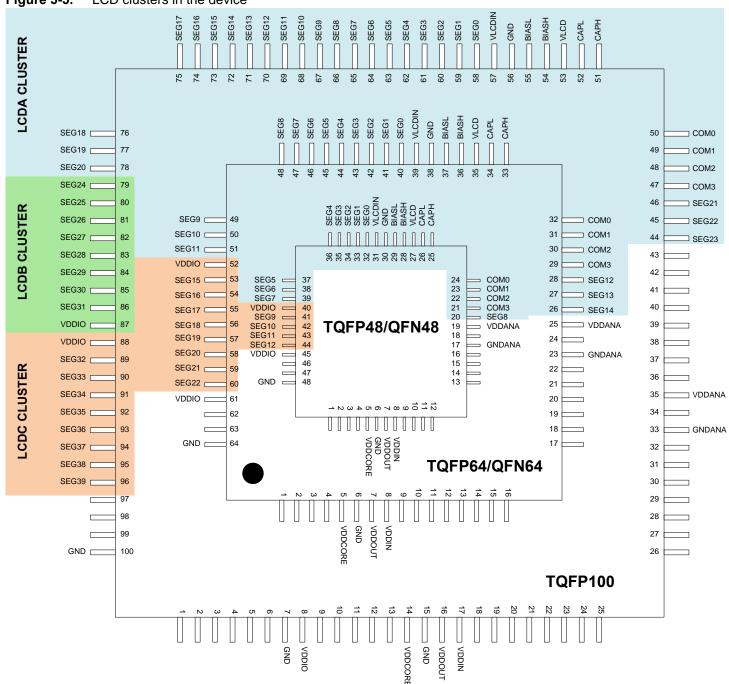

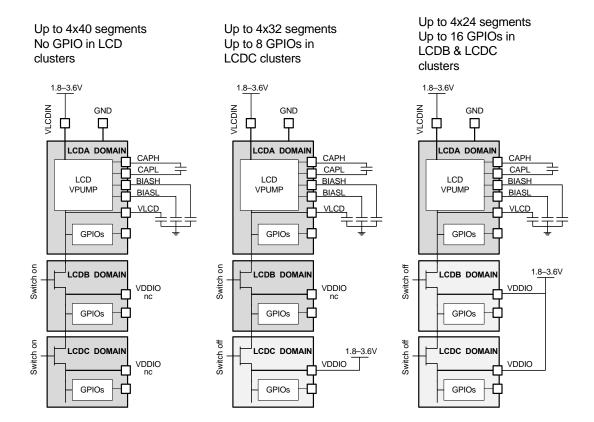

- Liquid Crystal Display (LCD) Module with Capacity up to 40 Segments and up to 4 Common Terminals

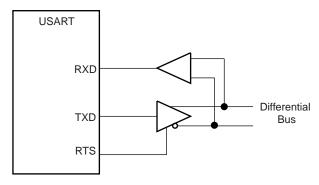

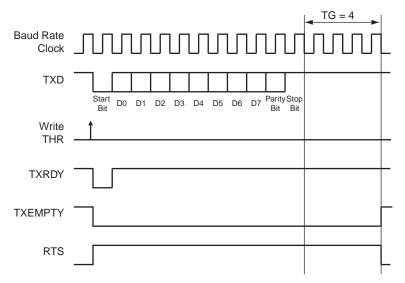

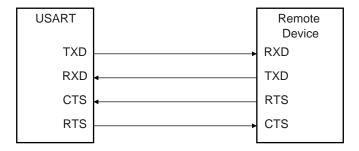

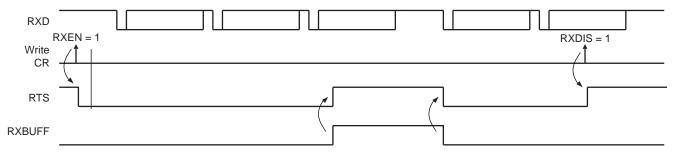

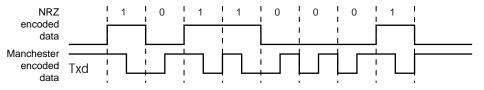

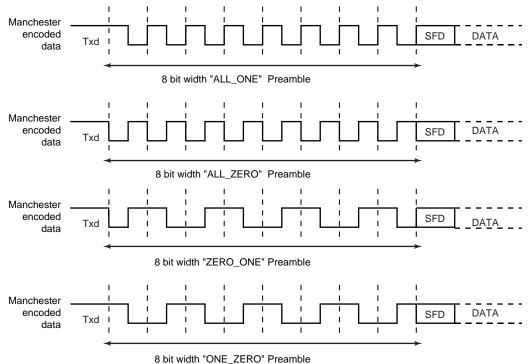

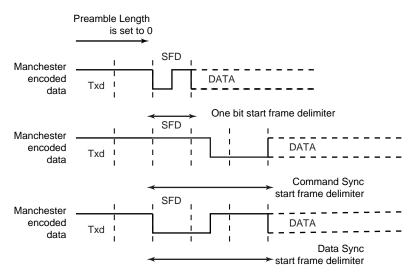

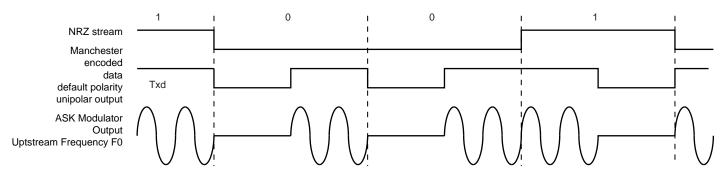

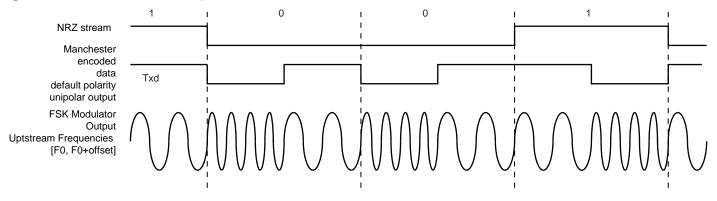

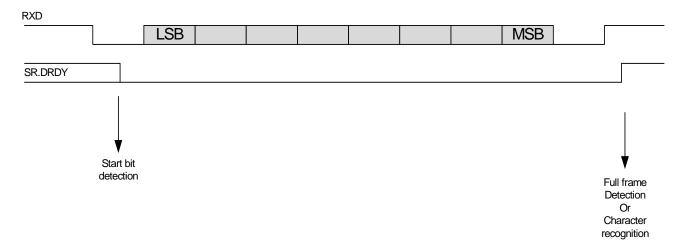

- One USART with ISO7816, IrDA®, RS-485, SPI, Manchester and LIN Mode

- Three USART with SPI Mode

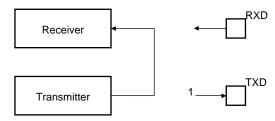

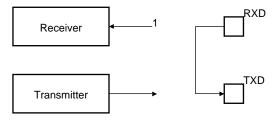

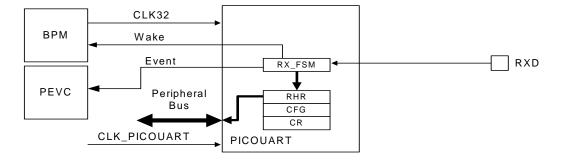

- One PicoUART for extended UART wake-up capabilities in all sleep modes

- Windowed Watchdog Timer (WDT)

- Asynchronous Timer (AST) with Real-time Clock Capability, Counter or Calendar Mode Supported

- Frequency Meter (FREQM) for Accurate Measuring of Clock Frequency

- Six 16-bit Timer/Counter (TC) Channels with capture, waveform, compare and PWM mode

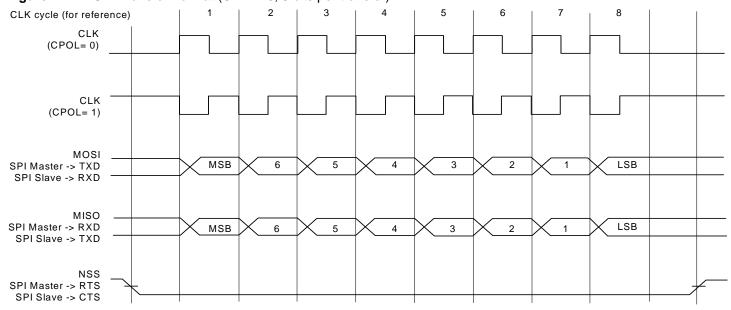

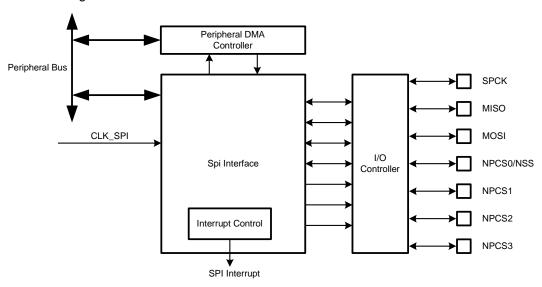

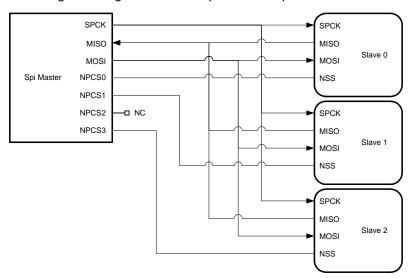

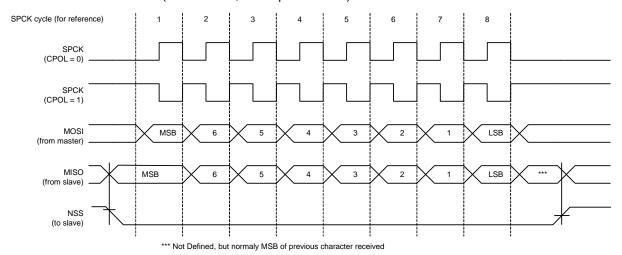

- One Master/Slave Serial Peripheral Interface (SPI) with Chip Select Signals

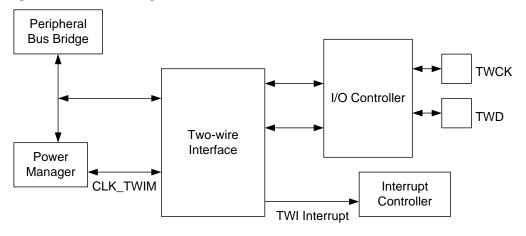

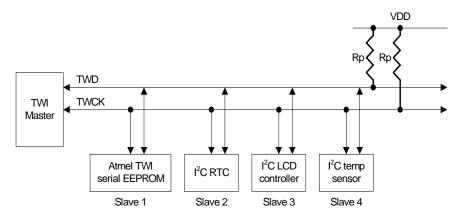

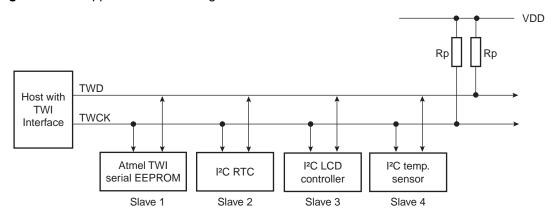

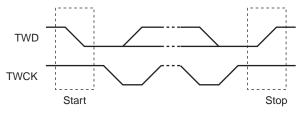

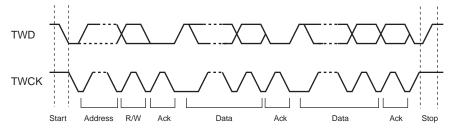

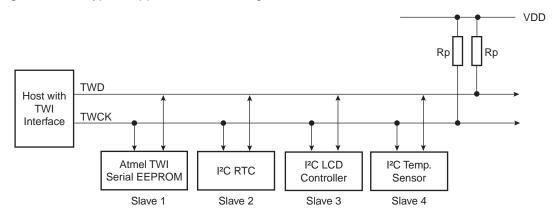

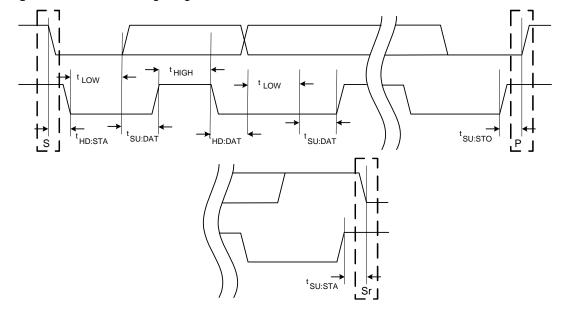

- Four Master and Two Slave Two-wire Interfaces (TWI), up to 3.4Mbit/s I<sup>2</sup>C-compatible

- One Advanced Encryption System (AES) with 128-bit key length

- One 16-channel ADC 300Ksps (ADC) with up to 12 Bits Resolution

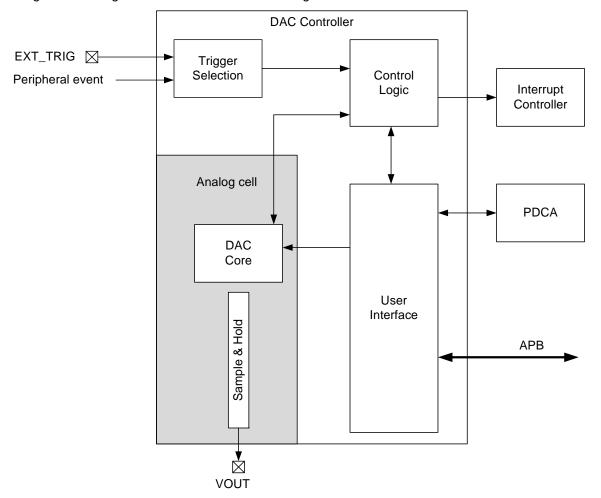

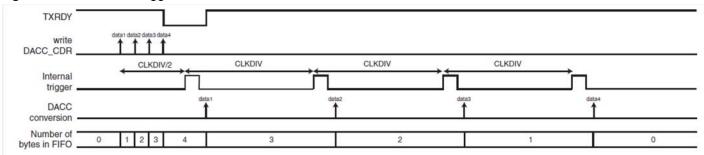

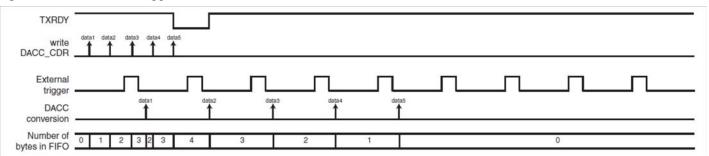

- One DAC 500Ksps (DACC) with up to 10 Bits Resolution

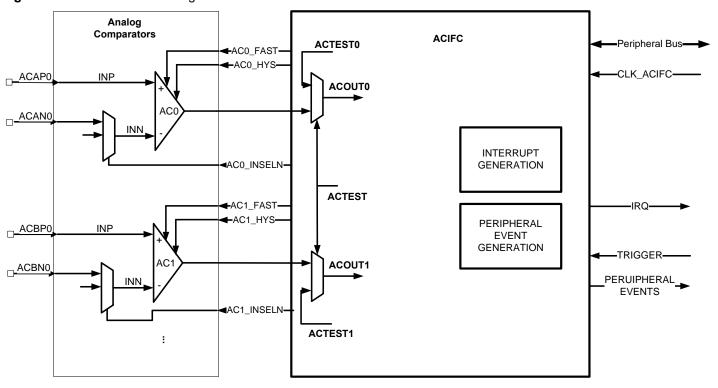

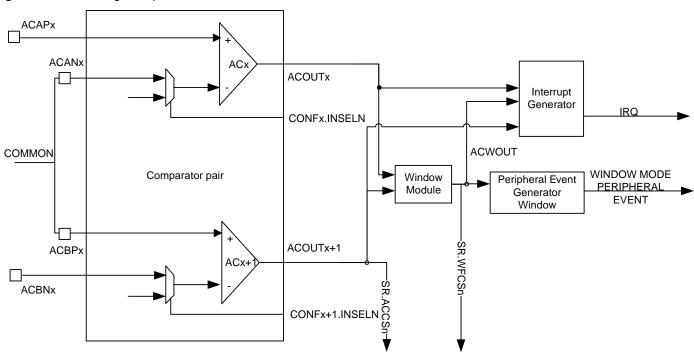

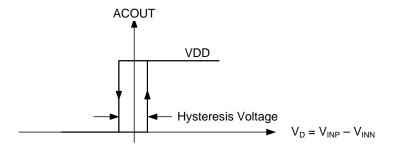

- Four Analog Comparators (ACIFC) with Optional Window Detection

- Capacitive Touch Module (CATB) supporting up to 32 buttons

- Audio Bitstream DAC (ABDACB) Suitable for Stereo Audio

- Inter-IC Sound (IISC) Controller, Compliant with Inter-IC Sound (I<sup>2</sup>S) Specification

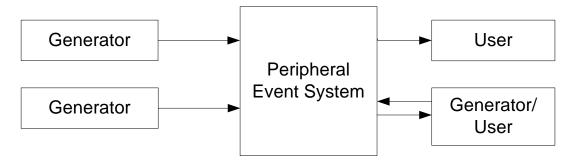

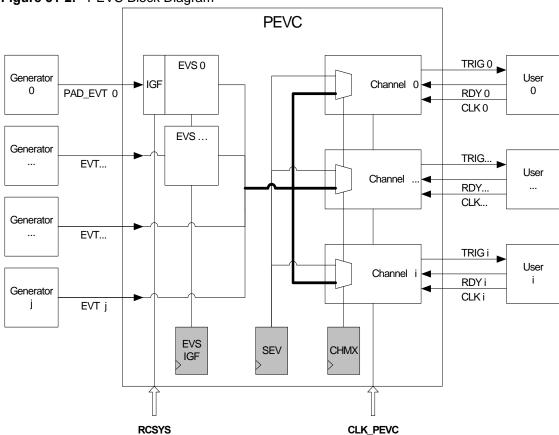

- Peripheral Event System for Direct Peripheral to Peripheral Communication

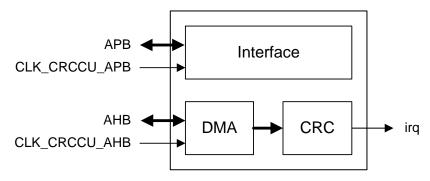

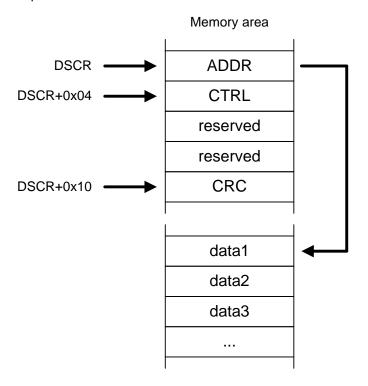

- 32-bit Cyclic Redundancy Check Calculation Unit (CRCCU)

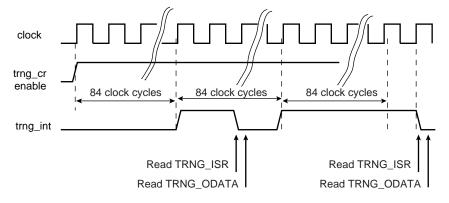

- Random generator (TRNG)

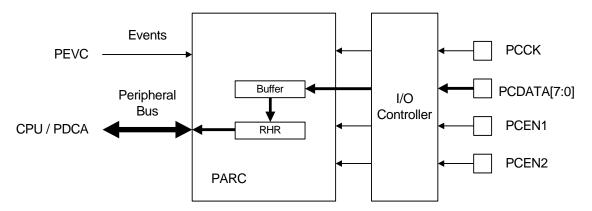

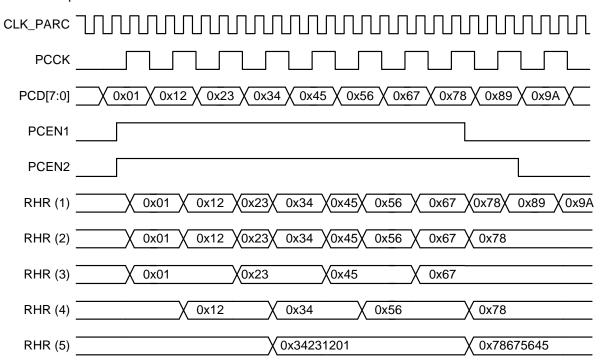

- Parallel Capture Module (PARC)

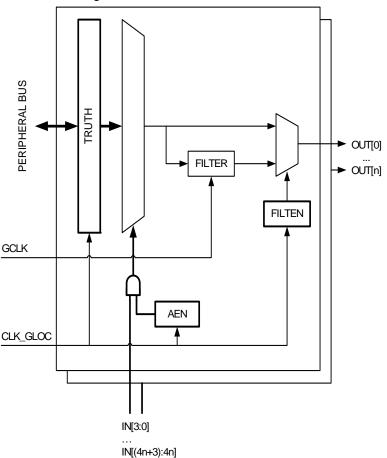

- Glue Logic Controller (GLOC)

#### I/O

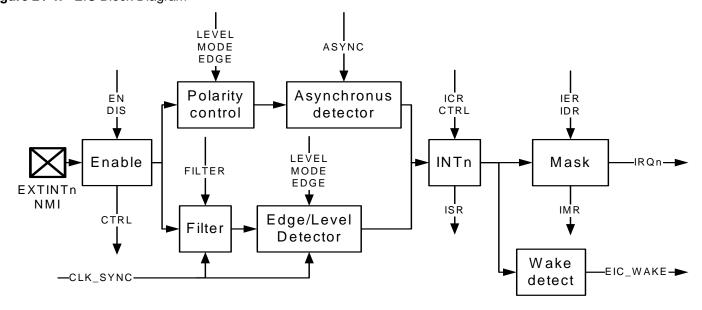

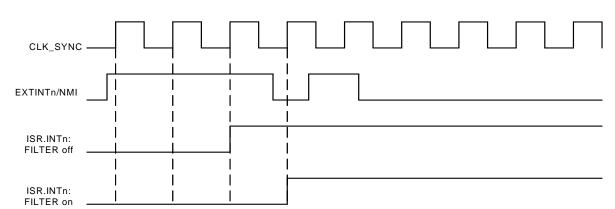

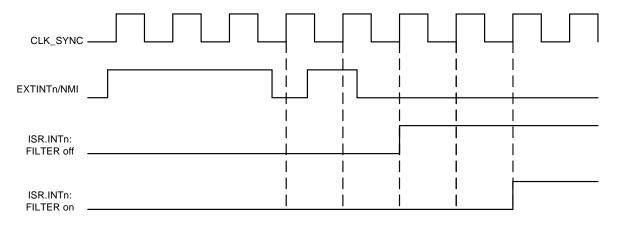

- Up to 75 I/O lines with external interrupt capability (edge or level sensitivity), debouncing, glitch filtering and slew-rate control

- Up to Six High-drive I/O Pins

- Single 1.68-3.6V Power Supply

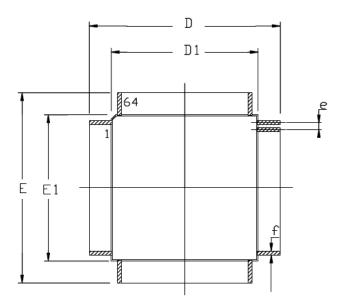

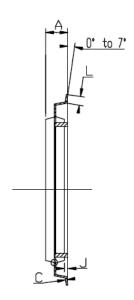

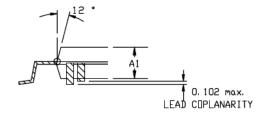

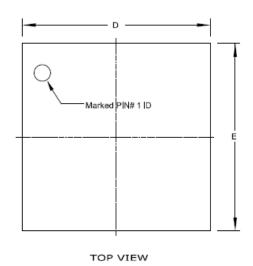

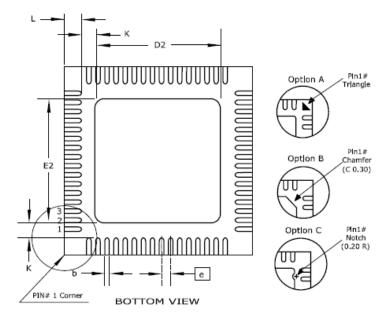

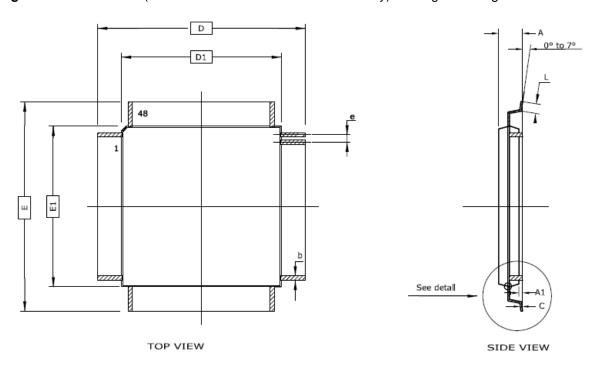

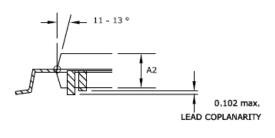

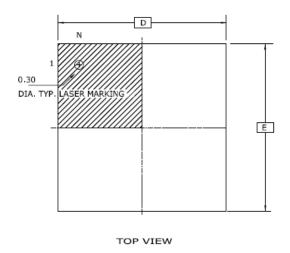

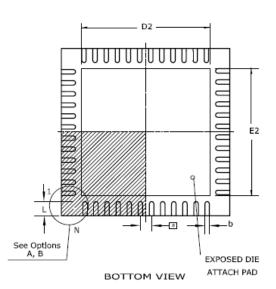

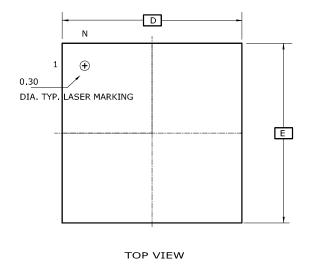

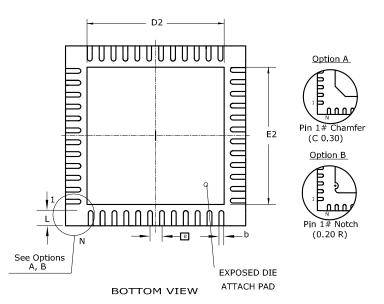

- Packages

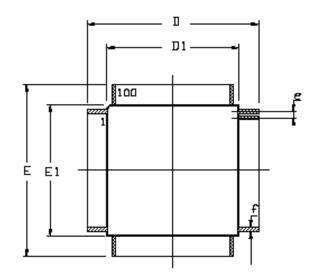

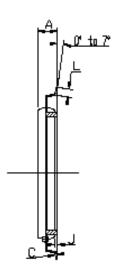

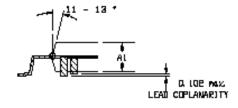

- 100-lead LQFP, 14 x 14 mm, pitch 0.5 mm/100-ball VFBGA, 7x7 mm, pitch 0.65 mm

- 64-lead LQFP, 10 x 10 mm, pitch 0.5 mm/64-pad QFN 9x9 mm, pitch 0.5 mm

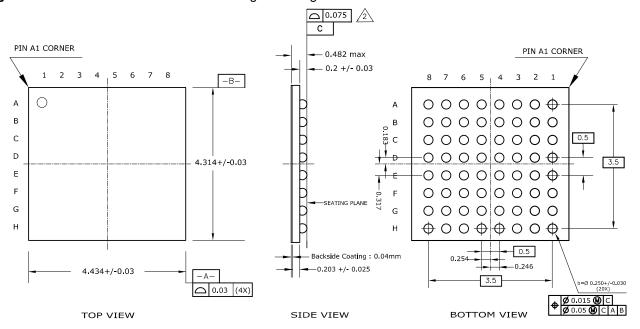

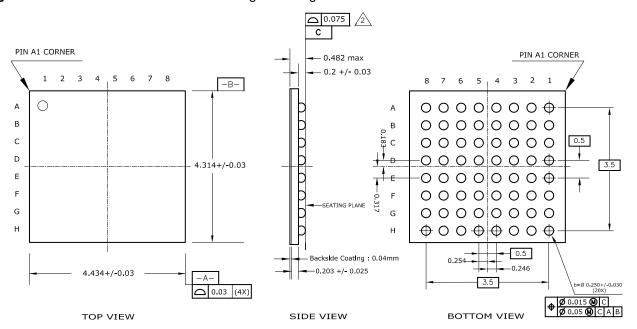

- 64-ball WLCSP, 4,314x4,434 mm, pitch 0.5 mm for SAM4LC4/2 and SAM4LS4/2 series

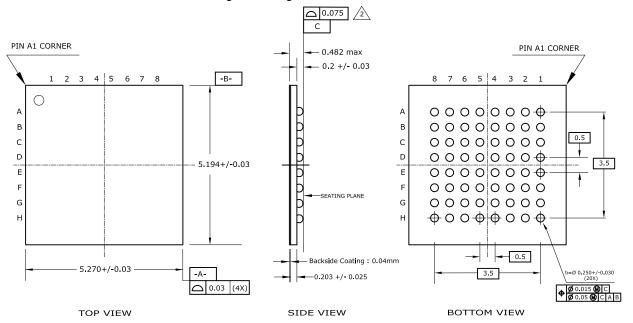

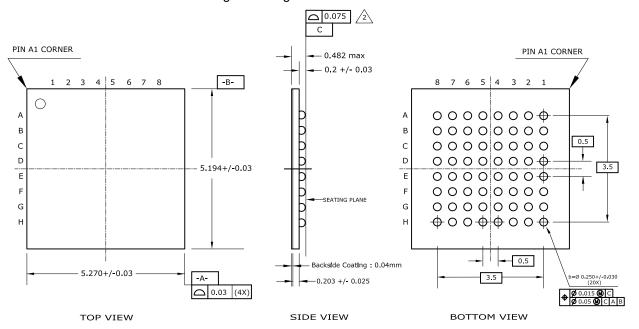

- 64-ball WLCSP, 5,270x5,194 mm, pitch 0.5 mm for SAM4LC8 and SAM4LS8 series

- 48-lead LQFP, 7 x 7 mm, pitch 0.5 mm/48-pad QFN 7x7 mm, pitch 0.5 mm

## 1. Description

Atmel's SAM4L series is a member of a family of Flash microcontrollers based on the high performance 32-bit ARM Cortex-M4 RISC processor running at frequencies up to 48MHz.

The processor implements a Memory Protection Unit (MPU) and a fast and flexible interrupt controller for supporting modern and real-time operating systems.

The ATSAM4L8/L4/L2 embeds state-of-the-art picoPower technology for ultra-low power consumption. Combined power control techniques are used to bring active current consumption down to 90 µA/MHz. The device allows a wide range of options between functionality and power consumption, giving the user the ability to reach the lowest possible power consumption with the feature set required for the application. On-chip regulator improves power efficiency when used in swichting mode with an external inductor or can be used in linear mode if application is noise sensitive.

The ATSAM4L8/L4/L2 supports 4 power saving strategies. The SLEEP mode put the CPU in idle mode and offers different sub-modes which automatically switch off/on bus clocks, PLL, oscillators. The WAIT and RETENTION modes provide full logic and RAM retention, associated with fast wake-up capability (<1.5 $\mu$ s) and a very low consumption of, respectively, 3  $\mu$ A and 1.5  $\mu$ A. In addition, WAIT mode supports SleepWalking features. In BACKUP mode, CPU, peripherals and RAM are powered off and, while consuming less than 0.5 $\mu$ A, the device is able to wake-up from external interrupts.

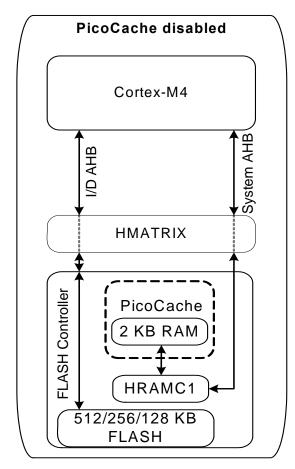

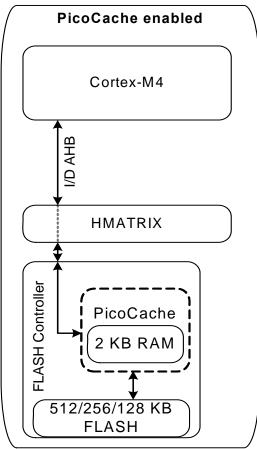

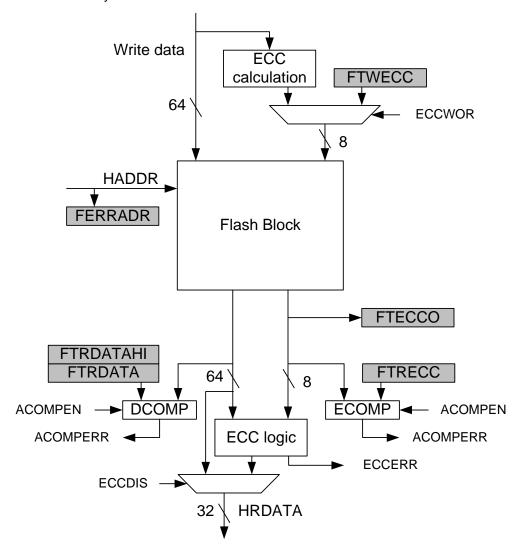

The ATSAM4L8/L4/L2 incorporates on-chip Flash tightly coupled to a low power cache (LPCACHE) for active consumption optimization and SRAM memories for fast access.

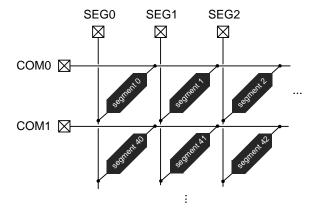

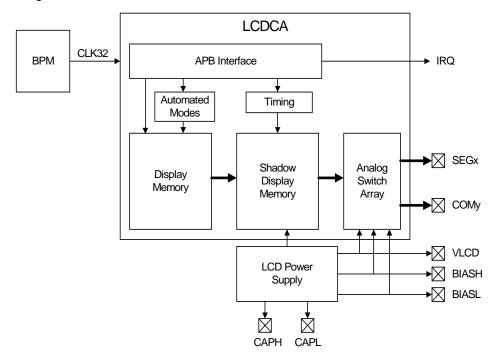

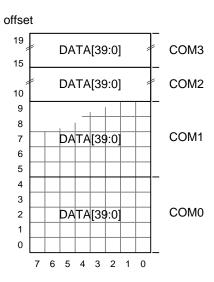

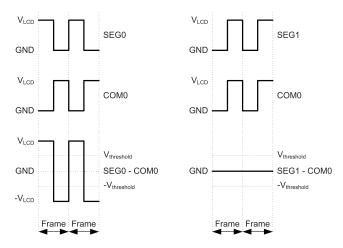

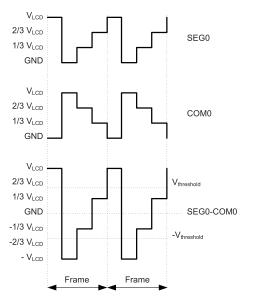

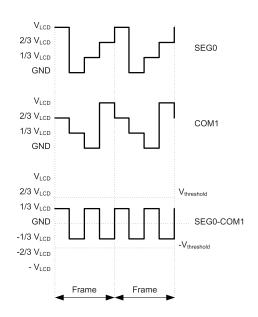

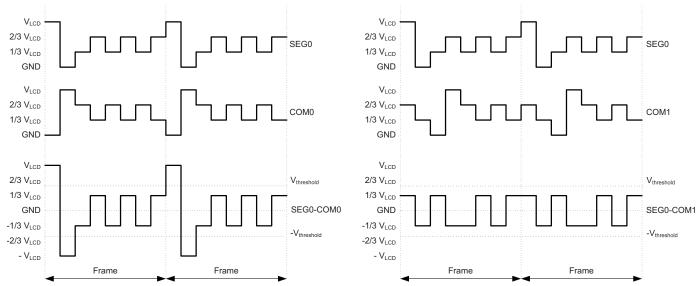

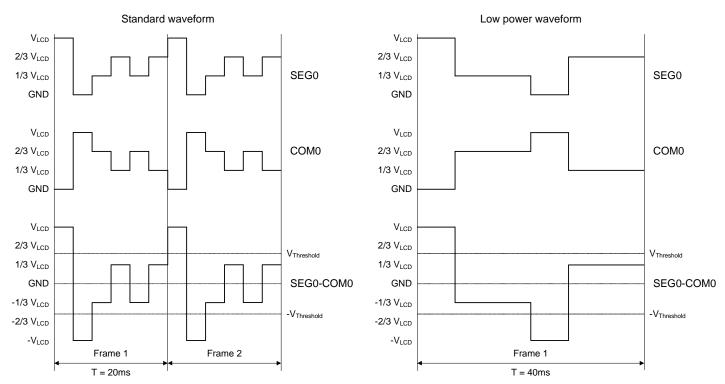

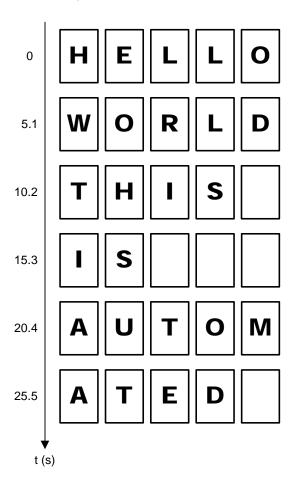

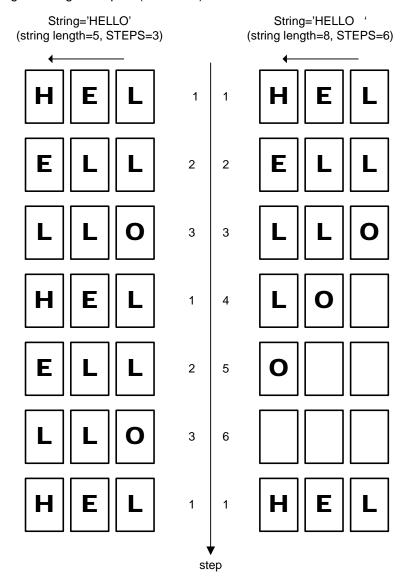

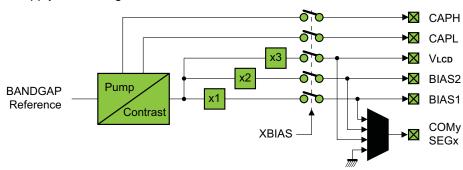

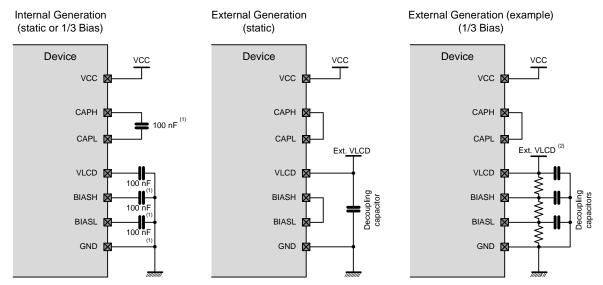

The LCD controller is intended for monochrome passive liquid crystal display (LCD) with up to 4 Common terminals and up to 40 Segments terminals. Dedicated Low Power Waveform, Contrast Control, Extended Interrupt Mode, Selectable Frame Frequency and Blink functionality are supported to offload the CPU, reduce interrupts and reduce power consumption. The controller includes integrated LCD buffers and integrated power supply voltage.

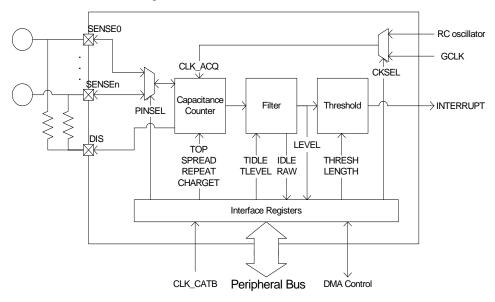

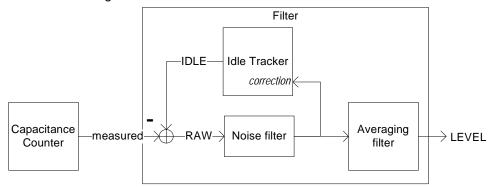

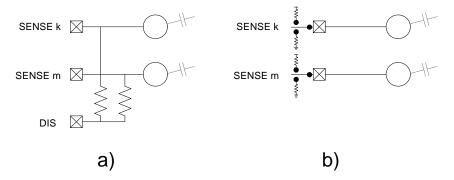

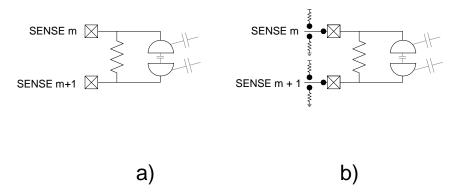

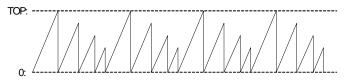

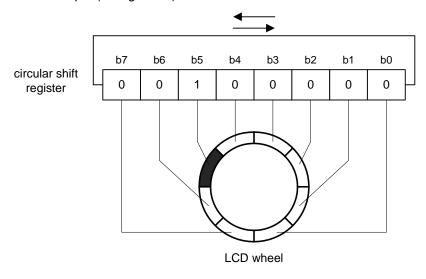

The low-power and high performance capacitive touch module (CATB) is introduced to meet the demand for a low power capacitive touch solution that could be used to handle buttons, sliders and wheels. The CATB provides excellent signal performance, as well as autonomous touch and proximity detection for up to 32 sensors. This solution includes an advanced sequencer in addition to an hardware filtering unit.

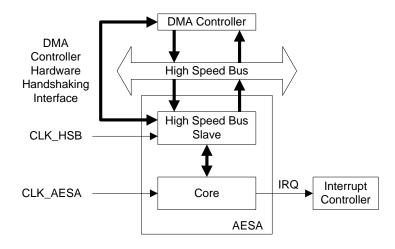

The Advanced Encryption Standard module (AESA) is compliant with the FIPS (Federal Information Processing Standard) Publication 197, Advanced Encryption Standard (AES), which specifies a symmetric block cipher that is used to encrypt and decrypt electronic data. Encryption is the transformation of a usable message, called the plaintext, into an unreadable form, called the ciphertext. On the other hand, decryption is the transformation that recovers the plaintext from the ciphertext. AESA supports 128 bits cryptographic key sizes.

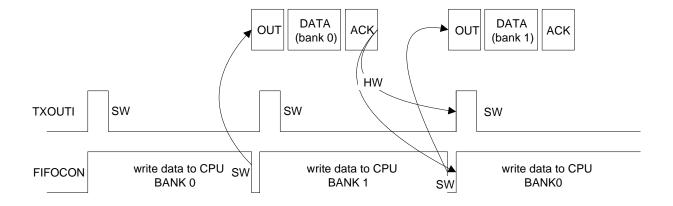

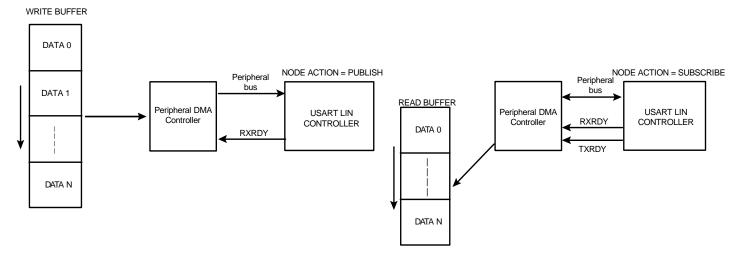

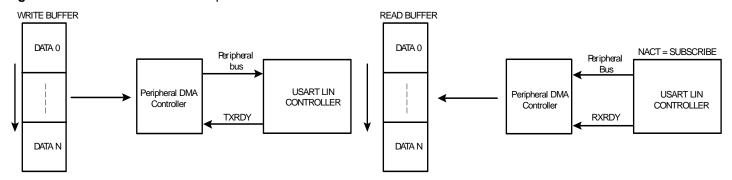

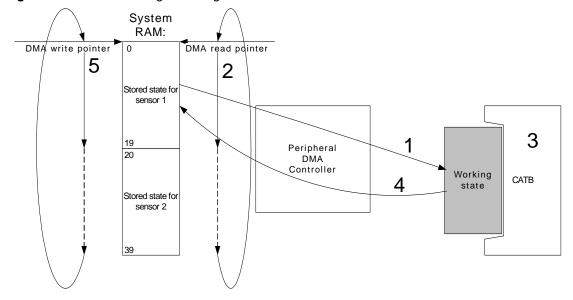

The Peripheral Direct Memory Access (DMA) controller enables data transfers between peripherals and memories without processor involvement. The Peripheral DMA controller drastically reduces processing overhead when transferring continuous and large data streams.

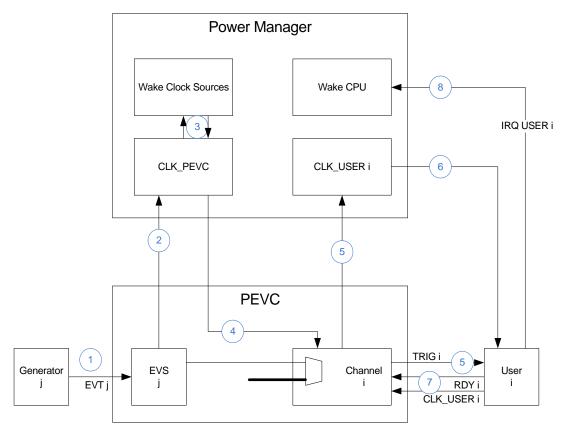

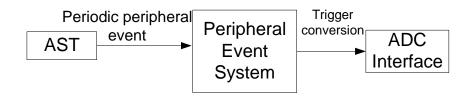

The Peripheral Event System (PES) allows peripherals to receive, react to, and send peripheral events without CPU intervention. Asynchronous interrupts allow advanced peripheral operation in low power modes.

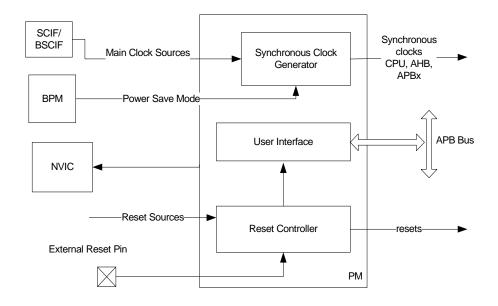

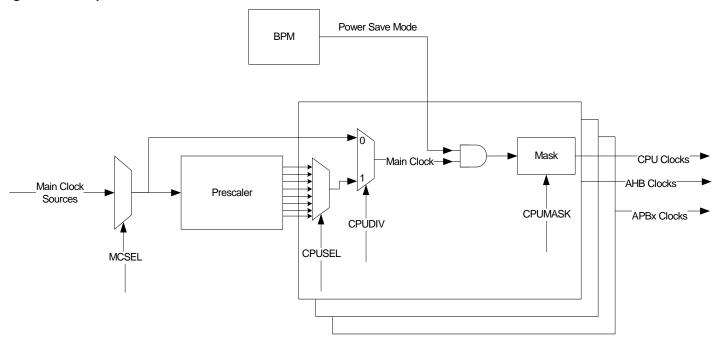

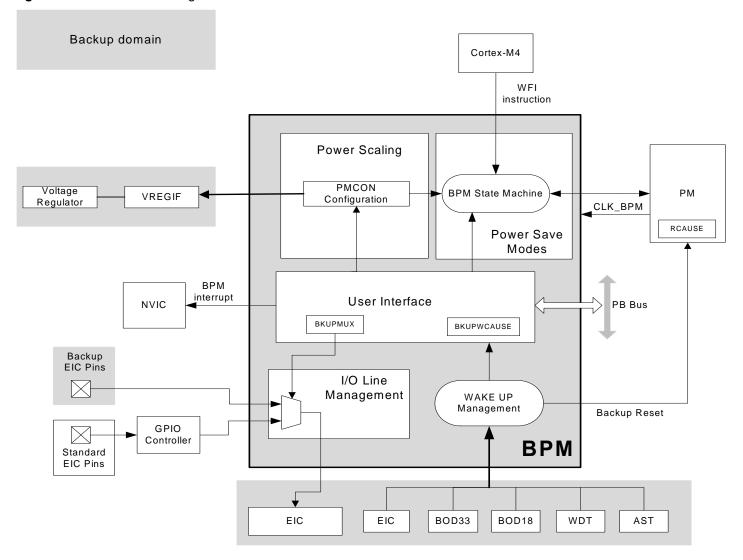

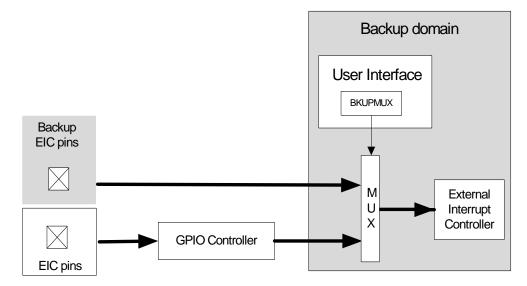

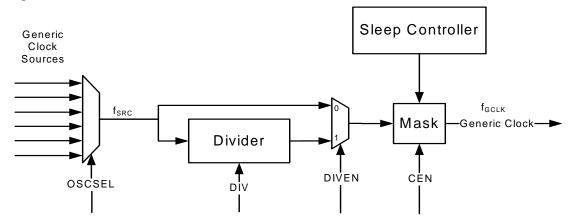

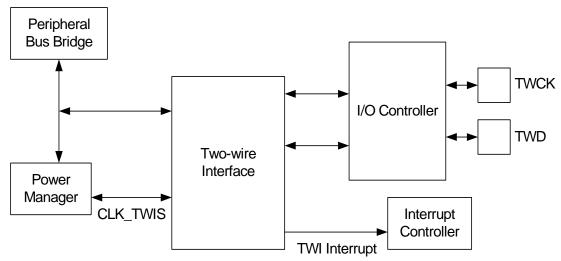

The Power Manager (PM) improves design flexibility and security. The Power Manager supports SleepWalking functionality, by which a module can be selectively activated based on peripheral

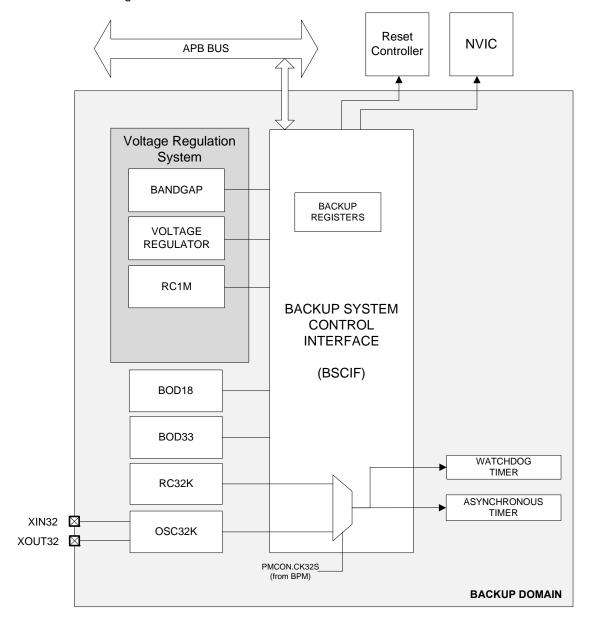

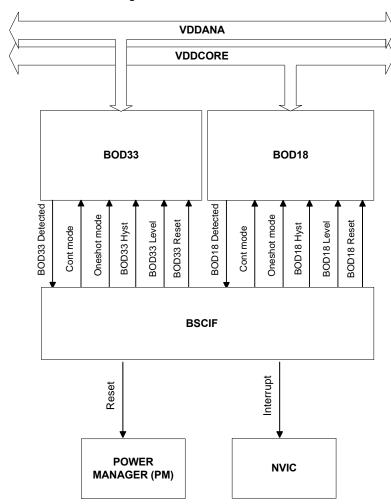

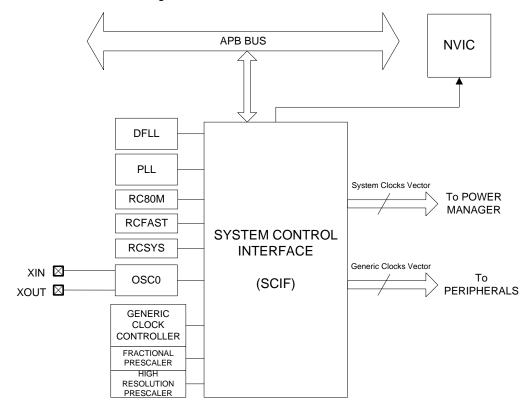

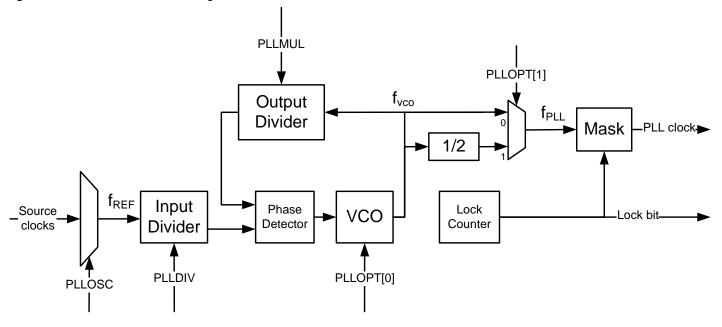

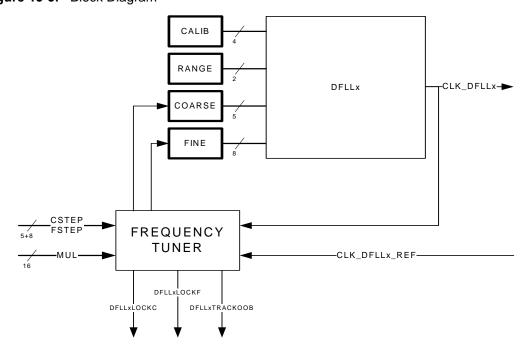

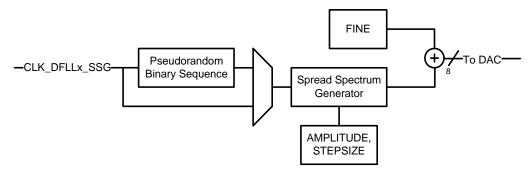

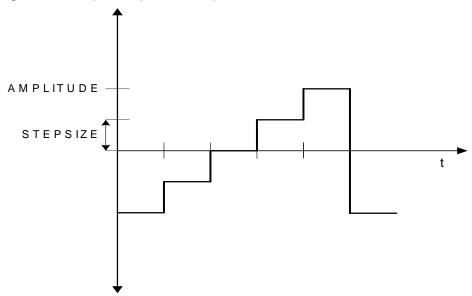

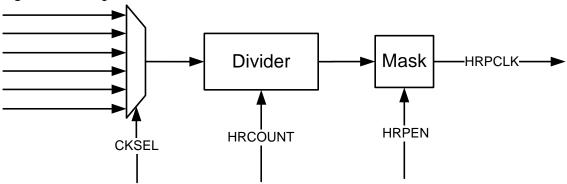

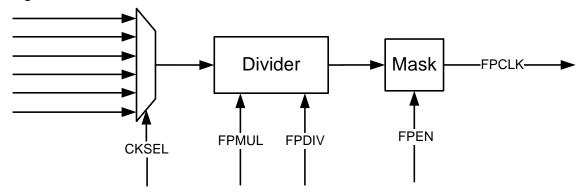

events, even in sleep modes where the module clock is stopped. Power monitoring is supported by on-chip Power-on Reset (POR18, POR33), Brown-out Detectors (BOD18, BOD33). The device features several oscillators, such as Phase Locked Loop (PLL), Digital Frequency Locked Loop (DFLL), Oscillator 0 (OSC0), Internal RC 4,8,12MHz oscillator (RCFAST), system RC oscillator (RCSYS), Internal RC 80MHz, Internal 32kHz RC and 32kHz Crystal Oscillator. Either of these oscillators can be used as source for the system clock. The DFLL is a programmable internal oscillator from 40 to 150MHz. It can be tuned to a high accuracy if an accurate reference clock is running, e.g. the 32kHz crystal oscillator.

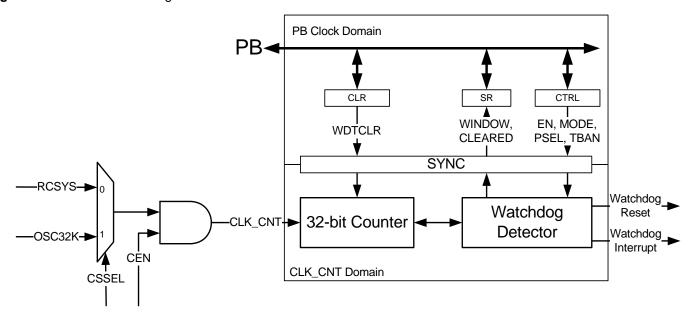

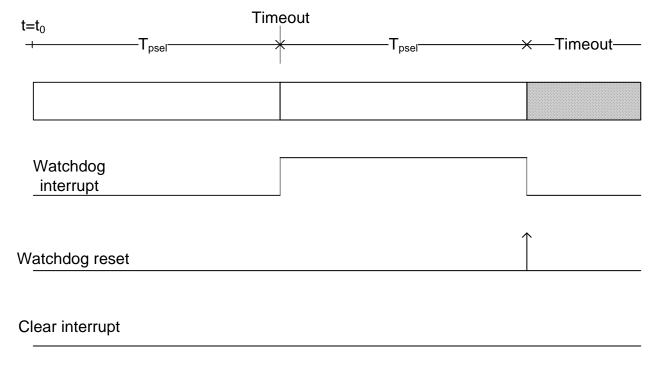

The Watchdog Timer (WDT) will reset the device unless it is periodically serviced by the software. This allows the device to recover from a condition that has caused the system to be unstable.

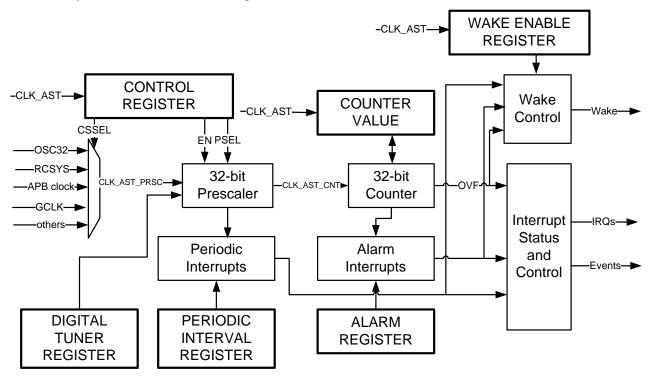

The Asynchronous Timer (AST) combined with the 32kHz crystal oscillator supports powerful real-time clock capabilities, with a maximum timeout of up to 136 years. The AST can operate in counter or calendar mode.

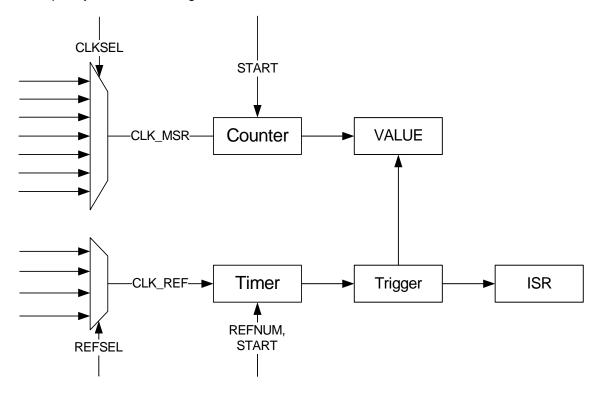

The Frequency Meter (FREQM) allows accurate measuring of a clock frequency by comparing it to a known reference clock.

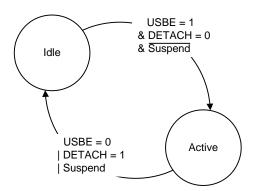

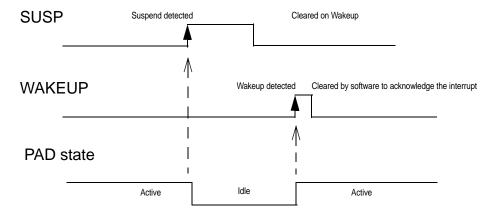

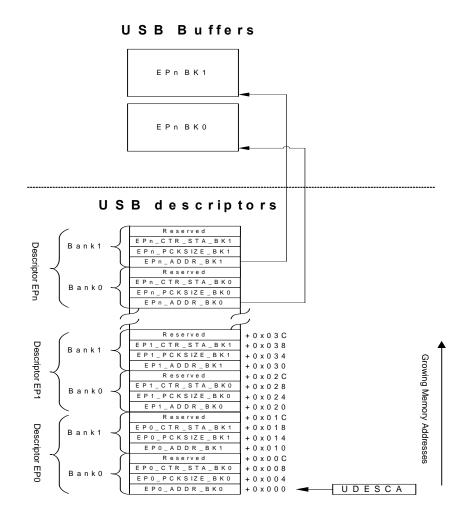

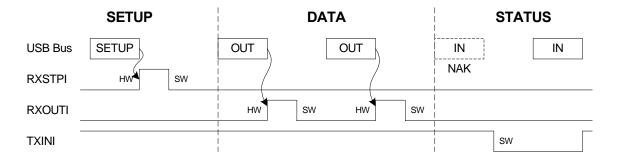

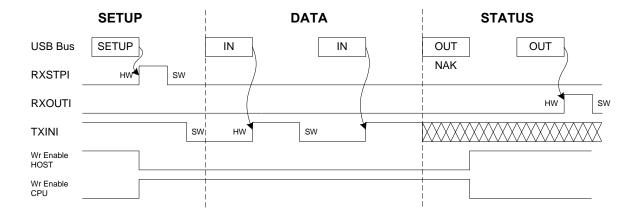

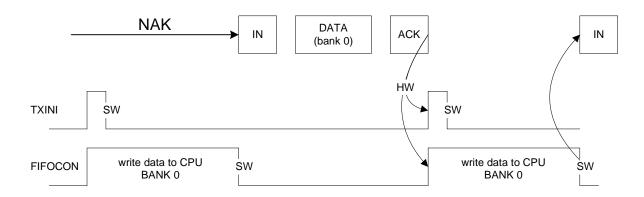

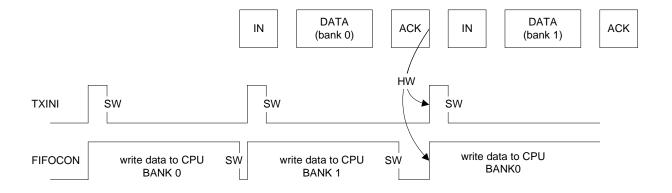

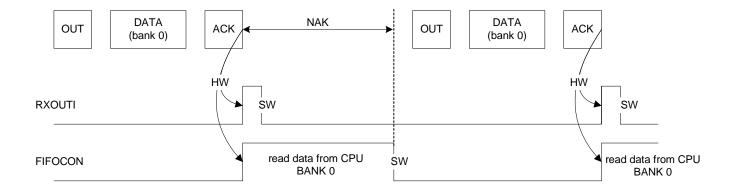

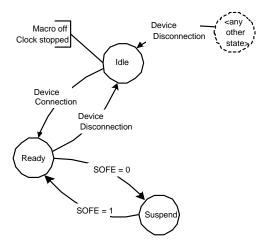

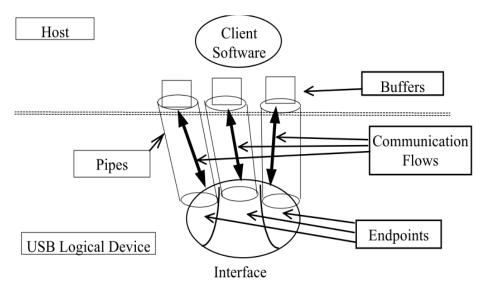

The Full-speed USB 2.0 device and embedded host interface (USBC) supports several USB classes at the same time utilizing the rich end-point configuration.

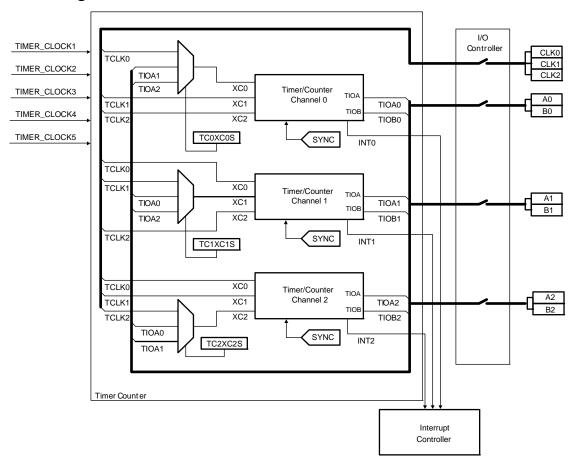

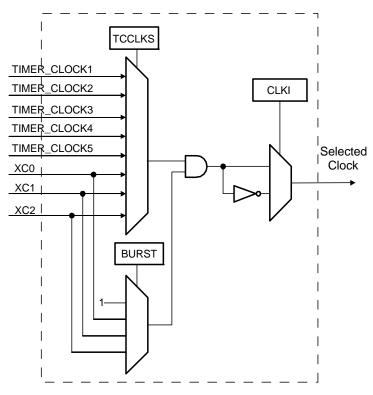

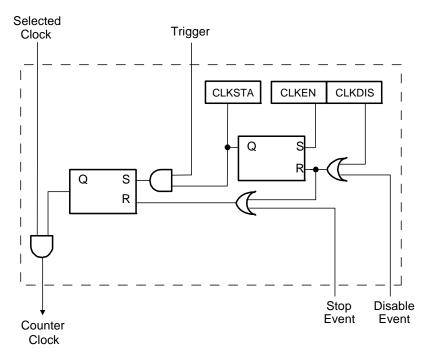

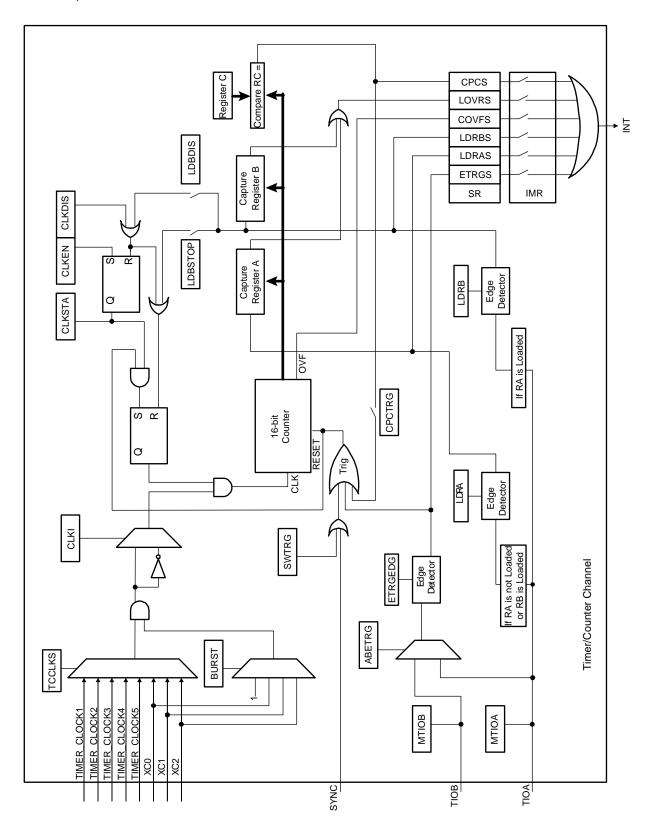

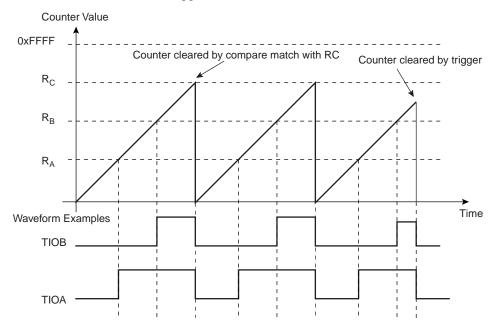

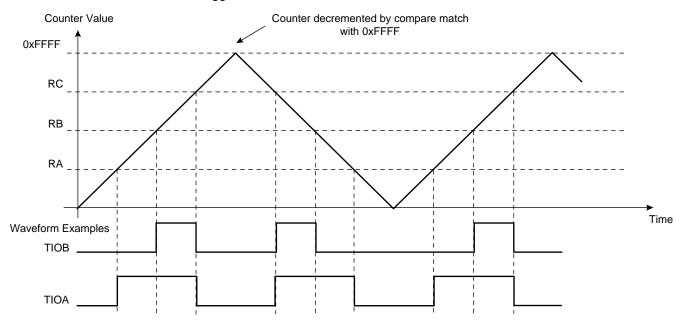

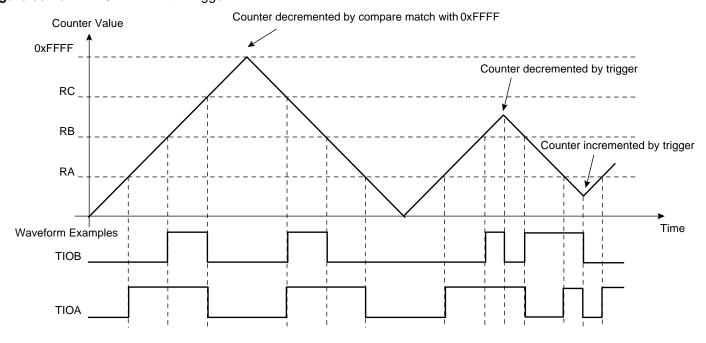

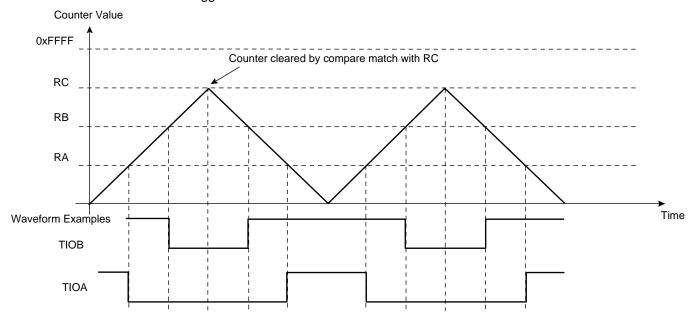

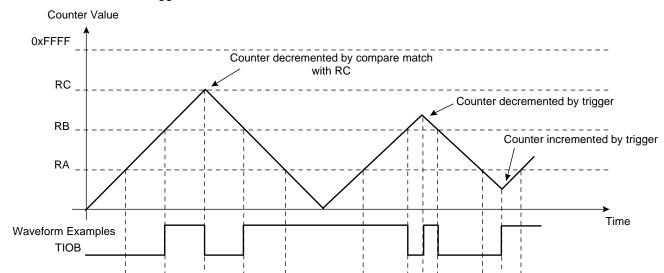

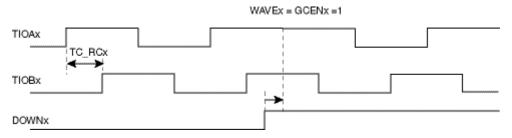

The device includes six identical 16-bit Timer/Counter (TC) channels. Each channel can be independently programmed to perform frequency measurement, event counting, interval measurement, pulse generation, delay timing, and pulse width modulation.

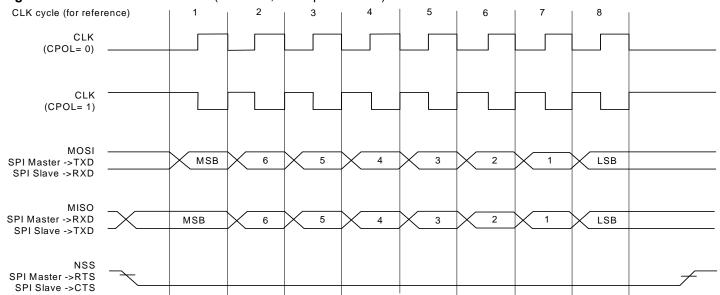

The ATSAM4L8/L4/L2 also features many communication interfaces, like USART, SPI, or TWI, for communication intensive applications. The USART supports different communication modes, like SPI Mode and LIN Mode.

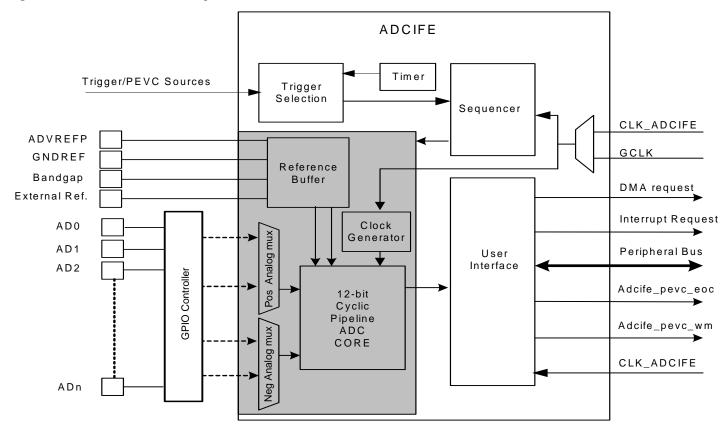

A general purpose 16-channel ADC is provided, as well as four analog comparators (ACIFC). The ADC can operate in 12-bit mode at full speed. The analog comparators can be paired to detect when the sensing voltage is within or outside the defined reference window.

Atmel offers the QTouch Library for embedding capacitive touch buttons, sliders, and wheels functionality. The patented charge-transfer signal acquisition offers robust sensing and includes fully debounced reporting of touch keys as well as Adjacent Key Suppression® (AKS®) technology for unambiguous detection of key events. The easy-to-use QTouch Suite toolchain allows you to explore, develop, and debug your own touch applications.

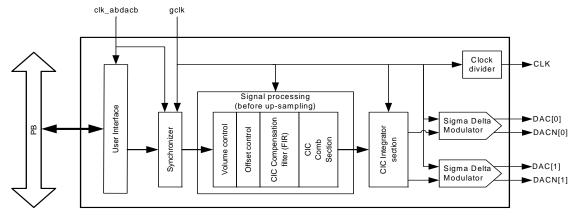

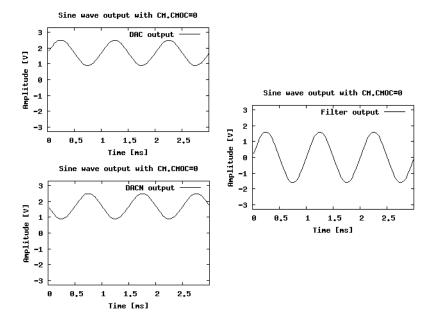

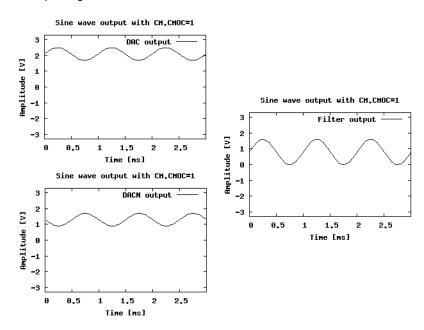

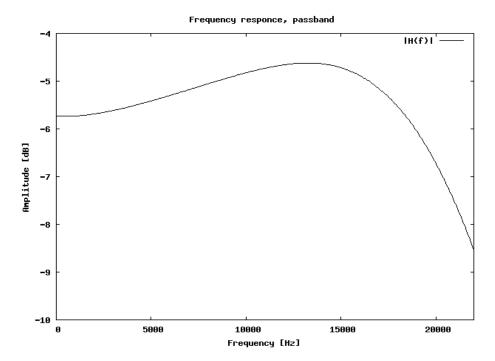

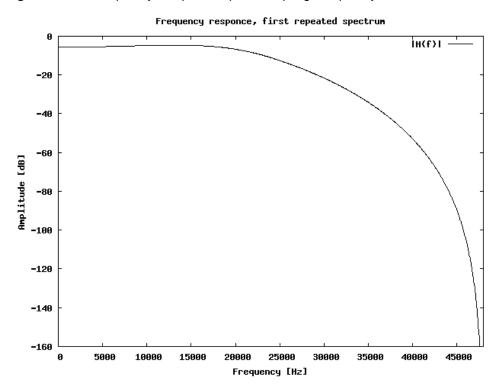

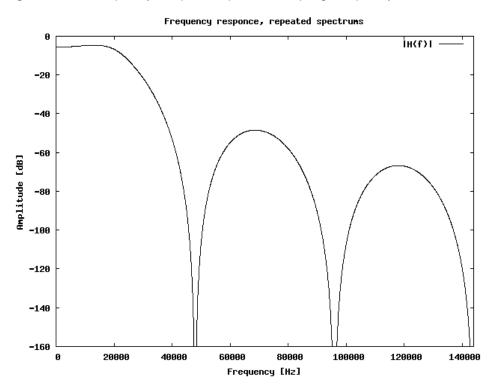

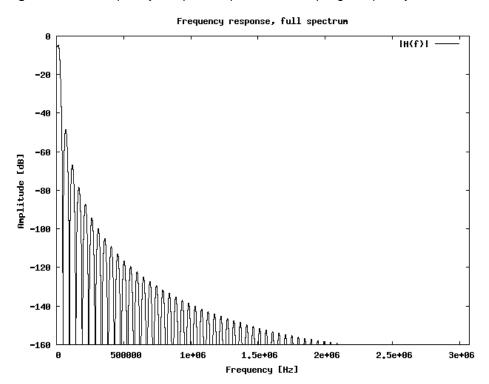

The Audio Bitstream DAC (ABDACB) converts a 16-bit sample value to a digital bitstream with an average value proportional to the sample value. Two channels are supported, making the ABDAC particularly suitable for stereo audio.

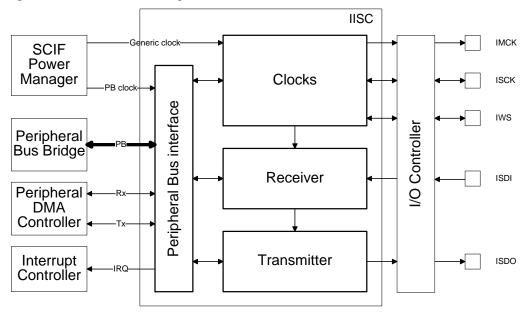

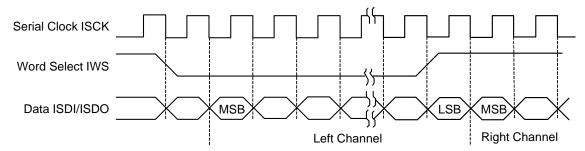

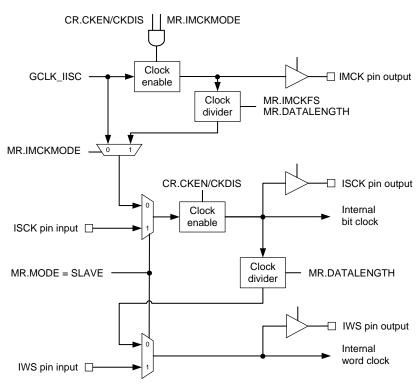

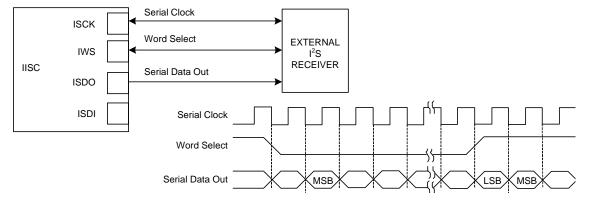

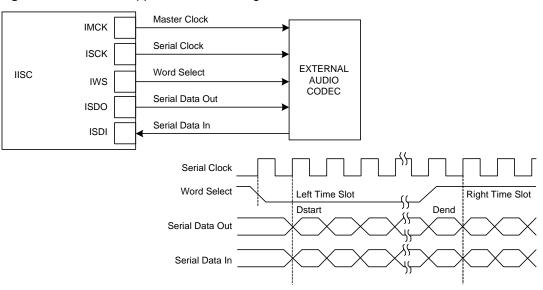

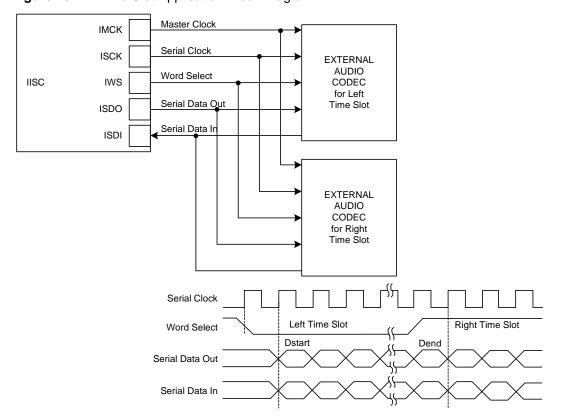

The Inter-IC Sound Controller (IISC) provides a 5-bit wide, bidirectional, synchronous, digital audio link with external audio devices. The controller is compliant with the Inter-IC Sound (I2S) bus specification.

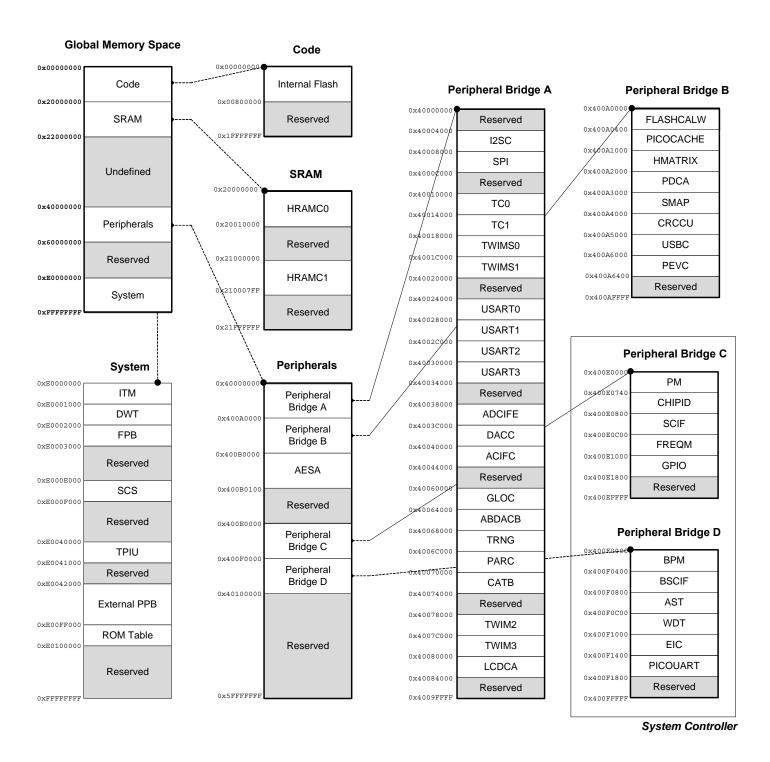

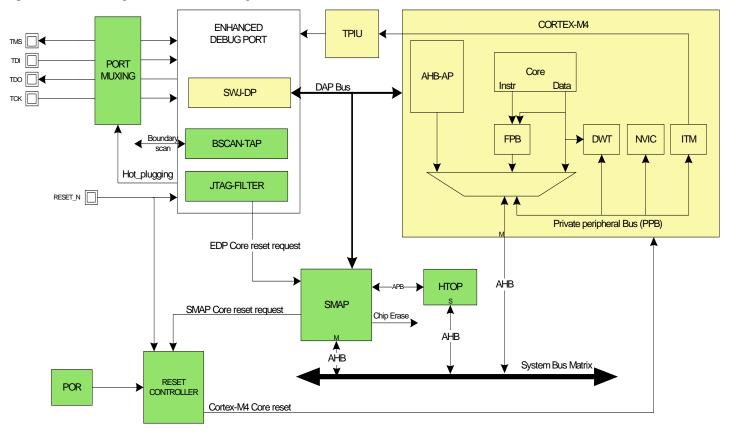

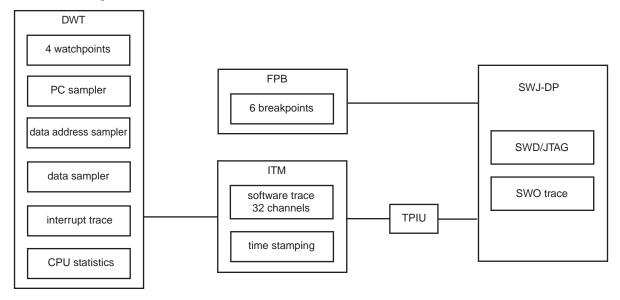

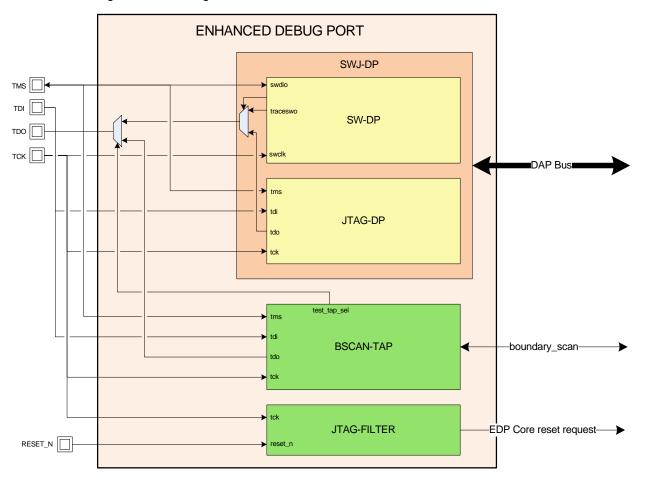

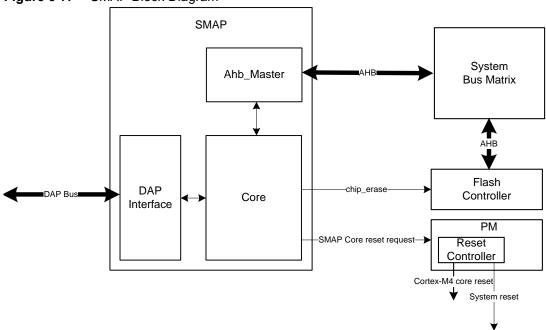

#### 2. Overview

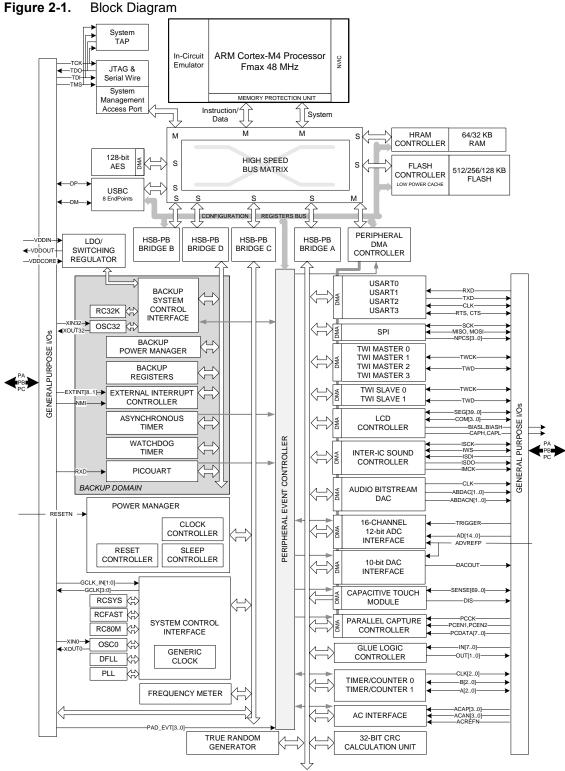

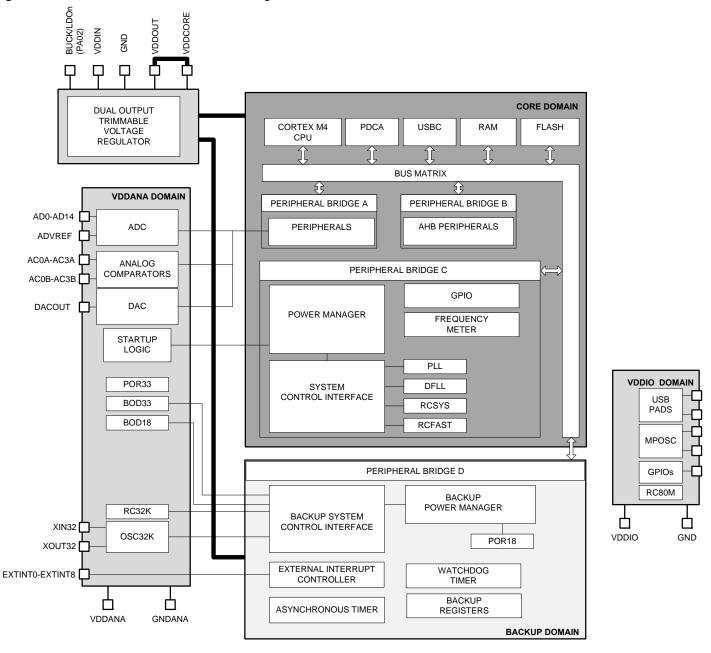

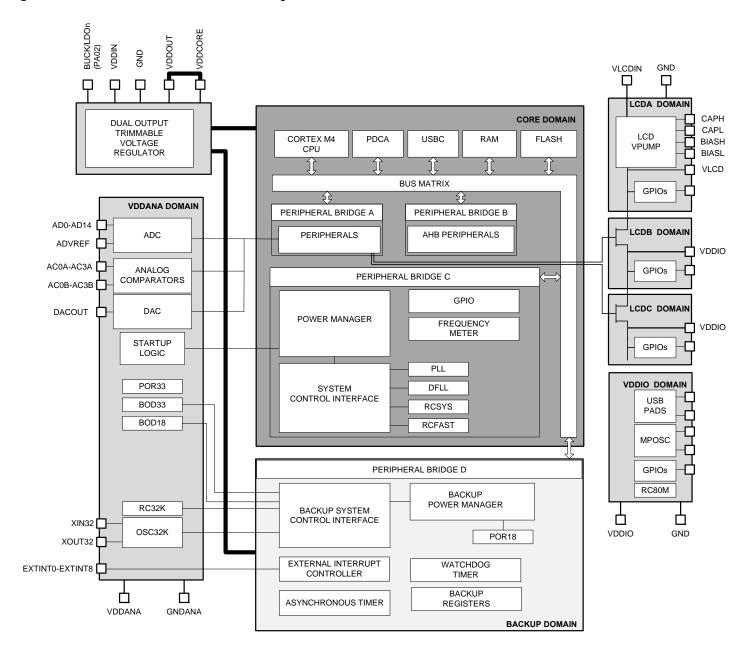

#### 2.1 **Block Diagram**

Figure 2-1.

6

# 2.2 Configuration Summary

42023H-SAM-11/2016

Table 2-1.Sub Series Summary

| Feature     | ATSAM4LC      | ATSAM4LS    |  |  |  |

|-------------|---------------|-------------|--|--|--|

| SEGMENT LCD | Yes           | No          |  |  |  |

| AESA        | Yes           | No          |  |  |  |

| USB         | Device + Host | Device Only |  |  |  |

Table 2-2.

ATSAM4LC Configuration Summary

| Feature                 | ATSAM4LC8/4/2C | ATSAM4LC8/4/2B | ATSAM4LC8/4/2A               |  |  |  |

|-------------------------|----------------|----------------|------------------------------|--|--|--|

| Number of Pins          | 100            | 64             | 48                           |  |  |  |

| Max Frequency           |                | 48MHz          |                              |  |  |  |

| Flash                   |                | 512/256/128KB  |                              |  |  |  |

| SRAM                    |                | 64/32/32KB     |                              |  |  |  |

| SEGMENT LCD             | 4x40           | 4x23           | 4x13                         |  |  |  |

| GPIO                    | 75             | 43             | 27                           |  |  |  |

| High-drive pins         | 6              | 3              | 1                            |  |  |  |

| External Interrupts     |                | 8 + 1 NMI      |                              |  |  |  |

| TWI                     | 2 Masters + 2  | Masters/Slaves | 1 Master + 1<br>Master/Slave |  |  |  |

| USART                   |                | 4              |                              |  |  |  |

| PICOUART                |                | 1              | 0                            |  |  |  |

| Peripheral DMA Channels |                | 16             |                              |  |  |  |

| AESA                    |                | 1              |                              |  |  |  |

| Peripheral Event System |                | 1              |                              |  |  |  |

| SPI                     |                | 1              |                              |  |  |  |

| Asynchronous Timers     |                | 1              |                              |  |  |  |

| Timer/Counter Channels  | 6              |                | 3                            |  |  |  |

| Parallel Capture Inputs |                | 8              |                              |  |  |  |

| Frequency Meter         |                | 1              |                              |  |  |  |

| Watchdog Timer          |                | 1              |                              |  |  |  |

| Power Manager           | 1              |                |                              |  |  |  |

| Glue Logic LUT          | :              | 1              |                              |  |  |  |

Table 2-2.

ATSAM4LC Configuration Summary

| Feature             | ATSAM4LC8/4/2C                      | ATSAM4LC8/4/2B         | ATSAM4LC8/4/2A |  |  |  |  |  |

|---------------------|-------------------------------------|------------------------|----------------|--|--|--|--|--|

|                     | Digital Freque                      | ency Locked Loop 20-1  | 50MHz (DFLL)   |  |  |  |  |  |

|                     | Phase                               | Locked Loop 48-240M    | Hz (PLL)       |  |  |  |  |  |

|                     | Crystal Oscillator 0.6-30MHz (OSC0) |                        |                |  |  |  |  |  |

| Oscillators         | Crystal Oscillator 32 kHz (OSC32K)  |                        |                |  |  |  |  |  |

| Oscillators         | RC Oscillator 80MHz (RC80M)         |                        |                |  |  |  |  |  |

|                     | RC O                                | scillator 4,8,12MHz (R | CFAST)         |  |  |  |  |  |

|                     |                                     | Oscillator 115kHz (RC  | •              |  |  |  |  |  |

|                     | RC Oscillator 32kHz (RC32K)         |                        |                |  |  |  |  |  |

| ADC                 | 15-channel                          | 7-channel              | 3-channel      |  |  |  |  |  |

| DAC                 | 1-channel                           |                        |                |  |  |  |  |  |

| Analog Comparators  | 4                                   | 2                      | 1              |  |  |  |  |  |

| CATB Sensors        | 32                                  | 32                     | 26             |  |  |  |  |  |

| USB                 |                                     | 1                      |                |  |  |  |  |  |

| Audio Bitstream DAC |                                     | 1                      |                |  |  |  |  |  |

| IIS Controller      |                                     | 1                      |                |  |  |  |  |  |

| Packages            | TQFP/VFBGA                          | TQFP/QFN/<br>WLCSP     | TQFP/QFN       |  |  |  |  |  |

Table 2-3.

ATSAM4LS Configuration Summary

| Feature                 | ATSAM4LS8/4/2C | ATSAM4LS8/4/2B               | ATSAM4LS8/4/2A                           |  |  |  |  |  |

|-------------------------|----------------|------------------------------|------------------------------------------|--|--|--|--|--|

| Number of Pins          | 100            | 64                           | 48                                       |  |  |  |  |  |

| Max Frequency           |                | 48MHz                        |                                          |  |  |  |  |  |

| Flash                   |                | 512/256/128KB                |                                          |  |  |  |  |  |

| SRAM                    |                | 64/32/32KB                   |                                          |  |  |  |  |  |

| SEGMENT LCD             |                | NA                           |                                          |  |  |  |  |  |

| GPIO                    | 80             | 48                           | 32                                       |  |  |  |  |  |

| High-drive pins         | 6              | 3                            | 1                                        |  |  |  |  |  |

| External Interrupts     | 8 + 1 NMI      |                              |                                          |  |  |  |  |  |

| TWI                     | 2 Masters + 2  | 1 Master + 1<br>Master/Slave |                                          |  |  |  |  |  |

| USART                   |                | 4                            | 3 in LC sub series<br>4 in LS sub series |  |  |  |  |  |

| PICOUART                |                | 1                            | 0                                        |  |  |  |  |  |

| Peripheral DMA Channels |                | 16                           |                                          |  |  |  |  |  |

| AESA                    |                | NA                           |                                          |  |  |  |  |  |

| Peripheral Event System | 1              |                              |                                          |  |  |  |  |  |

| SPI                     | 1              |                              |                                          |  |  |  |  |  |

| Asynchronous Timers     |                | 1                            |                                          |  |  |  |  |  |

Table 2-3.

ATSAM4LS Configuration Summary

| Feature                 | ATSAM4LS8/4/2C                               | ATSAM4LS8/4/2B                                                                                                                                                                | ATSAM4LS8/4/2A                                 |  |  |  |  |  |

|-------------------------|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|--|--|--|--|--|

| Timer/Counter Channels  | 6                                            |                                                                                                                                                                               | 3                                              |  |  |  |  |  |

| Parallel Capture Inputs |                                              | 8                                                                                                                                                                             |                                                |  |  |  |  |  |

| Frequency Meter         |                                              | 1                                                                                                                                                                             |                                                |  |  |  |  |  |

| Watchdog Timer          |                                              | 1                                                                                                                                                                             |                                                |  |  |  |  |  |

| Power Manager           |                                              | 1                                                                                                                                                                             |                                                |  |  |  |  |  |

| Glue Logic LUT          |                                              | 2 1                                                                                                                                                                           |                                                |  |  |  |  |  |

| Oscillators             | Phase<br>Crysta<br>Cryst<br>RC<br>RC O<br>RC | ency Locked Loop 20-1<br>Locked Loop 48-240M<br>I Oscillator 0.6-30MHz<br>al Oscillator 32kHz (O:<br>Oscillator 80MHz (RC<br>scillator 4,8,12MHz (RC<br>Oscillator 115kHz (RC | Hz (PLL)<br>(OSC0)<br>SC32K)<br>80M)<br>CFAST) |  |  |  |  |  |

| ADC                     | 15-channel                                   | 7-channel                                                                                                                                                                     | el 3-channel                                   |  |  |  |  |  |

| DAC                     |                                              | 1-channel                                                                                                                                                                     |                                                |  |  |  |  |  |

| Analog Comparators      | 4                                            | 2                                                                                                                                                                             | 1                                              |  |  |  |  |  |

| CATB Sensors            | 32                                           | 32                                                                                                                                                                            | 26                                             |  |  |  |  |  |

| USB                     |                                              | 1                                                                                                                                                                             |                                                |  |  |  |  |  |

| Audio Bitstream DAC     |                                              | 1                                                                                                                                                                             |                                                |  |  |  |  |  |

| IIS Controller          |                                              | 1                                                                                                                                                                             |                                                |  |  |  |  |  |

| Packages                | TQFP/VFBGA                                   | TQFP/QFN/<br>WLCSP                                                                                                                                                            | TQFP/QFN                                       |  |  |  |  |  |

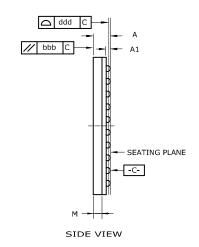

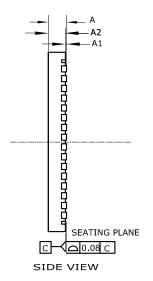

## 3. Package and Pinout

## 3.1 Package

42023H-SAM-11/2016

The device pins are multiplexed with peripheral functions as described in Section 3.2 "Peripheral Multiplexing on I/O lines" on page 19.

#### 3.1.1 ATSAM4LCx Pinout

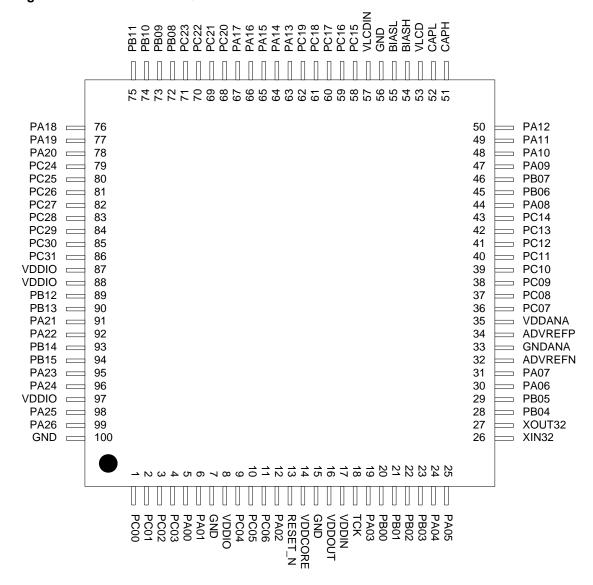

Figure 3-1. ATSAM4LC TQFP100 Pinout

9

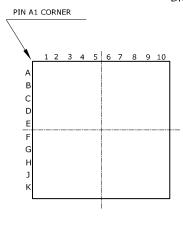

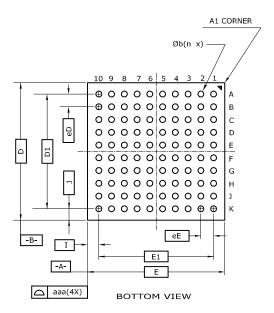

Figure 3-2. ATSAM4LC VFBGA100 Pinout

|   | 1            | 2           | 3     | 4     | 5       | 6           | 7    | 8     | 9    | 10    |

|---|--------------|-------------|-------|-------|---------|-------------|------|-------|------|-------|

| Α | PA05         | PA04        | GND   | VDDIN | VDDOUT  | VDD<br>CORE | PA02 | VDDIO | GND  | PC00  |

| В | PB05         | XIN32       | PA03  | TCK   | RESET_N | PC06        | PC03 | PA01  | PA00 | GND   |

| С | PB04         | XOUT32      | PA06  | PB03  | PC04    | PC05        | PC02 | PC01  | PA26 | VDDIO |

| D | (AD<br>VREFN | GNDANA      | PA07  | PC10  | PB01    | PA23        | PB14 | PB15  | PA25 | PA24  |

| Ε | VDDANA       | AD<br>VREFP | PC08  | PC11  | PB02    | VDDIO       | PB12 | PB13  | PA21 | PA22  |

| F | PC09         | PC07        | PC12  | PC13  | PA09    | PC27        | PC29 | PC30  | PC31 | VDDIO |

| G | PC14         | PA08        | PB06  | PC19  | PA15    | PB08        | PB09 | PB10  | PC26 | PC28  |

| Н | PB07         | PA10        | PA11  | PC17  | PA13    | PA17        | PC20 | PC23  | PC25 | PA20  |

| J | CAPL         | PA12        | PB00  | BIASL | PC15    | PC16        | PA16 | PC22  | PC24 | PA19  |

| K | САРН         | VLCD        | BIASH | GND   | VLCDIN  | PC18        | PA14 | PC21  | PB11 | PA18  |

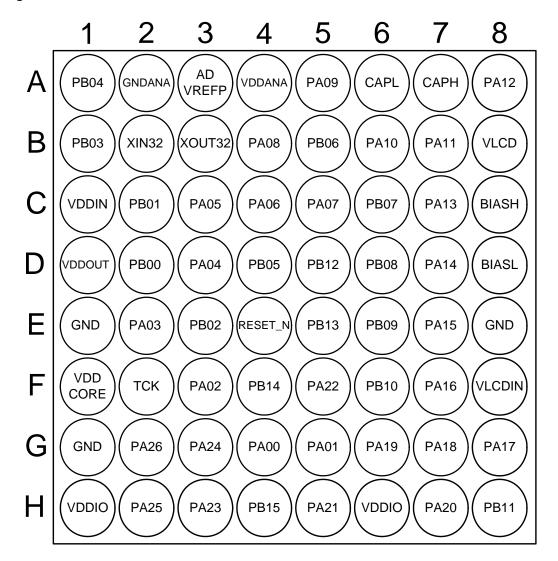

Figure 3-3. ATSAM4LC WLCSP64 Pinout

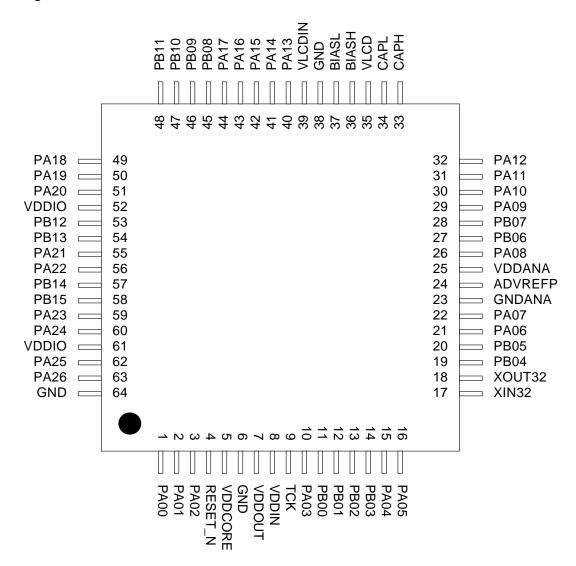

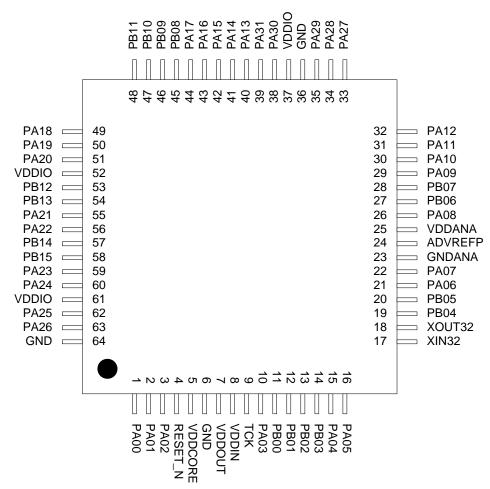

Figure 3-4. ATSAM4LC TQFP64/QFN64 Pinout

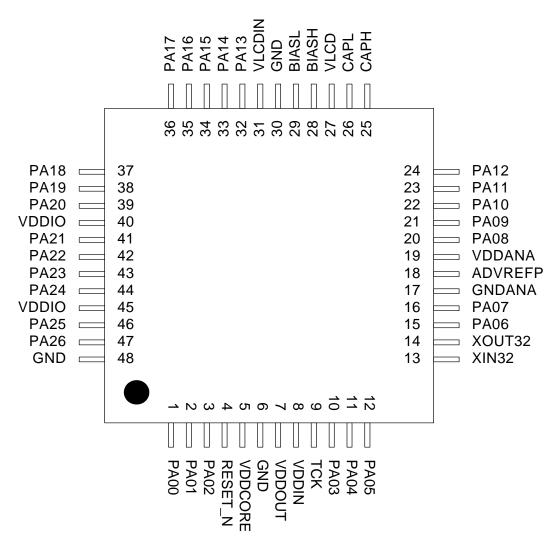

Figure 3-5. ATSAM4LC TQFP48/QFN48 Pinout

#### 3.1.2 ATSAM4LSx Pinout

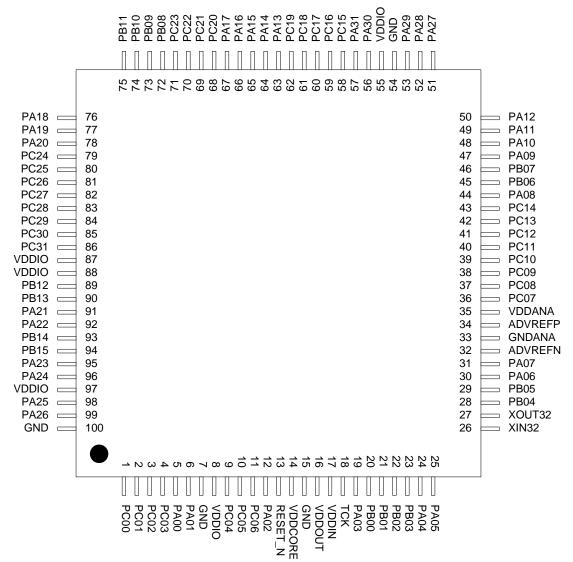

Figure 3-6. ATSAM4LS TQFP100 Pinout

Figure 3-7. ATSAM4LS VFBGA100 Pinout

|   | 1           | 2           | 3    | 4     | 5       | 6           | 7    | 8     | 9    | 10    |

|---|-------------|-------------|------|-------|---------|-------------|------|-------|------|-------|

| Α | PA05        | PA04        | GND  | VDDIN | VDDOUT  | VDD<br>CORE | PA02 | VDDIO | GND  | PC00  |

| В | PB05        | XIN32       | PA03 | TCK   | RESET_N | PC06        | PC03 | PA01  | PA00 | GND   |

| С | PB04        | XOUT32      | PA06 | PB03  | PC04    | PC05        | PC02 | PC01  | PA26 | VDDIO |

| D | AD<br>VREFN | GNDANA      | PA07 | PC10  | PB01    | PA23        | PB14 | PB15  | PA25 | PA24  |

| Е | VDDANA)(    | AD<br>VREFP | PC08 | PC11  | PB02    | (VDDIO)     | PB12 | PB13  | PA21 | PA22  |

| F | PC09        | PC07        | PC12 | PC13  | PA09    | PC27        | PC29 | PC30  | PC31 | VDDIO |

| G | PC14        | PA08        | PB06 | PC19  | PA15    | PB08        | PB09 | PB10  | PC26 | PC28  |

| Н | PB07        | PA10        | PA11 | PC17  | PA13    | PA17        | PC20 | PC23  | PC25 | PA20  |

| J | PA28        | PA12        | PB00 | VDDIO | PC15    | PC16        | PA16 | PC22  | PC24 | PA19  |

| K | PA27        | PA29        | GND  | PA30  | PA31    | PC18        | PA14 | PC21  | PB11 | PA18  |

Figure 3-8. ATSAM4LS WLCSP64 Pinout

|   | 1      | 2      | 3           | 4       | 5    | 6     | 7    | 8     |

|---|--------|--------|-------------|---------|------|-------|------|-------|

| Α | PB04   | GNDANA | AD<br>VREFP | VDDANA  | PA09 | PA28  | PA27 | PA12  |

| В | РВ03   | XIN32  | XOUT32      | PA08    | PB06 | PA10  | PA11 | PA29  |

| С | VDDIN  | PB01   | PA05        | PA06    | PA07 | PB07  | PA13 | GND   |

| D | VDDOUT | PB00   | PA04        | PB05    | PB12 | PB08  | PA14 | VDDIO |

| Ε | GND    | PA03   | PB02        | RESET_N | PB13 | PB09  | PA15 | PA30  |

| F | VDD    | TCK    | PA02        | PB14    | PA22 | PB10  | PA16 | PA31  |

| G | GND    | PA26   | PA24        | PA00    | PA01 | PA19  | PA18 | PA17  |

| Η | VDDIO  | PA25   | PA23        | PB15    | PA21 | VDDIO | PA20 | PB11  |

Figure 3-9. ATSAM4LS TQFP64/QFN64 Pinout

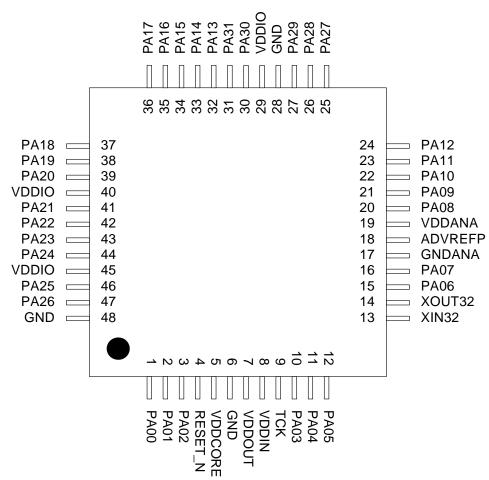

Figure 3-10. ATSAM4LS TQFP48/QFN48 Pinout

See Section 3.3 "Signals Description" on page 31 for a description of the various peripheral signals.

Refer to "Electrical Characteristics" on page 1121 for a description of the electrical properties of the pin types used.

## 3.2 Peripheral Multiplexing on I/O lines

## 3.2.1 Multiplexed Signals

Each GPIO line can be assigned to one of the peripheral functions. The following tables (Section 3-1 "100-pin GPIO Controller Function Multiplexing" on page 19 to Section 3-4 "48-pin GPIO Controller Function Multiplexing" on page 28) describes the peripheral signals multiplexed to the GPIO lines.

Peripheral functions that are not relevant in some parts of the family are grey-shaded.

For description of differents Supply voltage source, refer to the Section 5. "Power and Startup Considerations" on page 43.

**Table 3-1.** 100-pin GPIO Controller Function Multiplexing (Sheet 1 of 4)

|     | ATSAM4LC   |     | ATSAM4LS   | Pin  | GPIO | Supply |               |               | G                | PIO Function    | ns                |                |                 |

|-----|------------|-----|------------|------|------|--------|---------------|---------------|------------------|-----------------|-------------------|----------------|-----------------|

| QFN | VFBGA      | QFN | VFBGA      |      |      |        | Α             | В             | С                | D               | E                 | F              | G               |

| 5   | В9         | 5   | В9         | PA00 | 0    | VDDIO  |               |               |                  |                 |                   |                |                 |

| 6   | B8         | 6   | B8         | PA01 | 1    | VDDIO  |               |               |                  |                 |                   |                |                 |

| 12  | A7         | 12  | A7         | PA02 | 2    | VDDIN  | SCIF<br>GCLK0 | SPI<br>NPCS0  |                  |                 |                   |                | CATB<br>DIS     |

| 19  | В3         | 19  | В3         | PA03 | 3    | VDDIN  |               | SPI<br>MISO   |                  |                 |                   |                |                 |

| 24  | A2         | 24  | A2         | PA04 | 4    | VDDANA | ADCIFE<br>AD0 | USART0<br>CLK | EIC<br>EXTINT2   | GLOC<br>IN1     |                   |                | CATB<br>SENSE0  |

| 25  | <b>A</b> 1 | 25  | A1         | PA05 | 5    | VDDANA | ADCIFE<br>AD1 | USART0<br>RXD | EIC<br>EXTINT3   | GLOC<br>IN2     | ADCIFE<br>TRIGGER |                | CATB<br>SENSE1  |

| 30  | С3         | 30  | C3         | PA06 | 6    | VDDANA | DACC<br>VOUT  | USART0<br>RTS | EIC<br>EXTINT1   | GLOC<br>IN0     | ACIFC<br>ACAN0    |                | CATB<br>SENSE2  |

| 31  | D3         | 31  | D3         | PA07 | 7    | VDDANA | ADCIFE<br>AD2 | USART0<br>TXD | EIC<br>EXTINT4   | GLOC<br>IN3     | ACIFC<br>ACAP0    |                | CATB<br>SENSE3  |

| 44  | G2         | 44  | G2         | PA08 | 8    | LCDA   | USART0<br>RTS | TC0<br>A0     | PEVC<br>PAD EVT0 | GLOC<br>OUT0    |                   | LCDCA<br>SEG23 | CATB<br>SENSE4  |

| 47  | F5         | 47  | F5         | PA09 | 9    | LCDA   | USART0<br>CTS | TC0<br>B0     | PEVC<br>PAD EVT1 | PARC<br>PCDATA0 |                   | LCDCA<br>COM3  | CATB<br>SENSE5  |

| 48  | H2         | 48  | H2         | PA10 | 10   | LCDA   | USART0<br>CLK | TC0<br>A1     | PEVC<br>PAD EVT2 | PARC<br>PCDATA1 |                   | LCDCA<br>COM2  | CATB<br>SENSE6  |

| 49  | Н3         | 49  | Н3         | PA11 | 11   | LCDA   | USART0<br>RXD | TC0<br>B1     | PEVC<br>PAD EVT3 | PARC<br>PCDATA2 |                   | LCDCA<br>COM1  | CATB<br>SENSE7  |

| 50  | J2         | 50  | J2         | PA12 | 12   | LCDA   | USART0<br>TXD | TC0<br>A2     |                  | PARC<br>PCDATA3 |                   | LCDCA<br>COM0  | CATB<br>DIS     |

| 63  | Н5         | 63  | Н5         | PA13 | 13   | LCDA   | USART1<br>RTS | TC0<br>B2     | SPI<br>NPCS1     | PARC<br>PCDATA4 |                   | LCDCA<br>SEG5  | CATB<br>SENSE8  |

| 64  | <b>K</b> 7 | 64  | <b>K</b> 7 | PA14 | 14   | LCDA   | USART1<br>CLK | TC0<br>CLK0   | SPI<br>NPCS2     | PARC<br>PCDATA5 |                   | LCDCA<br>SEG6  | CATB<br>SENSE9  |

| 65  | G5         | 65  | G5         | PA15 | 15   | LCDA   | USART1<br>RXD | TC0<br>CLK1   | SPI<br>NPCS3     | PARC<br>PCDATA6 |                   | LCDCA<br>SEG7  | CATB<br>SENSE10 |

Table 3-1.

100-pin GPIO Controller Function Multiplexing (Sheet 2 of 4)

|     | ATSAM4LC |     | ATSAM4LS | Pin  | GPIO | Supply |                | 0 (1 111        | G               | PIO Functio     | ns                |                |                 |

|-----|----------|-----|----------|------|------|--------|----------------|-----------------|-----------------|-----------------|-------------------|----------------|-----------------|

| QFN | VFBGA    | QFN | VFBGA    |      |      |        | Α              | В               | С               | D               | E                 | F              | G               |

| 66  | J7       | 66  | J7       | PA16 | 16   | LCDA   | USART1<br>TXD  | TC0<br>CLK2     | EIC<br>EXTINT1  | PARC<br>PCDATA7 |                   | LCDCA<br>SEG8  | CATB<br>SENSE11 |

| 67  | Н6       | 67  | Н6       | PA17 | 17   | LCDA   | USART2<br>RTS  | ABDACB<br>DAC0  | EIC<br>EXTINT2  | PARC<br>PCCK    |                   | LCDCA<br>SEG9  | CATB<br>SENSE12 |

| 76  | K10      | 76  | K10      | PA18 | 18   | LCDA   | USART2<br>CLK  | ABDACB<br>DACN0 | EIC<br>EXTINT3  | PARC<br>PCEN1   |                   | LCDCA<br>SEG18 | CATB<br>SENSE13 |

| 77  | J10      | 77  | J10      | PA19 | 19   | LCDA   | USART2<br>RXD  | ABDACB<br>DAC1  | EIC<br>EXTINT4  | PARC<br>PCEN2   | SCIF<br>GCLK0     | LCDCA<br>SEG19 | CATB<br>SENSE14 |

| 78  | H10      | 78  | H10      | PA20 | 20   | LCDA   | USART2<br>TXD  | ABDACB<br>DACN1 | EIC<br>EXTINT5  | GLOC<br>IN0     | SCIF<br>GCLK1     | LCDCA<br>SEG20 | CATB<br>SENSE15 |

| 91  | E9       | 91  | E9       | PA21 | 21   | LCDC   | SPI<br>MISO    | USART1<br>CTS   | EIC<br>EXTINT6  | GLOC<br>IN1     | TWIM2<br>TWD      | LCDCA<br>SEG34 | CATB<br>SENSE16 |

| 92  | E10      | 92  | E10      | PA22 | 22   | LCDC   | SPI<br>MOSI    | USART2<br>CTS   | EIC<br>EXTINT7  | GLOC<br>IN2     | TWIM2<br>TWCK     | LCDCA<br>SEG35 | CATB<br>SENSE17 |

| 95  | D6       | 95  | D6       | PA23 | 23   | LCDC   | SPI<br>SCK     | TWIMS0<br>TWD   | EIC<br>EXTINT8  | GLOC<br>IN3     | SCIF<br>GCLK IN0  | LCDCA<br>SEG38 | CATB<br>DIS     |

| 96  | D10      | 96  | D10      | PA24 | 24   | LCDC   | SPI<br>NPCS0   | TWIMS0<br>TWCK  |                 | GLOC<br>OUT0    | SCIF<br>GCLK IN1  | LCDCA<br>SEG39 | CATB<br>SENSE18 |

| 98  | D9       | 98  | D9       | PA25 | 25   | VDDIO  | USBC<br>DM     | USART2<br>RXD   |                 |                 |                   |                | CATB<br>SENSE19 |

| 99  | C9       | 99  | C9       | PA26 | 26   | VDDIO  | USBC<br>DP     | USART2<br>TXD   |                 |                 |                   |                | CATB<br>SENSE20 |

|     |          | 51  | K1       | PA27 | 27   | LCDA   | SPI<br>MISO    | IISC            | ABDACB<br>DAC0  | GLOC<br>IN4     | USART3<br>RTS     |                | CATB<br>SENSE0  |

|     |          | 52  | J1       | PA28 | 28   | LCDA   | SPI<br>MOSI    | IISC<br>ISDI    | ABDACB<br>DACN0 | GLOC<br>IN5     | USART3<br>CTS     |                | CATB<br>SENSE1  |

|     |          | 53  | K2       | PA29 | 29   | LCDA   | SPI<br>SCK     | IISC<br>IWS     | ABDACB<br>DAC1  | GLOC<br>IN6     | USART3<br>CLK     |                | CATB<br>SENSE2  |

|     |          | 56  | K4       | PA30 | 30   | LCDA   | SPI<br>NPCS0   | IISC<br>ISDO    | ABDACB<br>DACN1 | GLOC<br>IN7     | USART3<br>RXD     |                | CATB<br>SENSE3  |

|     |          | 57  | K5       | PA31 | 31   | LCDA   | SPI<br>NPCS1   | IISC            | ABDACB<br>CLK   | GLOC<br>OUT1    | USART3<br>TXD     |                | CATB<br>DIS     |

| 20  | J3       | 20  | J3       | PB00 | 32   | VDDIN  | TWIMS1<br>TWD  | USART0<br>RXD   |                 |                 |                   |                | CATB<br>SENSE21 |

| 21  | D5       | 21  | D5       | PB01 | 33   | VDDIN  | TWIMS1<br>TWCK | USART0<br>TXD   | EIC<br>EXTINT0  |                 |                   |                | CATB<br>SENSE22 |

| 22  | E5       | 22  | E5       | PB02 | 34   | VDDANA | ADCIFE<br>AD3  | USART1<br>RTS   | ABDACB<br>DAC0  | IISC            | ACIFC<br>ACBN0    |                | CATB<br>SENSE23 |

| 23  | C4       | 23  | C4       | PB03 | 35   | VDDANA | ADCIFE<br>AD4  | USART1<br>CLK   | ABDACB<br>DACN0 | IISC<br>ISDI    | ACIFC<br>ACBP0    |                | CATB<br>DIS     |

| 28  | C1       | 28  | C1       | PB04 | 36   | VDDANA | ADCIFE<br>AD5  | USART1<br>RXD   | ABDACB<br>DAC1  | IISC<br>ISDO    | DACC<br>EXT TRIG0 |                | CATB<br>SENSE24 |

| 29  | B1       | 29  | B1       | PB05 | 37   | VDDANA | ADCIFE<br>AD6  | USART1<br>TXD   | ABDACB<br>DACN1 | IISC<br>IMCK    |                   |                | CATB<br>SENSE25 |

| 45  | G3       | 45  | G3       | PB06 | 38   | LCDA   | USART3<br>RTS  |                 | GLOC<br>IN4     | IISC            |                   | LCDCA<br>SEG22 | CATB<br>SENSE26 |

| 46  | H1       | 46  | H1       | PB07 | 39   | LCDA   | USART3<br>CTS  |                 | GLOC<br>IN5     | TC0<br>A0       |                   | LCDCA<br>SEG21 | CATB<br>SENSE27 |

Table 3-1.

100-pin GPIO Controller Function Multiplexing (Sheet 3 of 4)

|     | ATSAM4LC   |     | ATSAM4LS   | Pin  | GPIO | Supply |                | <b>3</b> (2-2-2- | GI               | PIO Functio  | ns               |                |                 |

|-----|------------|-----|------------|------|------|--------|----------------|------------------|------------------|--------------|------------------|----------------|-----------------|

| QFN | VFBGA      | QFN | VFBGA      |      |      |        | Α              | В                | С                | D            | E                | F              | G               |

| 72  | G6         | 72  | G6         | PB08 | 40   | LCDA   | USART3<br>CLK  |                  | GLOC<br>IN6      | TC0<br>B0    |                  | LCDCA<br>SEG14 | CATB<br>SENSE28 |

| 73  | G7         | 73  | <b>G</b> 7 | PB09 | 41   | LCDA   | USART3<br>RXD  | PEVC<br>PAD EVT2 | GLOC<br>IN7      | TC0<br>A1    |                  | LCDCA<br>SEG15 | CATB<br>SENSE29 |

| 74  | G8         | 74  | G8         | PB10 | 42   | LCDA   | USART3<br>TXD  | PEVC<br>PAD EVT3 | GLOC<br>OUT1     | TC0<br>B1    | SCIF<br>GCLK0    | LCDCA<br>SEG16 | CATB<br>SENSE30 |

| 75  | K9         | 75  | К9         | PB11 | 43   | LCDA   | USART0<br>CTS  | SPI<br>NPCS2     |                  | TC0<br>A2    | SCIF<br>GCLK1    | LCDCA<br>SEG17 | CATB<br>SENSE31 |

| 89  | E7         | 89  | E7         | PB12 | 44   | LCDC   | USART0<br>RTS  | SPI<br>NPCS3     | PEVC<br>PAD EVT0 | TC0<br>B2    | SCIF<br>GCLK2    | LCDCA<br>SEG32 | CATB<br>DIS     |

| 90  | E8         | 90  | E8         | PB13 | 45   | LCDC   | USART0<br>CLK  | SPI<br>NPCS1     | PEVC<br>PAD EVT1 | TC0<br>CLK0  | SCIF<br>GCLK3    | LCDCA<br>SEG33 | CATB<br>SENSE0  |

| 93  | D7         | 93  | D7         | PB14 | 46   | LCDC   | USART0<br>RXD  | SPI<br>MISO      | TWIM3<br>TWD     | TC0<br>CLK1  | SCIF<br>GCLK IN0 | LCDCA<br>SEG36 | CATB<br>SENSE1  |

| 94  | D8         | 94  | D8         | PB15 | 47   | LCDC   | USART0<br>TXD  | SPI<br>MOSI      | TWCK             | TC0<br>CLK2  | SCIF<br>GCLK IN1 | LCDCA<br>SEG37 | CATB<br>SENSE2  |

| 1   | A10        | 1   | A10        | PC00 | 64   | VDDIO  | SPI<br>NPCS2   | USART0<br>CLK    |                  | TC1<br>A0    |                  |                | CATB<br>SENSE3  |

| 2   | C8         | 2   | C8         | PC01 | 65   | VDDIO  | SPI<br>NPCS3   | USART0<br>RTS    |                  | TC1<br>B0    |                  |                | CATB<br>SENSE4  |

| 3   | <b>C</b> 7 | 3   | <b>C</b> 7 | PC02 | 66   | VDDIO  | SPI<br>NPCS1   | USART0<br>CTS    | USART0<br>RXD    | TC1<br>A1    |                  |                | CATB<br>SENSE5  |

| 4   | В7         | 4   | В7         | PC03 | 67   | VDDIO  | SPI<br>NPCS0   | EIC<br>EXTINT5   | USART0<br>TXD    | TC1<br>B1    |                  |                | CATB<br>SENSE6  |

| 9   | C5         | 9   | C5         | PC04 | 68   | VDDIO  | SPI<br>MISO    | EIC<br>EXTINT6   |                  | TC1<br>A2    |                  |                | CATB<br>SENSE7  |

| 10  | C6         | 10  | C6         | PC05 | 69   | VDDIO  | SPI<br>MOSI    | EIC<br>EXTINT7   |                  | TC1<br>B2    |                  |                | CATB<br>DIS     |

| 11  | В6         | 11  | В6         | PC06 | 70   | VDDIO  | SPI<br>SCK     | EIC<br>EXTINT8   |                  | TC1<br>CLK0  |                  |                | CATB<br>SENSE8  |

| 36  | F2         | 36  | F2         | PC07 | 71   | VDDANA | ADCIFE<br>AD7  | USART2<br>RTS    | PEVC<br>PAD EVT0 | TC1<br>CLK1  |                  |                | CATB<br>SENSE9  |

| 37  | E3         | 37  | E3         | PC08 | 72   | VDDANA | ADCIFE<br>AD8  | USART2<br>CLK    | PEVC<br>PAD EVT1 | TC1<br>CLK2  | USART2<br>CTS    |                | CATB<br>SENSE10 |

| 38  | F1         | 38  | F1         | PC09 | 73   | VDDANA | ADCIFE<br>AD9  | USART3<br>RXD    | ABDACB<br>DAC0   | IISC<br>ISCK | ACIFC<br>ACAN1   |                | CATB<br>SENSE11 |

| 39  | D4         | 39  | D4         | PC10 | 74   | VDDANA | ADCIFE<br>AD10 | USART3<br>TXD    | ABDACB<br>DACN0  | IISC<br>ISDI | ACIFC<br>ACAP1   |                | CATB<br>SENSE12 |

| 40  | E4         | 40  | E4         | PC11 | 75   | VDDANA | ADCIFE<br>AD11 | USART2<br>RXD    | PEVC<br>PAD EVT2 |              |                  |                | CATB<br>SENSE13 |

| 41  | F3         | 41  | F3         | PC12 | 76   | VDDANA | ADCIFE<br>AD12 | USART2<br>TXD    | ABDACB<br>CLK    | IISC<br>IWS  |                  |                | CATB<br>SENSE14 |

| 42  | F4         | 42  | F4         | PC13 | 77   | VDDANA | ADCIFE<br>AD13 | USART3<br>RTS    | ABDACB<br>DAC1   | IISC<br>ISDO | ACIFC<br>ACBN1   |                | CATB<br>SENSE15 |

| 43  | G1         | 43  | G1         | PC14 | 78   | VDDANA | ADCIFE<br>AD14 | USART3<br>CLK    | ABDACB<br>DACN1  | IISC<br>IMCK | ACIFC<br>ACBP1   |                | CATB<br>DIS     |

| 58  | J5         | 58  | J5         | PC15 | 79   | LCDA   | TC1<br>A0      |                  |                  | GLOC<br>IN4  |                  | LCDCA<br>SEG0  | CATB<br>SENSE16 |

Table 3-1.

100-pin GPIO Controller Function Multiplexing (Sheet 4 of 4)

|     | O        |     | <u> </u> |      |      |        | - manapioza   | <u> </u>       | ,                |                 |                  |                | 1               |

|-----|----------|-----|----------|------|------|--------|---------------|----------------|------------------|-----------------|------------------|----------------|-----------------|

|     | ATSAM4LC |     | ATSAM4LS | Pin  | GPIO | Supply |               |                | G                | PIO Functio     | ns               |                |                 |

| QFN | VFBGA    | QFN | VFBGA    |      |      |        | Α             | В              | С                | D               | E                | F              | G               |

| 59  | J6       | 59  | J6       | PC16 | 80   | LCDA   | TC1<br>B0     |                |                  | GLOC<br>IN5     |                  | LCDCA<br>SEG1  | CATB<br>SENSE17 |

| 60  | H4       | 60  | H4       | PC17 | 81   | LCDA   | TC1<br>A1     |                |                  | GLOC<br>IN6     |                  | LCDCA<br>SEG2  | CATB<br>SENSE18 |

| 61  | K6       | 61  | K6       | PC18 | 82   | LCDA   | TC1<br>B1     |                |                  | GLOC<br>IN7     |                  | LCDCA<br>SEG3  | CATB<br>SENSE19 |

| 62  | G4       | 62  | G4       | PC19 | 83   | LCDA   | TC1<br>A2     |                |                  | GLOC<br>OUT1    |                  | LCDCA<br>SEG4  | CATB<br>SENSE20 |

| 68  | Н7       | 68  | H7       | PC20 | 84   | LCDA   | TC1<br>B2     |                |                  |                 |                  | LCDCA<br>SEG10 | CATB<br>SENSE21 |

| 69  | K8       | 69  | K8       | PC21 | 85   | LCDA   | TC1<br>CLK0   |                |                  | PARC<br>PCCK    |                  | LCDCA<br>SEG11 | CATB<br>SENSE22 |

| 70  | J8       | 70  | J8       | PC22 | 86   | LCDA   | TC1<br>CLK1   |                |                  | PARC<br>PCEN1   |                  | LCDCA<br>SEG12 | CATB<br>SENSE23 |

| 71  | Н8       | 71  | Н8       | PC23 | 87   | LCDA   | TC1<br>CLK2   |                |                  | PARC<br>PCEN2   |                  | LCDCA<br>SEG13 | CATB<br>DIS     |

| 79  | J9       | 79  | J9       | PC24 | 88   | LCDB   | USART1<br>RTS | EIC<br>EXTINT1 | PEVC<br>PAD EVT0 | PARC<br>PCDATA0 |                  | LCDCA<br>SEG24 | CATB<br>SENSE24 |

| 80  | Н9       | 80  | Н9       | PC25 | 89   | LCDB   | USART1<br>CLK | EIC<br>EXTINT2 | PEVC<br>PAD EVT1 | PARC<br>PCDATA1 |                  | LCDCA<br>SEG25 | CATB<br>SENSE25 |

| 81  | G9       | 81  | G9       | PC26 | 90   | LCDB   | USART1<br>RXD | EIC<br>EXTINT3 | PEVC<br>PAD EVT2 | PARC<br>PCDATA2 | SCIF<br>GCLK0    | LCDCA<br>SEG26 | CATB<br>SENSE26 |

| 82  | F6       | 82  | F6       | PC27 | 91   | LCDB   | USART1<br>TXD | EIC<br>EXTINT4 | PEVC<br>PAD EVT3 | PARC<br>PCDATA3 | SCIF<br>GCLK1    | LCDCA<br>SEG27 | CATB<br>SENSE27 |

| 83  | G10      | 83  | G10      | PC28 | 92   | LCDB   | USART3<br>RXD | SPI<br>MISO    | GLOC<br>IN4      | PARC<br>PCDATA4 | SCIF<br>GCLK2    | LCDCA<br>SEG28 | CATB<br>SENSE28 |

| 84  | F7       | 84  | F7       | PC29 | 93   | LCDB   | USART3<br>TXD | SPI<br>MOSI    | GLOC<br>IN5      | PARC<br>PCDATA5 | SCIF<br>GCLK3    | LCDCA<br>SEG29 | CATB<br>SENSE29 |

| 85  | F8       | 85  | F8       | PC30 | 94   | LCDB   | USART3<br>RTS | SPI<br>SCK     | GLOC<br>IN6      | PARC<br>PCDATA6 | SCIF<br>GCLK IN0 | LCDCA<br>SEG30 | CATB<br>SENSE30 |

| 86  | F9       | 86  | F9       | PC31 | 95   | LCDB   | USART3<br>CLK | SPI<br>NPCS0   | GLOC<br>OUT1     | PARC<br>PCDATA7 | SCIF<br>GCLK IN1 | LCDCA<br>SEG31 | CATB<br>SENSE31 |

**Table 3-2.** 64-pin GPIO Controller Function Multiplexing (Sheet 1 of 3)

| ATSAM4LC | ATSAM4LS | Pin  | GPIO | Supply |               |              | G | SPIO Functio | ns |   |             |

|----------|----------|------|------|--------|---------------|--------------|---|--------------|----|---|-------------|

| QFP      | QFP      |      |      | ဟ      |               |              |   |              |    |   |             |

| QFN      | QFN      |      |      |        | Α             | В            | С | D            | E  | F | G           |

| 1        | 1        | PA00 | 0    | VDDIO  |               |              |   |              |    |   |             |

| 2        | 2        | PA01 | 1    | VDDIO  |               |              |   |              |    |   |             |

| 3        | 3        | PA02 | 2    | VDDIN  | SCIF<br>GCLK0 | SPI<br>NPCS0 |   |              |    |   | CATB<br>DIS |

| 10       | 10       | PA03 | 3    | VDDIN  |               | SPI<br>MISO  |   |              |    |   |             |

Table 3-2.

64-pin GPIO Controller Function Multiplexing (Sheet 2 of 3)

| ATSAM4LC   | ATSAM4LS   | Pin  | GPIO | Supply |               | ·               | G. G. G. G.      | PIO Function    | ns                |                |                 |

|------------|------------|------|------|--------|---------------|-----------------|------------------|-----------------|-------------------|----------------|-----------------|

|            | 1          | Δ.   | 5    | Sul    |               |                 | <u> </u>         | runcuo          |                   |                |                 |

| QFP<br>QFN | QFP<br>QFN |      |      |        | Α             | В               | С                | D               | E                 | F              | G               |

| 15         | 15         | PA04 | 4    | VDDANA | ADCIFE<br>AD0 | USART0<br>CLK   | EIC<br>EXTINT2   | GLOC<br>IN1     |                   |                | CATB<br>SENSE0  |

| 16         | 16         | PA05 | 5    | VDDANA | ADCIFE<br>AD1 | USART0<br>RXD   | EIC<br>EXTINT3   | GLOC<br>IN2     | ADCIFE<br>TRIGGER |                | CATB<br>SENSE1  |

| 21         | 21         | PA06 | 6    | VDDANA | DACC<br>VOUT  | USART0<br>RTS   | EIC<br>EXTINT1   | GLOC<br>IN0     | ACIFC<br>ACAN0    |                | CATB<br>SENSE2  |

| 22         | 22         | PA07 | 7    | VDDANA | ADCIFE<br>AD2 | USART0<br>TXD   | EIC<br>EXTINT4   | GLOC<br>IN3     | ACIFC<br>ACAP0    |                | CATB<br>SENSE3  |

| 26         | 26         | PA08 | 8    | LCDA   | USART0<br>RTS | TC0<br>A0       | PEVC<br>PAD EVT0 | GLOC<br>OUT0    |                   | LCDCA<br>SEG23 | CATB<br>SENSE4  |

| 29         | 29         | PA09 | 9    | LCDA   | USART0<br>CTS | TC0<br>B0       | PEVC<br>PAD EVT1 | PARC<br>PCDATA0 |                   | COM3           | CATB<br>SENSE5  |

| 30         | 30         | PA10 | 10   | LCDA   | USART0<br>CLK | TC0<br>A1       | PEVC<br>PAD EVT2 | PARC<br>PCDATA1 |                   | LCDCA<br>COM2  | CATB<br>SENSE6  |

| 31         | 31         | PA11 | 11   | LCDA   | USART0<br>RXD | TC0<br>B1       | PEVC<br>PAD EVT3 | PARC<br>PCDATA2 |                   | LCDCA<br>COM1  | CATB<br>SENSE7  |

| 32         | 32         | PA12 | 12   | LCDA   | USART0<br>TXD | TC0<br>A2       |                  | PARC<br>PCDATA3 |                   | LCDCA<br>COM0  | CATB<br>DIS     |

| 40         | 40         | PA13 | 13   | LCDA   | USART1<br>RTS | TC0<br>B2       | SPI<br>NPCS1     | PARC<br>PCDATA4 |                   | LCDCA<br>SEG5  | CATB<br>SENSE8  |

| 41         | 41         | PA14 | 14   | LCDA   | USART1<br>CLK | TC0<br>CLK0     | SPI<br>NPCS2     | PARC<br>PCDATA5 |                   | LCDCA<br>SEG6  | CATB<br>SENSE9  |

| 42         | 42         | PA15 | 15   | LCDA   | USART1<br>RXD | TC0<br>CLK1     | SPI<br>NPCS3     | PARC<br>PCDATA6 |                   | LCDCA<br>SEG7  | CATB<br>SENSE10 |

| 43         | 43         | PA16 | 16   | LCDA   | USART1<br>TXD | TC0<br>CLK2     | EIC<br>EXTINT1   | PARC<br>PCDATA7 |                   | LCDCA<br>SEG8  | CATB<br>SENSE11 |

| 44         | 44         | PA17 | 17   | LCDA   | USART2<br>RTS | ABDACB<br>DAC0  | EIC<br>EXTINT2   | PARC<br>PCCK    |                   | LCDCA<br>SEG9  | CATB<br>SENSE12 |

| 49         | 49         | PA18 | 18   | LCDA   | USART2<br>CLK | ABDACB<br>DACN0 | EIC<br>EXTINT3   | PARC<br>PCEN1   |                   | LCDCA<br>SEG18 | CATB<br>SENSE13 |

| 50         | 50         | PA19 | 19   | LCDA   | USART2<br>RXD | ABDACB<br>DAC1  | EIC<br>EXTINT4   | PARC<br>PCEN2   | SCIF<br>GCLK0     | LCDCA<br>SEG19 | CATB<br>SENSE14 |

| 51         | 51         | PA20 | 20   | LCDA   | USART2<br>TXD | ABDACB<br>DACN1 | EIC<br>EXTINT5   | GLOC<br>IN0     | SCIF<br>GCLK1     | LCDCA<br>SEG20 | CATB<br>SENSE15 |

| 55         | 55         | PA21 | 21   | LCDC   | SPI<br>MISO   | USART1<br>CTS   | EIC<br>EXTINT6   | GLOC<br>IN1     | TWIM2<br>TWD      | LCDCA<br>SEG34 | CATB<br>SENSE16 |

| 56         | 56         | PA22 | 22   | LCDC   | SPI<br>MOSI   | USART2<br>CTS   | EIC<br>EXTINT7   | GLOC<br>IN2     | TWIM2<br>TWCK     | LCDCA<br>SEG35 | CATB<br>SENSE17 |

| 59         | 59         | PA23 | 23   | LCDC   | SPI<br>SCK    | TWIMS0<br>TWD   | EIC<br>EXTINT8   | GLOC<br>IN3     | SCIF<br>GCLK IN0  | LCDCA<br>SEG38 | CATB<br>DIS     |

| 60         | 60         | PA24 | 24   | LCDC   | SPI<br>NPCS0  | TWIMS0<br>TWCK  |                  | GLOC<br>OUT0    | SCIF<br>GCLK IN1  | LCDCA<br>SEG39 | CATB<br>SENSE18 |

| 62         | 62         | PA25 | 25   | VDDIO  | USBC<br>DM    | USART2<br>RXD   |                  |                 |                   |                | CATB<br>SENSE19 |

| 63         | 63         | PA26 | 26   | VDDIO  | USBC<br>DP    | USART2<br>TXD   |                  |                 |                   |                | CATB<br>SENSE20 |

Table 3-2.

64-pin GPIO Controller Function Multiplexing (Sheet 3 of 3)

| ATSAM4LC   | ATSAM4LS   | Pin  | GPIO | Supply |                |                  |                  | PIO Functio  | ns                |                |                 |

|------------|------------|------|------|--------|----------------|------------------|------------------|--------------|-------------------|----------------|-----------------|

| QFP<br>QFN | QFP<br>QFN |      |      | Š      | Α              | В                | С                | D            | E                 | F              | G               |

|            | 33         | PA27 | 27   | LCDA   | SPI<br>MISO    | IISC             | ABDACB<br>DAC0   | GLOC<br>IN4  | USART3<br>RTS     |                | CATB<br>SENSE0  |

|            | 34         | PA28 | 28   | LCDA   | SPI<br>MOSI    | IISC<br>ISDI     | ABDACB<br>DACN0  | GLOC<br>IN5  | USART3<br>CTS     |                | CATB<br>SENSE1  |

|            | 35         | PA29 | 29   | LCDA   | SPI<br>SCK     | IISC<br>IWS      | ABDACB<br>DAC1   | GLOC<br>IN6  | USART3<br>CLK     |                | CATB<br>SENSE2  |

|            | 38         | PA30 | 30   | LCDA   | SPI<br>NPCS0   | IISC<br>ISDO     | ABDACB<br>DACN1  | GLOC<br>IN7  | USART3<br>RXD     |                | CATB<br>SENSE3  |

|            | 39         | PA31 | 31   | LCDA   | SPI<br>NPCS1   | IISC<br>IMCK     | ABDACB<br>CLK    | GLOC<br>OUT1 | USART3<br>TXD     |                | CATB<br>DIS     |

| 11         | 11         | PB00 | 32   | VDDIN  | TWIMS1<br>TWD  | USART0<br>RXD    |                  |              |                   |                | CATB<br>SENSE21 |

| 12         | 12         | PB01 | 33   | VDDIN  | TWIMS1<br>TWCK | USART0<br>TXD    | EIC<br>EXTINT0   |              |                   |                | CATB<br>SENSE22 |

| 13         | 13         | PB02 | 34   | VDDANA | ADCIFE<br>AD3  | USART1<br>RTS    | ABDACB<br>DAC0   | IISC<br>ISCK | ACIFC<br>ACBN0    |                | CATB<br>SENSE23 |

| 14         | 14         | PB03 | 35   | VDDANA | ADCIFE<br>AD4  | USART1<br>CLK    | ABDACB<br>DACN0  | IISC<br>ISDI | ACIFC<br>ACBP0    |                | CATB<br>DIS     |

| 19         | 19         | PB04 | 36   | VDDANA | ADCIFE<br>AD5  | USART1<br>RXD    | ABDACB<br>DAC1   | IISC<br>ISDO | DACC<br>EXT TRIG0 |                | CATB<br>SENSE24 |

| 20         | 20         | PB05 | 37   | VDDANA | ADCIFE<br>AD6  | USART1<br>TXD    | ABDACB<br>DACN1  | IISC<br>IMCK |                   |                | CATB<br>SENSE25 |

| 27         | 27         | PB06 | 38   | LCDA   | USART3<br>RTS  |                  | GLOC<br>IN4      | IISC<br>IWS  |                   | LCDCA<br>SEG22 | CATB<br>SENSE26 |

| 28         | 28         | PB07 | 39   | LCDA   | USART3<br>CTS  |                  | GLOC<br>IN5      | TC0<br>A0    |                   | LCDCA<br>SEG21 | CATB<br>SENSE27 |

| 45         | 45         | PB08 | 40   | LCDA   | USART3<br>CLK  |                  | GLOC<br>IN6      | TC0<br>B0    |                   | LCDCA<br>SEG14 | CATB<br>SENSE28 |

| 46         | 46         | PB09 | 41   | LCDA   | USART3<br>RXD  | PEVC<br>PAD EVT2 | GLOC<br>IN7      | TC0<br>A1    |                   | LCDCA<br>SEG15 | CATB<br>SENSE29 |

| 47         | 47         | PB10 | 42   | LCDA   | USART3<br>TXD  | PEVC<br>PAD EVT3 | GLOC<br>OUT1     | TC0<br>B1    | SCIF<br>GCLK0     | LCDCA<br>SEG16 | CATB<br>SENSE30 |

| 48         | 48         | PB11 | 43   | LCDA   | USART0<br>CTS  | SPI<br>NPCS2     |                  | TC0<br>A2    | SCIF<br>GCLK1     | LCDCA<br>SEG17 | CATB<br>SENSE31 |

| 53         | 53         | PB12 | 44   | LCDC   | USART0<br>RTS  | SPI<br>NPCS3     | PEVC<br>PAD EVT0 | TC0<br>B2    | SCIF<br>GCLK2     | LCDCA<br>SEG32 | CATB<br>DIS     |

| 54         | 54         | PB13 | 45   | LCDC   | USART0<br>CLK  | SPI<br>NPCS1     | PEVC<br>PAD EVT1 | TC0<br>CLK0  | SCIF<br>GCLK3     | LCDCA<br>SEG33 | CATB<br>SENSE0  |

| 57         | 57         | PB14 | 46   | LCDC   | USART0<br>RXD  | SPI<br>MISO      | TWIM3<br>TWD     | TC0<br>CLK1  | SCIF<br>GCLK IN0  | LCDCA<br>SEG36 | CATB<br>SENSE1  |

| 58         | 58         | PB15 | 47   | LCDC   | USART0<br>TXD  | SPI<br>MOSI      | TWIM3<br>TWCK    | TC0<br>CLK2  | SCIF<br>GCLK IN1  | LCDCA<br>SEG37 | CATB<br>SENSE2  |

Table 3-3.

64-pin GPIO Controller Function Multiplexing for WLCSP package (Sheet 1 of 3)

| ATSAM4LC   | ATSAM4LS   | Pin  | GPIO | Supply |               | ·               |                  | PIO Function    | ns                | ·              |                 |

|------------|------------|------|------|--------|---------------|-----------------|------------------|-----------------|-------------------|----------------|-----------------|

|            | WLCSP      |      |      |        | Α             | В               | С                | D               | E                 | F              | G               |

| G4         | G4         | PA00 | 0    | VDDIO  |               |                 |                  |                 |                   |                |                 |

| G5         | G5         | PA01 | 1    | VDDIO  |               |                 |                  |                 |                   |                |                 |

| F3         | F3         | PA02 | 2    | VDDIN  | SCIF<br>GCLK0 | SPI<br>NPCS0    |                  |                 |                   |                | CATB<br>DIS     |

| E2         | E2         | PA03 | 3    | VDDIN  |               | SPI<br>MISO     |                  |                 |                   |                |                 |

| D3         | D3         | PA04 | 4    | VDDANA | ADCIFE<br>AD0 | USART0<br>CLK   | EIC<br>EXTINT2   | GLOC<br>IN1     |                   |                | CATB<br>SENSE0  |

| С3         | C3         | PA05 | 5    | VDDANA | ADCIFE<br>AD1 | USART0<br>RXD   | EIC<br>EXTINT3   | GLOC<br>IN2     | ADCIFE<br>TRIGGER |                | CATB<br>SENSE1  |

| C4         | C4         | PA06 | 6    | VDDANA | DACC<br>VOUT  | USART0<br>RTS   | EIC<br>EXTINT1   | GLOC<br>IN0     | ACIFC<br>ACAN0    |                | CATB<br>SENSE2  |

| C5         | C5         | PA07 | 7    | VDDANA | ADCIFE<br>AD2 | USART0<br>TXD   | EIC<br>EXTINT4   | GLOC<br>IN3     | ACIFC<br>ACAP0    |                | CATB<br>SENSE3  |

| В4         | B4         | PA08 | 8    | LCDA   | USART0<br>RTS | TC0<br>A0       | PEVC<br>PAD EVT0 | GLOC<br>OUT0    |                   | LCDCA<br>SEG23 | CATB<br>SENSE4  |

| A5         | A5         | PA09 | 9    | LCDA   | USART0<br>CTS | TC0<br>B0       | PEVC<br>PAD EVT1 | PARC<br>PCDATA0 |                   | LCDCA<br>COM3  | CATB<br>SENSE5  |

| В6         | В6         | PA10 | 10   | LCDA   | USART0<br>CLK | TC0<br>A1       | PEVC<br>PAD EVT2 | PARC<br>PCDATA1 |                   | LCDCA<br>COM2  | CATB<br>SENSE6  |

| В7         | B7         | PA11 | 11   | LCDA   | USART0<br>RXD | TC0<br>B1       | PEVC<br>PAD EVT3 | PARC<br>PCDATA2 |                   | LCDCA<br>COM1  | CATB<br>SENSE7  |

| A8         | A8         | PA12 | 12   | LCDA   | USART0<br>TXD | TC0<br>A2       |                  | PARC<br>PCDATA3 |                   | LCDCA<br>COM0  | CATB<br>DIS     |

| <b>C</b> 7 | <b>C</b> 7 | PA13 | 13   | LCDA   | USART1<br>RTS | TC0<br>B2       | SPI<br>NPCS1     | PARC<br>PCDATA4 |                   | LCDCA<br>SEG5  | CATB<br>SENSE8  |

| D7         | D7         | PA14 | 14   | LCDA   | USART1<br>CLK | TC0<br>CLK0     | SPI<br>NPCS2     | PARC<br>PCDATA5 |                   | LCDCA<br>SEG6  | CATB<br>SENSE9  |

| <b>E</b> 7 | E7         | PA15 | 15   | LCDA   | USART1<br>RXD | TC0<br>CLK1     | SPI<br>NPCS3     | PARC<br>PCDATA6 |                   | LCDCA<br>SEG7  | CATB<br>SENSE10 |

| F7         | F7         | PA16 | 16   | LCDA   | USART1<br>TXD | TC0<br>CLK2     | EIC<br>EXTINT1   | PARC<br>PCDATA7 |                   | LCDCA<br>SEG8  | CATB<br>SENSE11 |

| G8         | G8         | PA17 | 17   | LCDA   | USART2<br>RTS | ABDACB<br>DAC0  | EIC<br>EXTINT2   | PARC<br>PCCK    |                   | LCDCA<br>SEG9  | CATB<br>SENSE12 |

| G7         | <b>G</b> 7 | PA18 | 18   | LCDA   | USART2<br>CLK | ABDACB<br>DACN0 | EIC<br>EXTINT3   | PARC<br>PCEN1   |                   | LCDCA<br>SEG18 | CATB<br>SENSE13 |

| G6         | G6         | PA19 | 19   | LCDA   | USART2<br>RXD | ABDACB<br>DAC1  | EIC<br>EXTINT4   | PARC<br>PCEN2   | SCIF<br>GCLK0     | LCDCA<br>SEG19 | CATB<br>SENSE14 |

| Н7         | H7         | PA20 | 20   | LCDA   | USART2<br>TXD | ABDACB<br>DACN1 | EIC<br>EXTINT5   | GLOC<br>IN0     | SCIF<br>GCLK1     | LCDCA<br>SEG20 | CATB<br>SENSE15 |

| H5         | Н5         | PA21 | 21   | LCDC   | SPI<br>MISO   | USART1<br>CTS   | EIC<br>EXTINT6   | GLOC<br>IN1     | TWIM2<br>TWD      | LCDCA<br>SEG34 | CATB<br>SENSE16 |

| F5         | F5         | PA22 | 22   | LCDC   | SPI<br>MOSI   | USART2<br>CTS   | EIC<br>EXTINT7   | GLOC<br>IN2     | TWIM2<br>TWCK     | LCDCA<br>SEG35 | CATB<br>SENSE17 |

Table 3-3.

64-pin GPIO Controller Function Multiplexing for WLCSP package (Sheet 2 of 3)

| ATSAM4LC | ATSAM4LS   | Pin   | GPIO | Supply |               | ·                |                 | PIO Functio  | ns                | ·              |                 |

|----------|------------|-------|------|--------|---------------|------------------|-----------------|--------------|-------------------|----------------|-----------------|

| WLCSP    | ,          |       |      | "      | Α             | В                | С               | D            | E                 | F              | G               |

|          |            |       |      |        | SPI           | TWIMS0           | EIC             | GLOC         | SCIF              | LCDCA          | CATB            |

| Н3       | Н3         | PA23  | 23   | LCDC   | SCK           | TWD              | EXTINT8         | IN3          | GCLK IN0          | SEG38          | DIS             |

| G3       | G3         | PA24  | 24   | LCDC   | SPI<br>NPCS0  | TWIMS0<br>TWCK   |                 | GLOC<br>OUT0 | SCIF<br>GCLK IN1  | LCDCA<br>SEG39 | CATB<br>SENSE18 |

| 63       | GS         | PA24  | 24   | LCDC   | USBC          | USART2           |                 | 0010         | GCLK INT          | 35039          | CATB            |

| H2       | H2         | PA25  | 25   | VDDIO  | DM            | RXD              |                 |              |                   |                | SENSE19         |

|          |            |       |      |        | USBC          | USART2           |                 |              |                   |                | CATB            |

| G2       | G2         | PA26  | 26   | VDDIO  | DP            | TXD              |                 |              |                   |                | SENSE20         |

|          | <b>A</b> 7 | PA27  | 27   | LCDA   | SPI<br>MISO   | IISC<br>ISCK     | ABDACB<br>DAC0  | GLOC<br>IN4  | USART3<br>RTS     |                | CATB<br>SENSE0  |

|          | A6         | PA28  | 28   | LCDA   | SPI<br>Mosi   | IISC<br>ISDI     | ABDACB<br>DACN0 | GLOC<br>IN5  | USART3<br>CTS     |                | CATB<br>SENSE1  |

|          | В8         | PA29  | 29   | LCDA   | SPI<br>SCK    | IISC<br>IWS      | ABDACB<br>DAC1  | GLOC<br>IN6  | USART3<br>CLK     |                | CATB<br>SENSE2  |

|          | E8         | PA30  | 30   | LCDA   | SPI<br>NPCS0  | IISC<br>ISDO     | ABDACB<br>DACN1 | GLOC<br>IN7  | USART3<br>RXD     |                | CATB<br>SENSE3  |

|          | F8         | PA31  | 31   | LCDA   | SPI<br>NPCS1  | IISC<br>IMCK     | ABDACB<br>CLK   | GLOC<br>OUT1 | USART3<br>TXD     |                | CATB<br>DIS     |

| D2       | D2         | PB00  | 32   | VDDIN  | TWIMS1<br>TWD | USART0<br>RXD    |                 |              |                   |                | CATB<br>SENSE21 |

|          | - DE       | 1 500 | -    | VDDIIV | TWIMS1        | USART0           | EIC             |              |                   |                | CATB            |

| C2       | C2         | PB01  | 33   | VDDIN  | TWCK          | TXD              | EXTINT0         |              |                   |                | SENSE22         |

| E3       | E3         | PB02  | 34   | VDDANA | ADCIFE<br>AD3 | USART1<br>RTS    | ABDACB<br>DAC0  | IISC<br>ISCK | ACIFC<br>ACBN0    |                | CATB<br>SENSE23 |

| B1       | B1         | PB03  | 35   | VDDANA | ADCIFE<br>AD4 | USART1<br>CLK    | ABDACB<br>DACN0 | IISC<br>ISDI | ACIFC<br>ACBP0    |                | CATB<br>DIS     |

| A1       | A1         | PB04  | 36   | VDDANA | ADCIFE<br>AD5 | USART1<br>RXD    | ABDACB<br>DAC1  | IISC<br>ISDO | DACC<br>EXT TRIG0 |                | CATB<br>SENSE24 |

| D4       | D4         | PB05  | 37   | VDDANA | ADCIFE<br>AD6 | USART1<br>TXD    | ABDACB<br>DACN1 | IISC         |                   |                | CATB<br>SENSE25 |

|          |            |       |      |        | USART3        |                  | GLOC            | IISC         |                   | LCDCA          | САТВ            |

| B5       | B5         | PB06  | 38   | LCDA   | RTS           |                  | IN4             | IWS          |                   | SEG22          | SENSE26         |

| C6       | C6         | PB07  | 39   | LCDA   | USART3<br>CTS |                  | GLOC<br>IN5     | TC0<br>A0    |                   | LCDCA<br>SEG21 | CATB<br>SENSE27 |

| D6       | D6         | PB08  | 40   | LCDA   | USART3<br>CLK |                  | GLOC<br>IN6     | TC0<br>B0    |                   | LCDCA<br>SEG14 | CATB<br>SENSE28 |

| E6       | E6         | PB09  | 41   | LCDA   | USART3<br>RXD | PEVC<br>PAD EVT2 | GLOC<br>IN7     | TC0<br>A1    |                   | LCDCA<br>SEG15 | CATB<br>SENSE29 |

| F6       | F6         | PB10  | 42   | LCDA   | USART3<br>TXD | PEVC<br>PAD EVT3 | GLOC<br>OUT1    | TC0<br>B1    | SCIF<br>GCLK0     | LCDCA<br>SEG16 | CATB<br>SENSE30 |

| Н8       | Н8         | PB11  | 43   | LCDA   | USART0<br>CTS | SPI<br>NPCS2     |                 | TC0          | SCIF<br>GCLK1     | LCDCA<br>SEG17 | CATB<br>SENSE31 |

|          |            |       |      | 2007   | USART0        | SPI              | PEVC            | TC0          | SCIF              | LCDCA          | CATB            |

| D5       | D5         | PB12  | 44   | LCDC   | RTS           | NPCS3            | PAD EVT0        | B2           | GCLK2             | SEG32          | DIS             |

Table 3-3.

64-pin GPIO Controller Function Multiplexing for WLCSP package (Sheet 3 of 3)

| ATSAM4LC | ATSAM4LS | Pin  | GPIO | Supply |               |              | GI               | PIO Functio | ns               |                |                |

|----------|----------|------|------|--------|---------------|--------------|------------------|-------------|------------------|----------------|----------------|

| WLCSP    | WLCSP    |      |      |        | Α             | В            | С                | D           | E                | F              | G              |

| E5       | E5       | PB13 | 45   | LCDC   | USART0<br>CLK | SPI<br>NPCS1 | PEVC<br>PAD EVT1 | TC0<br>CLK0 | SCIF<br>GCLK3    | LCDCA<br>SEG33 | CATB<br>SENSE0 |

| F4       | F4       | PB14 | 46   | LCDC   | USART0<br>RXD | SPI<br>MISO  | TWIM3<br>TWD     | TC0<br>CLK1 | SCIF<br>GCLK IN0 | LCDCA<br>SEG36 | CATB<br>SENSE1 |

| H4       | H4       | PB15 | 47   | LCDC   | USART0<br>TXD | SPI<br>MOSI  | TWIM3<br>TWCK    | TC0<br>CLK2 | SCIF<br>GCLK IN1 | LCDCA<br>SEG37 | CATB<br>SENSE2 |

Table 3-4.

48-pin GPIO Controller Function Multiplexing (Sheet 1 of 2)

| Part                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |          | e 3-4. | . 70         | PIII | C. 10 00  | TO Controller Function Multiplexing (Sheet 1 of 2) |        |         |              |         |          |         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------|--------------|------|-----------|----------------------------------------------------|--------|---------|--------------|---------|----------|---------|

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4LC      | 4LS    |              |      | <u>~</u>  |                                                    |        | G       | PIO Function | ns      |          |         |