### 31/2 Digit LCD, Low Power Display, A/D Converter with Overrange Recovery

The Intersil HT7136A is a high performance, low power  $3^{1}/_{2}$  digit, A/D converter. Included are seven segment decoders, display drivers, a reference, and a clock. The HT7136A is designed to interface with a liquid crystal display (LCD) and includes a multiplexed backplane drive.

The HT7136A brings together a combination of high accuracy, versatility, and true economy. It features auto-zero to less than  $10\mu V$ , zero drift of less than  $1\mu V/^{0}C$ , input bias current of 10pA (Max), and rollover error of less than one count. True differential inputs and reference are useful in all systems, but give the designer an uncommon advantage when measuring load cells, strain gauges and other bridge type transducers. Finally, the true economy of single power supply operation, enables a high performance panel meter to be built with the addition of only 10 passive components and a display.

The HT7136A is an improved version of the ICL7126, eliminating the overrange hangover and hysteresis effects, and should be used in its place in all applications. It can also be used as a plug-in replacement for the ICL7106 in a wide variety of applications, changing only the passive components.

#### Features

- First Reading Overrange Recovery in One Conversion Period

- Guaranteed Zero Reading for 0V Input on All Scales

- · True Polarity at Zero for Precise Null Detection

- 1pA Typical Input Current

- True Differential Input and Reference, Direct Display Drive

LCD HT7136A

- Low Noise Less Than 15μV<sub>P-P</sub>

- · On Chip Clock and Reference

- · No Additional Active Circuits Required

- · Low Power Less Than 1mW

- Surface Mount Package Available

- · Drop-In Replacement for ICL7126, No Changes Needed

- · Pb-Free Plus Anneal Available (RoHS Compliant)

### Ordering Information

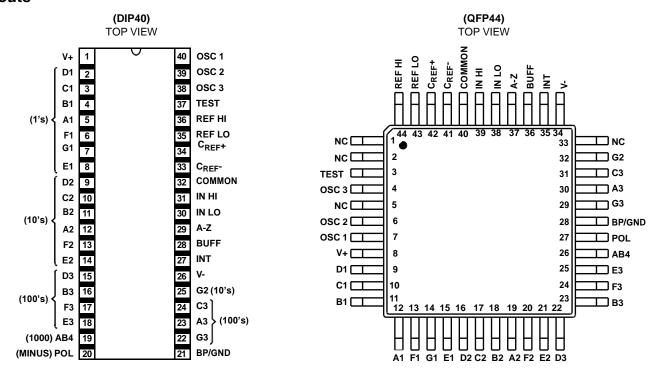

HT7136ANZ DIP40

HT7136ARQZ LQFP44(10\*10) HT7136ARSZ SSOP48

$T_A = -45^{\circ}$  to  $85^{\circ}$  C for all packages

### **Pinouts**

###

### **Operating Conditions**

| Tomporaturo | Dango |      | 0°C to 70°C     |

|-------------|-------|------|-----------------|

| remperature | Range | <br> | <br>0 0 10 70 0 |

### **Thermal Information**

| Thermal Resistance (Typical, Note 2)     | θ <sub>JA</sub> (°C/W) |

|------------------------------------------|------------------------|

| PDIP Package*                            | 50                     |

| MQFP Package                             |                        |

| Maximum Junction Temperature             | 150°C                  |

| Maximum Storage Temperature Range65      | 5°C to 150°C           |

| Maximum Lead Temperature (Soldering 10s) | 300°C                  |

| (MQFP - Lead Tips Only)                  |                        |

<sup>\*</sup>Pb-free PDIPs can be used for through hole wave solder processing only. They are not intended for use in Reflow solder processing applications.

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES:

- 1. Input voltages may exceed the supply voltages provided the input current is limited to ±100μA.

- 2.  $\theta_{JA}$  is measured with the component mounted on a low effective thermal conductivity test board in free air. See Tech Brief TB379 for details.

### Electrical Specifications (Note 3)

| PARAMETER                                                                   | TEST CONDITIONS                                                                                                          | MIN    | TYP          | MAX    | UNITS              |

|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------|--------------|--------|--------------------|

| SYSTEM PERFORMANCE                                                          |                                                                                                                          | Į.     | Į.           | Į.     | Į.                 |

| Zero Input Reading V <sub>IN</sub> = 0V, Full Scale = 200mV                 |                                                                                                                          | -000.0 | ±000.0       | +000.0 | Digital<br>Reading |

| Ratiometric Reading                                                         | $V_{IN} = V_{REF}, V_{REF} = 100 \text{mV}$                                                                              | 999    | 999/<br>1000 | 1000   | Digital<br>Reading |

| Rollover Error                                                              | -V <sub>IN</sub> = +V <sub>IN</sub> ≅ 200mV Difference in Reading for Equal Positive and Negative Inputs Near Full Scale | -      | ±0.2         | ±1     | Counts             |

| Linearity                                                                   | Full Scale = 200mV or Full Scale = 2V Maximum Deviation from Best Straight Line Fit (Note 5)                             | -      | ±0.2         | ±1     | Counts             |

| Common Mode Rejection Ratio                                                 | $V_{CM} = \pm 1V$ , $V_{IN} = 0V$ , Full Scale = 200mV (Note 5)                                                          | -      | 50           | -      | μV/V               |

| Noise                                                                       | V <sub>IN</sub> = 0V, Full Scale = 200mV (Peak-To-Peak Value Not Exceeded 95% of Time) (Note 5)                          |        | 15           | -      | μV                 |

| Leakage Current Input                                                       | V <sub>IN</sub> = 0V (Note 5)                                                                                            |        | 1            | 10     | pА                 |

| Zero Reading Drift                                                          | V <sub>IN</sub> = 0V, 0°C To 70°C (Note 5)                                                                               |        | 0.2          | 1      | μV/°C              |

| Scale Factor Temperature Coefficient                                        | V <sub>IN</sub> = 199mV, 0°C To 70°C, (Ext. Ref. 0ppm/x°C) (Note 5)                                                      |        | 1            | 5      | ppm/°C             |

| COMMON Pin Analog Common Voltage                                            | 25kΩ Between Common and Positive Supply (With Respect to + Supply)                                                       |        | 3.0          | 3.2    | V                  |

| Temperature Coefficient of Analog<br>Common                                 | 25kΩ Between Common and Positive Supply (With Respect to + Supply) (Note 5)                                              | -      | 150          | -      | ppm/°C             |

| SUPPLY CURRENT                                                              |                                                                                                                          | •      |              | •      |                    |

| V+ Supply Current                                                           | V <sub>IN</sub> = 0 (Does Not Include Common Current) 16kHz<br>Oscillator (Note 6)                                       | -      | 70           | 100    | μА                 |

| DISPLAY DRIVER                                                              | ,                                                                                                                        | ı      | II.          | ı      | L                  |

| Peak-To-Peak Segment Drive Voltage and Peak-To-Peak Backplane Drive Voltage | V+ to V- = 9V (Note 4)                                                                                                   | 4      | 5.5          | 6      | V                  |

#### NOTES:

- 3. Unless otherwise noted, specifications apply to the HT7136A at T<sub>A</sub> = 25°C, f<sub>CLOCK</sub> = 48kHz. HT7136A is tested in the circuit of Figure 1.

- 4. Back plane drive is in phase with segment drive for "off" segment, 180 degrees out of phase for "on" segment. Frequency is 20 times conversion rate. Average DC component is less than 50mV.

- 5. Not tested, guaranteed by design.

- 6. 48kHz oscillator increases current by 20μA (Typ).

# Typical Applications and Test Circuits

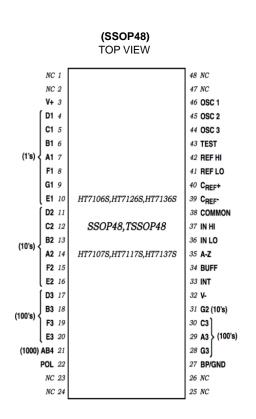

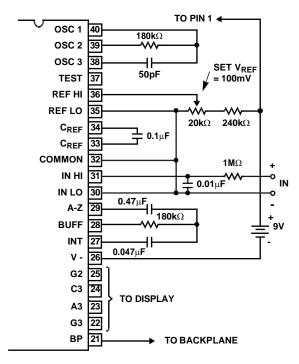

FIGURE 1. HT7136A TEST CIRCUIT AND TYPICAL APPLICATION WITH LCD DISPLAY COMPONENTS SELECTED FOR 200mV FULL SCALE

### Design Information Summary Sheet

### OSCILLATOR FREQUENCY

$f_{OSC} = 0.45/RC$   $C_{OSC} > 50pF$ ;  $R_{OSC} > 50k\Omega$  $f_{OSC}$  (Typ) = 48kHz

### OSCILLATOR PERIOD

$t_{OSC} = RC/0.45$

#### INTEGRATION CLOCK FREQUENCY

$f_{CLOCK} = f_{OSC}/4$

### • INTEGRATION PERIOD

$t_{INT} = 1000 \times (4/f_{OSC})$

#### 60/50Hz REJECTION CRITERION

$t_{INT}/t_{60Hz}$  or  $t_{INT}/t_{50Hz}$  = Integer

### • OPTIMUM INTEGRATION CURRENT

$I_{INT} = 1\mu A$

### • FULL SCALE ANALOG INPUT VOLTAGE

$V_{INFS}$  (Typ) = 200mV or 2V

### • INTEGRATE RESISTOR

$$R_{INT} = \frac{V_{INFS}}{I_{INT}}$$

### • INTEGRATE CAPACITOR

$$C_{INT} = - V_{INT} -$$

#### INTEGRATOR OUTPUT VOLTAGE SWING

$$V_{INT} = \frac{(t_{INT})(I_{INT})}{C_{INT}} -$$

### • VINT MAXIMUM SWING:

$$(V- + 0.5V) < V_{INT} < (V+ - 0.5V), V_{INT} (Typ) = 2V$$

### DISPLAY COUNT

$$COUNT = 1000 \times \frac{V_{IN}}{V_{REF}}$$

#### CONVERSION CYCLE

$$t_{CYC} = t_{CL0CK} \times 4000$$

$$t_{CYC} = t_{OSC} \times 16,000$$

when  $t_{OSC} = 48 \text{kHz}$ ;  $t_{CYC} = 333 \text{ms}$

### COMMON MODE INPUT VOLTAGE

$$(V- + 1V) < V_{IN} < (V+ - 0.5V)$$

### AUTO-ZERO CAPACITOR

$$0.01 \mu F < C_{AZ} < 1 \mu F$$

#### REFERENCE CAPACITOR

$$0.1 \mu F < C_{RFF} < 1 \mu F$$

### · V<sub>COM</sub>

Biased between V+ and V-.

#### V<sub>COM</sub> ≅ V+ - 2.8V

Regulation lost when V+ to V- <  $\cong$ 6.8V. If V<sub>COM</sub> is externally pulled down to (V + to V -)/2, the V<sub>COM</sub> circuit will turn off.

#### POWER SUPPLY: SINGLE 9V

V+ - V- = 9V

Digital supply is generated internally

$$V_{TEST} \cong V+ - 4.5V$$

DISPLAY: LCD

Type: Direct drive with digital logic supply amplitude.

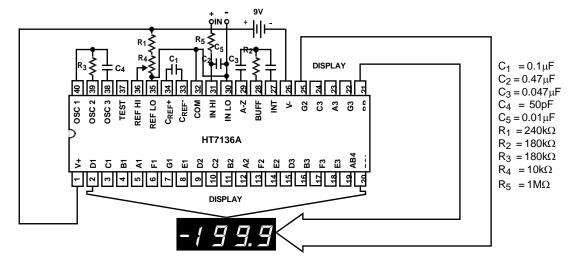

## Typical Integrator Amplifier Output Waveform (INT Pin)

TOTAL CONVERSION TIME = 4000 x tclock = 16,000 x tosc

### Pin Descriptions

| PIN NUMBER |          |                    |                   |                                                                                                                                                                   |  |  |

|------------|----------|--------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 44 PIN     |          | -                  |                   |                                                                                                                                                                   |  |  |

| 40 PIN DIP | FLATPACK | NAME               | FUNCTION          | DESCRIPTION                                                                                                                                                       |  |  |

| 1          | 8        | V+                 | Supply            | Power Supply.                                                                                                                                                     |  |  |

| 2          | 9        | D1                 | Output            | Driver Pin for Segment "D" of the display units digit.                                                                                                            |  |  |

| 3          | 10       | C1                 | Output            | Driver Pin for Segment "C" of the display units digit.                                                                                                            |  |  |

| 4          | 11       | B1                 | Output            | Driver Pin for Segment "B" of the display units digit.                                                                                                            |  |  |

| 5          | 12       | A1                 | Output            | Driver Pin for Segment "A" of the display units digit.                                                                                                            |  |  |

| 6          | 13       | F1                 | Output            | Driver Pin for Segment "F" of the display units digit.                                                                                                            |  |  |

| 7          | 14       | G1                 | Output            | Driver Pin for Segment "G" of the display units digit.                                                                                                            |  |  |

| 8          | 15       | E1                 | Output            | Driver Pin for Segment "E" of the display units digit.                                                                                                            |  |  |

| 9          | 16       | D2                 | Output            | Driver Pin for Segment "D" of the display tens digit.                                                                                                             |  |  |

| 10         | 17       | C2                 | Output            | Driver Pin for Segment "C" of the display tens digit.                                                                                                             |  |  |

| 11         | 18       | B2                 | Output            | Driver Pin for Segment "B" of the display tens digit.                                                                                                             |  |  |

| 12         | 19       | A2                 | Output            | Driver Pin for Segment "A" of the display tens digit.                                                                                                             |  |  |

| 13         | 20       | F2                 | Output            | Driver Pin for Segment "F" of the display tens digit.                                                                                                             |  |  |

| 14         | 21       | E2                 | Output            | Driver Pin for Segment "E" of the display tens digit.                                                                                                             |  |  |

| 15         | 22       | D3                 | Output            | Driver pin for segment "D" of the display hundreds digit.                                                                                                         |  |  |

| 16         | 23       | В3                 | Output            | Driver pin for segment "B" of the display hundreds digit.                                                                                                         |  |  |

| 17         | 24       | F3                 | Output            | Driver pin for segment "F" of the display hundreds digit.                                                                                                         |  |  |

| 18         | 25       | E3                 | Output            | Driver pin for segment "E" of the display hundreds digit.                                                                                                         |  |  |

| 19         | 26       | AB4                | Output            | Driver pin for both "A" and "B" segments of the display thousands digit.                                                                                          |  |  |

| 20         | 27       | POL                | Output            | Driver pin for the negative sign of the display.                                                                                                                  |  |  |

| 21         | 28       | BP/GND             | Output            | Driver pin for the LCD backplane/Power Supply Ground.                                                                                                             |  |  |

| 22         | 29       | G3                 | Output            | Driver pin for segment "G" of the display hundreds digit.                                                                                                         |  |  |

| 23         | 30       | А3                 | Output            | Driver pin for segment "A" of the display hundreds digit.                                                                                                         |  |  |

| 24         | 31       | C3                 | Output            | Driver pin for segment "C" of the display hundreds digit.                                                                                                         |  |  |

| 25         | 32       | G2                 | Output            | Driver pin for segment "G" of the display tens digit.                                                                                                             |  |  |

| 26         | 34       | V-                 | Supply            | Negative power supply.                                                                                                                                            |  |  |

| 27         | 35       | INT                | Output            | Integrator amplifier output. To be connected to integrating capacitor.                                                                                            |  |  |

| 28         | 36       | BUFF               | Output            | Input buffer amplifier output. To be connected to integrating resistor.                                                                                           |  |  |

| 29         | 37       | A-Z                | Input             | Integrator amplifier input. To be connected to auto-zero capacitor.                                                                                               |  |  |

| 30         | 38       | IN LO              | Input             | Differential inputs. To be connected to input voltage to be measured. LO and HI                                                                                   |  |  |

| 31         | 39       | IN HI              |                   | designators are for reference and do not imply that LO should be connected to lower potential, e.g., for negative inputs IN LO has a higher potential than IN HI. |  |  |

| 32         | 40       | COMMON             | Supply/<br>Output | Internal voltage reference output.                                                                                                                                |  |  |

| 33         | 41       | C <sub>REF</sub> - |                   | Connection pins for reference capacitor.                                                                                                                          |  |  |

| 34         | 42       | C <sub>REF</sub> + |                   |                                                                                                                                                                   |  |  |

| 35<br>36   | 43<br>44 | REF LO<br>REF HI   | Input             | Input pins for reference voltage to the device. REF HI should be positive reference t REF LO.                                                                     |  |  |

| 37         | 3        | TEST               | Input             | Display test. Turns on all segments when tied to V+.                                                                                                              |  |  |

| 38         | 4        | OSC3               | Output            | Device clock generator circuit connection pins.                                                                                                                   |  |  |

| 39         | 6        | OSC2               | Output            |                                                                                                                                                                   |  |  |

| 40         | 7        | OSC1               | Input             |                                                                                                                                                                   |  |  |

## **Detailed Description**

### **Analog Section**

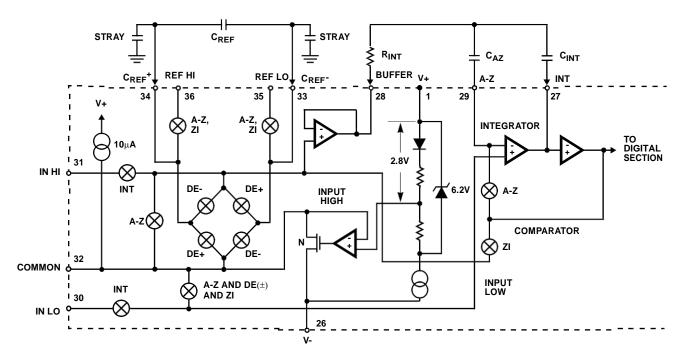

Figure 2 shows the Analog Section for the HT7136A. Each measurement cycle is divided into four phases. They are (1) auto-zero (A-Z), (2) signal integrate (INT) and (3) deintegrate (DE), (4) zero integrate (ZI).

### Auto-Zero Phase

During auto-zero three things happen. First, input high and low are disconnected from the pins and internally shorted to analog

COMMON. Second, the reference capacitor is charged to the reference voltage. Third, a feedback loop is closed around the system to charge the auto-zero capacitor  $C_{AZ}$  to compensate for offset voltages in the buffer amplifier, integrator, and comparator. Since the comparator is included in the loop, the A-Z accuracy is limited only by the noise of the system. In any case, the offset referred to the input is less than  $10\mu V$ .

### Signal Integrate Phase

During signal integrate, the auto-zero loop is opened, the internal short is removed, and the internal input high and low

are connected to the external pins. The converter then integrates the differential voltage between IN HI and IN LO for a fixed time. This differential voltage can be within a wide common mode range: up to 1V from either supply. If, on the other hand, the input signal has no return with respect to the converter power supply, IN LO can be tied to analog COMMON to establish the correct common mode voltage. At the end of this phase, the polarity of the integrated signal is determined.

### De-Integrate Phase

The final phase is de-integrate, or reference integrate. Input low is internally connected to analog COMMON and input high is connected across the previously charged reference capacitor. Circuitry within the chip ensures that the capacitor will be connected with the correct polarity to cause the integrator output to return to zero. The time required for the output to return to zero is proportional to the input signal. Specifically the digital reading displayed is:

DISPLAY READING =

$$1000 \left( \frac{V_{IN}}{V_{REF}} \right)$$

.

### Zero Integrator Phase

The final phase is zero integrator. First, input low is shorted to analog COMMON. Second, the reference capacitor is charged to the reference voltage. Finally, a feedback loop is closed around the system to IN HI to cause the integrator output to return to zero. Under normal conditions, this phase lasts for between 11 to 140 clock pulses, but after a "heavy" overrange conversion, it is extended to 740 clock pulses.

### Differential Input

The input can accept differential voltages anywhere within the common mode range of the input amplifier, or specifically from 0.5V below the positive supply to 1V above the negative supply. In this range, the system has a CMRR of 86dB typical. However, care must be exercised to assure the integrator output does not saturate. A worst case condition would be a large positive common mode voltage with a near full scale negative differential input voltage. The negative input signal drives the integrator positive when most of its swing has been used up by the positive common mode voltage. For these critical applications the integrator output swing can be reduced to less than the recommended 2V full scale swing with little loss of accuracy. The integrator output can swing to within 0.3V of either supply without loss of linearity.

#### Differential Reference

The reference voltage can be generated anywhere within the power supply voltage of the converter. The main source of common mode error is a roll-over voltage caused by the reference capacitor losing or gaining charge to stray capacity on its nodes. If there is a large common mode voltage, the reference capacitor can gain charge (increase voltage) when called up to de-integrate a positive signal but lose charge (decrease voltage) when called up to de-integrate a negative input signal. This difference in reference for positive or negative input voltage will give a roll-over error. However, by selecting the reference capacitor such that it is large enough in comparison to the stray capacitance, this error can be held to less than 0.5 count worst case. (See Component Value Selection.)

FIGURE 2. ANALOG SECTION OF HT7136A

### Analog COMMON

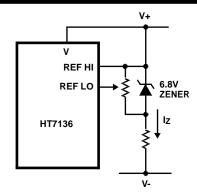

This pin is included primarily to set the common mode voltage for battery operation or for any system where the input signals are floating with respect to the power supply. The COMMON pin sets a voltage that is approximately 2.8V more negative than the positive supply. This is selected to give a minimum end-of-life battery voltage of about 6.8V. However, analog COMMON has some of the attributes of a reference voltage. When the total supply voltage is large enough to cause the zener to regulate (>7V), the COMMON voltage will have a low voltage coefficient (0.001%/V), low output impedance ( $\cong$ 15 $\Omega$ ), and a temperature coefficient typically less than 150ppm/ $^{O}$ C.

The limitations of the on chip reference should also be recognized, however. Due to their higher thermal resistance, plastic parts are poorer in this respect than ceramic. The combination of reference Temperature Coefficient (TC), internal chip dissipation, and package thermal resistance can increase noise near full scale from 25μV to 80μV<sub>P-P</sub>. Also the linearity in going from a high dissipation count such as 1000 (20 segments on) to a low dissipation count such as 1111 (8 segments on) can suffer by a count or more. Devices with a positive TC reference may require several counts to pull out of an over range condition. This is because over-range is a low dissipation mode, with the three least significant digits blanked. Similarly, units with a negative TC may cycle between over range and a non-over range count as the die alternately heats and cools. All these problems are of course eliminated if an external reference is used.

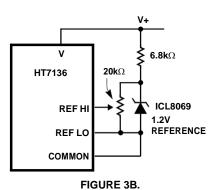

The HT7136A, with its negligible dissipation, suffers from none of these problems. In either case, an external reference can easily be added, as shown in Figure 3.

Analog COMMON is also used as the input low return during auto-zero and de-integrate. If IN LO is different from analog COMMON, a common mode voltage exists in the system and is taken care of by the excellent CMRR of the converter. However, in some applications IN LO will be set at a fixed known voltage (power supply common for instance). In this application, analog COMMON should be tied to the same point, thus removing the common mode voltage from the converter. The same holds true for the reference voltage. If reference can be conveniently tied to analog COMMON, it should be since this removes the common mode voltage from the reference system.

Within the IC, analog COMMON is tied to an N-Channel FET that can sink approximately 3mA of current to hold the voltage 2.8V below the positive supply (when a load is trying to pull the common line positive). However, there is only  $10\mu A$  of source current, so COMMON may easily be tied to a more negative voltage thus overriding the internal reference.

FIGURE 3A.

FIGURE 3. USING AN EXTERNAL REFERENCE

#### **TEST**

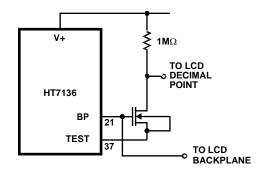

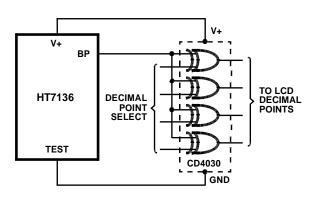

The TEST pin serves two functions. On the HT7136A it is coupled to the internally generated digital supply through a  $500\Omega$  resistor. Thus it can be used as the negative supply for externally generated segment drivers such as decimal points or any other presentation the user may want to include on the LCD display. Figures 4 and 5 show such an application. No more than a 1mA load should be applied.

FIGURE 4. SIMPLE INVERTER FOR FIXED DECIMAL POINT

The second function is a "lamp test". When TEST is pulled high (to V+) all segments will be turned on and the display should read "-1888". The TEST pin will sink about 5mA under these conditions.

**CAUTION:** On the HT7136A, in the lamp test mode, the segments have a constant DC voltage (no square-wave) and may burn the LCD display if left in this mode for several minutes.

FIGURE 5. EXCLUSIVE "OR" GATE FOR DECIMAL POINT DRIVE

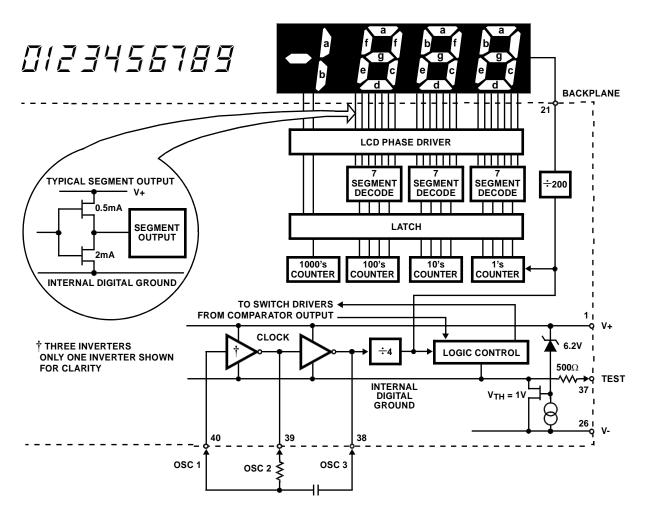

### **Digital Section**

Figures 6 shows the digital section for the HT7136A. In the HT7136A, an internal digital ground is generated from a 6V Zener diode and a large P-Channel source follower. This supply is made stiff to absorb the relatively large capacitive currents when the back plane (BP) voltage is switched. The BP frequency is the clock frequency divided by 800. For three readings/second this is a 60Hz square wave with a nominal amplitude of 5V. The segments are driven at the same frequency and amplitude and are in phase with BP when OFF, but out of phase when ON. In all cases negligible DC voltage exists across the segments.

The polarity indication is "on" for negative analog inputs. If IN LO and IN HI are reversed, this indication can be reversed also, if desired.

FIGURE 6. HT7136A DIGITAL SECTION

### System Timing

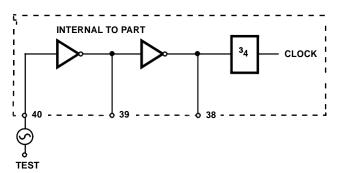

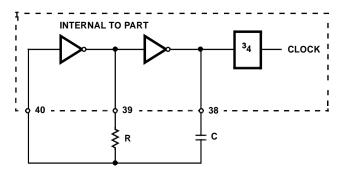

Figure 7 shows the clocking arrangement used in the HT7136A. Two basic clocking arrangements can be used:

- 1. Figure 9A, an external oscillator connected to DIP pin 40.

- 2. Figure 9B, an R-C oscillator using all three pins.

The oscillator frequency is divided by four before it clocks the decade counters. It is then further divided to form the three convert-cycle phases. These are signal integrate (1000 counts), reference de-integrate (0 to 2000 counts) and auto-zero (1000 to 3000 counts). For signals less than full scale, auto-zero gets the unused portion of reference de-integrate. This makes a complete measure cycle of 4,000 counts (16,000 clock pulses) independent of input voltage. For three readings/second, an oscillator frequency of 48kHz would be used.

To achieve maximum rejection of 60Hz pickup, the signal integrate cycle should be a multiple of 60Hz. Oscillator frequencies of 240kHz, 120kHz, 80kHz, 60kHz, 48kHz, 40kHz, 33<sup>1</sup>/<sub>3</sub>kHz, etc., should be selected. For 50Hz rejection, Oscillator frequencies of 200kHz, 100kHz, 66<sup>2</sup>/<sub>3</sub>kHz, 50kHz, 40kHz, etc. would be suitable. Note that 40kHz (2.5 readings/sec.) will reject both 50Hz and 60Hz (also 400Hz and 440Hz).

FIGURE 7A. EXTERNAL OSCILLATOR

FIGURE 7B. RCOSCILLATOR FIGURE 7. CLOCK CIRCUITS

### Component Value Selection

### Integrating Resistor

Both the buffer amplifier and the integrator have a class A output stage with  $100\mu A$  of quiescent current. They can supply  $1\mu A$  of drive current with negligible nonlinearity. The integrating resistor should be large enough to remain in this very linear region over the input voltage range, but small enough that undue leakage requirements are not placed on the PC board. For 2V full scale,  $1.8M\Omega$  is near optimum and similarly a  $180k\Omega$  for a 200mV scale.

### Integrating Capacitor

The integrating capacitor should be selected to give the maximum voltage swing that ensures tolerance buildup will not saturate the integrator swing (approximately 0.3V from either supply). In the HT7136A, when the analog COMMON is used as a reference, a nominal +2V full-scale integrator swing is fine. For three readings/second (48kHz clock) nominal values for  $C_{INT}$  are  $0.047\mu F$  and  $0.5\mu F$ , respectively. Of course, if different oscillator frequencies are used, these values should be changed in inverse proportion to maintain the same output swing.

An additional requirement of the integrating capacitor is that it must have a low dielectric absorption to preventroll-over errors. While other types of capacitors are adequate for this application, polypropylene capacitors give undetectable errors at reasonable cost.

### Auto-Zero Capacitor

The size of the auto-zero capacitor has some influence on the noise of the system. For 200mV full scale where noise is very important, a  $0.47\mu F$  capacitor is recommended. On the 2V scale, a  $0.047\mu F$  capacitor increases the speed of recovery from overload and is adequate for noise on this scale.

### Reference Capacitor

A  $0.1\mu F$  capacitor gives good results in most applications. However, where a large common mode voltage exists (i.e., the REF LO pin is not at analog COMMON) and a 200mV scale is used, a larger value is required to prevent roll-over error. Generally  $1\mu F$  will hold the roll-over error to 0.5 count in this instance.

### **Oscillator Components**

For all ranges of frequency a  $180k\Omega$  resistor is recommended and the capacitor is selected from the equation:

$$f = \frac{0.45}{RC}$$

For 48kHz Clock (3 Readings/s.),

C = 50pF.

### Reference Voltage

The analog input required to generate full scale output (2000 counts) is: VIN = 2VREF. Thus, for the 200mV and 2V scale, VRFF should equal 100mV and 1V, respectively. However, in many applications where the A/D is connected to a transducer, there will exist a scale factor other than unity between the input voltage and the digital reading. For instance, in a weighing system, the designer might like to have a full scale reading when the voltage from the transducer is 0.662V. Instead of dividing the input down to 200mV, the designer should use the input voltage directly and select V<sub>RFF</sub> = 0.341V. Suitable values for integrating resistor and capacitor would be  $330k\Omega$  and  $0.047\mu F$ . This makes the system slightly quieter and also avoids a divider network on the input. Another advantage of this system occurs when a digital reading of zero is desired for  $V_{IN} \neq 0$ . Temperature and weighing systems with a variable fare are examples. This offset reading can be conveniently generated by connecting the voltage transducer between IN HI and COMMON and the variable (or fixed) offset voltage between COMMON and IN LO.

Values shown are for 200mV full scale, 3 readings/sec., floating supply voltage (9V battery).

FIGURE 8. HT7136A USING THE INTERNAL REFERENCE

### Typical Applications

The HT7136A may be used in a wide variety of configurations. The circuits which follow show some of the possibilities, and serve to illustrate the exceptional versatility of these A/D converters.

The following application notes contain very useful information on understanding and applying this part and are available from Intersil.

### **Application Notes**

| NOTE # | DESCRIPTION                                                                            |  |  |  |

|--------|----------------------------------------------------------------------------------------|--|--|--|

| AN016  | "Selecting A/D Converters"                                                             |  |  |  |

| AN017  | "The Integrating A/D Converter"                                                        |  |  |  |

| AN018  | "Do's and Don'ts of Applying A/D Converters"                                           |  |  |  |

| AN023  | "Low Cost Digital Panel Meter Designs"                                                 |  |  |  |

| AN032  | "Understanding the Auto-Zero and Common Mode<br>Performance of the ICL7136/7/9 Family" |  |  |  |

| AN046  | "Building a Battery-Operated Auto Ranging DVM with the ICL7106"                        |  |  |  |

| AN052  | "Tips for Using Single Chip 3 <sup>1</sup> / <sub>2</sub> Digit A/D Converters"        |  |  |  |

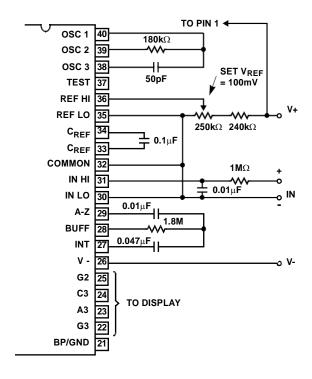

FIGURE 9. RECOMMENDED COMPONENT VALUES FOR 2V FULL SCALE

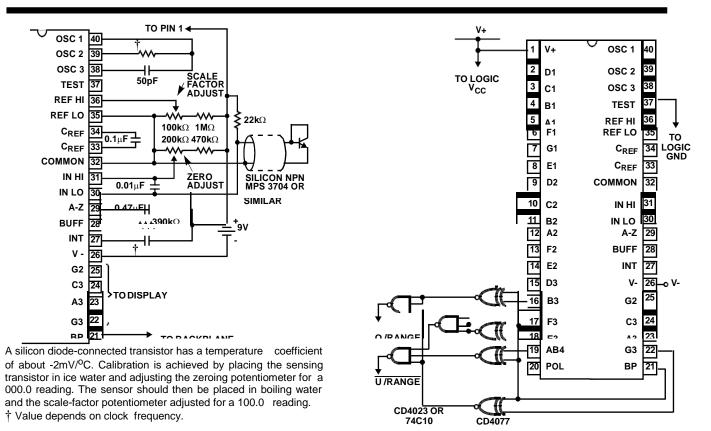

FIGURE 10. HT7136A USED AS A DIGITAL CENTIGRADE THERMOMETER

FIGURE 11. CIRCUIT FOR DEVELOPING UNDERRANGE AND OVERRANGE SIGNAL FROM HT7136A OUTPUTS

Test is used as a common-mode reference level to ensure compatibility with most op amps.

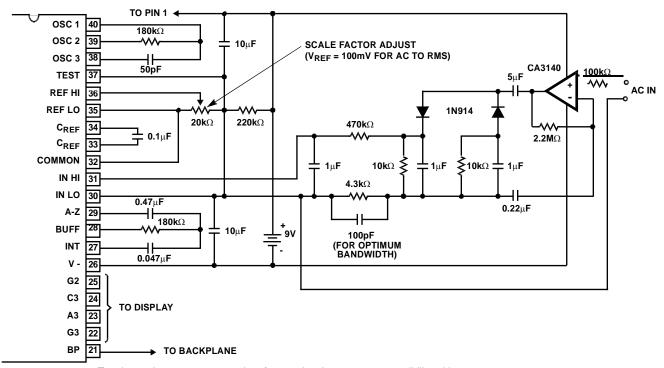

FIGURE 12. AC TO DC CONVERTER WITH HT7136A

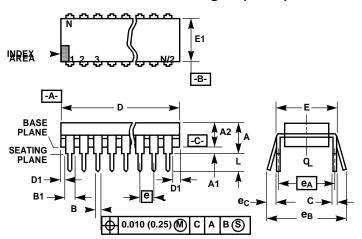

### Dual-In-Line Plastic Packages (PDIP)

#### NOTES:

- Controlling Dimensions: INCH. In case of conflict between English and Metric dimensions, the inch dimensions control.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- Symbols are defined in the "MO Series Symbol List" in Section 2.2 of Publication No. 95.

- 4. Dimensions A, A1 and L are measured with the package seated in JEDEC seating plane gauge GS-3.

- 5. D, D1, and E1 dimensions do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.010 inch (0.25mm).

- E and e<sub>A</sub> are measured with the leads constrained to be perpendicular to datum -C-

- 7.  $e_B$  and  $e_C$  are measured at the lead tips with the leads unconstrained.  $e_C$  must be zero or greater.

- 8. B1 maximum dimensions do not include dambar protrusions. Dambar protrusions shall not exceed 0.010 inch (0.25mm).

- 9. N is the maximum number of terminal positions.

- Corner leads (1, N, N/2 and N/2 + 1) for E8.3, E16.3, E18.3, E28.3, E42.6 will have a B1 dimension of 0.030 - 0.045 inch (0.76 - 1.14mm).

# **E40.6** (JEDEC MS-011-AC ISSUE B) 40 LEAD DUAL-IN-LINE PLASTIC PACKAGE

|                | INCHES    |       | MILLIMETERS |       |       |

|----------------|-----------|-------|-------------|-------|-------|

| SYMBOL         | MIN       | MAX   | MIN         | MAX   | NOTES |

| Α              | -         | 0.250 | -           | 6.35  | 4     |

| A1             | 0.015     | -     | 0.39        | -     | 4     |

| A2             | 0.125     | 0.195 | 3.18        | 4.95  | -     |

| В              | 0.014     | 0.022 | 0.356       | 0.558 | -     |

| B1             | 0.030     | 0.070 | 0.77        | 1.77  | 8     |

| С              | 0.008     | 0.015 | 0.204       | 0.381 | -     |

| D              | 1.980     | 2.095 | 50.3        | 53.2  | 5     |

| D1             | 0.005     | -     | 0.13        | -     | 5     |

| Е              | 0.600     | 0.625 | 15.24       | 15.87 | 6     |

| E1             | 0.485     | 0.580 | 12.32       | 14.73 | 5     |

| е              | 0.100 BSC |       | 2.54 BSC    |       | -     |

| e <sub>A</sub> | 0.600 BSC |       | 15.24 BSC   |       | 6     |

| eB             | -         | 0.700 | -           | 17.78 | 7     |

| L              | 0.115     | 0.200 | 2.93        | 5.08  | 4     |

| N              | 40        |       | 4           | 0     | 9     |

Rev. 0 12/93

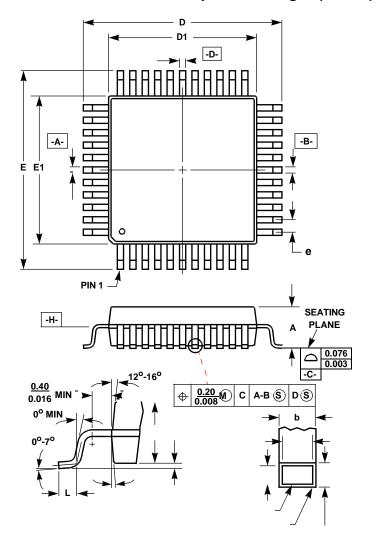

# Metric Plastic Quad Flatpack Packages (MQFP)

Q44.10x10 (JEDEC MS-022AB ISSUE B)

44 LEAD METRIC PLASTIC QUAD FLATPACK PACKAGE

|        | INCHES    |       | MILLIMETERS |       |       |

|--------|-----------|-------|-------------|-------|-------|

| SYMBOL | MIN       | MAX   | MIN         | MAX   | NOTES |

| Α      | -         | 0.096 | -           | 2.45  | -     |

| A1     | 0.004     | 0.010 | 0.10        | 0.25  | -     |

| A2     | 0.077     | 0.083 | 1.95        | 2.10  | -     |

| b      | 0.012     | 0.018 | 0.30        | 0.45  | 6     |

| b1     | 0.012     | 0.016 | 0.30        | 0.40  | -     |

| D      | 0.515     | 0.524 | 13.08       | 13.32 | 3     |

| D1     | 0.389     | 0.399 | 9.88        | 10.12 | 4, 5  |

| Е      | 0.516     | 0.523 | 13.10       | 13.30 | 3     |

| E1     | 0.390     | 0.398 | 9.90        | 10.10 | 4, 5  |

| L      | 0.029     | 0.040 | 0.73        | 1.03  | -     |

| N      | 44        |       | -           | 14    | 7     |

| е      | 0.032 BSC |       | 0.80        | BSC   | -     |

Rev. 2 4/99

#### NOTES:

- Controlling dimension: MILLIMETER. Converted inch dimensions are not necessarily exact.

- 2. All dimensions and tolerances per ANSI Y14.5M-1982.

- 3. Dimensions D and E to be determined at seating plane -C-

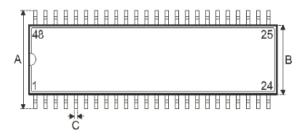

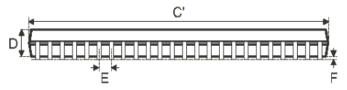

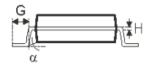

# Package Information 48-pin SSOP (300mil) Outline Dimensions

| Symbol | Dimensions in mil |      |      |  |  |  |

|--------|-------------------|------|------|--|--|--|

| Symbol | Min.              | Nom. | Max. |  |  |  |

| Α      | 395               | _    | 420  |  |  |  |

| В      | 291               | _    | 299  |  |  |  |

| С      | 8                 | _    | 12   |  |  |  |

| C,     | 613               | _    | 637  |  |  |  |

| D      | 85                | _    | 99   |  |  |  |

| E      | _                 | 25   | _    |  |  |  |

| F      | 4                 | _    | 10   |  |  |  |

| G      | 25                | _    | 35   |  |  |  |

| Н      | 4                 | _    | 12   |  |  |  |

| α      | 0°                | _    | 8°   |  |  |  |