### Half-Bridge Gate Driver

#### **Features**

- Floating high-side driver in bootstrap operation to 600V

- Drives two N-channel MOSFETs or IGBTs in a half bridge configuration

- 290mA source/600mA sink output current capability

- Outputs tolerant to negative transients

- Internal dead time of 520ns to protect MOSFETs

- Wide low side gate driver supply voltage: 10V to 20V

- Logic input (IN and SD\*) 3.3V capability

- Schmitt triggered logic inputs

- Undervoltage lockout for V<sub>cc</sub> (logic and low side supply)

- Extended temperature range: -40°C to +125°C

#### **Description**

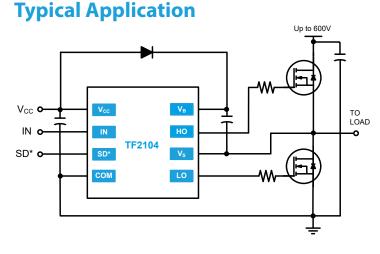

The TF2104 is a high voltage, high speed gate driver capable of driving N-channel MOSFETs and IGBTs in a half bridge configuration. TF Semiconductor's high voltage process enables the TF2104's high side to switch to 600V in a bootstrap operation.

The TF2104 logic inputs are compatible with standard TTL and CMOS levels (down to 3.3V) to interface easily with controlling devices. The driver outputs feature high pulse current buffers designed for minimum driver cross conduction. TF2104 has a fixed internal deadtime of 520ns (typical).

The TF2104 is offered in PDIP-8 and SOIC-8(N) packages and operate over an extended -40  $^{\circ}$ C to +125  $^{\circ}$ C temperature range.

#### **Ordering Information**

|             |           | Y          | ear Year Week Week |

|-------------|-----------|------------|--------------------|

| PART NUMBER | PACKAGE   | PACK / Qty | MARK               |

| TF2104-3AS  | PDIP-8    | Tube / 50  | TF2104<br>Lot ID   |

| TF2104-TAU  | SOIC-8(N) | Tube / 100 | TF2104             |

| TF2104-TAH  | SOIC-8(N) | T&R / 2500 | ✓ IF2104<br>Lot ID |

## Motor Controls

**Applications**

DC-DC Converters

AC-DC Inverters

Class D Power Amplifiers

14/ 114/

**TF2104**

#### Half-Bridge Gate Driver

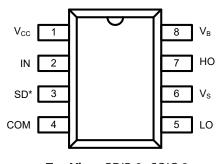

Top View: PDIP-8, SOIC-8

TF2104

## **Pin Descriptions**

| PIN NAME        | PIN NUMBER | PIN DESCRIPTION                                                                          |

|-----------------|------------|------------------------------------------------------------------------------------------|

| V <sub>cc</sub> | 1          | Logic and low side supply                                                                |

| IN              | 2          | Logic input for high-side and low-side gate driver outputs (HO and LO), in phase with HO |

| SD*             | 3          | Logic input for shutdown, enabled low                                                    |

| СОМ             | 4          | Low-side and logic return                                                                |

| LO              | 5          | Low-side gate drive output                                                               |

| V <sub>s</sub>  | 6          | High-side floating supply return                                                         |

| НО              | 7          | High-side gate drive output                                                              |

| V <sub>B</sub>  | 8          | High-side floating supply                                                                |

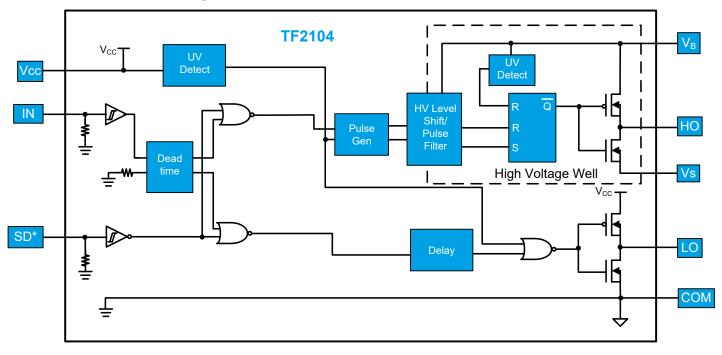

### **Functional Block Diagram**

#### Half-Bridge Gate Driver

## Absolute Maximum Ratings (NOTE1)

| $V_{\rm B}$ - High side floating supply voltage0.3V to +624V                                |

|---------------------------------------------------------------------------------------------|

| $V_s$ - High side floating supply offset voltageV <sub>B</sub> -24V to V <sub>B</sub> +0.3V |

| $V_{HO}$ -Highside floating output voltageV <sub>s</sub> -0.3V to V <sub>B</sub> +0.3V      |

| $dV_s/dt$ - Offset supply voltage transient50 V/ns                                          |

|                                                                                             |

| V <sub>cc</sub> - Low-side fixed supply voltage    | 0.3V to +24V                |

|----------------------------------------------------|-----------------------------|

| V <sub>10</sub> - Low-side output voltage          | 0.3VtoV <sub>cc</sub> +0.3V |

| V <sub>IN</sub> - Logic input voltage (IN and SD*) | 0.3V to $V_{cc}^{cc}$ +0.3V |

**NOTE1** Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| $P_{D}\text{-}$ Package power dissipation at $T_{A} \leq 25\ ^\circC$ SOIC-80.625W PDIP-81.0W |

|-----------------------------------------------------------------------------------------------|

| SOIC-8(N) Thermal Resistance (NOTE2)                                                          |

| θ <sub>IA</sub>                                                                               |

| PDIP-8 Thermal Resistance (NOTE2)                                                             |

| θ <sub>JA</sub> 125 °C/W                                                                      |

|                                                                                               |

| T <sub>J</sub> - Junction operating temperature+150 °C                                        |

| T <sub>L</sub> - Lead Temperature (soldering, 10 seconds)+300 °C                              |

| $\rm T_{stg}$ - Storage temerature55 to 150 $^{\circ}\rm C$                                   |

**NOTE2** Thermal resistance and power dissipation ratings are measured under board mounted and still air conditions.

### **Recommended Operating Conditions**

| Symbol          | Parameter                                  | MIN                 | МАХ                 | Unit |

|-----------------|--------------------------------------------|---------------------|---------------------|------|

| V <sub>B</sub>  | High side floating supply absolute voltage | V <sub>s</sub> + 10 | V <sub>s</sub> + 20 | V    |

| Vs              | High side floating supply offset voltage   | NOTE3               | 600                 | V    |

| V <sub>HO</sub> | High side floating output voltage          | Vs                  | V <sub>B</sub>      | V    |

| V <sub>cc</sub> | Low side fixed supply voltage              | 10                  | 20                  | V    |

| V               | Low side output voltage                    | 0                   | V <sub>cc</sub>     | V    |

| V <sub>IN</sub> | Logic input voltage (IN and SD*)           | 0                   | 5                   | V    |

| T <sub>A</sub>  | Ambient temperature                        | -40                 | 125                 | °C   |

**NOTE3** Logic operational for  $V_{c}$  of -5V to +600V. Logic state held for  $V_{c}$  of -5V to - $V_{RC}$

## TF2104

#### Half-Bridge Gate Driver

### DC Electrical Characteristics (NOTE4)

$V_{\text{BIAS}}(V_{\text{CC}},V_{\text{BS}})$  = 15V,  $T_{\text{A}}$  = 25 °C , unless otherwise specified.

| Symbol             | Parameter                                                     | Conditions                           | MIN | ТҮР  | МАХ | Unit |

|--------------------|---------------------------------------------------------------|--------------------------------------|-----|------|-----|------|

| V <sub>IH</sub>    | Logic "1" (IN) & Logic "0" (SD*) input voltage                | $V_{cc} = 10V \text{ to } 20V$       | 2.5 |      |     |      |

| V <sub>IL</sub>    | Logic "0" (IN) & Logic "1" (SD*) input voltage                | Note 5                               |     |      | 0.8 | v    |

| V <sub>OH</sub>    | High level output voltage, V <sub>BIAS</sub> - V <sub>O</sub> | $I_0 = 2mA$                          |     | 0.05 | 0.2 |      |

| V <sub>OL</sub>    | Low level output voltage, $V_o$                               | $I_0 = 2mA$                          |     | 0.02 | 0.1 |      |

| I <sub>LK</sub>    | Offset supply leakage current                                 | VB = VS = 600V                       |     |      | 50  |      |

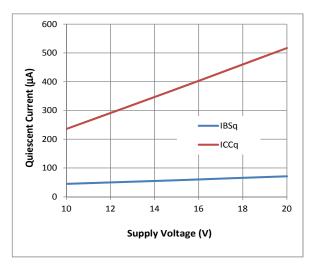

| I <sub>BSQ</sub>   | Quiescent V <sub>BS</sub> supply current                      | $V_{IN} = 0V \text{ or } 5V$         |     | 60   | 100 |      |

| I <sub>ccq</sub>   | Quiescent V <sub>cc</sub> supply current                      | $V_{IN} = 0V \text{ or } 5V$         |     | 350  | 500 | μA   |

| I <sub>IN+</sub>   | Logic "1" input bias current                                  | $V_{IN} = 5V, SD^* = 0V$             |     | 3    | 10  |      |

| I <sub>IN-</sub>   | Logic "0" input bias current                                  | $V_{IN} = 0V, SD^* = 5V$             |     |      | 5   |      |

| $V_{CCUV+}$        | V <sub>cc</sub> supply under-voltage positive going threshold |                                      | 8.0 | 8.9  | 9.8 |      |

| V <sub>CCUV-</sub> | V <sub>cc</sub> supply under-voltage negative going threshold |                                      | 7.4 | 8.2  | 9.0 | V    |

| I <sub>O+</sub>    | Output high short circuit pulsed current                      | $V_0 = 0V$ , PW $\leq 10 \ \mu s$    | 130 | 290  |     |      |

| I <sub>0-</sub>    | Output low short circuit pulsed current                       | $V_{o} = 15V$ , PW $\leq 10 \ \mu s$ | 270 | 600  |     | mA   |

**NOTE4** The  $V_{IIF}$  and  $I_{IIF}$  parameters are applicable to the two logic input pins: IN and SD\*. The  $V_0$  and  $I_0$  parameters are applicable to the respective output pins: H0 and L0 **NOTE5** For optimal operation, it is recommended that the input pulse (to IN and SD\*) should have an amplitude of 2.5V minimum with a pulse width of 1µs minimum.

**TF2104**

Half-Bridge Gate Driver

## **AC Electrical Characteristics**

$V_{_{BIAS}}(V_{_{CC}},V_{_{BS}})$  = 15V,  $C_{_L}$  = 1000pF, and  $T_{_A}$  = 25 °C , unless otherwise specified.

| Symbol           | Parameter                                               | Conditions     | MIN | ТҮР | МАХ | Unit |

|------------------|---------------------------------------------------------|----------------|-----|-----|-----|------|

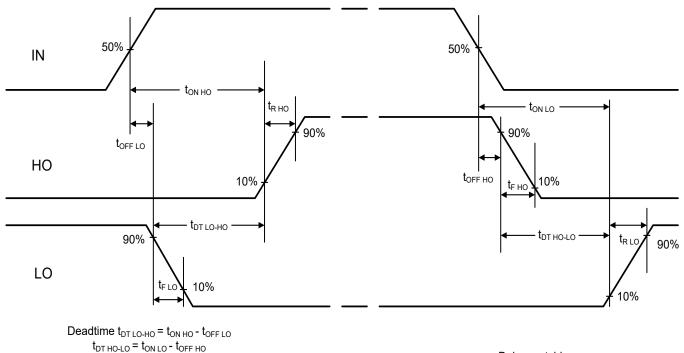

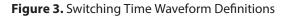

| t <sub>on</sub>  | Turn-on propagation delay                               | $V_s = 0V$     |     | 680 | 820 |      |

| t <sub>off</sub> | Turn-off propagation delay                              | $V_{s} = 600V$ |     | 150 | 220 |      |

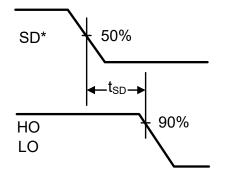

| t <sub>sD</sub>  | Shutdown propagation delay                              |                |     | 160 | 220 |      |

| t <sub>DM</sub>  | Delay matching, HS & LS turn-on/turn-off                |                |     |     | 60  | ns   |

| t <sub>r</sub>   | Turn-on rise time                                       |                |     | 70  | 170 |      |

| t <sub>r</sub>   | Turn-off fall time                                      | $V_s = 0V$     |     | 35  | 90  |      |

| t <sub>DT</sub>  | Deadtime: t <sub>DT LO-HO</sub> & t <sub>DT HO-LO</sub> |                | 400 | 520 | 650 |      |

Half-Bridge Gate Driver

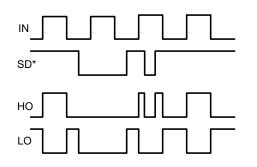

Figure 1. Input / Output Timing Diagram

Figure 2. Shutdown Waveform Definition

Deadtime matching  $t_{MDT} = t_{DT LO-HO} - t_{DT HO-LO}$

$\begin{array}{l} \text{Delay matching} \\ t_{\text{DM OFF}} = t_{\text{OFF LO}} - t_{\text{OFF HO}} \\ t_{\text{DM ON}} = t_{\text{ON LO}} - t_{\text{ON HO}} \end{array}$

#### Half-Bridge Gate Driver

TF Semiconductor Solutions

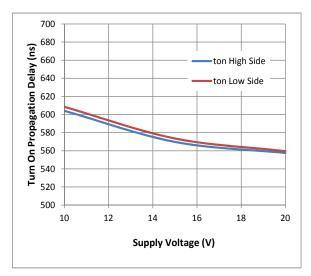

Figure 4. Turn-on Propagation Delay vs. Supply Voltage

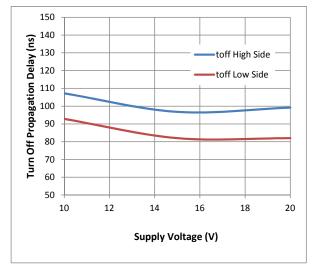

Figure 6. Turn-off Propagation Delay vs. Supply Voltage

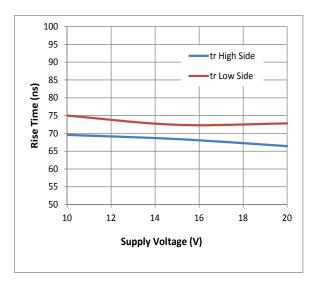

Figure 8. Rise Time vs. Supply Voltage

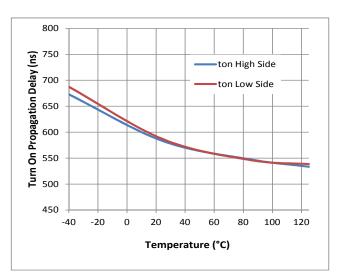

Figure 5. Turn-on Propagation Delay vs. Temperature

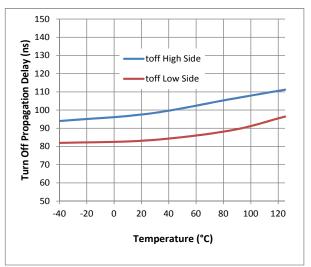

Figure 7. Turn-off Propagation Delay vs. Temperature

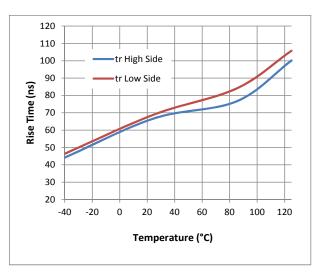

Figure 9. Rise Time vs. Temperature

#### Half-Bridge Gate Driver

TF Semiconductor Solutions

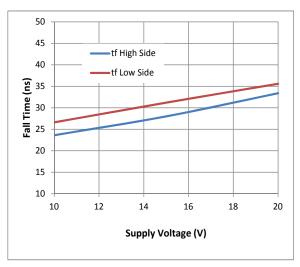

Figure 10. Fall Time vs. Supply Voltage

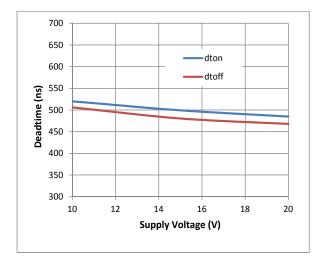

Figure 12. Deadtime vs. Supply Voltage

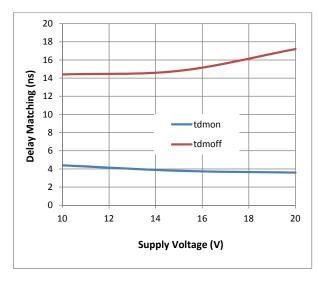

Figure 14. Delay Matching vs. Supply Voltage

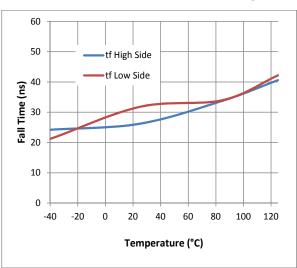

Figure 11. Fall Time vs. Temperature

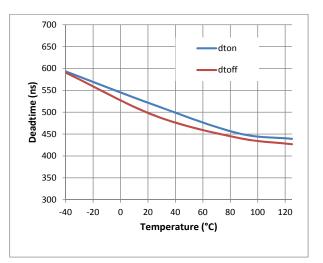

Figure 13. Deadtime vs. Temperature

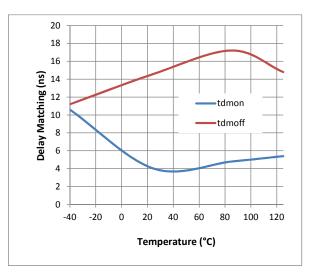

#### Half-Bridge Gate Driver

TF Semiconductor Solutions

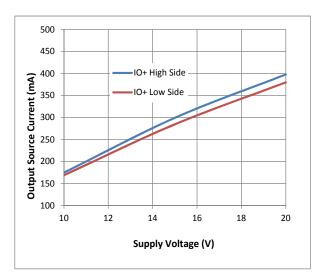

Figure 16. Output Source Current vs. Supply Voltage

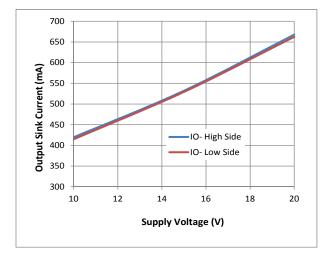

Figure 18. Output Sink Current vs. Supply Voltage

Figure 20. Quiescent Current vs. Supply Voltage

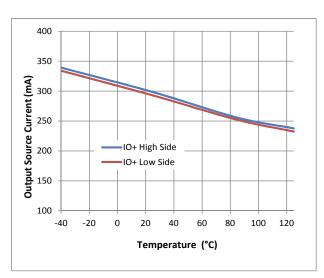

Figure 17. Output Source Current vs. Temperature

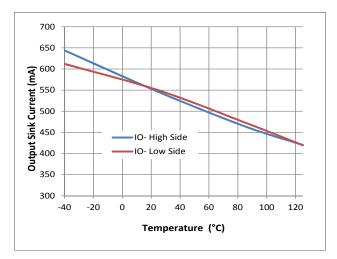

Figure 19. Output Sink Current vs. Temperature

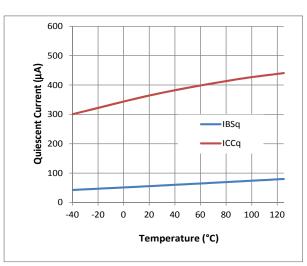

Figure 21. Quiescent Current vs. Temperature

#### Half-Bridge Gate Driver

TF Semiconductor Solutions

tfs

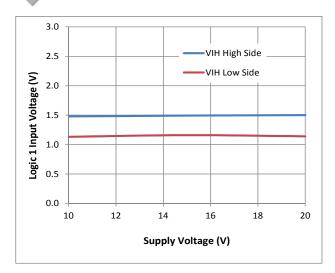

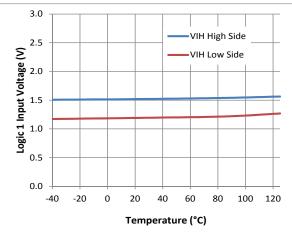

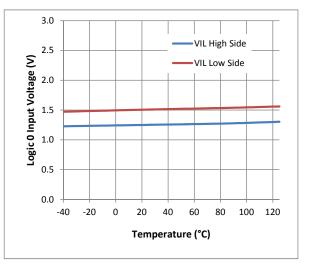

Figure 22. Logic 1 Input Voltage vs. Supply Voltage

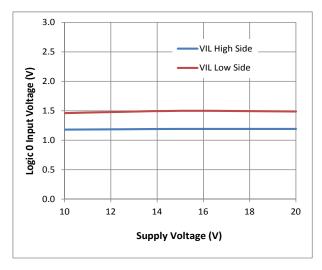

Figure 24. Logic 0 Input Voltage vs. Supply Voltage

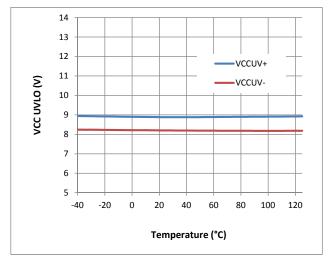

Figure 26. V<sub>cc</sub> UVLO vs. Temperature

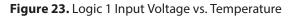

Figure 25. Logic 0 Input Voltage vs. Temperature

Figure 27. Offset Supply Leakage Current Temperature, VB=VS= 600V

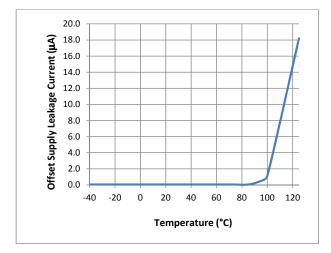

#### Halfbridge Configuration

A common configuration used for the TF2104 is a halfbridge (see fig. 28). In a half-bridge configuration the source of the high-side MOSFET ( $Q_H$ ) and the drain of the low-side MOSFET ( $Q_L$ ) are connected. That line ( $V_s$ ) is both the return for the high side in the gate driver IC as well as the output of the half-bridge. When  $Q_H$  is on and  $Q_L$  is off,  $V_s$  swings to high voltage, and when  $Q_H$  is off and  $Q_L$ is on,  $V_s$  swings to GND. Hence the output switches from GND to high voltage at the frequency of HIN and LIN, this line drives a transformer for a power supply, or a coil on a motor. In this half-bridge configuration, high voltage DC is input to the MOSFETs, and converted to a high voltage switching signal to output to load (fig 28). The MOSFETs operate in saturation mode and an important function of the gate driver is to turn on the MOSFET quickly to minimize switching losses from the linear region of the MOSFET (turn on and turn off); the TF2104 has a typical rise/fall time of 70ns/35ns into a 1nF load.

Another important function of the gate driver IC in the half-bridge configuration is to convert the logic signals of control (TF2104 operates at logic 3V), to a voltage level and current capacity to drive the gate of the MOSFET and IGBT; this requires driving large currents initially to turn on/ turn off the MOSFET quickly. Also the floating well of the high-side allows high voltage operation in the bootstrap operation.

Figure 28. TF2104 in a half-bridge configuration

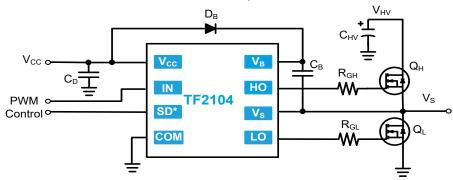

#### **Bootstrap Operation**

The supply for the TF2104 High Side is provided by the bootstrap capacitor  $C_{_B}$  (see fig 29). In the half-bridge configuration,  $V_s$  swings from 0V to  $V_{_{HV}}$  depending on the PWM input ot the IC. When  $V_s$  is 0V,  $V_{_{BS}}$  will go below  $V_{_{CC}}$  and  $V_{_{CC}}$  will charge  $C_{_B}$ . When HO goes high,  $V_s$  swings to  $V_{_{HV}}$ , and  $V_{_{BS}}$  remains at  $V_{_{CC}}$  minus a diode drop ( $D_{_B}$ ) due to the voltage on  $C_{_B}$ . This is the supply for the high side gate driver and allows the gate driver to function with the floating well ( $V_s$ ) at the high voltage.

When considering the **value of the bootstrap capacitor**  $C_{\rm B}$ , it is important that it is sized to provide enough energy to quickly drive the gate of  $Q_{\rm H}$ . Values of  $1\mu$ F to  $10\mu$ F are recommended, exact value depending on gate capacitance, and the noise in application. It is key to use a low ESR capacitor that is close to the device. This will best quickly supply charge to the gate of the MOSFET.

Figure 29. TF2104 high side in bootstrap operation

#### Half-Bridge Gate Driver

For a more detailed description on Gate Resistor Selection and Bootstrap Capacitor Selectrion, see the TF Semiconductor's High Voltage Gate Driver Application Note (AN1347).

#### **Gate Drive Control**

The most crucial time in the gate drive is the turn on and turn off of the MOSFET, and performing this function quickly, but with minimal noise and ringing is key. Too fast a rise/fall time can cause unnecessary ringing, and too slow a rise/fall time will increase switching losses in the MOSFET.

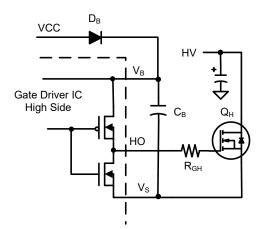

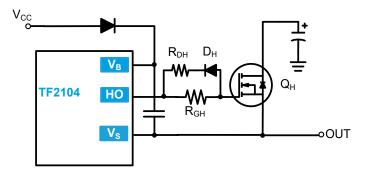

An example of just the high side gate driver is shown in figure 30 (any selection of gate driver components should be the same for high side and low side drive); two extra components are seen,  $R_{DH}$  and  $D_{H}$ . With the careful selection of  $R_{GH}$  and  $R_{DH}$ , it is possible to selectively control the rise time and fall time of the gate drive. For turn on, all current will go from the IC through  $R_{GH}$  and charge the MOSFET gate capacitor, hence increasing or decreasing  $R_{GH}$  will increase or decrease rise time in the application. With the addition of  $D_{H}$ , the fall time can be separately controlled as the turn off current flows from the MOSFET gate capacitor, through  $D_{H}$  and  $R_{DH}$  to the driver in the IC to VS. So increasing or decreasing R

Increasing turn on and turn off has the effect of limiting ringing and noise due to parasitic inductances, hence with a noisy environment, it may be necessary to increase the gate resistors. For **gate resistor value selection** the exact value depends on the type of application and desired level of noise and ringing expected. Generally, power supplies switch at a fast speed, and want to squeeze out efficiency of the MOSFETs, solower values are recommended, for example RGH =  $5\Omega - 20\Omega$ . For motors, the switching speed is generally slower, and the application has more inherent noise, so higher values are recommended, for example RGH =  $20\Omega - 100\Omega$ .

Figure 30. Gate Drive Control

TF2104

#### Half-Bridge Gate Driver

## **Application Information**

#### **Layout Considerations**

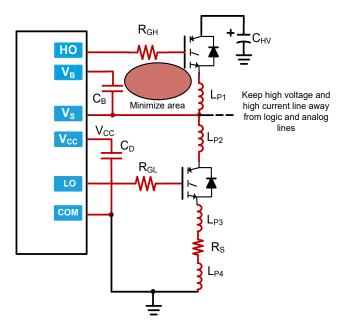

Layout plays a considerable role in noise and ringing in a circuit; unwanted noise coupling, unpredicted glitches and abnormal operation could arise due to poor layout of the associated components. Figure 31 shows a halfbridge schematic with parasitic inductances in the high current path  $(L_{p_1}, L_{p_2}, L_{p_3}, L_{p_4})$  which would be caused by inductance in the metal of the trace. Considering fig. 31, the length of the tracks in red should be minimized, and the bootstrap capacitor  $(C_B)$ and the decoupling capacitor  $(C_D)$  should be placed as close to the IC as possible. Low ESR ceramic capacitors should be used to minimize inductance. And finally the gate resistors  $(R_{GH} \text{ and } R_{GL})$  and the sense resistor  $(R_S)$ should be surface mount devices. These suggestions will reduce the parasitics due to the PCB traces.

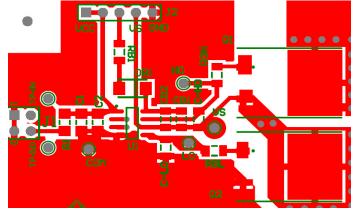

A layout example is seen in figure 32. Here there are two bootstrap capacitors (CB1 and CB2) and two decoupling capacitors (C1 and C2), and the caps are placed as close as possible to the HVIC. But even if only using one boostrap cap and one decoupling capacitor, it needs to be as close as possible to minimize inductance between the cap and the driver.

Generally, for the **decoupling capacitor** on VCC, at least one low ESR capacitor is recommended with it close to the device as shown in figure 32. Recommended values are  $1\mu$ F to  $10\mu$ F. A second smaller decoupling capacitor is sometimes added to provide better high frequency response (for example  $0.1\mu$ F).

Figure 31. Layout Suggestions for TF2104 in a halfbridge

**Figure 32.** Layout example for TF2104 (U1) in a halfbridge, notice the bootstrap caps (CB1, CB2), VCC caps (C1 and C2), and bootstrap diode (DB1) adjacent to the IC.

Half-Bridge Gate Driver

# Application Exam

TF Semiconductor Solutions

tfss

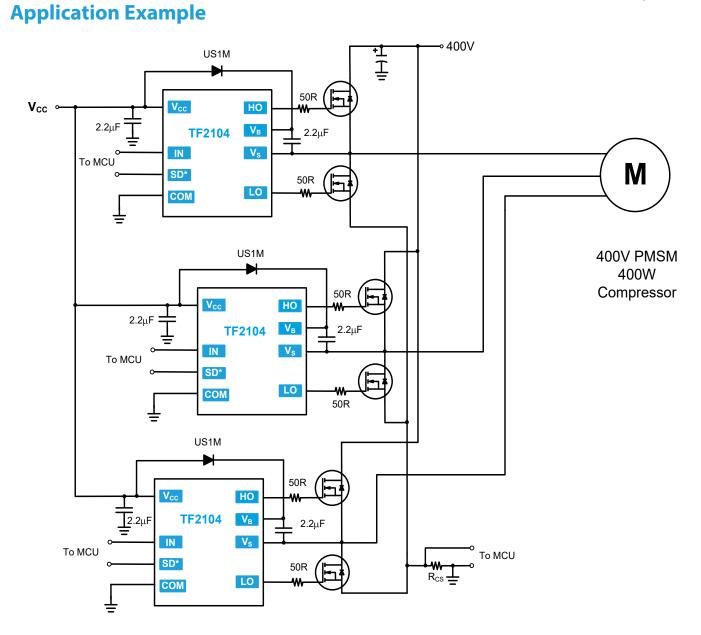

Figure 33. Three Phase Motor Driver using the TF2104

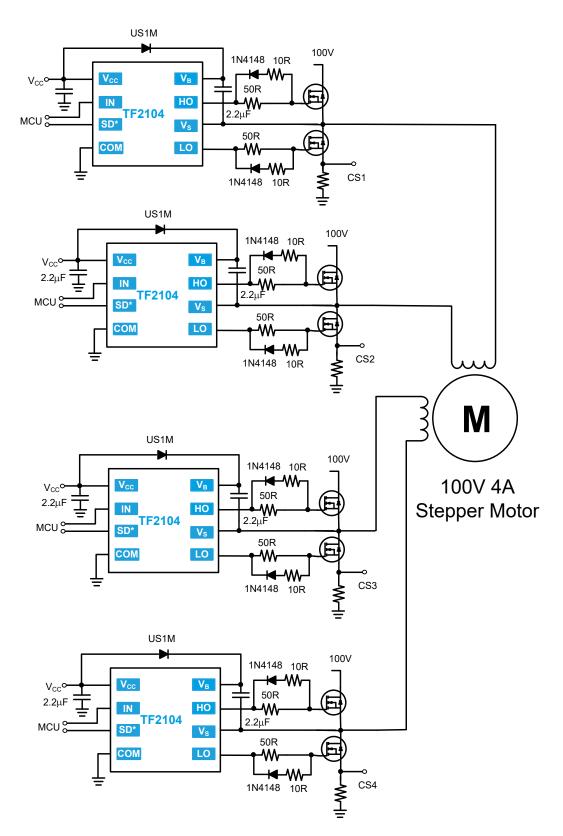

Figure 34. Motor Driver using the TF2104 for 100V, 4A Stepper Motor

TF Semiconductor Solutions

tfss

Half-Bridge Gate Driver

**TF2104**

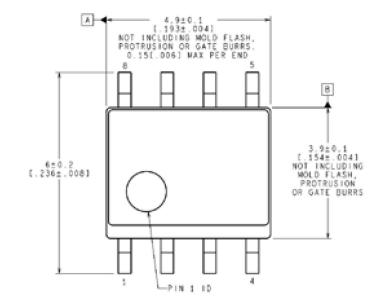

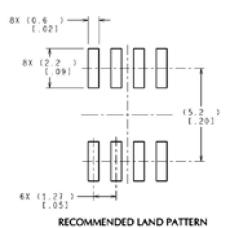

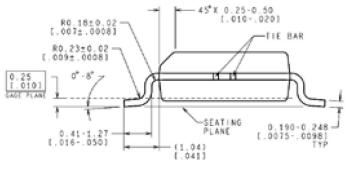

Package Dimensions (SOIC-8 N)

Please contact support@tfsemi.com for package availability.

1.35-1.75 [.053-.069] TYP 1.27 6X (1.45 ъ □ 0.11.0041 C ľ 8X 0.35-0.51 {.0138-.02001 Φ 0.25(.010)❷ C AS 83 0.10-0.25 [.004-.010] TYP

NOTES: UNLESS OTHERWISE SPECIFIED

1. REFERENCE JEDEC REGISTRATION MS-012, VARIATION AA.

CONTROLLING DIMENSION IS MILLIMETER VALUES IN [ ] ARE INCHES DIMENSIONS IN ( ) FOR REFERENCE ONLY

#### Half-Bridge Gate Driver

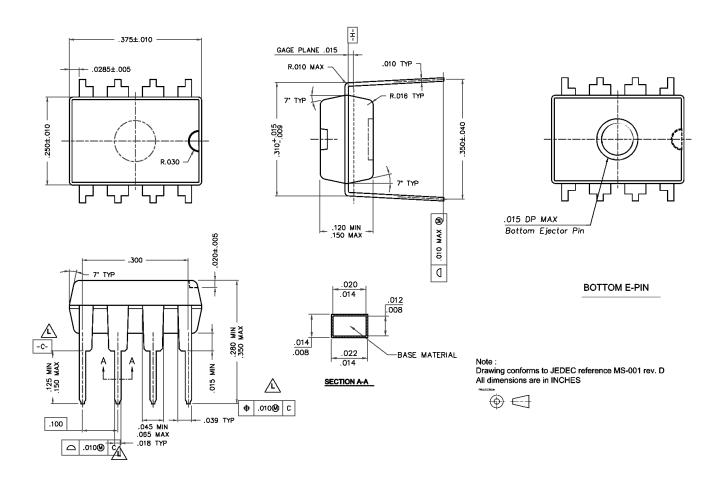

## Package Dimensions (PDIP-8)

Please contact support@tfsemi.com for package availability.

Half-Bridge Gate Driver

| Rev. | Change                                    | Owner           | Date      |

|------|-------------------------------------------|-----------------|-----------|

| 1.0  | First release, final datasheet            | Keith Spaulding | 1/29/2016 |

| 1.1  | Added deadtime graphs, fig. 12 and fig 13 | Keith Spaulding | 2/26/2016 |

| 1.2  | Text edit                                 | Keith Spaulding | 7/17/2017 |

| 1.3  | Add Note 5                                | Duke Walton     | 7/25/2019 |

#### **Important Notice**

TF Semiconductor Solutions (TFSS) PRODUCTS ARE NEITHER DESIGNED NOR INTENDED FOR USE IN MILITARY AND/OR AEROSPACE, AUTOMOTIVE OR MEDICAL DEVICES OR SYSTEMS UNLESS THE SPECIFIC TFSS PRODUCTS ARE SPECIFICALLY DESIGNATED BY TFSS FOR SUCH USE. BUYERS ACKNOWLEDGE AND AGREE THAT ANY SUCH USE OF TFSS PRODUCTS WHICH TFSS HAS NOT DESIGNATED FOR USE IN MILITARY AND/OR AEROSPACE, AUTOMOTIVE OR MEDICAL DEVICES OR SYSTEMS IS SOLELY AT THE BUYER'S RISK.

TFSS assumes no liability for application assistance or customer product design. Customers are responsible for their products and applications using TFSS products.

Resale of TFSS products or services with statements different from or beyond the parameters stated by TFSS for that product or service voids all express and any implied warranties for the associated TFSS product or service. TFSS is not responsible or liable for any such statements.

©2019 TFSS. All Rights Reserved. Information and data in this document are owned by TFSS wholly and may not be edited , reproduced, or redistributed in any way without the express written consent from TFSS.

For additional information please contact support@tfproducts.com or visit www.tfsemi.com