### **Key Parameters**

| Rated Output Current (1 MHz) <sup>(1)</sup>  | 12.5 A |

|----------------------------------------------|--------|

| Operating PWM Frequency Range <sup>(2)</sup> | 3 MHz  |

| Operating Input Voltage Range                | 60 V   |

| Bias Supply Voltage                          | 12 V   |

Output Current and PWM Frequency Ratings are functions of Operating Conditions. See Notes 1 & 2.

### Features

- Separate and independent high side and low side control inputs

- Input signal compatible with 3.3 V or 5 V CMOS logic levels

- 20 ns minimum input pulse width

- 20 ns delay time input to output

- 1 ns switching time at output node

- Robust level shifter operating from negative transient conditions

- False trigger immunity greater than 100 V/ns at output node

- Synchronous charging for high side bootstrap supply

- Regulated gate drive buffer output to drive output FETs at safe operating level

- Undervoltage lockout for high side and low side power supplies

- LGA Chip Scale Package

### **Applications**

- Buck and Boost Converters

- Half-Bridge, Full Bridge or LLC Isolated Converters

- Class D Switching Audio Amplifier

- Single Phase and Three Phase Motor Drive Inverter\*

#### \*Optimized device for motor drive is EPC21521

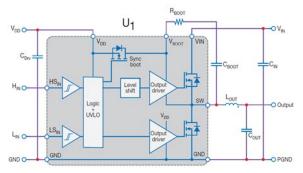

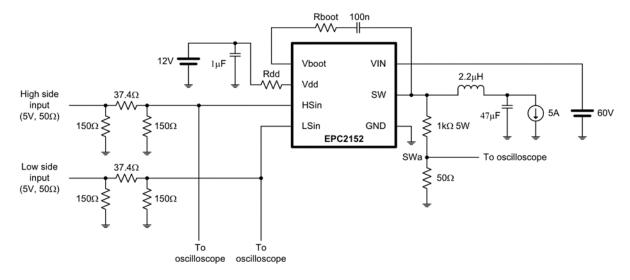

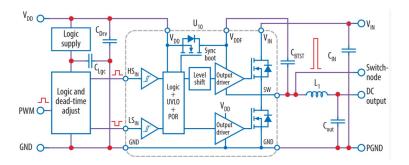

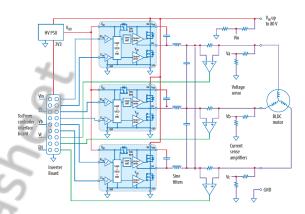

## **Typical Application**

Synchronous Buck Converter

$R_{\rm BOOT}$  is used to adjust di/dt of HS FET turn-on transition. SW node peak over-voltage spike should be kept below Abs Max Ratings of  $V_{\rm SW(continuous)}$  and  $V_{\rm SW(pulse)}$ .

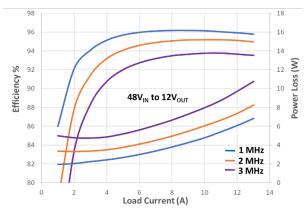

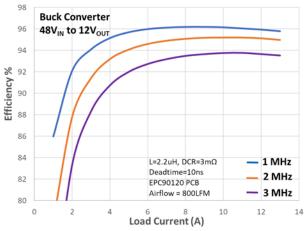

## **Performance Curves**

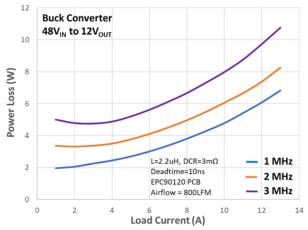

Buck Converter Topology,  $V_{\rm IN}$  = 48 V,  $V_{\rm OUT}$  = 12 V, Deadtime = 10ns, L = 2.2  $\mu$ H, DCR = 3 m $\Omega$ ,  $R_{\rm BOOT}$  = 2.2  $\Omega$ , EPC90120 PCB, Airflow = 800 LFM.

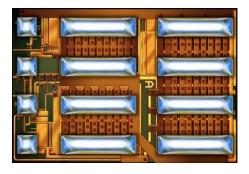

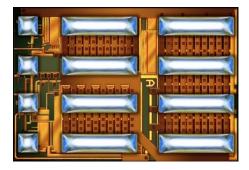

## **Die Photo**

3.85 mm x 2.59 mm x 0.63 mm

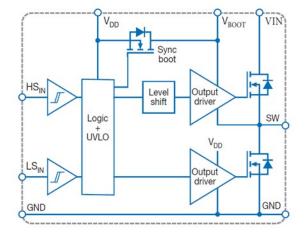

### **Functional Block Diagram**

### **General Description**

The EPC2152 is a single chip driver plus eGaN® FET half-bridge power stage product family. Integration is implemented using EPC's proprietary GaN IC technology. Input logic interface, level shifting, bootstrap charging and gate drive buffer circuits along with eGaN output FETs configured as a halfbridge are integrated within a monolithic chip. This results in a chip-scale LGA form factor device that measures only 3.85 mm x 2.59 mm x 0.63 mm.

The two eGaN output FETs in half-bridge topology are designed to have same R<sub>DS(on)</sub>. Integration of eGaN FETs with on-chip gate drive buffers practically eliminate effects of common source inductance and gate drive loop inductance. Monolithic integration combined with a pinout that uses low inductance LGA solder bumps, result in a high-current output node that can switch within 1 ns under full load with PWM frequency up to 3 MHz.

The charging path for the floating bootstrap supply is integrated using GaN FET driven by a synchronous circuit. This eliminates the need for an external bootstrap diode with associated reverse recovery charge that may result in significant power loss at high frequency switching. This synchronous bootstrap charging circuit also minimizes the voltage drop in the bootstrap charging path to ensure adequate voltage for the bootstrap power supply.

Robust level shifters from low side to high side channels are designed to operate correctly even at large negative clamped voltage and to avoid false trigger from fast dv/dt transients exceeding 100 V/ns.

Internal regulation of the gate drive voltage based on feedback from the driven output FETs ensures a safe gate voltage level while still turning on the output FETs to a low R<sub>DS(on)</sub> state. Additional protection is provided by separate high side and low side undervoltage lockout (UVLO) circuits with lockout levels referenced to the gate drive buffer circuit to avoid operating the output FETs in a high R<sub>DS(on)</sub> state.

The EPC2152 device is capable of interfacing to digital controllers that use standard 3.3 V or 5V CMOS logic levels. Separate and independent high side and low side logic control inputs allow external controllers to set deadtimes for optimal operating efficiency.

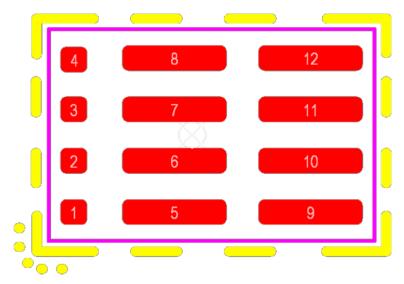

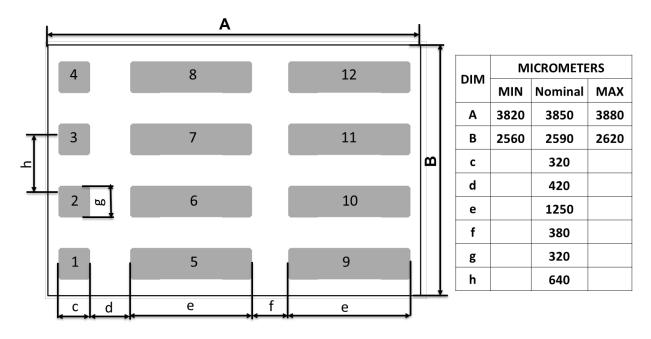

## Pinout Description, Pad View

| Pin#            | Pin Name          | Pin<br>Type | Description                                                                                                                                                           |

|-----------------|-------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1               | V <sub>BOOT</sub> | S           | Floating bootstrap power supply referenced to SW, connect an external bypass capacitor from $V_{BOOT}$ to SW                                                          |

| 2               | V <sub>DD</sub>   | S           | Operating power supply referenced to GND, connect an external bypass capacitor from V <sub>DD</sub> to GND                                                            |

| 3               | HS <sub>in</sub>  | S           | High side PWM logic input, level referenced to GND                                                                                                                    |

| 4               | LS <sub>in</sub>  | S           | Low side PWM logic input, level referenced to GND                                                                                                                     |

| 5, 9            | VIN               | Р           | Input bus voltage. Connected to high side eGaN FET drain terminal.                                                                                                    |

| 6, 7,<br>10, 11 | SW                | Р           | Output switching node. Connected to output of eGaN half-<br>bridge power stage. The floating bootstrap power supply,<br>V <sub>BOOT</sub> , is also referenced to SW. |

| 8, 12           | GND               | Р           | Power ground. Connected to low side eGaN FET source terminal. The operating power supply, V <sub>DD</sub> , is also referenced to GND.                                |

Pin Type : P=Power, S=Signal and Supply

### **Absolute Maximum Ratings**

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur and device reliability may be affected. All voltage parameters are absolute voltages referenced to GND unless indicated otherwise.

| Symbol                              | Parameter                                                 | Min  | Max  | Units |

|-------------------------------------|-----------------------------------------------------------|------|------|-------|

| V <sub>IN</sub>                     | Input Voltage (VIN to GND)                                |      | 70   | V     |

| V <sub>SW(continuous)</sub>         | Output Switching Node (SW to GND), Continuous             |      | 70   | V     |

| V <sub>SW(pulse50ns)</sub>          | Output Switching Node (SW to GND), PW<50ns <sup>(3)</sup> | -2.5 | 72.5 | V     |

| V <sub>SW(pulse2ns)</sub>           | Output Switching Node (SW to GND), PW<2ns (4)             | -10  | 80   | V     |

| V <sub>DD</sub>                     | Low Side Supply Voltage (V <sub>DD</sub> to GND)          |      | 14   | V     |

| V <sub>BOOT</sub> - V <sub>SW</sub> | High Side Supply Voltage (VBOOT to SW)                    |      | 14   | V     |

| HS <sub>in</sub>                    | High Side Logic Input (HS <sub>in</sub> to GND)           |      | 5.5  | V     |

| LS <sub>in</sub>                    | Low Side Logic Input (LS <sub>in</sub> to GND)            |      | 5.5  | V     |

| TJ                                  | Junction Temperature                                      |      | 150  | C     |

| T <sub>STG</sub>                    | Storage Temperature                                       | -55  | 150  | C     |

### **ESD Ratings**

| Symbol | Parameter                                | Min     | Max | Units |

|--------|------------------------------------------|---------|-----|-------|

| HBM    | Human-body model (JEDEC JS-001)          | +/-1000 |     | V     |

| CDM    | Charged-device model (JEDEC JESD22-C101) | +/-500  |     | V     |

## **Thermal Characteristics**

$R_{\theta JA}$  is determined with the device mounted on 1 in<sup>2</sup> of copper pad, single layer 2 oz copper on FR4 board.

| Symbol           | Parameter                               | Тур  | Units |

|------------------|-----------------------------------------|------|-------|

| R <sub>θJC</sub> | Thermal Resistance, Junction to Case    | 0.47 | °C/W  |

| R <sub>θJB</sub> | Thermal Resistance, Junction to Board   | 3    | °C/W  |

| R <sub>θJA</sub> | Thermal Resistance, Junction to Ambient | 46   | °C/W  |

## **Recommended Operating Conditions**

For proper operation the device should be used within the recommended conditions. All voltage parameters are absolute voltages referenced to GND unless indicated otherwise.

| Symbol                              | Symbol Parameter                                 |     | Тур | Max              | Units |

|-------------------------------------|--------------------------------------------------|-----|-----|------------------|-------|

| V <sub>IN</sub>                     | Input Voltage (VIN to GND)                       | 0   |     | 60               | V     |

| V <sub>DD</sub>                     | Low Side Supply Voltage (V <sub>DD</sub> to GND) | 11  | 12  | 13               | V     |

| V <sub>BOOT</sub> - V <sub>SW</sub> | High Side Supply Voltage (VBOOT to VSW)          | 11  | 12  | 13               | V     |

| HS <sub>in</sub>                    | High Side Logic Input (HS <sub>in</sub> to GND)  | 0   |     | 5 <sup>(5)</sup> | V     |

| LS <sub>in</sub>                    | Low Side Logic Input (LS <sub>in</sub> to GND)   | 0   |     | 5 <sup>(5)</sup> | V     |

| Tj                                  | Operating Junction Temperature                   | -40 |     | 125              | °C    |

### **Electrical Characteristics**

Nominal  $V_{IN} = 48 \text{ V}$ ,  $V_{DD} = 12 \text{ V}$  and  $(V_{BOOT} - V_{SW}) = 12 \text{ V}$ . All typical ratings are specified at  $T_A = 25^{\circ}$ C. Min and max ratings are specified over operating  $T_j$  range of -40C° to 125°C unless otherwise indicated.

| Symbol                    | Parameter                                                    | Test Conditions                                                       | Min          | Тур          | Max          | Units |

|---------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------|--------------|--------------|--------------|-------|

| Operating P               | ower Supply                                                  |                                                                       |              |              |              |       |

| IDDQ                      | Off State Total Quiescent Current                            | HS <sub>in</sub> & LS <sub>in</sub> = OFF, V <sub>DD</sub> =12V       |              | 22           |              | mA    |

| I <sub>DD_1MHz</sub>      | Total Operating Current @1MHz                                | PWM=1MHz, 50% On-Time                                                 |              | 29           |              | mA    |

| I <sub>DD_3MHz</sub>      | Total Operating Current @3MHz                                | PWM=3MHz, 50% On-Time                                                 |              | 42           |              | mA    |

| Bootstrap Pov             | wer Supply                                                   | ·                                                                     | •            |              |              |       |

| I <sub>BOOTQ</sub>        | Off State Bootstrap Supply Current                           | $HS_{in} = OFF$ , $(V_{BOOT} - V_{SW}) = 12V$                         |              | 8            |              | mA    |

| IBOOT_1MHz                | Bootstrap Supply Current @1MHz                               | HS PWM=1MHz, 50% On-Time                                              |              | 13           |              | mA    |

| BOOT_3MHz                 | Bootstrap Supply Current @3MHz                               | HS PWM=3MHz, 50% On-Time                                              |              | 20           |              | mA    |

| V <sub>SYNC_BOOT</sub>    | Sync Boot Generated (V <sub>BOOT</sub> -V <sub>SW</sub> )    | I <sub>SYNC_BOOT</sub> = 20mA                                         |              | 11.5         |              | V     |

| Undervoltage              | Lockout                                                      | ·                                                                     | •            |              |              |       |

| V <sub>DD (UVLO+)</sub>   | UVLO Trip Level V <sub>DD</sub> Rising                       | LS <sub>in</sub> = ON, V <sub>DD</sub> Ramps Up                       |              | 7.50         |              | V     |

| V <sub>DD (HYST)</sub>    | UVLO V <sub>DD</sub> Falling Hysteresis                      | LS <sub>in</sub> = ON, V <sub>DD</sub> Ramps Down                     |              | 0.75         |              | V     |

| VBOOT (UVLO+)             | UVLO Trip Level (V <sub>BOOT</sub> -V <sub>SW</sub> ) Rising | HS <sub>in</sub> = ON, V <sub>BOOT</sub> Ramps Up                     |              | 7.25         |              | V     |

| VBOOT (HYST)              | UVLO (VBOOT-VSW) Falling Hysteresis                          | HS <sub>in</sub> = ON, V <sub>BOOT</sub> Ramps Down                   |              | 0.75         |              | V     |

| Logic Input Pi            | ns                                                           | ·                                                                     |              |              |              |       |

| V <sub>IH</sub>           | High-level Logic Threshold                                   | HS <sub>in</sub> , LS <sub>in</sub> Rising                            | 2.4          |              |              | V     |

| V <sub>IL</sub>           | Low-level Logic Threshold                                    | HS <sub>in</sub> , LS <sub>in</sub> Falling                           |              |              | 0.8          | V     |

| V <sub>IHyst</sub>        | Logic Threshold Hysteresis                                   | $V_{IH}$ Rising – $V_{IL}$ Falling                                    |              | 0.5          |              | V     |

| R <sub>in</sub>           | Input Pulldown Resistance                                    | HS <sub>in</sub> , LS <sub>in</sub> = 5V                              |              | 5            |              | kΩ    |

| <b>Output Powe</b>        | r FETs                                                       | ·                                                                     |              |              |              |       |

| R <sub>DS(on)_HS</sub>    | High Side FET R <sub>DS(on)</sub>                            | I <sub>DS</sub> = +/-10A, HS <sub>in</sub> =ON, LS <sub>in</sub> =OFF |              | 8.5          |              | mΩ    |

| V <sub>HS_DS_Clamp</sub>  | High Side 3 <sup>rd</sup> Quadrant Clamp                     | I <sub>DS</sub> = -10A, HS <sub>in</sub> & LS <sub>in</sub> = OFF     |              | -2           |              | V     |

| R <sub>DS(on)_LS</sub>    | Low Side FET R <sub>DS(on)</sub>                             | I <sub>DS</sub> = +/-10A, LS <sub>in</sub> =ON, HS <sub>in</sub> =OFF |              | 8.5          |              | mΩ    |

| VLS_DS_Clamp              | Low Side 3 <sup>rd</sup> Quadrant Clamp                      | I <sub>DS</sub> = -10A, HS <sub>in</sub> & LS <sub>in</sub> = OFF     |              | -2           |              | V     |

| ILEAK_VIN-SW              | Leakage Current VIN to SW                                    | HS <sub>in</sub> = OFF, VIN = 80V, SW = 0V                            |              |              | 100          | μA    |

| LEAK_SW-GND               | Leakage Current SW to GND                                    | LS <sub>in</sub> = OFF, SW = 80V                                      |              |              | 100          | μA    |

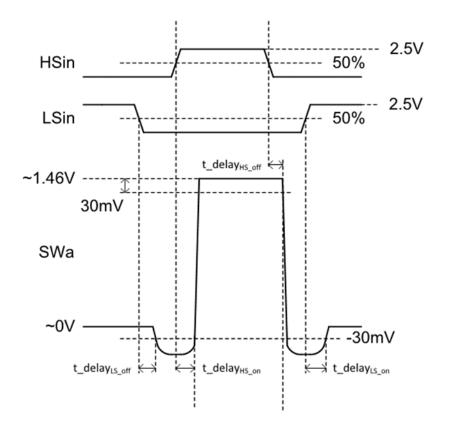

| Dynamic Char              | acteristics (Logic Input to Outpu                            | ut Switching Node) (see Figure 1                                      | . Timing Dia | agram and Te | est Circuit) |       |

| t_delay <sub>HS_on</sub>  | High-Side On Propagation Delay                               | SW = 0V and HS FET Turn-On                                            |              | 20           |              | ns    |

| t_delay <sub>LS_on</sub>  | Low-Side On Propagation Delay                                | SW = 60V and LS FET Turn-On                                           |              | 20           |              | ns    |

| t_delay <sub>HS_off</sub> | High-Side Off Propagation Delay                              | SW = 60V and HS FET Turn-Off                                          |              | 20           |              | ns    |

| t_delay <sub>LS_off</sub> | Low-Side Off Proprgation Delay                               | SW = 0V and LS FET Turn-Off                                           |              | 20           |              | ns    |

| t_match <sub>on</sub>     | Delay Matching LS <sub>off</sub> to HS <sub>on</sub>         | LS Turn-Off to HS Turn-On                                             |              | 0            |              | ns    |

| t_match <sub>Off</sub>    | Delay Matching HS <sub>off</sub> to LS <sub>on</sub>         | HS Turn-Off to LS Turn-On                                             |              | 0            |              | ns    |

| PW min                    | Minimum Input Pulse-Width                                    | 50% to 50% Width                                                      |              | 20           |              | ns    |

Figure 1a. Test Circuit for Dynamic Characteristics

Figure 1b. Logic Input to Output Switching Node Timing Diagram

| V <sub>DD</sub>                                                             | V <sub>BOOT</sub> -V <sub>SW</sub>                                              | HSin | LSin | HS FET | LS FET            |

|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------|------|------|--------|-------------------|

| <uvlo< td=""><td>-</td><td>-</td><td>-</td><td>OFF</td><td>OFF</td></uvlo<> | -                                                                               | -    | -    | OFF    | OFF               |

| >UVLO                                                                       | <uvlo< td=""><td>-</td><td>0</td><td>OFF</td><td>OFF</td></uvlo<>               | -    | 0    | OFF    | OFF               |

| >UVLO                                                                       | <uvlo< td=""><td>-</td><td>1</td><td>OFF</td><td>ON <sup>(5)</sup></td></uvlo<> | -    | 1    | OFF    | ON <sup>(5)</sup> |

|                                                                             |                                                                                 | 0    | 0    | OFF    | OFF               |

|                                                                             | VLO                                                                             | 0    | 1    | OFF    | ON                |

|                                                                             | VLO                                                                             | 1    | 0    | ON     | OFF               |

|                                                                             |                                                                                 | 1    | 1    | BOTH   | ON <sup>(6)</sup> |

### **Truth Table**

### Notes

<u>Note 1:</u> Output current rating is measured with Vin = 48 V,  $V_{out}$  = 12 V, PWM frequency = 1 MHz, PCB mounted using EPC90120 Eval Board, 800 LFM airflow, operating at ambient temperature of 25°C. Case temperature is measured on top of the die, with emissivity adjusted to 0.95, not to exceed 125°C at thermal equilibrium. Actual maximum output current depends on power dissipation, maximum allowed junction temperature, thermal management method and the operating environment.

<u>Note 2:</u> Operating PWM switching frequency range is a function of power dissipation, maximum allowed junction temperature and minimum duty cycle. Running at higher PWM switching frequency lowers the maximum output current rating.

<u>Note 3:</u> The output switching node (SW) is clamped above VIN by the HS FET or below GND by the LS FET at their respective source drain voltage in the 3<sup>rd</sup> quadrant. This is an operating condition when both HS and LS FETs are in the off states during the deadtime period which is set by the application circuit with typical value of 10 ns. The Absolute Minimum Rating is determined by LS FET 3<sup>rd</sup> quadrant clamp voltage above VIN. The time duration that the device can stay in the negative clamp voltage region is subjected to the amount of load current and maximum allowed junction temperature.

<u>Note 4:</u> During HS FET or LS FET turn-on transitions with hard switching conditions, the fast di/dt of the HS FET or LS FET coupled with the power loop inductance ( $V_{peak} = L_{power loop} * di/dt$ ) would cause a transient over-voltage spike above VIN or below GND. The Absolute Minimum Rating is amount of peak voltage spike, caused by LS FET di/dt, below GND for less than 2ns pulse duration. Conversely the Absolute Maximum Rating is amount of peak voltage spike, caused by HS FET di/dt, above VIN, for less than 2ns pulse duration.

<u>Note 5:</u> For logic input voltage above 5 V, a 5 k $\Omega$  resistor in series should be inserted to limit the input current into the logic input pins HS<sub>in</sub> and LS<sub>in</sub>.

<u>Note 6:</u> LS<sub>in</sub> commands LS FET to turn-on to charge bootstrap supply through sync boot

<u>Note 7:</u> Internal logic follows HS<sub>in</sub>, LS<sub>in</sub> respectively and does not lock-out when both HS and LS FETs are commanded to turn on together. Users need to implement shoot through prevention logic depending on application topology. Deadtime insertion circuit must not generate overlapping pulse widths shorter than minimum pulse width specifications, that might cause both HS and LS FETs to turn-on together.

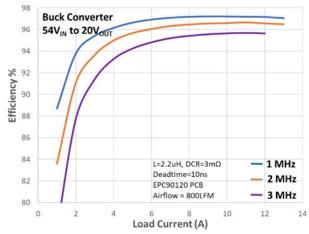

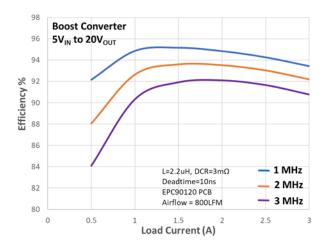

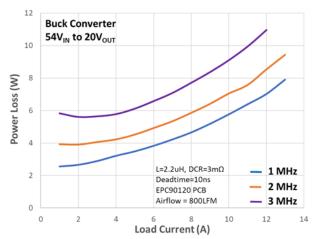

**Typical Performance Characteristics**

Figure 2a. 48VIN-12VOUT Efficiency vs. Load Current

Figure 3a. 54VIN-20VOUT Efficiency vs. Load Current

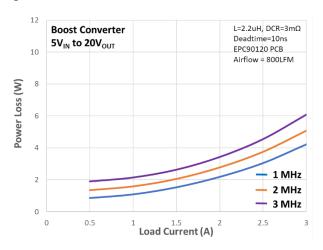

Figure 4a. 5VIN-20VOUT Efficiency vs. Load Current

Figure 2b. 48VIN-12VOUT Power Loss vs. Load Current

Figure 3b. 54VIN-20VOUT Power Loss vs. Load Current

Figure 4b. 5VIN-20VOUT Power Loss vs. Load Current

### **Application Information**

#### Layout Guidelines

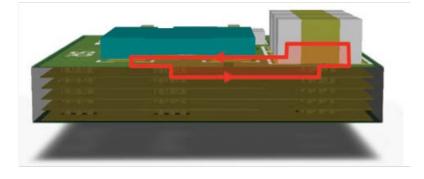

Monolithic integration of the half-bridge output FETs as well as their associated gate drivers significantly reduce parasitic common source inductance (CSI) and gate drive loop inductance. What remains is the high frequency power loop inductance that is controlled by the PCB layout of the DC input capacitors in relationship to the current flow direction through the pin configuration and layout geometry of the output FETs in the half-bridge power stage. Experimental data confirmed that the efficiency curves can be impacted by as much as 4% depending on the power loop inductance varying from 0.4 nH to 3 nH [1]. Another negative effect of excessive power loop inductance is the over-voltage spike at the SW node. Decreasing the high frequency

loop inductance results in lower voltage overshoot, increased input voltage capability, and reduced EMI.

A recommended layout technique for the EPC2152 device is shown in Figure 5a [2]. This PCB layout uses the concept of creating a low-profile magnetic field cancellation loop in a multilayer PCB as shown in Figure 5b. The design utilizes the first inner layer connected to the GND plane as a power loop return path. Separated only by a thin substrate, the top layer power loop and first inner layer current return path directly underneath generate opposing magnetic fields with induced currents that have The opposite direction. result is а magnetic fields that cancellation of translates into a reduction in parasitic inductance.

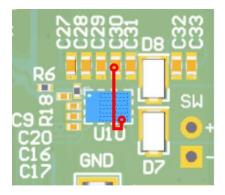

Figure 5a: Top View

Figure 5b: Side View

#### Figure 5: Recommended layout technique to minimize power loop inductance

#### Adjusting Switching Speed

The EPC2152 device is designed to switch in less than 1 ns to minimize output FET switching losses. Using the recommended layout guidelines, shown in Figure 5 can minimize the high frequency loop inductance to less than 0.2 nH as demonstrated in EPC90120 development board [2]. However, the fast di/dt at turn-on can induce a higher than acceptable overvoltage spike at the SW node. Designers can reduce the rise time of the SW node by inserting an optional R<sub>BOOT</sub> resistor in series with the bootstrap bypass capacitor  $C_{BOOT}$  as illustrated in Test Circuit for Dynamic Characteristics (Figure 1a). This helps to reduce over-voltage spike in the positive going edge during hard switching conditions. To reduce the negative transient voltage

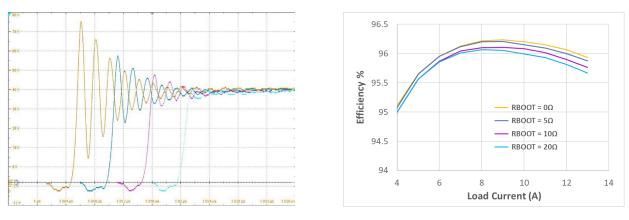

spike below ground for negative going edge during hard switching conditions, designers can insert optional RDD resistor in series with the bias supply bypass capacitor C<sub>DRV</sub> also shown in the same Test Circuit (Figure 1a). The switching waveforms using different values of R<sub>BOOT</sub> on rising SW node are shown in Figure 6a under the operating conditions of  $V_{IN}$  = 48 V,  $V_{OUT}$  = 12 V and  $I_{OUT}$  = 10 A. Increasing R<sub>BOOT</sub> value helps to decrease switching speed, lower over-voltage spike and reduce ringing. The power loss penalty is only 0.2% at  $I_{OUT} = 10$  A with  $R_{BOOT}$  increasing from 0  $\Omega$  to 20  $\Omega$  as shown in Figure 6b. The associated peak over-rail voltage spike above V<sub>IN</sub> of 48 V ranges from 35V over with  $R_{BOOT} = 0 \Omega$  to only 8 V over at  $R_{BOOT} = 10 \Omega$ (Figure 6a). At  $R_{BOOT} = 20 \Omega$  the waveform is critically damped.

Figure 6: Impact of  $R_{BOOT}$  value on SW node switching characteristics, over-rail voltage spike and efficency for a buck converter operating from  $V_{IN}$  = 48 V,  $V_{OUT}$  = 12 V.

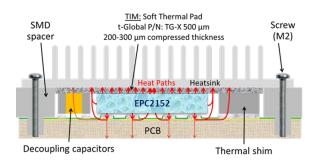

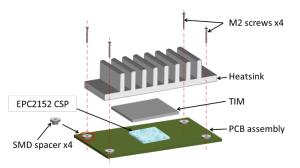

#### <u>Top Side Cooling</u>

The chip-scale packaging (CSP) of the EPC2152 device offers the possibility of sixsided cooling, with effective heat extraction from the bottom, top, and sides of the die. Designers can opt for using the device in still air or with airflow by simply using the underlying PCB for heat dissipation. By mounting the device on a multi-layer PCB with 2 oz. copper using the recommended layout guideline as demonstrated in the EPC90120 development board [2], the device can operate continuously in still air at an ambient temperature of 25C under the operating conditions of  $V_{IN}$  = 48 V,  $V_{OUT}$  = 12 V,  $I_{OUT} = 10$  A while switching the synchronous buck converter at 1MHz.

Figure 7a: Cross-Sectional View

The attachment of a heatsink to the device can increase power throughput. Figure 7 shows a simple method to attach a heatsink to the EPC2152 CSP device. The approach makes use of low profile threaded mechanical SMD spacers (Würth Elektronik Part Number 9774010243R) that are simply soldered into the PCB. The spacer sets the heatsink height above the board to 1 mm and when a compliant thermal interface material is applied to the backside of the device, provides the correct compression and thermal interface impedance. The heatsink can be mechanically fastened by just inserting screws through the threads of the SMD spacers. An increase of output current capability up to +60% has been demonstrated using this method [3].

#### Figure 7: Recommended approach to attach a heatsink to the backside of the device

#### EPC90120 Development Board

A quick way to evaluate the EPC2152 device in actual application is the EPC90120 development board [2] that measures 50mm x 50mm. The board configures the EPC2152 to operate as either buck or boost converter with all critical components in place. The layout supports optimal switching performance using the recommended layout guideline. There are also various probe points to facilitate simple waveform measurement and efficiency calculation. A block diagram of the circuit is shown in Figure 8a and a picture of the board is shown in Figure 8b.

Figure 8a: Block Diagram Schematic

Figure 8: EPC90120 development board

Figure 8b: Top Side Photo

### References

[1] EPC White Paper WP010 - Optimizing PCB Layout. This white paper explores the optimization of PCB layout for an eGaN FET based point of load (POL) buck converter, comparing the conventional designs and proposing a new optimal layout to further reduce parasitic.

WP010 Download Link: <u>bit.ly/EPCWP010</u>.

[2] EPC90120 Development Board Quick Start Guide. This QSG guide describes the EPC90120 development board in details containing the Bill of Materials (BOM), the circuit schematic as well as quick start procedure for buck and boost converter configurations. The layout uses the optimized guideline and users can download the Gerber files from EPC website.

EPC90120 QSG Download Link: <u>bit.ly/EPC90120</u>.

EPC90120 Gerber File Download link: <u>bit.ly/EPC90120Gerbers</u>.

[3] EPC How2AppNote 012 - How to Get More Power Out of an eGaN Converter with a Heatsink.

How2AppNote 012 Download link: <a href="https://bit.ly/EPCH2AN012">bit.ly/EPCH2AN012</a>

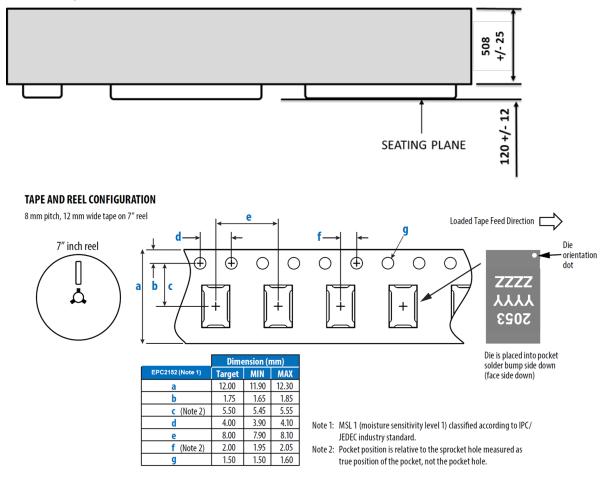

### **Packaging Information**

DIE OUTLINE, Pad View

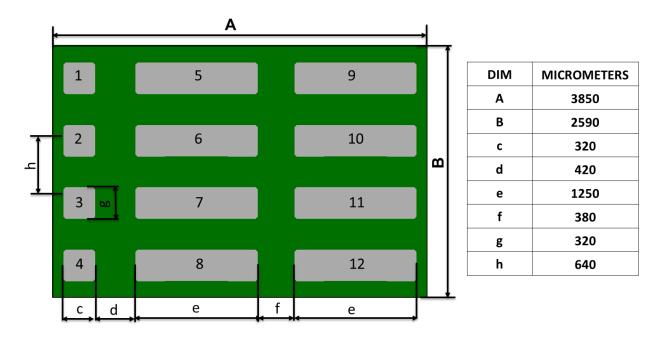

#### **RECOMMENDED LAND PATTERN**

(measurements in µm, The land pattern is solder mask defined)

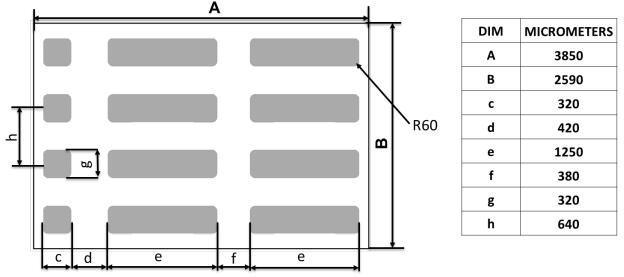

#### RECOMMENDED STENCIL DRAWING (measurements in µm)

Recommended stencil should be 4mil (100  $\mu m$ ) thick, laser cut stainless steel, opening per drawing. The corner has a radius of R60

Intended for use with SAC305 Type 4 solder, reference 88.5% metals content.

Additional assembly resources are available at epc-co.com/epc/DesignSupport/AssemblyBasics.aspx

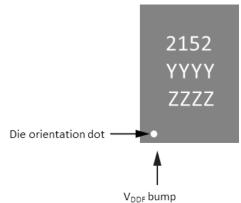

#### **DIE MARKINGS**

| Part           | Laser Markings           |                               |                               |  |  |

|----------------|--------------------------|-------------------------------|-------------------------------|--|--|

| Part<br>Number | Part #<br>Marking Line 1 | Lot_DateCode<br>Marking Line2 | Lot_DateCode<br>Marking Line3 |  |  |

| EPC2152        | 2152                     | YYYY                          | ZZZZ                          |  |  |

#### **SIDE VIEW,** not to scale

Efficient Power Conversion Corporation (EPC) reserves the right to make changes without further notice to any products herein. Preliminary specification sheet contains informaton regarding a product EPC is considering for production release. EPC does not assume any liability arising out of the application or use of any product or circuit described herin; neither does it convey any license under its patent rights, nor the rights of other.

eGaN<sup>\*</sup> is a registered trademark of Efficient Power Conversion Corporation. EPC Patents: <u>http://epc-co.com/epc/AboutEPC/Patents.aspx</u>

Revision 1.3 July 20, 2020

## Addendum for EPC21521 – Optimized Motor Drive Version

### **Key Parameters**

| Rated Load Current (100kHz) (1)              | 10 A <sub>RMS</sub> |

|----------------------------------------------|---------------------|

| Operating PWM Frequency Range <sup>(2)</sup> | 1 MHz               |

| Operating Input Voltage Range                | 60 V                |

| Bias Supply Voltage                          | 12 V                |

Output Current and PWM Frequency Ratings are functions of Operating Conditions. See Notes 1 & 2.

### Features

- Designed for Motor Drive Inverter Applications

- Separate and independent high side and low side control inputs

- Input signal compatible with 3.3 V or 5 V CMOS logic levels

- 20 ns minimum input pulse width

- 20 ns delay time input to output

- 20 V/ns switching time at output node

- Robust level shifter operating from negative transient conditions

- Immunity to transients within driven phase and from other phases

- Synchronous charging for high side bootstrap supply

- Regulated gate drive buffer output to drive output FETs at safe operating level

- Undervoltage lockout for high side and low side power supplies

- LGA Chip Scale Package

## Applications

• Single Phase and Three Phase Motor Drive Inverter

## **Typical Application**

3-Phase Motor Drive Inverter

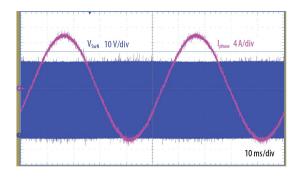

## Performance Curves

Switch-node and phase current waveforms of the motor drive measured in the modulation frequency timescale when operating from a 48 V DC supply and delivering 10  $A_{\rm RMS}$  per phase into the motor.

# Die Photo

3.85 mm x 2.59 mm x 0.63 mm