### IO-Link communication master transceiver IC

#### **Features**

- Supply voltage from 18 V to 32.5 V

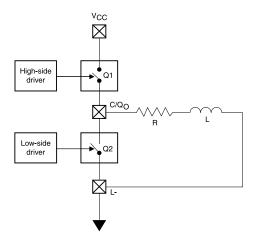

- Programmable output stages: high-side, low-side or push-pull (< 2 Ω)</li>

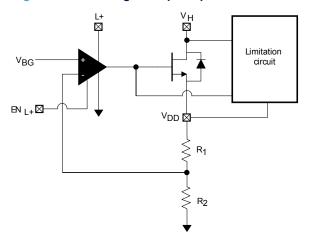

- Up to 500 mA L+ protected high-side driver

- COM1, COM2 and COM3 mode supported

- Additional IEC61131-2 type 1 input

- Short-circuit and overcurrent output protection through current limitation and programmable cut-off current

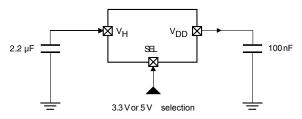

- 3.3 V / 5 V, 50 mA linear regulator

- 5 mA IO-Link digital input

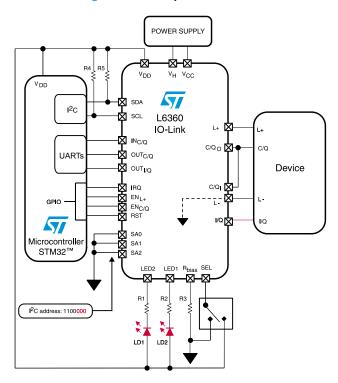

- Fast mode I<sup>2</sup>C for IC control, configuration and diagnostic

- · Diagnostic dual LED sequence generator and driver

- 5 V and 3.3 V compatible I/Os

- Overvoltage protection (> 36 V)

- Overtemperature protection

- ESD protection

- Miniaturized VFQFPN 26L (3.5x5x1 mm) package

### **Applications**

- · Industrial sensors

- · Factory automation

- · Process control

# Product status link

| Product summary |                            |  |  |  |  |

|-----------------|----------------------------|--|--|--|--|

| Order code      | L6360TR                    |  |  |  |  |

| Package         | VFQFPN 26L<br>(3.5x5x1 mm) |  |  |  |  |

| Packing         | Tape and reel              |  |  |  |  |

### **Description**

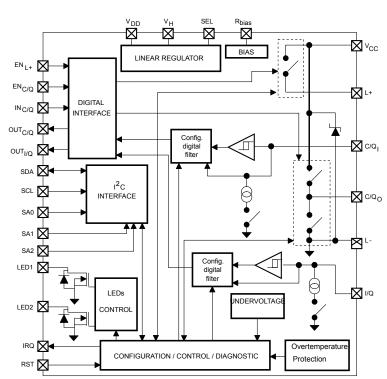

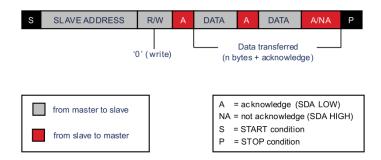

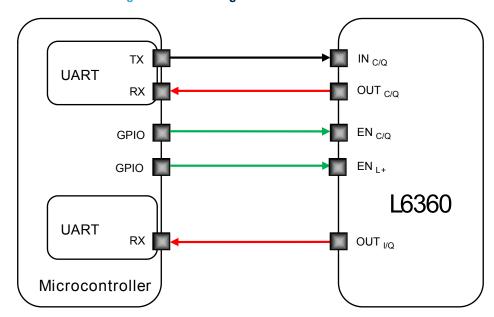

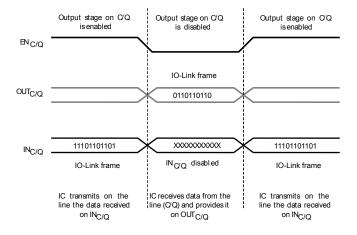

The L6360 is a monolithic IO-Link master port compliant with PHY2 (3-wire) supporting COM1 (4.8 kbaud), COM2 (38.4 kbaud) and COM3 (230.4 kbaud) modes. The C/Q<sub>O</sub> output stage is programmable: high-side, low-side or push-pull; also cut-off current, cut-off current delay time, and restart delay are programmable. Cut-off current and cut-off current delay time, combined with thermal shutdown and automatic restart, protect the device against overload and short-circuit. C/Qo and L+ output stages are able to drive resistive, inductive and capacitive loads. Inductive loads up to 10 mJ can be driven. Supply voltage is monitored and low voltage conditions are detected. The L6360 transfers, through the PHY2(C/Q<sub>O</sub> pin), data received from a host microcontroller through the USART (IN C/Q<sub>O</sub> pin), or to the USART (OUT C/Q<sub>I</sub> pin) data received from PHY2 (C/Q<sub>I</sub> pin). To enable full IC control, configuration and monitoring (i.e. fault conditions stored in the status register), the communication between the system microcontroller and the L6360 is based on a fast mode 2-wire I<sup>2</sup>C. The L6360 has nine registers to manage the programmable parameters and the status of the IC. Monitored fault conditions are: L+ line, overtemperature, C/Q overload, linear regulator undervoltage, and parity check. Internal LED driver circuitries, in open drain configuration, provide two programmable sequences to drive two LEDs.

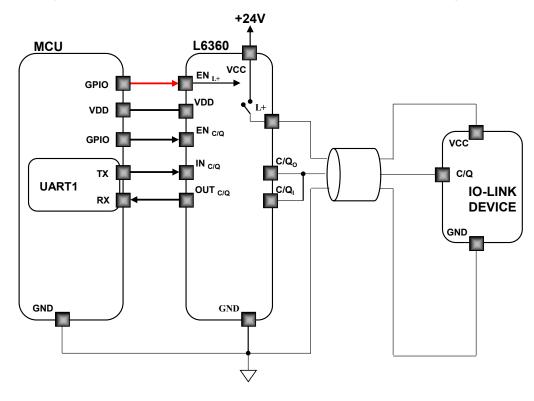

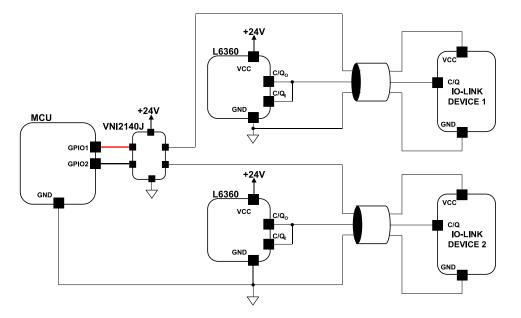

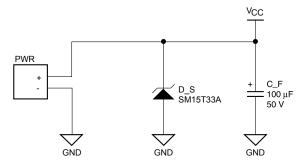

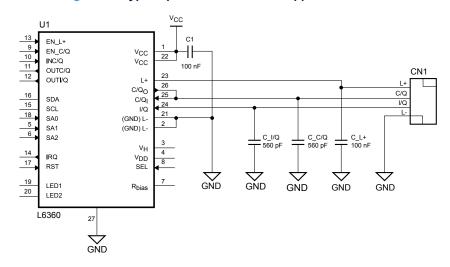

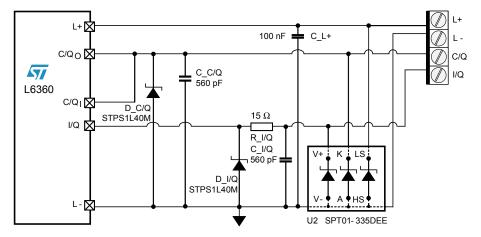

## 1 Block diagram

Figure 1. Block diagram

DS8900 - Rev 7 page 2/63

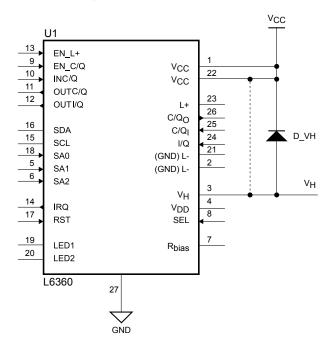

## 2 Pin configuration

C/QO C/QI I/Q L+ VCC  $v_{\text{CC}}$ LED2 LED1  $V_{\mathsf{H}}$ SA0  $V_{\text{DD}}$ SA1 RST SDA SA2 SCL R<sub>bias</sub> SEL IRQ 11 12 13 EN<sub>C/Q</sub> IN<sub>C/Q</sub> OUT<sub>C/Q</sub> OUT<sub>I/Q</sub> EN<sub>L+</sub>

Figure 2. Pin connection (top through view)

**Table 1. Pin description**

| Number | Name               | Function                                                                                  | Туре         |

|--------|--------------------|-------------------------------------------------------------------------------------------|--------------|

| 1      | V <sub>CC</sub>    | IC power supply                                                                           | Supply       |

| 2      | L-                 | L- line (IC ground)                                                                       | Supply       |

| 3      | V <sub>H</sub>     | Linear regulator supply voltage                                                           | Supply       |

| 4      | V <sub>DD</sub>    | Linear regulator output voltage                                                           | Output       |

| 5      | SA1                | Serial address 1                                                                          | Input        |

| 6      | SA2                | Serial address 2                                                                          | Input        |

| 7      | R <sub>bias</sub>  | External resistor for internal reference generation                                       | Input        |

| 8      | SEL                | Linear regulator 3.3 V/5 V voltage selection. Output is 5 V when SEL pin is pulled to GND | Input        |

| 9      | EN <sub>C/Q</sub>  | C/Q output enable                                                                         | Input        |

| 10     | IN <sub>C/Q</sub>  | C/Q channel logic input                                                                   | Input        |

| 11     | OUT <sub>C/Q</sub> | C/Q channel logic output                                                                  | Output       |

| 12     | OUT <sub>I/Q</sub> | I/Q channel logic output                                                                  | Output       |

| 13     | EN <sub>L+</sub>   | L+ switch enable. When EN <sub>L+</sub> is high the switch is closed                      | Input        |

| 14     | IRQ                | Interrupt request signal (open drain)                                                     | Output       |

| 15     | SCL                | Serial clock line                                                                         | Input        |

| 16     | SDA                | Serial data line                                                                          | Input/output |

| 17     | RST                | Reset - active low                                                                        | Input        |

| 18     | SA0                | Serial address 0                                                                          | Input        |

| 19     | LED1               | Status/diagnostic LED (open drain)                                                        | Output       |

DS8900 - Rev 7 page 3/63

| Number | Name             | Function                           | Туре   |

|--------|------------------|------------------------------------|--------|

| 20     | LED2             | Status/diagnostic LED (open drain) | Output |

| 21     | L-               | L- line (IC ground)                | Supply |

| 22     | V <sub>CC</sub>  | IC power supply                    | Supply |

| 23     | L+               | L+ line                            | Supply |

| 24     | I/Q              | I/Q channel line                   | Input  |

| 25     | C/Q <sub>I</sub> | Transceiver (C/Q channel) line     | Input  |

| 26     | C/Q <sub>O</sub> | Transceiver (C/Q channel) line     | Output |

DS8900 - Rev 7 page 4/63

## 3 Absolute maximum ratings

Table 2. Absolute maximum ratings

| Symbol                                                                                          | Parameter                                                                 | Value                         | Unit |

|-------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-------------------------------|------|

| V <sub>CC</sub>                                                                                 | Supply voltage                                                            | V <sub>CLAMP</sub>            |      |

| V <sub>SEL</sub>                                                                                | Linear regulator selection pin voltage                                    | -0.3 to 4                     |      |

| V <sub>DD</sub>                                                                                 | V <sub>DD</sub> Linear regulator output voltage                           |                               |      |

| V <sub>H</sub>                                                                                  | V <sub>H</sub> Linear regulator input voltage                             |                               |      |

| V <sub>SDA</sub> , V <sub>SCL</sub> , V <sub>SA0</sub> ,<br>V <sub>SA1</sub> , V <sub>SA2</sub> | I <sup>2</sup> C voltage                                                  | -0.3 to V <sub>DD</sub> + 0.3 |      |

| V <sub>LED1,2</sub>                                                                             | LED1,2 voltage                                                            | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| $V_{C/QI}, V_{I/Q}$                                                                             | C/Q <sub>I</sub> , I/Q voltage                                            | -0.3 to V <sub>CC</sub> + 0.3 |      |

| V <sub>RST</sub>                                                                                | Reset voltage                                                             | -0.3 to V <sub>DD</sub> + 0.3 |      |

| V <sub>IRQ</sub>                                                                                | IRQ voltage                                                               | -0.3 to V <sub>DD</sub> + 0.3 |      |

| V <sub>Rbias</sub>                                                                              | External precision resistance voltage                                     | -03 to 4                      |      |

| V <sub>ESD</sub>                                                                                | Electrostatic discharge (human body model)                                | 2000                          |      |

| I <sub>CLAMP</sub>                                                                              | Current through $V_{CLAMP}$ in surge test (1 kV, 500 $\Omega$ ) condition | 2                             | А    |

| I <sub>C/QO</sub> , I <sub>L+</sub>                                                             | C/Q <sub>O</sub> , L+ current (continuous)                                | Internally limited            | Α    |

| IOUT <sub>C/Q</sub> , IOUT <sub>I/Q</sub>                                                       | $OUT_{C/Q},OUT_{I/Q}$ output current                                      | ±5                            | mA   |

| I <sub>SDA</sub>                                                                                | I <sup>2</sup> C transmission data current (open drain pin)               | 10                            | mA   |

| I <sub>RQ</sub>                                                                                 | Interrupt request signal current                                          | 2 <sup>(1)</sup>              | А    |

| I <sub>LED1,2</sub>                                                                             | LED1, 2 current                                                           | 10                            | mA   |

| E <sub>load</sub>                                                                               | L+ demagnetization energy                                                 | 10                            | mJ   |

| P <sub>TOT</sub>                                                                                | Power dissipation at T <sub>C</sub> = 25 °C                               | Internally limited            | W    |

| P <sub>LR</sub>                                                                                 | Linear regulator power dissipation 200                                    |                               | mW   |

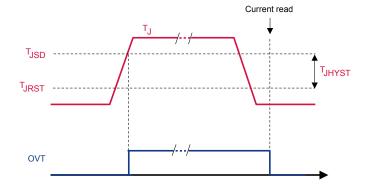

| TJ                                                                                              | Junction operating temperature                                            | Internally limited            | °C   |

| T <sub>STG</sub>                                                                                | Storage temperature range                                                 | -55 to 150                    | C    |

<sup>1.</sup> Peak value during fast transient test only.

DS8900 - Rev 7 page 5/63

## 4 Recommended operating conditions

Table 3. Recommended operating conditions

| Symbol            | Parameter                      | Min.  | Тур. | Max.            | Unit |

|-------------------|--------------------------------|-------|------|-----------------|------|

| V <sub>CC</sub>   | Supply voltage                 | 18    |      | 32.5            | V    |

| V <sub>H</sub>    | Linear regulator input voltage | 7     |      | V <sub>CC</sub> | V    |

| f <sub>SCL</sub>  | SCL clock frequency            |       |      | 400             | kHz  |

| R <sub>bias</sub> | Precision resistance           | -0.1% | 124  | 0.1%            | kΩ   |

| TJ                | Junction temperature           | -40   |      | 125             | °C   |

Table 4. Thermal data

| Symbol                | Parameter                                              | Тур. | Unit |

|-----------------------|--------------------------------------------------------|------|------|

| R <sub>thj-case</sub> | Thermal resistance, junction-to-case                   | 6    | °C/W |

| R <sub>thj-amb</sub>  | Thermal resistance, junction-to-ambient <sup>(1)</sup> | 50   | °C/W |

<sup>1.</sup> Mounted on FR4 PCB with 2 signal Cu layers and 2 power Cu layers interconnected through vias.

DS8900 - Rev 7 \_\_\_\_\_\_ page 6/63

## **5** Electrical characteristics

(18 V < V<sub>CC</sub> < 30 V; -40 °C < T<sub>J</sub> < 125 °C; V<sub>DD</sub> = 5 V; unless otherwise specified).

Table 5. Supply

| Symbol                | Parameter                                              | Test conditions                    | Min. | Тур. | Max. | Unit  |

|-----------------------|--------------------------------------------------------|------------------------------------|------|------|------|-------|

| V <sub>CLAMP</sub>    | Voltage clamp                                          | I = 5 mA                           | 36   |      |      | V     |

| V <sub>UV</sub>       | Undervoltage on threshold                              |                                    | 16   | 17   | 18   | V     |

| V <sub>UVH</sub>      | Undervoltage hysteresis                                |                                    | 0.3  | 1    |      | V     |

| V <sub>REGLN5H</sub>  | Linear regulator undervoltage high threshold           | SEL = L                            | 4.3  |      | 4.7  |       |

| V <sub>REGLN5L</sub>  | Linear regulator undervoltage low threshold            | SEL = L                            | 3.6  |      | 4.2  | .,    |

| V <sub>REG5HYS</sub>  | Linear regulator undervoltage hysteresis               | SEL = L                            | 0.1  |      |      | V     |

| V <sub>REGLN33H</sub> | Linear regulator undervoltage high threshold           | SEL = H                            | 2.8  |      | 3.1  |       |

| V <sub>REGLN33L</sub> | Linear regulator undervoltage low threshold            | SEL = H                            | 2.5  |      | 2.7  | V     |

| V <sub>REG33HYS</sub> | Linear regulator undervoltage hysteresis               | SEL = H                            | 0.1  |      |      | V     |

| $V_{QTHH}$            | C/Q <sub>I</sub> and I/Q upper voltage threshold       |                                    | 10.5 |      | 12.9 | V     |

| $V_{QTHL}$            | C/Q <sub>I</sub> and I/Q lower voltage threshold       |                                    | 8    |      | 11.4 | V     |

| $V_{QHY}$             | C/Q and I/Q hysteresis voltage                         |                                    | 1    |      |      | V     |

| V <sub>demag</sub>    | L+ demagnetization voltage                             | I = 5 mA                           | -8.5 | -6.5 | -4.8 | V     |

| V <sub>fHS</sub>      | C/Q high-side freewheeling diode forward voltage       | I = 10 mA                          |      | 0.5  |      | V     |

| $V_{fLS}$             | C/Q low-side freewheeling diode forward voltage        | I = 10 mA                          |      | 0.5  |      | V     |

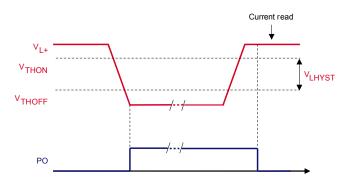

| V <sub>LTHOFF</sub>   | L+ line diagnostic lower threshold                     |                                    | 9    | 10   | 11   | V     |

| $V_{LTHY}$            | L+ line diagnostic hysteresis                          |                                    | 0.1  | 1    |      | ٧     |

| V <sub>LTHON</sub>    | L+ line diagnostic upper threshold                     |                                    | 10   | 11   | 12   | V     |

| I.                    | Curanti aumant                                         | OFF-state                          |      | 100  |      | μA    |

| I <sub>S</sub>        | Supply current                                         | ON-state V <sub>CC</sub> at 32.5 V |      | 4    |      | mA    |

| I <sub>OFFCQ</sub>    | OFF-state C/Q <sub>O</sub> current                     | $EN_{C/Q} = 0, V_{C/Q} = 0 V$      |      |      | 1    | μA    |

|                       |                                                        |                                    | 70   | 115  | 190  |       |

| I <sub>COQ</sub>      | C/Q <sub>O</sub> low- and high-side cut-off current    | Programmable                       | 150  | 220  | 300  | mA    |

| ·coq                  | or and high olds car on carroin                        | riogrammasic                       | 290  | 350  | 440  | 111/5 |

|                       |                                                        |                                    | 430  | 580  | 720  |       |

| I <sub>LIMQ</sub>     | C/Q <sub>O</sub> low- and high-side limitation current |                                    | 500  |      | 1600 | mA    |

| I <sub>OFFL</sub>     | L+ OFF-state current                                   | $EN_{L+} = 0, V_{L+} = 0 V$        | 0    |      | 200  | μA    |

| I <sub>COL</sub>      | L+ cut-off current                                     |                                    | 480  | 580  | 730  | mA    |

| I <sub>LIML</sub>     | L+ limitation current                                  |                                    | 500  |      | 1600 | mA    |

| I <sub>INC/Qi</sub>   | C/Q <sub>I</sub> pull-down current                     | Programmable                       | 5    |      | 6.5  | mA    |

| INO/QI                | ,,                                                     |                                    | 2    |      | 3.3  | mA    |

| I <sub>INI/Q</sub>    | I/Q pull-down current                                  |                                    | 2    |      | 3    | mA    |

DS8900 - Rev 7 page 7/63

| Symbol              | Parameter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Test conditions                                     | Min. | Тур.                    | Max. | Unit |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------|-------------------------|------|------|

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | I <sub>OUT</sub> = 0.2 A at T <sub>J</sub> = 25 °C  |      | 1                       |      | Ω    |

| R <sub>ONL</sub>    | L+ high-side ON-state resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | I <sub>OUT</sub> = 0.2 A at T <sub>J</sub> = 125 °C |      |                         | 2    | Ω    |

| <b>D</b>            | O/O high side ON state assistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | I <sub>OUT</sub> = 0.2 A at T <sub>J</sub> = 25 °C  |      | 1                       |      | Ω    |

| R <sub>ONCQH</sub>  | C/Q <sub>O</sub> high-side ON-state resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I <sub>OUT</sub> = 0.2 A at T <sub>J</sub> = 125 °C |      |                         | 2    | Ω    |

| Б                   | O/O Januarida ON data arabida ara                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | I <sub>OUT</sub> = 0.2 A at T <sub>J</sub> = 25 °C  |      | 0.6                     |      | Ω    |

| R <sub>ONCQL</sub>  | C/Q <sub>O</sub> low-side ON-state resistance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | I <sub>OUT</sub> = 0.2 A at T <sub>J</sub> = 125 °C |      |                         | 1.2  | Ω    |

|                     | IN to O/O proposation delection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Push-pull (CQ <sub>O</sub> rising edge)             |      | 140                     |      | ns   |

| t <sub>dINC/Q</sub> | IN <sub>C/Q</sub> to C/Q <sub>O</sub> propagation delay time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Push-pull (CQ <sub>O</sub> falling edge)            |      | 160                     |      | ns   |

|                     | EN 4.000 supporting delay fire                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Push-pull (CQ <sub>O</sub> rising edge)             |      | 110                     |      | ns   |

| t <sub>ENC/Q</sub>  | EN <sub>C/Q</sub> to C/Q <sub>O</sub> propagation delay time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Push-pull (CQ <sub>O</sub> falling edge)            |      | 225                     |      | ns   |

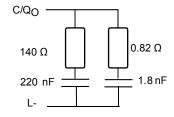

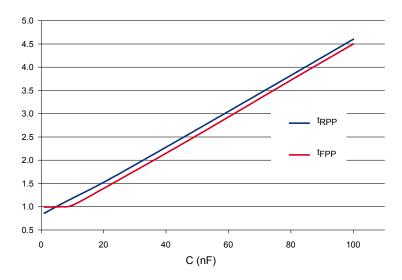

| t <sub>rPP</sub>    | C/Q rise time in push-pull configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10% to 90%                                          | 250  |                         | 860  | ns   |

| t <sub>fPP</sub>    | C/Q fall time in push-pull configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 10% to 90%                                          | 290  |                         | 860  | ns   |

| t <sub>rHS</sub>    | C/Q rise time in high-side configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                     |      | 410                     |      | ns   |

| t <sub>fHS</sub>    | C/Q fall time in high-side configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                     |      | 700                     |      | ns   |

| t <sub>rLS</sub>    | C/Q rise time in low-side configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                     |      | 750                     |      | ns   |

| t <sub>fLS</sub>    | C/Q fall time in low-side configuration                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                     |      | 530                     |      | ns   |

| t <sub>ENL</sub>    | ENL to L+ propagation delay time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                     |      | 1                       |      | μs   |

| t <sub>rL+</sub>    | L+ rise time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                     |      | 3                       |      | μs   |

| t <sub>fL+</sub>    | L+ fall time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                     |      | 25                      |      | μs   |

|                     | C/Q <sub>I</sub> to OUT <sub>C/Q</sub> (falling) propagation delay time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                     |      | 40                      |      | ns   |

| t <sub>dC/Qi</sub>  | C/Q <sub>I</sub> to OUT <sub>C/Q</sub> (rising) propagation delay time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                     |      | 100                     |      | ns   |

|                     | I/Q to OUT <sub>I/Q</sub> (falling) propagation delay time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                     |      | 40                      |      | ns   |

| t <sub>dI/Q</sub>   | I/Q to OUT <sub>I/Q</sub> (rising) propagation delay time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                     |      | 100                     |      | ns   |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                     |      | 100                     |      | μs   |

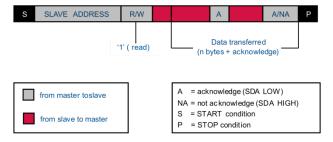

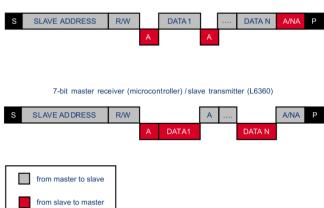

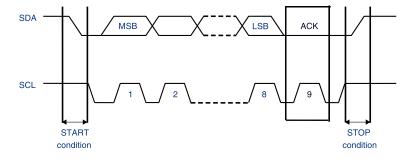

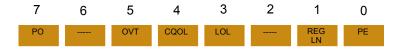

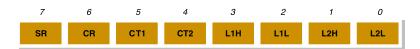

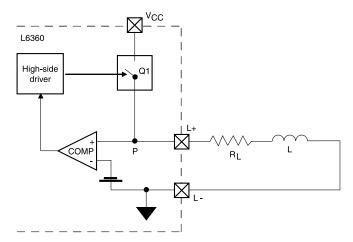

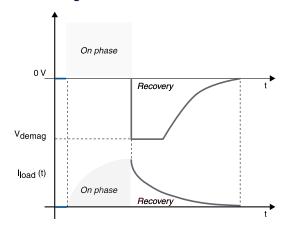

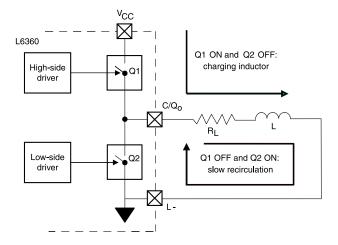

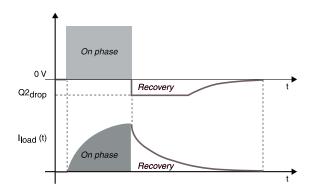

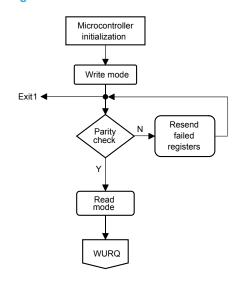

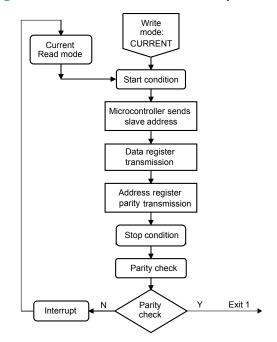

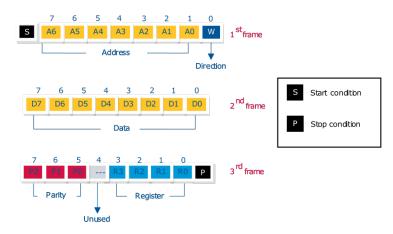

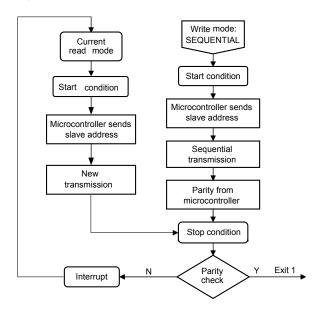

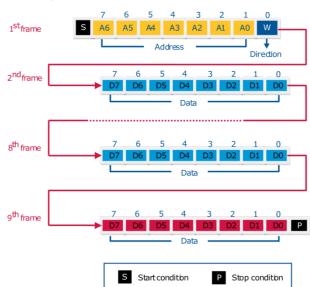

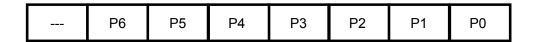

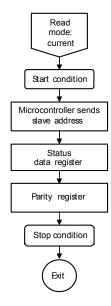

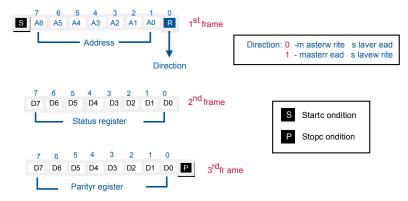

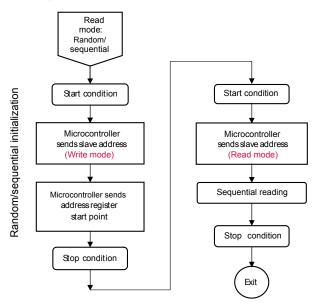

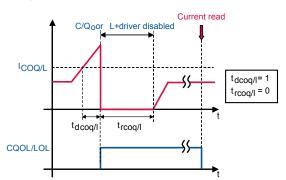

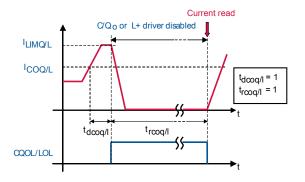

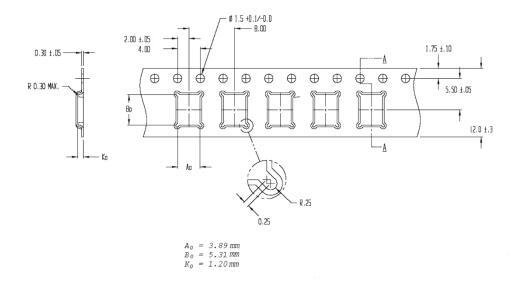

| 4                   | C/O law and high side out off ourrant delay time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Drawawahla                                          |      | 150                     |      | μs   |