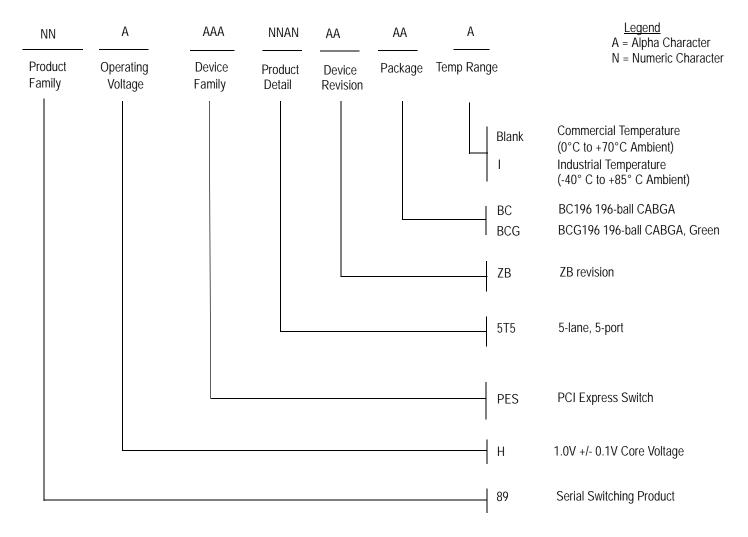

# 5-Lane 5-Port PCI Express® Switch

# 89PES5T5 Data Sheet

### **Device Overview**

The 89HPES5T5 is a member of IDT's PRECISE<sup>™</sup> family of PCI Express switching solutions. The PES5T5 is an 5-lane, 5-port peripheral chip that performs PCI Express Base switching. It provides connectivity and switching functions between a PCI Express upstream port and up to four downstream ports and supports switching between downstream ports.

## Features

- <sup>u</sup> High Performance PCI Express Switch

- Five 2.5Gbps PCI Express lanes

- Five switch ports

- Upstream port is x1

- Downstream ports are x1

- Low-latency cut-through switch architecture

- Support for Max Payload Sizes up to 256 bytes

- One virtual channel

- Eight traffic classes

- PCI Express Base Specification Revision 1.1 compliant

- <sup>u</sup> Flexible Architecture with Numerous Configuration Options

- Automatic lane reversal on all ports

- Automatic polarity inversion

- Ability to load device configuration from serial EEPROM

- <sup>u</sup> Legacy Support

- PCI compatible INTx emulation

- Bus locking

### <sup>u</sup> Highly Integrated Solution

- Requires no external components

- Incorporates on-chip internal memory for packet buffering and queueing

- Integrates five 2.5 Gbps embedded SerDes with 8B/10B encoder/decoder (no separate transceivers needed)

- <sup>u</sup> Reliability, Availability, and Serviceability (RAS) Features

- Internal end-to-end parity protection on all TLPs ensures data integrity even in systems that do not implement end-to-end CRC (ECRC)

- Supports ECRC and Advanced Error Reporting

- Supports PCI Express Native Hot-Plug, Hot-Swap capable I/O

- Compatible with Hot-Plug I/O expanders used on PC motherboards

- <sup>u</sup> Power Management

- Utilizes advanced low-power design techniques to achieve low typical power consumption

- Supports PCI Power Management Interface specification (PCI-PM 1.2)

- Unused SerDes are disabled.

- Supports Advanced Configuration and Power Interface Specification, Revision 2.0 (ACPI) supporting active link state

#### <sup>u</sup> Testability and Debug Features

- Built in Pseudo-Random Bit Stream (PRBS) generator

- Numerous SerDes test modes

- Ability to read and write any internal register via the SMBus

- Ability to bypass link training and force any link into any mode

- Provides statistics and performance counters

IDT and the IDT logo are registered trademarks of Integrated Device Technology, Inc.

#### © 2019 Renesas Electronics Corporation

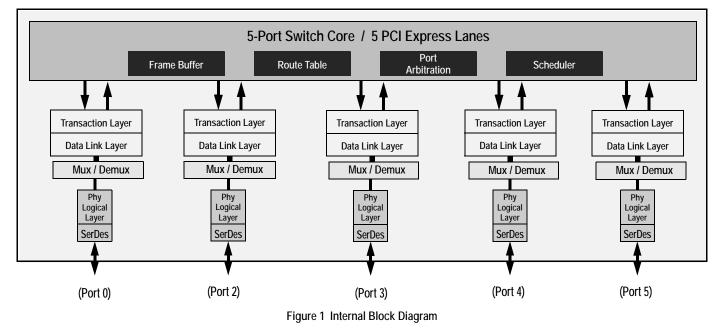

### Block Diagram

- <sup>u</sup> 11 General Purpose Input/Output Pins

- Each pin may be individually configured as an input or output

- Each pin may be individually configured as an interrupt input

- Some pins have selectable alternate functions

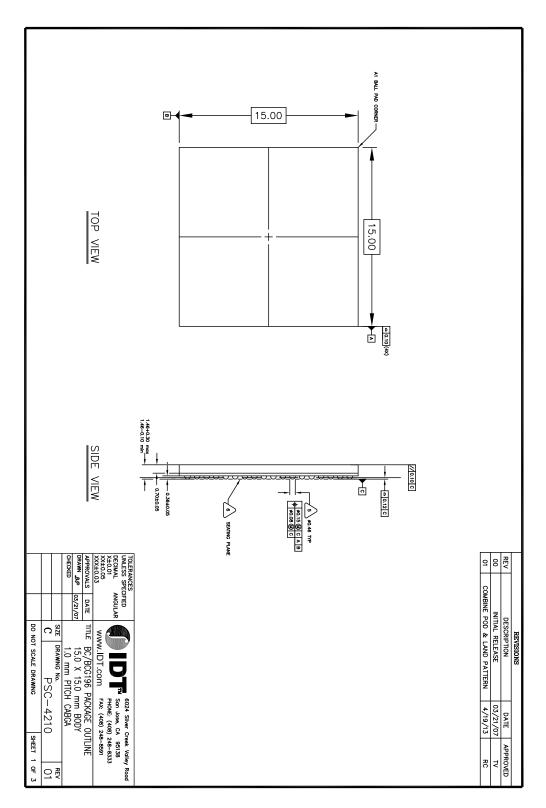

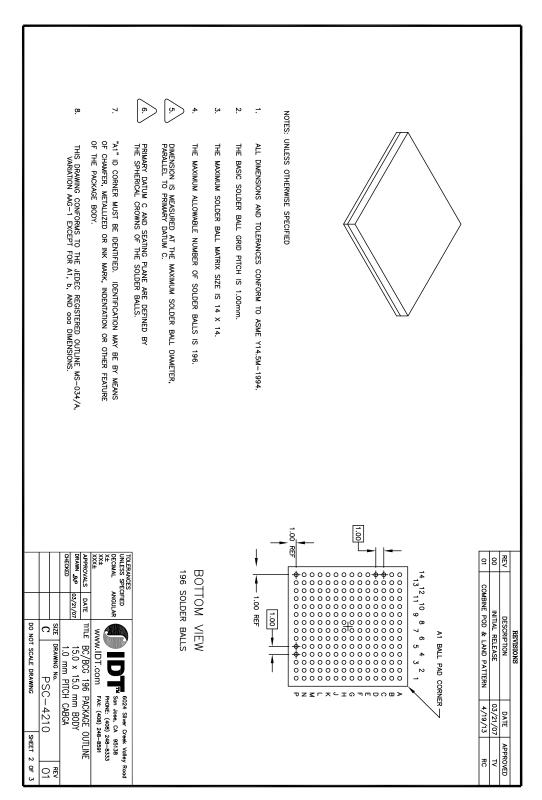

- <sup>u</sup> Packaged in a 15mm x 15mm 196-ball BGA with 1mm ball spacing

### **Product Description**

Utilizing standard PCI Express interconnect, the PES5T5 provides the most efficient I/O connectivity solution for applications requiring high throughput, low latency, and simple board layout with a minimum number of board layers. It provides 2.5 GBps (20 Gbps) of aggregated, full-duplex switching capacity through 5 integrated serial lanes, using proven and robust IDT technology. Each lane provides 2.5 Gbps of bandwidth in both directions and is fully compliant with PCI Express Base specification revision 1.1.

The PES5T5 is based on a flexible and efficient layered architecture. The PCI Express layer consists of SerDes, Physical, Data Link and Transaction layers in compliance with PCI Express Base specification Revision 1.1. The PES5T5 can operate either as a store and forward or cut-through switch and is designed to switch memory and I/O transactions. It supports eight Traffic Classes (TCs) and one Virtual Channel (VC) with sophisticated resource management to allow efficient switching for applications requiring additional narrow port connectivity.

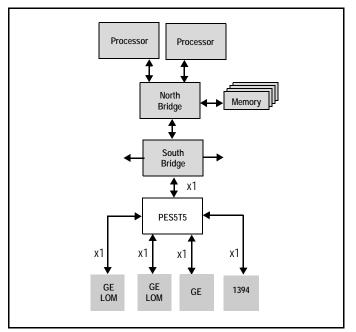

Figure 2 I/O Expansion Application

### **SMBus Interface**

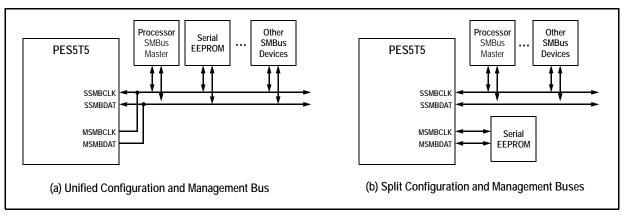

The PES5T5 contains two SMBus interfaces. The slave interface provides full access to the configuration registers in the PES5T5, allowing every configuration register in the device to be read or written by an external agent. The master interface allows the default configuration register values of the PES5T5 to be overridden following a reset with values programmed in an external serial EEPROM. The master interface is also used by an external Hot-Plug I/O expander.

Six pins make up each of the two SMBus interfaces. These pins consist of an SMBus clock pin, an SMBus data pin, and 4 SMBus address pins. In the slave interface, these address pins allow the SMBus address to which the device responds to be configured. In the master interface, these address pins allow the SMBus address of the serial configuration EEPROM from which data is loaded to be configured. The SMBus address is set up on negation of PERSTN by sampling the corresponding address pins. When the pins are sampled, the resulting address is assigned as shown in Table 1.

| Bit | Slave<br>SMBus<br>Address | Master<br>SMBus<br>Address |

|-----|---------------------------|----------------------------|

| 1   | SSMBADDR[1]               | MSMBADDR[1]                |

| 2   | SSMBADDR[2]               | MSMBADDR[2]                |

| 3   | SSMBADDR[3]               | MSMBADDR[3]                |

| 4   | 0                         | MSMBADDR[4]                |

| 5   | SSMBADDR[5]               | 1                          |

| 6   | 1                         | 0                          |

| 7   | 1                         | 1                          |

Table 1 Master and Slave SMBus Address Assignment

As shown in Figure 3, the master and slave SMBuses may be used in a unified or split configuration. In the unified configuration, shown in Figure 3(a), the master and slave SMBuses are tied together and the PES5T5 acts both as a SMBus master as well as a SMBus slave on this bus. This requires that the SMBus master or processor that has access to PES5T5 registers supports SMBus arbitration. In some systems, this SMBus master interface may be implemented using general purpose I/O pins on a processor or micro controller, and may not support SMBus arbitration. To support these systems, the PES5T5 may be configured to operate in a split configuration as shown in Figure 3(b).

In the split configuration, the master and slave SMBuses operate as two independent buses and thus multi-master arbitration is never required. The PES5T5 supports reading and writing of the serial EEPROM on the master SMBus via the slave SMBus, allowing in system programming of the serial EEPROM.

Figure 3 SMBus Interface Configuration Examples

### **Hot-Plug Interface**

The PES5T5 supports PCI Express Hot-Plug on each downstream port. To reduce the number of pins required on the device, the PES5T5 utilizes an external I/O expander, such as that used on PC motherboards, connected to the SMBus master interface. Following reset and configuration, whenever the state of a Hot-Plug output needs to be modified, the PES5T5 generates an SMBus transaction to the I/O expander with the new value of all of the outputs. Whenever a Hot-Plug input changes, the I/O expander generates an interrupt which is received on the IOEXPINTN input pin (alternate function of GPIO) of the PES5T5. In response to an I/O expander interrupt, the PES5T5 generates an SMBus transaction to read the state of all of the Hot-Plug inputs from the I/O expander.

### **General Purpose Input/Output**

The PES5T5 provides 11 General Purpose Input/Output (GPIO) pins that may be used by the system designer as bit I/O ports. Each GPIO pin may be configured independently as an input or output through software control. Some GPIO pins are shared with other on-chip functions. These alternate functions may be enabled via software, SMBus slave interface, or serial configuration EEPROM.

# **Pin Description**

The following tables lists the functions of the pins provided on the PES5T5. Some of the functions listed may be multiplexed onto the same pin. The active polarity of a signal is defined using a suffix. Signals ending with an "N" are defined as being active, or asserted, when at a logic zero (low) level. All other signals (including clocks, buses, and select lines) will be interpreted as being active, or asserted, when at a logic one (high) level.

| Signal                 | Туре | Name/Description                                                                                                                                                                                                                                                                                |  |  |  |

|------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PE0RP[0]<br>PE0RN[0]   | I    | PCI Express Port 0 Serial Data Receive. Differential PCI Express receive pair for port 0.                                                                                                                                                                                                       |  |  |  |

| PE0TP[0]<br>PE0TN[0]   | 0    | PCI Express Port 0 Serial Data Transmit. Differential PCI Express trans-<br>mit pair for port 0.                                                                                                                                                                                                |  |  |  |

| PE2RP[0]<br>PE2RN[0]   | I    | PCI Express Port 2 Serial Data Receive. Differential PCI Express receive pair for port 2.                                                                                                                                                                                                       |  |  |  |

| PE2TP[0]<br>PE2TN[0]   | 0    | PCI Express Port 2 Serial Data Transmit. Differential PCI Express trans-<br>mit pair for port 2.                                                                                                                                                                                                |  |  |  |

| PE3RP[0]<br>PE3RN[0]   | I    | PCI Express Port 3 Serial Data Receive. Differential PCI Express receive pair for port 3.                                                                                                                                                                                                       |  |  |  |

| PE3TP[0]<br>PE3TN[0]   | 0    | PCI Express Port 3 Serial Data Transmit. Differential PCI Express trans<br>mit pair for port 3.                                                                                                                                                                                                 |  |  |  |

| PE4RP[0]<br>PE4RN[0]   | I    | PCI Express Port 4 Serial Data Receive. Differential PCI Express receive pair for port 4.                                                                                                                                                                                                       |  |  |  |

| PE4TP[0]<br>PE4TN[0]   | 0    | PCI Express Port 4 Serial Data Transmit. Differential PCI Express transmit pair for port 4.                                                                                                                                                                                                     |  |  |  |

| PE5RP[0]<br>PE5RN[0]   | I    | PCI Express Port 5 Serial Data Receive. Differential PCI Express receive pair for port 5.                                                                                                                                                                                                       |  |  |  |

| PE5TP[0]<br>PE5TN[0]   | 0    | PCI Express Port 5 Serial Data Transmit. Differential PCI Express trans-<br>mit pair for port 5.                                                                                                                                                                                                |  |  |  |

| PEREFCLKP<br>PEREFCLKN | I    | PCI Express Reference Clock. Differential reference clock pair input. This clock is used as the reference clock by on-chip PLLs to generate the clocks required for the system logic and on-chip SerDes. The frequency of the differential reference clock is determined by the REFCLKM signal. |  |  |  |

| REFCLKM                | I    | PCI Express Reference Clock Mode Select. This signal selects the fre-<br>quency of the reference clock input.<br>0x0 - 100 MHz<br>0x1 - 125 MHz                                                                                                                                                 |  |  |  |

Table 2 PCI Express Interface Pins

| Signal          | Туре | Name/Description                                                                                                                  |

|-----------------|------|-----------------------------------------------------------------------------------------------------------------------------------|

| MSMBADDR[4:1]   | ļ    | Master SMBus Address. These pins determine the SMBus address of the serial EEPROM from which configuration information is loaded. |

| MSMBCLK         | I/O  | Master SMBus Clock. This bidirectional signal is used to synchronize transfers on the master SMBus.                               |

| MSMBDAT         | I/O  | Master SMBus Data. This bidirectional signal is used for data on the master SMBus.                                                |

| SSMBADDR[5,3:1] | ļ    | Slave SMBus Address. These pins determine the SMBus address to which the slave SMBus interface responds.                          |

| SSMBCLK         | I/O  | Slave SMBus Clock. This bidirectional signal is used to synchronize trans-<br>fers on the slave SMBus.                            |

| SSMBDAT         | I/O  | Slave SMBus Data. This bidirectional signal is used for data on the slave SMBus.                                                  |

Table 3 SMBus Interface Pins

| Signal  | Туре | Name/Description                                                                                                                                                                                                         |

|---------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO[0] | 1/0  | General Purpose I/O.<br>This pin can be configured as a general purpose I/O pin.<br>Alternate function pin name: P2RSTN<br>Alternate function pin type: Output<br>Alternate function: Reset output for downstream port 2 |

| GPIO[1] | I/O  | General Purpose I/O.<br>This pin can be configured as a general purpose I/O pin.<br>Alternate function pin name: P4RSTN<br>Alternate function pin type: Output<br>Alternate function: Reset output for downstream port 4 |

| GPIO[2] | I/O  | General Purpose I/O.<br>This pin can be configured as a general purpose I/O pin.<br>Alternate function pin name: IOEXPINTNO<br>Alternate function pin type: Input<br>Alternate function: I/O Expander interrupt 0 input  |

| GPIO[3] | 1/0  | General Purpose I/O.<br>This pin can be configured as a general purpose I/O pin.<br>Alternate function pin name: IOEXPINTN1<br>Alternate function pin type: Input<br>Alternate function: I/O Expander interrupt 1 input  |

| GPIO[4] | 1/0  | General Purpose I/O.<br>This pin can be configured as a general purpose I/O pin.<br>Alternate function pin name: IOEXPINTN2<br>Alternate function pin type: Input<br>Alternate function: I/O Expander interrupt 2 input  |

| GPIO[5] | I/O  | General Purpose I/O.<br>This pin can be configured as a general purpose I/O pin.                                                                                                                                         |

| GPIO[6] | I/O  | General Purpose I/O.<br>This pin can be configured as a general purpose I/O pin.                                                                                                                                         |

Table 4 General Purpose I/O Pins (Part 1 of 2)

| Signal   | Туре | Name/Description                                                                                                                                                                                                         |

|----------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO[7]  | I/O  | General Purpose I/O.<br>This pin can be configured as a general purpose I/O pin.<br>Alternate function pin name: GPEN<br>Alternate function pin type: Output<br>Alternate function: General Purpose Event (GPE) output   |

| GPIO[8]  | I/O  | General Purpose I/O.<br>This pin can be configured as a general purpose I/O pin.                                                                                                                                         |

| GPIO[9]  | I/O  | General Purpose I/O.<br>This pin can be configured as a general purpose I/O pin.<br>Alternate function pin name: P3RSTN<br>Alternate function pin type: Output<br>Alternate function: Reset output for downstream port 3 |

| GPIO[10] | I/O  | General Purpose I/O.<br>This pin can be configured as a general purpose I/O pin.<br>Alternate function pin name: P5RSTN<br>Alternate function pin type: Output<br>Alternate function: Reset output for downstream port 5 |

Table 4 General Purpose I/O Pins (Part 2 of 2)

| Signal    | Туре | Name/Description                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APWRDISN  | ļ    | Auxiliary Power Disable Input. When this pin is active, it disables the device from using auxiliary power supply.                                                                                                                                                                                                                                                                                          |

| CCLKDS    | I    | <b>Common Clock Downstream</b> . The assertion of this pin indicates that all downstream ports are using the same clock source as that provided to downstream devices. This bit is used as the initial value of the Slot Clock Configuration bit in all of the Link Status Registers for downstream ports. The value may be override by modifying the SCLK bit in the downstream port's PCIELSTS register. |

| CCLKUS    | I    | <b>Common Clock Upstream</b> . The assertion of this pin indicates that the upstream port is using the same clock source as the upstream device. This bit is used as the initial value of the Slot Clock Configuration bit in the Link Status Register for the upstream port. The value may be overridden by modifying the SCLK bit in the PA_PCIELSTS register.                                           |

| MSMBSMODE | I    | Master SMBus Slow Mode. The assertion of this pin indicates that the master SMBus should operate at 100 KHz instead of 400 kHz. This value may not be overridden.                                                                                                                                                                                                                                          |

| PERSTN    | l    | Fundamental Reset. Assertion of this signal resets all logic inside the PES5T5 and initiates a PCI Express fundamental reset.                                                                                                                                                                                                                                                                              |

Table 5 System Pins (Part 1 of 2)

| Signal      | Туре | Name/Description                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RSTHALT     | I    | <b>Reset Halt.</b> When this signal is asserted during a PCI Express fundamental reset, the PES5T5 executes the reset procedure and remains in a reset state with the Master and Slave SMBuses active. This allows software to read and write registers internal to the device before normal device operation begins. The device exits the reset state when the RSTHALT bit is cleared in the PA_SWCTL register by an SMBus master. |

| SWMODE[2:0] | I    | Switch Mode.         These configuration pins determine the PES5T5 switch operating mode.           0x0 -         Normal switch mode           0x1 -         Normal switch mode with Serial EEPROM initialization           0x2 - through 0xF Reserved                                                                                                                                                                              |

| WAKEN       | I/O  | Wake Input/Output. The WAKEN signal is an input or output. The WAKEN signal input/output selection can be made through the WAKEDIR bit setting in the WAKEUPCNTL register.                                                                                                                                                                                                                                                          |

Table 5 System Pins (Part 2 of 2)

| Signal      | Туре | Name/Description                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| JTAG_TCK    | I    | JTAG Clock. This is an input test clock used to clock the shifting of data into or out of the boundary scan logic or JTAG Controller. JTAG_TCK is independent of the system clock with a nominal 50% duty cycle.                                                                                                                                                                                                                                                      |

| JTAG_TDI    | I    | JTAG Data Input. This is the serial data input to the boundary scan logic or JTAG Controller.                                                                                                                                                                                                                                                                                                                                                                         |

| JTAG_TDO    | 0    | JTAG Data Output. This is the serial data shifted out from the boundary scan logic or JTAG Controller. When no data is being shifted out, this signal is tri-stated.                                                                                                                                                                                                                                                                                                  |

| JTAG_TMS    | I    | <b>JTAG Mode</b> . The value on this signal controls the test mode select of the boundary scan logic or JTAG Controller.                                                                                                                                                                                                                                                                                                                                              |

| JTAG_TRST_N | I    | JTAG Reset. This active low signal asynchronously resets the boundary scan logic and JTAG TAP Controller. An external pull-up on the board is recommended to meet the JTAG specification in cases where the tester can access this signal. However, for systems running in functional mode, one of the following should occur:<br>1) actively drive this signal low with control logic<br>2) statically drive this signal low with an external pull-down on the board |

Table 6 Test Pins

| Signal               | Туре | Name/Description                                                                                      |

|----------------------|------|-------------------------------------------------------------------------------------------------------|

| V <sub>DD</sub> CORE | I    | Core VDD. Power supply for core logic.                                                                |

| V <sub>DD</sub> IO   | I    | I/O VDD. LVTTL I/O buffer power supply.                                                               |

| V <sub>DD</sub> PE   | I    | <b>PCI Express Digital Power</b> . PCI Express digital power used by the digital power of the SerDes. |

| V <sub>DD</sub> APE  | I    | PCI Express Analog Power. PCI Express analog power used by the PLL and bias generator.                |

| V <sub>TT</sub> PE   | I    | PCI Express Termination Power.                                                                        |

| V <sub>SS</sub>      | I    | Ground.                                                                                               |

Table 7 Power and Ground Pins

# **Pin Characteristics**

**Note:** Some input pads of the PES5T5 do not contain internal pull-ups or pull-downs. Unused inputs should be tied off to appropriate levels. This is especially critical for unused control signal inputs which, if left floating, could adversely affect operation. Also, any input pin left floating can cause a slight increase in power consumption.

| Function            | Pin Name        | Туре | Buffer  | І/О<br>Туре      | Internal<br>Resistor | Notes            |

|---------------------|-----------------|------|---------|------------------|----------------------|------------------|

| PCI Express Inter-  | PE0RN[0]        | I    | CML     | Serial Link      |                      |                  |

| face                | PE0RP[0]        | I    |         |                  |                      |                  |

|                     | PE0TN[0]        | 0    |         |                  |                      |                  |

|                     | PE0TP[0]        | 0    |         |                  |                      |                  |

|                     | PE2RN[0]        | I    |         |                  |                      |                  |

|                     | PE2RP[0]        | I    |         |                  |                      |                  |

|                     | PE2TN[0]        | 0    |         |                  |                      |                  |

|                     | PE2TP[0]        | 0    |         |                  |                      |                  |

|                     | PE3RN[0]        | I    |         |                  |                      |                  |

|                     | PE3RP[0]        | I    |         |                  |                      |                  |

|                     | PE3TN[0]        | 0    |         |                  |                      |                  |

|                     | PE3TP[0]        | 0    |         |                  |                      |                  |

|                     | PE4RN[0]        | I    |         |                  |                      |                  |

|                     | PE4RP[0]        | I    |         |                  |                      |                  |

|                     | PE4TN[0]        | 0    |         |                  |                      |                  |

|                     | PE4TP[0]        | 0    |         |                  |                      |                  |

|                     | PE5RN[0]        | I    |         |                  |                      |                  |

|                     | PE5RP[0]        | I    |         |                  |                      |                  |

|                     | PE5TN[0]        | 0    |         |                  |                      |                  |

|                     | PE5TP[0]        | 0    |         |                  |                      |                  |

|                     | PEREFCLKN       | I    | LVPECL/ | Diff. Clock      |                      | Refer to Table 9 |

|                     | PEREFCLKP       | I    | CML     | Input            |                      |                  |

|                     | REFCLKM         | I    | LVTTL   | Input            | pull-down            |                  |

| SMBus               | MSMBADDR[4:1]   | I    | LVTTL   | Input            | pull-up              |                  |

|                     | MSMBCLK         | I/O  |         | STI <sup>1</sup> |                      |                  |

|                     | MSMBDAT         | I/O  |         | STI              |                      |                  |

|                     | SSMBADDR[5,3:1] | I    |         | Input            | pull-up              |                  |

|                     | SSMBCLK         | I/O  |         | STI              |                      |                  |

|                     | SSMBDAT         | I/O  |         | STI              |                      |                  |

| General Purpose I/O | GPIO[10:0]      | I/O  | LVTTL   | High Drive       | pull-up              |                  |

Table 8 Pin Characteristics (Part 1 of 2)

| Function     | Pin Name    | Туре | Buffer | I/O<br>Type | Internal<br>Resistor | Notes |

|--------------|-------------|------|--------|-------------|----------------------|-------|

| System Pins  | APWRDISN    | I    | LVTTL  | Input       | pull-down            |       |

|              | CCLKDS      | I    |        |             | pull-up              |       |

|              | CCLKUS      | I    |        |             | pull-up              |       |

|              | MSMBSMODE   | I    |        |             | pull-down            |       |

|              | PERSTN      | I    |        |             |                      |       |

|              | RSTHALT     | I    |        |             | pull-down            |       |

|              | SWMODE[2:0] | I    |        |             | pull-down            |       |

|              | WAKEN       | I/O  |        |             | open-drain           |       |

| EJTAG / JTAG | JTAG_TCK    |      | LVTTL  | STI         | pull-up              |       |

|              | JTAG_TDI    | I    |        | STI         | pull-up              |       |

|              | JTAG_TDO    | 0    |        |             |                      |       |

|              | JTAG_TMS    | I    |        | STI         | pull-up              |       |

|              | JTAG_TRST_N | I    |        | STI         | pull-up              |       |

Table 8 Pin Characteristics (Part 2 of 2)

<sup>1.</sup> Schmitt Trigger Input (STI).

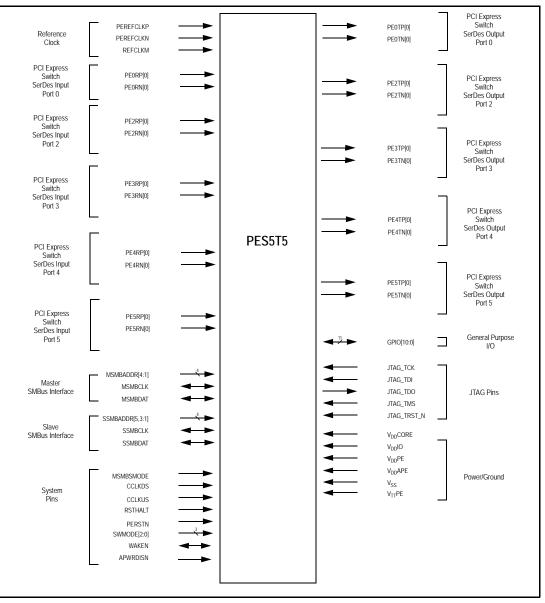

# Logic Diagram — PES5T5

Figure 4 PES5T5 Logic Diagram

## **System Clock Parameters**

Values based on systems running at recommended supply voltages and operating temperatures, as shown in Tables 13 and 14.

| Parameter                         | Description                                   | Min | Typical | Мах              | Unit              |

|-----------------------------------|-----------------------------------------------|-----|---------|------------------|-------------------|

| PEREFCLK                          |                                               |     |         |                  |                   |

| Refclk <sub>FREQ</sub>            | Input reference clock frequency range         | 100 |         | 125 <sup>1</sup> | MHz               |

| Refclk <sub>DC</sub> <sup>2</sup> | Duty cycle of input clock                     | 40  | 50      | 60               | %                 |

| T <sub>R</sub> , T <sub>F</sub>   | Rise/Fall time of input clocks                |     |         | 0.2*RCUI         | RCUI <sup>3</sup> |

| V <sub>SW</sub>                   | Differential input voltage swing <sup>4</sup> | 0.6 |         | 1.6              | V                 |

| Tjitter                           | Input clock jitter (cycle-to-cycle)           |     |         | 125              | ps                |

### Table 9 Input Clock Requirements

<sup>1.</sup> The input clock frequency will be either 100 or 125 MHz depending on signal REFCLKM.

$^{2}$  ClkIn must be AC coupled. Use 0.01 - 0.1  $\mu\mathrm{F}$  ceramic capacitors.

$^{3.}$  RCUI (Reference Clock Unit Interval) refers to the reference clock period.

<sup>4.</sup> AC coupling required.

# **AC Timing Characteristics**

| Parameter                                    | Description                                                                  | Min <sup>1</sup> | Typical <sup>1</sup> | Max <sup>1</sup> | Units |

|----------------------------------------------|------------------------------------------------------------------------------|------------------|----------------------|------------------|-------|

| PCIe Transmit                                | <u> </u>                                                                     |                  |                      |                  |       |

| UI                                           | Unit Interval                                                                | 399.88           | 400                  | 400.12           | ps    |

| T <sub>TX-EYE</sub>                          | Minimum Tx Eye Width                                                         | 0.7              | .9                   |                  | UI    |

| T <sub>TX-EYE-MEDIAN-to-</sub><br>MAX-JITTER | Maximum time between the jitter median and maximum deviation from the median |                  |                      | 0.15             | UI    |

| T <sub>TX-RISE</sub> , T <sub>TX-FALL</sub>  | D+ / D- Tx output rise/fall time                                             | 50               | 90                   |                  | ps    |

| T <sub>TX- IDLE-MIN</sub>                    | Minimum time in idle                                                         | 50               |                      |                  | UI    |

| T <sub>TX-IDLE-SET-TO-</sub><br>IDLE         | Maximum time to transition to a valid Idle after sending an Idle ordered set |                  |                      | 20               | UI    |

| T <sub>TX-IDLE-TO-DIFF-</sub><br>DATA        | Maximum time to transition from valid idle to diff data                      |                  |                      | 20               | UI    |

| T <sub>TX-SKEW</sub>                         | Transmitter data skew between any 2 lanes                                    |                  | 500                  | 1300             | ps    |

| T <sub>BTEn</sub>                            | Time from asserting Beacon TxEn to beacon being trans-<br>mitted on the lane |                  | 30                   | 80               | ns    |

| PCIe Receive                                 | · · · · · · · · · · · · · · · · · · ·                                        |                  | 1 1                  |                  |       |

| UI                                           | Unit Interval                                                                | 399.88           | 400                  | 400.12           | ps    |

| T <sub>RX-EYE</sub> (with jitter)            | Minimum Receiver Eye Width (jitter tolerance)                                | 0.4              |                      |                  | UI    |

Table 10 PCIe AC Timing Characteristics (Part 1 of 2)

| Parameter                     | Description                                             | Min <sup>1</sup> | Typical <sup>1</sup> | Max <sup>1</sup> | Units |

|-------------------------------|---------------------------------------------------------|------------------|----------------------|------------------|-------|

| T <sub>RX-EYE-MEDIUM TO</sub> | Max time between jitter median & max deviation          |                  |                      | 0.3              | UI    |

| T <sub>RX-IDLE-DET-DIFF</sub> | Unexpected Idle Enter Detect Threshold Integration Time |                  |                      | 10               | ms    |

| T <sub>RX-SKEW</sub>          | Lane to lane input skew                                 |                  |                      | 20               | ns    |

Table 10 PCIe AC Timing Characteristics (Part 2 of 2)

<sup>1.</sup> Minimum, Typical, and Maximum values meet the requirements under PCI Specification 1.1

| Signal                  | Symbol               | Reference<br>Edge | Min | Мах | Unit | Timing<br>Diagram<br>Reference |  |

|-------------------------|----------------------|-------------------|-----|-----|------|--------------------------------|--|

| GPIO                    |                      |                   |     |     |      |                                |  |

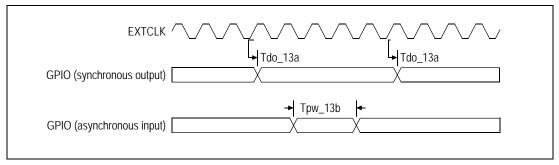

| GPIO[10:0] <sup>1</sup> | Tpw_13b <sup>2</sup> | None              | 50  | _   | ns   | See Figure 5.                  |  |

#### Table 11 GPIO AC Timing Characteristics

<sup>1.</sup> GPIO signals must meet the setup and hold times if they are synchronous or the minimum pulse width if they are asynchronous.

$^{\rm 2.}$  The values for this symbol were determined by calculation, not by testing.

Figure 5 GPIO AC Timing Waveform

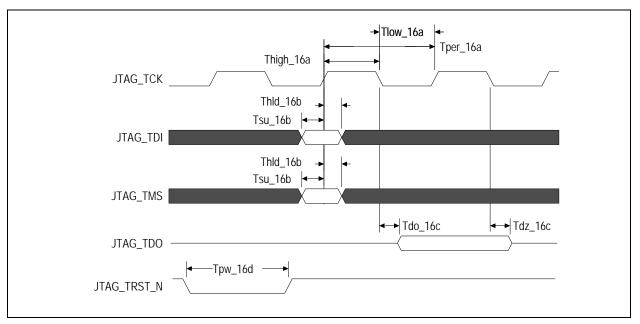

| Signal                  | Symbol                 | Reference<br>Edge | Min  | Max  | Unit | Timing<br>Diagram<br>Reference |  |  |  |

|-------------------------|------------------------|-------------------|------|------|------|--------------------------------|--|--|--|

| JTAG                    | JTAG                   |                   |      |      |      |                                |  |  |  |

| JTAG_TCK                | Tper_16a               | none              | 25.0 | 50.0 | ns   | See Figure 6.                  |  |  |  |

|                         | Thigh_16a,<br>Tlow_16a |                   | 10.0 | 25.0 | ns   |                                |  |  |  |

| JTAG_TMS <sup>1</sup> , | Tsu_16b                | JTAG_TCK rising   | 2.4  | —    | ns   |                                |  |  |  |

| JTAG_TDI                | Thld_16b               |                   | 1.0  | —    | ns   |                                |  |  |  |

| JTAG_TDO                | Tdo_16c                | JTAG_TCK falling  | _    | 11.3 | ns   |                                |  |  |  |

|                         | Tdz_16c <sup>2</sup>   |                   | _    | 11.3 | ns   |                                |  |  |  |

| JTAG_TRST_N             | Tpw_16d <sup>2</sup>   | none              | 25.0 | —    | ns   |                                |  |  |  |

#### Table 12 JTAG AC Timing Characteristics

<sup>1.</sup> The JTAG specification, IEEE 1149.1, recommends that JTAG\_TMS should be held at 1 while the signal applied at JTAG\_TRST\_N changes from 0 to 1. Otherwise, a race may occur if JTAG\_TRST\_N is deasserted (going from low to high) on a rising edge of JTAG\_TCK when JTAG\_TMS is low, because the TAP controller might go to either the Run-Test/Idle state or stay in the Test-Logic-Reset state.

$^{2\cdot}$  The values for this symbol were determined by calculation, not by testing.

Figure 6 JTAG AC Timing Waveform

# **Recommended Operating Supply Voltages**

| Symbol               | Parameter                                               | Minimum | Typical | Maximum | Unit |

|----------------------|---------------------------------------------------------|---------|---------|---------|------|

| V <sub>DD</sub> CORE | Internal logic supply                                   | 0.9     | 1.0     | 1.1     | V    |

| V <sub>DD</sub> I/O  | I/O supply except for SerDes LVPECL/CML                 | 3.135   | 3.3     | 3.465   | V    |

| V <sub>DD</sub> PE   | PCI Express Digital Power                               | 0.9     | 1.0     | 1.1     | V    |

| V <sub>DD</sub> APE  | PCI Express Analog Power                                | 0.9     | 1.0     | 1.1     | V    |

| V <sub>TT</sub> PE   | PCI Express Serial Data Transmit<br>Termination Voltage | 1.425   | 1.5     | 1.575   | V    |

| V <sub>SS</sub>      | Common ground                                           | 0       | 0       | 0       | V    |

Table 13 PES5T5 Operating Voltages

# **Power-Up/Power-Down Sequence**

This section describes the sequence in which various voltages must be applied to the part during power-up to ensure proper functionality. For the PES5T5, the power-up sequence must be as follows:

- 1. V<sub>DD</sub>I/O 3.3V

- 2. V<sub>DD</sub>Core, V<sub>DD</sub>PE, V<sub>DD</sub>APE 1.0V

- 3. V<sub>TT</sub>PE 1.5V

When powering up, each voltage level must ramp and stabilize prior to applying the next voltage in the sequence to ensure internal latch-up issues are avoided. There are no maximum time limitations in ramping to valid power levels.

The power-down sequence must be in the reverse order of the power-up sequence.

# **Recommended Operating Temperature**

| Grade      | Temperature            |

|------------|------------------------|

| Commercial | 0°C to +70°C Ambient   |

| Industrial | -40°C to +85°C Ambient |

Table 14 PES5T5 Operating Temperatures

### **Power Consumption**

Typical power is measured under the following conditions: 25°C Ambient, 35% total link usage on all ports, typical voltages defined in Table 13.

Maximum power is measured under the following conditions: 70°C Ambient, 85% total link usage on all ports, maximum voltages defined in Table 13.

All power measurements assume that the part is mounted on a 10 layer printed circuit board with 0 LFM airflow.

| Number of<br>Connected | Core Supply |             | PCIe Digital PCIe Analo<br>Supply Supply |             | •           | PCIe Termin-<br>ation Supply |             | I/O Supply  |               | Total       |               |              |              |

|------------------------|-------------|-------------|------------------------------------------|-------------|-------------|------------------------------|-------------|-------------|---------------|-------------|---------------|--------------|--------------|

| Lanes                  |             | Тур<br>1.0V | Max<br>1.1V                              | Тур<br>1.0V | Max<br>1.1V | Тур<br>1.0V                  | Max<br>1.1V | Тур<br>1.5V | Max<br>1.575V | Тур<br>3.3V | Max<br>3.465V | Typ<br>Power | Max<br>Power |

| 1/1/1/1/1              | mA          | 290         | 385                                      | 250         | 308         | 124                          | 143         | 115         | 141           | 3           | 3.3           |              |              |

|                        | Watts       | 0.29        | 0.42                                     | 0.25        | 0.34        | 0.12                         | 0.16        | 0.17        | 0.22          | 0.01        | 0.01          | 0.85         | 1.15         |

Table 15 PES5T5 Power Consumption

## **Thermal Considerations**

This section describes thermal considerations for the PES5T5 (15mm<sup>2</sup> BCG196 package). The data in Table 16 below contains information that is relevant to the thermal performance of the PES5T5 switch.

| Symbol                     | Parameter                                         | Value | Units | Conditions                            |

|----------------------------|---------------------------------------------------|-------|-------|---------------------------------------|

| T <sub>J(max)</sub>        | Junction Temperature                              | 125   | °C    | Maximum                               |

| T <sub>A(max)</sub>        | Ambient Temperature                               | 70    | OO    | Maximum for commercial-rated products |

| T <sub>A(max)</sub>        | Ambient Temperature                               | 85    | °C    | Maximum for industrial-rated products |

|                            |                                                   | 33.3  | °C/W  | Zero air flow                         |

| θ <sub>JA(effective)</sub> | Effective Thermal Resistance, Junction-to-Ambient | 29    | °C/W  | 1 m/S air flow                        |

|                            |                                                   | 26.6  | °C/W  | 2 m/S air flow                        |

| θ <sub>JB</sub>            | Thermal Resistance, Junction-to-Board             | 18.7  | °C/W  |                                       |

| θ <sub>JC</sub>            | Thermal Resistance, Junction-to-Case              | 9.8   | °C/W  |                                       |

| Р                          | Power Dissipation of the Device                   | 1.15  | Watts | Maximum                               |

Table 16 Thermal Specifications for PES5T5, 15x15mm BCG196 Package

# **DC Electrical Characteristics**

Values based on systems running at recommended supply voltages, as shown in Table 13.

Note: See Table 8, Pin Characteristics, for a complete I/O listing.

| I/О Туре    | Parameter                                   | Description                                             | Min <sup>1</sup> | Typ <sup>1</sup> | Max <sup>1</sup> | Unit | Conditions |

|-------------|---------------------------------------------|---------------------------------------------------------|------------------|------------------|------------------|------|------------|

| Serial Link | PCIe Transmit                               |                                                         |                  |                  |                  |      |            |

|             | V <sub>TX-DIFFp-p</sub>                     | Differential peak-to-peak output voltage                | 800              |                  | 1200             | mV   |            |

|             | V <sub>TX-DE-RATIO</sub>                    | De-emphasized differential output voltage               | -3               |                  | -4               | dB   |            |

|             | V <sub>TX-DC-CM</sub>                       | DC Common mode voltage                                  | -0.1             | 1                | 3.7              | V    |            |

|             | V <sub>TX-CM-ACP</sub>                      | RMS AC peak common mode output volt-<br>age             |                  |                  | 20               | mV   |            |

|             | V <sub>TX-CM-DC-</sub><br>active-idle-delta | Abs delta of DC common mode voltage between L0 and idle |                  |                  | 100              | mV   |            |

|             | V <sub>TX-CM-DC-line-</sub><br>delta        | Abs delta of DC common mode voltage between D+ and D-   |                  |                  | 25               | mV   |            |

|             | V <sub>TX-Idle-DiffP</sub>                  | Electrical idle diff peak output                        |                  |                  | 20               | mV   |            |

|             | V <sub>TX-RCV-Detect</sub>                  | Voltage change during receiver detection                |                  |                  | 600              | mV   |            |

|             | RL <sub>TX-DIFF</sub>                       | Transmitter Differential Return loss                    | 10               |                  |                  | dB   |            |

|             | RL <sub>TX-CM</sub>                         | Transmitter Common Mode Return loss                     | 6                |                  |                  | dB   |            |

|             | Z <sub>TX-DEFF-DC</sub>                     | DC Differential TX impedance                            | 80               | 100              | 120              | Ω    |            |

|             | Z <sub>OSE</sub>                            | Single ended TX Impedance                               | 40               | 50               | 60               | Ω    |            |

|             | Transmitter Eye<br>Diagram                  | TX Eye Height (De-emphasized bits)                      | 505              | 650              |                  | mV   |            |

|             | Transmitter Eye<br>Diagram                  | TX Eye Height (Transition bits)                         | 800              | 950              |                  | mV   |            |

|             | PCIe Receive                                |                                                         |                  |                  |                  |      |            |

|             | V <sub>RX-DIFFp-p</sub>                     | Differential input voltage (peak-to-peak)               | 175              |                  | 1200             | mV   |            |

|             | V <sub>RX-CM-AC</sub>                       | Receiver common-mode voltage for AC coupling            |                  |                  | 150              | mV   |            |

|             | RL <sub>RX-DIFF</sub>                       | Receiver Differential Return Loss                       | 10               |                  |                  | dB   |            |

|             | RL <sub>RX-CM</sub>                         | Receiver Common Mode Return Loss                        | 6                |                  |                  | dB   |            |

|             | Z <sub>RX-DIFF-DC</sub>                     | Differential input impedance (DC)                       | 80               | 100              | 120              | Ω    |            |

|             | Z <sub>RX-COMM-DC</sub>                     | Single-ended input impedance                            | 40               | 50               | 60               | Ω    |            |

|             | Z <sub>RX-COMM-HIGH-</sub><br>Z-DC          | Powered down input common mode impedance (DC)           | 200k             | 350k             |                  | Ω    |            |

|             | V <sub>RX-IDLE-DET-</sub><br>DIFFp-p        | Electrical idle detect threshold                        | 65               |                  | 175              | mV   |            |

| PCIe REFCLK |                                             |                                                         |                  |                  |                  |      |            |

|             | C <sub>IN</sub>                             | Input Capacitance                                       | 1.5              | _                |                  | pF   |            |

Table 17 DC Electrical Characteristics (Part 1 of 2)

| IDT 89PES                           | 5T5 Data Sheet                             |             |                  |                  |                             |      |                           |

|-------------------------------------|--------------------------------------------|-------------|------------------|------------------|-----------------------------|------|---------------------------|

| I/O Type                            | Parameter                                  | Description | Min <sup>1</sup> | Typ <sup>1</sup> | Max <sup>1</sup>            | Unit | Conditions                |

| Other I/Os                          | · · ·                                      |             |                  |                  | •                           |      |                           |

| LOW Drive                           | I <sub>OL</sub>                            |             | —                | 2.5              | —                           | mA   | $V_{OL} = 0.4v$           |

| Output                              | I <sub>ОН</sub>                            |             | —                | -5.5             | _                           | mA   | V <sub>OH</sub> = 1.5V    |

| High Drive<br>Output                | I <sub>OL</sub>                            |             | —                | 12.0             | —                           | mA   | $V_{OL} = 0.4v$           |

|                                     | I <sub>ОН</sub>                            |             | —                | -20.0            | —                           | mA   | V <sub>OH</sub> = 1.5V    |

| Schmitt Trig-<br>ger Input<br>(STI) | V <sub>IL</sub>                            |             | -0.3             | _                | 0.8                         | V    | _                         |

|                                     | V <sub>IH</sub>                            |             | 2.0              | _                | V <sub>DD</sub> IO + 0.5    | V    | _                         |

| Input                               | V <sub>IL</sub>                            |             | -0.3             | —                | 0.8                         | V    | _                         |

|                                     | V <sub>IH</sub>                            |             | 2.0              | _                | V <sub>DD</sub> IO +<br>0.5 | V    | _                         |

| Capacitance                         | C <sub>IN</sub>                            |             | -                | —                | 8.5                         | pF   | _                         |

| Leakage                             | Inputs                                     |             | -                | —                | <u>+</u> 10                 | μA   | V <sub>DD</sub> I/O (max) |

|                                     | I/O <sub>LEAK W/O</sub><br>Pull-ups/downs  |             | —                | _                | <u>+</u> 10                 | μΑ   | V <sub>DD</sub> I/O (max) |

|                                     | I/O <sub>LEAK WITH</sub><br>Pull-ups/downs |             | _                | _                | <u>+</u> 80                 | μΑ   | V <sub>DD</sub> I/O (max) |

Table 17 DC Electrical Characteristics (Part 2 of 2)

<sup>1.</sup> Minimum, Typical, and Maximum values meet the requirements under PCI Specification 1.1.

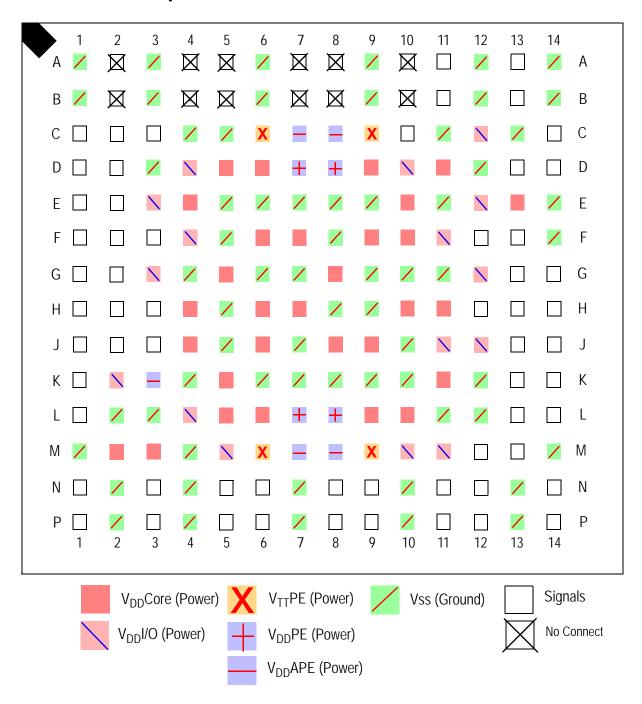

# Package Pinout — 196-BGA Signal Pinout for PES5T5

The following table lists the pin numbers and signal names for the PES5T5 device.

| Pin | Function           | Alt | Pin | Function             | Alt | Pin | Function             | Alt | Pin | Function             | Alt |

|-----|--------------------|-----|-----|----------------------|-----|-----|----------------------|-----|-----|----------------------|-----|

| A1  | V <sub>SS</sub>    |     | C7  | V <sub>DD</sub> APE  |     | E13 | V <sub>DD</sub> CORE |     | H5  | V <sub>SS</sub>      |     |

| A2  | NC                 |     | C8  | V <sub>DD</sub> APE  |     | E14 | V <sub>SS</sub>      |     | H6  | V <sub>DD</sub> CORE |     |

| A3  | V <sub>SS</sub>    |     | C9  | V <sub>TT</sub> PE   |     | F1  | MSMBDAT              |     | H7  | V <sub>DD</sub> CORE |     |

| A4  | NC                 |     | C10 | CCLKDS               |     | F2  | SSMBADDR_2           |     | H8  | V <sub>SS</sub>      |     |

| A5  | NC                 |     | C11 | V <sub>SS</sub>      |     | F3  | SSMBADDR_5           |     | H9  | V <sub>SS</sub>      |     |

| A6  | V <sub>SS</sub>    |     | C12 | V <sub>DD</sub> IO   |     | F4  | V <sub>DD</sub> IO   |     | H10 | V <sub>DD</sub> CORE |     |

| A7  | NC                 |     | C13 | V <sub>SS</sub>      |     | F5  | V <sub>SS</sub>      |     | H11 | V <sub>DD</sub> CORE |     |

| A8  | NC                 |     | C14 | SWMODE_0             |     | F6  | V <sub>DD</sub> CORE |     | H12 | GPIO_05              |     |

| A9  | V <sub>SS</sub>    |     | D1  | SSMBCLK              |     | F7  | V <sub>DD</sub> CORE |     | H13 | GPIO_03              | 1   |

| A10 | NC                 |     | D2  | SSMBDAT              |     | F8  | V <sub>SS</sub>      |     | H14 | GPIO_02              | 1   |

| A11 | PE0TN00            |     | D3  | V <sub>SS</sub>      |     | F9  | V <sub>DD</sub> CORE |     | J1  | JTAG_TDO             |     |

| A12 | V <sub>SS</sub>    |     | D4  | V <sub>DD</sub> IO   |     | F10 | V <sub>DD</sub> CORE |     | J2  | JTAG_TRST_N          |     |

| A13 | PE0RP00            |     | D5  | V <sub>DD</sub> CORE |     | F11 | V <sub>DD</sub> IO   |     | J3  | JTAG_TMS             |     |

| A14 | V <sub>SS</sub>    |     | D6  | V <sub>DD</sub> CORE |     | F12 | GPIO_00              | 1   | J4  | V <sub>DD</sub> CORE |     |

| B1  | V <sub>SS</sub>    |     | D7  | V <sub>DD</sub> PE   |     | F13 | PERSTN               |     | J5  | V <sub>SS</sub>      |     |

| B2  | NC                 |     | D8  | V <sub>DD</sub> PE   |     | F14 | V <sub>SS</sub>      |     | J6  | V <sub>DD</sub> CORE |     |

| B3  | V <sub>SS</sub>    |     | D9  | V <sub>DD</sub> CORE |     | G1  | MSMBADDR_4           |     | J7  | V <sub>SS</sub>      |     |

| B4  | NC                 |     | D10 | V <sub>DD</sub> IO   |     | G2  | MSMBCLK              |     | J8  | V <sub>DD</sub> CORE |     |

| B5  | NC                 |     | D11 | V <sub>DD</sub> CORE |     | G3  | V <sub>DD</sub> IO   |     | J9  | V <sub>DD</sub> CORE |     |

| B6  | V <sub>SS</sub>    |     | D12 | V <sub>SS</sub>      |     | G4  | V <sub>SS</sub>      |     | J10 | V <sub>SS</sub>      |     |

| B7  | NC                 |     | D13 | SWMODE_2             |     | G5  | V <sub>DD</sub> CORE |     | J11 | V <sub>DD</sub> IO   |     |

| B8  | NC                 |     | D14 | SWMODE_1             |     | G6  | V <sub>SS</sub>      |     | J12 | V <sub>DD</sub> IO   |     |

| B9  | V <sub>SS</sub>    |     | E1  | SSMBADDR_1           |     | G7  | V <sub>SS</sub>      |     | J13 | GPIO_06              |     |

| B10 | NC                 |     | E2  | SSMBADDR_3           |     | G8  | V <sub>DD</sub> CORE |     | J14 | GPIO_04              | 1   |

| B11 | PE0TP00            |     | E3  | V <sub>DD</sub> IO   |     | G9  | V <sub>SS</sub>      |     | K1  | JTAG_TDI             |     |

| B12 | V <sub>SS</sub>    |     | E4  | V <sub>DD</sub> CORE |     | G10 | V <sub>SS</sub>      |     | K2  | V <sub>DD</sub> IO   |     |

| B13 | PE0RN00            |     | E5  | V <sub>SS</sub>      |     | G11 | V <sub>SS</sub>      |     | K3  | V <sub>DD</sub> APE  |     |

| B14 | V <sub>SS</sub>    |     | E6  | V <sub>SS</sub>      |     | G12 | V <sub>DD</sub> IO   |     | K4  | V <sub>SS</sub>      |     |

| C1  | WAKEN              |     | E7  | V <sub>SS</sub>      |     | G13 | GPIO_01              | 1   | K5  | V <sub>DD</sub> CORE |     |

| C2  | APWRDISN           |     | E8  | V <sub>SS</sub>      |     | G14 | RSTHALT              |     | K6  | V <sub>SS</sub>      |     |

| C3  | CCLKUS             |     | E9  | V <sub>SS</sub>      |     | H1  | MSMBADDR_1           |     | K7  | V <sub>SS</sub>      |     |

| C4  | V <sub>SS</sub>    |     | E10 | V <sub>DD</sub> CORE |     | H2  | MSMBADDR_2           |     | K8  | V <sub>SS</sub>      |     |

| C5  | V <sub>SS</sub>    |     | E11 | V <sub>SS</sub>      |     | H3  | MSMBADDR_3           |     | К9  | V <sub>SS</sub>      |     |

| C6  | V <sub>TT</sub> PE |     | E12 | V <sub>DD</sub> IO   |     | H4  | V <sub>DD</sub> CORE |     | K10 | V <sub>SS</sub>      |     |

Table 18 PES5T5 196-pin Signal Pin-Out (Part 1 of 2)

| Pin | Function             | Alt | Pin | Function             | Alt | Pin | Function        | Alt | Pin | Function        | Alt |

|-----|----------------------|-----|-----|----------------------|-----|-----|-----------------|-----|-----|-----------------|-----|

| K11 | V <sub>DD</sub> CORE |     | L12 | V <sub>SS</sub>      |     | M13 | MSMBSMODE       |     | N14 | PE5RN00         |     |

| K12 | V <sub>SS</sub>      |     | L13 | GPIO_10              | 1   | M14 | V <sub>SS</sub> |     | P1  | PEREFCLKP       |     |

| K13 | GPIO_08              |     | L14 | GPIO_09              | 1   | N1  | PEREFCLKN       |     | P2  | V <sub>SS</sub> |     |

| K14 | GPIO_07              | 1   | M1  | V <sub>SS</sub>      |     | N2  | V <sub>SS</sub> |     | P3  | PE2RP00         |     |

| L1  | JTAG_TCK             |     | M2  | V <sub>DD</sub> CORE |     | N3  | PE2RN00         |     | P4  | V <sub>SS</sub> |     |

| L2  | V <sub>SS</sub>      |     | M3  | V <sub>DD</sub> CORE |     | N4  | V <sub>SS</sub> |     | P5  | PE2TN00         |     |

| L3  | V <sub>SS</sub>      |     | M4  | V <sub>SS</sub>      |     | N5  | PE2TP00         |     | P6  | PE3TP00         |     |

| L4  | V <sub>DD</sub> IO   |     | M5  | V <sub>DD</sub> IO   |     | N6  | PE3TN00         |     | P7  | V <sub>SS</sub> |     |

| L5  | V <sub>DD</sub> CORE |     | M6  | V <sub>TT</sub> PE   |     | N7  | V <sub>SS</sub> |     | P8  | PE3RP00         |     |

| L6  | V <sub>DD</sub> CORE |     | M7  | V <sub>DD</sub> APE  |     | N8  | PE3RN00         |     | P9  | PE4RN00         |     |

| L7  | V <sub>DD</sub> PE   |     | M8  | V <sub>DD</sub> APE  |     | N9  | PE4RP00         |     | P10 | V <sub>SS</sub> |     |

| L8  | V <sub>DD</sub> PE   |     | M9  | V <sub>TT</sub> PE   |     | N10 | V <sub>SS</sub> |     | P11 | PE4TP00         |     |

| L9  | V <sub>DD</sub> CORE |     | M10 | V <sub>DD</sub> IO   |     | N11 | PE4TN00         |     | P12 | PE5TN00         |     |

| L10 | V <sub>DD</sub> CORE |     | M11 | V <sub>DD</sub> IO   |     | N12 | PE5TP00         |     | P13 | V <sub>SS</sub> |     |

| L11 | V <sub>SS</sub>      |     | M12 | REFCLKM              |     | N13 | V <sub>SS</sub> |     | P14 | PE5RP00         |     |

Table 18 PES5T5 196-pin Signal Pin-Out (Part 2 of 2)

### **Alternate Signal Functions**

| Pin | GPIO    | Alternate  |

|-----|---------|------------|

| F12 | GPIO_00 | P2RSTN     |

| G13 | GPIO_01 | P4RSTN     |

| H14 | GPIO_02 | IOEXPINTN0 |

| H13 | GPIO_03 | IOEXPINTN1 |

| J14 | GPIO_04 | IOEXPINTN2 |

| K14 | GPIO_07 | GPEN       |

| L14 | GPIO_09 | P3RSTN     |

| L13 | GPIO_10 | P5RSTN     |

Table 19 PES5T5 Alternate Signal Functions

### **Power Pins**

| V <sub>DD</sub> Core | V <sub>DD</sub> Core | V <sub>DD</sub> IO | V <sub>DD</sub> PE | V <sub>DD</sub> APE | V <sub>TT</sub> PE |

|----------------------|----------------------|--------------------|--------------------|---------------------|--------------------|

| D5                   | H10                  | C12                | D7                 | C7                  | C6                 |

| D6                   | H11                  | D4                 | D8                 | C8                  | С9                 |

| D9                   | J4                   | D10                | L7                 | K3                  | M6                 |

| D11                  | JG                   | E3                 | L8                 | M7                  | M9                 |

| E4                   | J8                   | E12                |                    | M8                  |                    |

| E10                  | J9                   | F4                 |                    |                     |                    |

| E13                  | K5                   | F11                |                    |                     |                    |

| F6                   | K11                  | G3                 |                    |                     |                    |

| F7                   | L5                   | G12                |                    |                     |                    |

| F9                   | L6                   | J11                |                    |                     |                    |

| F10                  | L9                   | J12                |                    |                     |                    |

| G5                   | L10                  | K2                 | -                  |                     |                    |

| G8                   | M2                   | L4                 | 1                  |                     |                    |

| H4                   | M3                   | M5                 | 1                  |                     |                    |

| H6                   |                      | M10                | 1                  |                     |                    |

| H7                   | ]                    | M11                | 1                  |                     |                    |

Table 20 PES5T5 Power Pins

### **Ground Pins**

| V <sub>ss</sub> | V <sub>ss</sub> | V <sub>ss</sub> | V <sub>ss</sub> |

|-----------------|-----------------|-----------------|-----------------|

| A1              | D3              | G10             | L3              |

| A3              | D12             | G11             | L11             |

| A6              | E5              | H5              | L12             |

| A9              | E6              | H8              | M1              |

| A12             | E7              | H9              | M4              |

| A14             | E8              | J5              | M14             |

| B1              | E9              | J7              | N2              |

| B3              | E11             | J10             | N4              |

| B6              | E14             | K4              | N7              |

| В9              | F5              | K6              | N10             |

| B12             | F8              | К7              | N13             |

| B14             | F14             | K8              | P2              |

| C4              | G4              | К9              | P4              |

| C5              | G6              | K10             | P7              |

| C11             | G7              | K12             | P10             |

| C13             | G9              | L2              | P13             |

Table 21 PES5T5 Ground Pins

### **No Connection Pins**

| Pin | Pin |

|-----|-----|

| A2  | B2  |

| A4  | B4  |

| A5  | B5  |

| A7  | B7  |

| A8  | B8  |

| A10 | B10 |

Table 22 PES5T5 No Connection Pins

### Signals Listed Alphabetically

| Signal Name | I/O Type | Location                 | Signal Category              |

|-------------|----------|--------------------------|------------------------------|

| APWRDISN    | ļ        | C2                       | System                       |

| CCLKDS      | l        | C10                      |                              |

| CCLKUS      | I        | C3                       |                              |

| GPIO_00     | I/O      | F12                      | General Purpose Input/Output |

| GPIO_01     | I/O      | G13                      | -                            |

| GPIO_02     | I/O      | H14                      | -                            |

| GPIO_03     | I/O      | H13                      | -                            |

| GPIO_04     | I/O      | J14                      | -                            |

| GPIO_05     | I/O      | H12                      | -                            |

| GPIO_06     | I/O      | J13                      | -                            |

| GPIO_07     | I/O      | K14                      | -                            |

| GPIO_08     | I/O      | K13                      | -                            |

| GPIO_09     | I/O      | L14                      | -                            |

| GPIO_10     | I/O      | L13                      | -                            |

| JTAG_TCK    |          | L1                       | JTAG                         |

| JTAG_TDI    |          | K1                       | -                            |

| JTAG_TDO    | 0        | J1                       | -                            |

| JTAG_TMS    |          | J3                       | -                            |

| JTAG_TRST_N |          | J2                       | -                            |

| MSMBADDR_1  |          | H1                       | SMBus                        |

| MSMBADDR_2  |          | H2                       | -                            |

| MSMBADDR_3  | I        | H3                       | -                            |

| MSMBADDR_4  | I        | G1                       | -                            |

| MSMBCLK     | I/O      | G2                       | -                            |

| MSMBDAT     | I/O      | F1                       | -                            |

| MSMBSMODE   |          | M13                      | System                       |

| NC          | Se       | g of No Connection pins. |                              |

| PE0RN00     |          | B13                      | PCI Express                  |

| PE0RP00     | I        | A13                      | 1                            |

| PE0TN00     | 0        | A11                      | 1                            |

| PE0TP00     | 0        | B11                      | 1                            |

| PE2RN00     |          | N3                       | 1                            |

| PE2RP00     |          | P3                       | 1                            |

| PE2TN00     | 0        | P5                       | 1                            |

Table 23 PES5T5 Alphabetical Signal List (Part 1 of 2)

| Signal Name                                                                                                             | I/O Type                                  | Location              | Signal Category        |  |

|-------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----------------------|------------------------|--|

| PE2TP00                                                                                                                 | 0                                         | N5                    | PCI Express (cont.)    |  |

| PE3RN00                                                                                                                 |                                           | N8                    |                        |  |

| PE3RP00                                                                                                                 | l                                         | P8                    |                        |  |

| PE3TN00                                                                                                                 | 0                                         | N6                    |                        |  |

| PE3TP00                                                                                                                 | 0                                         | P6                    |                        |  |

| PE4RN00                                                                                                                 |                                           | P9                    |                        |  |

| PE4RP00                                                                                                                 |                                           | N9                    |                        |  |

| PE4TN00                                                                                                                 | 0                                         | N11                   |                        |  |

| PE4TP00                                                                                                                 | 0                                         | P11                   |                        |  |

| PE5RN00                                                                                                                 |                                           | N14                   |                        |  |

| PE5RP00                                                                                                                 | ļ                                         | P14                   |                        |  |

| PE5TN00                                                                                                                 | 0                                         | P12                   |                        |  |

| PE5TP00                                                                                                                 | 0                                         | N12                   |                        |  |

| PEREFCLKN                                                                                                               | l                                         | N1                    |                        |  |

| PEREFCLKP                                                                                                               | l                                         | P1                    |                        |  |

| PERSTN                                                                                                                  | l                                         | F13                   | System                 |  |

| REFCLKM                                                                                                                 |                                           | M12                   | PCI Express            |  |

| RSTHALT                                                                                                                 |                                           | G14                   | System                 |  |

| SSMBADDR_1                                                                                                              | l                                         | E1                    | SMBus                  |  |

| SSMBADDR_2                                                                                                              | l                                         | F2                    |                        |  |

| SSMBADDR_3                                                                                                              |                                           | E2                    |                        |  |