### **Brief Description**

The ZSSC3170 is a CMOS integrated circuit for highly accurate amplification and sensor specific correction of bridge sensor signals. Featuring a maximum analog gain of 420, as well as extended offset compensation capabilities, the ZSSC3170 is adjustable to nearly all resistive bridge sensor types.

Digital compensation of offset, sensitivity, temperature drift, and nonlinearity is accomplished via a 16-bit RISC microcontroller. Conditioning coefficients are stored in an EEPROM certified for automotive applications.

Measured values are provided by one of the digital LIN or PWM interfaces. Each interface can support end-of-line calibration using the sensor output. Noise sensitivity is greatly reduced because the calibration equipment and the ZSSC3170 are mated digitally.

For quick and easy evaluation and support for calibrating prototypes, IDT offers the ZSSC3170 SSC Evaluation Kit, which includes evaluation hardware, SSOP20 samples, and software.

#### **Features**

- Complies with LIN specifications 1.3 / 2.0 / 2.1

- Configurable LIN publisher frame content

- Data conversion rate of up to 430Hz fully utilizes the maximum LIN channel capacity of 20kbit/s

- PWM high-side and low-side switches, support for LIN communication for end-of-line calibration

- Digital compensation of offset, gain, temperature effects up to 2<sup>nd</sup> order, and nonlinearity up to 3<sup>rd</sup> order. Compensation of temperature sensor offset, gain, and nonlinearity up to 2<sup>nd</sup> order.

- Internal or external temperature reference

- · Media temperature sensing by diode or RTD

- Load dump protection of the LIN pin up to ±40V

- Accuracy ±0.25% FSO @ -20 to 85°C

±0.50% FSO @ -40 to 125°C

±1.00% FSO @ -40 to 150°C

- 3 EEPROM words available for optional user data

#### **Benefits**

- Measurement and temperature signal available via one output pin

- · Compatible with nearly all resistive bridge inputs

- · No external trimming components required

- Single-pass calibration minimizes calibration costs

- End-of-line calibration using sensor output

- Optimized for automotive environments with special protection circuitry, excellent electromagnetic compatibility, and numerous diagnostic features; AEC-Q100-qualified

#### **Available Support**

- Evaluation Kit

- Application Notes

- Calculation Tools

### **Physical Characteristics**

- Supply voltage: 7 to 18 V

- Current consumption in Sleep Mode: ≤ 100µA

- Input span: 1.8 to 267 mV/V

- ADC resolution: 13 to 14 bit

- Output resolution: up to 12-bit (LIN and PWM)

- Operating temperature range: -40 to 125°C

- Extended operating temperature range: ≤150°C

- RoHS-compliant delivery form options: SSOP20, DFN20, or die

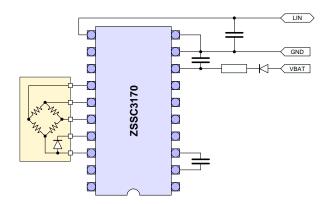

#### ZSSC3170 Basic Circuit

#### **Ordering Information** (See section 7 in the data sheet for additional options.)

| <b>Product Sales Code</b> | Description                                                     | Package                                                |

|---------------------------|-----------------------------------------------------------------|--------------------------------------------------------|

| ZSSC3170FE1B              | ZSSC3170 Die Revision F — Temperature range: -40°C to +150°C    | Unsawn on Wafer, 2450 pcs.                             |

| ZSSC3170FE1C              | ZSSC3170 Die Revision F — Temperature range: -40°C to +150°C    | Sawn on Wafer Frame, 2450 pcs.                         |

| ZSSC3170FE2               | ZSSC3170 SSOP20 Revision F — Temperature range: -40°C to +150°C | Add R for 13" reel, 2000 pcs. Add T for tube, 660 pcs. |

| ZSSC3170EE1B              | ZSSC3170 Die Revision E — Temperature range: -40°C to +150°C    | Unsawn on Wafer, 2450 pcs.                             |

| ZSSC3170EE1C              | ZSSC3170 Die Revision E — Temperature range: -40°C to +150°C    | Sawn on Wafer Frame, 2450 pcs.                         |

| ZSSC3170EE2               | ZSSC3170 SSOP20 Revision E — Temperature range: -40°C to +150°C | Add R for 13" reel, 2000 pcs. Add T for tube, 660 pcs. |

| ZSSC3170EE3R              | ZSSC3170 DFN20 Revision E — Temperature Range -40°C to +150°C   | 13" Reel, 4500 pcs                                     |

| ZSSC3170EA1B              | ZSSC3170 Die Revision E — Temperature range: -40°C to +125°C    | Unsawn on Wafer, 2450 pcs.                             |

| ZSSC3170EA1C              | ZSSC3170 Die Revision E — Temperature range: -40°C to +125°C    | Sawn on Wafer Frame, 2450 pcs.                         |

| ZSSC3170EA3R              | ZSSC3170 DFN20 Revision E — Temperature Range -40°C to +125°C   | 13" Reel, 4500 pcs                                     |

| ZSSC3170KIT               | ZSSC3170 Evaluation Kit and 5 SSOP20 samples                    | Kit                                                    |

# **Contents**

| 1 | ZS  | SC3170 Characteristics                                          | 5  |

|---|-----|-----------------------------------------------------------------|----|

|   | 1.1 | Absolute Maximum Ratings                                        | 5  |

|   | 1.2 | Operating Conditions                                            | 6  |

|   | 1.3 | Electrical Parameters                                           | 6  |

|   | 1.4 | Interface Characteristics                                       | 11 |

|   | 1.5 | EEPROM                                                          | 11 |

| 2 | Cir | cuit Description                                                | 12 |

|   | 2.1 | Signal Flow and Block Diagram                                   | 12 |

|   | 2.2 | Application Modes                                               | 13 |

|   | 2.3 | Analog Front End (AFE)                                          | 14 |

|   | 2.3 | .1 Programmable Gain Amplifier (PGA)                            | 14 |

|   | 2.3 | .2 Offset Compensation                                          | 14 |

|   | 2.3 | .3 Analog-to-Digital Converter                                  | 15 |

|   | 2.4 | Temperature Measurement                                         | 17 |

|   | 2.5 | System Control and Conditioning Calculation                     | 18 |

|   | 2.5 | .1 Operating Modes                                              | 18 |

|   | 2.5 | .2 Start-Up Phase                                               | 18 |

|   | 2.5 | .3 Measurement Cycle                                            | 19 |

|   | 2.5 | .4 Conditioning Calculation                                     | 20 |

|   | 2.6 | Signal Outputs                                                  | 20 |

|   | 2.6 | .1 PWM Outputs HOUT and LOUT                                    | 20 |

|   | 2.6 | .2 LIN Output                                                   | 21 |

|   | 2.7 | Digital Test and Calibration Interface                          | 21 |

|   | 2.8 | Diagnostic and Failsafe Features, Watchdog, and Error Detection | 21 |

|   | 2.9 | High Voltage, Reverse Polarity, and Short Circuit Protection    | 21 |

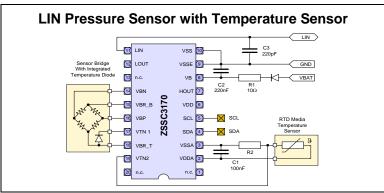

| 3 | Apı | olication Circuit Examples and External Components              | 22 |

|   | 3.1 | Application Circuit Examples                                    | 22 |

|   | 3.2 | Dimensioning of External Components                             |    |

| 4 | Pin | out and Package Options                                         | 24 |

| • | 4.1 | Die Pad Definitions and Configuration                           |    |

|   | 4.2 | SSOP20 Package                                                  |    |

|   | 4.3 | DFN20 Package                                                   |    |

|   |     |                                                                 |    |

| 5   | ESD P   | rotection and EMC Specification                                           | 26 |

|-----|---------|---------------------------------------------------------------------------|----|

| 6   | Reliabi | ility and RoHS Conformity                                                 | 26 |

| 7   | Orderii | ng Information                                                            | 26 |

| 8   | Relate  | d Documents                                                               | 27 |

| 9   | Glossa  | ary                                                                       | 27 |

| 10  | Docum   | nent Revision History                                                     | 29 |

| Li  | st of   | Figures                                                                   |    |

| Fig | ure 2.1 | Block Diagram of ZSSC3170                                                 | 12 |

| Fig | ure 2.2 | Measurement Cycle                                                         | 19 |

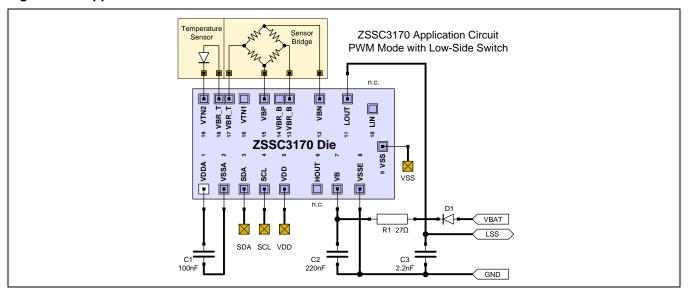

| Fig | ure 3.1 | Application Circuit in PWM Mode with Low-Side Switch                      | 22 |

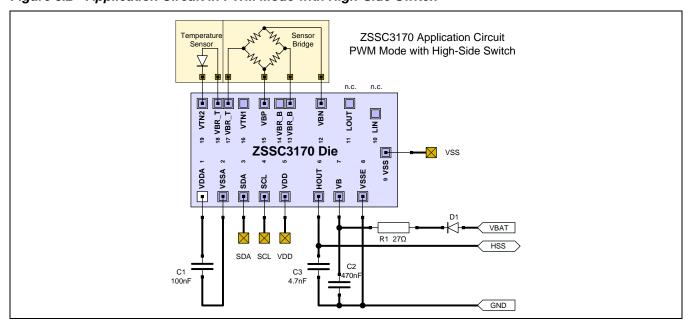

| Fig | ure 3.2 | Application Circuit in PWM Mode with High-Side Switch                     | 22 |

| _   |         | Application Circuit in LIN Mode                                           |    |

| Li  | st of   | Tables                                                                    |    |

| Tab | ole 1.1 | Absolute Maximum Ratings                                                  | 5  |

| Tab | ole 1.2 | Operating Conditions                                                      | 6  |

| Tab | ole 1.3 | Electrical Parameters                                                     | 6  |

| Tab | ole 1.4 | Interface Characteristics                                                 | 11 |

| Tab | ole 1.5 | EEPROM                                                                    | 11 |

| Tab | ole 2.1 | Configuration for Application Modes                                       | 13 |

| Tab | ole 2.2 | Adjustable Gain Stages, Corresponding Sensor Signal Spans, and Common Mod |    |

| Tab | ole 2.3 | Bridge Sensor Offset Shift Ranges                                         |    |

| Tab | ole 2.4 | A/D Resolution and Conversion Time in PWM Modes                           | 16 |

| Tab | ole 2.5 | A/D Resolution and Conversion Time in LIN Modes                           | 16 |

| Tab | ole 3.1 | Dimensioning of External Components for Application Examples              | 23 |

| Tab | ole 4.1 | Die Pad Definitions for ZSSC3170                                          | 24 |

| Tab | ole 4.2 | Pin Definition of SSOP20 Package                                          | 25 |

# 1 ZSSC3170 Characteristics

### 1.1 Absolute Maximum Ratings

The absolute maximum ratings are stress ratings only. The device might not function or be operable above the recommended operating conditions given in section 1.2. Stresses exceeding the absolute maximum ratings might also damage the device. In addition, extended exposure to stresses above the recommended operating conditions might affect device reliability. IDT does not recommend designing to the "Absolute Maximum Ratings."

Parameters are valid without time limit unless otherwise noted.

Table 1.1 Absolute Maximum Ratings

| No.    | Parameter                                                           | Symbol                               | Conditions             | Min  | Тур | Max          | Unit |

|--------|---------------------------------------------------------------------|--------------------------------------|------------------------|------|-----|--------------|------|

| 1.1.1  | External Supply Voltage — PWM Mode 1), 2)                           | VBAT <sub>PWM</sub>                  | To VSSE (external GND) | -18  |     | 18           | ٧    |

| 1.1.2  | Supply Voltage on VB Pin—<br>PWM Mode <sup>1), 2)</sup>             | $VB_{PWM}$                           | To VSSE                | -0.3 |     | 18           | V    |

| 1.1.3  | External Supply Voltage — LIN Mode 1), 2)                           | VBAT <sub>LIN</sub>                  | To VSS (external GND)  | -18  |     | 40           | V    |

| 1.1.4  | Supply Voltage on VB Pin—<br>LIN Mode <sup>1)</sup> , <sup>2)</sup> | $VB_{LIN}$                           | To VSS                 | -0.3 |     | 40           | V    |

| 1.1.5  | Voltage at HOUT and LOUT Pins 1, 2)                                 | $V_{\text{HOUT},}$ $V_{\text{LOUT}}$ | To VSSE                | -18  |     | 18           | V    |

| 1.1.6  | Voltage at LIN pin 1), 2)                                           | $V_{LIN}$                            | To VSS                 | -40  |     | 40           | V    |

| 1.1.7  | Analog Supply Voltage 3)                                            | VDDA                                 | To VSSA                | -0.3 |     | 6.5          | V    |

| 1.1.8  | Digital Supply Voltage 3)                                           | VDD                                  | To VSSA                | -0.3 |     | 6.5          | V    |

| 1.1.9  | Voltage at all other Analog or Digital Pins 3)                      | $V_{AIO},\ V_{DIO}$                  | To VSSA                | -0.3 |     | VDDA<br>+0.3 | V    |

| 1.1.10 | Storage Temperature                                                 | T <sub>STOR</sub>                    |                        | -40  |     | 150          | °C   |

| 1.1.11 | Extended Storage Temperature                                        | T <sub>STRG_EXT</sub>                | t < 10h                | -40  |     | 170          | °C   |

<sup>1)</sup> Refer to the ZSSC3170 High Voltage Protection Description for detailed specifications.

<sup>2)</sup> Refer to section 3.1 for the application circuit.

<sup>3)</sup> No measurement in mass production; parameter is guaranteed by design and/or quality monitoring.

### 1.2 Operating Conditions

Parameters are valid for the full operating temperature range without time limit unless otherwise noted.

Table 1.2 Operating Conditions

| No.   | Parameter                                        | Symbol               | Conditions                | Min | Тур | Max  | Unit |

|-------|--------------------------------------------------|----------------------|---------------------------|-----|-----|------|------|

| 1.2.1 | Supply Voltage 1)                                | VB                   | Voltage at pin VB to VSSE | 8.2 | 12  | 16.5 | V    |

| 1.2.2 | Supply Voltage - LIN Mode 1)                     | VB <sub>LIN</sub>    | Voltage at pin VB to VSS  | 7   | 12  | 18   | V    |

| 1.2.3 | Ambient Temperature                              | T <sub>AMB</sub>     |                           | -40 |     | 125  | °C   |

| 1.2.4 | Extended Ambient Temperature (ZSSC3170EExx only) | T <sub>AMB_EXT</sub> | 1000h @ +150°C            | 125 |     | 150  | °C   |

| 1.2.5 | Ambient Temperature<br>EEPROM Programming        | T <sub>AMB_EEP</sub> | See section 1.5.          | -40 |     | 150  | °C   |

| 1.2.6 | Bridge Resistance 2)                             | R <sub>BR</sub>      |                           | 2   |     | 25   | kΩ   |

<sup>1)</sup> Refer to the ZSSC3170 High Voltage Protection Description for detailed specifications.

### 1.3 Electrical Parameters

If not otherwise specified, all parameter limits are valid within operating conditions defined in section 1.2 and without time limit. All voltages are related to VSSA, if not otherwise specified.

Note: Refer to the important notes at the end of the table (page 10).

Table 1.3 Electrical Parameters

| No.     | Parameter                                                        | Symbol                                      | Conditions                                                                                                                                                | Min                     | Тур | Max       | Unit |  |  |

|---------|------------------------------------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----|-----------|------|--|--|

| 1.3.1   |                                                                  | Supply Current and Internal Supply Voltages |                                                                                                                                                           |                         |     |           |      |  |  |

| 1.3.1.1 | Supply Current                                                   | Is                                          | Excluding bridge supply current; excluding PWM current; oscillator adjusted (typical 2 MHz)                                                               |                         |     | 7         | mA   |  |  |

| 1.3.1.2 | Supply Current<br>LIN Sleep Mode                                 | I <sub>S_LINSLP</sub>                       | LIN Sleep Mode without current over LIN wire; PWM output pins not connected; VB <sub>LIN</sub> = 14.4V for max. value V <sub>LIN</sub> =VB <sub>LIN</sub> |                         | 40  | 100       | μА   |  |  |

| 1.3.1.3 | Internal Supply Voltage (generated internally)                   | $V_{VDA}$                                   | $V_{VDA} = V_{VDDA} - V_{VSSA}$<br>at $R_{BR} \ge 2k\Omega$ (see 1.2.6)                                                                                   | 4.3                     | 5   | 6         | V    |  |  |

| 1.3.1.4 | Supply Voltage Sensor<br>Bridge (internally at VDDA<br>and VSSA) | $V_{VBR}$                                   | $V_{VBR} = V_{VBR\_T} - V_{VBR\_B}$<br>at $R_{BR} \ge 2k\Omega$ (see 1.2.6)                                                                               | V <sub>VDA</sub> – 0.3V |     | $V_{VDA}$ |      |  |  |

<sup>2)</sup> No measurement in mass production; parameter is guaranteed by design and / or quality monitoring.

| No.     | Parameter                                                                                                    | Symbol                  | Conditions                                                                                                                                          | Min                                         | Тур | Max                                          | Unit                      |

|---------|--------------------------------------------------------------------------------------------------------------|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-----|----------------------------------------------|---------------------------|

| 1.3.2   |                                                                                                              | Ana                     | alog Front End (see section 2.3                                                                                                                     | 3)                                          |     |                                              |                           |

| 1.3.2.1 | Input Voltage Range                                                                                          | V <sub>IN_SPAN</sub>    | Analog gain: 2.8 to 420                                                                                                                             | 1                                           |     | 275                                          | mV/V                      |

| 1.3.2.2 | Maximum Bridge Sensor<br>Offset Compensation                                                                 | ОС                      | Depending on selected gain (see Table 2.3)                                                                                                          |                                             |     | 388                                          | %<br>V <sub>IN_SPAN</sub> |

| 1.3.2.3 | Bridge Input Current<br>Difference 1)                                                                        | I <sub>IN_DIFF</sub>    | T <sub>AMB</sub> = -25°C to 85°C                                                                                                                    | -2                                          |     | 2                                            | nA                        |

| 1.3.2.4 | Common Mode Input<br>Voltage Range                                                                           | V <sub>IN_CM</sub>      | Dependent on selected gain, XZC off (see Table 2.2); see 1.3.1.4 for V <sub>VBR</sub>                                                               | 0.29                                        |     | 0.65                                         | $V_{VBR}$                 |

| 1.3.3   |                                                                                                              | Tempera                 | ature Measurement (see section                                                                                                                      | on 2.4)                                     |     |                                              |                           |

| 1.3.3.1 | External Temperature<br>Diode Channel Gain                                                                   | A <sub>TSED</sub>       | FS = Full Scale                                                                                                                                     | 300                                         |     | 1300                                         | ppm<br>FS/mV              |

| 1.3.3.2 | External Temperature<br>Diode Bias Current                                                                   | I <sub>TSED</sub>       |                                                                                                                                                     | 10                                          | 20  | 40                                           | μА                        |

| 1.3.3.3 | External Temperature<br>Diode Input Range 1)                                                                 | $V_{TSED}$              | Relative to V <sub>VBR_T</sub>                                                                                                                      | 0                                           |     | 1.5                                          | V                         |

| 1.3.3.4 | External Temperature<br>Resistor Channel Gain                                                                | A <sub>TSER</sub>       |                                                                                                                                                     | 1200                                        |     | 4500                                         | ppm<br>FS/<br>(mV/V)      |

| 1.3.3.5 | External Temperature<br>Resistor Input Range 1)                                                              | $V_{TSER}$              | Relative to V <sub>VDDA</sub> -V <sub>VSSA</sub>                                                                                                    | 70%<br>V <sub>VDDA</sub> -V <sub>VSSA</sub> |     | 100%<br>V <sub>VDDA</sub> -V <sub>VSSA</sub> | V                         |

| 1.3.3.6 | Internal Temperature<br>Diode Sensitivity                                                                    | ST <sub>TSI</sub>       | Raw values, without conditioning calculation                                                                                                        | 700                                         |     | 2700                                         | ppm<br>FS/K               |

| 1.3.4   |                                                                                                              |                         | Sensor Diagnostic Tasks 2)                                                                                                                          |                                             |     |                                              |                           |

| 1.3.4.1 | Sensor Connection Loss<br>Resistance Threshold                                                               | RSCC <sub>TH</sub>      |                                                                                                                                                     | 20                                          |     | 100                                          | kΩ                        |

| 1.3.4.2 | Maximum Input<br>Capacitance for<br>Sensor Connection Check                                                  | cscc                    | Maximum: 10nF + 20%  If Sensor Short Check is enabled, the Sensor Connection Check High-Capacitances Mode must also be enabled. (Also see 1.3.4.3.) |                                             |     | 12                                           | nF                        |

| 1.3.4.3 | Maximum Input Capacitance for Sensor Connection Check with Sensor Short Check and Sensor Aging Check Enabled | CSCC <sub>SSC/SAC</sub> | Maximum: 1nF + 20% For using Sensor Short Check and Sensor Aging Check at the same time.                                                            |                                             |     | 1.2                                          | nF                        |

| 1.3.4.4 | Sensor Input Short<br>Resistance Threshold                                                                   | RSSC <sub>TH</sub>      |                                                                                                                                                     | 50                                          |     | 1000                                         | Ω                         |

| No.     | Parameter                                  | Symbol                 | Conditions                                                                                                                                                                     | Min                          | Тур      | Max  | Unit                  |  |

|---------|--------------------------------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|----------|------|-----------------------|--|

| 1.3.5   |                                            | A/D                    | Conversion (see section 2.3.                                                                                                                                                   | 3)                           |          |      |                       |  |

| 1.3.5.1 | ADC Resolution 1)                          | r <sub>ADC</sub>       |                                                                                                                                                                                |                              |          | 14   | Bit                   |  |

| 1.3.5.2 | DNL 1)                                     | DNL <sub>ADC</sub>     | r <sub>ADC</sub> = 14-bit, f <sub>OSC</sub> = 2MHz,<br>best fit, complete AFE;<br>see 1.3.5.4 for ADC <sub>INP_R</sub> .                                                       |                              |          | 0.95 | LSB                   |  |

| 1.3.5.3 | INL                                        | INL <sub>ADC</sub>     | r <sub>ADC</sub> = 14-bit, f <sub>OSC</sub> = 2MHz,<br>best fit, complete AFE;<br>see 1.3.5.4 for ADC <sub>INP_R</sub> .                                                       |                              |          | 8    | LSB                   |  |

| 1.3.5.4 | ADC Input Range                            | ADC <sub>INP_R</sub>   | See 1.3.1.4 for V <sub>VBR</sub> .                                                                                                                                             | 10                           |          | 90   | %<br>V <sub>VBR</sub> |  |

| 1.3.6   | PWM Output (Pins HOUT and LOUT) 2)         |                        |                                                                                                                                                                                |                              |          |      |                       |  |

| 1.3.6.1 | Output High Level – HSS;<br>HOUT Pin       | V <sub>HSS_</sub> H    | I <sub>SOURCE</sub> = 15mA,<br>VB ≥ 8.8V to VSSE                                                                                                                               | 4                            |          |      | V                     |  |

| 1.3.6.2 | Output Low Level – LSS;<br>LOUT Pin        | $V_{LSS\_L}$           | I <sub>SINK</sub> = 12mA to VSSE                                                                                                                                               |                              |          | 0.5V | V                     |  |

| 1.3.6.3 | Leakage Current<br>LOUT Pin                | I <sub>LEAK_LOUT</sub> | Sink; high level at LOUT                                                                                                                                                       |                              |          | 50   | μA                    |  |

| 1.3.6.4 | Rise Time HSS 1)                           | t <sub>HSS_RISE</sub>  | V <sub>HOUT</sub> = 0.5V→4V                                                                                                                                                    |                              |          | 15   | μs                    |  |

| 1.3.6.5 | Slew Rate HSS 1)                           | SR <sub>HSS</sub>      | V <sub>HOUT</sub> = 0.5V→4V                                                                                                                                                    |                              |          | 2    | V/µs                  |  |

| 1.3.6.6 | Fall Time LSS 1)                           | t <sub>LSS_FALL</sub>  | V <sub>LOUT</sub> = 4V→0.5V                                                                                                                                                    |                              |          | 15   | μs                    |  |

| 1.3.6.7 | Slew Rate LSS 1)                           | SR <sub>LSS</sub>      | V <sub>LOUT</sub> = 4V→0.5V                                                                                                                                                    | -2                           |          |      | V/µs                  |  |

| 1.3.6.8 | PWM Full-Scale<br>Resolution <sup>1)</sup> | r <sub>PWM_FS</sub>    | D = 1% to 99 %                                                                                                                                                                 | 11                           |          |      | Bit                   |  |

| 1.3.6.9 | Duty Cycle 1)                              | D                      | Adjustable with 8-bit resolution                                                                                                                                               | 1                            |          | 99   | %                     |  |

| 1.3.7   | (All voltages                              | LIN<br>related to V    | l Interface – Main Parameters<br>/SS; R <sub>VBAT LIN</sub> Power Supply Li                                                                                                    | <sup>3)</sup><br>ine Resista | nce = 50 | (nO) |                       |  |

| 1.3.7.1 | Output Low Level Transmitter               | V <sub>LIN_L</sub>     | CO, NVBAI_LIN I OWE! CUPPLY E                                                                                                                                                  | 0.6                          | 1.2      | 2.0  | V                     |  |

| 1.3.7.2 | Output High Level<br>Transmitter           | V <sub>LIN_H</sub>     | Driver off                                                                                                                                                                     | 0.9                          |          | 1    | VB                    |  |

| 1.3.7.3 | Output Current                             | I <sub>LIN_L</sub>     | Sink; driver on                                                                                                                                                                | 40                           | 90       | 200  | mA                    |  |

| 1.3.7.4 | Pull-Up Resistance                         | R <sub>LIN_PU</sub>    | In series with diode to VB                                                                                                                                                     | 20                           | 30       | 47   | kΩ                    |  |

| 1.3.7.5 | Input Current LIN Recessive,               | ILINPASrec             | $ \begin{array}{l} \text{-40°C} \leq T_{AMB} \leq 125^{\circ}\text{C}; \\ V_{LIN} \geq VB;  7V \leq VB \leq 18V; \\ 7V \leq V_{LIN} \leq 18V;  \text{driver off} \end{array} $ |                              | 3        | 20   | μА                    |  |

| 1.0.7.0 | Overvoltage at LIN                         | 'LIINP'ASTEC           | $\begin{aligned} &125^{\circ}C \leq T_{AMB} \leq 150^{\circ}C;\\ &V_{LIN} \geq VB; \ 7V \leq VB \leq 18V;\\ &7V \leq V_{LIN} \leq 18V; \ driver \ off \end{aligned}$           |                              | 3        | 50   | μΑ                    |  |

| No.      | Parameter                                         | Symbol                 | Conditions                                                                                                                                                                                                                                                  | Min   | Тур | Max   | Unit |

|----------|---------------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|------|

| 1.3.7.6  | Input Current LIN<br>Dominant                     | LINPASdom              | V <sub>LIN</sub> = 0V; VB = 12V;<br>driver off                                                                                                                                                                                                              | -1    |     |       | mA   |

| 1.3.7.7  | Input Current LIN<br>Recessive,<br>No GND for Bus | I <sub>LIN_NOGND</sub> | $ 0V \leq V_{LIN} \leq 18V; \\ V_{GND} = V_{VB}; \ VB = 12V $                                                                                                                                                                                               | -1    |     | 1     | mA   |

| 1.3.7.8  | Input Current LIN                                 |                        | $-40^{\circ}\text{C} \leq \text{T}_{\text{AMB}} \leq 125^{\circ}\text{C};$ $\text{V}_{\text{GND}} = \text{V}_{\text{SUP}} = 0\text{V};$ $0\text{V} \leq \text{V}_{\text{LIN}} \leq 18\text{V}$                                                              |       | 3   | 20    | μA   |

| 1.3.7.6  | No GND for Bus                                    | ILIN_LOSTVB            |                                                                                                                                                                                                                                                             |       | 3   | 50    | μA   |

| 1.3.7.9  | Slew Rate 3)                                      | SR <sub>LIN</sub>      | Rising and falling edges, transmit and receive                                                                                                                                                                                                              | 0.5   | 1.3 | 3     | V/µs |

| 1.3.7.10 | Input Low Level Receiver                          | V <sub>RECL</sub>      |                                                                                                                                                                                                                                                             |       |     | 0.4   | VB   |

| 1.3.7.11 | Input High Level Receiver                         | V <sub>RECH</sub>      |                                                                                                                                                                                                                                                             | 0.6   |     |       | VB   |

| 1.3.7.12 | Input Hysteresis Receiver                         | V <sub>RECHYS</sub>    | V <sub>RECHYS</sub> = V <sub>RECH</sub> - V <sub>RECL</sub>                                                                                                                                                                                                 | 0.08  |     | 0.12  | VB   |

| 1.3.7.13 | Input Center Point<br>Receiver                    | V <sub>BUS_CNT</sub>   | $V_{BUS\_CNT} = (V_{RECL} + V_{RECH})/2$                                                                                                                                                                                                                    | 0.475 | 0.5 | 0.525 | VB   |

| 1.3.7.14 | Duty Cycle 1                                      | D1                     | $TH_{Rec(max)} = 0.744 * VB; \\ TH_{Dom(max)} = 0.581 * VB; \\ VB = 7.0 \text{ to } 18V; \\ E_{Bit} = 50 \mu s; \\ D1 = t_{BUS\_rec(min)}/(2 * t_{Bit}) \\ (See ZSSC3170 LIN \\ Interface Description \\ for details.)$                                     | 0.396 |     |       | -    |

| 1.3.7.15 | Duty Cycle 2                                      | D2                     | $\begin{split} TH_{Rec(min)} &= 0.422 * VB; \\ TH_{Dom(min)} &= 0.284 * VB; \\ VB &= 7.6 \text{ to } 18V; \ t_{Bit} = 50 \mu s; \\ D1 &= t_{BUS\_rec(max)}/(2 * t_{Bit}) \\ (See \ ZSSC3170 \ LIN \ Interface \ Description \\ for \ details.) \end{split}$ |       |     | 0.581 | -    |

| 1.3.7.16 | Duty Cycle 3                                      | D3                     | $TH_{Rec(max)} = 0.778 * VB; \\ TH_{Dom(max)} = 0.616 * VB; \\ VB = 7.0 \text{ to } 18V; t_{Bit} = 96\mu s; \\ D3 = t_{BUS\_rec(min)}/(2 * t_{Bit}) \\ (See ZSSC3170 LIN \\ Interface Description \\ \text{for details.})$                                  | 0.417 |     |       | -    |

| No.      | Parameter                                                                | Symbol                            | Conditions                                                                                                                                                                                                 | Min | Тур | Max   | Unit |

|----------|--------------------------------------------------------------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|------|

| 1.3.7.17 | Duty Cycle 4                                                             | D4                                | $TH_{Rec(min)} = 0.389 * VB; \\ TH_{Dom(min)} = 0.251 * VB; \\ VB = 7.6 to 18V; t_{Bit} = 96\mu s; \\ D4 = t_{BUS\_rec(max)}/(2 * t_{Bit}) \\ (See ZSSC3170 LIN \\ Interface Description \\ for details.)$ |     |     | 0.590 | -    |

| 1.3.8    |                                                                          |                                   | System Response                                                                                                                                                                                            |     |     |       |      |

| 1.3.8.1  | Start-Up Time 1)                                                         | t <sub>START</sub>                | Until first valid output;<br>f <sub>OSC</sub> = 2MHz                                                                                                                                                       |     |     | 30    | ms   |

| 1.3.8.2  | Response Time<br>LIN_Mode;<br>Typical LIN<br>Configuration <sup>4)</sup> | t <sub>RESP</sub> _<br>LIN_2_14_5 | f <sub>OSC</sub> = 2.2MHz; 14-bit<br>resolution; LIN Mode;<br>100% final value<br>(see Table 2.5)                                                                                                          |     |     | 3.6   | ms   |

| 1.3.8.3  | Response Time PWM<br>Mode; Typical PWM<br>Configuration <sup>5)</sup>    | t <sub>RESP</sub> _<br>PWM_2_14_2 | f <sub>OSC</sub> = 1.8MHz; 14-bit<br>resolution; PWM Mode;<br>100% final value<br>(see Table 2.4)                                                                                                          |     |     | 20    | ms   |

| 1.3.8.4  | Overall Error AFE 6), 7)                                                 | F <sub>AFE_85</sub>               | T <sub>AMB</sub> : -20°C to 85°C                                                                                                                                                                           |     |     | 0.25  | %FS  |

|          | (f <sub>OSC</sub> = 2MHz, XZC off;<br>no sensor related errors;          | F <sub>AFE_125</sub>              | T <sub>AMB</sub> : -40°C to 125°C                                                                                                                                                                          |     |     | 0.5   | %FS  |

|          | relative to digital value)                                               | F <sub>AFE_150</sub>              | T <sub>AMB</sub> : -40°C to 150°C                                                                                                                                                                          |     |     | 1.0   | %FS  |

<sup>1)</sup> No measurement in mass production; parameter is guaranteed by design and/or quality observation.

<sup>2)</sup> In PWM Mode with Low-Side Switch (LSS) and PWM Mode with High-Side Switch (HSS), the sensor connection check (SCC) and the sensor short check (SSC) diagnostics are available only for ZSSC3170 silicon revision "F" and any subsequent revisions

<sup>3)</sup> For complete specification, see the ZSSC3170 LIN Interface Description.

<sup>4) 2-</sup>step A/D conversion (ADCORD=1), 14-bit resolution (ADCRES=1), resolution 2nd conversion step 5-bit (ADCMODE=11)

<sup>5) 2-</sup>step A/D conversion (ADCORD=1), 14-bit resolution (ADCRES=1), resolution 2nd conversion step 2-bit (ADCMODE=00)

<sup>6)</sup> Deviation from ideal line including INL, gain, offset, and temperature errors.

<sup>7)</sup> With XZC active: additional total error of max. 25ppm/K at XZC = 31. Error decreases linearly at XZC < 31.

# 1.4 Interface Characteristics

Table 1.4 Interface Characteristics

| No.      | Parameter                           | Symbol                  | Conditions                              | Min        | Тур | Max  | Unit |

|----------|-------------------------------------|-------------------------|-----------------------------------------|------------|-----|------|------|

| 1.4.1    |                                     |                         | I <sup>2</sup> C™ Interface             |            |     |      |      |

| 1.4.1.1  | Input High Level 1)                 | $V_{I2C\_IN\_H}$        |                                         | 0.8        |     |      | VDDA |

| 1.4.1.2  | Input Low Level 1)                  | $V_{I2C\_IN\_L}$        |                                         |            |     | 0.2  | VDDA |

| 1.4.1.3  | Output Low Level 1)                 | $V_{I2C\_OUT\_L}$       | Open drain output current: < 2mA        |            |     | 0.15 | VDDA |

| 1.4.1.4  | SDA Load Capacity 1)                | $C_{SDA}$               |                                         |            |     | 400  | pF   |

| 1.4.1.5  | SCL Clock Frequency 1)              | f <sub>SCL</sub>        |                                         |            |     | 400  | kHz  |

| 1.4.1.6  | Internal Pull-Up Resistor 1)        | R <sub>I2C</sub>        |                                         | 25         |     | 100  | kΩ   |

| 1.4.2    |                                     | One-Wire Int            | erface at HOUT and LOUT (I              | LIN Protoc | ol) |      |      |

| 1.4.2.1  | Input Low Level 1)                  | $V_{OWI\_IN\_L}$        |                                         |            |     | 1    | ٧    |

| 1.4.2.2  | Input High Level 1)                 | $V_{\text{OWI\_IN\_H}}$ |                                         | 4          |     |      | V    |

| 1.4.2.3  | Start Window 1)                     | t <sub>START_WIN</sub>  | At f <sub>OSC</sub> = 2MHz              |            |     | 30   | ms   |

| 1) No me | asurement in mass production; param | eter is guarantee       | d by design and/or quality observation. | -          |     |      |      |

# 1.5 EEPROM

Table 1.5 EEPROM

| No.   | Parameter        | Symbol                   | Conditions                                      | Min | Тур | Max                 | Unit |

|-------|------------------|--------------------------|-------------------------------------------------|-----|-----|---------------------|------|

| 1.5.1 | Write Cycles     | NEEP_WRI_85              | T <sub>AMB</sub> < 85°C                         |     |     | 1000                |      |

| 1.5.1 | Write Cycles     | n <sub>EEP_WRI_150</sub> | T <sub>AMB</sub> < 150°C                        |     |     | 100                 |      |

| 1.5.2 | Read Cycles      | n <sub>eep_rd</sub>      |                                                 |     |     | 8 * 10 <sup>8</sup> |      |

| 1.5.3 | Data Retention   | t <sub>EEP_RET</sub>     | 100000h@55°C<br>+ 27000h@125°C<br>+ 3000h@150°C |     |     | 15                  | а    |

| 1.5.4 | Programming Time | t <sub>EEP_WRI</sub>     | Per written word, at f <sub>OSC</sub> = 2MHz    |     | 12  |                     | ms   |

# 2 Circuit Description

#### 2.1 Signal Flow and Block Diagram

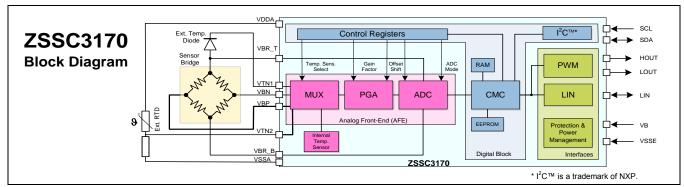

The signal path of the ZSSC3170 consists of the analog front end (AFE), the digital signal processing block, and interfaces including protection circuitry. Based on a differential structure, the bridge inputs VBP and VBN are handled by two signal lines each with a dynamic range symmetrical to the common mode potential (analog ground equal to VDDA/2). Therefore it is possible to amplify positive and negative input signals within the common mode range of the signal input.

VDDA\_\_ SCL I<sup>2</sup>CTM\* Ext. Temp Control Registers Diode VBR 1 HOUT Bridge Temp. Sens Select ADC Mode RAM **PWM** Offset Shift LOUT VTN1 C VBN\_\_ MUX PGA ADC CMC LIN LIN  $\ell_{oldsymbol{e}}$ Analog Front-End (AFE EEPROM Protection & Management VSSE VBR B Digital Block ZSSC3170 \* I2C™ is a trademark of NXP.

Figure 2.1 Block Diagram of ZSSC3170

The multiplexer (MUX) transmits the signals from either the bridge sensor or the selected temperature sensors to the analog-to-digital converter (ADC) in a defined sequence. The temperature sensor can either be an external or internal diode or an external thermistor (RTD), selected by EEPROM configuration. In LIN Mode, temperature output is available. For this temperature measurement, the same temperature sensor can be used as for calibration temperature, or a second temperature sensor input can be selected. The differential signal from the bridge sensor is pre-amplified by the programmable gain amplifier (PGA). The ADC converts bridge sensor and temperature signals into digital values.

The digital signal conditioning takes place in the calibration microcontroller (CMC) using a ROM-resident conditioning formula and sensor-specific coefficients stored in the EEPROM during calibration. The configuration data and the correction parameters can be programmed into the EEPROM by digital communication at the output pins or at the I<sup>2</sup>C™ interface. Depending on the programmed output configuration, the corrected sensor signal is output as a PWM signal (high-side switch or low-side switch) or as a digital value within a LIN frame. During the calibration procedure, the I<sup>2</sup>C™ interface can provide measurement values as well.

# 2.2 Application Modes

For each application, a configuration set must be established (generally prior to calibration) by programming the on-chip EEPROM for the following modes:

Table 2.1 Configuration for Application Modes

| Bridge Sensor Channel                                             |                                                                                                                                                                |  |  |  |

|-------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Input Voltage Range                                               | Select gain stage of the AFE with respect to the maximum sensor signal span and the zero point of the ADC.                                                     |  |  |  |

| Bridge Sensor Offset<br>Compensation (XZC)                        | Activate the analog sensor offset compensation if required; e.g., if the sensor offset voltage is close to or larger than the sensor span.                     |  |  |  |

| Resolution/Response Time                                          | Select appropriate resolution of the ADC. Settings will influence sampling rate, signal integration time, and therefore sensitivity to noise and disturbances. |  |  |  |

| Temperature Measurement                                           |                                                                                                                                                                |  |  |  |

| Temperature Measurement for the Correction of the Bridge Signal   | Select temperature sensor to calibrate temperature related errors.                                                                                             |  |  |  |

| Temperature Measurement for the<br>Temperature Output in LIN Mode | Select temperature sensor for temperature measurement.                                                                                                         |  |  |  |

| Output Signal                                                     |                                                                                                                                                                |  |  |  |

| Output Mode                                                       | Select PWM or LIN according to application requirements.                                                                                                       |  |  |  |

| LIN Mode                                                          | Select LIN compatibility to specification package LIN2.1, LIN2.0, or LIN1.3.                                                                                   |  |  |  |

| PWM Mode                                                          | Select switch type: high-side switch (HSS) or low-side switch (LSS).                                                                                           |  |  |  |

## 2.3 Analog Front End (AFE)

The analog front end (AFE) consists of the signal multiplexer (MUX), the programmable gain amplifier (PGA) and the analog-to-digital converter (ADC).

#### 2.3.1 Programmable Gain Amplifier (PGA)

Table 2.2 shows the adjustable gains, corresponding sensor signal spans, and common mode range limits. See section 2.3.2 for details for XZC.

Table 2.2 Adjustable Gain Stages, Corresponding Sensor Signal Spans, and Common Mode Ranges

| Overall<br>Gain | Maximum Input<br>Voltage Range            | Gain<br>Amp1 | Gain<br>Amp2 | Gain<br>Amp3 | Input Common Mode Range<br>V <sub>IN_CM</sub> [%VDDA] <sup>2)</sup> |                |

|-----------------|-------------------------------------------|--------------|--------------|--------------|---------------------------------------------------------------------|----------------|

| a <sub>IN</sub> | V <sub>IN_SPAN</sub> [mV/V] <sup>1)</sup> |              |              |              | XZC off                                                             | XZC on         |

| 420             | 1.8                                       | 30           | 7            | 2            | 29 to 65                                                            | 45 to 55       |

| 280             | 2.7                                       | 30           | 4.66         | 2            | 29 to 65                                                            | 45 to 55       |

| 210             | 3.6                                       | 15           | 7            | 2            | 29 to 65                                                            | 45 to 55       |

| 140             | 5.4                                       | 15           | 4.66         | 2            | 29 to 65                                                            | 45 to 55       |

| 105             | 7.1                                       | 7.5          | 7            | 2            | 29 to 65                                                            | 45 to 55       |

| 70              | 10.7                                      | 7.5          | 4.66         | 2            | 29 to 65                                                            | 45 to 55       |

| 52.5            | 14.3                                      | 3.75         | 7            | 2            | 29 to 65                                                            | 45 to 55       |

| 35              | 21.4                                      | 3.75         | 4.66         | 2            | 29 to 65                                                            | 45 to 55       |

| 26.3            | 28.5                                      | 3.75         | 3.5          | 2            | 29 to 65                                                            | 45 to 55       |

| 14              | 53.75                                     | 1            | 7            | 2            | 29 to 65                                                            | 45 to 55       |

| 9.3             | 80                                        | 1            | 4.66         | 2            | 29 to 65                                                            | 45 to 55       |

| 7               | 107                                       | 1            | 3.5          | 2            | 29 to 65                                                            | 45 to 55       |

| 2.8             | 267                                       | 1            | 1.4          | 2            | 32 to 57                                                            | Not applicable |

<sup>1)</sup> Recommended internal signal range: maximum 80% supply voltage. Range is defined by 80% of supply voltage divided by selected gain.

#### 2.3.2 Offset Compensation

The ZSSC3170 supports two methods of sensor offset compensation:

- Digital offset correction is processed during the digital signal conditioning by the calibration microcontroller (CMC).

- Bridge sensor offset compensation (XZC) is achieved by adding a compensation voltage at the analog signal path that removes coarse offset. XZC is needed for large offset values that would otherwise overdrive the analog signal path, and it can be adjusted by 6 EEPROM bits. Depending on the gain adjustment, XZC can handle offset values of up to 300% of the sensor signal range.

<sup>2)</sup> At maximum input signal (with XZC: +300% offset).

Table 2.3 Bridge Sensor Offset Shift Ranges

| Overall Gain<br>a <sub>IN</sub> | Maximum Input<br>Voltage Range<br>V <sub>IN_SPAN</sub> (mV/V) | Offset Shift<br>per Step<br>(%Full Span) | Approximate Maximum Offset Shift (mV/V) | Approximate Maximum Offset Shift (%V <sub>IN_SPAN</sub> ) |

|---------------------------------|---------------------------------------------------------------|------------------------------------------|-----------------------------------------|-----------------------------------------------------------|

| 420                             | 1.8                                                           | 12.5                                     | 7.8                                     | 388                                                       |

| 280                             | 2.7                                                           | 7.6                                      | 7.1                                     | 237                                                       |

| 210                             | 3.6                                                           | 12.5                                     | 15.5                                    | 388                                                       |

| 140                             | 5.4                                                           | 7.6                                      | 14.2                                    | 237                                                       |

| 105                             | 7.1                                                           | 12.5                                     | 31                                      | 388                                                       |

| 70                              | 10.7                                                          | 7.6                                      | 28                                      | 237                                                       |

| 52.5                            | 14.3                                                          | 12.5                                     | 62                                      | 388                                                       |

| 35                              | 21.4                                                          | 7.6                                      | 57                                      | 237                                                       |

| 26.3                            | 28.5                                                          | 5.2                                      | 52                                      | 161                                                       |

| 14                              | 53.6                                                          | 12.5                                     | 233                                     | 388                                                       |

| 10                              | 80                                                            | 7.6                                      | 207                                     | 237                                                       |

| 7                               | 107                                                           | 5.2                                      | 194                                     | 161                                                       |

| 2.8                             | 267                                                           | 0.83                                     | 78                                      | 26                                                        |

#### 2.3.3 Analog-to-Digital Converter

The analog-to-digital converter (ADC) is designed in full differential switched capacitor technology with a selectable resolution of 13 or 14 bits. The ADC can operate in first or second order configuration. The conversion is largely insensitive to short-term and long-term instabilities of the clock frequency.

- MSB segment conversion: In this first step of the A/D conversion, the measurement value is integrated

over the complete conversion time ensuring a high degree of noise suppression. To extend the integration

phase to the maximum, this fraction of the complete conversion time is selected to be as long as possible

corresponding to the time available.

- LSB segment conversion: To achieve a higher resolution, the residual value of the first step is converted in a subsequent step by a second converter. In first-order configuration, the second step is skipped (single-step conversion).

Table 2.4 A/D Resolution and Conversion Time in PWM Modes

| Mode                 | A/D Resolution<br>Total<br>(bit)                     | A/D Resolution<br>MSB Segment<br>Conversion<br>(bit) | A/D Resolution<br>LSB Segment<br>Conversion<br>(bit) | A/D Conversion<br>Mode<br>ADC MODE 1) | PWM Cycle Time<br>(f <sub>OSC</sub> = 1.8MHz)<br>(ms) |  |

|----------------------|------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|---------------------------------------|-------------------------------------------------------|--|

|                      | 14                                                   | 12                                                   | 2                                                    | 00                                    | 19.9                                                  |  |

|                      | 14                                                   | 11                                                   | 3                                                    | 01                                    | 10.8                                                  |  |

|                      | 14                                                   | 10                                                   | 4                                                    | 10                                    | 6.3                                                   |  |

| PWM /<br>ADC         | 14                                                   | 9                                                    | 5                                                    | 11                                    | 4.0                                                   |  |

| 2 step <sup>1)</sup> | 13                                                   | 11                                                   | 2                                                    | 00                                    | 10.8                                                  |  |

|                      | 13                                                   | 10                                                   | 3                                                    | 01                                    | 6.3                                                   |  |

|                      | 13                                                   | 9                                                    | 4                                                    | 10                                    | 4.0                                                   |  |

|                      | 13                                                   | 8                                                    | 5                                                    | 11                                    | 2.8                                                   |  |

| PWM/                 | 14                                                   | 14                                                   | n/a                                                  | n/a                                   | 37.5                                                  |  |

| ADC<br>1 step        | 13                                                   | 13                                                   | n/a                                                  | n/a                                   | 19.3                                                  |  |

| 1) See th            | See the ZSSC3170 Functional Description for details. |                                                      |                                                      |                                       |                                                       |  |

Table 2.5 A/D Resolution and Conversion Time in LIN Modes

| Mode                   | A/D Resolution<br>Total<br>(bit) | A/D Resolution<br>MSB Segment<br>Conversion<br>(bit) | A/D Resolution<br>LSB Segment<br>Conversion<br>(bit) | A/D Conversion<br>Mode<br>ADC MODE <sup>1)</sup> | Response Time <sup>2)</sup> in LIN Mode (fosc = 2.2MHz) (ms) |

|------------------------|----------------------------------|------------------------------------------------------|------------------------------------------------------|--------------------------------------------------|--------------------------------------------------------------|

|                        | 14                               | 12                                                   | 2                                                    | 00                                               | 16.3                                                         |

|                        | 14                               | 11                                                   | 3                                                    | 01                                               | 8.9                                                          |

|                        | 14                               | 10                                                   | 4                                                    | 10                                               | 5.2                                                          |

| LIN /<br>ADC<br>2 step | 14                               | 9                                                    | 5                                                    | 11                                               | 3.3                                                          |

|                        | 13                               | 11                                                   | 2                                                    | 00                                               | 8.9                                                          |

|                        | 13                               | 10                                                   | 3                                                    | 01                                               | 5.2                                                          |

|                        | 13                               | 9                                                    | 4                                                    | 10                                               | 3.3                                                          |

|                        | 13                               | 8                                                    | 5                                                    | 11                                               | 2.4                                                          |

| LIN /                  | 14                               | 14                                                   | n/a                                                  | n/a                                              | 61.5                                                         |

| ADC<br>1 step          | 13                               | 13                                                   | n/a                                                  | n/a                                              | 31.7                                                         |

<sup>1)</sup> See the ZSSC3170 Functional Description for details.

<sup>2)</sup> Total response time.

Equation (1) describes the conversion result:

$$Z_{ADC} = 2^{r} * \left( \frac{V_{ADC\_IN}}{V_{ADC\_REF} - RS_{ADC}} \right)$$

(1)

Where

Z<sub>ADC</sub> A/D conversion resultr A/D resolution in bits

$V_{ADC\_IN}$  Differential input voltage of ADC  $V_{ADC\_REF}$  Differential reference voltage of ADC

RS<sub>ADC</sub> ADC range shift adjustable by EEPROM configuration (RS<sub>ADC</sub> =  $\frac{1}{16}$ ,  $\frac{1}{8}$ ,  $\frac{1}{4}$ ,  $\frac{1}{2}$ )

By selecting different values of  $RS_{ADC}$ , the user can match the sensor input signal to the optimum input voltage range of the ADC. The ADC reference voltage  $V_{ADC\_REF}$  is defined as the difference between the bridge supply potentials at pins  $VBR\_T$  and  $VBR\_B$ . The theoretical ADC input voltage range  $ADC_{INP\_R}$  is equal to this ADC reference voltage.

A major constraint required for achieving the specified precision as well as the stability and nonlinearity parameters of the AFE is to use a maximum ADC input voltage range of 10% to 90% of ADC<sub>INP\_R</sub> within the application. This is of special importance for ensuring the specified parameters for the entire operating temperature range as well as all possible sensor bridge tolerances. The validity of these conditions is not checked by the ZSSC3170's failsafe functions and therefore must be ensured by the customer-specific configuration.

#### 2.4 Temperature Measurement

The following temperature sensors are supported by ZSSC3170 for both temperature and calibration temperature measurement:

- Internal pn-diode

- External pn-diode; anode to pin VBR\_T

- External resistive half-bridge with the thermistor connected in the upper branch

In PWM Mode, the conditioning calculation for the bridge sensor signal is based on values of the selected temperature sensor.

In LIN Mode, two temperature measurements are executed using either two different sensors or one sensor for both measurements. The temperature output value is the result of a conditioning calculation including offset compensation, gain correction, and 2<sup>nd</sup> order nonlinearity compensation. The conditioning coefficients are stored in the EEPROM.

#### 2.5 System Control and Conditioning Calculation

The system control performs the following tasks:

- · Sequencing of the start-up phase

- Control of measurement cycle based on EEPROM configuration data

- 16-bit conditioning calculation for each measurement signal based on EEPROM conditioning coefficients and ROM-resident signal conditioning algorithm

- · Processing of communication requests received at the serial interfaces

- · Control of calibration mode

- Processing of diagnostic and failsafe tasks

For a detailed description, refer to the ZSSC3170 Functional Description.

#### 2.5.1 Operating Modes

Three main modes are implemented in the integrated state machine:

- Normal Operation Mode (NOM) with continuous signal conditioning

- Command Mode (CM), which provides access to all internal registers and provides the basis for configuration and calibration of the ZSSC3170

- Diagnostic Mode (DM), which indicates detected error conditions

#### 2.5.2 Start-Up Phase

The start-up phase consists of the following time periods:

- Settling of the internal voltage supply represented by the voltage VDDA-VSSA. At the end of this period, the power-on-reset circuit (POR) switches off the reset signal.

- System start, readout of EEPROM, and signature check.

- Processing of the signal conditioning start routine containing bridge sensor signal and temperature

measurements, associated auto-zero measurements, and the conditioning calculation itself. Within this

period, the output pins are ready to receive special LIN frames resulting in entering the Command Mode

(CM). This start window is active for up to 30ms.

The ZSSC3170 switches into Normal Operation Mode (NOM) after the start window is passed. It proceeds with the cyclic processing of the measurement and conditioning tasks.

#### 2.5.3 Measurement Cycle

Depending on the EEPROM settings, the multiplexer selects the following inputs in a defined sequence:

- · Pre-amplified sensor bridge signal

- Temperature sensor defined by EEPROM configuration for calibration temperature

- Temperature sensor defined by EEPROM configuration for temperature measurement

- Auto-zero signal

- Diagnostic signals

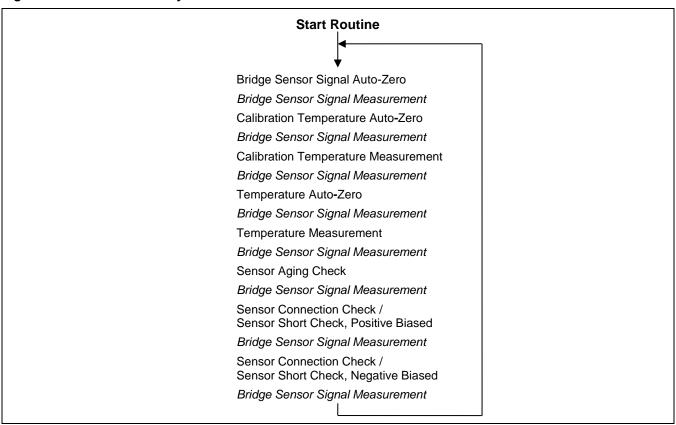

The CMC controls the complete measurement cycle following a basic flow shown in Figure 2.2.

All necessary measurements for bridge sensor and temperature signal are executed once after power-on within the start-up routine. This initial phase is followed by continuous processing of the complete measurement cycle. The sensor connection check (SCC), sensor short check (SSC), and sensor aging check (SAC) for diagnostic tasks (see section 2.8) are continuously executed within the regular measurement cycle even if the processing of the diagnostic function is disabled by the EEPROM configuration.

For details, refer to the ZSSC3170 Functional Description.

Figure 2.2 Measurement Cycle

#### 2.5.4 Conditioning Calculation

After digital auto-zero correction of the bridge sensor measurement value, the interim result is further processed based on the correction formula. Offset and gain with temperature effects up to 2<sup>nd</sup> order and non-linearity up to 3<sup>rd</sup> order can be compensated for, resulting in a positive 15-bit bridge sensor result value normalized to the range of [0;1].

In LIN Mode, the digital measurement value of the temperature is processed based on a proprietary correction formula as well. Offset, gain, and non-linearity up to 2<sup>nd</sup> order can be compensated for yielding a positive 15-bit temperature value normalized to the range of [0;1].

### 2.6 Signal Outputs

ZSSC3170 provides three signal outputs:

- LIN LIN Interface revision 2.1/2.0 with compatibility to revision 1.3

- HOUT PWM high-side switch (HSS)

- LOUT PWM low-side switch (LSS)

For the respective application, one signal output must be selected and configured as the active output. Idle outputs must be not connected.

To enter the Command Mode (CM), communication can be established at each of the three output pins. A dedicated command must be sent during the start window immediately after power-on (duration  $t_{START\_WN}$ ; see specification 1.4.2.3). The communication protocol at all pins is based on the LIN Data Link Layer. Note that communication at the HOUT pin uses the inverted signal levels of the LIN frame. In LIN Mode, communication at the LIN pin is always possible during Normal Operation Mode (NOM).

To enable communication within the start window, the output drivers are set to tri-state during this time. The outputs HOUT and LOUT are connected to internal pull-up resistors to ensure the necessary resistive stage. For the LIN transceiver, an internal pull-up resistor is implemented by default (according to the LIN Specification Package, Physical Layer section).

If not switched into CM before expiration of the 30ms start window, depending on the configuration, the ZSSC3170 will start to provide a PWM signal or can respond to communication requests of the LIN master.

The function set of the signal outputs is specified in detail in the following documents: the ZSSC3170 Functional Description and the ZSSC3170 LIN Interface Description.

Note: LIN Sleep Mode must be disabled for proper PWM operation.

#### 2.6.1 PWM Outputs HOUT and LOUT

In PWM Mode, the output signal is provided at the pins HOUT or LOUT accordingly.

The outputs are protected from short circuit overload by current limiters and time monitoring. Driving the signal lines with slew-rate-limited edges reduces electromagnetic emission. At the HOUT pin, a voltage higher than the maximum supply voltage can be tolerated. The notably low leakage current of LOUT is designed to cover the requirements of some unique electronic control units (ECU).

#### 2.6.2 LIN Output

The output of the integrated LIN transceiver at the LIN pin is compatible with the LIN revisions 2.1, 2.0 and 1.3. For details, refer to the *ZSSC3170 LIN Interface Description*. For LIN Physical Layer Conformance Tests, the control pins of the integrated LIN transceiver can be accessed separately in a LIN Conformance Test Mode.

### 2.7 Digital Test and Calibration Interface

Beyond the digital communication features accessed via the output pins, the ZSSC3170 provides an  $I^2C^{TM}$  compatible test and calibration interface with slave functionality. For a detailed description of the  $I^2C^{TM}$  interface, refer to the ZSSC3170 Functional Description.

### 2.8 Diagnostic and Failsafe Features, Watchdog, and Error Detection