# NxH3670UK

# Ultra-low power 2.4 GHz Bluetooth Low Energy transceiver for audio streaming

Rev. 3.3 — 13 November 2020

Product data sheet

### 1 General description

The NXH3670UK constitutes a highly integrated, single chip ultra-low power 2.4 GHz wireless transceiver with embedded MCU, targeted at wireless audio streaming for hearables, wireless headsets, and headphones.

The NXH3670UK chip integrates the following key functionalities – among others:

- A 2.4 GHz RF transceiver and digital modem supporting up to 2 Mbits/s

- Supporting Bluetooth Low Energy GFSK modulation 1 Mbps and 2 Mbps

- A low-power 16 MHz/32 MHz crystal oscillator and on-chip oscillators

- An RF MAC for supporting the lower protocol layers

- · A Cortex-M0 subsystem for system control and higher protocol layers

- An AES-128 security coprocessor

- · Audio interfaces and audio processing accelerators

- A CoolFlux DSP for audio processing

- · Multiple user interfaces for control, data, debug, and test

#### **CAUTION**

This device is sensitive to ElectroStatic Discharge (ESD). Observe precautions for handling electrostatic sensitive devices.

Such precautions are described in the ANSI/ESD S20.20, IEC/ST 61340-5, JESD625-A or equivalent standards.

#### **CAUTION**

Semiconductors are light sensitive. Exposure to light sources can cause the IC to malfunction.

The IC must be protected against light. The protection must be applied to all sides of the IC..

Unless otherwise specified:

- Typical values are at room temperature (25 °C) with nominal supply voltages of 1.2 V.

- Minimum/Maximum values are valid over operating temperature and voltage range as specified in <u>Table 26</u>.

#### 2 Features and benefits

- Transceiver characteristics

- 2.402 GHz to 2.480 GHz carrier frequency

- Bluetooth Low Energy 1 Mbps and 2 Mbps PHY modes

- 2 MHz channels in 1 Mbps and 2 Mbps modes

- · Receiver characteristics:

- Sensitivity -90 dBm in Bluetooth Low Energy 2 Mbps modulation mode

- Sensitivity -94 dBm in Bluetooth Low Energy 1 Mbps modulation mode

- Frequency offset correction up to ±300 kHz.

- RSSI measurement with ±3 dB accuracy

- · Transmitter characteristics:

- Programmable TX output power of −10 dBm to +4 dBm in steps of 2 dBm

- · Synthesizer characteristics:

- Fully integrated PLL, no external loop filter components

- Integrated power management:

- Low voltage supply 1.2 V

- Integrated supply generation for sensitive radio blocks

- Integrated supply generation for digital and memories

- Flexible low-power states

- Clock generation:

- Integrated low-power crystal oscillator

- Support for 16 MHz or 32 MHz crystals with ±60 ppm accuracy and crystal trimming

- On chip oscillators, including ultra low-power oscillator

- Low current consumption:

- Sleep current < 63 µA

- Continuous RX current < 3.7 mA at 1.2 V

- Continuous TX current < 7.3 mA at 1.2 V (0 dBm output power)

- MCU subsystem:

- ARM Cortex-M0 up to 16 MHz in low-power mode and 84 MHz in high-performance mode

- Flexible DMA engine

- Serial debug interface

- · Control/Data interfaces:

- SPI slave

- UART

- GPIOs

- RF MAC:

- Dedicated RF MAC accelerator

- AES security coprocessor

- Packet processing

- Timers

- CRC, whitening

#### Ultra-low power 2.4 GHz Bluetooth Low Energy transceiver for audio streaming

- · Audio interfaces and processing

- I<sup>2</sup>S and TDM interface

- G.722 codec accelerator

- CoolFlux DSP up to 16 MHz in low-power mode and 84 MHz in high-performance mode

- Asynchronous sample rate converter (ASRC)

- Latency control

- · Host-assisted boot via SPI

- Certified for Bluetooth specification version 4.2

- WLCSP package < 7.25 mm<sup>2</sup> (maximum die size after sawing) with 34 bumps

- Low number of external passive components

- Pb-free and compliant with RoHS Directive 2011/65/EU (RoHS 2)

- Operating temperature -20 °C to +85 °C

## 3 Applications

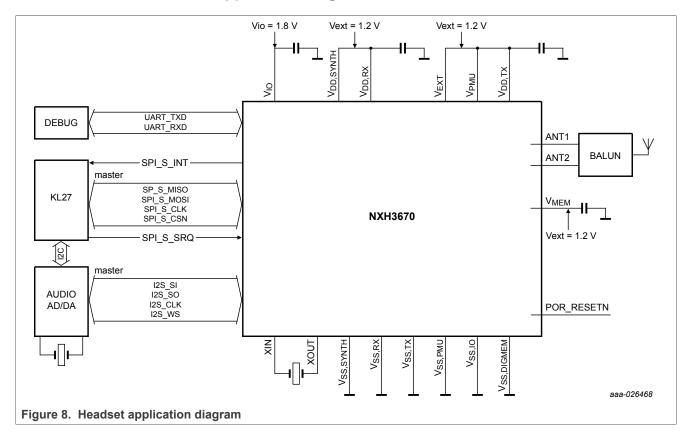

The main application target is gaming headsets, wireless headsets, and headphones.

Thanks to its support for audio, control and data, the NXH3670UK can be used in many applications where ultra-low power and small size are required.

Additional typical applications are mobile phone accessories and computer peripherals.

## 4 Ordering information

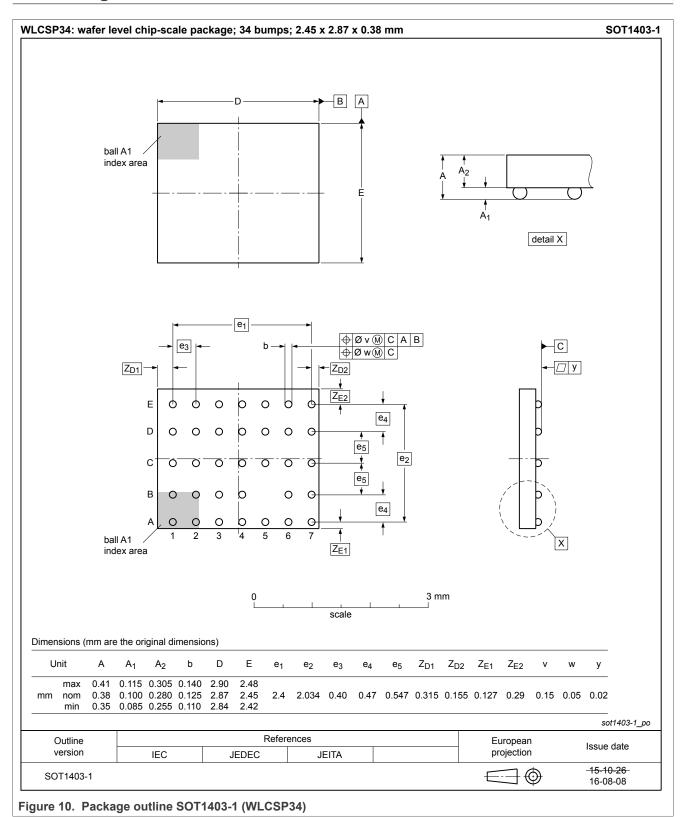

Table 1. Ordering information

| Type number | Package |                                                                 |           |

|-------------|---------|-----------------------------------------------------------------|-----------|

|             | Name    | Description                                                     | Version   |

| NXH3670UK   | WLCSP34 | waver level chip-scale package; 34 bumps; 2.45 × 2.87 × 0.38 mm | SOT1403-1 |

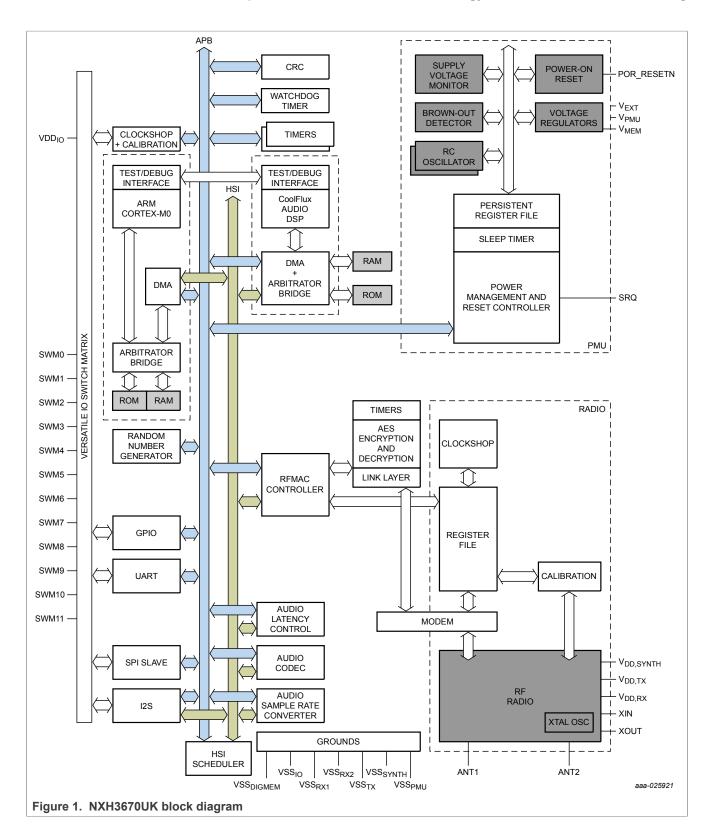

### 5 Block diagram

<u>Figure 1</u> shows an overview of the NXH3670UK architecture. The NXH3670UK consists of the following subsystems:

- · RF radio:

- An RF radio transceiver

- Digital RF modem and calibration logic

- · Wireless link controller:

- A clock shop for dividing, multiplexing, and calibrating clocks

- An ARM Cortex running up to 16 MHz in low-power mode and 84 MHz in high-performance mode:

- ROM for program

- RAM for program and data

- DMA engine

- A flexible RF MAC for the lower protocol layers:

- An RF MAC controller interfacing to the radio

- Packet transmit and receive

- CRC/whitening/assembly/dis-assembly accelerators

- Timers

- An AES security coprocessor

- Audio processing unit:

- Latency control unit

- Dual context G.722

- Sample rate converter

- A CoolFlux audio DSP with associated memories and DMA engine

- Interfaces:

- General-purpose IOs

- A debug and test UART

- An SPI slave

- An audio port supporting I<sup>2</sup>S and TDM modes

- Timers

- A watchdog timer

- A random number generator

- Power Management Unit (PMU):

- Voltage regulators

- Power-on reset (POR)

- Brownout detection (BOD)

- Power management and reset controller, sleep timer, persistent register file

- A 16 MHz/32 MHz crystal oscillator and various internal oscillators

- · A versatile IO switch matrix

These subsystems are described in more detail in <u>Section 7</u>.

### Ultra-low power 2.4 GHz Bluetooth Low Energy transceiver for audio streaming

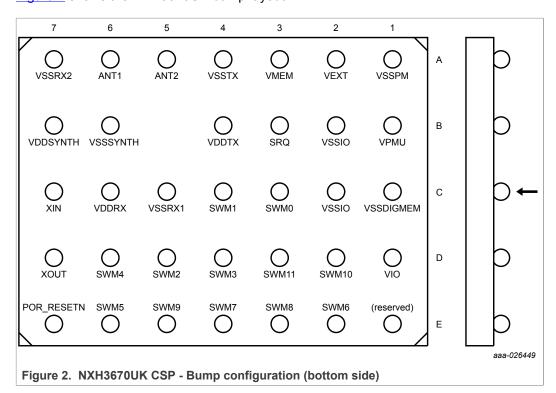

# 6 Package and pinning information

This chapter provides an overview on the NXH3670UK package and pinning.

#### 6.1 Package

Figure 2 shows the NXH3670UK bump layout

### 6.2 Pinning

<u>Table 2</u> lists the bump assignments, usage, and associated pad type. The different types are:

- PWR: supply bump

- GND: ground bump

- RF: RF signal bump

- · A: analog bump

- DIO: digital IO bump

At start-up, all digital IOs are set in 3-state input mode.

Table 2. NXH3670UK bumping

| Bump   | NXH3670UK bum<br>Symbol | Туре | Description                                                                                                                                   |

|--------|-------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Supply |                         |      | •                                                                                                                                             |

| A2     | V <sub>EXT</sub>        | PWR  | external power supply                                                                                                                         |

| D1     | V <sub>IO</sub>         | PWR  | IO bumps power supply                                                                                                                         |

| A3     | V <sub>MEM</sub>        | PWR  | To be used for external decoupling of internal supply node. Do not use to supply external circuit (externally connected to $V_{\text{EXT}}$ ) |

| B1     | V <sub>PMU</sub>        | PWR  | supply of the analog part of the PMU (externally connected to $V_{\text{EXT}}$ )                                                              |

| B4     | $V_{DD,TX}$             | PWR  | RF TX power supply (externally connected to $V_{\text{EXT}}$ )                                                                                |

| C6     | $V_{DD,RX}$             | PWR  | RF RX power supply (externally connected to V <sub>EXT</sub> )                                                                                |

| B7     | V <sub>DD,SYNTH</sub>   | PWR  | RF synthesizer power supply (externally connected to $\ensuremath{V_{\text{EXT}}})$                                                           |

| Ground |                         |      |                                                                                                                                               |

| C1     | $V_{SS, DIGMEM}$        | GND  | ground for the digital core and memories                                                                                                      |

| C5     | $V_{SS,RX1}$            | GND  | ground for the radio receiver                                                                                                                 |

| A7     | $V_{SS,RX2}$            | GND  | ground for the radio receiver                                                                                                                 |

| A4     | $V_{SS,TX}$             | GND  | ground for the radio transmitter                                                                                                              |

| B6     | V <sub>SS,SYNTH</sub>   | GND  | ground for the radio synthesizer                                                                                                              |

| A1     | V <sub>SS,PMU</sub>     | GND  | ground for the PMU                                                                                                                            |

| C2     | $V_{SS,IO}$             | GND  | ground for the digital IO pads and ESD structures                                                                                             |

| B2     | $V_{SS,IO}$             | GND  | ground for the digital IO pads and ESD structures                                                                                             |

| Radio  | ·                       | ·    |                                                                                                                                               |

| A6     | ANT1                    | RF   | balanced antenna connection terminal 1                                                                                                        |

| A5     | ANT2                    | RF   | balanced antenna connection terminal 2                                                                                                        |

| xosc   | ·                       |      |                                                                                                                                               |

| C7     | XIN                     | Α    | crystal oscillator input terminal                                                                                                             |

| D7     | XOUT                    | А    | crystal oscillator output terminal                                                                                                            |

| IO-SWM | ·                       | ·    |                                                                                                                                               |

| C3     | SWM0                    | DIO  | general-purpose digital IO                                                                                                                    |

| C4     | SWM1                    | DIO  | general-purpose digital IO                                                                                                                    |

| D5     | SWM2                    | DIO  | general-purpose digital IO                                                                                                                    |

| D4     | SWM3                    | DIO  | general-purpose digital IO                                                                                                                    |

| D6     | SWM4                    | DIO  | general-purpose digital IO                                                                                                                    |

| E6     | SWM5                    | DIO  | general-purpose digital IO                                                                                                                    |

| E2     | SWM6                    | DIO  | general-purpose digital IO                                                                                                                    |

| E4     | SWM7                    | DIO  | general-purpose digital IO                                                                                                                    |

| E3     | SWM8                    | DIO  | general-purpose digital IO                                                                                                                    |

| E5     | SWM9                    | DIO  | general-purpose digital IO                                                                                                                    |

Table 2. NXH3670UK bumping...continued

| Bump          | Symbol     | Туре | Description                                                 |  |  |

|---------------|------------|------|-------------------------------------------------------------|--|--|

| D2            | SWM10      | DIO  | general-purpose digital IO                                  |  |  |

| D3            | SWM11      | DIO  | general-purpose digital IO                                  |  |  |

| Miscellaneous |            |      |                                                             |  |  |

| E7            | POR_RESETN | DIO  | reset pin; active LOW, referenced to VBAT                   |  |  |

| В3            | SRQ        | DI   | service request; to be used by host to change power states. |  |  |

| E1            | -          | -    | (reserved)                                                  |  |  |

# 7 Functional description

#### 7.1 RF radio transceiver

#### 7.1.1 Features

The RF radio transceiver implements the complete physical layer of a 2.4 GHz ultra low-power RF wireless link. It includes:

- · RF functions and power and timing management

- Integrated analog RF front end with combined Rx/Tx interface

- · Symbol demodulation and timing/frequency recovery blocks

- Gaussian frequency shift keying (GFSK) with the following modulation parameters:

- Bluetooth Low Energy 2 Mbps mode

- h = 0.5

- BT = 0.5

- 2 Mbps throughput mode

- Bluetooth Low Energy 1 Mbps mode

- h = 0.5

- BT = 0.5

- 1 Mbps throughput mode

- · Accurate received signal strength indicator (RSSI)

- · Integrated frequency synthesizer

- · Automatic gain control

- Programmable transmit power

- Trimming and calibration during chip production, removing the need for trimming in the application

- · Continuous wave (CW) transmit for test mode

The RF radio transceiver consists of 3 functional blocks:

- · The synthesizer, which generates the RF carrier

- · The receiver

- The transmitter

The specifications for each of these blocks are described in <u>Section 7.1.2</u>, <u>Section 7.1.3</u>, and <u>Section 7.1.4</u>. They are guaranteed on NXH3670UK reference board schematics and layout.

In-band specifications are referred to RF antenna bumps.

Out-of-band specifications include band-pass filtering of reference board.

### 7.1.2 Synthesizer specification

<u>Table 3</u> summarizes the key specifications of the RF synthesizer.

Table 3. Synthesizer specifications

| Symbol                | Parameter                                                 | Min  | Тур | Max  | Unit |

|-----------------------|-----------------------------------------------------------|------|-----|------|------|

| f <sub>c</sub>        | Carrier frequency                                         | 2402 | -   | 2480 | MHz  |

| f <sub>c,res</sub>    | Carrier frequency resolution                              | -    | 1   | -    | MHz  |

| f <sub>ch,2Mbps</sub> | Non-overlapping channel spacing (2 Mbps and 1 Mbps modes) | -    | 2   | -    | MHz  |

| T <sub>PLL</sub>      | PLL turn-on/hop settling time                             | -    | 50  | -    | μs   |

| T <sub>txrx</sub>     | TX/RX turn around time using same channel                 | -    | 40  | -    | μs   |

### 7.1.3 Transmitter specification

Table 4 to Table 6 contain the detailed specifications of the RF transmitter.

Table 4. Transmitter generic specifications

| Symbol                | Parameter                                                           | Min                  | Тур    | Max | Unit |

|-----------------------|---------------------------------------------------------------------|----------------------|--------|-----|------|

| P <sub>RF</sub>       | lowest TX output power range                                        | -                    | -10    | -   | dBm  |

|                       | highest TX output power range                                       | -                    | 4      | -   | dBm  |

| $\Delta P_{RF}$       | TX output power: programming step size                              | -                    | 2      | -   | dBm  |

| P <sub>tol</sub>      | output power tolerance at 0 dBm <sup>[1]</sup>                      | -                    | ±1.5   | -   | dBm  |

| Z <sub>OUT</sub>      | output impedance - balanced                                         | -                    | 99-j42 | -   | Ω    |

| P <sub>2,harm</sub>   | power in 2 <sup>nd</sup> harmonic: all rates at 0 dBm               | -                    | -      | -30 | dBm  |

|                       | power in 2 <sup>nd</sup> harmonic: all rates at 4 dBm               | -                    | -      | -25 | dBm  |

| P <sub>3,harm</sub>   | power in 3 <sup>rd</sup> harmonic: all rates at 0 dBm               | -                    | -      | -30 | dBm  |

|                       | power in 3 <sup>rd</sup> harmonic: all rates at 4 dBm               | -                    | -      | -25 | dBm  |

| P <sub>4,harm</sub>   | power in 4 <sup>th</sup> harmonic: all rates at 0 dBm               | -                    | -      | -30 | dBm  |

|                       | power in 4 <sup>th</sup> harmonic: all rates at 4 dBm               | -                    | -      | -30 | dBm  |

| P <sub>spur</sub>     | spurious emissions (all output levels and ra                        | ates) <sup>[2]</sup> |        |     |      |

|                       | 30 MHz to1000 MHz                                                   | -                    | -      | -36 | dBm  |

|                       | 1 GHz to12.75 GHz                                                   | -                    | -      | -30 | dBm  |

|                       | 47 MHz to 74 MHz                                                    | -                    | -      | -54 | dBm  |

|                       | 87.5 MHz to 108 MHz                                                 | -                    | -      | -54 | dBm  |

|                       | 174 MHz to 230 MHz                                                  | -                    | -      | -54 | dBm  |

|                       | 470 MHz to 862 MHz                                                  | -                    | -      | -54 | dBm  |

| P <sub>spur0dBm</sub> | spurious emissions for P <sub>out</sub> < 0 dBm, 2.0 GHz to 3.0 GHz | -                    | -60    | -45 | dBm  |

#### Ultra-low power 2.4 GHz Bluetooth Low Energy transceiver for audio streaming

Table 4. Transmitter generic specifications...continued

| Symbol              | Parameter                                        | Min | Тур | Max               | Unit |

|---------------------|--------------------------------------------------|-----|-----|-------------------|------|

| Δh <sub>2Mbps</sub> | frequency deviation accuracy (2 Mbps – 0 dBm)    | -   | ±3  | ±7 <sup>[3]</sup> | %    |

| Δh <sub>1Mbps</sub> | frequency deviation accuracy<br>(1 Mbps - 0 dBm) | -   | ±3  | ±7 <sup>[3]</sup> | %    |

- Measured at 25 °C, full supply voltage range, tested with lab supply. Assuming perfect matching.

- Complies with EN 300 440 -1 V1.6.1, EN 300 328 V1.8.1, FCC CFR 47 part 15, ARIB STD-66, RSS-210

- Maximum value over temperature and for a supply exceeding 1.05 V

Table 5. Transmitter mode 2 Mbps Bluetooth Low Energy specifications

| Symbol                  | Parameter                              | Min | Тур  | Max | Unit |

|-------------------------|----------------------------------------|-----|------|-----|------|

| BW <sub>A2Mbps</sub>    | 20 dB bandwidth                        | -   | 2.06 | -   | MHz  |

| ACPR <sub>A2Mbps</sub>  | Adjacent Channel Power Ratio           | _   | -    | -30 | dBc  |

| AACPR <sub>A2Mbps</sub> | Alternate Adjacent Channel Power Ratio | -   | -    | -50 | dBc  |

Table 6. Transmitter mode 1 Mbps Bluetooth Low Energy specifications

| Symbol               | Parameter                              | Min | Тур   | Max | Unit |

|----------------------|----------------------------------------|-----|-------|-----|------|

| BW <sub>BLE</sub>    | 20 dB bandwidth                        | -   | 1.030 | -   | MHz  |

| ACPR <sub>BLE</sub>  | Adjacent Channel Power Ratio           | -   | -     | -30 | dBc  |

| AACPR <sub>BLE</sub> | Alternate Adjacent Channel Power Ratio | -   | -     | -50 | dBc  |

#### 7.1.4 Receiver specifications

<u>Table 7</u> to <u>Table 9</u> contain the detailed specifications of the RF radio receiver.

The following conventions are chosen:

- Maximum input power P<sub>in,max</sub> is given for a BER of 10<sup>-3</sup>

RX sensitivity P<sub>RX.\*</sub> is defined for a BER of 10<sup>-3</sup> for all modes

BER of  $10^{-3}$  corresponds to a PER of 30.8 % since a packet length of 46 bytes is used according to the Bluetooth Low Energy RF PHY test specification

- Co-channel interference C/I<sub>CO.\*</sub> and ACS (C/I) are measured with a wanted signal at -67 dBm and one interferer having the same modulation as the wanted signal. The measurement is done according to the Bluetooth Low Energy RF PHY test spec for all different modes

- IMD is measured with a wanted signal at -64 dBm and 2 interferers having the same power. The closest interferer is a CW signal and the other interferer has the same modulation as the wanted signal. The largest power of the interfering signals for which the wanted signal fulfills the sensitivity criterion is reported. The measurement is done according to the Bluetooth Low Energy RF PHY test spec for all different modes.

NXH3670UK

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2020. All rights reserved.

### Ultra-low power 2.4 GHz Bluetooth Low Energy transceiver for audio streaming

Table 7. Receiver generic specifications

| Symbol               | Parameter                               | Min | Тур    | Max | Unit |

|----------------------|-----------------------------------------|-----|--------|-----|------|

| P <sub>in,max</sub>  | maximum input power                     | -   | -10    | -   | dBm  |

| LO <sub>leak</sub>   | LO leakage                              | -   | -70    | -   | dBm  |

| OBB                  | out of band blocking <sup>[1]</sup>     |     |        |     |      |

|                      | 30 MHz to 2000 MHz                      | -   | 0      | -   | dBm  |

|                      | 2003 MHz to 2399 MHz                    | -   | -10    | -   | dBm  |

|                      | 2484 MHz to 2997 MHz                    | -   | -10    | -   | dBm  |

|                      | 3000 MHz to 12.75 GHz                   | -   | +10    | -   | dBm  |

| RSSI <sub>dyn</sub>  | RSSI dynamic range                      | -90 | -      | -10 | dBm  |

| RSSI <sub>tol</sub>  | RSSI tolerance                          | -3  | -      | +3  | dBm  |

| RSSI <sub>res</sub>  | RSSI resolution (monotonically)         | -   | -      | 3   | dBm  |

| IR                   | image Rejection, C/I <sup>[2]</sup>     | -   | -28    | -   | dB   |

| P <sub>spur,RX</sub> | spurious emissions RX - 25 MHz to 1 GHz | -   | -      | -57 | dBm  |

|                      | spurious emissions RX - above 1 GHz     | -   | -      | -47 | dBm  |

| Z <sub>in</sub>      | input impedance                         | -   | 99-j42 | -   | Ω    |

<sup>[1]</sup> As defined by Bluetooth Low Energy standard (Bluetooth spec 4.0 – Volume 6 – Part A – section 4.3).

Table 8. Receiver mode 2 Mbps Bluetooth Low Energy specifications

| Symbol                  | Parameter                | Min | Тур | Max | Unit |

|-------------------------|--------------------------|-----|-----|-----|------|

| P <sub>Rx,2Mbps</sub>   | RX sensitivity           | -   | -90 | -   | dBm  |

| C/I <sub>CO,2Mbps</sub> | co-channel C/I           | -   | 8   | -   | dB   |

| ACS <sub>1,2Mbps</sub>  | C/I at 2 MHz             | -   | -4  | -   | dB   |

| ACS <sub>2,2Mbps</sub>  | C/I at 4 MHz             | -   | -28 | -   | dB   |

| ACS <sub>N,2Mbps</sub>  | C/I at Δf ≥ 10 MHz       | -   | -45 | -   | dB   |

| IMD <sub>2Mbps</sub>    | CW at 6 MHz/8 MHz/10 MHz | -   | -36 | -   | dBm  |

Table 9. Receiver mode 1 Mbps Bluetooth Low Energy specifications

| Symbol                | Parameter               | Min | Тур | Max | Unit |

|-----------------------|-------------------------|-----|-----|-----|------|

| P <sub>Rx,BLE</sub>   | RX Sensitivity          | _   | -94 | -   | dBm  |

| C/I <sub>CO,BLE</sub> | co-channel C/I          | -   | 8   | -   | dB   |

| ACS <sub>1,BLE</sub>  | C/I at 1 MHz            | -   | -2  | -   | dB   |

| ACS <sub>2,BLE</sub>  | C/I at 2 MHz            | _   | -28 | -   | dB   |

| ACS <sub>N,BLE</sub>  | C/I at Δf ≥ 10 MHz      | -   | -45 | -   | dB   |

| IMD <sub>BLE</sub>    | CW at 3 MHz/4 MHz/5 MHz | _   | -36 | -   | dBm  |

<sup>[2]</sup> Measured at 0.1 % BER, desired signal 3 dB above sensitivity. Image frequency is 2 MHz below the RF frequency in 1 Mbps mode and 3 MHz above the RF frequency in 2 Mbps mode.

#### 7.2 Wireless link controller

The sections below are intended to give a summary of the functionality implemented in the wireless link controller.

#### 7.2.1 On-chip buses

#### 7.2.1.1 Advanced peripheral bus (APB)

Both the ARM Cortex-M0 and the CoolFlux audio DSP are masters on the APB. This bus is intended for configuration and status reporting.

The host can access all peripherals on the APB through the software API.

#### 7.2.1.2 HSI data bus

The High-speed interface (HSI) scheduler enables peripherals to access the HSI Data bus using a fixed schedule. The HSI data bus provides scheduled bus access with two-way handshaking between the source and destination peripheral.

### 7.2.2 ARM Cortex-M0 MCU subsystem

The ARM Cortex-M0 MCU subsystem consists of:

- An ARM Cortex-M0

- 128 kB ROM

- 96 kB RAM

- HSI/APB bridge

- 8 DMA channels; interfacing between the Cortex-M0 memories and the HSI data bus

The ARM Cortex-M0 is designed to run at a frequency up to 84 MHz. The maximum operating frequency is however dependent on the core voltage, allowing to trade off between high frequency and low current consumption.

The ARM Cortex-M0 is intended to control the overall system and execute the firmware for higher protocol layers. the RF MAC controller typically handles the lower protocol layers.

Table 10. ARM Cortex-M0 memories

| Memory   | Value                  |

|----------|------------------------|

| RAM size | 24 K × 32 bit [96 kB]  |

| ROM size | 32 K × 32 bit [128 kB] |

Table 11. ARM Cortex-M0 configuration

| Parameter  | Value                |

|------------|----------------------|

| Endianness | little endian        |

| Debug port | Serial Wire (SW-DBG) |

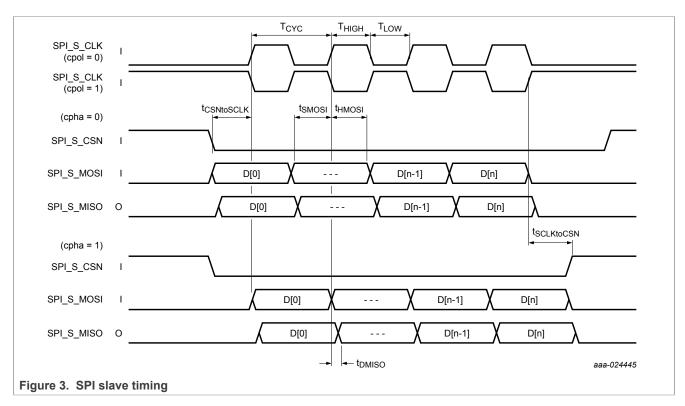

#### 7.2.3 SPI slave

The SPI slave hardware module provides the interface through which an external host can communicate as master with the wireless link controller. The SPI slave adheres to the 4-wire SPI specification, supporting operation mode 0.

The SPI slave includes:

- 2 buffers (RX and TX) of 72 bytes each:

- RX buffer: used to transmit message from external host to Cortex-M0

- TX buffer: used to transmit message from Cortex-M0 to external host

- · Flow control settings and status to manage the packet transfers

To allow the controller to request an SPI transfer, a signaling line (GPIO) from the controller to the host can be used.

Write operations of NXH3670UK SPI slave interface can be done with a clock frequency of 16 MHz. However, for read operations in the final application, the MISO output delay can impact the performances.

Table 12. SPI slave timing for  $V_{IO}$  = 1.20 V

| Symbol             | Parameter                                           | Conditions                                         | Min  | Тур | Max | Unit |

|--------------------|-----------------------------------------------------|----------------------------------------------------|------|-----|-----|------|

| T <sub>CYC</sub>   | clock cycle time                                    | V <sub>IO</sub> = 1.20 V, C <sub>out</sub> = 15 pF | 62.5 | -   | -   | ns   |

| T <sub>HIGH</sub>  | clock HIGH time as a percentage of T <sub>CYC</sub> |                                                    | 45   | -   | 55  | %    |

| T <sub>LOW</sub>   | clock LOW time as a percentage of T <sub>CYC</sub>  |                                                    | 45   | -   | 55  | %    |

| t <sub>SMOSI</sub> | MOSI setup time                                     |                                                    | 12.5 | -   | -   | ns   |

NXH3670UK

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2020. All rights reserved.

Table 12. SPI slave timing for  $V_{IO}$  = 1.20  $V_{...}$ continued

| Symbol                 | Parameter                    | Conditions                                                                | Min  | Тур | Max | Unit |

|------------------------|------------------------------|---------------------------------------------------------------------------|------|-----|-----|------|

| t <sub>HMOSI</sub>     | MOSI hold time               |                                                                           | 12.5 | -   | -   | ns   |

| t <sub>DMISO</sub>     | MISO output delay            | V <sub>IO</sub> = 1.20 V, C <sub>out</sub> = 15 pF, drive strength = HIGH | -    | -   | 30  | ns   |

| t <sub>CSNtoSCLK</sub> | chip select LOW to clock     |                                                                           | 15   | -   | -   | ns   |

| t <sub>SCLKtoCSN</sub> | clock to chip select<br>HIGH |                                                                           | 15   | -   | -   | ns   |

### Table 13. SPI slave timing for $V_{IO}$ = 1.80 V

| Symbol                 | Parameter                                           | Conditions                                                                | Min  | Тур | Max | Unit |

|------------------------|-----------------------------------------------------|---------------------------------------------------------------------------|------|-----|-----|------|

| T <sub>CYC</sub>       | clock cycle time                                    | V <sub>IO</sub> = 1.80 V, C <sub>out</sub> = 15 pF                        | 62.5 | -   | -   | ns   |

| T <sub>HIGH</sub>      | clock HIGH time as a percentage of T <sub>CYC</sub> |                                                                           | 45   | -   | 55  | %    |

| T <sub>LOW</sub>       | clock LOW time as a percentage of T <sub>CYC</sub>  |                                                                           | 45   | -   | 55  | %    |

| t <sub>SMOSI</sub>     | MOSI setup time                                     |                                                                           | 12.5 | -   | -   | ns   |

| t <sub>HMOSI</sub>     | MOSI hold time                                      |                                                                           | 12.5 | -   | -   | ns   |

| t <sub>DMISO</sub>     | MISO output delay                                   | V <sub>IO</sub> = 1.80 V, C <sub>out</sub> = 15 pF, drive strength = HIGH | -    | -   | 26  | ns   |

| t <sub>CSNtoSCLK</sub> | chip select LOW to clock                            |                                                                           | 15   | -   | -   | ns   |

| t <sub>SCLKtoCSN</sub> | clock to chip select<br>HIGH                        |                                                                           | 15   | -   | -   | ns   |

### Table 14. SPI slave timing for $V_{IO}$ = 2.50 V

| Symbol                 | Parameter                                           | Conditions                                                                   | Min  | Тур | Max | Unit |

|------------------------|-----------------------------------------------------|------------------------------------------------------------------------------|------|-----|-----|------|

| T <sub>CYC</sub>       | clock cycle time                                    | V <sub>IO</sub> = 2.50 V, C <sub>out</sub> = 15 pF                           | 62.5 | -   | -   | ns   |

| T <sub>HIGH</sub>      | clock HIGH time as a percentage of T <sub>CYC</sub> |                                                                              | 45   | -   | 55  | %    |

| T <sub>LOW</sub>       | clock LOW time as a percentage of T <sub>CYC</sub>  |                                                                              | 45   | -   | 55  | %    |

| t <sub>SMOSI</sub>     | MOSI setup time                                     |                                                                              | 12.5 | -   | -   | ns   |

| t <sub>HMOSI</sub>     | MOSI hold time                                      |                                                                              | 12.5 | -   | -   | ns   |

| t <sub>DMISO</sub>     | MISO output delay                                   | V <sub>IO</sub> = 2.50 V, C <sub>out</sub> = 15 pF, drive<br>strength = HIGH | -    | -   | 25  | ns   |

| t <sub>CSNtoSCLK</sub> | chip select LOW to clock                            |                                                                              | 15   | -   | -   | ns   |

| t <sub>SCLKtoCSN</sub> | clock to chip select<br>HIGH                        |                                                                              | 15   | -   | -   | ns   |

#### 7.2.4 **UARTs**

Depending on the selected IO switch matrix configuration (see <u>Section 7.2.11</u>), a UART interface is made available externally.

They are used for debug and testing purposes and are not available for interfacing with a Host. They can for instance be used by the ARM Cortex-M0 or the CoolFlux audio DSP for logging purposes.

More information about configuration parameters of UART interfaces can be found in Table 15.

Table 15. UART configuration parameters

| Property        | Value           |

|-----------------|-----------------|

| character width | 8 bit           |

| stop bits       | 1 bit           |

| parity          | no parity       |

| flow control    | no flow control |

| baud rate       | 888888          |

# 7.2.5 Dataport (I<sup>2</sup>S or TDM)

The dataport is used for audio transmission between the NXH3670UK and a host or a codec. The dataport can be configured in I<sup>2</sup>S or TDM mode. The dataport uses the same four lines for both I<sup>2</sup>S and TDM (<u>Table 16</u>).

Table 16. Dataport signals

| Signal name | Description                                                |

|-------------|------------------------------------------------------------|

| 12S_WS      | word select, indicating which channel is being transferred |

| I2S_CLK     | bit clock, synchronizing all devices on the bus            |

| 12S_SI      | input data line (regarding the NXH3670UK)                  |

| I2S_SO      | output data line (regarding the NXH3670UK)                 |

The following configuration options are available:

- I<sup>2</sup>S slave mode at 48 kHz

- Interface word length (common value for both input and output channels): 16 bits or 32 bits (left-justified with zero padding)

- I<sup>2</sup>S master mode supporting 50 kHz

- TDM slave mode supporting 2, 4, or 8 channels. The interface word length can be either 16 bits or 32 bits for 2 and 4 channels. The interface word length is limited to 16 bits for 8 channels.

Unused output channels can be tristated. The maximum bit rate is 6.2 Mbps. More information on the TDM interface can be found in the "NXH3670 TDM audio interface specification" application note (Ref. 3).

#### 7.2.6 Clock shop

The clock shop modules provide the necessary clocks for the ARM Cortex-M0 and all the other modules in the wireless link controller. Each module has its own clock or clocks, generated by the clock shop. Each clock individually has the following settings:

- · Clock source

- · Enable/disable

- · Division factor

For the clocks to be reprogrammed in a safe way (such that no spikes occur on the clock signal), the parameters have to be programmed in a certain order. For all clocks, it is recommended to disable the clock before changing the divider setting. The ARM Cortex-M0 clock itself is a special case, since it cannot be switched off or the system would lock up. For this reason, the parameter updates for this block are synchronized with the running clock during update.

Clock switching is glitch free for modules that require clock switching in active mode. These modules are:

- The ARM Cortex-M0

- The HSI bus

- The G.722 codecs

- The CoolFlux audio DSP

The clock shop can be programmed via software API by the ARM Cortex-M0.

The clock shop module also contains a calibration function. This function can be used to adjust the internal RC oscillator frequencies by comparing them with the 16 MHz/32 MHz crystal oscillator clock.

#### **7.2.7 Timers**

The NXH3670UK contains two identical hardware timer modules. Each timer module is a 16-bit interval timer with 3 independent capture/compare registers.

#### 7.2.8 Audio processing

The wireless link controller contains the following modules for audio processing: G.722 codec instance, sample rate converter, audio latency control instance, and the CoolFlux audio DSP.

#### 7.2.8.1 G.722 codec

The audio codec hardware module has the following specifications:

- 2 contexts, each context can independently encode/decode an audio stream

- Supported mode is subband ADPCM according to ITU-T G.722 mode 1

Typical sample rate of G.722 compression is 16 kHz but it can be used up to 48 kHz.

#### 7.2.8.2 Latency control

The latency control hardware module controls the end-to-end audio latency across the wireless link to a programmable value. This control is especially important for synchronous streams (for example left/right audio channel) where it is mandatory to

NXH3670UK

achieve the same audio latency. The latency control hardware module contains timers and an NCO, which are steered to maintain the configured audio latency.

#### 7.2.8.3 CoolFlux audio DSP

The CoolFlux audio DSP is a hardware audio accelerator used to implement audio functions such as audio compression/decompression codecs, equalization, and audio mixing. It is designed to work typically at 16 MHz or a lower frequency, but can run at a frequency up to 84 MHz in the configuration where an external regulator is used.

A test and debug interface, available on SWM IO through configuration is also provided.

The CoolFlux audio DSP subsystem is connected to the HSI data bus through a DMA engine, which can handle up to 8 independent queues. This DMA engine can reach the program memory and both X and Y data memories.

The CoolFlux audio DSP can access the APB bus via the APB memory bridge, through an APB arbiter. Conversely, the Cortex-M0 has access to CoolFlux IO register map, also via the APB memory bridge.

The boot loader running on the Cortex-M0 core loads the CoolFlux DSP program images from an external device, typically the host MCU. The loading is performed through the DMA interface, while holding the DSP in reset.

Amount of X and Y memories is configurable at startup from a fixed pool of ROM and RAM.

Table 17 indicates the sizes of the different memories:

Table 17. CoolFlux memories

| Memory                  | Value                 |

|-------------------------|-----------------------|

| P-RAM size              | 8 K × 32 bit [32 kB]  |

| P-ROM size              | 16 K × 32 bit [64 kB] |

| RAM pool (X and Y) size | 20 K × 24 bit [60 kB] |

| ROM pool (X and Y) size | 10 K× 24 bit [30 kB]  |

#### 7.2.9 Random number generator (RNG)

The Random number generator (RNG) is a true random number generator to be used for security purposes. It takes multiple clock sources as input to provide a random number on request.

#### 7.2.10 RF HWMAC accelerator

The RF HWMAC accelerator implements the medium access control (MAC) layer of the radio. The MAC consists of:

- RFMAC controller

- · Configuration interface toward the RF modem and RF radio

- DMA engine with 4 channels for interfacing with HSI bus and Cortex-M0

- · Radio data path

- Up to 4 configuration banks for TX and 4 configuration banks for RX

- Packet assembly, disassembly (address, header, payload)

- CRC accelerator

- Whitening accelerator

- AES security accelerator

- Off-line encryption/decryption of payload data using API control

- On-the-fly encryption/decryption of Bluetooth Low Energy payload data

- Accurate timers for packet timing

#### 7.2.10.1 External PA control

The following signals, available through the switch matrix, provide external PA support:

- PA enable

- RX enable

#### 7.2.11 Versatile IO switch matrix

This module allows connection of the various functional signals to a limited set of actual chip IO pins. The switch matrix pad voltage is referenced to VIO.

During reset (POR\_ RESETN), SWM pins are in 3-state.

Table 18 gives an overview of the functionalities that are multiplexed on each of the SWM pins:

Table 18. Versatile switch matrix

| Pin                  | Default               | Configuration A <sup>[1]</sup> | Configuration B <sup>[1]</sup> | Configuration C <sup>[1]</sup> | Configuration D <sup>[1]</sup> |

|----------------------|-----------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|

| SWM00                | SPI_S_MISO (output)   | SPI_S_MISO (output)            | SPI_S_MISO (output)            | SPI_S_MISO (output)            | SPI_S_MISO<br>(output)         |

| SWM01                | SPI_S_MOSI (input)    | SPI_S_MOSI (input)             | SPI_S_MOSI<br>(input)          | SPI_S_MOSI<br>(input)          | SPI_S_MOSI<br>(input)          |

| SWM02                | SPI_S_CLK (input)     | SPI_S_CLK (input)              | SPI_S_CLK (input)              | SPI_S_CLK (input)              | SPI_S_CLK (input)              |

| SWM03                | SPI_S_CSN<br>(output) | SPI_S_CSN<br>(output)          | SPI_S_CSN<br>(output)          | SPI_S_CSN<br>(output)          | SPI_S_CSN<br>(output)          |

| SWM04                | SPI_S_INT (output)    | SPI_S_INT (output)             | SPI_S_INT (output)             | SPI_S_INT (output)             | SPI_S_INT (output)             |

| SWM05 <sup>[2]</sup> | (3-state)             | (3-state)                      | (3-state)                      | I2S_SO<br>(output)             | (3-state)                      |

| SWM06 <sup>[2]</sup> | (3-state)             | I2S_SI<br>(input)              | I2S_SI<br>(input)              | I2S_SI<br>(input)              | UART_RXD<br>(input)            |

| SWM07 <sup>[2]</sup> | (3-state)             | I2S_SO<br>(output)             | I2S_SO<br>(output)             | UART_TXD<br>(output)           | UART_TXD<br>(output)           |

| SWM08 <sup>[2]</sup> | (3-state)             | UART_TXD<br>(output)           | EXT_RXEN(CRX) (output)         | EXT_RXEN(CRX) (output)         | EXT_RXEN(CRX) (output)         |

| SWM09 <sup>[2]</sup> | (3-state)             | UART_RXD<br>(input)            | EXT_PAEN(CTX) (output)         | EXT_PAEN(CTX) (output)         | EXT_PAEN(CTX) (output)         |

#### Ultra-low power 2.4 GHz Bluetooth Low Energy transceiver for audio streaming

Table 18. Versatile switch matrix...continued

| Pin                  | Default              | Configuration A <sup>[1]</sup> | Configuration B <sup>[1]</sup> | Configuration C <sup>[1]</sup> | Configuration D <sup>[1]</sup> |

|----------------------|----------------------|--------------------------------|--------------------------------|--------------------------------|--------------------------------|

| SWM10 <sup>[2]</sup> | (3-state)            | I2S_CLK<br>(input)             | I2S_CLK<br>(input)             | I2S_CLK<br>(input)             | (3-state)                      |

| SWM11 <sup>[2]</sup> | (3-state)            | I2S_WS<br>(input)              | I2S_WS<br>(input)              | I2S_WS<br>(input)              | (3-state)                      |

| SRQ                  | SPI_S_SRQ<br>(input) | SPI_S_SRQ<br>(input)           | SPI_S_SRQ<br>(input)           | SPI_S_SRQ<br>(input)           | SPI_S_SRQ<br>(input)           |

<sup>[1]</sup> The configuration of A,B,C, or D is performed by the host controller with an HCI SPI command just after booting the NXH3670.

Section 9.2 explains the default positions of SPI master and SPI slave during boot mode.

#### 7.2.12 Power management unit (PMU)

#### 7.2.12.1 General

The PMU module supports the following operating modes:

Operation on external power regulator (1.2 V)

It provides regulated power supplies from the external voltage to supply:

- Radio subsystem

- · Digital and memories

Under control of firmware, the PMU is able to optimize current consumption in each use case by enabling and controlling the supply of only the hardware blocks necessary for the use case.

The PMU also contains state machine that allows support of different low-power modes (see <u>Section 9</u>) and wake-up functionality. The wake-up can be triggered from the following sources:

- POR

- Low-power timer

- · SRQ (service request) pin

In addition, it contains functionality for supply voltage monitoring, Power-on reset (POR) and to detect power dips (BOD). It also includes a persistent register file for configuration and trimming that is kept in all power modes.

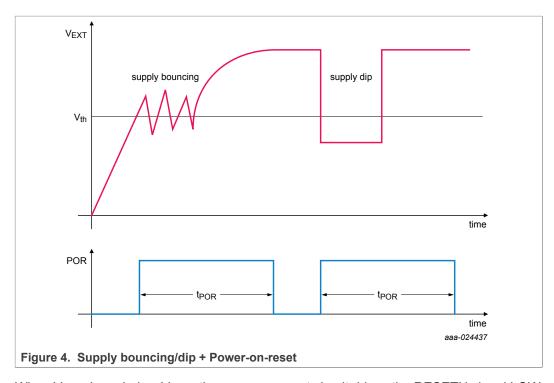

#### 7.2.12.2 Power-on reset (POR)

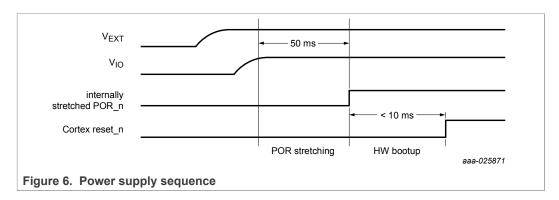

A power-on reset (POR) circuit ensures proper start-up of the chip. It comprises:

- A detector responsive to the presence (ramp-up) of the supply voltage VEXT

- A 50 ms delay circuit to stretch the POR signal. This delay is called TPOR. This delay

is to ensure proper start-up of the chip after connection with a new voltage supply

which can bounce.

The POR module is always enabled. A reset generated by the POR module resets the complete IC, including the PMU.

<sup>[2]</sup> SWM pins 5 to 11 are only enabled after the host controller triggers the function with an HCl SPI command.

### Ultra-low power 2.4 GHz Bluetooth Low Energy transceiver for audio streaming

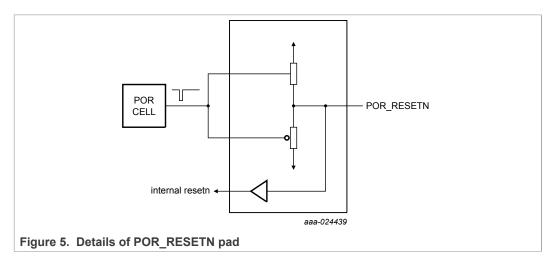

When  $V_{EXT}$  drops below  $V_{POR}$ , the power-on reset circuit drives the RESETN signal LOW weakly to generate a clean reset signal to reset the PMU. The PMU prolongs the reset for  $t_{POR}$  to reset the rest of the chip. When not active, the power-on reset circuit is driving the RESETN signal weakly HIGH (see <u>Figure 5</u>).

An external device can override the power-on reset circuit and trigger a reset by driving the RESETN signal LOW. It is not allowed to drive the RESETN signal HIGH or to put an external pull resistor on the RESETN signal. A HIGH on RESETN prevents correct operation of the power-on reset circuit.

#### Ultra-low power 2.4 GHz Bluetooth Low Energy transceiver for audio streaming

Table 19. POR

| Symbol           | Parameter           | Conditions                                                             | Min  | Тур | Max  | Unit |

|------------------|---------------------|------------------------------------------------------------------------|------|-----|------|------|

| T <sub>POR</sub> | POR stretching time |                                                                        | 34   | 50  | 102  | ms   |

| V <sub>TH</sub>  | POR threshold       | minimum $V_{EXT} = 0.8 \text{ V}$ , maximum $V_{EXT} = 1.45 \text{ V}$ | 0.68 | 8.0 | 0.89 | V    |

#### 7.2.12.3 Brownout detection (BOD)

In addition to the POR protecting the power domain which is continuously on, the NXH3670UK also has Brownout detection (BOD) for internal supplies. The brownout threshold voltage can be programmed. Each brownout detector generates a signal that can force a POR.

The goal of the BOD cells is to protect the circuit against malfunctioning if dips on the supply voltage occur.

#### 7.2.12.4 Persistent registers

The PMU also contains persistent registers. These registers are directly supplied from  $V_{\text{EXT}}$  so that their value is retained even when all other digital supplies are off.

These registers contain values that must be retained to allow restart from some low-power modes. The values that are stored here are configuration parameters and trimming values.

#### 7.2.12.5 Clock generation

The NXH3670UK typically derives its internal clocks from a 16 MHz/32 MHz crystal oscillator. In some modes, in order to save power or to generate faster clock, the chip can also generate clocks from internal oscillators. LPOs at 16 MHz and 20 MHz, HFOs at 44 MHz and 84 MHz and ULPO/LJO at 400 kHz oscillators are provided. The internal oscillators can be trimmed from the crystal oscillator clock.

#### 7.2.12.6 Crystal oscillator

An external crystal must be connected to the crystal oscillator pins (XIN, XOUT) in order to generate a clock for the NXH3670UK. Both 16 MHz and 32 MHz crystals are supported but internally the clock is 16 MHz.

The oscillator is provided with on-chip capacitors to remove the need for external load capacitors. A fraction of these capacitors is trimmable in order to adjust the frequency accuracy. The trimming is done through firmware during PCB assembly to get to the desired accuracy for the application.

The crystal oscillator is not enabled until the Cortex boots up; the control of the crystal remains under control of the firmware.

If a 16 MHz/32 MHz clock is already present in the application, this clock can be provided to the NXH3670UK through the XIN bump. However, to sustain RF performances (see <u>Table 22</u>), this clock must support the required characteristics.

If other devices want to slave from the NXH3670UK crystal, the crystal signal must be taken from the XIN bump. Constraints for this configuration can be found in  $\underline{\text{Table 23}}$ .

Table 20. 16 MHz crystal oscillator characteristics

| Symbol                | Parameter                                     | Conditions                                 | Min | Тур  | Max | Unit   |

|-----------------------|-----------------------------------------------|--------------------------------------------|-----|------|-----|--------|

| f <sub>XTAL</sub>     | crystal frequency                             |                                            | -   | 16   | -   | MHz    |

| $\Delta f_{XTAL}$     | crystal frequency tolerance [1]               | untrimmed, including temperature and aging | -60 | -    | +60 | ppm    |

| C <sub>L</sub>        | crystal load capacitance                      |                                            | 8   | 10   | 12  | pF     |

| C <sub>0</sub>        | crystal static capacitance                    |                                            | -   | 1.5  | 7   | pF     |

| R <sub>L-16</sub>     | crystal series resistance -<br>16 MHz         |                                            | -   | -    | 200 | Ω      |

| L <sub>S-16</sub>     | equivalent crystal serial inductance - 16 MHz |                                            | -   | -    | 90  | mH     |

| T <sub>XTAL</sub>     | crystal oscillator settling time [2]          |                                            | 0.8 | 1.5  | 2.5 | ms     |

| f <sub>noise16M</sub> | phase noise characteristics for               | offset from carrier at 10 kHz              | -   | -130 | -   | dBc/Hz |

|                       | 16 MHz crystal frequency                      | offset from carrier at 100 kHz             | -   | -136 | -   | dBc/Hz |

<sup>[1]</sup> To support a 1 Mbps data rate in NxH-C mode, a ±50 ppm accuracy is needed.

Table 21. 32 MHz crystal oscillator characteristics

| Symbol                | Parameter                                     | Conditions                                 | Min | Тур  | Max | Unit   |

|-----------------------|-----------------------------------------------|--------------------------------------------|-----|------|-----|--------|

| f <sub>XTAL</sub>     | crystal frequency                             |                                            | -   | 32   | -   | MHz    |

| $\Delta f_{XTAL}$     | crystal frequency tolerance [1]               | untrimmed, including temperature and aging | -60 | -    | +60 | ppm    |

| C <sub>L</sub>        | crystal load capacitance                      |                                            | 6   | 10   | 12  | pF     |

| C <sub>0</sub>        | crystal static capacitance                    |                                            | -   | 1.5  | 7   | pF     |

| R <sub>L-32</sub>     | crystal series resistance - 32 MHz            |                                            | -   | -    | 100 | Ω      |

| L <sub>S-32</sub>     | equivalent crystal serial inductance - 32 MHz |                                            | -   | -    | 45  | mH     |

| T <sub>XTAL</sub>     | crystal oscillator settling time [2]          |                                            | 0.8 | 1.5  | 2.5 | ms     |

| f <sub>noise32M</sub> | 32 MHz crystal frequency                      | offset from carrier at 10 kHz              | -   | -124 | -   | dBc/Hz |

|                       |                                               | offset from carrier at 100 kHz             | -   | -130 | -   | dBc/Hz |

<sup>[1]</sup> To support a 1 Mbps data rate in NxH-C mode, a ±50 ppm accuracy is needed.

Table 22. 16 MHz/32 MHz Input clock characteristics when external crystal is provided to XIN

| addio 22. To Milizoz Miliz Impactorock offaractoriotico wildir oxidifici oryotali lo provided to Alix |                                 |                                  |     |       |     |        |  |

|-------------------------------------------------------------------------------------------------------|---------------------------------|----------------------------------|-----|-------|-----|--------|--|

| Symbol                                                                                                | Parameter                       | Conditions                       | Min | Тур   | Max | Unit   |  |

| f <sub>CLK</sub>                                                                                      | crystal frequency               |                                  | -   | 16/32 | -   | MHz    |  |

| $\Delta f_{CLK}$                                                                                      | accuracy                        |                                  | -20 | -     | +20 | ppm    |  |

| $V_{PP}$                                                                                              | input clock amplitude           | peak to peak voltage (sine wave) | 500 | -     | 800 | mV     |  |

| f <sub>noise16M</sub>                                                                                 | phase noise characteristics for | offset from carrier at 10 kHz    | -   | -130  | -   | dBc/Hz |  |

|                                                                                                       | 16 MHz crystal frequency        | offset from carrier at 100 kHz   | -   | -136  | -   | dBc/Hz |  |

NXH3670UK

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2020. All rights reserved.

<sup>[2]</sup> Settling time depends on crystal parameters. Typical value based on 8 pF/60 mH/100  $\Omega$ .

<sup>[2]</sup> Settling time depends on crystal parameters. Typical value based on 8 pF/30 mH/100  $\Omega$ .

### Ultra-low power 2.4 GHz Bluetooth Low Energy transceiver for audio streaming

Table 22. 16 MHz/32 MHz Input clock characteristics when external crystal is provided to XIN...continued

| Symbol                                                | Parameter                     | Conditions                     | Min  | Тур  | Max    | Unit   |

|-------------------------------------------------------|-------------------------------|--------------------------------|------|------|--------|--------|

| f <sub>noise32M</sub> phase noise characteristics for | offset from carrier at 10 kHz | -                              | -124 | -    | dBc/Hz |        |

|                                                       | 32 MHz crystal frequency      | offset from carrier at 100 kHz | -    | -130 | -      | dBc/Hz |

Table 23. 16 MHz/32 MHz clock characteristics when external host loads from XIN

| Symbol           | Parameter              | Conditions                          |     | Min | Тур   | Max              | Unit |

|------------------|------------------------|-------------------------------------|-----|-----|-------|------------------|------|

| f <sub>CLK</sub> | crystal frequency      |                                     |     | -   | 16/32 | _                | MHz  |

| C <sub>L</sub>   | XIN pin load           |                                     |     | -   | -     | 5 <sup>[1]</sup> | pF   |

| V <sub>PP</sub>  | output clock amplitude | peak-to-peak voltage<br>(sine wave) | [2] | -   | 200   | -                | mV   |

<sup>[1]</sup> Depending on used crystal

### 7.2.13 One-time programmable (OTP) memory

The OTP holds trimming values for the PMU and RF. Programming of those bits is done during chip production.

<sup>[2]</sup> Output amplitude is configurable by firmware. The swing has impact on current consumption and phase noise. Full swing is needed in order to meet radio performance.

# 8 Debugging and testing facilities

#### **8.1 UART**

The NXH3670UK features a complete UART interface which both the ARM Cortex-M0 and the CoolFlux DSP can use. More information about configuration parameters of UART interfaces can be found in Table 15.

As well as this complete UART interface, the CoolFlux DSP has a dedicated TX-only UART for logging purposes

UARTs are available on SWM IOs according to <u>Table 18</u>.

### 9 Start-up and power modes

#### 9.1 Booting procedure

#### 9.1.1 Power supply sequence

To prevent leakage current via I/Os of NXH3670UK and undefined state of the SWMs,  $V_{IO}$  should not be enabled before  $V_{EXT}$ .  $V_{IO}$  is enabled preferably at the same time as or later than  $V_{EXT}$ .

#### 9.1.2 Boot loader

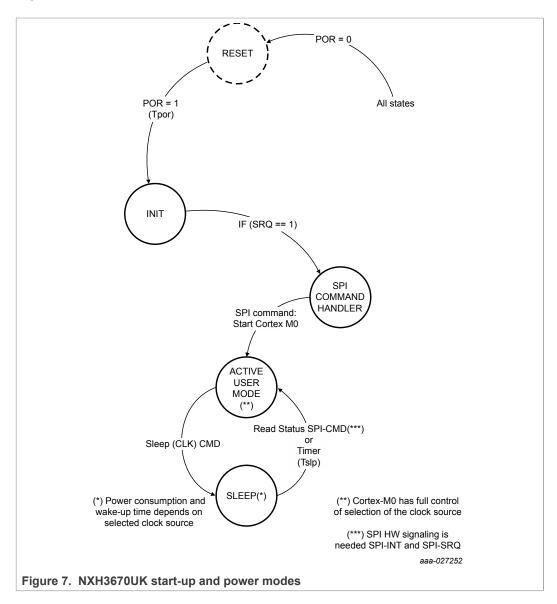

The boot loader is the default ROM code which is executed by the ARM Cortex M0 after a POR. The boot loader brings the IC in the 'active user mode' as shown in <u>Figure 7</u>. The boot loader in SPI Command Handler exposes command over SPI in order to load an image.

More information of the functionality can be found in <u>Section 9.2</u>.

Detailed boot loader commands can be found in the "NXH3670UK boot loader" document (Ref. 2).

### 9.1.3 Boot time

The boot time depends on several factors that are system and user application specific:

- · Size of the firmware to be downloaded

- · Speed of the SPI interface

- Maximum current allowed by the application (possibly limiting the speed of the SPI interface)

There is also a fixed time at start-up before the real boot procedure can start. This time includes POR reset, configuration, and start-up of the supplies and the clock. This time is less than 60 ms, considering a POR delay of 50 ms.

Ultra-low power 2.4 GHz Bluetooth Low Energy transceiver for audio streaming

### 9.2 State diagram

<u>Figure 7</u> shows how the NXH3670UK starts up and switches between different states. The sections below describe the different states and how the system switches between them. The different states are:

- Reset

- Init

- · SPI command handler

- · Active user mode

- SLEEP

### 9.2.1 Reset (undefined)

This state is the default state of the chip when the supply is connected. The full chip is OFF, with the core kept in a stable state by the POR cell.

All the functions in the chip are off or disabled. Only the POR cell is active.

This state can be entered from all other state for different reasons:

- · Supply voltage going below the minimum level

- BOD event (impact of BOD event is configurable by API after start-up)

- Firmware generated reset

As a POR state transition can be generated from all states, it is not repeated as possible state transition in the sections below.

When the power-on reset cell has settled, the chip can start up and enter the INIT state.

#### 9.2.2 Init

The init state configures the NXH3670UK for correct operation. This state can only be entered from the reset state. The supply voltage is measured and the PMU configures the different supply generation blocks to the right settings. The trimming and functional configuration settings are loaded from OTP. To keep the current consumption low in this state, most of the digital logic remains inactive.

The Cortex works from the on-chip 16 MHz LPO oscillator clock in the Init state.

The NXH3670UK checks the status of the SRQ (service request) input pin.

- If SRQ = logic 0, the NXH3670UK stays in the init state

- If SRQ = logic 1, the NXH3670UK enters the SPI command handler state

#### 9.2.3 SPI command handler

During this state, the MCU system is started and the boot loader firmware is executed from ROM to enable firmware download.

The NXH3670UK is slave of the host and download is started and executed through SPI commands

The following steps are performed:

- · SPI slave interface is enabled by default using:

- SMW00: SPI\_S\_MISO

- SMW01: SPI S MOSI

- SMW02: SPI\_S\_CLK

- SMW03: SPI S CS

- Based on a set of SPI commands, the host can download an image into the ARM Cortex-M0 memory

- When the firmware download is completed, the NXH3670UK moves to active user mode state upon receiving an SPI command

#### Ultra-low power 2.4 GHz Bluetooth Low Energy transceiver for audio streaming

Following functionality is provided to the host controller based on SPI commands:

• Read & Write ARM memory:

The host is able to read and write ARM memory.

• Read & Write CoolFlux memory:

The host is able to read and write CoolFlux program and data memory.

• Initialize/Disable CoolFlux:

The host can enable and disable the CoolFlux DSP.

· Start application:

The host is able to force the boot loader to start execution from a given ARM-programmemory location.

· Get version:

The host can retrieve the version of the boot loader and the hardware.

· Reset command:

The host can trigger a reset of the device.

Reinitialize SWM:

The host can reconfigure the SWM.

#### 9.2.4 Active user mode

In this state, the NXH3670UK can activate all blocks and run all necessary activities for the application. RF transmission and reception, audio processing, link control, SPI transfers are all done in active user mode state

Generally, the system only stays in this mode during the real period of activity. When this activity is finished, it switches to the sleep state. However, even in this mode the current consumption is minimized by stopping the clock and the supply to the blocks which are not active.

This state can be entered from the SPI command handler state after firmware download or from the sleep state when the chip wakes up.

The system can enter the sleep state based on a dedicated MCU command.

In the active user mode state, the SPI\_S\_SRQ and SPI\_S\_INT must be used for signaling from the host to the NXH3670UK.

#### 9.2.5 Sleep

The sleep state is the low-power mode state. To reduce current consumption, this state is used as much as possible between periods of activity of the chip. It allows the quickest restart as the full state of the chip is kept.

In this state, the digital logic that must retain its state is kept supplied. All the unnecessary clocks are stopped and the MCU are in idle state. Typically, the system runs on ULPO or LJO<sup>1</sup> but the firmware can decide to keep other clocks active (for example, the XTAL clock). Because the current consumption depends on the clocks and blocks that are requested to stay active by the MCU, it is variable in this state. However, most of the time the leakage of the digital logic and the clock generation determines the current consumption.

This state is entered from the active user mode state through a Cortex MCU sleep command.

The system can go back to the active user mode state based on interrupt, typically coming from an SPI read status command or a timer event.

NXH3670UK

All information provided in this document is subject to legal disclaimers.

<sup>1</sup> Applications using ULPO/LJO as sleep timer clock must consider the drift in frequency caused by a change in temperature or VEXT supply.

# 10 Current consumption

<u>Table 24</u> shows the NXH3670UK current consumption for different modes of operation. The conditions for the current values are given in the table. For the low-power modes and for the radio modes, the current is typically constant. For the use cases, the value given is an average of the current consumption over multiple periods of RF activity.

All values are measured on reference board for typical process at 1.2 V and 25  $^{\circ}$ C. They do not include the current from V<sub>IO</sub> as it depends on activity, switch matrix configuration, and application board load.

The NXH3670UK uses the high-performance (HP) mode.

Table 24. Current consumption

| Mode/Use case             | Conditions                                                                                                                                                                    | HP                 | Unit   |  |  |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--------|--|--|

| SLEEP <sup>[1]</sup>      | ULPO active and Cortex retention                                                                                                                                              | 63                 | μA     |  |  |

|                           | LJO active and Cortex retention (incremental) LJO frequency is 650 kHz                                                                                                        |                    | μΑ     |  |  |

|                           | CoolFlux memory retention (incremental)                                                                                                                                       | 10                 | μA     |  |  |

| XTAL oscillator<br>32 MHz | Includes RF band gap and XTAL LDO <sup>[2]</sup>                                                                                                                              | 115                | μΑ     |  |  |

| Start-up                  | maximum current during start-up, from POR to the active user mode state                                                                                                       | < 4                | mA     |  |  |

| Active                    | Cortex active baseline current. XTAL oscillator not included                                                                                                                  | 950 <sup>[3]</sup> | μΑ     |  |  |

|                           | audio subsystem baseline (incremental)                                                                                                                                        | 155                | μΑ     |  |  |

|                           | CoolFlux memory active (incremental)                                                                                                                                          |                    | μA     |  |  |

| Cortex                    | processor and memory only, excluding leakage and static clock tree consumption. Radio and audio inactive.                                                                     |                    |        |  |  |

|                           | WFI                                                                                                                                                                           | 17                 | µA/MHz |  |  |

|                           | while-1 loop                                                                                                                                                                  | 76                 | μΑ/MHz |  |  |

| CoolFlux                  | processor and memory only, excluding leakage and static clock tree consumption.                                                                                               |                    |        |  |  |

|                           | idle                                                                                                                                                                          | 8                  | μΑ/MHz |  |  |

|                           | SBC encoding                                                                                                                                                                  | 61                 | μΑ/MHz |  |  |

| Audio HW                  | dataport in 16 kHz – coder – decoder – ASRC – dataport out. Not including V <sub>IO</sub> current (use case dependent). (excluding leakage and static clock tree consumption) | 90                 | μΑ     |  |  |

| Radio activation          |                                                                                                                                                                               | 404                | μΑ     |  |  |

|                           | after that XTAL settles                                                                                                                                                       | 0.162              | ms     |  |  |

### Ultra-low power 2.4 GHz Bluetooth Low Energy transceiver for audio streaming

Table 24. Current consumption...continued

| Mode/Use case | Conditions                                                                                                                     | HP   | Unit |

|---------------|--------------------------------------------------------------------------------------------------------------------------------|------|------|

| Radio RX      | ramp-up current including RFMAC and RFPHY but not Cortex. All radio modes                                                      | 1.25 | mA   |

|               | ramp-up time                                                                                                                   | 0.12 | ns   |

|               | active current including RFMAC and RFPHY but not Cortex, All radio modes                                                       | 4.0  | mA   |

| Radio TX      | dio TX ramp-up current including RFMAC and RFPHY but not Cortex. All radio modes                                               |      | mA   |

|               | ramp-up time                                                                                                                   | 0.12 | ms   |

|               | active current at -10 dBm, including RFMAC and RFPHY but not Cortex. All radio modes, Ideal load presented to RF antenna bumps | 3.7  | mA   |

|               | active current at 0 dBm, including RFMAC and RFPHY but not Cortex. All radio modes. Ideal load presented to RF antenna bumps   | 7.2  | mA   |

|               | active current at 4 dBm, including RFMAC and RFPHY but not Cortex. All radio modes. Ideal load presented to RF antenna bumps   | 13.4 | mA   |

The XTAL oscillator current consumption must also be included for sleep mode calculations.

Murata XRCMD32M000FXP52R0 crystal (recommended).

This number includes static power consumption of the 84 MHz FRO

# 11 Limiting values

Table 25. Limiting values In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol              | Parameter                | Conditions                                                 | Min  | Max                 | Unit |  |

|---------------------|--------------------------|------------------------------------------------------------|------|---------------------|------|--|

| $V_{EXT,MAX}$       | supply voltage           | applying to all supplies connected to the V <sub>EXT</sub> | -0.5 | +1.5566             | V    |  |

| V <sub>IO,MAX</sub> | IO Pad voltage           | fail-safe operation between minimum and maximum values.    | -0.3 | +2.7                | V    |  |

| P <sub>TOT</sub>    | total power consumption  |                                                            | -    | 1                   | W    |  |

| T <sub>JUNCT</sub>  | junction temperature     |                                                            | -40  | +125                | °C   |  |

| T <sub>STO</sub>    | storage temperature      |                                                            | -40  | +150                | °C   |  |

| RH                  | operating humidity range | [1]                                                        | -    | 95                  | %    |  |

| V <sub>ES</sub>     | electrostatic handling   | human body model (HBM) <sup>[2]</sup>                      |      |                     |      |  |

|                     | voltage                  | all pins                                                   | -    | 2000 <sup>[3]</sup> | V    |  |

|                     |                          | charged device model (CDM) <sup>[4]</sup>                  |      |                     |      |  |

|                     |                          | all pins                                                   | -    | 500 <sup>[5]</sup>  | V    |  |

MSL - Moisture Sensitivity Level - JEDEC J-STD-20D - maximum level 3 (168 hours floor life at ≤ 30 °C and 60 % relative humidity)

Equivalent to discharging a 100 pF capacitor through a 1.5 kΩ series resistor (human body model) compliant with JESD22-A115-AJS-001-2014 norm.

JEDEC document JEP155 states that 500 V HBM allows safe manufacturing with a standard ESD control process Only applied to integrated component, Compliant with JESD22-C101-AC101F norm.

JEDEC document JEP157 states that 500 V HBM allows safe manufacturing with a standard ESD control process

### 12 Electrical characteristics

Table 26. Electric and environmental characteristics

| Symbol             | Parameter                                                                 | Conditions                                                            | Min                   | Тур                    | Max  | Unit            |