### PROGRAMMABLE OVERVOLTAGE PROTECTOR **OUAD FORWARD-CONDUCTING P-GATE THYRISTOR**

## **TISP61089Q SLIC Overvoltage Protector**

**Quad Voltage-Programmable Protector**

- Wide -20 V to -155 V Programming Range

- Low 5 mA max. Gate Triggering Current

- High 150 mA min. Holding Current

#### 10/700 Protection Voltage Specified

| Element                            | Protection Level<br>40 A, 10/700 |

|------------------------------------|----------------------------------|

| Diode                              | +12                              |

| Crowbar<br>V <sub>GG</sub> = -48 V | -64                              |

#### Rated for ITU-T and YD/T-950 10/700 impulses

#### Also rated for Telcordia Intra-building impulses

#### **Description**

The TISP61089Q is a quad forward-conducting buffered p-gate overvoltage protector. It is designed to protect monolithic SLICs (Subscriber Line Interface Circuits) against overvoltages on the telephone line caused by lightning, a.c. power contact and induction. The TISP61089Q limits voltages that exceed the SLIC supply rail voltage. The TISP61089Q parameters are specified to allow equipment compliance with Bellcore GR-1089-CORE, ITU-T K.20, K.21 and K.45 and YD/T-950.

The SLIC line driver section is typically powered from 0 V (ground) and a negative voltage in the region of -20 V to -75 V. The protector gate is connected to this negative supply. This references the protection (clipping) voltage to the negative supply voltage. As the protection voltage will then track the negative supply voltage the overvoltage stress on the SLIC is minimized.

Positive overvoltages are clipped to ground by diode forward conduction. Negative overvoltages are initially clipped close to the SLIC negative supply

rail value. If sufficient current is available from the overvoltage, then the protector will crowbar into a low voltage on-state condition. As the overvoltage subsides, the high holding current of the crowbar prevents d.c. latchup.

The TISP61089Q is intended to be used with a series combination of a 25  $\Omega$  or higher resistance and a suitable overcurrent protector. Power fault compliance requires the series overcurrent element to open-circuit or become high impedance (see Applications Information). For equipment compliant to ITU-T recommendations K.20 or K.21 only, the recommended 10  $\Omega$  series resistor value is set by the power cross requirements.

These monolithic protection devices are fabricated in ion-implanted planar vertical power structures for high reliability and are virtually transparent in normal operation. The TISP61089Q buffered gate design reduces the loading on the SLIC supply during overvoltages caused by power cross and induction. The TISP61089Q is available in an 8-pin plastic small-outline surface mount package.

# D Package (Top View)

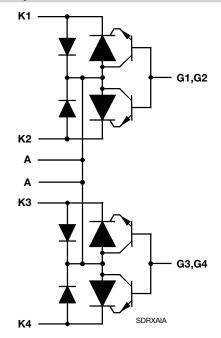

#### **Device Symbol**

#### **How to Order**

| Device     | Package                    | Carrier              | Order As       | Marking Code | Standard Quantity |

|------------|----------------------------|----------------------|----------------|--------------|-------------------|

| TISP61089Q | 8 Pin Small Outline (D008) | Embossed Tape Reeled | TISP61089QDR-S | 1089Q        | 2500              |

<sup>\*</sup>RoHS Directive 2002/95/EC Jan 27 2003 including Annex

JULY 2010

Specifications are subject to change without notice.

Customers should verify actual device performance in their specific applications.

## TISP61089Q SLIC Overvoltage Protector

## **BOURNS**®

#### Absolute Maximum Ratings, T<sub>J</sub> = 25 °C (Unless Otherwise Noted)

| Rating                                                                                                                                                                                                          | Symbol                          | Value             | Unit            |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-------------------|-----------------|----|

| Repetitive peak off-state voltage, I <sub>G</sub> = 0                                                                                                                                                           | -40 °C ≤ T <sub>J</sub> ≤ 85 °C | V <sub>DRM</sub>  | -170            | V  |

| Repetitive peak gate-cathode voltage, V <sub>KA</sub> = 0                                                                                                                                                       | -40 °C ≤ T <sub>J</sub> ≤ 85 °C | V <sub>GKRM</sub> | -167            |    |

| Non-repetitive peak on-state pulse current (see Notes 1 and 2)                                                                                                                                                  |                                 |                   |                 |    |

| 10/1000 µs (Bellcore GR-1089-CORE, Issue 1, November 1994, Section 4) 5/320 (ITU-T K.20/21/45, YD/T-950, open circuit voltage waveshape 10/700) 2/10 (Bellcore GR-1089-CORE, Issue 1, November 1994, Section 4) |                                 | I <sub>TSP</sub>  | 30<br>40<br>120 | А  |

| Non-repetitive peak on-state current, 60 Hz (see Notes 1, 2 and 3) 900 s                                                                                                                                        |                                 | I <sub>TSM</sub>  | 0.5             | А  |

| Non-repetitive peak gate current, 2/10 µs pulse, cathodes commoned (see Notes 1 and 2)                                                                                                                          |                                 | I <sub>GSM</sub>  | 40              | Α  |

| Junction temperature                                                                                                                                                                                            |                                 | TJ                | -40 to +150     | °C |

| Storage temperature range                                                                                                                                                                                       |                                 | T <sub>stg</sub>  | -40 to +150     | °C |

- NOTES: 1. Initially the protector must be in thermal equilibrium with T<sub>J</sub> = 25 °C. The surge may be repeated after the device returns to its initial conditions.

- 2. These non-repetitive rated currents are peak values for either polarity. The rated current values may be applied to any cathode-anode terminal pair. Additionally, all cathode-anode terminal pairs may have their rated current values applied simultaneously (in this case the anode terminal current will be four times the rated current value of an individual terminal pair).

- 3. EIA/JESD51-2 environment and EIA/JESD51-7 high effective thermal conductivity test board (multi-layer) connected with 0.6 mm printed wiring track widths.

#### **Recommended Operating Conditions**

|                |                                                                            | Min | Тур | Max | Unit |

|----------------|----------------------------------------------------------------------------|-----|-----|-----|------|

| $C_{G}$        | Gate decoupling capacitor                                                  |     | 100 |     | nF   |

| R <sub>S</sub> | TISP61089Q series resistor for first-level and second-level surge survival | 40  |     |     | 0    |

| l 's           | TISP61089Q series resistor for first-level surge survival                  | 25  |     |     | 32   |

#### Electrical Characteristics, T<sub>J</sub> = 25 °C (Unless Otherwise Noted)

|                   | Parameter                     | Test Conditions                                                            |             | Min  | Тур | Max | Unit |

|-------------------|-------------------------------|----------------------------------------------------------------------------|-------------|------|-----|-----|------|

| I <sub>D</sub>    | Off-state current             | $V_D = V_{DRM}, V_{GK} = 0$                                                |             |      |     | -5  | μΑ   |

| V <sub>(BO)</sub> | Breakover voltage             | 10/700 μs, $I_T$ = -40 A, $R_S$ = 55 Ω, $V_{GG}$ = -48 V, $C_G$ = 100nF    |             |      |     | -64 | V    |

| V <sub>F</sub>    | Forward voltage               | $I_F = 5 \text{ A}, t_W = 200 \ \mu \text{s}$                              |             |      |     | 3   | V    |

| V <sub>FRM</sub>  | Peak forward recovery voltage | 10/700 μs, $I_F$ = 40 A, $R_S$ = 55 Ω, $V_{GG}$ = -48 V, $C_G$ = 100nF     |             |      | 12  |     | V    |

| IH                | Holding current               | $I_T = -1 \text{ A, di/dt} = 1 \text{ A/ms, V}_{GG} = -100 \text{ V}$      |             | -150 |     |     | mA   |

| I <sub>GAS</sub>  | Gate reverse current          | $V_{GG} = V_{GK} = V_{GKRM}, V_{KA} = 0$                                   |             |      |     | -5  | μΑ   |

| I <sub>GT</sub>   | Gate trigger current          | $I_T = 3 \text{ A}, t_{p(g)} \ge 20  \mu\text{s}, V_{GG} = -100 \text{ V}$ |             |      |     | 5   | mA   |

| V <sub>GT</sub>   | Gate trigger voltage          | $I_T = 3 \text{ A}, t_{p(g)} \ge 20  \mu\text{s}, V_{GG} = -100 \text{ V}$ |             |      |     | 2.5 | V    |

| C <sub>AK</sub>   | Anode-cathode off-state       | f = 1 MHz, V <sub>d</sub> = 1 V I <sub>G</sub> = 0, (see Note 4)           | $V_D = -3V$ |      |     | 100 | pF   |

| ∪AK               | capacitance capacitance       | $V_{D} = -48V$                                                             |             |      | 50  | "   |      |

#### **Thermal Characteristics**

|                 | Parameter                               | Test Conditions                                                                 | Min | Тур | Max | Unit |

|-----------------|-----------------------------------------|---------------------------------------------------------------------------------|-----|-----|-----|------|

| $R_{\theta JA}$ | Junction to free air thermal resistance | P <sub>tot</sub> = 0.8 W, T <sub>A</sub> = 25 °C<br>5 cm <sup>2</sup> , FR4 PCB |     |     | 160 | °C/W |

#### **Parameter Measurement Information**

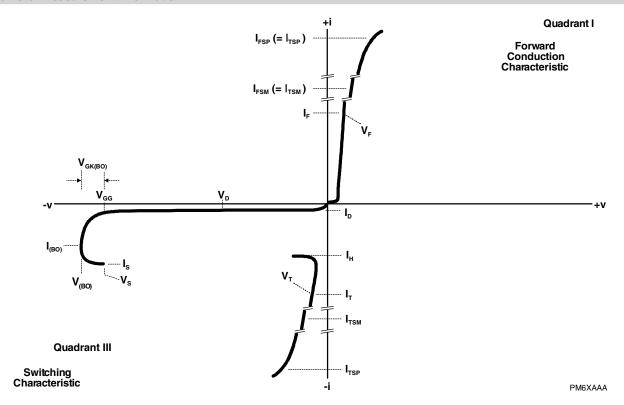

Figure 1. Voltage-Current Characteristic

#### **Applications Information**

#### **Typical Applications Circuit**

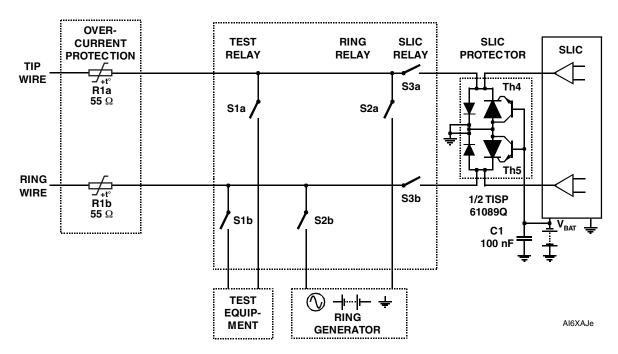

Figure 2 shows a typical TISP61089Q SLIC card protection circuit. The incoming line conductors, Ring (R) and Tip (T), connect to the relay matrix via the series overcurrent protection. Positive temperature coefficient (PTC) resistors can be used for overcurrent protection. Resistors will reduce the prospective current from the surge generator for both the TISP61089Q and the ring/test protector.

Figure 2. Typical Application Circuit

#### **Bourns Sales Offices**

| Region        | Phone            | Fax              |

|---------------|------------------|------------------|

| The Americas: | +1-951-781-5500  | +1-951-781-5700  |

| Europe:       | +41(0)41-7685555 | +41(0)41-7685510 |

| Asia-Pacific: | +886-2-25624117  | +886-2-25624116  |

#### **Technical Assistance**

| Region        | Phone            | Fax              |

|---------------|------------------|------------------|

| The Americas: | +1-951-781-5500  | +1-951-781-5700  |

| Europe:       | +41(0)41-7685555 | +41(0)41-7685510 |

| Asia-Pacific: | +886-2-25624117  | +886-2-25624116  |

#### www.bourns.com

Bourns® products are available through an extensive network of manufacturer's representatives, agents and distributors. To obtain technical applications assistance, a quotation, or to place an order, contact a Bourns representative in your area.