# **DDR 1.8 Amp Source / Sink** V<sub>TT</sub> Termination Regulator

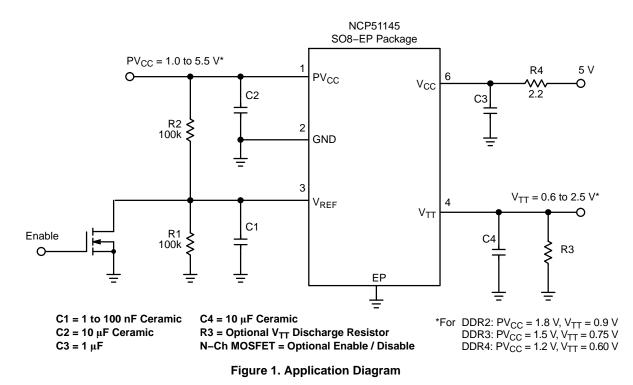

The NCP51145 is a linear regulator designed to supply a regulated V<sub>TT</sub> termination voltage for DDR–II, DDR–III, LPDDR–III and DDR–IV memory applications. The regulator is capable of actively sourcing and sinking  $\pm 1.8$  A peak currents while regulating an output voltage to within  $\pm 20$  mV. The output termination voltage is regulated to track V<sub>DDQ</sub> / 2 by two external voltage divider resistors connected to the PV<sub>CC</sub>, GND, and V<sub>REF</sub> pins.

The NCP51145 incorporates a high–speed differential amplifier to provide ultra–fast response to line and load transients. Other features include source/sink current limiting, soft–start and on–chip thermal shutdown protection.

### Features

- For DDR V<sub>TT</sub> Applications, Source/Sink Currents:

- Supports DDR–II to  $\pm 1.8$  A, DDR–III to  $\pm 1.5$  A

- Supports LPDDR-III and DDR-IV to ±1.2 A

- Stable Using Ceramic–Only (Very Low ESR) Capacitors

- Integrated Power MOSFETs

- High Accuracy V<sub>TT</sub> Output at Full-Load

- Fast Transient Response

- Built-in Soft-Start

- Shutdown for Standby or Suspend Mode

- Integrated Thermal and Current-Limit Protection

- V<sub>TT</sub> Remote Sense Available in the DFN8 2x2mm Package

- These Devices are Pb-Free and are RoHS Compliant

## **Typical Applications**

- DDR-II / DR-III / DDR-IV SDRAM Termination Voltage

- Motherboard, Notebook, and VGA Card Memory Termination

- Set Top Box, Digital TV, Printers

- Low Power DDR-3LP

#### **ORDERING INFORMATION**

| Device        | Package             | Shipping <sup>†</sup> |

|---------------|---------------------|-----------------------|

| NCP51145PDR2G | SOIC-8<br>(Pb-Free) | 2500 / Tape &<br>Reel |

| NCP51145MNTAG | DFN-8<br>(Pb-Free)  | 3000 / Tape &<br>Reel |

+For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

# NCP51145

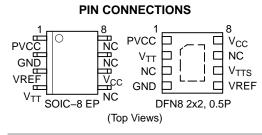

#### **PIN FUNCTION DESCRIPTION**

| Pin No.<br>SO8–EP | Pin No.<br>DFN8 | Pin Name         | Description                                                                                                                                                                                                                                                                             |

|-------------------|-----------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                 | 1               | PV <sub>CC</sub> | Input voltage which supplies current to the output pin. $C_{IN}\cong{}^{1\!\!/_2}\bullet C_{OUT}$                                                                                                                                                                                       |

| 2                 | 4               | GND              | Common Ground                                                                                                                                                                                                                                                                           |

| 3                 | 5               | V <sub>REF</sub> | Buffered reference voltage input equal to $\frac{1}{2}$ of V <sub>DDQ</sub> and active low shutdown pin. An external resistor divider dividing down the PV <sub>CC</sub> voltage creates the regulated output voltage. Pulling the pin to ground (0.15 V maximum) turns the device off. |

| 4                 | 2               | V <sub>TT</sub>  | Regulator output voltage capable of sourcing and sinking current while regulating the output rail. $C_{OUT}$ = 10 $\mu$ F Ceramic, or greater                                                                                                                                           |

| 5, 7, 8           | 3, 7            | NC               | True No Connect                                                                                                                                                                                                                                                                         |

| 6                 | 8               | V <sub>CC</sub>  | The V <sub>CC</sub> pin is a 5 V input pin that provides internal bias to the controller. $\rm PV_{CC}$ should always be kept lower or equal to V <sub>CC</sub> .                                                                                                                       |

| -                 | 6               | V <sub>TTS</sub> | V <sub>TT</sub> Sense                                                                                                                                                                                                                                                                   |

| EP                | EP              | EPAD             | Pad for thermal connection. The exposed pad must be connected to the ground plane using multiple vias for maximum power dissipation performance.                                                                                                                                        |

## NCP51145

#### **ABSOLUTE MAXIMUM RATINGS**

| Rating                                                                            | Symbol                                | Value      | Unit |

|-----------------------------------------------------------------------------------|---------------------------------------|------------|------|

| Input Supply Voltage Range ( $V_{cc} \ge PV_{CC}$ ) (Note 1)                      | PV <sub>CC</sub> ,<br>V <sub>CC</sub> | –0.3 to 6  | V    |

| Output Voltage Range                                                              | V <sub>TT</sub>                       | –0.3 to 6  | V    |

| Reference Input Range                                                             | V <sub>REF</sub>                      | -0.3 to 6  | V    |

| Maximum Junction Temperature                                                      | T <sub>J(max)</sub>                   | 150        | °C   |

| Storage Temperature Range                                                         | TSTG                                  | -65 to 150 | °C   |

| ESD Capability, Human Body Model (Note 2)                                         | ESDHBM                                | 2          | kV   |

| ESD Capability, Machine Model (Note 2)                                            | ESDMM                                 | 200        | V    |

| Lead Temperature Soldering<br>Reflow (SMD Styles Only), Pb–Free Versions (Note 3) | T <sub>SLD</sub>                      | 260        | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Refer to ELECTRICAL CHĂRACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

2. This device series incorporates ESD protection and is tested by the following methods:

ESD Human Body Model tested per AEC-Q100-002 (EIA/JESD22-A114)

ESD Machine Model tested per AEC-Q100-003 (EIA/JESD22-A115)

Latchup Current Maximum Rating: ≤150 mA per JEDEC standard: JESD78

3. For information, please refer to our Soldering and Mounting Techniques Reference Manual, SOLDERRM/D

## THERMAL CHARACTERISTICS

| Rating                                                                                                                                    | Symbol                               | Value     | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------|------|

| Thermal Characteristics, SO8–EP (Note 4)<br>Thermal Resistance, Junction–to–Air (Note 5)<br>Thermal Reference, Junction–to–Lead2 (Note 5) | R <sub>θJA</sub><br>R <sub>ΨJL</sub> | 82<br>TBD | °C/W |

4. Refer to ELECTRICAL CHARACTERISTIS and APPLICATION INFORMATION for Safe Operating Area.

5. Values based on copper area of 645 mm<sup>2</sup> (or 1 in<sup>2</sup>) of 1 oz copper thickness and FR4 PCB substrate.

#### **OPERATING RANGES** (Note 6)

| Rating              | Symbol           | Min  | Max  | Unit |

|---------------------|------------------|------|------|------|

| Input Voltage       | PV <sub>CC</sub> | 1.0  | 5.5  | V    |

| Bias Supply Voltage | V <sub>CC</sub>  | 4.75 | 5.25 | V    |

| Ambient Temperature | T <sub>A</sub>   | -40  | 85   | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

6. Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

# NCP51145

#### **ELECTRICAL CHARACTERISTICS**

$PV_{CC} = 1.8 \text{ V} / 1.5 \text{ V}; \text{ } V_{CC} = 5 \text{ V}; \text{ } V_{REF} = 0.9 \text{ V} / 0.75 \text{ V}; \text{ } C_{TT} = 10 \text{ } \mu\text{F} \text{ (Ceramic)}, \text{ } T_{A} = +25^{\circ}\text{C}, \text{ unless otherwise specified}.$

| Parameter                    | Test Conditions                                                           | Symbol              | Min  | Тур | Max  | Unit |

|------------------------------|---------------------------------------------------------------------------|---------------------|------|-----|------|------|

| REGULATOR OUTPUT             |                                                                           |                     | -    | -   |      |      |

| Output Offset Voltage        | I <sub>out</sub> = 0 A                                                    | V <sub>OS</sub>     | -16  | -   | +16  | mV   |

| Load Regulation              | $I_{out}$ = ±1.8 A, PV <sub>CC</sub> = 1.8 V, V <sub>REF</sub> = 0.9 V    |                     |      |     | +4   |      |

|                              | $I_{out}$ = ±1.5 A, PV <sub>CC</sub> = 1.5 V, V <sub>REF</sub> = 0.75 V   | Dur                 |      |     |      |      |

|                              | $I_{out}$ = ±1.2 A, PV <sub>CC</sub> = 1.35 V, V <sub>REF</sub> = 0.675 V | Reg <sub>load</sub> | -4   | _   |      | mV   |

|                              | $I_{out}$ = ±1.2 A, PV <sub>CC</sub> = 1.2 V, V <sub>REF</sub> = 0.6 V    |                     |      |     |      |      |

| INPUT AND STANDBY CURREN     | TS                                                                        |                     |      |     |      |      |

| Bias Supply Current          | I <sub>out</sub> = 0 A                                                    | I <sub>BIAS</sub>   | -    | 1   | 2.5  | mA   |

| Standby Current              | $V_{REF}$ < 0.2 V (Shutdown), $R_{LOAD}$ = 180 $\Omega$                   | I <sub>STB</sub>    | -    | 2   | 90   | μA   |

| CURRENT LIMIT PROTECTION     |                                                                           |                     |      |     |      |      |

|                              | $PV_{CC} = 1.8 V, V_{REF} = 0.9 V$                                        |                     | 2    | -   | 3.5  | A    |

| Current Limit                | PV <sub>CC</sub> = 1.5 V, V <sub>REF</sub> = 0.75 V                       | ILIM                | 1.5  | -   | 3.5  |      |

| SHUTDOWN THRESHOLDS          |                                                                           |                     |      |     |      | -    |

| Shutdown Threshold Voltage   | Enable                                                                    | V <sub>IH</sub>     | 0.45 | -   |      |      |

|                              | Shutdown                                                                  | VIL                 | -    | -   | 0.15 | V    |

| THERMAL SHUTDOWN             |                                                                           | -                   | -    | -   | -    |      |

| Thermal Shutdown Temperature | $V_{CC} = 5 V$                                                            | T <sub>SD</sub>     | -    | 125 | -    | °C   |

| Thermal Shutdown Hysteresis  | V <sub>CC</sub> = 5 V                                                     | T <sub>SH</sub>     | -    | 35  | -    | °C   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

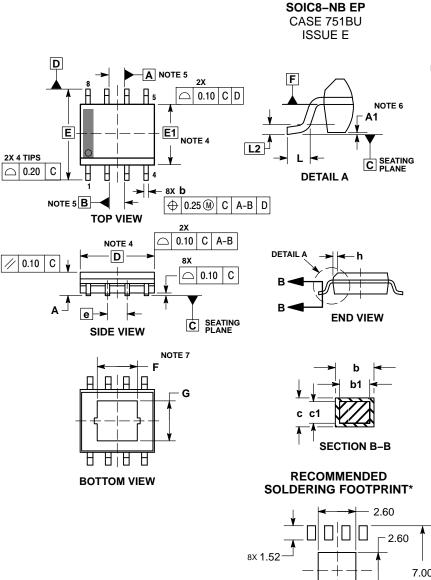

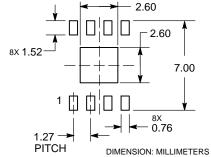

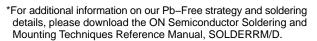

#### PACKAGE DIMENSIONS

NOTES:

- 1. DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994. CONTROLLING DIMENSION: MILLIMETERS.

- DIMENSION & DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE PROTRUSION SHALL BE 0.10mm IN EXCESS OF MAXIMUM MATERIAL CONDITION. 3.

- CONDITION. DIMENSION D DOES NOT INCLUDE MOLD FLASH, PROTRUSIONS, OR GATE BURRS. MOLD FLASH, PROTRUSIONS, OR GATE BURRS SHALL NOT EXCEED 0.15mm PER SIDE. DIMENSION E DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR 4. PROTRUSION SHALL NOT EXCEED 0.25mm PER SIDE. DIMENSIONS D AND E ARE DETERMINED AT DATUM F.

- 5. DIMENSIONS A AND B ARE TO BE DETERMINED

- DIMENSIONS A AND B ARE TO BE DETERMINED AT DATUM F. A1 IS DEFINED AS THE VERTICAL DISTANCE FROM THE SEATING PLANE TO THE LOWEST POINT ON THE PACKAGE BODY. TAB CONTOUR MAY VARY MINIMALLY TO INCLUDE 6.

- 7. TOOLING FEATURES.

|     | MILLIMETERS |       |  |  |  |

|-----|-------------|-------|--|--|--|

| DIM | MIN MAX     |       |  |  |  |

| Α   | 1.35        | 1.75  |  |  |  |

| A1  | 0.00        | 0.10  |  |  |  |

| b   | 0.31        | 0.51  |  |  |  |

| b1  | 0.28        | 0.48  |  |  |  |

| С   | 0.17        | 0.25  |  |  |  |

| c1  | 0.17 0.23   |       |  |  |  |

| D   | 4.90 BSC    |       |  |  |  |

| Е   | 6.00 BSC    |       |  |  |  |

| E1  | 3.90 BSC    |       |  |  |  |

| е   | 1.27        | 7 BSC |  |  |  |

| F   | 1.55        | 2.39  |  |  |  |

| G   | 1.55        | 2.39  |  |  |  |

| h   | 0.25        | 0.50  |  |  |  |

| L   | 0.40 1.27   |       |  |  |  |

| L2  | 0.25 BSC    |       |  |  |  |

DIMENSIONS: MILLIMETERS

\*For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

| DOCUMENT NUMBER:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 98AON18658D                            | Electronic versions are uncontrolled except when accessed directly from the Document Repository.<br>Printed versions are uncontrolled except when stamped "CONTROLLED COPY" in red. |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| DESCRIPTION:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | DFN8, 2.0X2.0, 0.5MM PITCH PAGE 1 OF 1 |                                                                                                                                                                                     |  |  |  |

| ON Semiconductor and (1) are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries.<br>ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. ON Semiconductor does not convey any license under its patent rights nor the |                                        |                                                                                                                                                                                     |  |  |  |

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <u>www.onsemi.com/site/pdf/Patent-Marking.pdf</u>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor date sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use a a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor houteds for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries

#### PUBLICATION ORDERING INFORMATION

#### LITERATURE FULFILLMENT:

#### TECHNICAL SUPPORT

ON Semiconductor Website: www.onsemi.com

Email Requests to: orderlit@onsemi.com

North American Technical Support: Voice Mail: 1 800–282–9855 Toll Free USA/Canada Phone: 011 421 33 790 2910 Europe, Middle East and Africa Technical Support: Phone: 00421 33 790 2910 For additional information, please contact your local Sales Representative