## WS7808QM-14/TR

### 0.1GHz–3GHz SP8T Diversity Antenna Switch with MIPI RFFE Interface

#### Descriptions

The WS7808QM-14/TR is a single-pole, eight-throw (SP8T) antenna switch with a Mobile Industry Processor Interface (MIPI). Using advanced switching technologies, the WS7808QM-14/TR maintains low insertion loss and high isolation for receive switching path. The high linearity performance and low insertion loss achieved by the WS7808QM-14/TR makes it an ideal choice for WCDMA and LTE applications.

The WS7808QM-14/TR is manufactured in a compact 2.0x2.0x0.55mm, 14-pin surface mount Quad Flat No-Lead (QFN) package.

### Features

- Small, low profile package 2.0mm x 2.0mm x 0.55mm

- Working frequency up to 3GHz

- Very low insertion loss

- Excellent isolation performance

- Low power consumption

- Exceptional linearity performance for 3G/4G application

- Very good ESD performance

#### Applications

- Cell phones

- Tablets

- Other RF front-end modules

http://omnivision-group.com

QFN 2.0x2.0-14L (Bottom view)

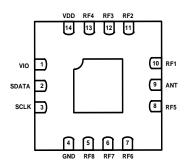

Pin configuration (Top view)

D= Device code \* = Month code (A~Z) Marking (Top view)

#### **Order information**

| Device         | Package         | Shipping        |

|----------------|-----------------|-----------------|

| WS7808QM-14/TR | QFN 2.0x2.0-14L | 3000/Reel &Tape |

#### **Pin information**

| in | Function | Description            | Transparent top view      |

|----|----------|------------------------|---------------------------|

| 1  | VIO      | MIPI Interface voltage |                           |

|    | SDATA    | Data input/output      |                           |

|    | SCLK     | Clock signal           |                           |

|    | GND      | Ground                 | VDD RF4 RF3 RF2           |

|    | RF8      | RF I/O path 8          | 14 13 12 11               |

| 6  | RF7      | RF I/O path 7          |                           |

| 7  | RF6      | RF I/O path 6          |                           |

| 8  | RF5      | RF I/O path 5          | SDATA 2 9 A<br>SCLK 3 8 F |

| )  | ANT      | Antenna input/output   |                           |

| )  | RF1      | RF I/O path 1          | 4 5 6 7                   |

|    | RF2      | RF I/O path 2          | GND RF8 RF7 RF6           |

| 2  | RF3      | RF I/O path 3          |                           |

| 3  | RF4      | RF I/O path 4          |                           |

| 4  | VDD      | VDD                    |                           |

Note 1: Bottom ground paddles must be connected to ground.

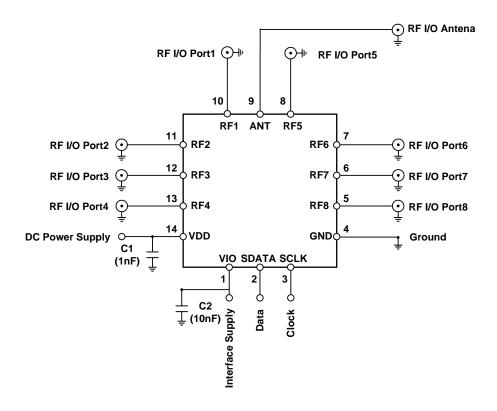

### **Application information**

#### WS7808QM-14/TR Evaluation Board Schematic

Note 2: filter capacitor is needed on VDD and VIO respectively

### **Recommended operating conditions**

| Parameters                         | Conditions                   | Spec      | ons | Unit      |    |

|------------------------------------|------------------------------|-----------|-----|-----------|----|

|                                    |                              | Min.      | Тур | Max.      |    |

| ESD Rating                         |                              |           |     |           |    |

| ESD All Pins                       | HBM, JESD22-A114             | -1000     |     | +1000     | V  |

|                                    | CDM                          | -500      |     | +500      | V  |

| Power Supply                       |                              |           |     |           |    |

| Power Supply Voltage               | Operating Voltage            | 2.5       | 2.8 | 3.6       | V  |

| Power Supply Current               | VDD≤3.0V                     |           | 29  | 44        | μA |

| Interface supply voltage level     |                              | 1.65      | 1.8 | 1.95      | V  |

| Control Voltage                    |                              |           | •   |           |    |

| SCLK port voltage                  |                              | 0.8 x VIO |     | VIO       | V  |

| SDATA port voltage                 |                              | 0         |     | 0.2 x VIO | V  |

| RF Impedance                       |                              |           |     |           |    |

| RF Port Input and Output Impedance |                              |           | 50  |           | Ω  |

|                                    | 50% of final control voltage |           |     |           |    |

| Turn-On Switching Time             | to 90% of final RF power,    |           | 5   |           | μs |

|                                    | switching between RF ports   |           |     |           |    |

### Absolute maximum ratings

Maximum ratings are absolute ratings, exceeding only one of these values may cause irreversible damage to the integrated circuit.

| Items                                     | Value        | Unit |

|-------------------------------------------|--------------|------|

| VDD Voltage                               | -0.3 to +4.0 | V    |

| SDATA, SCLK                               | -0.3 to +2.0 | V    |

| Maximum Input Power                       | Value        | Unit |

| Momentary, infrequent occurrence, 50 ohms | +29          | dBm  |

| Momentary, infrequent occurrence, 6:1     | +27          | dBm  |

| Continuous Operation, 50 ohms             | +28          | dBm  |

| Continuous Operation, 6:1                 | +26          | dBm  |

| Operation Temperature                     | -40 to +85   | °C   |

| Storage Temperature                       | -65 to +150  | °C   |

| MSL                                       | 3            |      |

| Reflow Times                              | 3            |      |

### **Characteristics (RF spec)**

Nominal test condition unless otherwise stated. All unused ports are  $50\Omega$  terminated. VDD=2.8V, Temp=+25°C, P<sub>IN</sub>=0dBm.

| Parameters                                  | Conditions                                | Spe  | cificati | ions | Unit |  |

|---------------------------------------------|-------------------------------------------|------|----------|------|------|--|

| Parameters                                  | Conditions                                | Min. | Тур.     | Max. | Jint |  |

| Insertion Loss                              | 0.1GHz to 1.0GHz                          |      | 0.40     | 0.55 |      |  |

|                                             | 1.0GHz to 2.0GHz                          |      | 0.45     | 0.65 | dB   |  |

| (ANT to RFX)                                | 2.0GHz to 2.7GHz                          |      | 0.70     | 1.00 |      |  |

| Isolation                                   | 0.1GHz to 1.0GHz                          | 28   | 33       |      |      |  |

| (ANT to RFX, RFXm to RFXn)                  | 1.0GHz to 2.0GHz                          | 19   | 24       |      | dB   |  |

| (ANT to REA, REALL to REAL)                 | 2.0GHz to 2.7GHz                          | 14   | 19       |      |      |  |

| Input Deturn Loop                           | 0.1GHz to 1.0GHz                          | 19   | 22       |      |      |  |

| Input Return Loss<br>(ANT to RFX)           | 1.0GHz to 2.0GHz                          | 17   | 20       |      | dB   |  |

| (ANT TO REA)                                | 2.0GHz to 2.7GHz                          | 12   | 15       |      |      |  |

| Second Harmonics                            | 0.7GHz to 1.0GHz, P <sub>IN</sub> =+26dBm | 80   | 90       |      |      |  |

| (ANT to RFX)                                | 1.0GHz to 2.0GHz, P <sub>IN</sub> =+26dBm | 78   | 88       |      | dBc  |  |

|                                             | 2.0GHz to 2.7GHz, PIN=+26dBm              | 76   | 86       |      |      |  |

| Third Harmonics                             | 0.7GHz to 1.0GHz, P <sub>IN</sub> =+26dBm | 71   | 81       |      |      |  |

| (ANT to RFX)                                | 1.0GHz to 2.0GHz, P <sub>IN</sub> =+26dBm | 69   | 79       |      | dBc  |  |

|                                             | 2.0GHz to 2.7GHz, P <sub>IN</sub> =+26dBm | 67   | 77       |      |      |  |

| 0.1dB Compression Point<br>(ANT to RFX)     | 0.7GHz to 2.7GHz                          |      | +28      |      | dBm  |  |

| 2rd Order Input Intercent Deint             | 0.7GHz to 2.7GHz                          |      |          |      |      |  |

| 3 <sup>rd</sup> Order Input Intercept Point | P <sub>IN</sub> =+26dBm                   |      | 62       |      | dBm  |  |

| (ANT to RFX)                                | $\Delta f = 1 \text{MHz}$                 |      |          |      |      |  |

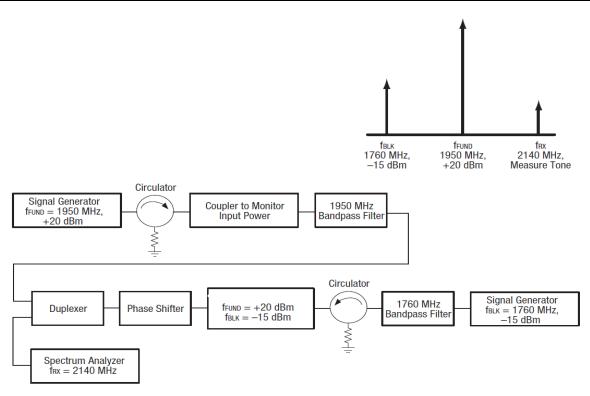

### **IMD2** Test Conditions

Nominal test condition unless otherwise stated. All unused ports are  $50\Omega$  terminated.

VDD=2.8V, Temp=+25°C, P<sub>IN</sub>=0dBm.

| Band | Transmit<br>Frequency<br>(MHz) | Transmit<br>Power<br>(dBm) | Frequency<br>Blocker,<br>Low<br>(MHz) | Frequency<br>Blocker,<br>High<br>(MHz) | Power<br>Blocker<br>(dBm) | Receive<br>Frequency<br>(MHz) |

|------|--------------------------------|----------------------------|---------------------------------------|----------------------------------------|---------------------------|-------------------------------|

| 1    | 1950.0                         |                            | 190                                   | 4090                                   |                           | 2140.0                        |

| 2    | 1880.0                         |                            | 80                                    | 3840                                   | 15                        | 1960.0                        |

| 4    | 1732.0                         | +20                        | 400                                   | 3864                                   |                           | 2132.0                        |

| 5    | 836.5                          | +20                        | 45                                    | 1718                                   | -15                       | 881.5                         |

| 7    | 2535.0                         |                            | 120                                   | 5187                                   |                           | 2655.0                        |

| 8    | 897.0                          |                            | 45                                    | 1839                                   |                           | 942.0                         |

### **IMD3 Test Conditions**

Nominal test condition unless otherwise stated. All unused ports are  $50\Omega$  terminated.

VDD=2.8V, Temp =+25°C, P<sub>IN</sub>=0dBm.

| Band | Transmit<br>Frequency | Transmit<br>Power | Frequency<br>Blocker, | Power<br>Blocker | Receive<br>Frequency |

|------|-----------------------|-------------------|-----------------------|------------------|----------------------|

|      | (MHz)                 | (dBm)             | (MHz)                 | (dBm)            | (MHz)                |

| 1    | 1950.0                |                   | 1760.0                |                  | 2140.0               |

| 2    | 1880.0                |                   | 1800.0                |                  | 1960.0               |

| 4    | 1732.0                | +20               | 1332.0                | -15              | 2132.0               |

| 5    | 836.5                 | +20               | 791.5                 | -15              | 881.5                |

| 7    | 2535.0                |                   | 2415.0                |                  | 2655.0               |

| 8    | 897.0                 |                   | 852.0                 |                  | 942.0                |

## **Triple Beat Ratio Test Conditions**

| Band | Transmit<br>Frequency<br>1<br>(MHz) | Transmit<br>Power 1<br>(dBm) | Transmit<br>Frequency<br>2<br>(MHz) | Transmit<br>Power 2<br>(dBm) | Frequency<br>Blocker @<br>ANT<br>(MHz) | Power<br>Blocker<br>(dBm) | TBR<br>Product<br>Frequency<br>(MHz) |

|------|-------------------------------------|------------------------------|-------------------------------------|------------------------------|----------------------------------------|---------------------------|--------------------------------------|

| 2    | 1880.0                              | +21.5                        | 1881.0                              | +21.5                        | 1960.0                                 | -30                       | $1960.0 \pm 1$                       |

| 5    | 836.5                               | 721.0                        | 881.5                               | +21.5                        | 881.5                                  | -30                       | 881.5±1                              |

#### Typical Third Order Intermodulation Test Setup

### Power ON and OFF sequence

It is very important that the user adheres to the correct power-on/off sequence in order to avoid damaging the device (Note 3).

#### Power ON

- 1) Apply voltage supply VDD

- 2) Wait 100 $\mu s$  or greater and then apply logic supply VIO

- 3) Wait 10µs or greater and then apply RFFE

- 4) Wait 5µs or greater after RFFE Trigger falling edge and then apply the RF Signal

#### Power OFF

- 1) Remove the RF Signal

- 2) Remove RFFE

- 3) Remove logic supply VIO

- 4) Remove voltage supply VDD

## WS7808QM-14/TR

|              | VDD V<br>ON O | IO RE<br>N TRIG |                          |        |           |

|--------------|---------------|-----------------|--------------------------|--------|-----------|

| VDD -        | ≥100us        | ↑<br> <br> <br> |                          |        | ≥100us    |

| VIO -        |               | /<br> <br>      |                          |        |           |

| -            |               | 1               |                          |        |           |

| Slave State  | Shut Down     | Start Up        |                          | Active | Shut Down |

| SDATA,SCLK - |               | ≥10us           | <del>∢&gt;</del><br>≥5us |        |           |

| RF Signal-   |               |                 |                          |        |           |

**Note 3:** VIO can be applied to the device after VDD or removed before VDD .It is important to wait 10 $\mu$ s after VIO & VDD are applied before sending SDATA to ensure correction data transmission. The minimum time between a power up and power down sequence (and vice versa) is  $\geq$  100us.

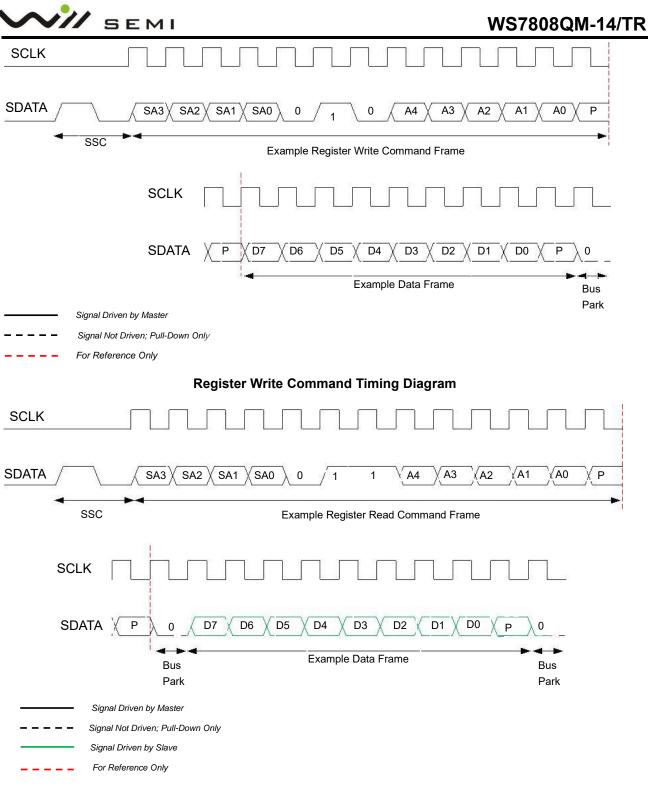

# **Command Sequence Bit Definitions**

|       |     |           |    |           |               |            | Devite         |     |            | Ex     |     | Extended Operation |        |     |  |

|-------|-----|-----------|----|-----------|---------------|------------|----------------|-----|------------|--------|-----|--------------------|--------|-----|--|

| Туре  | SSC | C11-C8    | C7 | C6-C5     | C4            | C3-C0      | Parity<br>Bits | BPC | DA7(1)-    | Parity | BPC | DA7(n)-            | Parity | врс |  |

|       |     |           |    |           |               |            | Dits           |     | DA0(1)     | Bits   | BFC | DA0(n)             | Bits   | BPC |  |

| Reg_0 | Y   | 6 A [2-0] | 1  | Data[6:5] | Dete[4]       | Data{3:0]  | Y              | Y   |            |        |     |                    |        |     |  |

| Write | Ţ   | SA[3:0]   | 1  | Data[0.5] | Data[4]       | Data(3.0]  | T              | T   | -          | -      | -   | -                  | -      | -   |  |

| Reg_1 | Y   | 6 A [2:0] | 0  | 10        | Adds[4]       | Data (2:01 | Y              |     | Dete[7:0]  |        |     |                    | Y      | ×   |  |

| Write | ř   | SA[3:0]   | 0  | 10        | Addr[4]       | Data{3:0]  | ř              | -   | Data[7:0]  | -      | -   | -                  | Ŷ      | Ŷ   |  |

| Reg   | Y   | 0.412-01  | 0  | 44        | ۵ ما ما مر ۸۱ | D-t-(2-0)  | V              | V   | Data [7:0] |        |     |                    | V      | ×   |  |

| Read  | Ŷ   | SA[3:0]   | 0  | 11        | Addr[4]       | Data{3:0]  | Y              | Y   | Data[7:0]  | -      | -   | -                  | Y      | Ŷ   |  |

Legend:

SSC = Sequence start command DA = Data/address frame bits BC = Byte count (# of consecutive addresses)

C = Command frame bits BPC = Bus park cycle

Register Read Command Timing Diagram

## **Register Truth Table (ANT)**

| Mode      |    |    |    | Regist | er Bits |    |    |    |

|-----------|----|----|----|--------|---------|----|----|----|

| wode      | D7 | D6 | D5 | D4     | D3      | D2 | D1 | D0 |

| Isolation |    | 0  | 0  | 0      | 0       | 0  | 0  | 0  |

| RF1       |    | 0  | 0  | 0      | 0       | 0  | 1  | 0  |

| RF2       |    | 0  | 0  | 0      | 1       | 0  | 1  | 0  |

| RF3       |    | 0  | 0  | 0      | 1       | 1  | 1  | 0  |

| RF4       |    | 0  | 0  | 0      | 1       | 0  | 1  | 1  |

| RF5       |    | 0  | 0  | 0      | 0       | 0  | 0  | 1  |

| RF6       |    | 0  | 0  | 0      | 1       | 0  | 0  | 1  |

| RF7       |    | 0  | 0  | 0      | 0       | 1  | 1  | 0  |

| RF8       |    | 0  | 0  | 0      | 0       | 1  | 0  | 0  |

# **Register Description and Programming**

| Registe             | r                |                          |                                                                                                                                                                            | Default       |

|---------------------|------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Name                | Address<br>(Hex) | Parameter                | Description                                                                                                                                                                | Name (Binary) |

| Register            | 0000             | MODE_CTRL                | Bits[6:0]:<br>See Register Truth Table for logic                                                                                                                           | 0000000       |

|                     |                  | SOFTWARE RESET           | Bits[7]:<br>Resets all data to default values except for<br>USID, GSID, or the<br>contents of the PM_TRIG Register.<br>0 = Normal operation (active)<br>1 = Software reset | 0             |

|                     |                  | COMMAND_FRAME_PARITY_ERR | Bit[6]:<br>Command sequence received with parity<br>error – discard command.                                                                                               | 0             |

|                     |                  | COMMAND_LENGTH_ERR       | Bit[5]:<br>Command length error.                                                                                                                                           | 0             |

| RFFE_STATUS         | 001A             | ADDRESS_FRAME_PARITY_ERR | Bit[4]:<br>Address frame parity error =1.                                                                                                                                  | 0             |

|                     |                  | DATA_FRAME_PARITY_ERR    | Bit[3]:<br>Data frame with parity error.                                                                                                                                   | 0             |

|                     |                  | READ_UNUSED_REG          | Bit[2]:<br>Read command to an invalid address.                                                                                                                             | 0             |

|                     |                  | WRITE_UNUSED_REG         | Bit[1]:<br>Write command to an invalid address.                                                                                                                            | 0             |

|                     |                  | BID_GID_ERR              | Bit[0]:<br>Read command with a BROADCAST_ID<br>(refer to the MIPI Alliance<br>Specification) or GSID.                                                                      | 0             |

| PM_TRIG<br>(Note 4) | 001C             | PWR_MODE                 | Bits[7:6]:<br>00 = Normal operation (active)<br>01 = Default settings (startup)<br>10 = Low power (low power)<br>11 = Reserved                                             | 00            |

## WS7808QM-14/TR

|                      |      | Trigger_Mask_2       | Bit[5]:<br>If this bit is set, trigger 2 is disabled. When<br>all triggers are disabled, if writing to a<br>register that is associated with trigger 2,<br>the data goes directly to the destination<br>register.   | 0        |  |

|----------------------|------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|

|                      |      | Trigger_Mask_1       | Bit[4]:<br>If this bit is set, trigger 1 is disabled. When<br>all triggers are disabled, if writing to a<br>register that is associated with trigger 1,<br>the data goes directly to the destination<br>register.   | 0        |  |

|                      |      | Trigger_Mask_0       | Bit[3]:<br>If this bit is set, trigger 0 is disabled. When<br>all triggers are disabled, if writing to a<br>register that is associated with trigger 0,<br>the data goes directly to the destination<br>register.   | 0        |  |

|                      |      | Trigger_2            | Bit[2]:<br>If this bit is set, data is loaded into the<br>trigger 2 registers.                                                                                                                                      | 0        |  |

|                      |      | Trigger_1            | Bit[1]:<br>If this bit is set, data is loaded into the<br>trigger 1 registers.                                                                                                                                      | 0        |  |

|                      |      | Trigger_0            | Bit[0]:<br>If this bit is set, data is loaded into the<br>trigger 0 registers.                                                                                                                                      | 0        |  |

| PRODUCT_ID           | 001D | PRODUCT_ID           | Bits[7:0]:<br>This is a read-only register. However,<br>during the programming of the Unique<br>Slave Identifier (USID), a write command<br>sequence is performed on this register but<br>the value is not changed. | 00001000 |  |

| MANUFAC-<br>TURER_ID | 001E | MANUFACTURER_ID[7:0] | Bits[7:0]:<br>Read-only register                                                                                                                                                                                    | 10111100 |  |

| MAN_USID             | 001F | Reserved             | Bits[7:6]:<br>Reserved                                                                                                                                                                                              | 00       |  |

|                      |      | MANUFACTURER_ID[9:8] | Bits[5:4]:<br>Read-only register                                                                                                                                                                                    | 11       |  |

|                      |      | USID                 | Bits[3:0]:<br>Programmable USID. A write to these bits<br>programs the USID.                                                                                                                                        | 1010     |  |

**Note 4**: Unlike the complete independence between triggers 0, 1, and 2, and also between the associated trigger masks 0, 1, and 2, respectively, as described in the MIPI RFFE Specification this device uses additional interactions between the provided trigger functions. The delayed application of updated data to all triggerable registers in this device may be accomplished using any of the three triggers (0, 1, or 2), provided that the particular triggerable used is not currently masked off. If multiple triggers are enabled, any or all of those are sufficient to cause the data to be transferred from shadow registers to destination registers for all triggerable registers in the device. It is also necessary to disable all three triggers (i.e., set all three trigger masks) to ensure that data written to any triggerable register will

SEMI

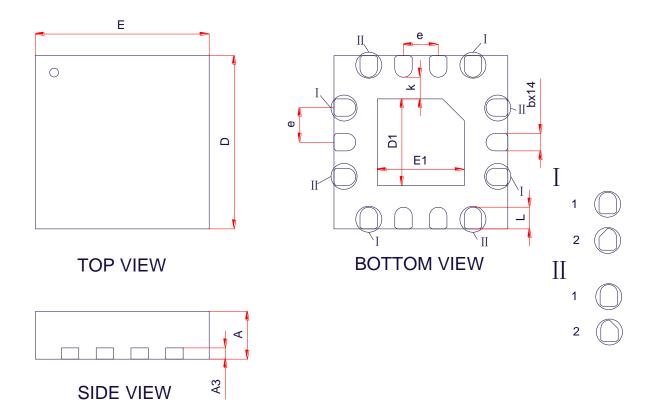

**Package Dimensions**

| Cumhal | Dimensions in Millimeters |      |      |  |  |  |

|--------|---------------------------|------|------|--|--|--|

| Symbol | Min.                      | Тур. | Max. |  |  |  |

| A      | 0.50                      | 0.55 | 0.60 |  |  |  |

| A3     | 0.152Ref.                 |      |      |  |  |  |

| D      | 1.95                      | 2.00 | 2.05 |  |  |  |

| E      | 1.95                      | 2.00 | 2.05 |  |  |  |

| D1     | 0.90                      | 1.00 | 1.10 |  |  |  |

| E1     | 0.90                      | 1.00 | 1.10 |  |  |  |

| b      | 0.15                      | 0.20 | 0.25 |  |  |  |

| е      | 0.40 BSC                  |      |      |  |  |  |

| L      | 0.19                      | 0.25 | 0.30 |  |  |  |

| К      | 0.20                      | 0.25 | 0.31 |  |  |  |

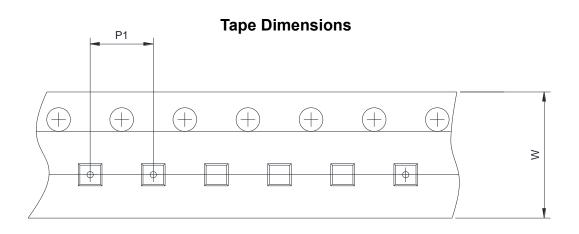

#### **Tape and Reel Information**

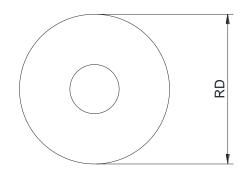

### **Reel Dimensions**

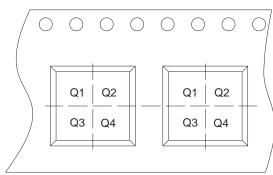

# **Quadrant Assignments For PIN1 Orientation In Tape**

User Direction of Feed

| RD   | Reel Dimension                          | ✓ 7inch | 13inch |        |    |

|------|-----------------------------------------|---------|--------|--------|----|

| W    | Overall width of the carrier tape       | 🕑 8mm   | 🗌 12mm | 🗌 16mm |    |

| P1   | Pitch between successive cavity centers | 2mm     | ✓ 4mm  | 8mm    |    |

| Pin1 | Pin1 Quadrant                           | ✓ Q1    | Q2     | 🗌 Q3   | Q4 |