# 16-Bit ANALOG-TO-DIGITAL CONVERTER with Onboard Reference (compatible to ADS1110A0)

## **FEATURES**

- D COMPLETE DATA ACQUISITION SYSTEM IN A TINY SOT23-6 PACKAGE

- D ONBOARD REFERENCE: Accuracy: 2.048V ±0.05% Drift: 5ppm/°C

- D ONBOARD PGA

- D ONBOARD OSCILLATOR

- D 16-BITS NO MISSING CODES

- D INL: 0.01% of FSR max

- **D** CONTINUOUS SELF-CALIBRATION

- **D SINGLE-CYCLE CONVERSION**

- D PROGRAMMABLE DATA RATE: 15SPS TO 240SPS

- D I <sup>2</sup>C INTERFACE—EIGHT AVAILABLE ADDRESSES

- D POWER SUPPLY: 2.7V to 5.5V

- D LOW CURRENT CONSUMPTION: 240 x A

# DESCRIPTION

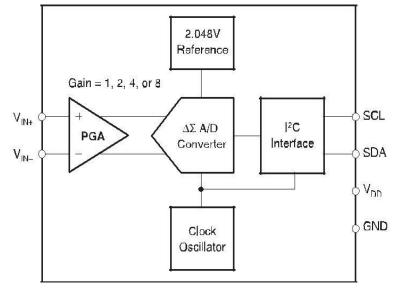

The HT8110A is a precision, continuously self-calibrating Analog-to-Digital (A/D) converter with differential inputs and up to 16 bits of resolution in a small SOT23-6 package. The onboard 2.048V reference provides an input range of

$\pm 2.048V$  differentially. The HT8110A uses an I<sup>2</sup> C-compatible serial interface and operates from a single power supply ranging from 2.7V to 5.5V.

The HT8110A can perform conversions at rates of 15, 30, 60, or 240 samples per second. The onboard programmable gain amplifier (PGA), which offers gains of up to 8, allows smaller signals to be measured with high resolution. In single-conversion mode, the HT8110A automatically powers down after a conversion, greatly reducing current consumption during idle periods.

The HT8110A is designed for applications requiring highresolution measurement, where space and power consumption are major considerations. Typical applications include portable instrumentation, industrial process control, and smart transmitters.

## **APPLICATIONS**

- D **PORTABLE INSTRUMENTATION**

- D INDUSTRIAL PROCESS CONTROL

- D SMART TRANSMITTERS

- D CONSUMER GOODS

- D FACTORY AUTOMATION

- D TEMPERATURE MEASUREMENT

### ABSOLUTE MAXIMUM RATINGS

| VDD to GND                        | -0.3V to +6V         |

|-----------------------------------|----------------------|

| Input Current                     | 100mA, Momentary     |

| Input Current                     | 10mA, Continuous     |

| Voltage to GND, VIN+, VIN-        | -0.3V to V DD + 0.3V |

| Voltage to GND, SDA, SCL          | −0.5V to 6V          |

| Maximum Junction Temperature      | +150°C               |

| Operating Temperature Range       | −40 °C to +125°C     |

| Storage Temperature Range         | −60 °C to +150°C     |

| Lead Temperature (soldering, 10s) | +300°C               |

### PACKAGE/ORDERING INFORMATION

| PRODUCT  | 2<br>I C<br>AD DR ESS | PACKAGE-LEA<br>D |    | SPECIFIED<br>TEMPERATURE<br>RANGE |

|----------|-----------------------|------------------|----|-----------------------------------|

| HT8110A0 | 1001 000              | SOT23-6          | RZ | −40 °C to +85°C                   |

### **ELECTRICAL CHARACTERISTICS**

All specifications at -40 °C to +85°C, VDD = 5V, and all PGAs, unless otherwise noted.

|                                        |                                         | HT8110A    |                   |             |                |

|----------------------------------------|-----------------------------------------|------------|-------------------|-------------|----------------|

| PARAMETER                              | CONDITIONS                              | MIN        | TYP               | MAX         | UNIT           |

| ANALOG INPUT                           |                                         |            |                   |             |                |

| Full-Scale Input Voltage               | (V N+) - (V N-)                         |            | ±2.048/PGA        |             | V              |

| Analog Input Voltage                   | V N+ to GND or $V N-$ to GND            | GND - 0.2  |                   | VDD + 0.2   | V              |

| Differential Input Impedance           |                                         |            | 2.8/PGA           |             | MΩ             |

| Common-Mode Input Impedance            | PGA = 1                                 |            | 3.5               |             | MΩ             |

|                                        | PGA=2                                   | ]          | 3.5               |             | MΩ             |

|                                        | PGA = 4                                 | ]          | 1.8               |             | MΩ             |

|                                        | PGA = 8                                 |            | 0.9               |             | MΩ             |

| SYSTEM PERFORMANCE                     |                                         |            |                   |             |                |

| Resolution and No Missing Codes        | DR = 00                                 | 12         |                   | 12          | Bits           |

|                                        | DR = 01<br>DR = 10                      | 14<br>15   |                   | 14<br>15    | Bits<br>Bits   |

|                                        | DR = 10<br>DR = 11                      | 15         |                   | 15          | Bits           |

| Data Data                              |                                         | -          | 240               |             |                |

| Data Rate                              | DR = 00<br>DR = 01                      | 180<br>45  | 240<br>60         | 308<br>77   | SPS<br>SPS     |

|                                        | DR = 01<br>DR = 10                      | 43         | 30                | 39          | SPS            |

|                                        | DR = 11                                 | 11         | 15                | 20          | SPS            |

| Output Noise                           |                                         |            | al Characteristic | -           |                |

|                                        |                                         | 000 . ypic | 1                 | 1           | % of FSR       |

| Integral Nonlinearity<br>Offset Error  | DR = 11, PGA = 1, End Point Fit PGA = 1 |            | ±0.004<br>1.2     | ±0.010<br>8 | % of FSR<br>mV |

|                                        | PGA = 2                                 |            | 0.7               | 4           | mV             |

|                                        | PGA = 4                                 |            | 0.5               | 2.5         | mV             |

|                                        | PGA = 8                                 |            | 0.4               | 1.5         | mV             |

| Offset Drift                           | PGA = 1                                 |            | 1.2               |             | ∞V/°C          |

|                                        | PGA=2                                   |            | 0.6               |             | ∞V/°C          |

|                                        | PGA = 4                                 |            | 0.3               |             | ∞V/°C          |

|                                        | PGA = 8                                 |            | 0.3               |             | ∞V/°C          |

| Offset vs VDD                          | PGA = 1                                 |            | 800               |             | x/V            |

|                                        | PGA = 2                                 |            | 400               |             | ∞V/V           |

|                                        | PGA = 4                                 |            | 200               |             | ∞V/V           |

|                                        | PGA = 8                                 |            | 150               |             | ∞V/V           |

| Gain Error                             |                                         |            | 0.05              | 0.40        | %              |

| PGA Gain Error Match                   | Match Between Any Two PGA Gains         |            | 0.02              | 0.10        | %              |

| Gain Error Drift                       |                                         |            | 5                 | 40          | ppm/°C         |

| Gain vs VDD                            |                                         |            | 80                |             | ppm/V          |

| Common-Mode Rejection                  | At DC and PGA = 8                       | 95         | 105               |             | dB             |

|                                        | At DC and PGA = 1                       |            | 100               |             | dB             |

| DIGITAL INPUT/OUTPUT                   |                                         |            |                   |             |                |

| Logic Level                            |                                         |            |                   | _           |                |

| IH                                     |                                         | 0.7 □ VDD  |                   | 6           | V              |

| IL OI                                  |                                         | GND - 0.5  |                   | 0.3 🗆 VDD   | V              |

| OL<br>Input Leakage                    | I <sub>OL</sub> = 3mA                   | GND        |                   | 0.4         | V              |

| IH                                     | VIH=5.5V                                | 1          | '  '              | 10          | ∞A             |

| чт<br>И                                | VIL = GND                               | -10        |                   |             | ∞A             |

| POWER-SUPPLY REQUIREMENTS              | V                                       |            |                   |             | 1              |

| Power Supply Voltage                   |                                         | 0.7        |                   | 5 5         |                |

| Power-Supply Voltage<br>Supply Current | Power Down                              | 2.7        | 0.05              | 5.5<br>2    | ∨<br>∞A        |

| Cappy Current                          | Active Mode                             |            | 240               | 350         | ∞A<br>∞A       |

| Deven Dissis ation                     | VDD = 5.0V                              |            |                   |             |                |

| Power Dissipation                      |                                         |            | 1.2<br>0.675      | 1.75        | mW<br>mW       |

| (1)                                    | V <sub>DD</sub> = 3.0V                  | I          | 0.075             | I           | 1 11174        |

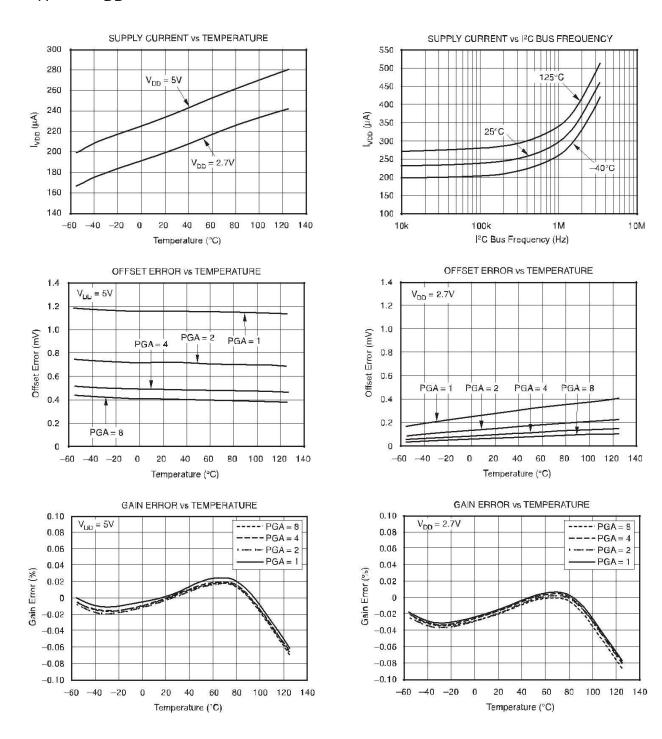

### **TYPICAL CHARACTERISTICS**

At TA =  $25^{\circ}$ C and VDD = 5V, unless otherwise noted.

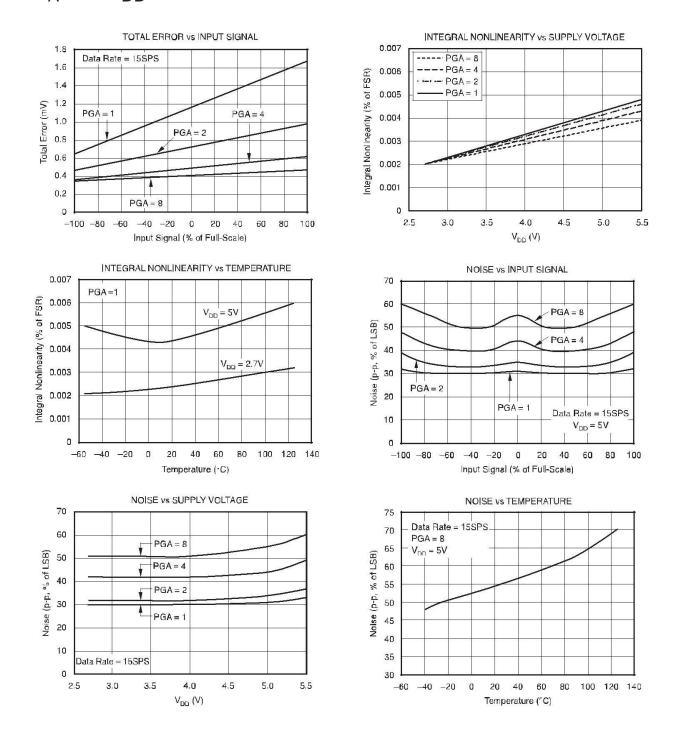

### **TYPICAL CHARACTERISTICS (continued)**

At TA = 25°C and VDD = 5V, unless otherwise noted.

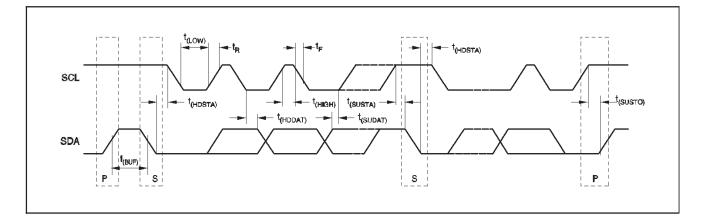

## Figure 1. I <sup>2</sup>C Timing Diagram

|                                                                                               |         | FAST MODE |     | HIGH-SPEED MODE |     |       |

|-----------------------------------------------------------------------------------------------|---------|-----------|-----|-----------------|-----|-------|

| PARAMETER                                                                                     |         | MIN       | MAX | MIN             | MAX | UNITS |

| SCLK operating frequency                                                                      | (SCLK)  |           | 0.4 |                 | 3.4 | MHz   |

| Bus free time between START and STOP condition                                                | (BUF)   | 600       |     | 160             |     | ns    |

| Hold time after repeated START condition.<br>After this period, the first clock is generated. | (HDSTA) | 600       |     | 160             |     | ns    |

| Repeated START condition setup time                                                           | (SUSTA) | 600       |     | 160             | 1   | ns    |

| Stop condition setup time                                                                     | (SUSTO) | 600       |     | 160             |     | ns    |

| Data hold time                                                                                | (HDDAT) | 0         |     | 0               |     | ns    |

| Data setup time                                                                               | (SUDAT) | 100       |     | 10              |     | ns    |

| SCLK clock LOW period                                                                         | (LOW)   | 1300      |     | 160             |     | ns    |

| SCLK clock HIGH period                                                                        | (HIGH)  | 600       |     | 60              |     | ns    |

| Clock/data fall time                                                                          | tF      |           | 300 |                 | 160 | ns    |

| Clock/data rise time                                                                          | tR      |           | 300 |                 | 160 | ns    |

Table 3. Timing Diagram Definitions

#### **CONFIGURATION REGISTER**

The 8-bit configuration register can be used to control the HT8110A's operating mode, data rate, and PGA settings. The configuration register format is shown in

Table 5. The default setting is 8CH.

| BIT      | 7       | 6 | 5 | 4  | 3   | 2   | 1    | 0     |

|----------|---------|---|---|----|-----|-----|------|-------|

| NAME     | ST/DRDY | 0 | 0 | SC | DR1 | DR0 | PGA1 | PGA 0 |

| DEFAU LT | 1       | 0 | 0 | 0  | 1   | 1   | 0    | 0     |

Table 5. Configuration Register

#### Bit 7: ST/DRDY

The meaning of the ST/DRDY bit depends on whether it is being written to or read from.

In single conversion mode, writing a 1 to the ST/DRDY bit causes a conversion to start, and writing a 0 has no effect. In continuous conversion mode, the HT8110A ignores the value written to ST/DRDY.

When read, ST/DRDY indicates whether the data in the output register is new data. If ST/DRDY is 0, the data just read from the output register is new, and has not been read before. If ST/DRDY is 1, the data just read from the output register has been read before.

The HT8110A sets ST/DRDY to 0 when it writes data into the output register. It sets ST/DRDY to 1 after any of the bits in the configuration register have been read. (Note that the read value of the bit is independent of the value written to this bit.)

In continuous-conversion mode, use ST/DRDY to determine when new conversion data is ready. If ST/DRDY is 1, the data in the output register has already been read, and is not new. If it is 0, the data in the output register is new, and has not yet been read.

In single-conversion mode, use ST/DRDY to determine when a conversion has completed. If ST/DRDY is 1, the output register data is old, and the conversion is still in process; if it is 0, the output register data is the result of the new conversion. Note that the output register is returned from the HT8110A before the configuration register. The state of the ST/DRDY bit applies to the data just read from the output register, and not to the data from the next read operation.

#### Bits 6-5: Reserved

Bits 6 and 5 must be set to zero.

#### Bit 4: SC

SC controls whether the HT8110A is in continuous conversion or single conversion mode. When SC is 1, the HT8110A is in single conversion mode; when SC is 0, the HT8110A is in continuous conversion mode. The default setting is 0.

#### Bits 3-2: DR

Bits 3 and 2 control the HT8110A's data rate, as shown in Table 6.

| DR 1         | DR 0         | DATA RATE |

|--------------|--------------|-----------|

| 0            | 0            | 240SPS    |

| 0            | 1            | 60SPS     |

| 1            | 0            | 30SPS     |

| <b>1</b> (1) | <b>1</b> (1) | 15SPS     |

Default setting.

Table 6. DR Bits

#### Bits 1-0: PGA

Bits 1 and 0 control the HT8110A's gain setting, as shown in Table 7.

| PGA1                  | PGA0                  | GAIN                  |

|-----------------------|-----------------------|-----------------------|

| 0 <sup>(1)</sup><br>0 | 0 <sup>(1)</sup><br>1 | 1 <sup>(1)</sup><br>2 |

| 1                     | 0                     | 4                     |

| 1                     | 1                     | 8                     |

Default setting.

Table 7. PGA Bits

#### **READING FROM THE HT8110A**

To read the output register and the configuration register from the HT8110A, address the HT8110A for reading, then read three bytes. The first two bytes will be the output register's contents, and the third will be the configuration register's contents.

It is not required to read the configuration register byte. It is permissible to read fewer than three bytes during a read operation.

Reading more than three bytes from the HT8110A has

no effect. All bytes following the third will be FFH.

It is possible to ignore the ST/DRDY bit and read data from the HT8110A's output register at any time, without regard to whether a new conversion is complete. If the output register is read more than once during a conversion cycle, it will return the same data each time. New data will be returned only when the output register has been updated.

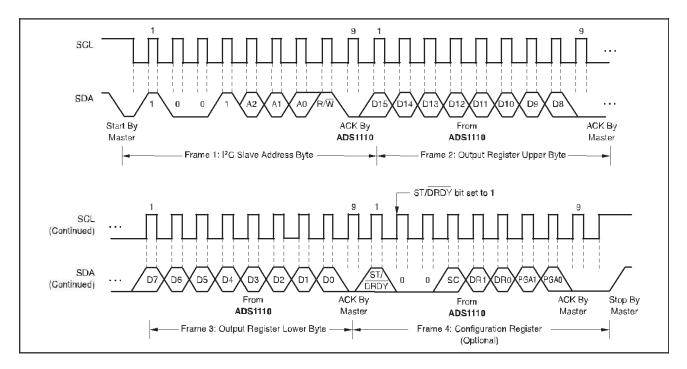

A timing diagram of a typical HT8110A read operation is shown in Figure 2.

#### WRITING TO THE HT8110A

To write to the configuration register, address the HT8110A for writing, and send one byte. The byte will be written to the configuration register. Note that the output register cannot be written to.

Writing more than one byte to the HT8110A has no effect. The HT8110A will ignore any bytes sent to it after the first one, and it will only acknowledge the first byte.

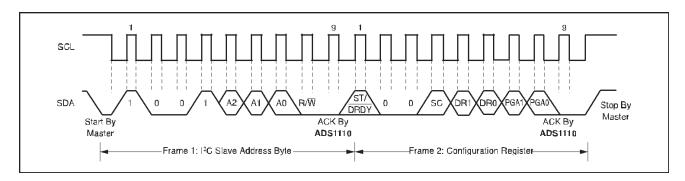

A timing diagram of a typical HT8110A write operation is shown in Figure 3.

Figure 2. Timing Diagram for Reading From the HT8110A

Figure 3. Timing Diagram for Writing To the HT8110A

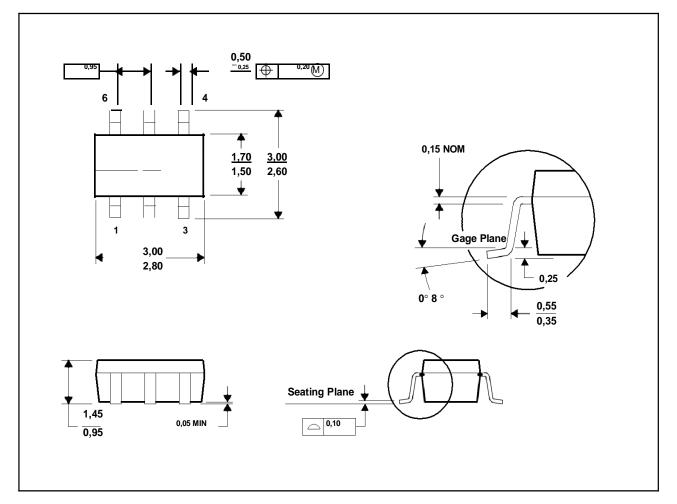

### SOT23-6

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion.

- D. Leads 1, 2, 3 may be wider than leads 4, 5, 6 for package orientation.